东芝开发了具有低导通电阻和高可靠性的肖特基势垒二极管内嵌式SiC MOSFET

2022年12月9日

东芝电子元件及存储装置株式会社

东芝株式会社

日本川崎——东芝电子元件及存储装置株式会社和东芝株式会社(Toshiba Corporation,统称“东芝”)共同研发出一种SiC金属氧化物半导体场效应晶体管(MOSFET),其将嵌入式肖特基势垒二极管(SBD)排列成格子花纹(check-pattern embedded SBD),以降低导通电阻并提高可靠性。东芝实验证实,与现有SiC MOSFET相比,这种设计结构在不影响可靠性的情况下[1],可将导通电阻[2](RonA)降低约20%。

功率器件是管理各种电子设备电能,降低功耗以及实现碳中和社会的重要元器件。碳化硅被广泛视为下一代功率器件的材料,因为碳化硅相较于硅材料可进一步提高电压并降低损耗。虽然碳化硅功率器件目前主要用于列车逆变器,但其具有极为广泛的应用前景,包括车辆电气化和工业设备小型化。然而,必须首先解决一个问题:SiC MOSFET反向操作期间,体二极管双极性导通会造成导通电阻性能下降。

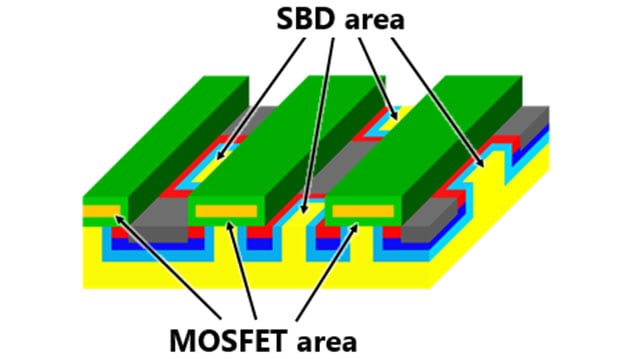

东芝电子元件及存储装置株式会社开发了一种将肖特基势垒二极管嵌入MOSFET,使体二极管失活的器件结构,但发现用嵌入式SBD代替MOSFET沟道会降低沟道密度并增加RonA。现在新的内嵌式SBD结构解决了这一问题,东芝证实这种方法显著提高了性能特征。

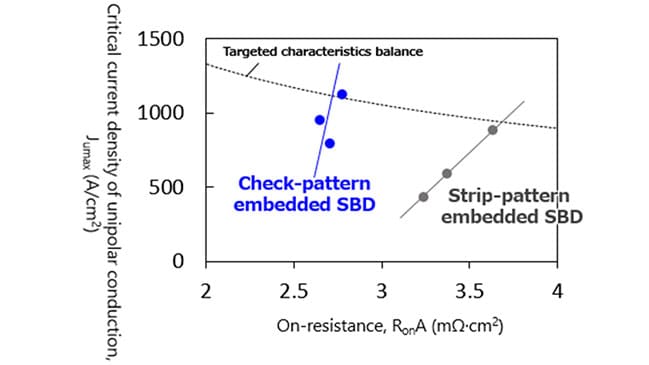

T东芝通过将SBD按格子花纹分布,降低了SBD嵌入式SiC MOSFET的导通损耗,并实现了良好的二极管导电性。优化设计的1.2kV级SBD嵌入式MOSFET导通电流特性评估结果证实,采用格子花纹设计将嵌入式SBD靠近体二极管可以有效限制寄生二极管双极性导通,相同SBD占位面积条件下,单极性反向导通电流是条形花纹排列SBD实现电流的两倍。2.7mΩ・cm2条件下,RonA降低约20%。

SiC MOSFET用于电机驱动应用逆变器时,这种经过验证的改进效果是至关重要的。东芝正在继续进行评估,以改善动态特性和可靠性,并开发有助于实现碳中和的更具吸引力的高性能功率半导体器件。

12月3日至7日,在美国旧金山举行的国际功率半导体会议——第68届IEEE国际电子元件会议上报道了新器件结构的详情。

注:

[1]截至2022年12月,东芝调研。

[2]导通电阻是MOSFET工作期间(导通)漏极和源极之间的电阻值。

新研发的格子花纹嵌入式SBD-SiC MOSFET的示意图

1,2kV级SiC MOSFET特性对比

*本文提及的公司名称、产品名称和服务名称可能是其各自公司的商标。

*本文档中的产品价格和规格、服务内容和联系方式等信息,在公告之日仍为最新信息,如有变更,恕不另行通知。