# 高チャネル移動度と高信頼性を両立させた MOS型 GaN 素子を実現するプロセス技術

Process Technology for MOS Type GaN Devices Offering High Channel Mobility and High Reliability

蔵口 雅彦 KURAGUCHI Masahiko 梶原 瑛祐 KAJIWARA Yosuke 向井 章 MUKAI Akira

GaN (窒化ガリウム)を用いたパワー素子は、パワーエレクトロニクス機器の小型化や低損失化を可能にするものとして期待されている。特に、MOS (金属酸化膜半導体)型 GaN素子は、単体でノーマリーオフ動作と高速スイッチングが可能であることから有望視されている。

東芝グループは、ゲート部を掘り込んだリセスゲート構造のMOS型GaN素子に対し、チャネル移動度に影響するAIN (窒化アルミニウム)層の結晶性を選択的に制御するプロセス技術を開発した。この独自プロセス技術を採用した素子を評価し、ゲート部における高いチャネル移動度と、高温・高ドレイン電圧下での高い信頼性の両立を確認した。

Gallium nitride (GaN) power semiconductor devices are expected to contribute to the realization of small, low-loss power electronics equipment. In particular, metal-oxide semiconductor (MOS) type GaN devices are promising candidates for next-generation power devices that can achieve normally-off operation by themselves in addition to high-speed switching.

The Toshiba Group has developed a process technology for MOS type GaN devices that makes it possible to selectively control the crystallization of an aluminum nitride (AIN) film on the recessed gate structure. Through evaluation tests of prototypes fabricated using this process technology, we have confirmed that it has the potential to achieve high channel mobility at the gate as well as high reliability under high-temperature, high-drain-voltage conditions.

## まえがき

GaNを用いたパワー素子は、その高い絶縁破壊電界強度と、高い電子移動度を持つ2次元電子ガス(注1)が誘起されることから、低オン抵抗かつ低スイッチング損失が実現できる。そのため、GaNパワー素子を用いた電源は、高いスイッチング周波数で動作可能となり、低損失化による省エネ化や小型化が期待される。

一方で、GaN素子は、通常ノーマリーオン動作であるが、電源応用にはノーマリーオフ動作が要求される。そこで、低耐圧のSi(シリコン)パワー素子と組み合わせた疑似ノーマリーオフ型素子や、ゲートにp型GaN層を形成することでノーマリーオフ動作を実現する素子が開発されている<sup>(1)</sup>。東芝グループは、疑似ノーマリーオフ型素子の開発<sup>(2)</sup>とともに、次世代デバイスとして、単体でノーマリーオフ動作を有し、少ない電荷によるゲート駆動で高速動作が可能なMOS型GaN素子の開発を進めている<sup>(3)</sup>。

MOS型GaN素子でノーマリーオフ動作を実現するには、ゲート部を掘り込んだリセスゲート構造にして、ゲート直下に誘起される2次元電子ガスを抑制する必要がある。しか

(注1) 半導体中で、動きが妨げられることなくシート(2次元)状にたくさんの 電子が分布する状態。 し、絶縁層/GaN界面のチャネル移動度が、フォノン散乱により  $100 \text{ cm}^2/(\text{V} \cdot \text{s})$  程度に抑制されるため、低オン抵抗とノーマリーオフ動作の両立が困難であった。

そこで今回、ALD (原子層堆積) 法により、AIN層形成において、ゲート部だけ高品質な単結晶を形成し、それ以外のエリアはアモルファス層を形成する独自のプロセス技術を新たに開発した。この技術の適用で、ノーマリーオフ動作を維持しつつ、チャネル移動度を $105 \, \mathrm{cm}^2/(\mathrm{V}\cdot\mathrm{s})$ から490  $\mathrm{cm}^2/(\mathrm{V}\cdot\mathrm{s})$ まで向上させた。更に、ゲート部以外をアモルファス層で形成することにより、高温高電圧下において高い信頼性を確保した。

ここでは、開発したMOS型GaN素子の、独自プロセス技術と特性について述べる。

#### 2. 開発したMOS型GaN素子の構造

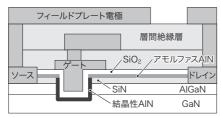

図1に、開発した素子構造を示す。ノーマリーオフ動作を実現するために、ゲート部を掘り込んだリセスゲート構造とし、掘り込み部に $SiO_2$ (二酸化ケイ素)から成るゲート絶縁層を形成している。また、素子耐圧の確保などを目的として、フィールドプレート電極を形成している。図2に、この素子のゲート部の形成フローを示す。まず、SiN(窒化ケイ素)層から成る表面保護層を形成した後、ドライエッチング

AIGaN:窒化アルミニウムガリウム

#### 図1. MOS型GaN素子の断面構造

ゲート部を掘り込んだリセスゲート構造で、2次元電子ガスの誘起を抑制し、 ノーマリーオフ動作を実現している。

Cross-sectional structure of MOS type GaN device

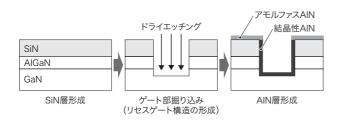

#### 図2. リセスゲート構造の形成フロー

リセスゲート部に結晶性のAIN層とアモルファスAIN層を選択的に形成することで、高いチャネル移動度と高い信頼性を実現した。

Flow of processes for fabrication of recessed gate structure

でゲート部をGaN層に至るまで掘り込んでリセスゲート構造にする。そして、このリセスゲート部を含む領域に、ALD法を用いてAIN層を形成する。このとき、ゲート部は、GaN層の結晶性を継承するためAIN層を単結晶とし、リセスゲート部以外のSiN層上のAIN層は、アモルファス層として堆積する。このように、選択的に結晶性を制御するプロセス技術を開発し、適用した。

AIN層の形成後は、連続してALD法で $SiO_2$ ゲート絶縁膜を形成する。その後、ゲート電極や、ソース電極、ドレイン電極などを形成し、層間絶縁層とフィールドプレート電極を形成することで、図1に示す素子を作製した。

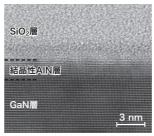

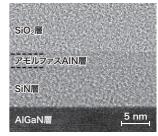

図3に、実際に作製した素子のリセスゲート領域とゲート電極-ドレイン電極間領域の断面TEM (透過型電子顕微鏡)像を示す。各々の層の組成は、元素分析により特定した。それぞれ、GaN層とSiO $_2$ 層との間、SiN層とSiO $_2$ 層との間に形成されたAIN層部分を拡大して示している。図3(a)に示すように、リセスゲート領域では、GaN層を継承してAIN層まで規則正しく原子が配列する結晶性を確認した。それに対し、図3(b)に示すように、ゲート電極-ドレイン電極間領域において、アモルファス層であるSiN層上のAIN層は、原子配列に規則性を持たないアモルファスであることを確認した。

(a) リセスゲート領域

(b) ゲート電極-ドレイン電極間領域

#### 図3. AIN膜の断面TEM像

リセスゲート部のAIN層は、結晶性を持つのに対し、SIN層上のAIN層は アモルファスを形成していることが分かる。

Cross-sectional transmission electron microscope (TEM) images of AIN film-fabricated areas

## 3. AIN層による高いチャネル移動度の実現

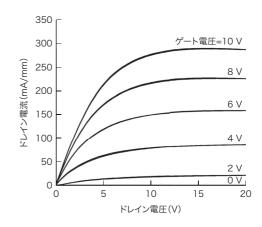

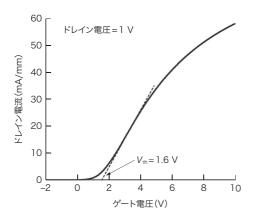

開発したMOS型 GaN素子の特性例として、**図4**に出力特性を、**図5**にドレイン電圧 1 Vのときの伝達特性を示す。図4に示すように、ゲート電圧 0 Vでドレイン電流が流れないノーマリーオフ動作を実現している。また、図5に示すように、ドレイン電流の外挿値から導出したしきい値電圧  $V_{th}$ は、1.6 Vであった。

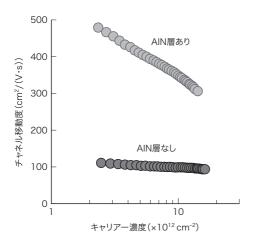

ゲート電圧を変化させて、ゲート下のキャリアー濃度を変えたときのチャネル移動度の評価結果を、図6に示す。ここでは、比較のために、AIN層のない素子の評価結果も同時に示した。AIN層を形成することで、AIN層のない素子で最大  $105~{\rm cm^2/}\,({\rm V\cdot s})$  だったチャネル移動度が、 $490~{\rm cm^2/}\,({\rm V\cdot s})$  まで増加した。これらのことは、高品質なAIN層を形成したことにより、AIN/GaN界面で高いチャネル移動度が実現されていることを示している。ここで、チャネル移動

図4. MOS型GaN素子の出力特性

ゲート電圧0Vでは電流が遮断されており、ノーマリーオフ動作を実現している

Output characteristics of MOS type GaN device

図5. MOS型GaN素子の伝達特性

ドレイン電流の外挿値から算出した $V_{

m th}$ は、 $1.6~{

m V}$ であった。 Transfer characteristics of MOS type GaN device

図6. チャネル移動度のキャリアー濃度依存性

AIN層を形成することにより、AIN層のない素子に比べ、大幅なチャネル移動度の向上を実現した。

Dependence of channel mobility on carrier density

度が向上した主な要因は、フォノン散乱の抑制と推定している<sup>(4)</sup>。この技術により、特性オン抵抗のうちゲート部が占める抵抗分を低減でき、耐圧650 V向けの素子においては、特性オン抵抗を約20%低減できた。

## 4. 高い信頼性の実現

3章で述べたように、開発したMOS型GaN素子は、ノーマリーオフ動作と高いチャネル移動度を実現したが、高い信頼性も同時に両立している。

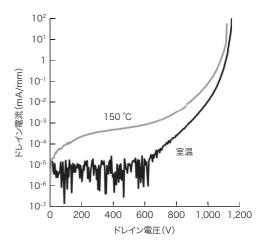

図7は、室温と150 °CでのMOS型GaN素子の耐圧特性である。両温度ともに、約1,200 Vの耐圧を示しており、650 V系パワー素子としては、十分な耐圧を保持している。

また、図8は、高温・高電圧下における加速試験による

## 図7. MOS型GaN素子の耐圧特性

室温と150 ℃のどちらも、約1,200 Vの耐圧を実現しており、650 V系パワー素子を想定すると、十分な耐圧を保持している。

Breakdown characteristics of MOS type GaN device

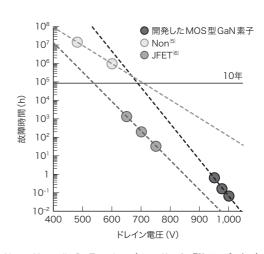

Non : Normally-On Transistor (ノーマリーオン型トランジスター) JFET : Junction Field Effect Transistor (接合型電界効果トランジスター)

#### 図8. 高温・高電圧下での信頼性試験の結果

高温・高電圧下での加速試験において、実用に向けて十分な寿命を確保できるポテンシャルを備えていることを確認した。

Results of reliability tests when high voltage applied at high temperature

素子の信頼性試験の結果を示している。ここでは、温度 150 °Cにおいて、一定電圧を印加したときの故障時間を、印加電圧に対してプロットしている。故障時間は、0.1 %の素子が故障することを推定した時間である。この試験結果から、温度 150 °C、ドレイン電圧 650 Vにおいて、推定される寿命は 10 年を超えている。これは、既に実用化が始まっている疑似ノーマリーオフ型素子(5)やゲートに p 型 GaN 層を形成することでノーマリーオフ動作を実現する素子(6)などと比較しても遜色のない値であり、MOS 型 GaN 素子が十分な

素子信頼性を確保できるポテンシャルを備えていることを示 している。

図3で示したように、開発したMOS型GaN素子は、リセスゲート部に結晶性のAIN層を形成することでチャネル移動度の向上を実現している。これに対し、ゲート電極ードレイン電極間のAIN層はアモルファス層である。高電圧下で高い電界強度にさらされるゲート電極ードレイン電極間においては、均一なアモルファス層を形成することで、高温・高電圧下での高信頼性の確保に寄与していると考えられる。このように、AIN層の結晶性を選択的に制御するプロセス技術の開発により、低オン抵抗と高い信頼性を備えるMOS型GaN素子が実現できる。

## 5. あとがき

リセスゲート構造において、AIN層を形成した素子を開発 し、MOS型GaN素子が性能や信頼性の観点から有望な 素子構造であることを示した。

MOS型 GaN素子の実用化には、 $V_{\rm th}$ 変動の抑制など、一層の高信頼性化が必要である。今後も、プロセス技術の開発を進め、単体でノーマリーオフ動作と高速動作が可能な MOS型 GaNパワー素子の実用化を通じて、小型化や省エネ化が要求されるパワーエレクトロニクス分野に貢献していく。

## 文 献

- Nakazawa, N. et al. Improved hysteresis in a normally-off AlGaN/ GaN MOS heterojunction field-effect transistor with a recessed gate structure formed by selective regrowth. Jpn. J. Appl. Phys. 2017, 56, 9, p.091003.1-091003.4.

- (2) Sugiyama, T. et al. "Stable cascode GaN HEMT operation by direct gate drive". Proc. 2020 32nd Int. Symposium on Power Semiconductor Devices and ICs (ISPSD). Vienna, Austria, 2020-09. IEEE. 2020, p.22–25.

- (3) Kajiwara, Y. et al. "Highly Reliable GaN-MOSFETs with High Channel Mobility Gate by Selective-Area Crystallization". Proc. 2020 32nd Int. Symposium on Power Semiconductor Devices and ICs (ISPSD). Vienna, Austria, 2020-09, IEEE. 2020, p.302– 305

- (4) Mukai, A. et al. "Gate-Channel Mobility Enhancement by Using AlN Interlayer in Recessed-Gate GaN-MOSFETs". 13th Int. Conf. Nitride Semiconductors 2019 (ICNS-13). Bellevue, WA, 2019-07, Materials Research Society. 2019, B08.02.

- (5) Chowdhury, S. et al. "650 V Highly Reliable GaN HEMTs on Si Substrates over Multiple Generations: Matching Silicon CMOS Manufacturing Metrics and Process Control". 2016 IEEE Compound Semiconductor Integrated Circuit Symposium Tech. Dig. 2016. Austin, TX, 2016-10, IEEE. 2016, p.221–224.

- (6) Tanaka, K. et al. "Reliability of Hybrid-Drain-Embedded Gate Injection Transistor". 2017 IEEE Int. Reliability Physics Symposium (IRPS 2017). Monterey, CA, 2017-04, IEEE. 2017, p.328–337.

蔵口 雅彦 KURAGUCHI Masahiko, Ph.D. 研究開発センター 先端デバイス研究所電子デバイスラボラトリー博士(工学) 応用物理学会会員 Electron Devices Lab.

**梶原 瑛祐** KAJIWARA Yosuke, Ph.D. 研究開発センター 先端デバイス研究所 電子デバイスラボラトリー 博士 (理学) Electron Devices Lab.

**向井** 章 MUKAI Akira 研究開発センター 先端デバイス研究所 電子デバイスラボラトリー Electron Devices Lab.