## 車載用半導体製品の品質を作り込む 信頼性・解析技術

Reliability and Analysis Technologies to Improve Quality of Automotive Semiconductor Products

若井 伸之 WAKAI Nobuyuki 豊田 尚志 TOYODA Hisashi 遠藤 幸一 ENDO Koichi

自動車の電動・電子化の進展とともに車載機器の高機能化が進んでおり、車載用半導体製品にはゼロディフェクト(不良ゼロ)を目指した高い品質レベルが求められている。その実現には、製造工程での量産管理だけでなく、開発・設計段階から品質・信頼性の作り込みが不可欠となっている。

東芝デバイス&ストレージ(株)は、開発時において、信頼性を高めたデバイス構造の採用や、TEG (Test Elements Group) 検証による高度な信頼性見積もり、不良を効果的にスクリーニングするための技術の導入などの取り組みを行っている。また、設計源流での品質改善のために、ロックイン発熱解析(LIT)や時間分解エミッション(TRE)顕微鏡を用いた動作解析技術の開発や、X線照射による影響を考慮した、不良箇所の特定技術の向上を図っている。

The sophistication of in-vehicle electronic equipment resulting from the advancement of technologies for automotive electronics and electroactuation in recent years has given rise to the need for automotive semiconductor products with high quality targeted at achieving zero defects. It is therefore necessary to implement quality and reliability improvement activities at the initial stage of development as well as at the mass production stage.

Toshiba Electronic Devices & Storage Corporation has been engaged in the development of automotive semiconductor products applying the following technologies to attain high quality at the design stage: device structure optimization to improve the reliability of each product, advanced technology to estimate reliability using a test element group (TEG) pattern, and a screening method to detect potential defects. In order to improve upstream design quality, we have also been focusing on development using operating analysis technologies, including lock-in thermography (LIT) and time-resolved emission (TRE) microscopy, as well as improvement of the defect position specification method taking into consideration the effect of X-ray irradiation.

### 1. まえがき

自動車に搭載される電子機器の高機能化とともに、車載用半導体製品にはゼロディフェクト(不良ゼロ)の高い品質レベルが求められている。しかし、それを実現するには、製造工程での量産管理の強化だけではなく、半導体製品の開発・設計段階からの不具合検出や解析力を向上させた品質・信頼性の作り込みが不可欠である。また、分業化(アウトソーシング)が進むSi(シリコン)ウエハーの製造、組み立て、及びテストの各工程においても、車載用半導体製品を製造するために強化された管理内容を展開することが必要になる。更に、開発から量産管理までの流れを、顧客とともに連携していくことで、車載システムの高機能化を支えるとともにエンドユーザーに安全・安心な車載用半導体製品を提供できると考えられる。

東芝デバイス&ストレージ(株)は、半導体製品開発に

クオリティーゲートシステムによる社内開発品認定システム(IQS : Internal Quality System)<sup>(1)</sup>を適用しており、開発の各段階におけるデザインレビューを充実し、更にミスによる開発の後戻りを削減することで、高い品質・信頼性レベルを確保する体制を構築している。

ここでは、品質・信頼性レベルを更に向上させるために取り組んでいる、信頼性・解析技術について述べる。

### 2. 信頼性技術の向上への取り組み

車載用半導体製品の信頼性認定には、米国の車載用電子部品信頼性認定標準化団体であるAEC (Automotive Electronics Council) が発行するAEC-Q100(集積回路用)<sup>(2)</sup>、AEC-Q101(個別半導体用)<sup>(3)</sup>が広く参照されており、一般に、その内容に従った認定試験の結果に基づいて対象製品の信頼性が判断されている。しかし、この信頼性認定試験で十分な結果を得るために、要素技術の開発・

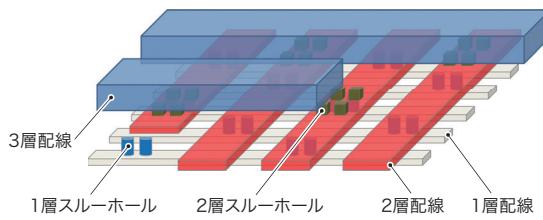

図1. LDMOS搭載パワーICの配線層レイアウト

1層目と2層目の配線の重なりを少なくし電流集中を回避するデザインにより、3層以上の上層において、電流密度の部分的な上昇を抑制できる。

Schematic diagram showing layout of metal layers in power integrated circuit (IC) using laterally diffused metal-oxide semiconductor (LDMOS)

設計段階から対象製品に求められる信頼性条件を明確化して試験実施計画を立案し、各故障モードの耐用年数などの要求仕様を十分にカバーできるようにその製品を作り込むことが不可欠である。

## 2.1 パワーIC系デバイス開発時の信頼性向上の取り組み

大電流を流すパワーICに搭載されるLDMOS FET（横方向二重拡散金属酸化膜半導体型電界トランジスター：以下LDMOSと略記）では、高温動作中の電子衝突によってCu（銅）などの配線用金属原子の拡散が配線抵抗の上昇を引き起こすエレクトロマイグレーション（EM：Electromigration）が、信頼性を低下させる懸念項目の一つとなっている。しかし、図1に示す積層配線において、特に1層配線と2層配線の下層域での重なりを抑制するデザインを採用し電流集中を回避することで、電流密度が上昇しやすいスルーホール配線（ビア）を削減し、全体の許容電流密度を引き上げることができる<sup>④</sup>。

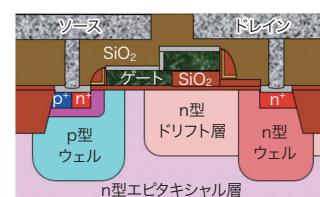

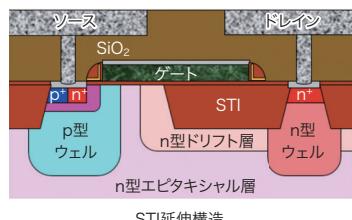

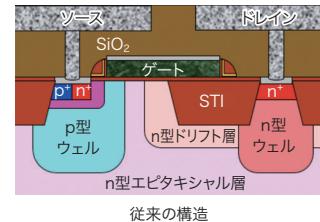

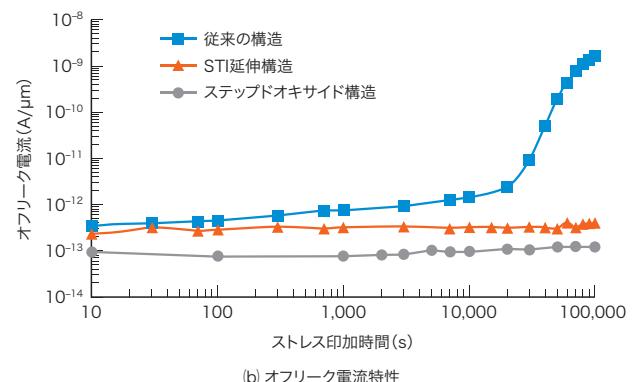

また当社は、消費電力の増加や回路動作の不具合を引き起こすLDMOSのホットキャリア注入<sup>(注1)</sup>に起因したオフリーク電流の増加メカニズムを解明するとともに、0.13 μm世代のnチャネルLDMOSでは、n型ドリフト層上の素子分離（STI：Shallow Trench Isolation）領域を伸ばしたSTI延伸構造、あるいはn型ドリフト層上のSTI領域をステップドオキサイド構造（階段状に酸化膜を形成した構造）に変更することで、従来の構造に比べてオフリーク電流の増加を抑制できることを確認した（図2）<sup>(5)</sup>。開発したSTI延伸構造やステップドオキサイド構造を採用することにより、LDMOSの信頼性向上、すなわち長寿命化を実現できる。

## 2.2 ミッションプロファイルと信頼性見積もり

近年、車載環境条件を細分化したミッションプロファイルが適用

(注1) ドrain-ソース間の電界で加速されたホットキャリアが、酸化膜などに注入され、トランジスター特性が劣化する現象。

(a) LDMOS構造

(b) オフリーク電流特性

SiO<sub>2</sub>:二酸化ケイ素

図2. LDMOS構造によるオフリーク電流特性の改善

開発したSTI延伸構造やステップドオキサイド構造を備えたLDMOSでは、従来の構造に比べてオフリーク電流の増加を抑制できることを確認した。

Improvement in off-leak current of LDMOS devices with different structures

されており、半導体製品の信頼性試験の実施計画においても対応が必要となってきている。信頼性見積もりは、加速モデルを適用した試験条件の結果から換算することができるが、一般に、Siウエハー製造委託先（ファンドリー）で広く採用されている信頼性判断条件は125 °Cとなっており、ミッションプロファイルで網羅されている、150 °Cまでの温度条件範囲との間に差異がある。温度と時間の関係から信

頼性見積もりは可能であるが、より正確に信頼性を見極めるためには、実ストレスの試験結果に基づいた加速性適合の確認が不可欠になる。このため、Siウェハーファンドリーに追加データの取得を依頼するか、対象の半導体製品に搭載される構造を備えたテストパターンであるTEGで実際に測定評価を行うことが必要になる。この状況を踏まえて、当社は、TEGを評価できる環境を構築するとともに、複雑化する信頼性見積もり条件にも対応できる体制を確立している。

### 2.3 テストスクリーニングの強化事例

Siウェハーや完成品で行うテストでは、良品と判定されたものが市場で初期不良を起こす場合があり、それらを除去するスクリーニング作業が重要となる。代表的なスクリーニング方法として、バーンイン(Burn-in)がある。半導体製品の実際の動作条件を強化したバーンインストレスを加えることにより、短時間で発生する初期不良を検出して除去する方法である。

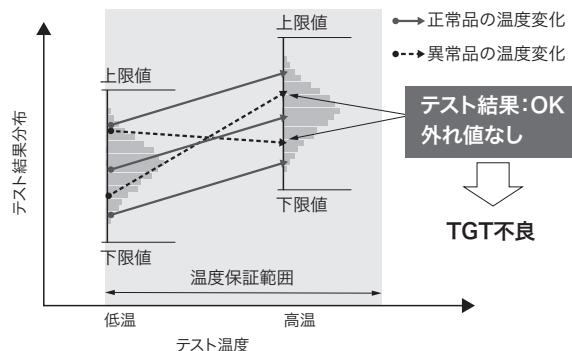

一方で、ストレスに対して単純な特性変化を示さない不具合品が存在する場合もある。低温と高温のテストを行って、それぞれの条件でスペックに収まっている場合には、不良品と判別することはできない。しかし、各温度での測定結果を一つ一つの製品ごとの変化量として捉え、判断項目に追加したテスト(TGT: Temperature Gradient Test)を行うことで、ほかのサンプルとは異なる挙動を示す潜在的な不具合品を検出することができる。この温度傾斜を利用したスクリーニング手法の概要を、図3に示す。リソグラフィーやエッ칭工程などで適正な加工ができなかった場合に生じる局所的な欠陥に起因した不具合品を、このTGTで検出可能である<sup>(6)</sup>。

図3. TGTによるスクリーニング例

低温と高温の両測定条件に対して、一定の傾きを持った特性変化を示さないサンプルを検出することで、不具合品を見付けることができる。

Example of screening by means of temperature gradient test (TGT)

### 3. 解析技術の向上への取り組み

半導体製品の開発段階、又は出荷後に故障が発生した場合には、通常、故障解析とその結果に基づいた対策を行う。故障解析は、電気的特性データと過去の事例から故障モードを特定し、製品を分解して内部を詳細に調べ、その結果から故障メカニズムの推定と検証を行う。そして、最終的に設計自体の変更も含めた根本的な対策を行う。

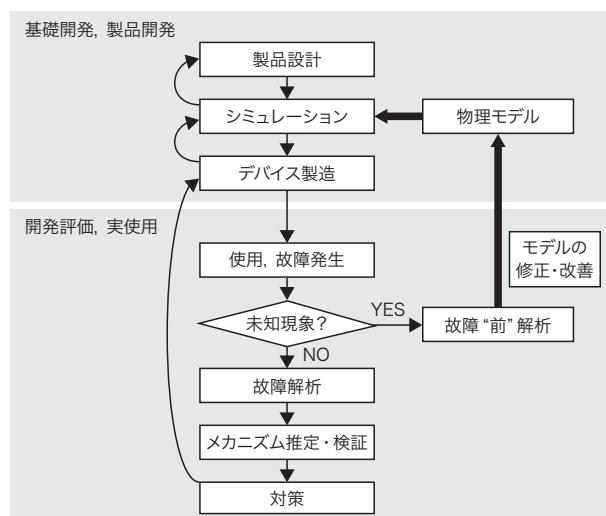

しかし、車載用途では新しい使用方法や環境が日々変化しているため、過去の事例や合理的な見解を見いだしづらい場合がある。過去の事例からの推定が難しい場合には、シミュレーションを活用することが一つの解決手段となる<sup>(7)</sup>。デバイス開発の際のシミュレーションを用いて、デバイス構造上の不具合や使用条件に伴う異常な動作の解明に役立てることも可能である。しかし、シミュレーションは、故障現象を説明できる物理モデルの裏付けがないと十分な検証ができないため、実デバイスの動作を把握することが重要となる。また、車載用途で使用されるパワーデバイスは、多数の単位構造素子が並列接続されており、電気的特性だけでは素子間のアンバランスの検出が難しいことから、動作状態での解析が有効となる。異常動作を十分に解析することで物理モデルの再構築が可能となり、最終的には図4に示すフローで設計源流での設計品質を向上させている。このよう

図4. 故障“前”解析を利用した設計源流の品質改善フロー

故障“前”解析の手法を用いて物理モデルを再構築することにより、設計源流での品質向上を図っている。

Flow of product development quality improvement using pre-fault analysis

に、解析技術の向上への取り組みは、最終的なデバイスの信頼性向上につながると考えられる。

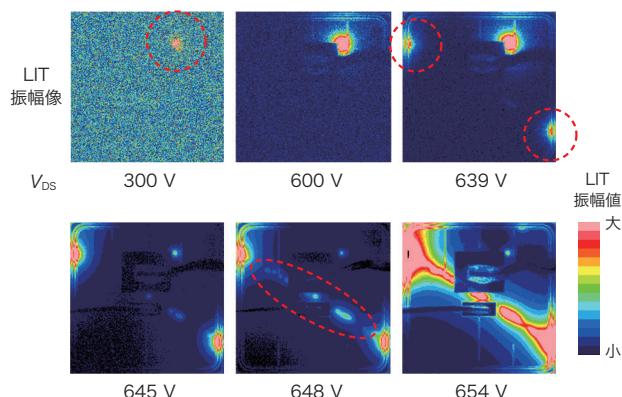

### 3.1 発熱と発光解析の事例

図5は、リーク不良特性を示す設計耐圧600 V以上のnチャネルパワーMOSFET（金属酸化膜半導体型電界効果トランジスター）に対し、LITを用いて発熱分布を観測した例である<sup>(8)</sup>。各画像は同一チップの表面領域を表し、主な発熱部がカラーチャートで示されている。ドレイン-ソース間電圧  $V_{DS}$  が300 V前後からチップ上部の赤色破線内に点状の発熱部が現れ、639 Vを超えるとチップを斜めに横切る直線状の、2種類の発熱パターンが観測された。リーク原因は、単純に一つではなく、2種類の要因があったことが推察された。

図6はIGBT（絶縁ゲートバイポーラートランジスター）の

図5. MOSFET耐圧リーク不良品のLIT観測

$V_{DS}$ の上昇に伴って、2種類の発熱パターンが観測され、リークには2種類の要因が影響していることが示唆された。

Results of LIT observations of leakage defects of metal-oxide-semiconductor field-effect transistor (MOSFET)

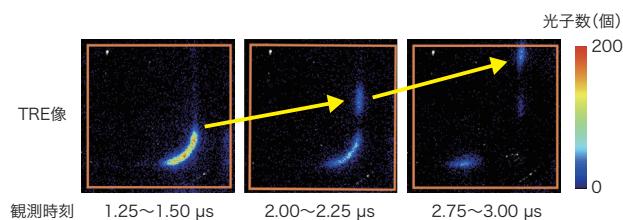

図6. IGBTアバランシェ降伏時の電流による発光のTRE観測

IGBTのアバランシェ降伏電流に伴う発光をTRE顕微鏡で観察したところ、電流集中の発生後に、その電流集中箇所が移動していくことが分かった。

Results of TRE microscopy observations of light emissions caused by avalanche breakdown current in insulated gate bipolar transistor (IGBT)

アバランシェ降伏電流に伴う発光を、TRE顕微鏡で観測した例である<sup>(9)</sup>。チップのコーナー部分を、0.75 μsごとに0.25 μsの時間幅を積算して観測した結果を示しており、発光箇所が移動していく様子が観測された。多くのシミュレーション結果で報告されているとおり、電流集中が発生し、時間の経過とともにその電流集中箇所が移動していくことが、実デバイスによる観測でも確認できた。

このように、新しい用途・バイアス条件において適切にデバイスが動作するかどうかを検証できる解析技術と評価環境についても、検討を続けていている。

### 3.2 X線照射の影響

未開封の状態で半導体製品の内部異常を確認するには、X線CT（コンピューター断層撮影）が有効である。特に、マイクロフォーカスX線管を用いたX線CT装置では、最大で数千倍に拡大して透視することが可能であり、LITなどの併用による観察が原因究明に役立てられている。一方で、X線照射による半導体デバイスへの影響が懸念されている。X線源の試料への接近や、長時間のX線照射によって、解析対象デバイスの特性が変動するため、X線によるダメージを最小限にとどめることが必要になる。

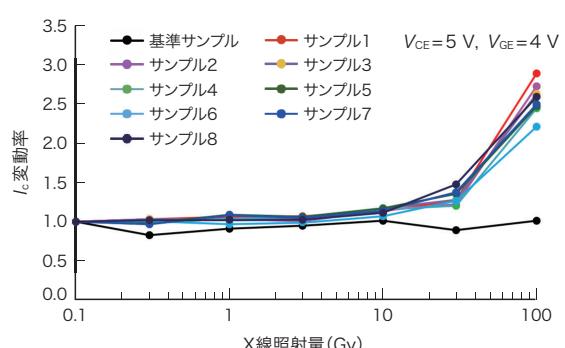

IGBTへのX線照射結果を図7に示す。30 Gyからコレクター電流  $I_c$  の増加が観察され、100 Gy照射では  $I_c$  が2倍以上に増えた。更に、100 GyではMOSFETのしきい値変動や、1,000 Gyではフラットバンド電圧変動なども発生する。このような長時間のX線照射が半導体デバイスの特性に影響するため、解析内容がX線照射の影響を抑えるべき案件

$V_{CE}$ :コレクター-エミッター間電圧

$V_{GE}$ :ゲート-エミッター間電圧

図7. X線照射によるIGBTの特性変動

IGBTにX線を照射したところ、30 Gyから  $I_c$  が増加し始め、100 Gyでは  $I_c$  の変化量は2倍を超えた。

Changes in collector current of IGBT when irradiated by X-rays

かどうかを見極め、故障原因を損なわない故障解析手順及び条件で解析を進めている。

#### 4. あとがき

今回述べた、車載用半導体デバイス開発時の信頼性の確認や、ミッションプロファイルに対応した信頼性見積もり、温度傾斜を利用したスクリーニング方法、LITやTREを活用した動作解析と設計改善につながる解析フローの見直し、解析時のX線の影響確認といった信頼性・解析技術などを適用することで、開発・設計段階からの品質の作り込みと信頼性技術、及び不良箇所を特定する解析技術の向上を実現させることができた。

自動車に搭載される電子機器の高機能化が継続され、車載用半導体製品に採用される新たなSiプロセスやパッケージ技術の開発も進められていく中で、この流れに合わせてゼロディフェクトを実現するためには、今後も更なる信頼性・解析技術の向上が不可欠と考えられる。

#### 文 献

- (1) 瀬戸屋 孝, ほか. 先端半導体LSIデバイスの信頼性保証技術. 東芝レビュー. 2005, 60, 5, p.10-13.

- (2) AEC-Q100:2014. Failure mechanism based stress test qualification for integrated circuits.

- (3) AEC-Q101:2013. Failure mechanism based stress test qualification for discrete semiconductors in automotive applications.

- (4) 東芝. 半導体装置. 特許第4372046号. 2009-11-25.

- (5) Takahashi, K. et al. "Hot-carrier induced off-state leakage current increase of LDMOS and approach to overcome the phenomenon". Proc. of 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD 2018). Chicago, IL, 2018-05, IEEE. 2018, p.303-306.

- (6) Wang, Q. et al. "Reliable screening for zero-defect quality improvement by temperature gradient testing". Proc. of 2013 e-Manufacturing & Design Collaboration Symposium (eMDC 2013). Hsinchu, Taiwan, 2013-09, IEEE. 2013, p.1-4.

- (7) 遠藤幸一. Siパワー半導体の現状と信頼性：故障前解析の紹介（パワー半導体の現状と信頼性）. 日本信頼性学会誌. 2015, 37, 1, p.34-41.

- (8) Endo, K. et al. Thermoreflectance mapping observation of Power MOSFET under UIS avalanche breakdown condition. Microelectronics Reliability. 2015, 55, 9-10, p.1628-1633.

- (9) Endo, K. et al. "Direct photo emission motion observation of current filaments in the IGBT under avalanche breakdown condition". Proc. of 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD 2016). Prague, Czech Republic, 2016-06, IEEE. 2016, p.367-370.

若井 伸之 WAKAI Nobuyuki

東芝デバイス&ストレージ(株)

ミックスドシグナル IC 事業部 品質信頼性技術部

ESD Association・IEEE 会員

Toshiba Electronic Devices & Storage Corp.

豊田 尚志 TOYODA Hisashi

東芝デバイス&ストレージ(株)

ディスクリート半導体事業部 ディスクリート半導体信頼性技術部

Toshiba Electronic Devices & Storage Corp.

遠藤 幸一 ENDO Koichi

東芝デバイス&ストレージ(株)

ディスクリート半導体事業部 ディスクリート半導体信頼性技術部

日本信頼性学会・応用物理学会・日本品質管理学会会員

Toshiba Electronic Devices & Storage Corp.