The National Action of Telephrane (1997) and the National Action of Telephrane (1997) and the National Actional Actional

# Quality Control of Trench Field Plate Power MOSFETs by Correlation of Trench Angle and Wafer Warpage

Hiroaki Kato Advanced Discrete Development Center Toshiba Electronic Devices & Storage Corporation Nomi, Ishikawa, Japan https://orcid.org/0000-0002-7921-1948

Katsura Miyashita Advanced Discrete Development Center Toshiba Electronic Devices & Storage Corporation Nomi, Ishikawa, Japan katsura.miyashita@toshiba.co.jp

Toshifumi Nishiguchi Advanced Discrete Development Center Toshiba Electronic Devices & Storage Corporation Nomi, Ishikawa, Japan toshifumi.nishiguchi@toshiba.co.jp

Kenya Kobayashi Advanced Discrete Development Center Toshiba Electronic Devices & Storage Corporation Nomi, Ishikawa, Japan kenya.kobayashi@toshiba.co.jp

Saya Shimomura Advanced Discrete Development Center Toshiba Electronic Devices & Storage Corporation Nomi, Ishikawa, Japan saya1.shimomura@toshiba.co.jp

Abstract-Field-Plate (FP) MOSFET structure has been studied to get higher performance characteristics. To get low drift layer resistance, reduction of the trench width is one typical method with FP-MOSFET because it enables us to design the fine cell pitch of the FP-MOSFET. Trench width is relevant to trench angle. However large trench angle for better characteristics causes the variation of the dielectric breakdown voltage on the oxide film that separating the gate and source. Therefore, process window becomes always narrow to get excellent characteristic. For quality control of trench angle, we find that wafer the warpage is relevant to the trench angle. We confirmed the dependence by simulation and experiment. Furthermore, we acquire four correlation data related to the wafer warpage after field plate oxidation. Subsequently, we derived the regression equation for quality control and confirmed the validity of the equation.

Keywords— process control, field-plate, Power MOSFET, trench, wafer warpage.

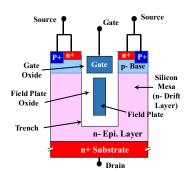

Fig. 1. Schematic cross-sectional structure of trench field plate MOSFET (unit cell) [8] [9].

# I. INTRODUCTION

Trench Power MOSFETs have been developed as semiconductor devices for high-speed switching for a long time. In recent years trench Power MOSFET having field plate (FP-MOSFET) has been studied to get higher performance characteristics [1]-[7]. Typical structure of FP-MOSFET is shown in Fig.1. The structure has field plate (FP) and thick

field plate oxide in each trench. Due to the field-plate effect, high breakdown voltage can be achieved with an ultra-low drift layer resistance.

#### II. IMPORTANCE OF TRENCH ANGLE

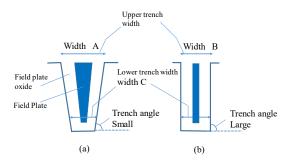

Reduction of the trench width is one typical method for improving performance with FP-MOSFET because it enables us to design the fine cell pitch of the FP-MOSFET. Trench width is relevant to trench angle. Comparison of trench structures is shown in Fig.2. Bottom trench widths (width C) are identical for both cases. However, width A is larger than width B. Therefor the pitch shrink is restricted by small trench angle.

Fig. 2. Comparison of trench structure. (a) Small trench angle (b) Large trench angle

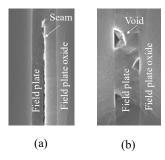

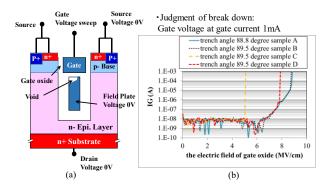

On the other hand, there is a limit to increase trench angles. If we design large trench angle, seams of the poly-silicon become larger. The seam becomes the void by phosphorus diffusion (Fig.3 (a) (b)). If voids are gathered at the top of the FP (Fig.4 (a)), the electric field in the oxide film, separating the gate and source, becomes strong. It causes the variation of the dielectric breakdown voltage at time zero dielectric breakdown (TZDB) (Fig.4 (a) (b)). To address this challenge, we added high temperature anneal not to generate the voids and confirmed the effect [10]. However, it does not work enough for extremely large trench angle.

Fig. 3. (a) Cross sectional SEM photograph of FP after polysilicon formation. (b) Cross sectional SEM photograph of FP after phosphorus diffusion. (c) Measurement condition on TZDB.

Fig. 4. (a) Measurement condition on Time Zero Dielectric Breakdown (TZDB) (b) The variation of the dielectric breakdown voltage at TZDB.

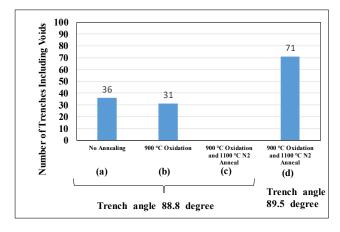

Fig. 5 shows the number of trenches including voids among 100 trenches. The voids completely disappeared after  $1100~^{\circ}\text{C}~\text{N}_2$  anneal at trench angle 88.8 degree, but not at 89.5 degree. Therefore, process window becomes always narrow to get excellent characteristic. Thus, quality control of trench angle is very significant.

Fig. 5. Number of trenches including voids of (a) no annealing with trench angle of 88.8 degree, (b) 900 °C oxidation only with trench angle of 88.8 degree (c) 900 °C oxidation and 1100 °C  $\rm N_2$  annealing with trench angle of 88.8 degree [10], and (d) 900 °C oxidation and 1100 °C  $\rm N_2$  annealing with trench angle of 89.5 degree

#### III. TRENCH LAYOUT AND THE WAFER WARPAGE

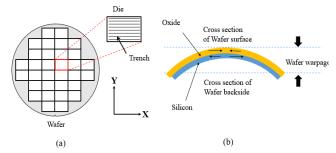

The definition of direction is shown in Fig.6 (a). The trench is extended to X-direction. Once we form the oxide on the wafer surface, wafer becomes convex because of the compressive stress in the oxide in Fig.6 (b). The stress is occurred by the difference of the coefficient of thermal expansion (CTE) [11]-[13].

Fig. 6. (a) Definition of X-direction and Y-direction, (b) Definition of wafer warpage

# IV. CORRELATION BETWEEN THE TRENCH ANGLE AND THE WAFER WARPAGE

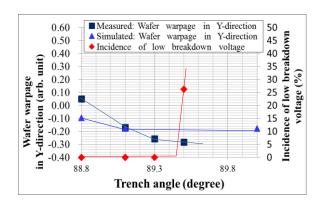

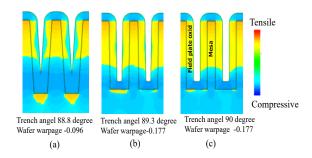

We confirmed dependence for trench angle of the incidence of low breakdown voltage at TZDB. 219 pieces were evaluated at each angle. Samples with breakdown electric field of less than 8.3 MV/cm were considered as "defective" in Fig. 7. Defects are rapidly increasing at 89.5 degree. This result is also consistent with the behavior of void occurrence rate inside the trench (Fig. 5). In addition, we evaluated wafer warpage because control of the wafer warpage is very important for FP-MOSFET[8] [9]. As a result, we find that wafer the warpage in Y-direction after field plate oxidation is relevant to the trench angle (Fig. 7). Typically, wafer warpage is affected by shear stresses. Therefore we go over Y-directional shear stress after field plate oxidation by utilizing the simulation model that was already developed [13]. Consequently, it turned out that the field plate oxide at trench bottom has strong compressive stress as the angle decreases.

Fig. 7. Wafer warpage after field plate oxidation and Incidence of low breakdown voltage.

The stress produces the tensile stress on the silicon at trench bottom (Fig. 8). Furthermore, the simulated wafer warpage indicates the similar tendency to an actual value (Fig.7).

Fig. 8. Simulated shear stress distribution in Y-direction after field plate oxidation.

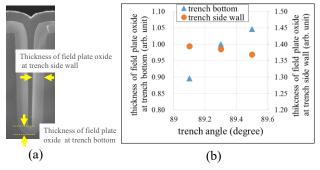

In addition to the simulation, we clarified strong compressive stress at trench bottom by checking the oxide thickness after FP formation. The thickness of field plate oxide at trench bottom is proportional to the trench angle. In contrast, the dependence of the thickness of field plate oxide at trench side is small (Fig.9). It indicates that the supply of oxidant at field plate oxidation was reduced at the bottom of the trench because the compressive stress of the oxide film at the bottom of the trench was strong by the narrow width.

Fig. 9. (a) Cross section after field plate formation in Y-direction. (b) Thickness of field plate oxide at trench bottom and trench side wall.

# V. QUALITY CONTROL

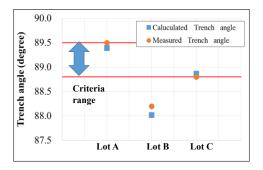

We acquire another four correlation data related to the wafer warpage after field plate oxidation. They are film thickness of the wafer backside, width of the trench, depth of the trench and the thickness of filed plate oxide. Then we derived the regression equation. The equation enables us to calculate the trench angle by using the previously described quality control data of four parameters and the wafer warpage after field plate oxidation. We confirmed the validity of the formula by using three lots with different trench angles. The result of the trench angle by utilizing the regression equation is shown in Fig. 10. Measured trench angles fit in well to calculated trench angles.

Regression equation: Wafer warpage (arb. unit) = 39.5 - 6.33E-3 (film thickness of the wafer backside) + 5.35E-3 (depth of the trench) - 9.41E-3 (width of the trench) - 4.64E-1 (trench angle) + 3.59E-4(the thickness of filed plate oxide)

Fig. 10. Measured trench angles fit in well to calculated trench angles by wafer warpage.

#### VI. CONCLUSION

We confirmed dependence for trench angle of the incidence of low breakdown voltage at TZDB. Defects are increasing rapidly under the condition of 89.5 degree. The TZDB result indicates the similar tendency to the number of trenches including voids. In addition, we found the correlation between trench angle and wafer warpage after field plate oxidation and confirmed the mechanism by two methods. One is Y-directional shear stress simulation that was already developed. The other is checking the oxide thickness after FP formation. Furthermore, we derived the regression equation for quality control by correlation of trench angle and wafer warpage and confirmed the validity of the equation.

## ACKNOWLEDGMENT

The authors would like to thank Kohei Oasa and Tatsuya Nishiwaki for useful discussions, Tetsuya Ohno and Ryo Terada for SEM observation, and Hiroyuki Kamijo for their encouragement.

## REFERENCES

- Y. Baba, N. Matsuda, S. Yanagiya, S. Hiraki and S. Yasuda, "A Study on a High Blocking Voltage UMOS-FET with a Double Gate Structure," Proc. of ISPSD, 1992, pp. 300-302.

- [2] W. Saito, "Comparison of Theoretical Limits between Superjunction and Field Plate Structures," Proc. of ISPSD, 2013, pp. 241-244.

- [3] G. E. J. Koops, E. A. Hijzen, R. J. E Hueting and M. A. A. in't Zandt, "Resurf stepped oxide (RSO) MOSFET for 85V having a record-low specific on-resistance," Proc. of ISPSD, 2004, pp.185-188.

- [4] M. A. Gajda, S. W. Hodgskiss, L. A. Mounfield and N. T. Irwin, "Industrialization of resurf stepped oxide technology for power transistors," Proc. of ISPSD, 2006, pp.109-112.

- [5] P. Goarin, G. E. J. Koops, R. van Dalen, C. L. Cam and J. Saby, "Split-gate resurf stepped oxide (RSO) MOSFETs for 25 V applications with record low gate-to-drain charge," Proc. of ISPSD, 2007, pp. 61-64.

- [6] K. Kobayashi, T. Nishiguchi, S. Katoh, T. Kawano and Y. Kawaguchi, "100 V Class Multiple Stepped Oxide Field Plate Trench MOSFET (MSO-FP-MOSFET) Aimed to Ultimate Structure Realization," Proc. of ISPSD, 2015, pp. 382-385.

- [7] K. Kobayashi, H. Kato, T. Nishiguchi, S. Shimomura, T. Ohno, T. Nishiwaki, K. Aida, K. Ichinoseki, K. Oasa and Y. Kawaguchi, "100-

- V Class Two-step-oxide Field-Plate Trench MOSFET to Achieve Optimum RESURF Effect and Ultralow On-resistance," Proc. of ISPSD'19, pp. 99-102, 2019.

- [8] H. Kato, T. Nishiguchi, S. Shimomura, K. Miyashita and K. Kobayashi, "Process Control Technique to Reduce Wafer Warpage for Trench Field Plate Power," Proc. of ISSM'18, PC-O-026, 2018.

- [9] H. Kato, T. Nishiguchi, S. Shimomura, K. Miyashita and K. Kobayashi, "Mechanism and Control Technique of Wafer Warpage in Process Integration for Trench Field Plate Power MOSFET," IEEE Transactions on Semiconductor Manufacturing, vol. 32, issue 4, pp. 417-422, Nov. 2019.

- [10] S. Shimomura, H. Kato, T. Shiraishi, T. Ohno, T. Nishiguchi, K. Miyashita and K. Kobayashi, "Process Control Technique to Dramatically Reduce Voids in Phosphorus-Doped Poly-Silicon for Trench Field-Plate MOSFETs," Proc. of eMDC'19, N5,2019.

- [11] H. Yamadera, "Measurement and Control of Thermal Stress in Thin Films," TOYOTA Central Lab. R&D Review 34, no.1, 1999, pp. 19-24. (In Japanese)

- [12] G.G. Stoney, "The tensions of metallic films deposited by electrolysis," Proc. R. Soc. Land. A82 (1909) 172-175.

- [13] T. Nishiguchi and K. Kobayashi, "Modeling for Silicon Wafer Warpage of Trench MOSFET using Process Stress Simulation," Joint Technical Meeting of IEE Japan, EDD-15-068 / SPC-15-150, 2015, pp. 23-28. (In Japanese)

- [14] K. Yamabe and K. Imai, "Nonplanar Oxidation and Reduction of Oxide Leakage Currents at Silicon Corners by Rounding-off Oxidation," IEEE Transactions on Electron Devices, vol. 34, No. 8, pp. 1681-1687, Aug. 1987.

#### **AUTHOR BIOGRAPHY**

Hiroaki Kato received bachelor degree in electrical engineering from Okayama University, Okayama, Japan, in 1997. He joined NEC Corporation and was engaged in the power ICs device development. In 2014, he moved to Toshiba Corporation and he has been an engineer of the development of power MOSFETs process integlation technology.