S. Asaba et al., "Impact of Reverse Current Spreading on Diode Conduction Reliability of SBD-Embedded SiC-MOSFET with Deep p-Shield Structure", 2024 36th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Bremen, Germany, 2024, pp. 5-8. Doi: 10.1109/ISPSD59661.2024.10579582 © 2024 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. And published article is uploaded in IEEE Xplore (https://ieeexplore.icee.org/document/10579582)

# Impact of reverse current spreading on diode conduction reliability of SBD-embedded SiC MOSFET with deep p-shield structure

Shunsuke Asaba<sup>1,2</sup>, Masaru Furukawa<sup>1</sup>, Yuji Kusumoto<sup>1</sup>, Ryosuke Iijima<sup>2</sup> and Hiroshi Kono<sup>1</sup>

<sup>1</sup>Toshiba Electronic Devices & Storage Corporation, Hyogo, Japan

<sup>2</sup>Corporate R&D Center, Toshiba Corporation, Kanagawa, Japan

shunsuke.asaba@toshiba.co.jp

Abstract—The device structure of SBD-embedded MOSFET was investigated and the complicated trade-off relationship of onstate resistance, short-circuit ruggedness, and diode conduction capability was improved. TCAD analysis indicated that bipolar conduction in body diode of MOSFET with deep p-shield can be suppressed by developing current spreading layer structure. The fabricated devices demonstrated adequate ruggedness in shortcircuit operation and unipolar conduction capability in diode operation while obtaining low on-state resistance. The reduction in leakage by the developed structure enabled drift layer tuning and finally low on-resistance of 2.0 m $\Omega$ ·cm<sup>2</sup> was demonstrated.

#### Keywords— SiC, MOSFET, Embedded SBD, Short circuit

#### I. INTRODUCTION

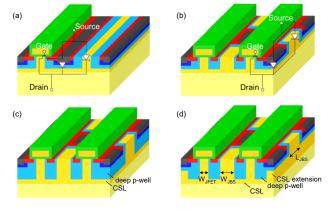

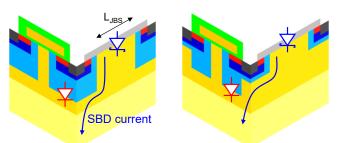

Bipolar conduction in diode operation of SiC MOSFET causes a reliability problem due to expanding crystal defects of SiC substrates. Embedding Schottky barrier diode (SBD) into the cell structure of SiC MOSFET is a credible design to avoid such bipolar degradation and has been commercially available [1-8]. Fig.1.(a) illustrates the device structure and equivalent circuit diagram of the cell design with striped pattern embedded-SBD. When reverse current smaller than the critical current density called Jumax (maximum current density of unipolar conduction) flows, current is dominated by unipolar conduction through embedded SBD. We reported a drastic decrease in specific on-resistance (RonA) while improving Jumax by employing the cell structure with two-dimensional SBD layout shown in Fig. 2(b) [3]. A design strategy for realizing both low RonA and high Jumax was shown; however, securing short-circuit (SC) ruggedness is another important demand considering application of low RonA SiC MOSFET. In particular, the destruction mechanism attributed to embedded SBD [4] has to be considered carefully. There is a complicated trilemma in determining device design to satisfy the requirements of low RonA, high Jumax, and good SC ruggedness. Improvement in SC ruggedness by introducing deep p-well structure that suppresses SC current and Schottky leakage has recently been reported (Fig. 1(c)) [5-6]. Considering commercial application, demonstrating the advantage of introducing deep p-well structure while realizing high Jumax and low R<sub>on</sub>A is essential. In this paper, we propose the developed cell structure with extended CSL (Current Spreading Layer) as shown in Fig. 1(d). The mechanism to improve  $J_{umax}$  and SC ruggedness while obtaining low  $R_{on}A$  was investigated and performance improvement was evaluated.

#### II. DEVEPOPMENT OF THE CELL STRUCTURE

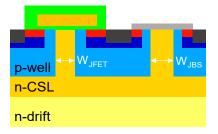

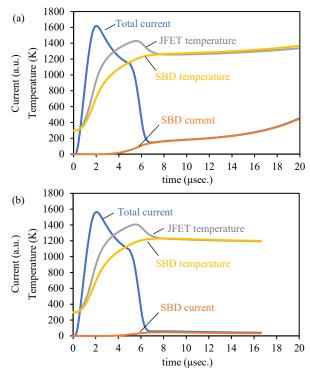

### A. Importance of narrow W<sub>JBS</sub> for SC-ruggedness

Firstly, TCAD simulation was conducted in order to clarify the SC failure mechanism and determine appropriate geometry of embedded SBD. The simplified two-dimensional structures containing the MOSFET region and embedded SBD with different W<sub>JBS</sub> (width of Junction Barrier for Schottky junction) as shown in Fig. 2 were computed. Long gate turn-on of 5.0 microseconds was applied and the simulations were continued regardless of the device temperature so that behavior of SBD leakage could be clarified. Figure 3 shows the simulated waveforms of current and temperature when wide or narrow W<sub>JBS</sub> was used. Immediately after gate is turned on, drain current through channel rapidly increases. Generated Joule heat elevates the temperature of the JFET region and that causes SC current saturation in approximately 2 microseconds. After gate turn-off, drain current rapidly decreases. Despite the negligible difference in current attributed to channel, a different behavior was observed in the SBD current. Initially after gate turn-on, SBD current did not appear for both W<sub>JBS</sub> geometry. This is

Fig. 1 Device structure of the SBD-embedded SiC MOSFETs.

(a) Conventional stripe-SBD (b) 2D-SBD

(c) 2D-SBD + deep p-well

(d) 2D-SBD + deep p-well with CSL extension (This work)

because p-Base structure is designed to control the reverse bias of Schottky junction in the blocking mode. Although reverse leakage is well suppressed by the junction barrier effect, leakage may increase when temperature is elevated extremely. As for the model with wide W<sub>JBS</sub>, leakage continues to increase even after gate was turned off, which leads to thermal runaway. Choosing metals with high Schottky barrier height and narrower W<sub>JBS</sub> are the solution to reduce leakage of SBD in SC operation. However, both of them simultaneously degrade J<sub>umax</sub> because of higher voltage drop and loss of effective area. We determined the maximum W<sub>JBS</sub> essential for securing SC ruggedness through the TCAD investigation and used it in designing the cell structure, which is described below.

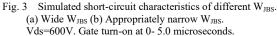

#### B. J<sub>umax</sub> improvement by the extended CSL

$J_{umax}$  improvement by modifying the device structure without changing metal or  $W_{JBS}$  is discussed. We have reported that the clamping effect of embedded SBDs against the bipolar conduction is strongly influenced by the spreading of SBD current[7-8]. Now we examine the contribution of CSL structure in deep p-well structure in order to improve

Fig. 2 Schematical diagram of the simulated device structure.

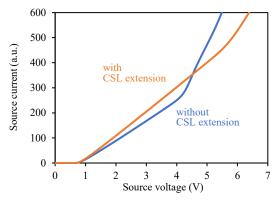

fundamental Jumax by comparing the developed structure with CSL extension to the conventional structure without CSL extension. Extended CSL is placed under the ohmic contact region alternating with some portion of deep p-well. Injected SBD current can easily conduct below the p-n junction underneath the ohmic contacts. What is important is that introducing the CSL extension does not influence the shield effect on the Schottky interface. This is because the SBD junction is always placed between the deep p-well stripes in the common spacing of W<sub>JBS</sub>. Therefore, low leakage of SBD in the reverse bias can be maintained while enhancing spreading of SBD current in the forward bias. To evaluate the enhancement effect in SBD current spreading, device structure models combine cross-sectional planes perpendicular and parallel to the MOS gate stripes of the cell structure (Fig. 4). Considering this model is equivalent to examining the longest route of SBD current. Figure 5 shows the simulated diode

Fig. 4 Simplified device structure used in the TCAD simulation.(a) conventional structure without CSL extension.(b) proposed structure with CSL extension.Arrow lines schematically illustrate SBD current flow.

Fig. 5 Simulated diode characteristics. 175°C

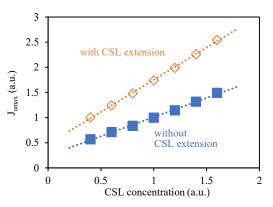

Fig. 6 Simulated Jumax dependency on the CSL doping concentration.

characteristics at the high temperature of 175°C. When source voltage larger than Schottky barrier height is applied, unipolar current through SBD linearly increases. When even larger voltage is applied, bipolar current through parasitic p-n junction is observed.  $J_{\text{umax}}$  which is the boundary point between unipolar and bipolar conduction is determined by the curvature transition. Obvious increase in Jumax by introducing CSL extension was confirmed. Spreading SBD current below parasitic p-n junction modulates potential distribution, which prevents bipolar conduction. Figure 6 shows the Jumax dependency on doping concentration of CSL. Jumax is almost doubled by introducing CSL extension over all simulated CSL doping concentrations. Since higher doping concentration of CSL increases total leakage of the device and not only of the embedded SBD region, CSL extension is fascinating when considering overall design of SBD-embedded MOSFET chip. It is shown that CSL extension enhances the current spreading effect, leading to fundamental improvement in Jumax without modulating W<sub>JBS</sub>. Doping concentrations of CSL were also determined through the TCAD analysis.

## III. DEMONSTRATION OF SUPERIOR PERFORMANCE TRADE-OFF

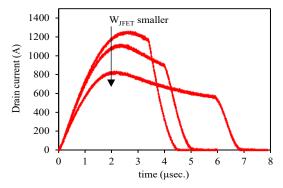

We fabricated 1.2-kV-class SiC MOSFETs utilizing the developed structure with deep p-well employing CSL extension. Devices with different  $W_{JFET}$  (JFET width) were prepared and tested in order to confirm the trade-off relationship between  $R_{on}A$  and SC ruggedness. SC stress is repeatedly applied while increasing duration until device is destroyed, and the final duration was determined to be SCWT (Short-circuit withstand

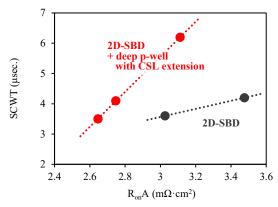

time). Figure 7 shows the SC waveforms when destruction happened. Immediately after gate turned on, drain current increased and saturated in 2-3 microseconds. After drain current once decreased to zero by gate turn-off, the devices were destroyed in about ten microseconds after turn-off (not shown in the figure). Narrower  $W_{JFET}$  diminished the peak current and resulted in longer SCWT. This dependency is evidence supporting the existence of a mechanism whereby JFET resistance suppresses short-circuit current and narrower  $W_{JFET}$  emphasized this self-stop effect. Figure 8 shows the trade-off relationship between  $R_{on}A$  and SCWT. Compared to conventional design with shallow p-well structure, the developed structure with deep p-well exhibited better SC ruggedness with smaller  $R_{on}A$  compromise. It is demonstrated that deep p-well structure evidently improves SC ruggedness.

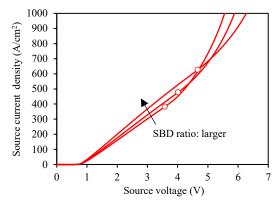

We also fabricated MOSFETs with different SBD area ratios and common  $W_{JBS}$  in order to evaluate the clamping effect of integrated SBDs. Figure 9 shows the diode characteristics measured at the high temperature of 175°C. Unipolar current by embedded SBD linearly increased and conductivity modulation due to bipolar conduction through parasitic p-n diode was observed as well as the simulation result shown in Figure 3. As the contribution of enlarged Schottky junction area, the amount of unipolar current was reasonably increased. Although CSL structure and  $W_{JBS}$  were not changed, increase in source voltage of  $J_{umax}$  was measured. It is suggested that plenty of SBD current also contributed to modification of the potential near the p-n junctions, which

Fig. 7 Measured short-circuit characteristic of fabricated MOSFETs with various  $W_{\rm JFET}.$

Fig. 8 Relationship between measured SCWT and RonA.

Fig. 9 Diode characteristics of 1.2-kV-class MOSFETs measured at the high temperature of 175°C. Circles on the line indicate J<sub>umax</sub>.

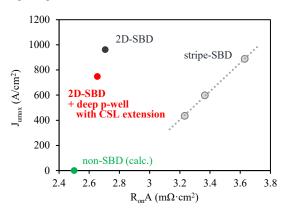

Fig. 10 Relationship between measured Jumax (175°C) and RonA (R.T.).

suppressed bipolar conduction more effectively. We also confirmed that  $R_{on}A$  was not affected by enlarging SBD area ratio. This proves that ohmic contact and source drift have minor effects on the total resistance of the fabricated devices. Figure 10 shows the relation between  $J_{umax}$  and  $R_{on}A$  of the MOSFETs with a typical design. Obtained  $J_{umax}$  was certainly smaller than that of the conventional device structure with shallow p-well depth. It is supposed that optimization, such as enlarging the SBD area ratio, would realize a better trade-off between  $J_{umax}$  and  $R_{on}A$ . What is important is that feasibility of improving the trade-off of low  $R_{on}A$ , high  $J_{umax}$  and good SC ruggedness by the developed cell design is demonstrated.

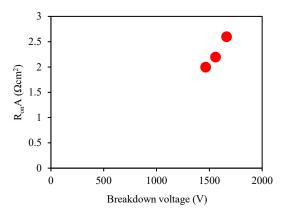

#### IV. RESISTANCE REDUCTION UTILIZING LEAKAGE SUPPRESSION

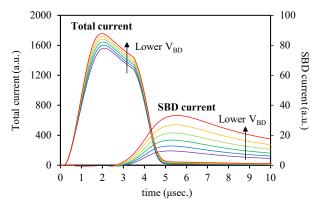

We examined further  $R_{on}A$  reduction by aggressive tuning of the drift layer design. Figure 11 shows the simulated SBD leakage in SC condition when the various drift layer designs are adopted. Although leakage increased, thermal runaway was not observed owing to the excellent electric field reduction effect of the developed deep p-well structure. Fabricated MOSFET with the optimized design demonstrated ultra-low  $R_{on}A$  of 2.0 m $\Omega \cdot cm^2$  (Fig. 12). Reduction in SBD leakage is an important effect that offers flexibility in designing the entire device structure of SBD-embedded MOSFET.

Fig. 11 Simulated SC characteristics of the structures with various drift layer designs. Vds=600V. Gate turn-on at 0- 3.5 microseconds. Breakdown voltage were culculated to be 1601, 1550, 1500, 1445 and 1383 V, respectively.

Fig. 12 Measured  $R_{on}A$  and breakdown voltage of MOSFETs with various drift layer designs.

## V. SUMMARY

The device structure of SiC MOSFET with embedded SBD was investigated in order to improve the complicated trade-off relationship of on-state resistance, diode conduction capability, and SC ruggedness. Introducing deep p-well and modifying the shape of CSL structure were considered. TCAD simulation revealed optimal geometry to shield integrated Schottky junction and Jumax improvement effect by enhanced SBD current spreading. Fabricated 1.2-kV-class MOSFETs demonstrated improvement in the trade-off relationship between SC-ruggedness and RonA as the effect of introducing deep p-well structure. Measured diode characteristics showed good unipolar conduction capability although further tuning is desired. The developed design technology allowed the aggressive drift layer design and the fabricated device finally exhibited R<sub>on</sub>A of 2.0 m $\Omega$ ·cm<sup>2</sup>, which is outstandingly low for SBD-embedded 1.2-kV-class SiC MOSFET.

#### REFERENCES

- K. Kawahara, S. Hino, K. Sadamatsu, Y. Nakao, Y. Yamashiro, Y. Yamamoto, T. Iwamatsu, S. Nakata, S. Tomohisa and S. Yamakawa, "6.5 kV schottky-barrier-diode-embedded SiC-MOSFET for compact full-unipolar module," 2017 29th International Symposium on Power Semiconductor Devices and IC's (ISPSD), Sapporo, Japan, 2017, pp. 41-44.

- [2] H. Kono, S. Asaba, T. Ohashi, T. Ogata, M. Furukawa, K. Sano, M. Yamaguchi and H. Suzuki, "Improving the specific on-resistance and short-circuit ruggedness tradeoff of 1.2-kV-class SBD-embedded SiC MOSFETs through cell pitch reduction and internal resistance optimization," 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 2021, pp. 227-230.

- [3] S. Asaba, M. Furukawa, Y. Kusumoto, R. Iijima and H. Kono, "Design guidelines for SBD integration into SiC-MOSFET breaking Ron A diode conduction capability trade-off," 2022 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2022, pp. 9.2.1-9.2.4.

- [4] K. Kashiwa, M. Takahashi, Y. Kitamura, H. Yano and N. Iwamuro, "Comparative study on short-circuit and surge current capabilities of 1.2 kV SiC SBD-embedded MOSFETs", Japanese Journal of Applied Physics, 62, SC1073, 2023.

- [5] D. Kim, S. DeBoer, S. Y. Jang, A. J. Morgan and W. Sung, "A Comparison of Short-Circuit Failure Mechanisms of 1.2 kV 4H-SiC MOSFETs and JBSFETs," 2022 IEEE 9th Workshop on Wide Bandgap Power Devices & Applications (WiPDA), Redondo Beach, CA, USA, 2022, pp. 54-57.

- [6] D. Kim, S. Y. Jang, S. DeBoer, A. J. Morgan and W. Sung, "An Optimal Design for 1.2kV 4H-SiC JBSFET (Junction Barrier Schottky Diode Integrated MOSFET) With Deep P-Well," in *IEEE Electron Device Letters*, vol. 43, no. 5, pp. 785-788, May 2022.

- [7] T. Ohashi, H. Kono, S. Kanie, T. Ogata, K. Sano, H. Suzuki, S. Asaba, S. Fukatsu and R. Iijima, "Improved Clamping Capability of Parasitic Body Diode Utilizing New Equivalent Circuit Model of SBD-embedded SiC MOSFET," 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 2021, pp. 79-82.

- [8] M. Furukawa, Y. Shimizu, K. Tanaka, Y. Kotani, M. Kobayashi, H. Kono, H. Hayakawa and G. Tchouangue, "650-V and 1200-V SiC MOSFETs with Low RonA and Strong Reduction in Switching Losses," *PCIM Europe 2022; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, Nuremberg, Germany, 2022, pp. 1-6.