# Package Mounting Guide QFN

**Revision 1.0**

2016-03

TOSHIBA CORPORATION

## Table of Contents

| Pre | oface                                                             | . 4 |

|-----|-------------------------------------------------------------------|-----|

| F   | Purpose of this document                                          | . 4 |

| I   | ntended Audience                                                  | . 4 |

| F   | References for package                                            | . 4 |

| A   | Abbreviation                                                      | . 4 |

| 1.  | Overview                                                          | . 5 |

| 2.  | Package structure                                                 | . 5 |

| 3.  | Design guide for printed wiring board                             | . 5 |

| 3   | 3.1. Lead design                                                  | . 5 |

| 3   | 3.2. Design around E-Pad                                          | . 5 |

|     | 3.2.1. Land pattern and solder resist design                      | 6   |

|     | 3.2.2. Arrangement and number of thermal via                      |     |

|     | 3.2.3. Thermal via dimensions                                     |     |

| 3   | 3.3. Metal mask design                                            | . 8 |

| 4.  | Mounting guide for printed wiring board                           | . 9 |

| 2   | I.1. Mounting flow                                                | . 9 |

|     | 4.1.1. Printing solder paste                                      | 9   |

|     | 4.1.2. Mounting package                                           | 9   |

|     | 4.1.3. Soldering (reflow soldering)                               | 9   |

|     | 4.1.4. Visual inspection                                          | 9   |

| 2   | I.2. Reflow thermal profile                                       | 10  |

| 5.  | Rework                                                            | 11  |

| 6.  | PCBA design dimensions for reference (package: QFN48-P-0707-0.50) | 12  |

| 7.  | Revision History                                                  | 13  |

| RE  | STRICTIONS ON PRODUCT USE                                         | 14  |

## List of Figures

| Figure 3.1 Land pattern example of E-Pad                        |  |

|-----------------------------------------------------------------|--|

| Figure 3.2 Design example of solder mask                        |  |

| Figure 3.3 Heat dissipation image                               |  |

| Figure 3.4 Relation between thermal via and heat resistance     |  |

| Figure 3.5 Images of land pattern and thermal via arrangement . |  |

| Figure 3.6 Recommended thermal via dimensions                   |  |

| Figure 3.7 Recommended metal mask pattern                       |  |

| Figure 4.1 Thermal profile example                              |  |

| Figure 5.1 Rework overview                                      |  |

## List of Tables

| Table 2.1 | Package characteristic | 5 |

|-----------|------------------------|---|

| Table 3.1 | Revision History1      | 3 |

#### Preface

#### Purpose of this document

This document describes design techniques and mounting methods for improving the solder ability and heat dissipation of our products, and aims at producing the the printed circuit board assembly (PCBA) with high manufacturability.

#### **Intended Audience**

This document is to be intended for use as a guide for those who are involved in the printed wiring board design and soldering process. The knowledge of heat dissipation and package mounting methods is required for use.

#### **References for package**

This document describes the printed wiring board design and the PCBA guidelines. Since each package has a different land pattern dimension, refer to the following documents for each package when you design the printed wiring board.

| Document                              | Note                             |

|---------------------------------------|----------------------------------|

| Package Mounting Guide                | This document                    |

| Technical data sheet                  | Package information (dimensions) |

| Land pattern dimensions for reference | Land patterns for each package   |

#### Abbreviation

Some of the abbreviations used in this document are shown below.

- SMD Surface Mount Device

- QFN Quad Flat Non-Leaded Package

- CAD Computer Aided Design

## 1. QFN

Recently, many circuits are integrated in semiconductor devices by refinements and advanced features, and also calorific values are increasing due to high-speed operation. Moreover, the structure is difficult to radiate heat due to miniaturization and increased density of electric devices. Then, the heat problems of the semiconductor are an important factor in electronic device development because it affects the operation speed and the product life. On the other hand, poor-wetting of solder such as voids may occur in the case of conventional lead-free soldering, and heat dissipation or reliability of the soldering may be spoiled. As an example which solves these problems, the design technique and the mounting method of improving the heat dissipation and the reliability are explained.

## 2. Package structure

Packages are divided into two types by the mounting method; the pin insertion type and surface-mount type (hereinafter SMD). This document is targeted to the QFN in SMD packages. The package characteristics are as follows.

| Name | Figure | Characteristic                                                                                                                                                                                                                                     |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFN  |        | A package having single-inline terminal pads along four edges<br>of the bottom face. The terminal pads may or may not be<br>exposed on the package sides.<br>(Quotations from: JEITA ED-7303C, Names and Codes for<br>Integrated Circuit Packages) |

| Table 2.1 | Package  | characteristic  |

|-----------|----------|-----------------|

|           | i uonugo | 011414010110110 |

In the QFN package, a metallic pad is exposed from the center of the package bottom, and the pad is called Exposed pad (hereinafter E-Pad). The heat dissipation and soldering intensity are high by soldering E-Pad to the printed wiring board.

## 3. Design guide for printed wiring board

## 3.1. Lead design

For the lead shapes and dimensions, refer to the land pattern dimensions for reference. The dimensions are compliant with JEITA ET-7501 Level3. The CAD data of these dimensions are available on the Toshiba website.

## 3.2. Design around E-Pad

Form the land pattern for the E-Pad on the package with E-Pad, and solder to the printed wiring board. Since the land pattern for the E-Pad has the large soldering area, air bubbles remain easily and they cause voids. Moreover, since the lead-free soldering used in many solders is poor-wetting and high surface tension at dissolution, voids tend to occur. Therefore, measures to prevent voids are required. In the next sections, the design is explained with the Figure of QFN48-P-0707-0.50.

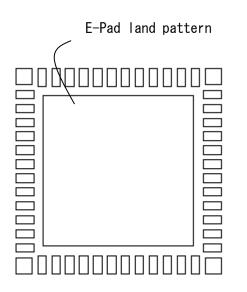

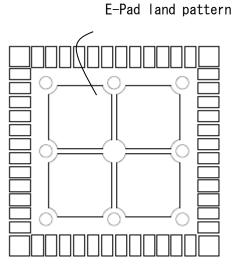

#### 3.2.1. Land pattern and solder resist design

Soldering area where E-Pad is soldered is made by dividing a land pattern by a solder resist. Generally, the smaller number of divisions makes a soldering area larger, and which makes voids more likely to occur. On the contrary, if the number of division is large, a solder resist area becomes large, and a soldering area becomes small, then the solder intensity tends to be weak. To keep the stable solder intensity, it is important to arrange the solder area with few deviations, in sufficient balance. The solder area with the solder resist is recommended about 50% or more of area to the E-Pad.

Figure 3.1 Land pattern example of E-Pad

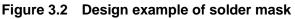

#### 3.2.2. Arrangement and number of thermal via

Thermal vias are through holes that go through a printed wiring board, and raise heat dissipation of the package. It is recommended that the thermal vias are arranged to the perimeter of the E-Pad land pattern. Connect the one side of a thermal via to the E-Pad land pattern, and the other side to the copper plane of the internal layer. This copper plane serves as heat diffusion. The optimum number of thermal vias is determined by thermal and electric analysis or measurement with consideration of the power consumption of products.

Figure 3.3 Heat dissipation image

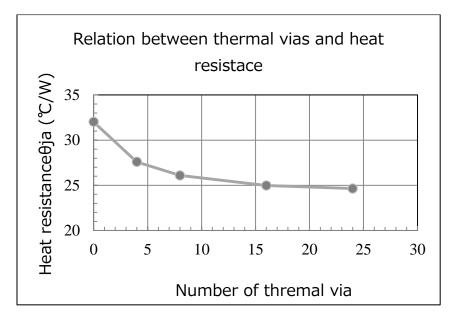

Figure 3.4 shows a simulation result of heat resistance simulation for the thermal via arrangement and number of thermal vias. Figure 3.5 shows images of relationship between the number of thermal via and arrangement. Since heat is accumulated directly under the package even if many thermal vias are set in the E-Pad, heat dissipation cannot be expected. Arranging thermal vias evenly on the edge of the E-Pad land pattern can diffuse heat and lowers heat resistance with the small number of those. The recommended optimum thermal vias dimension is about 3 mm long according to the simulation result and the land pattern dimensions. Number of thermal via should be calculated with the perimeter length of a package to be used and the recommended interval.

| P-VQFN48-0707-0.50-004 (E-Pad: 5.54 mm × 5.5 mm)                         |

|--------------------------------------------------------------------------|

| $2.8 \text{ mm} \times 2.8 \text{ mm} \times 0.29 \text{ mm}$            |

| Equivalent for 4-layer board of JEDEC (width: 76.2 mm, length: 114.3 mm) |

| 25°C                                                                     |

| 0m/s                                                                     |

|                                                                          |

| Figure 3.4 | Relation between thermal via and heat resistance |

|------------|--------------------------------------------------|

|------------|--------------------------------------------------|

| Number of thermal via<br>and arrangement     | 1            | 4                  | 8 | 16 | 24 |

|----------------------------------------------|--------------|--------------------|---|----|----|

| Inside of land<br>pattern for<br>Exposed Pad | Land pattern | o o<br>Thermal via |   |    |    |

#### Figure 3.5 Images of land pattern and thermal via arrangement

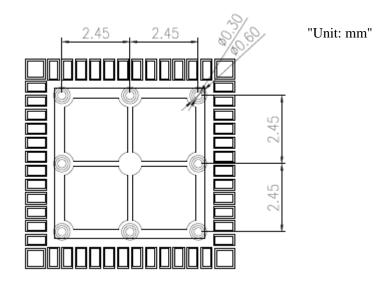

#### 3.2.3. Thermal via dimensions

Thermal vias are arranged outside of the E-Pad, and take intervals from the land pattern. This interval prevents soaking up solder to the thermal vias and solder ball generation. The diameter of the thermal via is about 0.30 to 0.33 mm, and copper via plating about 20  $\mu$ m is recommended for the inside of the via.

#### 3.3. Metal mask design

A metal mask is a lithograph for printing a solder paste on the land pattern of a printed wiring board. Recommended thickness of the metal mask is from 125 to 175  $\mu$ m. However, the adjustment of the thickness may be also required due to the balance of peripheral parts size.

#### Figure 3.7 Recommended metal mask pattern

## 4. Mounting guide for printed wiring board

### 4.1. Mounting flow

The recommended soldering method for each package is reflow process. For the reflow process, refer to section 4.1.1 to 4.1.4.

#### 4.1.1. Printing solder paste

A solder paste is a pasty composite material made by mixing solder, flux, and the like. The solder paste is printed through a metal mask to the land pattern of the printed wiring board.

#### 4.1.2. Mounting package

A package is mounted to the position where the solder paste is printed. In addition, use of the package which absorbed moisture may generate a crack because of the heat generated by soldering. Please observe the precautions for unpacking conditions. For the package tends to absorb moisture, it is recommended to bake in advance.

#### 4.1.3. Soldering (reflow soldering)

The printed wiring board mounting a package is soldered by the heating of a reflow oven. The package should be heated so that the temperature of the soldering may not exceed the maximum reflow temperature profile.

#### 4.1.4. Visual inspection

In the visual inspection, a position gap, a solder bridge, and a poor-wetting soldering are confirmed.

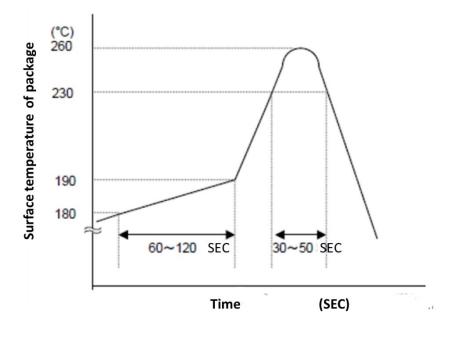

## 4.2. Reflow thermal profile

Figure 4.1 shows an example of the reflow thermal profile. In this example, a surface temperature of the package is preheated for 60 to 120 seconds at about 180 to 190°C. After that, the temperature raises gradually, and the surface temperature of the package continues the state which is about 230 to 260°C (peak temperature) for 30 to 50 seconds. In addition, temperature profiles differ due to a package. Confirm the temperature profile of the package to be used.

- Temperature and time should be set less than the above profile.

- Optimum temperature should be set due to solder paste types.

Figure 4.1 Thermal profile example

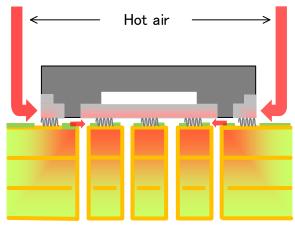

## 5. Rework

Use a heater nozzle which heats the target package only to remove the package. The PCBA is preheated using a convection-type heater. Thermal profile at removal is the same as that of mounting, however, the peak time should be as short as possible. When the package with E-Pad is difficult to remove, heat the back of the PCBA with a heater. In the case of removal, please take care so that the land on the board does not exfoliate.

In addition, Toshiba warrants neither for reusing of the removal package nor the soldering reliability of removal part.

Figure 5.1 Rework overview

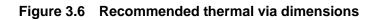

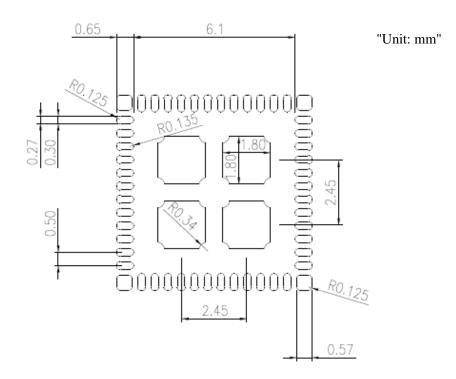

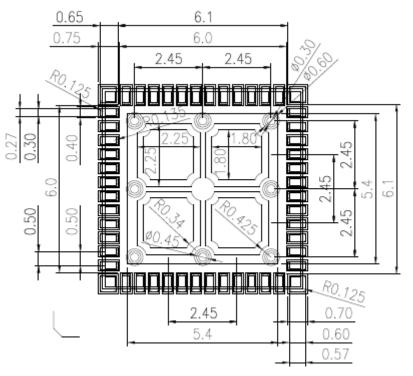

## 6. PCBA design dimensions for reference (package: QFN48-P-0707-0.50)

″Unit: mm″

Notes

- All linear dimensions are given in millimeters unless otherwise specified.

- This drawing is based on JEITA ET-7501 Level3 and should be treated as a reference only. TOSHIBA is not responsible for any incorrect or incomplete drawings and information.

- You are solely responsible for all aspects of your own land pattern, including but not limited to soldering processes.

- The drawing shown may not accurately represent the actual shape or dimensions.

- Before creating and producing designs and using, customers must also refer to and comply with the latest versions of all relevant TOSHIBA information and the instructions for the application that Product will be used with or for.

## 7. Revision History

|          | · · · · · · · · · · · · · · · · · · · |                |  |  |

|----------|---------------------------------------|----------------|--|--|

| Revision | evision Date Description              |                |  |  |

| 1.0      | 2016-03-17                            | Newly released |  |  |

|          |                                       |                |  |  |

Table 7.1 Revision History

#### **RESTRICTIONS ON PRODUCT USE**

- Toshiba Corporation, and its subsidiaries and affiliates (collectively "TOSHIBA"), reserve the right to make changes to the information in this document, and related hardware, software and systems (collectively "Product") without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.