CDMOS 形リニアー集積回路 シリコン

# **TB9103FTG**

Automotive 1ch H-bridge(2ch Half-bridge) Gate Driver

### 1. 概要

TB9103FTG は、車載用 2ch Half-bridge Gate Driver です。

1ch H-bridge Gate Driver としても使用できます。

スリープモードにより低消費電力化が可能です。

各種異常検出機能を有し、異常時は、ゲート駆動をシャットダウンし、DIAG 端子(オープンドレイン)より異常を通知します。

### 2. 用途

n型 MOSFET と組み合せて使用し、車載用スライドドア、バックドアなどのラッチモーター用途として、またシート、ウィンドウなどの駆動用途に適しています。

また、メカリレーを使用しているモーター制御部の半導体化に適 しています。

質量: 0.04 g (標準)

### 3. 特長

- 制御モードを 2 モード搭載: Half-bridge mode、H-bridge mode

- 2ch の独立した Half-bridge として使用可能

- ch 毎にデッドタイム制御、シャットダウン制御

- Half-bridge を組み合わせ H-bridge として使用可能

- H-bridge としてデッドタイム制御、シャットダウン制御

- 低電力スリープモード

- 各種異常檢出搭載:

- VB 低電圧検出、VCC 低電圧検出、VCP 高電圧検出

- ゲート・ソース間電圧検出、ゲート電圧異常シャットダウン

- ドレイン・ソース間電圧検出(検出レベル設定可能)、過電流シャットダウン

- 過熱検出、シャットダウン

- 異常検出時オープンドレイン出力端子から通知

- 動作電圧範囲: 7~18V

- AEC-Q100 Rev-J (適合予定): グレード1

- 小型パッケージ OFN24 4mm□

製品量産開始時期 2025-02

これは参考資料です。本資料での最終機器設計はしないでください。

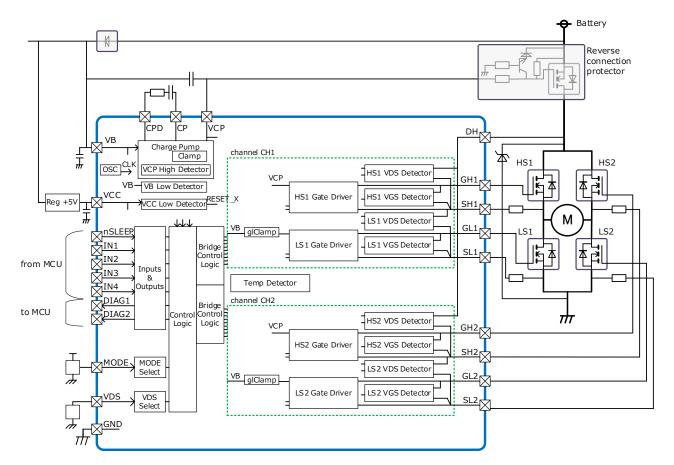

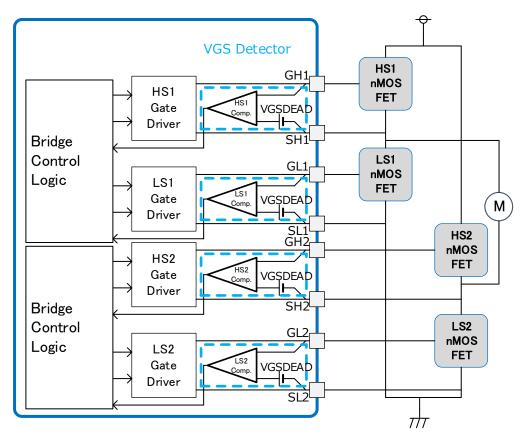

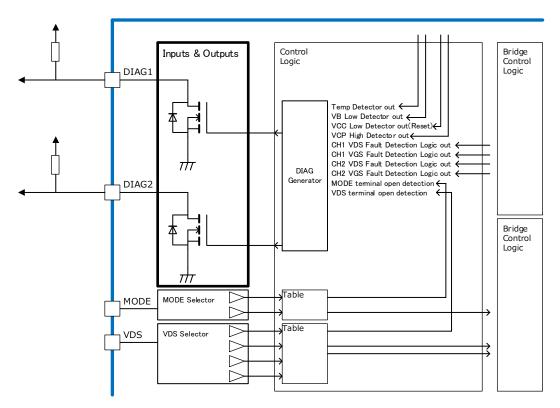

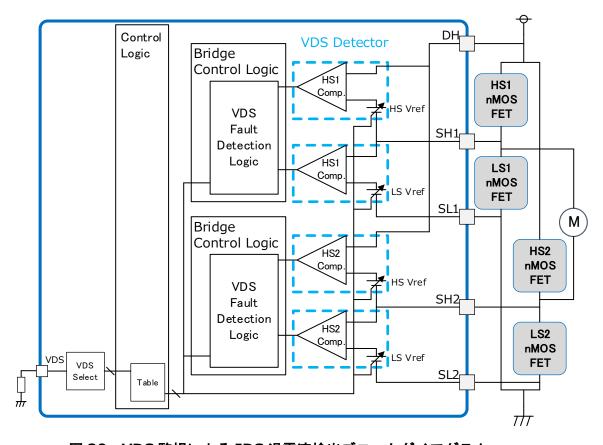

### 4. ブロック図

図 1 TB9103FTG 機能ブロック図

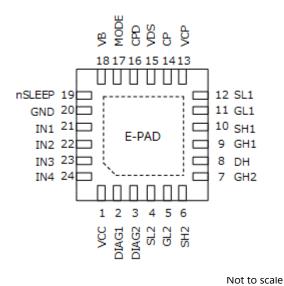

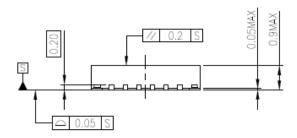

### 5. 端子配置図

図 2 端子配置図 (top view)

**TB9103FTG**

### 6. 端子説明

### 表 1 TB9103FTG 端子表

| 端子番号 | 名称     | 入出力 | 端子説明                                                                          |

|------|--------|-----|-------------------------------------------------------------------------------|

| 1    | VCC    | -   | IC の電源端子です。                                                                   |

| 2    | DIAG1  | OUT | 異常検出機能による診断結果の出力端子です。                                                         |

| 3    | DIAG2  | OUT | 異常検出機能による診断結果の出力端子です。                                                         |

| 4    | SL2    | IN  | ローサイド FET "LS2"向けゲートドライバ—回路の基準端子です。<br>ローサイド FET "LS2"の VDS 検出に用いる基準端子です。     |

| 5    | GL2    | OUT | ローサイド FET "LS2"向けゲートドライバ—回路の出力端子です。                                           |

| 6    | SH2    | IN  | ハイサイド FET "HS2"向けゲートドライバ—回路の基準端子です。<br>ハイサイド FET "HS2"の VDS 検出に用いるモニター基準端子です。 |

| 7    | GH2    | OUT | ハイサイド FET "HS2"向けゲートドライバ—回路の出力端子です。                                           |

| 8    | DH     | IN  | ハイサイド FET "HS1", "HS2"の VDS 検出に用いる基準端子です。                                     |

| 9    | GH1    | OUT | ハイサイド FET "HS1"のゲート駆動信号出力端子です。                                                |

| 10   | SH1    | IN  | ハイサイド FET "HS1"のソース端子電圧入力端子です。                                                |

| 11   | GL1    | OUT | ローサイド FET "LS1"のゲート駆動信号出力端子です。                                                |

| 12   | SL1    | IN  | ローサイド FET "LS1"の VDS 検出に用いる基準電位の入力端子です。                                       |

| 13   | VCP    | -   | IC の電源端子です。チャージポンプ回路の最終入出力端子です。<br>平滑キャパシタを接続します。                             |

| 14   | СР     | -   | IC の電源端子です。チャージポンプ回路の昇圧入力端子です。                                                |

| 15   | VDS    | IN  | VDS 検出の検出電圧を設定するための電圧入力端子です。                                                  |

| 16   | CPD    | -   | IC の電源端子です。チャージポンプ回路のドライブ出力端子です。                                              |

| 17   | MODE   | IN  | ブリッジの動作モードを設定する電圧入力端子です。                                                      |

| 18   | VB     | -   | IC の電源端子です。バッテリー電圧を印加してください。                                                  |

| 19   | nSLEEP | IN  | IC をスリープモードにする電圧入力端子です。<br>電圧をロジックレベル Low にするとスリープモードに入ります。                   |

| 20   | GND    | -   | GND 端子です。                                                                     |

| 21   | IN1    | IN  | ブリッジを構成するパワーFET の ON/OFF を制御するロジックレベル信号入力端子 1 です。                             |

| 22   | IN2    | IN  | ブリッジを構成するパワーFET の ON/OFF を制御するロジックレベル信号入力端子 2 です。                             |

| 23   | IN3    | IN  | ブリッジを構成するパワーFET の ON/OFF を制御するロジックレベル信号入力端子 3 です。                             |

| 24   | IN4    | IN  | ブリッジを構成するパワーFET の ON/OFF を制御するロジックレベル信号入力端子 4 です。                             |

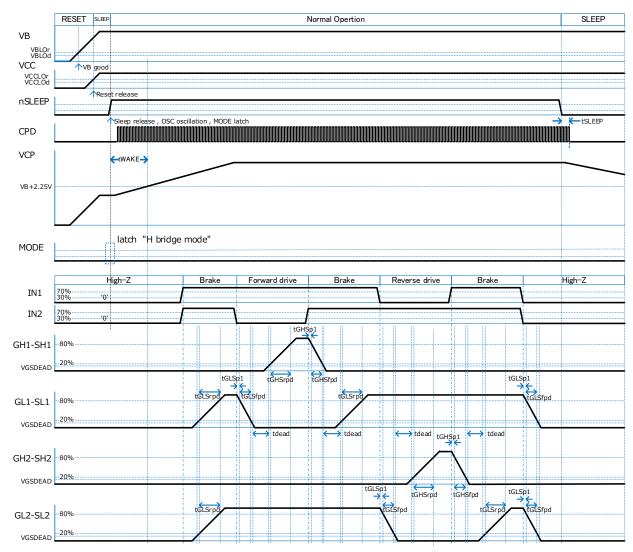

### 7. 動作説明

TB9103FTG が取りうる動作状態を、表 2 に示します。

TB9103FTG は、VCC が低電圧であることを検出すると、リセット状態となります。

また、VCC が通常電圧時に nSLEEP=Low であると、TB9103FTG はスリープ状態となり、各部の動作は停止します。

スリープ状態では、DIAG 出力は High-Z 状態となりますが、異常状態を記憶しているラッチは初期化せず値を保持します。 DIAG 出力はスリープが解除されると異常状態に従って出力します。

スリープ状態を指示した後、少なくとも tSLEEP の最大期間は、スリープ状態を維持してください。 通常動作状態に移行すると、TB9103FTG は MODE 端子を見て Half-bridge か H-bridge かの動作モードを設定します。動作モード設定を保持する条件は、"リセット解除状態、かつスリープ解除状態(nSLEEP=High)"が成立したときです。

リセット時とスリープ時には、nSLEEP,IN1, IN2, IN3, IN4 を全て Low にしてください。

通常動作状態を指示した後 tWAKE 期間は、チャージポンプ電圧が上昇するまでゲートドライブを避けるため IN1, IN2, IN3, IN4 を全て Low("High-Z")にしてください。

ゲートドライブ部は、MCU の指示を IN1, IN2, IN3, IN4 から受け取り、指示に応じたゲート出力 (GH1, GL1, GH2, GL2) をします。ゲートドライブ部は、MCU からの指示が変更される毎に、デッド タイムとして自動的に外付けのハイサイド側 FET とローサイド側 FET がどちらもオフであることを確認します。

### 表 2 動作状態

| IC の動作状態                               | チャージ<br>ポンプ | Bridge<br>Control<br>Logic | DIAG 出力<br>(DIAG1,<br>DIAG2) | ゲート出力<br>(GH1, GL1,<br>GH2, GL2) | 外部 FET の動作状態                |

|----------------------------------------|-------------|----------------------------|------------------------------|----------------------------------|-----------------------------|

| VCC 低下検出解除状態<br>nSLEEP=H<br>(スリープ解除状態) | 動作          | 動作                         | 動作                           | 動作                               | 動作<br>(ゲート出力に応じた動作)         |

| VCC 低下検出解除状態<br>nSLEEP= L<br>(スリープ状態)  | 停止          | 停止<br>注 2                  | High-Z<br>注 1<br>注 3         | RL                               | High-Z<br>(ハイサイド、ローサイドともオフ) |

| VCC 低下検出状態<br>nSLEEP=H<br>(スリープ解除状態)   | 停止          | 停止<br>初期状態                 | L                            | RL                               | High-Z<br>(ハイサイド、ローサイドともオフ) |

| VCC 低下検出状態<br>nSLEEP=L<br>(スリープ状態)     | 停止          | 停止<br>初期状態                 | High-Z<br>注 3                | RL                               | High-Z<br>(ハイサイド、ローサイドともオフ) |

記号の説明:

RL: 抵抗による Low, L: Low, H: High, High-Z: ハイ・インピーダンス状態

注1: 異常状態を記憶している内部のラッチは値を保持しています。

注 2: スリープ時 IN1, IN2, IN3, IN4 からのあらゆる指示は、実行されません。

注 3: 外部プルアップにより High 出力します。

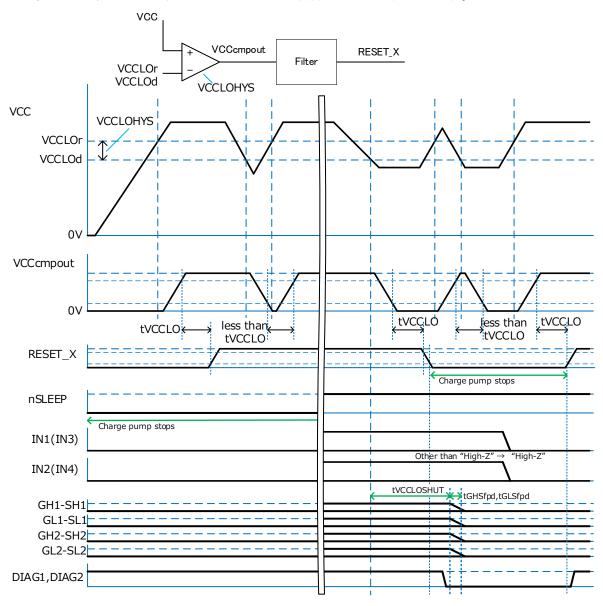

### 7.1. VCC 低電圧検出回路

VCC 低電圧検出回路は VCC 端子の電圧を監視し電圧低下を検出します。

電圧が VCCLOd 以下になるとリセットとなり、全ての回路は停止し全ての外部 FET のゲート駆動は Off(シャットダウン)となります。電圧が VCCLOr 以上になるとリセットは解除されます。リセット解 除後は通常動作を開始します。

また、チャタリングを防止するために検出用コンパレータはヒステリシス VCCLOHYS を有し、コン パレータの後段にフィルタを内蔵しており tVCCLO 未満のパルスを除去します。

図3 VCC 低電圧検出動作

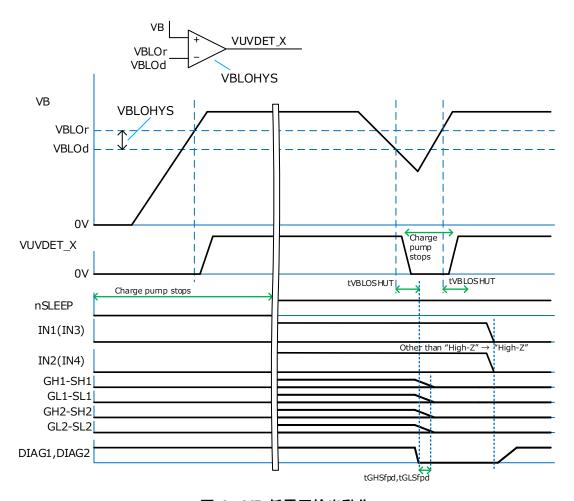

### 7.2. VB 低電圧検出回路

VB 低電圧検出回路は VB 端子の電圧を監視し電圧低下を検出します。

制御ロジック回路は、外部 FET の中途なオンを避けるため、電圧が VBLOd 以下になると、チャージ ポンプ回路を停止し、全外部 FET のゲート駆動を Off (シャットダウン) にし DIAG1, DIAG2 端子にエ ラー出力します。

その後電圧が VBLOr 以上になるとチャージポンプの動作を開始させます。ゲートドライブを再開させ るには、Half-bridge モード時は、IN1, IN2, IN3, IN4 端子を全て Low に、H-bridge モード時は、IN1, IN2 端子を Low(High-Z の指示)にします。するとシャットダウンを解除し、DIAG1, DIAG2 端子を正常 に戻し、tWAKE 時間後通常動作を開始することができます。また、チャタリングを防止するために、検 出用コンパレータはヒステリシス VBLOHYS を有しています。

図 4 VB 低電圧検出動作

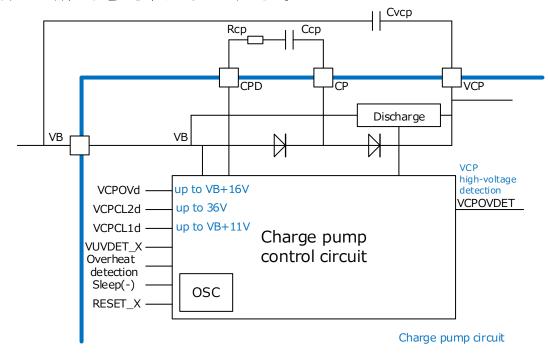

### 7.3. チャージポンプ回路

TB9103FTG は外部ハイサイド n 型 MOSFET のゲートを駆動するため、チャージポンプ回路を内蔵し ています。

その駆動はラジオの AM 帯域より下の 200kHz(Typ.)で行います。

チャージポンプ動作は、nSLEEP 端子=Low 時や、内部リセット期間、VB 低電圧検出期間は停止しま

チャージポンプ電圧はクランプ電圧 VCPCL1d を上回った場合は直ちに昇圧を停止することで一定電 圧に保たれます。

VCP 端子には外部から電圧を印加しないでください。

図 5 チャージポンプ回路例

表 3 チャージポンプ回路 動作定義

| IC の動作状態                                                             | チャージポンプの動作 | VCP 放電動作 |

|----------------------------------------------------------------------|------------|----------|

| リセット (VCC 低電圧検出)                                                     | 停止         | 停止       |

| スリープ (nSLEEP=Low)                                                    | 停止         | 停止       |

| VB 低電圧検出 (VUVDET_X=0)                                                | 停止         | 停止       |

| VCP クランプ 1 電圧超過 (VCPCL1d <vcp)< td=""><td>停止</td><td>停止</td></vcp)<> | 停止         | 停止       |

| VCP クランプ 2 電圧超過 (VCPCL2d <vcp)< td=""><td>停止</td><td>放電</td></vcp)<> | 停止         | 放電       |

| VCP 高電圧検出電圧超過 (VCPOVd <vcp)< td=""><td>停止</td><td>放電</td></vcp)<>    | 停止         | 放電       |

| 過熱検出                                                                 | 停止         | 停止       |

| 上記以外                                                                 | 動作         | 停止       |

#### 7.3.1. チャージポンプ高電圧クランプ回路

チャージポンプ電圧はTB9103FTGの素子耐圧超過を防ぐためにVCPCL2dを上回った場合には直ち に昇圧を停止するほか、外部に接続された平滑コンデンサ CVCP の放電も実施します。

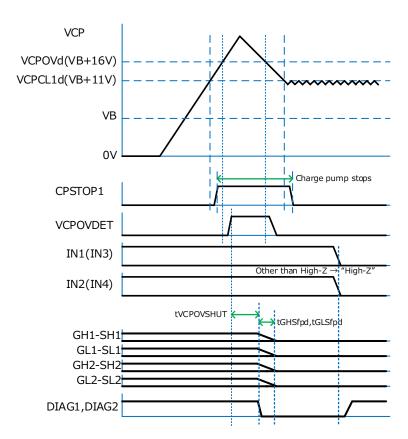

#### 7.3.2. チャージポンプ高電圧検出回路

VCP 高電圧検出回路は VCP 端子の電圧を監視し電圧上昇を検出します。

制御ロジック回路は、外部 FET のゲート、ソース間耐圧超過を防ぐため、電圧が VCPOVd を上回っ た場合には 直ちに昇圧を停止し 外部に接続された平滑コンデンサ CVCP の放電も実施します。

さらに全外部 FET のゲート駆動を Off (シャットダウン) にし DIAG1, DIAG2 端子にエラー出力しま

その後電圧が VCPOVd 以下になるとチャージポンプの動作を開始させます。

ゲートドライブを再開させるには、Half-bridge モード時は、IN1, IN2, IN3, IN4 端子を全て Low に、 H-bridge モード時は、IN1, IN2 端子を Low(High-Z の指示)にします。すると、シャットダウンを解除 し、DIAG1, DIAG2 端子を正常に戻し、tWAKE 時間後通常動作を開始することができます。

図 6 チャージポンプ高電圧検出、シャットダウン動作

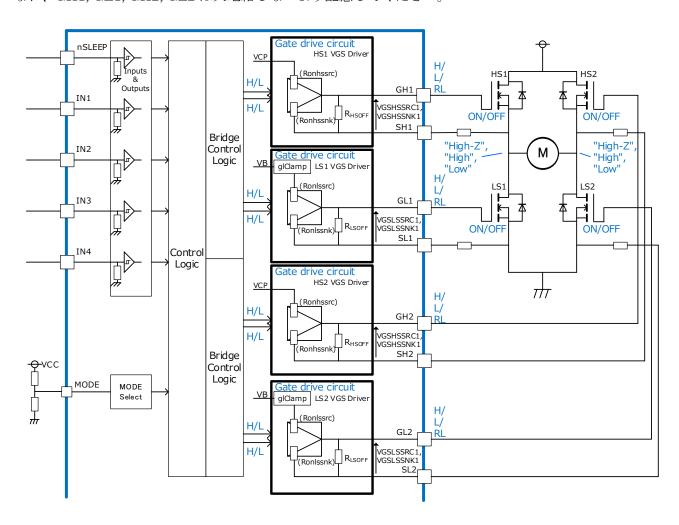

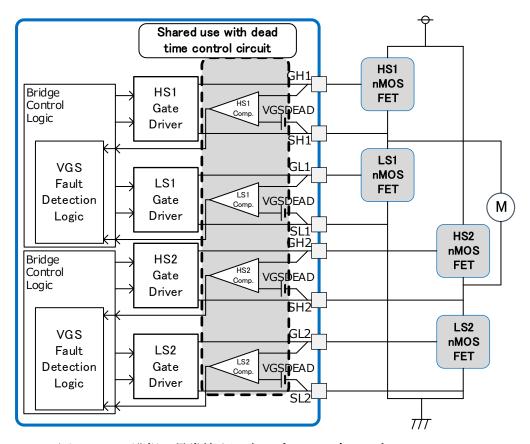

### 7.4. ゲート駆動回路

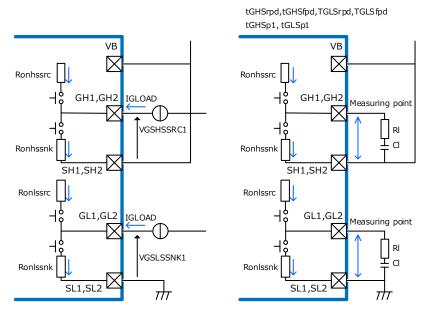

ゲート駆動部のブロック図を、図7に示します。

ハイサイドのゲートドライバは、外付けのハイサイドの n 型 MOSFET をオンするために十分な電圧が出力され、その出力抵抗 Ronhssre は  $500\Omega$ (Typ.)です。一方オフのときは出力抵抗 Ronhssnk の  $50\Omega$ (Typ.)を介して外部 FET のゲート、ソース間をシャントします。

ローサイドのゲートドライバは、外付けのローサイドのn型 MOSFET をオンするために十分な電圧が出力されますが、外部 FET のゲート電圧を定格値以下とするために、IC 内部でクランプした電圧が出力されます。その出力抵抗 Ronlssrc は  $500\Omega$ (Typ.)です。一方オフのときは出力抵抗 Ronlssnk の  $50\Omega$ (Typ.)を介して外部 FET のゲート、ソース間をシャントします。

IC がリセットやスリープの状態のときには、ゲートドライバの出力はプルダウン抵抗 RHSOFF, RLSOFF の 150k $\Omega$  (Typ.) によって外部 FET のゲート、ソース間をシャントします。 なお、GH1, GL1, GH2, GL2 は天地絡しないよう配慮してください。

図7 ゲート駆動回路のブロックダイアグラム

### 7.4.1. ゲート. ソース間電圧検出回路

デッドタイム終了を判定するため、ゲート、ソース間電圧を VGSDEAD と比較します。

図8 デッドタイム制御回路 VGS 電圧検出部

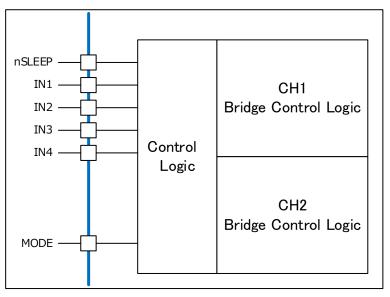

### 7.5. 制御ロジック (Control Logic , Bridge Control Logic)

TB9103FTG は、ブリッジ制御用に入力端子を5端子(nSLEEP および IN1, IN2, IN3, IN4) 有し、 また Half-bridge/H-bridge 選択用入力端子(MODE)を 1 端子有します。

図9 制御ロジック ブロック構成例

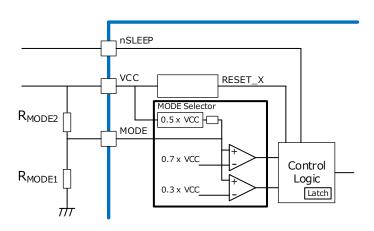

#### 7.5.1. モードの設定

TB9103FTG は、MODE 端子の電圧により、動作モードを選択することができます。この設定は、 MODE 端子を VCC にプルアップするか、GND ヘプルダウンすることで選択されますが、抵抗を介して 行う場合、IC 内部の抵抗値よりも十分小さい抵抗値を選択する必要があります。選択されたモードは、 "電源 VCC が VCCLOr を上回り、かつ、nSLEEP=High を満たしたとき"に、ラッチします。

図10にMODE端子のインターフェース回路を示します。

図 10 MODE 端子インターフェース回路

注:上図は、ICについて、機能・動作の説明をするため、一部省略、簡略化しています。

| X : 11000 till 1 % RX/C |                    |            |                           |  |  |  |  |  |

|-------------------------|--------------------|------------|---------------------------|--|--|--|--|--|

| R <sub>MODE2</sub> , R  | MODE1 設定           | MODE 端子電圧  | ブリッジモード                   |  |  |  |  |  |

| R <sub>MODE2</sub>      | R <sub>MODE1</sub> | WIODE 端于电圧 | フリッシモート                   |  |  |  |  |  |

| <47kΩ+10%               | オープン               | MODE2set   | Half-bridge mode (独立 2ch) |  |  |  |  |  |

| オープン                    | <47kΩ+10%          | MODE1set   | H-bridge mode             |  |  |  |  |  |

| オープン                    | オープン               | 上記以外       | エラー (表8 検出機能 モード端子オープン参照) |  |  |  |  |  |

表 4 MODE 端子の設定

### 7.5.1.1. モード設定端子オープン検出回路

TB9103FTG は MODE 端子オープンを検出し、全外部 FET を Off (シャットダウン)及び、DIAG1, DIAG2 端子にエラー出力します。

エラー出力の更新は再度モード状態をラッチするタイミング(リセット解除後 もしくは n SLEEP 解除後)です。

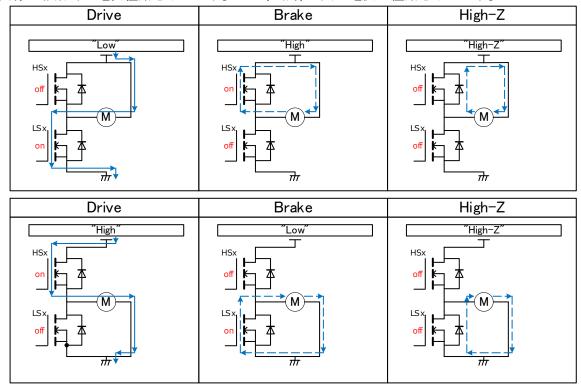

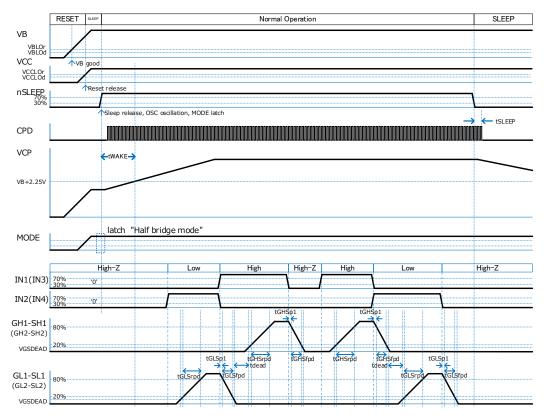

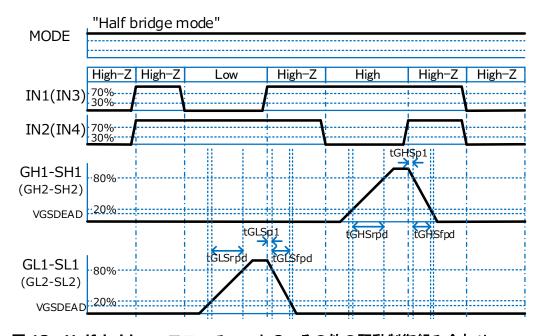

### 7.5.2. Half-bridge mode

#### 7.5.2.1. 動作説明

TB9103FTG は、Half-bridge mode 時、独立した2チャンネルとして動作します。

第1の Half-bridge CH1は IN1, IN2 端子の信号で制御されます。Half-bridge mode では、ハイサイ ドの外部 FET HS1 とローサイドの外部 FET LS1 が同時にオンしないよう、IN1, IN2 端子による駆動 指示が変更された際には、自動的にデッドタイムが挿入されます。 ゲート電圧異常検出機能は、GH1, SH1 間電圧、ならびに GL1, SL1 間電圧を監視し、IN1, IN2 端子の指示との差異を監視マスク時間外に 比較します。ドレイン電流の過電流検出機能は、DH, SH1 間電圧、ならびに SH1, SL1 間電圧を監視 し、外部 FET が十分なオン状態であることを監視マスク時間外に監視し判定します。

第2の Half-bridge CH2 は IN3, IN4 端子の信号で制御されます。Half-bridge mode では、ハイサイ ドの外部 FET HS2 とローサイドの外部 FET LS2 が同時にオンしないよう、IN3, IN4 端子による駆動 指示が変更された際には、自動的にデッドタイムが挿入されます。 ゲート電圧異常検出機能は、GH2、 SH2 間電圧、ならびに GL2, SL2 間電圧を監視し、IN3, IN4 端子の指示との差異を監視マスク時間外に 比較します。ドレイン電流の過電流検出機能は、DH, SH2 間電圧、ならびに SH2, SL2 間電圧を監視 し、外部 FET が十分なオン状態であることを監視マスク時間外に監視し判定します。

TB9103FTG は、モーター電流を測定する機能は有していません。外付けでモニター用抵抗を設置する 際は、絶対最大定格内でご使用ください。

なお、未使用のチャンネルは、入力端子 INx を Low としてください。

注: INx = IN1, IN2, IN3, IN4

#### 7.5.2.2. 真理值表

Half-bridge mode において、取りうる動作状態を表 5、表 6に示します。

表 5 第 1 の Half-bridge CH1 真理値表

| 内部     | Inputs |     |     | Out   | outs | = 4 00                       |

|--------|--------|-----|-----|-------|------|------------------------------|

| H=リセット | nSLEEP | IN1 | IN2 | GH1   | GL1  | 説明                           |

| Н      | Х      | Х   | Х   | RL    | RL   | IC はリセット モーターの相入力は High-Z    |

| L      | L      | Х   | Х   | RL    | RL   | IC はスリープモード モーターの相入力は High-Z |

| L      | Н      | L   | L   | L     | L    | モーターの相入力は High-Z             |

| L      | Н      | Н   | L   | Н     | L    | モーターの相入力は High               |

| L      | Н      | L   | Н   | L     | Н    | モーターの相入力は Low                |

| L      | Н      | Н   | Н   | d L l |      | モーターの相入力は High-Z 注 1         |

### 表 6 第 2 の Half-bridge CH2 真理値表

| 内部     | Inputs |     |     | Outp | outs | -¥.np                        |  |

|--------|--------|-----|-----|------|------|------------------------------|--|

| H=リセット | nSLEEP | IN3 | IN4 | GH2  | GL2  | 説明                           |  |

| Н      | Х      | Χ   | Х   | RL   | RL   | IC はリセット モーターの相入力は High-Z    |  |

| L      | L      | Х   | Х   | RL   | RL   | IC はスリープモード モーターの相入力は High-Z |  |

| L      | Н      | L   | L   | L    | L    | モーターの相入力は High-Z             |  |

| L      | Н      | Н   | L   | Н    | L    | モーターの相入力は High               |  |

| L      | Н      | L   | Н   | L    | Н    | モーターの相入力は Low                |  |

| L      | Н      | Н   | Н   | L    | L    | モーターの相入力は High-Z 注 1         |  |

記号の説明:

X: Don't care RL: 抵抗を介した Low L: 能動素子による Low H: 能動素子による High High-Z: ハイ・インピーダンス状態

注1: 異常検出時の解除動作は行われません。

#### 7.5.2.3. 電流経路の定義

Half-bridge mode 時、TB9103FTG で使用する外部 n型 MOSFET の電流経路を図 11 のように定義し ます。実線は駆動時の電流経路を示します。また、点線は回生電流の経路を示します。

**Preliminary**

図 11 電流経路の定義

### 7.5.2.4. 駆動制御フローチャート

Half-bridge mode における駆動制御フローチャートを図 12 に示します。 また、図12に記載していない駆動制御の組み合わせを、図13に示します。

図 12 Half-bridge フローチャート 1 (チャンネル毎)

図 13 Half-bridge フローチャート 2 その他の駆動制御組み合わせ

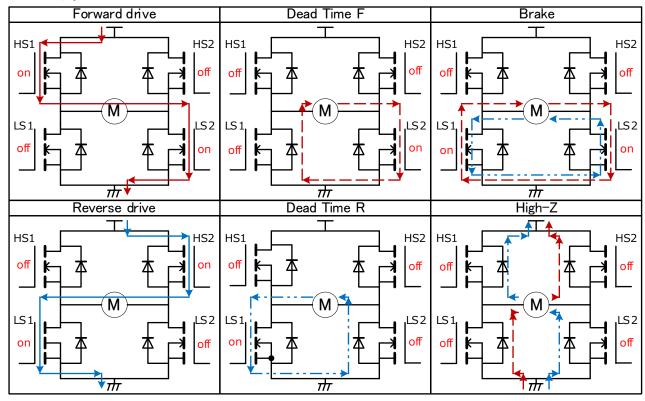

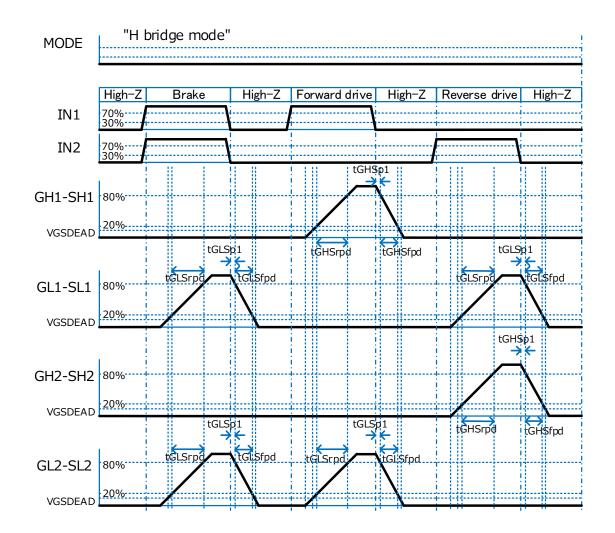

### 7.5.3. H-bridge mode

#### 7.5.3.1. 動作説明

TB9103FTG は、H-bridge mode 時、1 チャンネルの H-bridge として動作します。

制御は、IN1, IN2 端子の信号で行います。IN3, IN4 端子は、GND に接続することを推奨します。H-bridge mode では、ハイサイドの FET HS1, HS2 とローサイドの FET LS1, LS2 が同時にオンして貫通電流が流れないよう、IN1, IN2 端子による駆動指示が変更された際には自動的にデッドタイムが挿入されます。ゲート電圧異常検出機能は、GH1, SH1 間電圧、GL1, SL1 間電圧、GH2, SH2 間電圧ならびに GL2, SL2 間電圧を監視し、IN1, IN2 端子の指示との差異を監視マスク時間外に比較します。ドレイン電流の過電流検出機能は、DH, SH1 間電圧、SH1, SL1 間電圧、DH, SH2 間電圧、SH2, SL2 間電圧を監視し、IN1 がオン状態であることを監視マスク時間外に判定します。

TB9103FTG は、モーター電流を測定する機能は有していません。外付けでモニター用抵抗を設置する際は、絶対最大定格内でご使用ください。

#### 7.5.3.2. 真理値表

H-bridge mode において、取りうる論理状態を表7に示します。

#### 表7 Hブリッジモード 真理値表

| 内部         | In     | puts |     |     | Out | puts |     |                                  |  |  |

|------------|--------|------|-----|-----|-----|------|-----|----------------------------------|--|--|

| H=<br>リセット | nSLEEP | IN1  | IN2 | GH1 | GL1 | GH2  | GL2 | 説明                               |  |  |

| Н          | Х      | Х    | Х   | RL  | RL  | RL   | RL  | IC はリセット モーターの相入力は High-Z        |  |  |

| L          | L      | Х    | Х   | RL  | RL  | RL   | RL  | IC はスリープモード モーターの相入力は High-Z     |  |  |

| L          | Н      | L    | L   | L   | L   | L    | L   | モーターの相入力は High-Z                 |  |  |

| L          | Н      | Н    | L   | Н   | L   | L    | Н   | モーターの相入力は Forward drive(SH1→SH2) |  |  |

| L          | Н      | L    | Н   | L   | Н   | Н    | L   | モーターの相入力は Reverse drive(SH2→SH1) |  |  |

| L          | Н      | Н    | Н   | L   | Н   | L    | Н   | モーターの相入力は Brake                  |  |  |

記号の説明:

X: Don't care RL: 抵抗を介した Low L: 能動素子による Low、

H: 能動素子による High High-Z: ハイ・インピーダンス状態

注: IN3, IN4 端子は、GND に接続することを推奨します。

#### 7.5.3.3. 電流経路の定義

H-bridge mode 時、TB9103FTG で使用する外部 n型 MOSFET の電流経路を図 14 のように定義しま

赤色の実線は Forward drive 中の電流経路を示し、青色の実線は Reverse drive 中の電流経路を示しま す。

また、点線は Forward drive 中の回生電流の経路を示し、2 点鎖線は Reverse drive 中の回生電流の経 路を示します。

図 14 電流経路定義

#### 7.5.3.4. 駆動制御フローチャート

H-bridge mode におけるブリッジ駆動制御フローチャートを図 **15** に示します。 また、図 **15** に記載していない駆動制御の組み合わせを、図 **16** に示します。

図 15 H-bridge フローチャート1

図 16 H-bridge フローチャート2 その他の駆動制御組み合わせ

#### 7.6. 異常検出機能

TB9103FTG は各種異常検出機能を有します。本章ではその説明を行いますが、VCC 低電圧検出(7.1 章)、VB 低電圧検出(7.2 章)、チャージポンプ高電圧検出回路(7.3.2 章)、モード設定端子オープン検出回 路(7.5.1.1 章)、VDS 検出しきい値設定端子オープン検出回路(7.6.5.1 章)、および過熱検出(7.6.6 章)につ いては各章をご確認ください。

#### 7.6.1. 異常検出機能の種類と、対応動作

TB9103FTG は、表 8 に示す異常状態を検出する機能、ゲートドライブをシャットダウンする機能、 表 9 に示す異常状態に応じた DIAG 1. DIAG2 端子への出力機能を備えています。

異常検出は、同時に複数発生することもあり得ます。

また、ゲートをドライブ中に異常を検出してシャットダウンすると、シャットダウンしたことでゲート 駆動異常判定も同時に発生することもあります。

DIAG1, DIAG2 端子への出力は、異常状態に優先順位を付け、最優先の異常状態に対応した出力を行 います。(表 9)

### 表8 検出機能と対応する動作

| No. | 検出機能                                     | ゲートドライブ出力(VGS),                                                                             | 解除条件                                                                                                                             |

|-----|------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|     |                                          | チャージポンプ動作状態                                                                                 |                                                                                                                                  |

| 1   | CH1(HS1, LS1)<br>IDS 過電流判定<br>(DS 間電圧監視) | Half-bridge mode<br>時:GH1=GL1=Low<br>H-bridge mode 時:<br>GH1=GL1=GH2=GL2=Low<br>チャージポンプ=動作  | Half-bridge mode 時:IN1, IN2 端子を他から Low へ変化<br>H-bridge mode 時:IN1, IN2 端子を他から Low へ変化                                            |

| 2   | CH1(HS1, LS1)<br>ゲート駆動異常判定<br>(GS 間電圧監視) | Half-bridge mode<br>時:GH1=GL1=Low<br>H-bridge mode 時:<br>GH1=GL1=GH2=GL2=Low<br>チャージポンプ=動作  | Half-bridge mode 時:IN1, IN2 端子を他から Low へ変化<br>H-bridge mode 時:IN1, IN2 端子を他から Low へ変化                                            |

| 3   | CH2(HS2, LS2)<br>IDS 過電流判定<br>(DS 間電圧監視) | Half-bridge mode 時:<br>GH2=GL2=Low<br>H-bridge mode 時:<br>GH1=GL1=GH2=GL2=Low<br>チャージポンプ=動作 | Half-bridge mode 時:IN3, IN4 端子を他から Low へ変化<br>H-bridge mode 時:IN1, IN2 端子を他から Low へ変化                                            |

| 4   | CH2(HS2, LS2)<br>ゲート駆動異常判定<br>(GS 間電圧監視) | Half-bridge mode<br>時:GH2=GL2=Low<br>H-bridge mode 時:<br>GH1=GL1=GH2=GL2=Low<br>チャージポンプ=動作  | Half-bridge mode 時:IN3, IN4 端子を他から Low へ変化<br>H-bridge mode 時:IN1, IN2 端子を他から Low へ変化                                            |

| 5   | MODE 端子オープン                              | GH1=GL1=GH2=GL2=Low<br>チャージポンプ=動作                                                           | nSLEEP=High かつ VCC によるリセット解除を満たした時、解消されていると復帰                                                                                    |

| 6   | VDS 端子オープン                               | GH1=GL1=GH2=GL2=Low<br>チャージポンプ=動作                                                           | 解消されると復帰                                                                                                                         |

| 7   | 過熱検出                                     | GH1=GL1=GH2=GL2=Low<br>チャージポンプ=停止                                                           | チャージポンプは解消され次第、復帰 注 2, 注 3<br>Half-bridge mode 時:IN1, IN2, IN3, IN4 端子を他から Low<br>へ変化<br>H-bridge mode 時:IN1, IN2 端子を他から Low へ変化 |

| 8   | VB 低電圧検出                                 | GH1=GL1=GH2=GL2=Low<br>チャージポンプ=停止                                                           | チャージポンプは解消され次第、復帰 注 2, 注 3<br>Half-bridge mode 時:IN1, IN2, IN3, IN4 端子を他から Low<br>へ変化<br>H-bridge mode 時:IN1, IN2 端子を他から Low へ変化 |

| 9   | VCC 低電圧検出                                | GH1=GL1=GH2=GL2=RL<br>チャージポンプ=停止                                                            | 低電圧が解消されると復帰<br>注 1                                                                                                              |

| 10  | VCP 高電圧検出                                | GH1=GL1=GH2=GL2=Low<br>チャージポンプ=停止                                                           | チャージポンプは解消され次第、復帰 注 2, 注 3<br>Half-bridge mode 時:IN1, IN2, IN3, IN4 端子を他から Low<br>へ変化<br>H-bridge mode 時:IN1, IN2 端子を他から Low へ変化 |

| 11  | 未検出時                                     | 正常動作                                                                                        | _                                                                                                                                |

記号の説明:

RL: ゲート・ソース間のシャント抵抗を介した Low

- 注 1: VCC 低電圧を検出すると、TB9103FTG 内はリセット状態となります。

- 注 2: 解除動作を行っても検出状態が続いていれば、全ゲートドライブは Low、チャージポンプは停止 状態になります。

- 注 3: IN1, IN2, IN3, IN4 端子による解除動作を行い解除が完了しても、ゲートドライブを再開するに はtWAKE 期間待つ必要があります。

### 表 9 検出内容と DIAG1, DIAG2 端子

| No. | 検出した内容                               | DIAG 出力 | DIAG1 端子 | DIAG2 端子 | 備考            |

|-----|--------------------------------------|---------|----------|----------|---------------|

|     |                                      | 優先度     | 出力       | 出力       |               |

| 5   | MODE 端子オープン                          | High    | Low      | Low      | CH 共通の異常を検出した |

| 6   | VDS 端子オープン                           | High    | Low      | Low      | CH 共通の異常を検出した |

| 7   | 過熱検出                                 | High    | Low      | Low      | CH 共通の異常を検出した |

| 8   | VB 低電圧検出                             | High    | Low      | Low      | CH 共通の異常を検出した |

| 9   | VCC 低電圧検出                            | High    | Low      | Low      | CH 共通の異常を検出した |

| 10  | VCP 高電圧検出                            | High    | Low      | Low      | CH 共通の異常を検出した |

| 1   | CH1(HS1, LS1)<br>IDS 過電流判定(DS 間電圧監視) | Middle  | Low      | High     | CH1 で異常を検出した  |

| 2   | CH1(HS1, LS1)<br>ゲート駆動異常判定(GS 間電圧監視) | Middle  | Low      | High     | CH1 で異常を検出した  |

| 3   | CH2(HS2, LS2)<br>IDS 過電流判定(DS 間電圧監視) | Low     | High     | Low      | CH2 で異常を検出した  |

| 4   | CH2(HS2, LS2)<br>ゲート駆動異常判定(GS 間電圧監視) | Low     | High     | Low      | CH2 で異常を検出した  |

| 11  | 未検出時                                 | _       | High     | High     | _             |

注: DIAG 出力優先度は、異常事象が複数発生しているとき、DIAG1, DIAG2 に表示する状態を決定します。

### 7.6.2. DIAG1, DIAG2 端子

DIAG1, DIAG2 端子はオープンドレイン出力となっており、外付け抵抗を介して電源(VCC)に接続 する必要があります。プルアップ先は、DIAG 信号を入力して判定などに用いる回路(MCU等)の電源 端子に接続してください。

図 17 DIAG1, DIAG2 端子

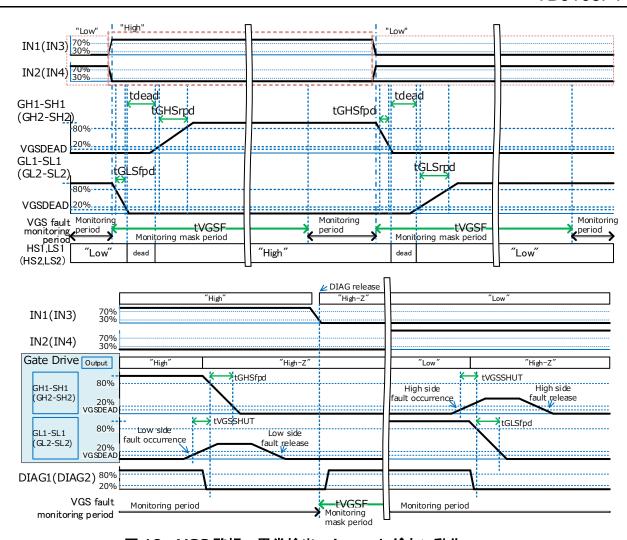

### 7.6.3. VGS 監視、ゲートドライバ異常検出、シャットダウン動作

TB9103FTG は、IN1, IN2, IN3, IN4 端子による駆動の指示と、GH1, GH2, GL1, GL2 端子の状態が 一致しているかの監視をデッドタイム制御の一部回路を流用して行います。駆動の指示が変更された際 は、変更されてから tVGSF 経つまでの間は判定をしません。tVGSF 時間以外において、表 5、表 6、表 7と異なる状態であった場合、ゲートドライバ異常と判定します。

ゲートドライバ異常と判定すると、DIAG1, DIAG2 端子を表 9-No.2, 4 の状態にし、Half-bridge mode 時は異常判定されたチャンネルの全外部 FET を Off(シャットダウン)にします。H-bridge mode 時は、全 外部 FET を Off(シャットダウン)にします。

一度ゲートドライバ異常と判定して外部 FET を Off にした後動作を復帰させるには、Half-bridge mode 時は異常判定されたチャンネルの INx 端子を全て Low にします。H-bridge mode 時は IN1, IN2 端子を Low にします。

注: INx = IN1, IN2, IN3, IN4

図18 VGS監視、異常検出回路 ブロックダイアグラム

図 19 VGS 監視、異常検出、シャットダウン動作

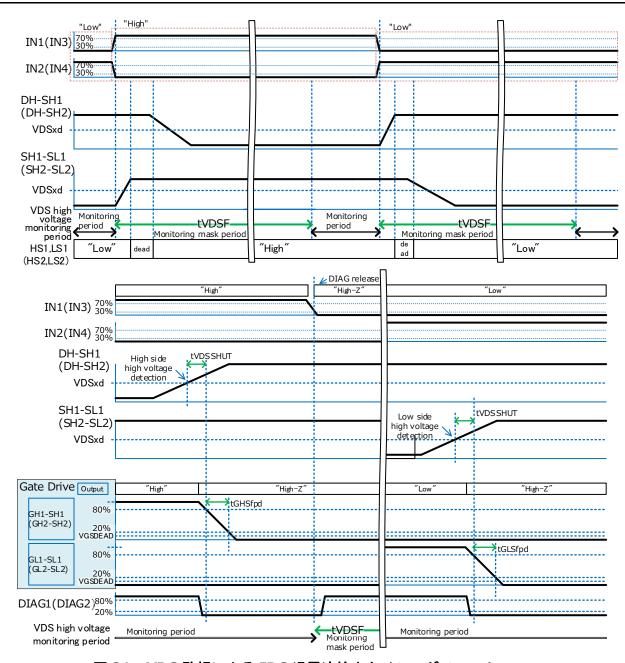

### 7.6.4. VDS 監視、IDS 過電流検出、シャットダウン動作

外部 FET との接続概念を図 20 に示します。

TB9103FTG は、外部 FET のゲートが駆動されている期間ドレイン、ソース間電圧 VDS が設定した 電圧 HS Vref, LS Vref より低いかを、監視します。

駆動の指示が変更された際は、変更されてから tVDSF 経つまでの間は監視をしません。tVDSF 時間 以外において、外部 FET のゲートがオンに駆動されている期間 VDS が設定電圧 HS\_Vref, LS\_Vref より も高いと過電流と判定します。

過電流と判定すると、DIAG 端子を表 9-No.1, 3 の状態にし、Half-bridge mode 時は異常判定されたチ ャンネルの全外部 FET の駆動を Off(シャットダウン)にします。H-bridge mode 時は、全外部 FET の駆 動を Off(シャットダウン)にします。

一度、過電流と判定して外部 FET を Off(シャットダウン)にした後、動作を復帰させるには、Halfbridge mode 時は異常判定されたチャンネルの INx 端子を全て Low にします。H-bridge mode 時は IN1, IN2 端子を Low にします。

注: INx = IN1, IN2, IN3, IN4

図 20 VDS 監視による IDS 過電流検出ブロックダイアグラム

図 21 VDS 監視による IDS 過電流検出タイミングチャート

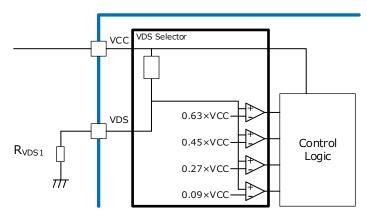

#### 7.6.5. VDS 検出しきい値電圧の設定

VDS 検出に用いるハイサイドしきい値電圧 "HS Vref" とローサイドしきい値電圧 "LS Vref" は、 VDS 端子に加える電圧により設定できます。また、VDS 監視を無効にする機能も有します。

この設定は外付けの抵抗で選択されますが、VCC の消費電流を極力小さくするため比較的高い抵抗値 とする必要があります。

図 22 VDS 端子 インターフェース回路

注: 上図は、IC について、機能・動作の説明をするため、一部省略、簡略化しています。

| R <sub>VDS1</sub> の例<br>R <sub>VDS1</sub> | - VDS 端子電圧 | VDS しきい値電圧設定<br>(HS_Vref, LS_Vref) |  |  |

|-------------------------------------------|------------|------------------------------------|--|--|

| オープン                                      | VDS4dset   | エラー                                |  |  |

| 270kΩ ±10%                                | VDS3dset   | VDS3d                              |  |  |

| 130kΩ ±10%                                | VDS2dset   | VDS2d                              |  |  |

| 51kΩ ±10%                                 | VDS1dset   | VDS1d                              |  |  |

| ≦1kΩ ±10%                                 | VDS0dset   | VDS 検出 Disable                     |  |  |

表 10 VDS しきい値電圧設定

#### 7.6.5.1. VDS 検出しきい値設定端子オープン検出回路

TB9103FTG は VDS 端子オープンを検出し全外部 FET を Off (シャットダウン) にし DIAG1, DIAG2 端子にエラー出力します。エラー出力の解除は解消され次第自動復帰します。

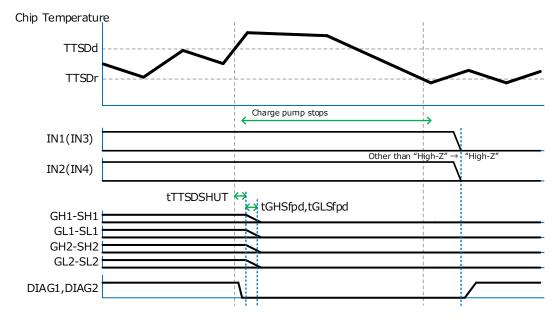

### 7.6.6. 過熱シャットダウン

過熱検出センサーは、チップの温度を監視し、温度上昇を検出します。

制御ロジック回路は、チップが過熱検出温度 TTSDd を超えると、チャージポンプ回路を停止し、全外部 FET のゲート駆動を Off (シャットダウン) にし、DIAG1, DIAG2 端子にエラー出力します。

その後チップの温度が解除しきい値温度 TTSDr よりも低くなると、チャージポンプの動作を開始させます。

ゲートドライブを再開させるには、Half-bridge モード時は、IN1, IN2, IN3, IN4 端子を全て Low に、H-bridge モード時は、IN1, IN2 端子を Low(High-Z の指示)にします。するとシャットダウンを解除し、DIAG1, DIAG2 端子を正常に戻し、tWAKE 時間後通常動作を開始することができます。

図23 過熱検出 タイミングチャート

### 8. 製品仕様・定格

### 8.1. 絶対最大定格

特に指定がない場合、 $Ta=-40\sim125$ ° C,電圧は GND を基準とし、電流は端子に流れ込む方向を正と します。

| 番号     | 項目                        | 記号       | 測定条件                | 定格                   | 単位 |

|--------|---------------------------|----------|---------------------|----------------------|----|

| 8.1.1  | 電源電圧 1                    | \ /le    |                     | -0.3 ~ Vcp+0.3 (≦18) | V  |

| 8.1.2  | VB                        | Vb       | ≤1sec               | ~ Vcp+0.3 (≦40)      | V  |

| 8.1.3  | 電源電圧 2<br>VCC             | Vcc      |                     | -0.3 ~ 6             | V  |

| 8.1.4  | チャージポンプ電圧 1               | Van 1    |                     | -0.3 ~ Vb+0.3 (≦36)  | V  |

| 8.1.5  | CPD                       | Vcp1     | ≤1sec               | ~ Vb+0.3 (≦40)       | V  |

| 8.1.6  | チャージポンプ電圧 2               | V0       |                     | -0.3 ~ Vcp+0.3 (≦36) | V  |

| 8.1.7  | CP                        | Vcp2     | ≤1sec               | ~ Vcp+0.3 (≦40)      | V  |

| 8.1.8  | チャージポンプ電圧 3               | V2       |                     | -0.3 ~ 36            | V  |

| 8.1.9  | VCP                       | Vcp3     | ≤1sec               | ~ 40                 | V  |

| 8.1.10 | ハイサイドゲート端子電圧<br>GH1, GH2  | Vgh      |                     | -0.3 ~ Vcp+0.3 (≦40) | V  |

| 8.1.11 | ローサイドゲート端子電圧<br>GL1, GL2  | Vgl      |                     | -0.3 ~ Vb+0.3 (≦40)  | V  |

| 8.1.12 | ハイサイドドレイン端子電圧<br>DH       | Vdh      |                     | -0.3 ~ Vcp+0.3 (≦40) | V  |

| 8.1.13 | ハイサイドソース端子電圧              | ) / - I- |                     | -0.3 ~ Vcp+0.3 (≦40) | V  |

| 8.1.14 | SH1, SH2                  | Vsh      | ≤0.1msec            | -2 ~                 | V  |

| 8.1.15 | ローサイドソース端子電圧              | Val      |                     | -0.3 ~ Vb+0.3 (≦40)  | V  |

| 8.1.16 | SL1, SL2                  | VsI      | ≤0.1msec            | -2 ~                 | V  |

| 8.1.17 | 端子電圧 nSLEEP               | Vin1     |                     | -0.3 ~ 6             | V  |

| 8.1.18 | 端子電圧 IN1, IN2, IN3, IN4   | Vin2     |                     | -0.3 ~ Vcc+0.3 (≦6)  | V  |

| 8.1.19 | 端子電圧 MODE                 | Vin3     |                     | -0.3 ~ 40            | V  |

| 8.1.20 | 端子電圧 VDS                  | Vin4     |                     | -0.3 ~ Vb+0.3 (≦40)  | V  |

| 8.1.21 | 端子電圧 DIAG1, DIAG2         | Vod1     |                     | -0.3 ~ 6             | V  |

| 8.1.22 | 端子間差電圧 VB, DH             | Vdif1    | VB-DH               | -2 ~ 2               | V  |

| 8.1.23 | 端子間差電圧 DH, SH1, SH2       | Vdif2    | SH1-DH,<br>SH2-DH   | ~ 2                  | V  |

| 8.1.24 | 端子間差電圧 SH1, SH2, SL1, SL2 | Vdif3    | SL1-SH1,<br>SL2-SH2 | ~ 2                  | V  |

| 8.1.25 | 周囲温度                      | Та       |                     | -40 ~ 125            | °C |

| 8.1.26 | 接合温度                      | Tj       |                     | -40 ~ 150            | °C |

| 8.1.27 | 保存温度                      | Tstg     |                     | -55 ~ 150            | °C |

注: 絶対最大定格は、瞬時たりとも超えてはならない規格です。絶対最大定格を超えると IC の破壊や 劣化や損傷の原因となりIC以外に障害を与えるおそれがあります。

いかなる動作条件においても必ず絶対最大定格を超えないように設計を行ってください。

ご使用に際しては、記載された動作範囲内でご使用ください。

### 8.2. 動作範囲

| 番号    | 項目                | 記号     | 測定条件         | 最小  | 標準 | 最大  | 単位 |

|-------|-------------------|--------|--------------|-----|----|-----|----|

| 8.2.1 | 電源電圧動作範囲 1<br>VB  | VBrng  | VBrng≧VCCrng | 7   | -  | 18  | V  |

| 8.2.2 | 電源電圧動作範囲 2<br>VCC | VCCrng | VBrng≧VCCrng | 4.5 | -  | 5.5 | V  |

| 8.2.3 | 接合温度動作範囲3         | Tjrng  |              | -40 | -  | 150 | °C |

### 8.3. 熱抵抗

| 番号    | 項目  | 記号    | 測定条件 | 最小 | 標準   | 最大 | 単位   |

|-------|-----|-------|------|----|------|----|------|

| 8.3.1 | 熱抵抗 | RthJA | -    | ı  | 39.9 | •  | °C/W |

### 8.4. 電気的特性

特に指定がない場合、VB=7~18V, VCC=4.5~5.5V(VB≥VCC), Ta=-40~125°C とします。 全ての電圧は GND を基準とし、電流は端子に流れ込む方向を正とします。

### 8.4.1. 電源

| 番号      | 項目                      | 記号      | 測定条件                                                                                                      |   | 標準 | 最大  | 単位 |

|---------|-------------------------|---------|-----------------------------------------------------------------------------------------------------------|---|----|-----|----|

| 8.4.1.1 | 動作電源電流<br>VB            | IVB     | nSLEEP=High,<br>無負荷(外部 FET 不接続),<br>Rcp=10Ω, Ccp=0.1μF, Cvcp=2.2μF                                        | - | -  | 10  | mA |

| 8.4.1.2 | 動作電源電流<br>VCC           | IVCC    | nSLEEP=High                                                                                               | - | -  | 2.5 | mA |

| 8.4.1.3 | スリープモード時<br>電源電流<br>VB  | ISLEEP1 | nSLEEP=Low, Ta=25°C                                                                                       | - | -  | 14  | μΑ |

| 8.4.1.4 | スリープモード時<br>電源電流<br>VCC | ISLEEP2 | nSLEEP=Low, Ta=25°C                                                                                       | - | -  | 14  | μΑ |

| 8.4.1.5 | スリープモード<br>への移行時間       | tSLEEP  | VB=7V 時 nSLEEP 端子 High→Low から GL1,<br>GL2 端子 VB×0.9 まで 図 12, 図 15 参照                                      | - | -  | 15  | μs |

| 8.4.1.6 | スリープモード<br>からの復帰時間      | tWAKE   | nSLEEP 端子 Low→High から VCP=VB+2.25V<br>まで<br>IVCP=-10mA, Rcp=10Ω, Ccp=0.1 μ F,<br>Cvcp=2.2μF 図 12, 図 15 参照 | - | -  | 0.5 | ms |

### 8.4.2. チャージポンプ

| 番号      | 項目                                 | 記号         | 測定条件                                                                                  | 最小    | 標準     | 最大    | 単位  |

|---------|------------------------------------|------------|---------------------------------------------------------------------------------------|-------|--------|-------|-----|

| 8.4.2.1 | チャージポンプ<br>電圧                      | VCP1       | VB=7V~18V, IVCP=-2mA<br>GH1, GL1, GH2, GL2 は無負荷<br>Rcp=10Ω, Ccp=0.1 μ F<br>Cvcp=2.2μF | VB+ 5 | VB+1 1 | VB+14 | V   |

| 8.4.2.2 | チャージポンプ<br>スイッチング<br>周波数           | fCP        |                                                                                       | 100   | 200    | 400   | kHz |

| 8.4.2.3 | チャージポンプ<br>クランプ電圧                  | VCPCL1d    | 図 5, 図 6 参照                                                                           | VB+10 | VB+11  | VB+14 | V   |

| 8.4.2.4 | チャージポンプ<br>クランプ電圧                  | VCPCL2d    | 図 5 参照                                                                                | 33    | 36     | 39    | V   |

| 8.4.2.5 | チャージポンプ<br>高電圧検出                   | VCPOVd     | 図 5, 図 6 参照                                                                           | VB+15 | VB+16  | VB+18 | V   |

| 8.4.2.6 | チャージポンプ<br>高電圧検出,<br>シャットダウン<br>時間 | tVCPOVSHUT | 無負荷<br>VCPOVd <vcp vgs="80%&lt;br" →="">図 6 参照</vcp>                                  | -     | -      | 15    | μs  |

| 8.4.2.7 | チャージポンプ<br>放電電流                    | IVCPDIS    | VB=18V, VCP=32V                                                                       | 10    | 70     | 200   | mA  |

### 8.4.3. 制御入出力

| 番号       | 項目                                              | 記号       | 測定条件               | 最小      |    | 最大      | 単位 |

|----------|-------------------------------------------------|----------|--------------------|---------|----|---------|----|

| 8.4.3.1  | ローレベル<br>入力電圧<br>nSLEEP, IN1,<br>IN2, IN3, IN4  | VIL      |                    | -       | -  | 0.3×VCC | V  |

| 8.4.3.2  | ハイレベル<br>入力電圧<br>nSLEEP, IN1,<br>IN2, IN3, IN4  | VIH      |                    | 0.7×VCC | -  | -       | V  |

| 8.4.3.3  | 入力電圧<br>ヒステリシス<br>nSLEEP, IN1,<br>IN2, IN3, IN4 | VIHYS    |                    | 0.1     | -  | -       | V  |

| 8.4.3.4  | ローレベル<br>入力電流<br>nSLEEP, IN1,<br>IN2, IN3, IN4  | IIL      | VCC=5.0V, VIN=0V   | -5      | -  | 5       | μΑ |

| 8.4.3.5  | ハイレベル<br>入力電流<br>nSLEEP, IN1,<br>IN2, IN3, IN4  | IIH      | VCC=5.0V, VIN=5.0V | 25      | 50 | 100     | μΑ |

| 8.4.3.6  | MODE 端子                                         | MODE2set | Half-bridge mode   | 0.7×VCC | -  | -       | V  |

| 8.4.3.7  | 設定電圧                                            | MODE1set | H-bridge mode      | -       | -  | 0.3×VCC | V  |

| 8.4.3.8  | MODE 端子                                         | IMODE2   | 表 4 参照             | 1.5     | 8  | 20      | μΑ |

| 8.4.3.9  | 設定電流                                            | IMODE1   | 表 4 参照             | -20     | -8 | -1.5    | μΑ |

| 8.4.3.10 | DIAG<br>High-Z<br>出力電流                          | IDIAGOFF | DIAG1=DIAG2=VCC    | -       | -  | 10      | μΑ |

| 8.4.3.11 | DIAG<br>ローレベル<br>出力電圧                           | VDIAGLO  | IDIAGLO=1mA        | -       | -  | 0.5     | V  |

### 8.4.4. FET ゲートドライバ

| 番号       | 項目                            | 記号        | 測定条件                                               | 最小                 | 標準  | 最大     | 単位 |

|----------|-------------------------------|-----------|----------------------------------------------------|--------------------|-----|--------|----|

| 8.4.4.1  | ハイサイド GS 間                    | VGSHSSRC1 | VB=7~18V<br>SH1=SH2=VB, 無負荷<br>GH1-SH1, GH2-SH2    | VCP-<br>VB<br>-0.2 | -   | VCP-VB | V  |

| 8.4.4.2  | - 駆動電圧                        | VGSHSSNK1 | SH1=SH2=VB, 無負荷<br>GH1-SH1, GH2-SH2                | -                  | -   | 0.5    | V  |

| 8.4.4.3  |                               | VGSLSSRC1 | VB=9~18V<br>SL1=SL2=GND, 無負荷<br>GL1-SL1, GL2-SL2   | 8.9                | 11  | 14     | V  |

| 8.4.4.4  | ローサイド GS 間<br>駆動電圧            | VGSLSSRC2 | VB=7~9V<br>SL1=SL2=GND, 無負荷<br>GL1-SL1, GL2-SL2    | VB-0.1             | -   | VB     | V  |

| 8.4.4.5  |                               | VGSLSSNK1 | SL1=SL2=GND, 無負荷<br>GL1-SL1, GL2-SL2               | -                  | -   | 0.5    | V  |

| 8.4.4.6  | ハイサイド GS 間<br>駆動出力抵抗<br>ソース方向 | Ronhssrc  | SH1=SH2=VB, IGLOAD=-1mA<br>GH1-SH1, GH2-SH2        | 250                | 500 | 1000   | Ω  |

| 8.4.4.7  | ハイサイド GS 間<br>駆動出力抵抗<br>シンク方向 | Ronhssnk  | SH1=SH2=VB, IGLOAD=1mA<br>GH1-SH1, GH2-SH2         | 20                 | 50  | 150    | Ω  |

| 8.4.4.8  | ローサイド GS 間<br>駆動出力抵抗<br>ソース方向 | Ronlssrc  | SL1=SL2=GND, IGLOAD=-1mA<br>GL1-SL1, GL2-SL2       | 250                | 500 | 1000   | Ω  |

| 8.4.4.9  | ローサイド GS 間<br>駆動出力抵抗<br>シンク方向 | Ronlssnk  | SL1=SL2=GND, IGLOAD=1mA<br>GL1-SL1, GL2-SL2        | 20                 | 50  | 150    | Ω  |

| 8.4.4.10 | ハイサイド<br>ターンオン時間              | tGHSrpd   | SH1=SH2=VB, RI=10Ω, CI=10nF<br>図 19 参照             | 1                  | 8   | 20     | μs |

| 8.4.4.11 | ハイサイド<br>ターンオフ時間              | tGHSfpd   | SH1=SH2=VB, RI=10Ω, CI=10nF<br>図 19 参照             | 0.1                | 0.8 | 5      | μs |

| 8.4.4.12 | ローサイド<br>ターンオン時間              | tGLSrpd   | SL1=SL2=GND, RI=10Ω, CI=10nF<br>図 19 参照            | 1                  | 8   | 20     | μs |

| 8.4.4.13 | ローサイド<br>ターンオフ時間              | tGLSfpd   | SL1=SL2=GND, RI=10Ω, CI=10nF<br>図 19 参照            | 0.1                | 0.8 | 5      | μs |

| 8.4.4.14 | 入力伝搬遅延時間                      | tGHSp1    | SL1=SL2=GND, RI=10Ω, CI=10nF<br>図 12 参照            | 0.1                | 0.5 | 2      | μs |

| 8.4.4.15 | 入力伝搬遅延時間                      | tGLSp1    | SL1=SL2=GND, RI=10Ω, CI=10nF<br>図 12 参照            | 0.1                | 0.5 | 2      | μs |

| 8.4.4.16 | 最小デッドタイム                      | tdead     | SH1=SH2=VB, SL1=SL2=GND<br>RI=10Ω, CI=10nF 図 19 参照 | 0.5                | 1.5 | 6      | μs |

| 8.4.4.17 | デッドタイム判定用<br>VGS 電圧           | VGSDEAD   | 図 19 参照                                            | 0.6                | 1.5 | 1.8    | V  |

| 8.4.4.18 | ハイサイド<br>ホールドオフ抵抗             | RHSOFF    | ゲート・ソース間のシャント抵抗<br>SH1=SH2=GND                     | 75                 | 150 | 300    | kΩ |

| 8.4.4.19 | ローサイド<br>ホールドオフ抵抗             | RLSOFF    | ゲート・ソース間のシャント抵抗                                    | 75                 | 150 | 300    | kΩ |

# **Preliminary**

### 8.4.5. 状態検出

| 番号       | 項目                           | 記号         | 測定条件                                                           | 最小            | 標準  | 最大            | 単位 |

|----------|------------------------------|------------|----------------------------------------------------------------|---------------|-----|---------------|----|

| 8.4.5.1  |                              | VCCLOd     | VCC 低下 検出                                                      | 3.9           | -   | 4.3           | V  |

| 8.4.5.2  | ┤VCC 低電圧検出<br>│              | VCCLOr     | VCC 上昇 解除                                                      | 4.0           | -   | 4.5           | V  |

| 8.4.5.3  | VCC 低電圧検出ヒステリシス              | VCCLOHYS   | VCCLOd < VCCLOr                                                | 0.1           | -   | -             | V  |

| 8.4.5.4  | VCC 低電圧検出<br>フィルタ時間          | tVCCLO     | 図3参照                                                           | 3             | 4   | 12            | μs |

| 8.4.5.5  | VCC 低電圧検出<br>シャットダウン<br>時間   | tVCCLOSHUT | 無負荷<br>VCC <vcclod →<br="">VGS=80% 図3参照</vcclod>               | 3             | 10  | 25            | μs |

| 8.4.5.6  |                              | VBLOd      | VB 低下 検出                                                       | 5.1           | -   | 5.7           | V  |

| 8.4.5.7  | ·VB 低電圧検出                    | VBLOr      | VB 上昇 解除                                                       | 5.2           | -   | 6.0           | V  |

| 8.4.5.8  | VB 低電圧検出<br>ヒステリシス           | VBLOHYS    | VBLOd < VBLOr                                                  | 0.1           | -   | -             | V  |

| 8.4.5.9  | VB 低電圧検出<br>シャットダウン<br>時間    | tVBLOSHUT  | 無負荷<br>VB <vblod vgs="80%&lt;br" →="">図 4 参照</vblod>           | -             | -   | 15            | μs |

| 8.4.5.10 | VGS ゲート駆動<br>異常検出マスク<br>時間   | tVGSF      | 図 19 参照                                                        | 134           | 268 | 536           | μs |

| 8.4.5.11 | VGS ゲート駆動<br>異常検出シャットダウン時間   | tVGSSHUT   | 無負荷<br>異常状態 → VGS=80%<br>図 19 参照                               | -             | -   | 5             | μs |

| 8.4.5.12 |                              | VDS4dset   | ──<br>VDS 検出機能 設定エラー<br>─VDS3d 選択<br>VDS2d 選択<br>─VDS1d 選択     | 0.65 ×<br>VCC | -   | VCC           | V  |

| 8.4.5.13 |                              | VDS3dset   |                                                                | 0.47 ×<br>VCC | -   | 0.61 ×<br>VCC | V  |

| 8.4.5.14 | VDS 検出レベル設定                  | VDS2dset   |                                                                | 0.29 ×<br>VCC | -   | 0.43 ×<br>VCC | V  |

| 8.4.5.15 |                              | VDS1dset   | VDS 検出機能 disable                                               | 0.11 ×<br>VCC | -   | 0.25 ×<br>VCC | V  |

| 8.4.5.16 |                              | VDS0dset   |                                                                | 0             | -   | 0.07 ×<br>VCC | V  |

| 8.4.5.17 | VDS 端子<br>入力電流               | IVDS       |                                                                | -38           | -28 | 0.1           | μΑ |

| 8.4.5.18 | VDS 検出レベル設定<br>シャットダウン<br>時間 | tVDS4dSHUT | 無負荷<br>VDS 端子=VDS4dset →<br>VGS=80%                            | -             | -   | 5             | μs |

| 8.4.5.19 |                              | VDS3d      |                                                                | 0.76          | 0.9 | 1.04          | V  |

| 8.4.5.20 | VDS 検出レベル                    | VDS2d      |                                                                | 0.51          | 0.6 | 0.69          | V  |

| 8.4.5.21 |                              | VDS1d      |                                                                | 0.25          | 0.3 | 0.35          | V  |

| 8.4.5.22 | VDS 検出マスク時間                  | tVDSF      | 図 21 参照                                                        | 134           | 268 | 536           | μs |

| 8.4.5.23 | VDS 高電圧検出<br>シャットダウン<br>時間   | tVDSSHUT   | 無負荷<br>VDSxd <vds vgs="80%&lt;br" →="">図 21 参照 x=1, 2, 3</vds> | 3             | 10  | 25            | μs |

| 8.4.5.24 | 過熱シャットダウン                    | TTSDd      | 検出                                                             | 155           | 175 | 195           | °C |

| 8.4.5.25 | 検出温度                         | TTSDr      | 解除                                                             | 110           | 130 | 150           | °C |

| 8.4.5.26 | 過熱検出<br>シャットダウン<br>時間        | tTTSDSHUT  | 無負荷<br>TTSDd <tj vgs="80%&lt;br" →="">図 23 参照</tj>             | -             | -   | 15            | μs |

注: TSD 規格は設計上のものであり、出荷テストは行われていません。 過熱シャットダウン回路は、異常状態を一時的に回避するためのものです。 これは、ICの損傷を防ぐことを保証するものではありません。

### 8.5. 測定回路

図 24 ゲート駆動部の測定

### 9. 応用回路例

以下に示す情報は本デバイスの実装ガイドとしてのみに使われるものであり、機能動作や性能を保証し たものではありません。

### 9.1. 応用回路の例

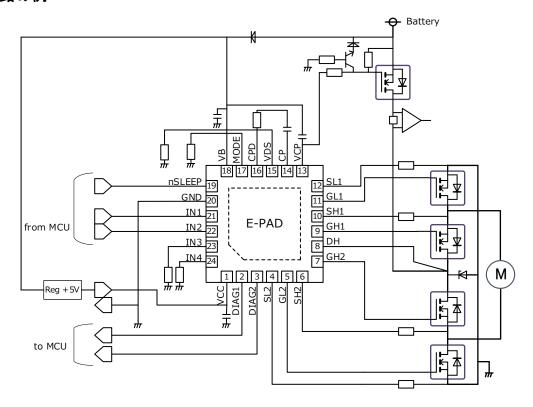

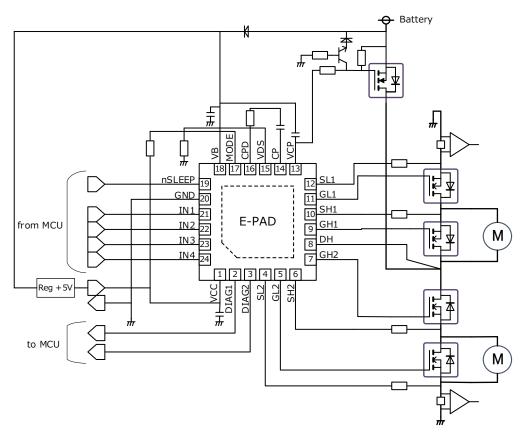

### 図 25 TB9103FTG H-bridge mode 応用回路例

注: 本図面はあくまでアプリケーションの1例であり、実使用時には十分な機能評価をして頂く必要が あります。

図 26 TB9103FTG Half-bridge mode 応用回路例

注: 本図面はあくまでアプリケーションの1例であり、実使用時には十分な機能評価をして頂く必要が あります。

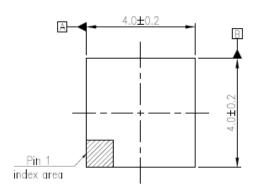

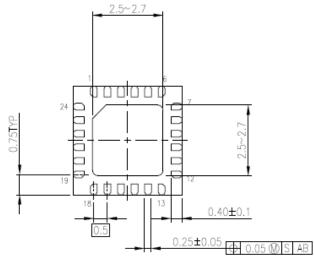

### 10. 外形図

### 10.1. 外形寸法図

Package dimensions

P-VQFN24-0404-0.50-003

"Unit:mm"

図 27 パッケージ外形図

質量: 0.04g (標準)

注意

本図は説明のための図です。

図に表記されていない寸法等については弊社担当までお問い合わせください。

## 11. 変更履歴

| 日付         | リビジョン | 変更内容の説明 |

|------------|-------|---------|

| 2024-08-21 | 1.0   | 初版      |

|            |       |         |

### 12. 使用上のご注意およびお願い事項

### 12.1. 使用上の注意事項

- (1) 絶対最大定格は複数の定格の、どの1つの値も瞬時たりとも超えてはならない規格です。 複数の定格のいずれに対しても超えることができません。 絶対最大定格を超えると破壊、損傷および劣化の原因となり、破裂・燃焼による傷害を負うこと があります。

- (2) 過電流の発生やIC の故障の場合に大電流が流れ続けないように、適切な電源ヒューズを使用してください。IC は絶対最大定格を超えた使い方、誤った配線、および配線や負荷から誘起される異常パルスノイズなどが原因で破壊することあり、この結果、IC に大電流が流れ続けることで、発煙・発火に至ることがあります。破壊における大電流の流出入を想定し、影響を最小限にするため、ヒューズの容量や溶断時間、挿入回路位置などの適切な設定が必要となります。

### 12.2. 使用上の留意点

(1) 過電流保護回路過電流制限回路

(通常: カレントリミッター回路) はどのような場合でも IC を保護するわけではありません。動作後は、速やかに過電流状態を解除するようお願いします。絶対最大定格を超えた場合など、ご使用方法や状況により、過電流制限回路が正常に動作しなかったり、動作する前に IC が破壊したりすることがあります。また、動作後、長時間過電流が流れ続けた場合、ご使用方法や状況によっては、IC が発熱などにより破壊することがあります。

(2) 熱遮断回路

熱遮断回路 (通常: サーマルシャットダウン回路) は、どのような場合でも IC を保護するわけではありません。動作後は、速やかに発熱状態を解除するようお願いします。絶対最大定格を超えて使用した場合など、ご使用法や状況により、熱遮断回路が正常に動作しなかったり、動作する前に IC が破壊したりすることがあります。

Rev. 1.0

### 製品取り扱い上のお願い

株式会社東芝およびその子会社ならびに関係会社を以下「当社」といいます。 本資料に掲載されているハードウエア、ソフトウエアおよびシステムを以下「本製品」といいます。

- 本製品に関する情報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を得て本 資料を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

- 当社は品質、信頼性の向上に努めていますが、半導体・ストレージ製品は一般に誤作動または故障する場合があります。本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウエア・ソフトウエア・システムに必要な安全設計を行うことをお願いします。なお、設計および使用に際しては、本製品に関する最新の情報(本資料、仕様書、データシート、アプリケーションノート、半導体信頼性ハンドブックなど)および本製品が使用される機器の取扱説明書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

- 本製品は、特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な財産損害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下"特定用途"という)に使用されることは意図されていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇宙機器、医療機器(ヘルスケア除く)、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連機器、昇降機器、発電関連機器などが含まれますが、本資料に個別に記載する用途は除きます。特定用途に使用された場合には、当社は一切の責任を負いません。なお、詳細は当社営業窓口まで、または当社 Web サイトのお問い合わせフォームからお問い合わせください。

- ◆ 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

- ◆ 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用することはできません。

- 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及 び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をしておりません。

- 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あるいは その他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、「米国 輸出管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってくださ い。

- 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず当社営業窓口までお問い合わせください。本製品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査の上、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は一切の責任を負いかねます。

### 東芝デバイス&ストレージ株式会社

https://toshiba.semicon-storage.com/jp/