Photocouplers Infrared LED & Photo IC

# **TLP5222**

### 1. Applications

- Isolated gate drive for IGBT / Power MOSFET

- Industrial Inverters •

- AC Servos •

- Photovoltaic (PV) Inverters •

- Uninterruptible Power Supply (UPS) •

### 2. General

The TLP5222 is a highly integrated and multi-functional gate driver photocoupler with 2.5 A output current housed in a long creepage and clearance SO16L package.

The TLP5222, a smart gate driver photocoupler, includes functions of desaturation detection, isolated FAULT status feedback, soft gate turn-off, active Miller clamp, under voltage lockout (UVLO) and automatic FAULT status reset.

The TLP5222 consists of two infrared light-emitting diodes (LEDs) and two high-gain and high-speed photodetector ICs. They realize high current, high-speed output control and FAULT status feedback with electrical isolation between a primary side and secondary side.

### 3. Features

| (1)  | Dool output our   | ant                      | +                                   |

|------|-------------------|--------------------------|-------------------------------------|

| (1)  | Peak output curr  | ent                      | : ± 2.5 A (max)                     |

| (2)  | Operating tempe   | erature                  | : – 40 to 110 °C                    |

| (3)  | Power supply vo   | ltage                    | : 15 to 30 V                        |

| (4)  | Threshold input   | current                  | : 6 mA (max)                        |

| (5)  | Supply current    |                          | : 5 mA (max)                        |

| (6)  | Propagation dela  | ly time                  | : 250 ns (max)                      |

| (7)  | DESAT leading e   | dge blanking time        | : 1.4 µs (typ.)                     |

| (8)  | DESAT mute tim    | e                        | : 25.5 µs (typ.)                    |

| (9)  | Common-mode       | transient immunity       | : ± 25 kV/µs (min)                  |

| (10) | Isolation voltage |                          | : 5000 Vrms (min)                   |

| (11) | Safety standards  | 5                        |                                     |

|      | UL approved       | : UL1577, File No. E6734 | 9                                   |

|      | cUL approved      | : CSA Component Accept   | ance Service No. 5A File No. E67349 |

|      | VDE approved      | : EN 60747-5-5, EN 6236  | 58-1 (Note 1)                       |

|      | CQC approved      | : GB4943.1, GB8898 Jap   | an Factory                          |

仅适用干海拔 2000m 以下地区安全使用

Note 1: When a VDE approved type is needed, please designate the Option (D4).

Start of commercial production 2022-07

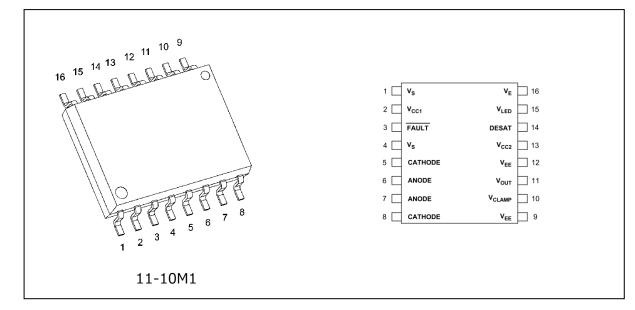

### 4. Packaging and Pin Assignment

### 4.1. Pin Description

| Pin No. | Symbol           | Description                                |

|---------|------------------|--------------------------------------------|

| 1       | Vs               | Input side Ground terminal                 |

| 2       | $V_{CC1}$        | Input side Power Supply terminal           |

| 3       | FAULT            | Fault Output terminal                      |

| 4       | Vs               | Input side Ground terminal                 |

| 5       | CATHODE          | LED Cathode terminal                       |

| 6       | ANODE            | LED Anode terminal                         |

| 7       | ANODE            | LED Anode terminal                         |

| 8       | CATHODE          | LED Cathode terminal                       |

| 9       | $V_{EE}$         | Output side Negative Power Supply terminal |

| 10      | $V_{CLAMP}$      | Miller current Clamp terminal              |

| 11      | V <sub>OUT</sub> | Output terminal                            |

| 12      | $V_{\text{EE}}$  | Output side Negative Power Supply terminal |

| 13      | $V_{CC2}$        | Output side Positive Power Supply terminal |

| 14      | DESAT            | Desaturation monitor terminal              |

| 15      | $V_{LED}$        | Not connect, for testing only              |

| 16      | V <sub>E</sub>   | Common terminal                            |

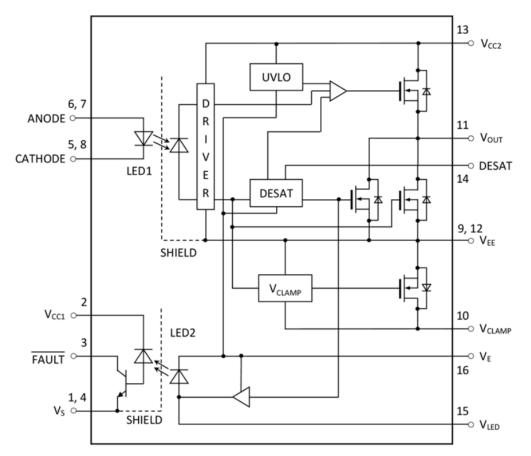

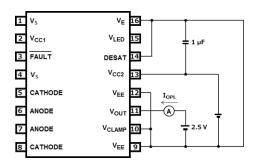

### 5. Internal Circuit (Note)

Note : Bypass capacitors (1  $\mu$ F) must be connected between pin 13 (V<sub>CC2</sub>) and 16 (V<sub>E</sub>) to stabilize the operation of the high gain linear amplifier. When V<sub>E</sub> – V<sub>EE</sub> > 0 V (with negative gate drive), another bypass capacitor (1  $\mu$ F) must be connected between pin 9 or 12 (V<sub>EE</sub>) and 16 (V<sub>E</sub>). Failure to provide the bypassing may impair the switching property. The total lead length between each capacitor and the coupler should not exceed 1 cm.

### 6. Principal of Operation

### 6.1 Truth table

| Input<br>Current<br>(I <sub>F</sub> ) | Output side Positive<br>Power Supply<br>(V <sub>CC2</sub> - V <sub>E</sub> ) | DESAT Monitor<br>(Pin 14 input) | FAULT Output<br>( Pin 3 output ) | Output Voltage<br>( Pin 11 output ) |

|---------------------------------------|------------------------------------------------------------------------------|---------------------------------|----------------------------------|-------------------------------------|

| OFF                                   | $> V_{UVLO}^+$                                                               | Not Active                      | High                             | Low                                 |

| OFF                                   | < V <sub>UVLO</sub> <sup>-</sup>                                             | Not Active                      | High                             | Low                                 |

| ON                                    | $> V_{UVLO}^+$                                                               | Active (< V <sub>DESAT</sub> )  | High                             | High                                |

| ON                                    | $> V_{UVLO}^+$                                                               | Active (> V <sub>DESAT</sub> )  | Low                              | Low                                 |

| ON                                    | < V <sub>UVLO</sub>                                                          | Not Active                      | High                             | Low                                 |

### 6.2. Mechanical Parameters

| Characteristics              | Dimensions  | Unit |

|------------------------------|-------------|------|

| Creepage distances           | 8.0 (min)   |      |

| Clearance distances          | 0.0 (11111) | mm   |

| Internal isolation thickness | 0.4 (min)   |      |

#### 7. Absolute Maximum Ratings (Note) (Unless otherwise specified, Ta = 25 $^{\circ}$ C)

|                          | Characterist                      | ics                       | Symbol                               | Note             | Rating                          | Unit  |

|--------------------------|-----------------------------------|---------------------------|--------------------------------------|------------------|---------------------------------|-------|

| LED &                    | LED Input forward current         |                           | Ι <sub>F</sub>                       |                  | 25                              | mA    |

| FAULT<br>feedback IC     | LED Input forward current der     | rating (Ta ≥ 90 °C)       | ΔI <sub>F</sub> /ΔTa                 |                  | -0.65                           | mA/°C |

| (Controller              | LED Peak transient input forw     | ard current               | I <sub>FPT</sub>                     | Note 1           | 1                               | А     |

| side)                    | LED Reverse input voltage         |                           | V <sub>R</sub>                       |                  | 5                               | V     |

|                          | Input side supply voltage         |                           | V <sub>CC1</sub>                     |                  | -0.5 to 7                       | V     |

|                          | FAULT feedback IC output cur      | rent                      | IFAULT                               |                  | 8                               | mA    |

|                          | FAULT feedback IC output vol      | tage                      | VFAULT                               |                  | -0.5 to V <sub>CC1</sub>        | V     |

|                          | LED power dissipation             |                           | PD                                   | Note 3           | 60                              | mW    |

|                          | LED power dissipation deratin     | g (Ta ≥ 90 °C)            | $\Delta P_D / \Delta Ta$             | Note 3           | -1.9                            | mW/°C |

| Output IC<br>(Gate side) | Peak high level output<br>current | Ta = -40 to 110 °C        | I <sub>OPH</sub>                     | Note 2<br>Note 3 | -2.5                            | А     |

| (oute slac)              | Peak low level output<br>current  | $Ta = -40 \ to \ 110 \ C$ | I <sub>OPL</sub>                     |                  | +2.5                            | А     |

|                          | Output side total supply voltage  | je                        | (V <sub>CC2</sub> -V <sub>EE</sub> ) |                  | -0.5 to 35                      | V     |

|                          | Output side negative supply v     | oltage                    | (V <sub>E</sub> -V <sub>EE</sub> )   |                  | -0.5 to 15                      | V     |

|                          | Output side positive supply vo    | ltage                     | $(V_{CC2}-V_E)$                      |                  | $-0.5$ to $35 - (V_E - V_{EE})$ | V     |

|                          | Output voltage                    |                           | V <sub>OUT</sub>                     |                  | $V_{EE}$ to $V_{CC2}$           | V     |

|                          | Peak Miller clamp sinking curr    | ent                       | I <sub>Clamp</sub>                   |                  | 2.5                             | А     |

|                          | Miller clamp terminal voltage     |                           | V <sub>Clamp</sub>                   |                  | $V_{EE}$ to $V_{CC2}$           | V     |

|                          | DESAT terminal voltage            |                           | V <sub>DESAT</sub>                   |                  | $V_E$ to $V_E$ + 10             | V     |

|                          | Output IC power dissipation       |                           | PO                                   | Note 3           | 600                             | mW    |

|                          | P <sub>O</sub> derating           | (Ta ≥ 90 °C)              | ∆ P <sub>O</sub> /∆Ta                | Note 3           | -13.0                           | mW/°C |

| Common                   | Operating temperature             |                           | Topr                                 |                  | -40 to 110                      | °C    |

|                          | Storage temperature               |                           | T <sub>stg</sub>                     |                  | -55 to 125                      | °C    |

|                          | Lead soldering temperature (1     | .0 s)                     | T <sub>sol</sub>                     | Note 4           | 260                             | °C    |

|                          | Isolation voltage (AC, 60 s, R.   | H. ≤ 60 %)                | BVS                                  | Note 5           | 5000                            | Vrms  |

Note : Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings. Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook ("Handling Precautions"/"Derating Concept and Methods") and individual reliability data (i.e. reliability test report and estimated failure rate, etc.)

- Note 1: Pulse width  $\leq$  1  $\mu s,$  300 pps

- Note 2: Exponential waveform. Pulse width  $\leq$  0.3  $\mu s,\,f\leq$  25 kHz,  $V_{\text{CC2}}$  = 15 to 30 V

- Note 3: Mounting on a substrate designated in accordance with JEDEC JESD51-7.

- Note 4: For the effective lead soldering area.

- Note 5: This device considered a two-terminal device: All pins on the LED & feedback IC side are shorted together, and all pins on the Output IC side are shorted together.

### 8. Recommended Operation Conditions (Note)

| Characteristics                     | Symbol                                | Note             | Min | Max                                      | Unit |

|-------------------------------------|---------------------------------------|------------------|-----|------------------------------------------|------|

| Output side total supply voltage    | (V <sub>CC2</sub> - V <sub>EE</sub> ) | Note 1<br>Note 2 | 15  | 30                                       | V    |

| Output side negative supply voltage | (V <sub>E</sub> - V <sub>EE</sub> )   | Note 1<br>Note 3 | 0   | 15                                       | V    |

| Output side positive supply voltage | (V <sub>CC2</sub> - V <sub>E</sub> )  | Note 1<br>Note 2 | 15  | 30 - (V <sub>E</sub> - V <sub>EE</sub> ) | V    |

| Input side supply voltage           | V <sub>CC1</sub>                      |                  | 2.7 | 5.5                                      | V    |

| LED Input on-state current          | I <sub>F(ON)</sub>                    | Note 4           | 7.5 | 12                                       | mA   |

| LED Input off-state voltage         | V <sub>F(OFF)</sub>                   |                  | 0   | 0.8                                      | V    |

Note: The recommended operating conditions are given as a design guide necessary to obtain the intended performances of the device. Each parameter is an independent value. When creating a system design using this device, the electrical characteristics specified in this datasheet should also be considered.

Note 1: If the rising and falling slopes of  $V_{CC2}$  and  $V_{EE}$  are so steep, the internal circuit operation may not be stable. In that case, please design the slopes to be 0.5 V/µs or less.

Note 2: 15 V is the recommended minimum operating positive supply voltage ( $V_{CC2} - V_E$ ) to ensure adequate margin in excess of the maximum  $V_{UVLO+}$  threshold of 12.5V.

Note 3: This supply is optional. Required only when negative gate drive is implemented.

Note 4: The rise and fall times of the input on-current should be less than 500  $\mu s.$

#### 9. Electrical Characteristics (Note) (Unless otherwise specified, Ta = - 40 to 110 °C, $V_{CC2}$ - $V_{EE}$ = 15 to 30 V, $V_E$ - $V_{EE}$ = 0 V)

| Characteristics                                     | Symbol                         | Note   | Test<br>Circuit | Test Conditions                                                             | Min                       | Тур.                      | Max   | Unit |

|-----------------------------------------------------|--------------------------------|--------|-----------------|-----------------------------------------------------------------------------|---------------------------|---------------------------|-------|------|

| Input forward voltage                               | V <sub>F</sub>                 |        | onour           | I <sub>F</sub> = 10 mA, Ta = 25 ℃                                           | 1.48                      | 1.67                      | 1.93  | V    |

| Input reverse current                               | I <sub>R</sub>                 |        |                 | V <sub>R</sub> = 5 V, Ta = 25 ℃                                             | -                         | -                         | 10    | μA   |

| Input capacitance<br>(between Anode and<br>Cathode) | Ct                             |        |                 | V = 0 V, f = 1 MHz, Ta = 25 ℃                                               | -                         | 20                        | _     | pF   |

| FAULT low level output                              |                                |        |                 | $I_{FAULT} = 1.1 \text{ mA}, V_{CC1} = 5.5 \text{ V}$                       | -                         | 0.27                      | 0.4   |      |

| voltage                                             | Vfaultl                        |        |                 | $I_{FAULT} = 1.1 \text{ mA}, V_{CC1} = 2.7 \text{ V}$                       | -                         | 0.27                      | 0.4   | V    |

| FAULT high level output                             | Ifaulth                        |        |                 | $V_{\overline{FAULT}} = V_{CC1} = 5.5 \text{ V}, \text{ Ta} = 25 ^{\circ}C$ | -                         | -                         | 0.5   |      |

| current                                             | IFAULTH                        |        |                 | $V_{FAULT} = V_{CC1} = 2.7 \text{ V}, \text{ Ta} = 25 ^{\circ}C$            | -                         | -                         | 0.3   | μA   |

| Peak high level output<br>current                   | I <sub>OPH</sub>               | Note 1 | 13.1.1          | I <sub>F</sub> = 10 mA, V <sub>OUT</sub> = V <sub>CC2</sub> - 4 V           | -                         | -2.9                      | -2.0  |      |

| Peak low level output<br>current                    | I <sub>OPL</sub>               | Note 1 | 13.1.2          | $V_{OUT} = V_{EE} + 2.5 V$                                                  | 2.0                       | 3.1                       | -     | A    |

| Low level output current during fault condition     | I <sub>OLF</sub>               |        | 13.1.3          | $V_{OUT} - V_{EE} = 14 V$                                                   | 90                        | 180                       | 230   | mA   |

| High level output voltage                           | V <sub>OH</sub>                |        | 13.1.4          | I <sub>OUT</sub> = - 650 μA                                                 | V <sub>CC2</sub> -<br>2.9 | V <sub>CC2</sub> -<br>1.6 | -     |      |

| Low level output voltage                            | V <sub>OL</sub>                |        | 13.1.5          | I <sub>OUT</sub> = 100 mA                                                   | -                         | 0.12                      | 0.5   | V    |

| Clamp threshold voltage                             | V <sub>tClamp</sub>            |        |                 | I <sub>CL</sub> = 100 mA                                                    | -                         | 2.3                       | -     |      |

| Clamp low level sinking<br>current                  | I <sub>CL</sub>                |        | 13.1.6          | $V_{Clamp} = V_{EE} + 2.5 V$                                                | 0.35                      | 2.2                       | _     | А    |

| High level supply current                           | I <sub>CC2H</sub>              |        | 13.1.7          | $I_F = 10 \text{ mA}$                                                       | -                         | 2.9                       | 5     |      |

| Low level supply current                            | I <sub>CC2L</sub>              |        | 13.1.8          | $I_F = 0 mA$                                                                | -                         | 2.2                       | 5     |      |

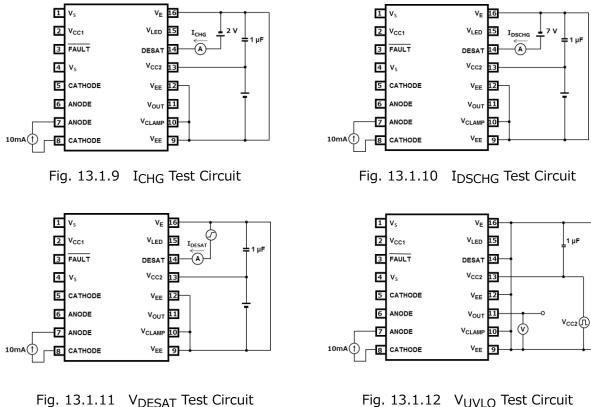

| Blanking capacitor<br>charging current              | I <sub>CHG</sub>               |        | 13.1.9          | $I_F = 10 \text{ mA}, V_{\text{DESAT}} = 2 \text{ V}$                       | -0.33                     | -0.26                     | -0.13 | mA   |

| Blanking capacitor<br>discharging current           | I <sub>DSCHG</sub>             |        | 13.1.10         | V <sub>DESAT</sub> = 7 V                                                    | 10                        | 27.7                      | -     |      |

| DESAT threshold voltage                             | V <sub>DESAT</sub>             |        | 13.1.11         | $I_F = 10 \text{ mA}, I_{DESAT} > 0$                                        | 6.0                       | 6.6                       | 7.5   |      |

| UVLO threshold voltage                              | V <sub>UVLO</sub> <sup>+</sup> |        | 13.1.12         | $I_F = 10$ mA, $V_{OUT} > 5$ V                                              | 10.5                      | 11.4                      | 12.5  | N    |

|                                                     | V <sub>UVLO</sub>              |        | 13.1.12         | $I_F$ = 10 mA, $V_{OUT}$ < 5 V                                              | 9.2                       | 10.0                      | 11.1  | V    |

| UVLO hysteresis                                     | UVLO <sub>HYS</sub>            |        |                 | V <sub>UVLO</sub> <sup>+</sup> - V <sub>UVLO</sub> <sup>-</sup>             | 0.4                       | 1.4                       | -     |      |

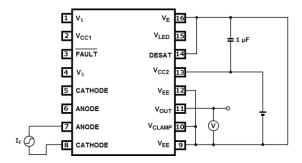

| Threshold input current<br>(L/H)                    | I <sub>FLH</sub>               |        | 13.1.13         | V <sub>CC2</sub> = 30 V, V <sub>OUT</sub> > 5 V                             | -                         | 1.1                       | 6.0   | mA   |

| Threshold input voltage<br>(H/L)                    | V <sub>FHL</sub>               |        |                 | V <sub>CC2</sub> = 30 V, V <sub>OUT</sub> < 5 V                             | 0.8                       | -                         | _     | V    |

Note: All typical values are at  $\,V_{CC2}$  –  $V_E$  = 30 V,  $T_a$  = 25  $\,^{\circ}\!\!\!C$  , unless otherwise noted.

Note 1:  $I_0$  application time  $\leq$  10  $\;\mu\text{s},$  single pulse

#### **10. Isolation Characteristics** (Unless otherwise specified, Ta = 25 °C)

| Characteristics                     | Symbol         | Note   | Test Conditions                 | Min              | Тур.             | Max | Unit |

|-------------------------------------|----------------|--------|---------------------------------|------------------|------------------|-----|------|

| Total capacitance (input to output) | CS             | Note 1 | V <sub>S</sub> = 0 V, f = 1 MHz | -                | 1.0              | -   | pF   |

| Isolation resistance                | R <sub>S</sub> | Note 1 | $V_S$ = 500 V, R.H. $\leq$ 60 % | 10 <sup>12</sup> | 10 <sup>14</sup> | _   | Ω    |

| Isolation voltage                   | BVS            | Note 1 | AC, 60 s                        | 5000             | -                | -   | Vrms |

Note 1: This device considered a two-terminal device: All pins on the LED & feedback IC side are shorted together, and all pin on the Output IC side are shorted together.

#### **11. Switching Characteristics (Note)** (Unless otherwise specified, Ta = - 40 to 110 °C, $V_{CC2}$ - $V_{FF}$ = 15 to 30 V, $V_F$ - $V_{FF}$ = 0 V)

|                                            |                   | e specifieu,                       | 1a –             | - 40 10         | 110 °C, V <sub>CC2</sub> -                              | $\mathbf{v}_{\text{EE}} = 15 10$                                | 30 V, | VE-V | EE - C | <b>v</b> ) |

|--------------------------------------------|-------------------|------------------------------------|------------------|-----------------|---------------------------------------------------------|-----------------------------------------------------------------|-------|------|--------|------------|

| Character                                  | istics            | Symbol                             | Note             | Test<br>Circuit | Test Conc                                               | litions                                                         | Min   | Тур. | Max    | Unit       |

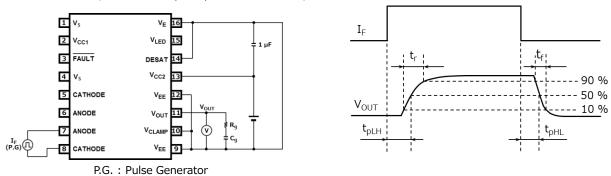

| Propagation                                | $L \rightarrow H$ | t <sub>pLH</sub>                   |                  |                 |                                                         | $\begin{array}{l} I_F = 0 \ \rightarrow \ 10 \\ mA \end{array}$ | 100   | 170  | 250    |            |

| delay time                                 | $H\toL$           | t <sub>pHL</sub>                   | Note 1           |                 |                                                         | $\begin{array}{l} I_F = 10 \rightarrow 0 \\ mA \end{array}$     | 100   | 165  | 250    |            |

| Pulse width dist                           | ortion            | t <sub>pHL</sub> -t <sub>pLH</sub> |                  |                 | $R_{g} = 10 \Omega,$<br>$C_{g} = 10 nF,$                | $I_F = 0 \leftrightarrow 10$                                    | _     | 5    | 50     |            |

| Propagation del<br>(device to devic        |                   | t <sub>psk</sub>                   | Note 1<br>Note 2 | 13.1.14         | f = 10  kHz,<br>duty = 50 %                             | $I_F = 0 \leftrightarrow 10$<br>mA                              | -150  | -    | 150    | ns         |

| Rise time                                  |                   | t <sub>r</sub>                     | Note 1           |                 |                                                         | $\begin{array}{l} I_F = 0 \rightarrow 10 \\ mA \end{array}$     | -     | 58   | -      |            |

| Fall time                                  |                   | t <sub>f</sub>                     | Note 1           |                 |                                                         | $\begin{array}{l} I_F = 10 \rightarrow 0 \\ mA \end{array}$     | _     | 57   | _      |            |

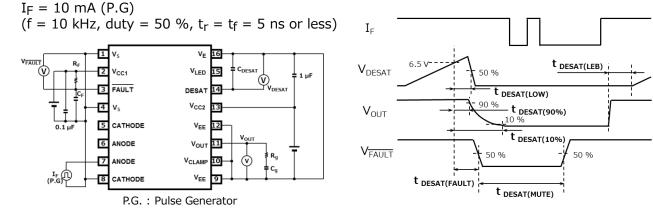

| DESAT sense to<br>V <sub>OUT</sub> delay   | 90%               | t <sub>DESAT</sub> (90%)           |                  |                 |                                                         |                                                                 | _     | 145  | 500    | ns         |

| DESAT sense to<br>V <sub>OUT</sub> delay   | 0 10%             | t <sub>DESAT(10%)</sub>            |                  |                 | $C_{DESAT} = 100 \text{ pF},$<br>$R_{g} = 10 \Omega,$   |                                                                 | _     | 2.1  | 3      |            |

| DESAT leading blanking time                | edge              | t <sub>DESAT(LEB)</sub>            |                  |                 | $C_g = 10 \ s_2,$<br>$C_g = 10 \ nF$                    |                                                                 | _     | 1.4  | _      | μs         |

| DESAT sense to<br>V <sub>DESAT</sub> delay | 50%               | t <sub>DESAT(LOW)</sub>            |                  | 13.1.15         |                                                         |                                                                 | _     | 167  | -      | ns         |

| DESAT dense to                             |                   | t <sub>DESAT(FAULT)</sub>          | Note 3           |                 | $C_{DESAT} = 100 \text{ pF},$<br>$R_{q} = 10 \Omega,$   | $C_F = Open$                                                    | -     | 340  | 500    | ns         |

| level FAULT sig                            | nal delay         | CDESAT(FAULT)                      | 1000 0           |                 | $C_{g} = 10 \text{ nF},$                                | $C_F = 1 nF$                                                    | -     | 640  | -      | 110        |

| DESAT input m                              | ute time          | t <sub>DESAT(MUTE)</sub>           |                  |                 | $V_{CC1} = 5 V,$<br>$R_F = 2.1 k\Omega$                 | -                                                               | 15    | 25.5 | 40     | μs         |

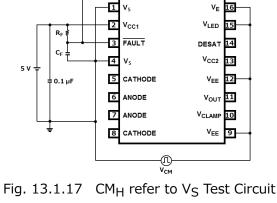

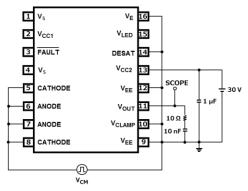

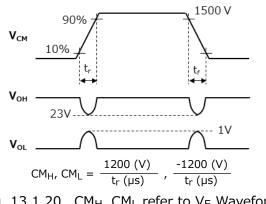

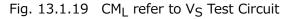

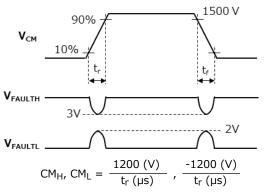

| High level comr                            | non-mode          | CM                                 | Note 3           | 13.1.16         | Ta = 25 ℃,<br>V <sub>CM</sub> = 1500 V <sub>P-P</sub> , | C <sub>F</sub> = Open                                           | ±25   | ±40  | -      |            |

| transient immu                             |                   | CM <sub>H</sub>                    | Note 4           | 13.1.17         | V <sub>CC2</sub> = 30 V,                                | C <sub>F</sub> = 1 nF                                           | ±50   | ±100 | -      | k)//up     |

| Low level comm                             |                   | CML                                | Note 3           | 13.1.18         | R <sub>F</sub> = 2.1 kΩ,<br>R <sub>q</sub> = 10 Ω,      | $C_F = Open$                                                    | ±25   | ±40  | I      | kV/µs      |

| transient immu                             | nity              |                                    | Note 5           | 13.1.19         | $C_g = 10 \text{ nF}$                                   | C <sub>F</sub> = 1 nF                                           | ±50   | ±100 | -      |            |

Note: All typical values are at  $V_{CC2} - V_E = 30$  V,  $T_a = 25$  °C, unless otherwise noted.

Note 1: Input signal: f = 10 kHz, duty = 50 %, tr = tf = 5 ns or less

Note 2: The propagation delay skew,  $t_{psk}$ , is equal to the magnitude of the worst-case difference in  $t_{pHL}$  and/or  $t_{pLH}$  that will be seen between units at the same given conditions (supply voltage, input current, temperature, etc).

Note 3: Even  $C_{\text{F}}$  is open, less than 15 pF of probe and stray wiring capacitance is included.

Note 4: High level common mode transient immunity is the maximum tolerable slew rate  $(dV_{CM}/dt)$  of the common mode pulse  $(V_{CM})$  to assure that the output will remain in the high state  $(V_{OUT} > 23 \text{ V}, \text{VFAULT} > 3 \text{ V})$ .

Note 5: Low level common mode transient immunity is the maximum tolerable slew rate ( $dV_{CM}/dt$ ) of the common mode pulse ( $V_{CM}$ ) to assure that the output will remain in a low state ( $V_{OUT} < 1 \text{ V}$ ,  $\sqrt{FAULT} < 2 \text{ V}$ ).

### 12. Application Information

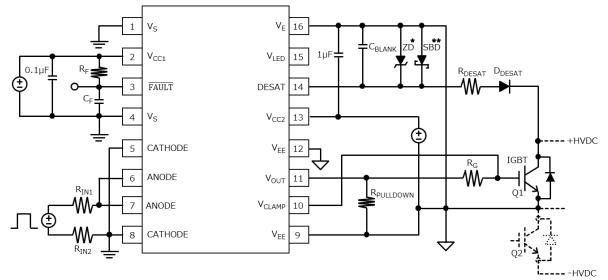

Fig 12.1 Recommended application circuit with positive gate drive, desaturation detection and active Miller clamp

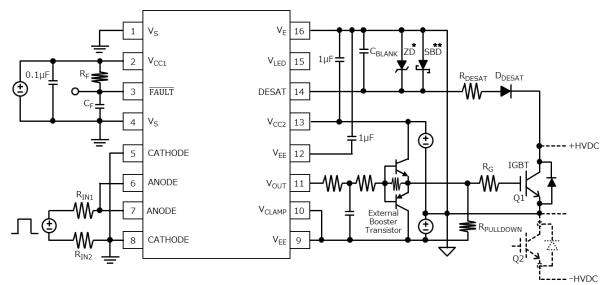

# Fig 12.2 Recommended application circuit with negative gate drive, external booster transistors and desaturation detection

Note : Bypass capacitors (1  $\mu$ F) must be connected between pin 13 (V<sub>CC2</sub>) and 16 (V<sub>E</sub>) to stabilize the operation of the high gain linear amplifier. When V<sub>E</sub> – V<sub>EE</sub> > 0 V (with negative gate drive), another bypass capacitor (1  $\mu$ F) must be connected between pin 9 or 12 (V<sub>EE</sub>) and 16 (V<sub>E</sub>). Failure to provide the bypassing may impair the switching property. The total lead length between each capacitor and the coupler should not exceed 1 cm.

Refer to the connection of pin 14 and pin 16 for a desaturation detection function. The desaturation diode  $D_{\text{DESAT}}$  600V / 1200V fast recovery type and capacitor  $C_{\text{BLANK}}$  are external components required for fault detection circuits. Also, select a resistance  $R_{\text{DESAT}}$  of 500 ohms or more for protection of DESAT pin 14. For details, refer to the application note "Smart Gate Driver Coupler Tips for Designing DESAT Detection Circuits".

- \* : Zener diode for DESAT pin protection. CUZ8V2 is recommended.

- \* \* : Schottky diode for DESAT false detection prevention. CUS05F30 is recommended.

### **13.** Characteristics Figures

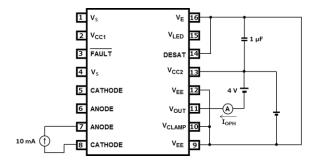

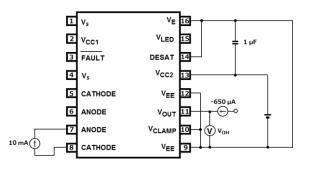

Fig. 13.1.1 I<sub>OPH</sub> Test Circuit

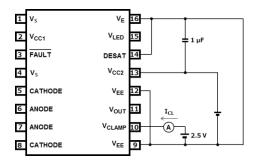

Fig. 13.1.3  $I_{OLF}$  Test Circuit

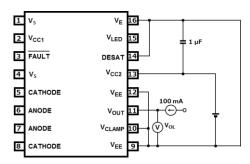

Fig. 13.1.5 V<sub>OL</sub> Test Circuit

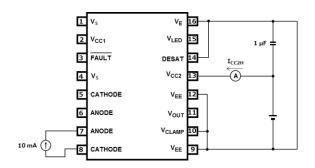

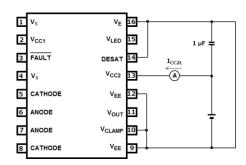

Fig. 13.1.7  $I_{CC2H}$  Test Circuit

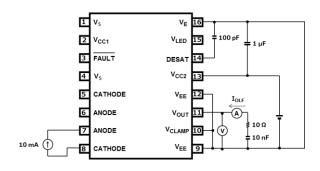

Fig. 13.1.2 I<sub>OPL</sub> Test Circuit

Fig. 13.1.4 V<sub>OH</sub> Test Circuit

Fig. 13.1.6 I<sub>CL</sub> Test Circuit

Fig. 13.1.8 I<sub>CC2L</sub> Test Circuit

Fig. 13.1.11 V<sub>DESAT</sub> Test Circuit

Fig. 13.1.13 I<sub>FLH</sub> Test Circuit

$I_{F} = 10 \text{ mA} (P.G)$  $(f = 10 \text{ kHz}, \text{duty} = 50 \%, t_r = t_f = 5 \text{ ns or less})$

Fig. 13.1.14 t<sub>PLH</sub>, t<sub>PHL</sub>, t<sub>r</sub>, t<sub>f</sub> Test Circuit and Waveform

SCOPE

Fig. 13.1.16 CM<sub>H</sub> refer to V<sub>E</sub> Test Circuit

Fig. 13.1.18 CM<sub>L</sub> refer to V<sub>E</sub> Test Circuit

SCOPE 1 Vs  $V_{\mathsf{E}}$ 2 V<sub>CC1</sub> VLED 15 FAULT 3 DESAT 14 CF 4 ٧٩ V<sub>CC2</sub> 13 5 V (1) 9 mA 5 CATHODE  $V_{\text{EE}}$ 12 0.1 µF 6 ANODE 11 VOUT 7 ANODE VCLAME 10 8 CATHODE  $V_{EE}$ 9 -П-V<sub>СМ</sub>

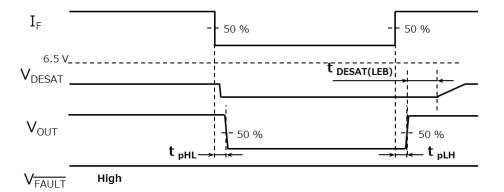

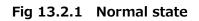

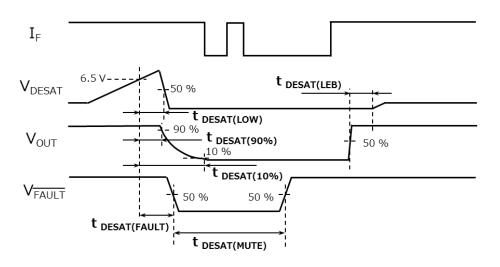

## 13.2 Timing Chart

Fig 13.2.2 Protection state (when  $I_F$  turns off within the  $t_{DESAT(MUTE)}$ )

Fig 13.2.3 Protection state (when  $I_F$  turns off after the  $t_{DESAT(MUTE)}$ )

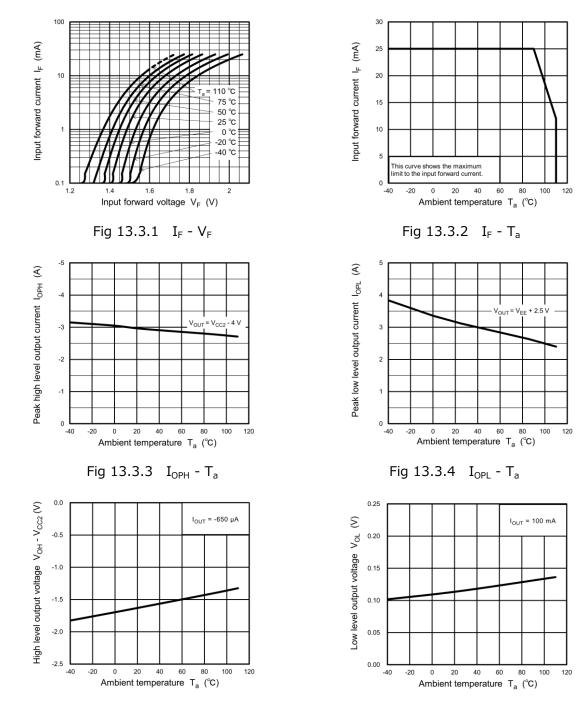

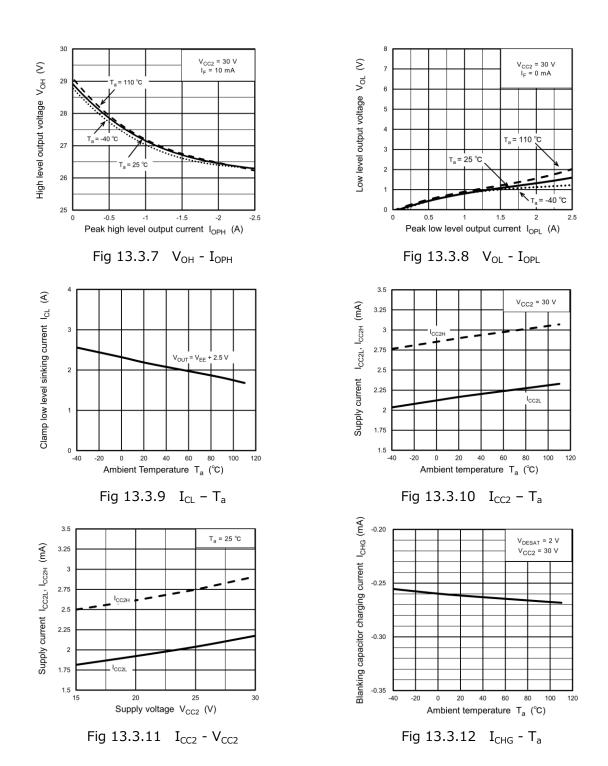

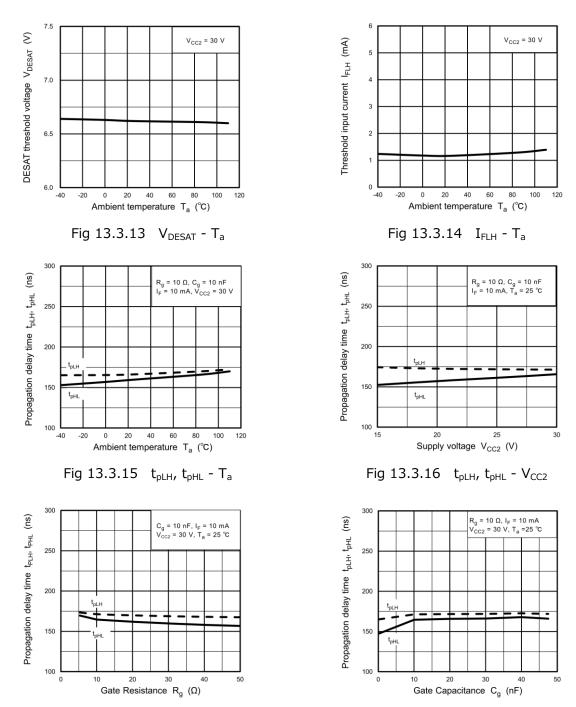

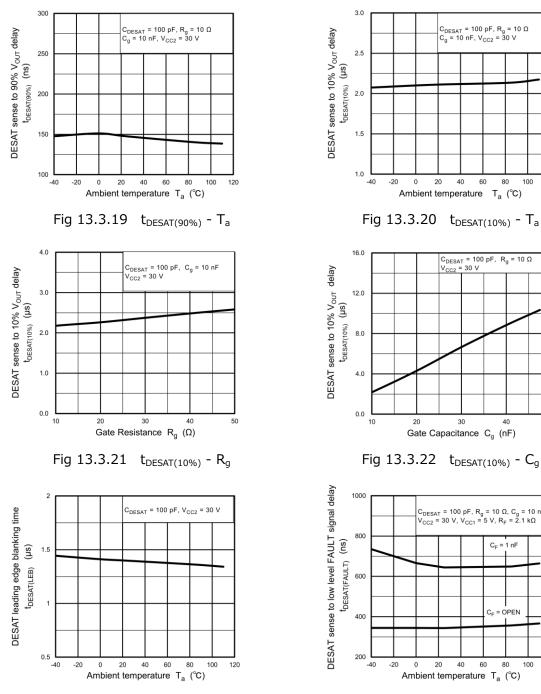

## 13.3 Characteristics Curves (Note)

TOSHIBA

Fig 13.3.5 (  $V_{\text{OH}}$  -  $V_{\text{CC2}}$  ) -  $T_{\text{a}}$

Fig 13.3.6  $V_{OL}$  -  $T_a$

Fig 13.3.17  $t_{pLH}$ ,  $t_{pHL}$  -  $R_g$

Fig 13.3.18  $t_{\text{pLH}},\,t_{\text{pHL}}$  -  $C_{\text{g}}$

100 120

50

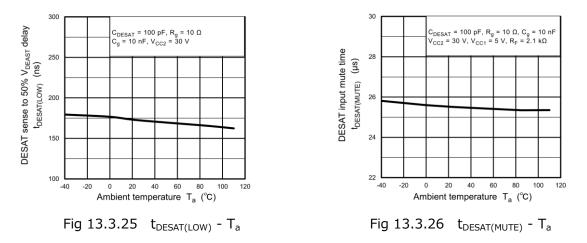

$C_{DESAT} = 100 \text{ pF}, R_g = 10 \Omega$  $C_g = 10 \text{ nF}, V_{CC2} = 30 \text{ V}$

$C_{DESAT} = 100 \text{ pF}, R_g = 10 \Omega$  $V_{CC2} = 30 \text{ V}$

Fig 13.3.23  $t_{\text{DESAT(LEB)}}$  -  $T_a$

Fig 13.3.24 t<sub>DESAT(FAULT)</sub> - T<sub>a</sub>

20

30

Gate Capacitance Cg (nF)

$C_{DESAT} = 100 \text{ pF}, R_g = 10 \Omega, C_g = 10 \text{ nF}$  $V_{CC2} = 30 \text{ V}, V_{CC1} = 5 \text{ V}, R_F = 2.1 \text{ k}\Omega$

C<sub>F</sub> = 1 nF

Cr = OPEN

100

120

Note : The above characteristics curves are presented for reference only and not guaranteed by production test, unless otherwise noted.

### 14. Soldering and Storage

### 14.1. Precautions for Soldering

The soldering temperature should be controlled as closely as possible to the conditions shown below, irrespective of whether a soldering iron or a reflow soldering method is used.

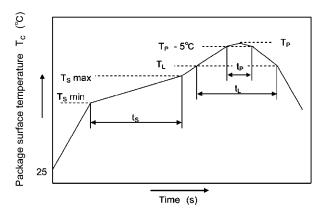

$\cdot\,$  When using soldering reflow.

The soldering temperature profile is based on the package surface temperature.

(See the figure shown below, which is based on the package surface temperature.)

Reflow soldering must be performed once or twice.

The mounting should be completed with the interval from the first to the last mountings being 2 weeks.

|                                                        | Symbol         | Min | Max | Unit |

|--------------------------------------------------------|----------------|-----|-----|------|

| Preheat temperature                                    | Ts             | 150 | 200 | °C   |

| Preheat time                                           | ts             | 60  | 120 | s    |

| Ramp-up rate ( $T_L$ to $T_P$ )                        |                |     | 3   | °C/s |

| Liquidus temperature                                   | TL             | 2   | 17  | °C   |

| Time above T <sub>L</sub>                              | tL             | 60  | 150 | s    |

| Peak temperature                                       | Τ <sub>Ρ</sub> |     | 260 | °C   |

| Time during which $T_c$ is between (T_P – 5) and $T_P$ | t <sub>P</sub> |     | 30  | s    |

| Ramp-down rate $(T_P \text{ to } T_L)$                 |                |     | 6   | °C/s |

#### An Example of a Temperature Profile When Lead(Pb)-Free Solder Is Used

· When using soldering flow

Preheat the device at a temperature of 150°C (package surface temperature) for 60 to 120 seconds. Mounting condition of 260°C within 10 seconds is recommended.

- Flow soldering must be performed once.

- When using soldering Iron

Complete soldering within 10 seconds for lead temperature not exceeding  $260^{\circ}$  or within 3 seconds not exceeding  $350^{\circ}$ .

Heating by soldering iron must be done only once per lead.

### 14.2. Precautions for General Storage

- · Avoid storage locations where devices may be exposed to moisture or direct sunlight.

- Follow the precautions printed on the packing label of the device for transportation and storage.

- $\cdot\,$  Keep the storage location temperature and humidity within a range of 5  $^\circ$  to 35  $^\circ$  and 45 % to 75 %, respectively.

- $\cdot\,$  Do not store the products in locations with poisonous gases (especially corrosive gases) or in dusty conditions.

- Store the products in locations with minimal temperature fluctuations. Rapid temperature changes during storage can cause condensation, resulting in lead oxidation or corrosion, which will deteriorate the solderability of the leads.

- $\cdot\,$  When restoring devices after removal from their packing, use anti-static containers.

- $\cdot\,$  Do not allow loads to be applied directly to devices while they are in storage.

- If devices have been stored for more than two years under normal storage conditions, it is recommended that you check the leads for ease of soldering prior to use.

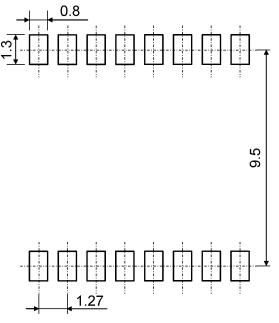

## 15. Land Pattern Dimensions (for reference only)

Unit: mm

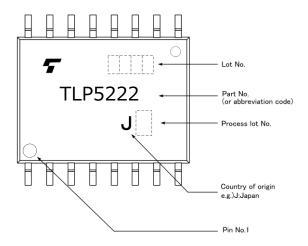

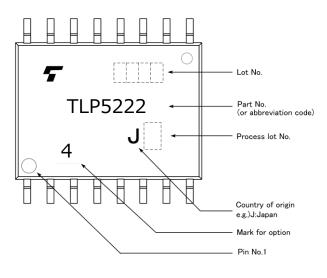

16. Marking

### 17. EN 60747-5-5 Option (D4) Specification

- Part number: TLP5222 (Note 1)

- The following part naming conventions are used for the devices that have been qualified according to option (D4) of EN 60747.

Example: TLP5222(D4-TP,E

- D4: EN 60747 option

- TP: Tape type

- E: [[G]]/RoHS COMPATIBLE (Note 2)

- Note 1: Use TOSHIBA standard type number for safety standard application. e.g., TLP5222(D4-TP,E  $\rightarrow$  TLP5222

- Note 2: Please contact your Toshiba sales representative for details on environmental information such as the product's RoHS compatibility.

RoHS is the Directive 2011/65/EU of the European Parliament and of the Council of 8 June 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment.

|                                                                                | Description                                                                                                                                | Symbol           | Rating                                                        | Unit           |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------|----------------|

| Application classification                                                     |                                                                                                                                            |                  |                                                               |                |

| for rated mains volta<br>for rated mains volta                                 |                                                                                                                                            |                  | I-IV<br>I-III                                                 | _              |

| Climatic classification                                                        |                                                                                                                                            |                  | 40 / 110 / 21                                                 | _              |

| Pollution degree                                                               |                                                                                                                                            |                  | 2                                                             | _              |

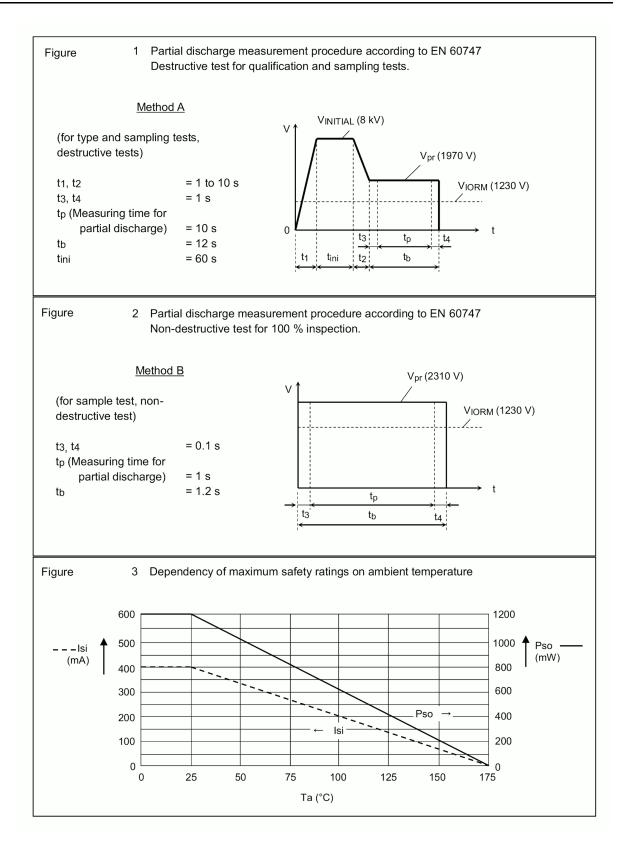

| Maximum operating insu                                                         | lation voltage                                                                                                                             | VIORM            | 1230                                                          | Vpeak          |

| Input to output test voltag<br>Vpr = 1.6 × VIORM, 1<br>tp = 10 s, partial disc | type and sample test                                                                                                                       | Vpr              | 1970                                                          | Vpeak          |

| Input to output test volta<br>Vpr = 1.875 × VIORM<br>tp = 1 s, partial disch   | Λ, 100 % production test                                                                                                                   | Vpr              | 2310                                                          | Vpeak          |

| Highest permissible over (transient overvoltag                                 | 6                                                                                                                                          | VTR              | 8000                                                          | Vpeak          |

| current (input currer                                                          | ax. permissible ratings in case of fault,<br>also refer to thermal derating curve)<br>it IF, P <sub>SO</sub> = 0)<br>al power dissipation) | lsi<br>Pso<br>Ts | 400<br>1200<br>175                                            | mA<br>mW<br>°C |

| Insulation resistance                                                          | VIO = 500 V, Ta = 25 °C<br>VIO = 500 V, Ta = 100 °C<br>VIO = 500 V, Ta = Ts                                                                | Rsi              | ≥ 10 <sup>12</sup><br>≥ 10 <sup>11</sup><br>≥ 10 <sup>9</sup> | Ω              |

#### Fig 17.1 EN 60747 Insulation Characteristics

| Minimum creepage distance    | Cr  | 8.0 mm |

|------------------------------|-----|--------|

| Minimum clearance            | CI  | 8.0 mm |

| Minimum insulation thickness | ti  | 0.4 mm |

| Comparative tracking index   | CTI | 500    |

| Fig 17.2 | Insulation R | Related | Specifications | (Note) |

|----------|--------------|---------|----------------|--------|

|----------|--------------|---------|----------------|--------|

Note: This photocoupler is suitable for safe electrical isolation only within the safety limit data. Maintenance of the safety data shall be ensured by means of protective circuits.

Fig 17.3 Marking on Packing for EN 60747

Fig 17.4 Marking Example (Note)

Note: The above marking is applied to the photocouplers that have been qualified according to option (D4) of EN 60747.

## 18. Ordering Information (Example of Item Name)

| Item Name       | VDE Option   | Packing (MOQ)            |

|-----------------|--------------|--------------------------|

| TLP5222(E       |              | Magazine (50 pcs)        |

| TLP5222(TP,E    |              | Tape and reel (1500 pcs) |

| TLP5222(D4,E    | EN 60747-5-5 | Magazine (50 pcs)        |

| TLP5222(D4-TP,E | EN 60747-5-5 | Tape and reel (1500 pcs) |

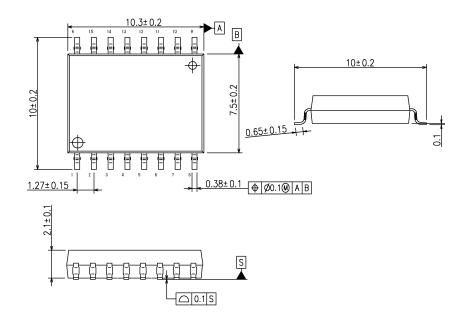

## Package Dimensions

Unit: mm

Weight: 0.364 g (typ.)

| Package Name(s)  |  |

|------------------|--|

| TOSHIBA: 11-10M1 |  |

### **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- GaAs (Gallium Arsenide) is used in Product. GaAs is harmful to humans if consumed or absorbed, whether in the form of dust or vapor. Handle with care and do not break, cut, crush, grind, dissolve chemically or otherwise expose GaAs in Product.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without

limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile

technology products (mass destruction weapons). Product and related software and technology may be controlled under the

applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the

U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited

except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

## **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

https://toshiba.semicon-storage.com/