# **TOSHIBA**

株式会社 東芝 セミコンダクター社

# はじめに

この度は弊社 32 ビットマイクロコントローラ TLCS-900/H1 シリーズ、 TMP92CF26A をご利用いただき、誠にありがとうございます。

本 LSI をご利用になる前に、「使用上の注意、制限事項」の章を参照されますことをお願い致します。

#### 低電圧/低消費電力

# CMOS 32 ビット マイクロコントローラ TMP92CF26AXBG

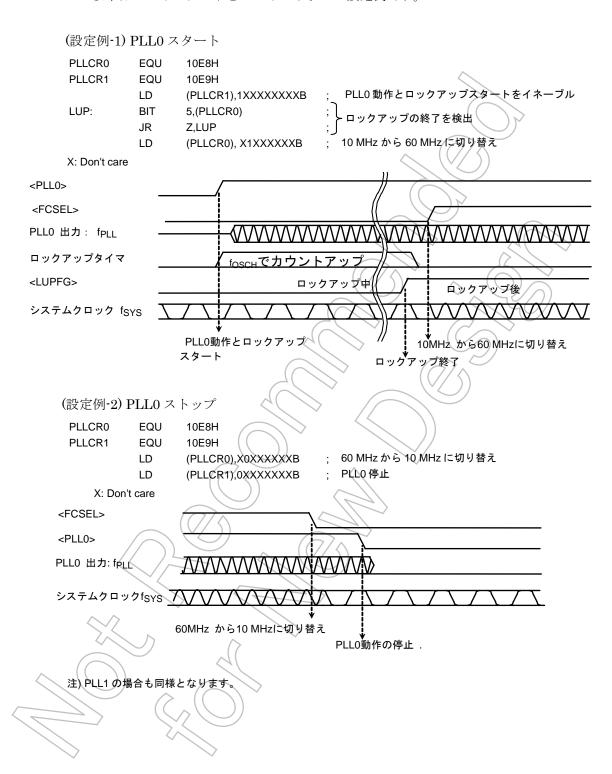

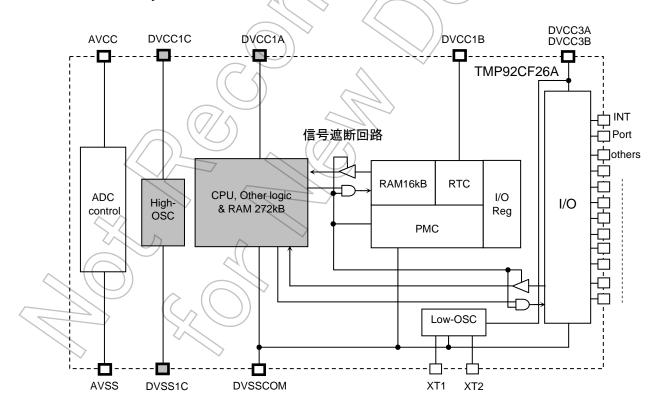

## 1. 概要と特長

TMP92CF26A は、低電圧/低消費電力動作が可能な高速・高機能 32 ビットマイクロコントローラです。TMP92CF26AXBG は 228 ピン BGA パッケージ製品です。

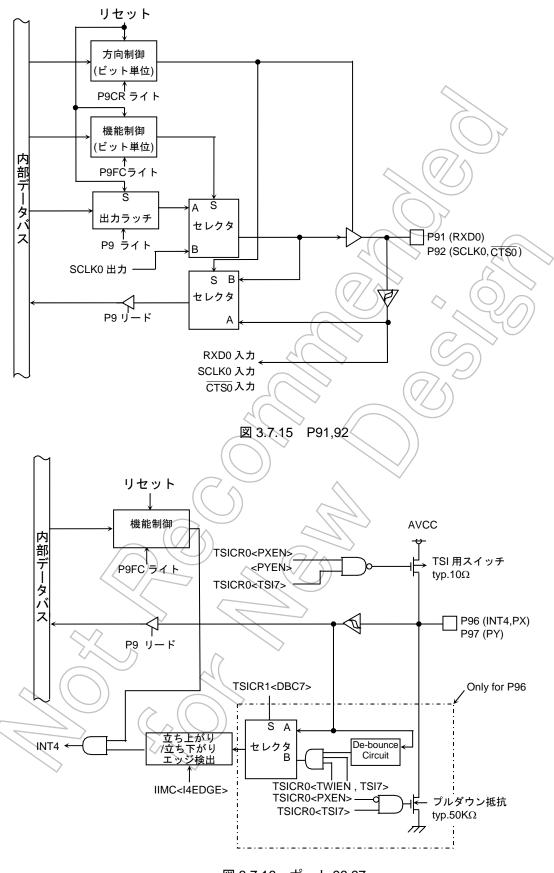

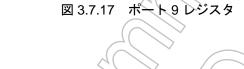

特長は次のとおりです。

- (1) オリジナル 32 ビット CPU (高速 900/H1\_CPU 使用)

- TLCS-900L1 と命令ニモニックで互換

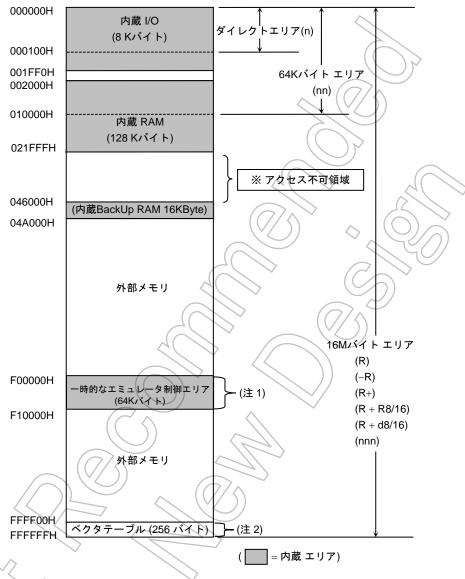

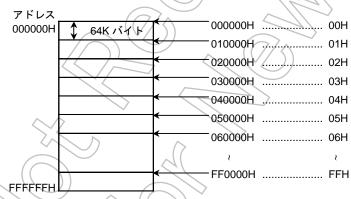

- 16M バイトのリニアアドレス空間

- 汎用レジスタ&レジスタバンク方式

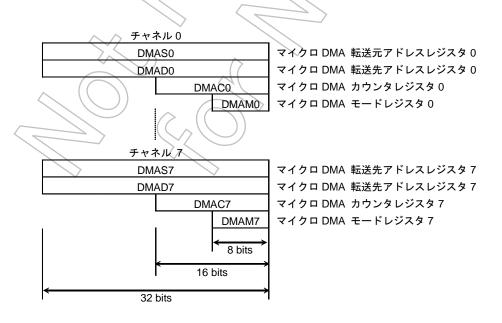

- マイクロ DMA: 8 チャネル (62.5ns /4 バイト@fsys= 80MHz)

- (2) 最小命令実行時間: 12.5ns (@fsys=80MHz)

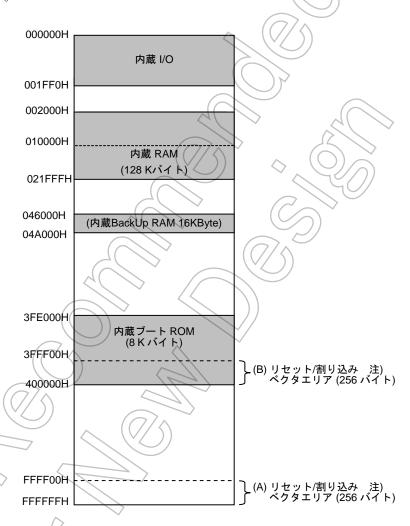

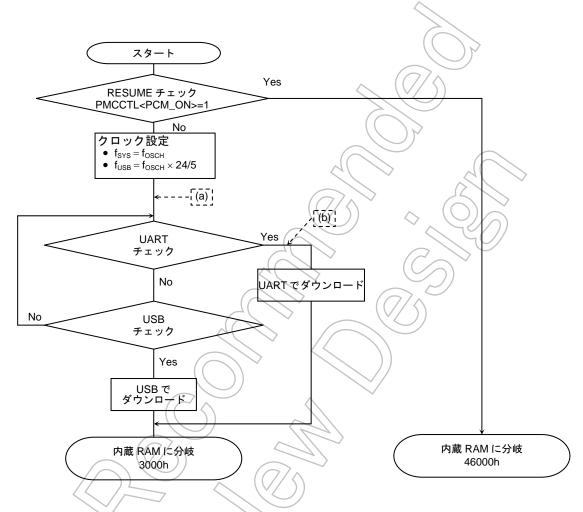

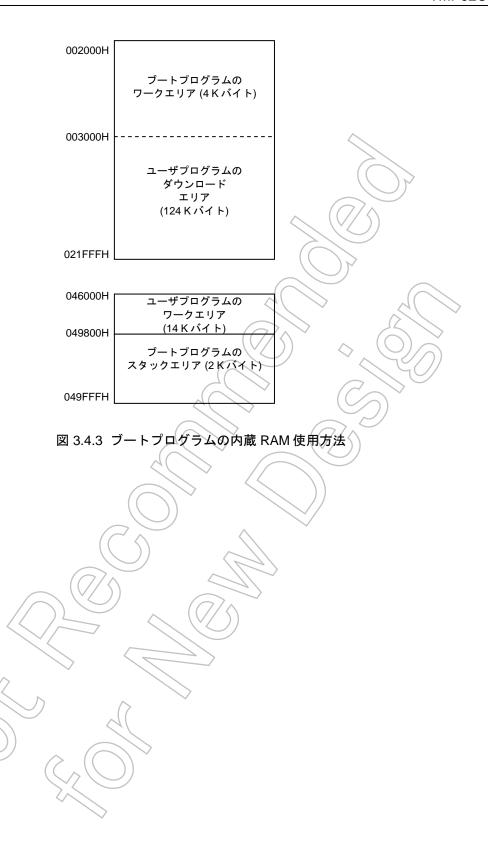

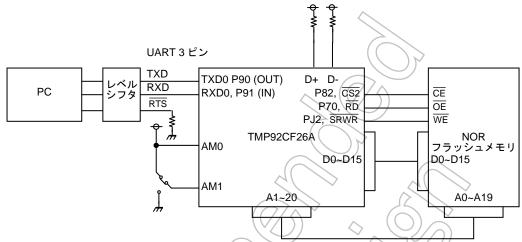

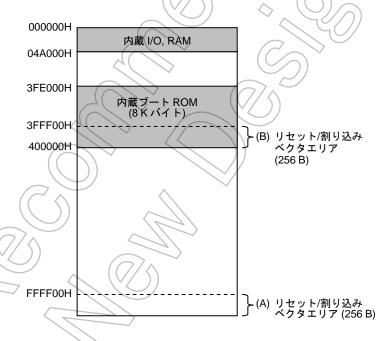

- (3) 内蔵 RAM: 144K バイト (プログラム、データ、表示メモリ用として使用可能) 内蔵 ROM: 8K バイト(Boot 専用メモリ) ユーザープログラムを USB、UART から内蔵 RAM へのロードが可能です。

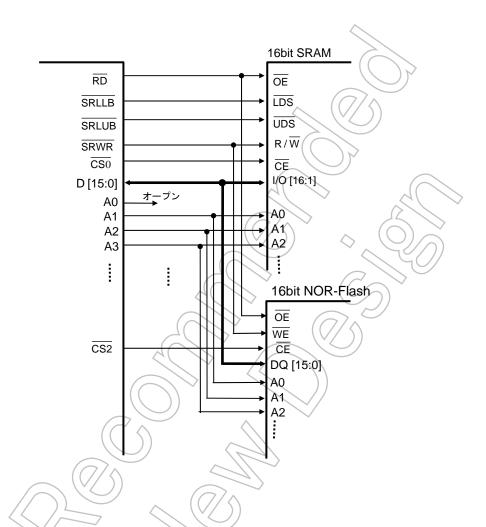

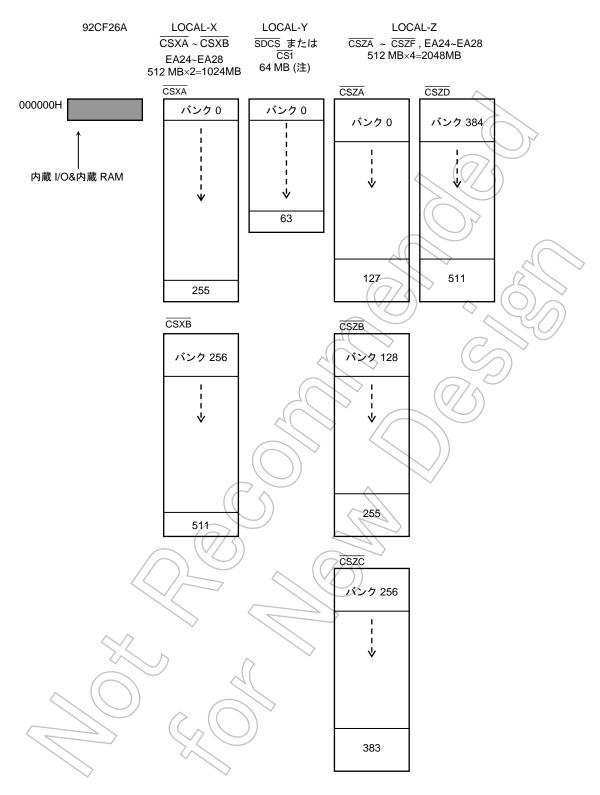

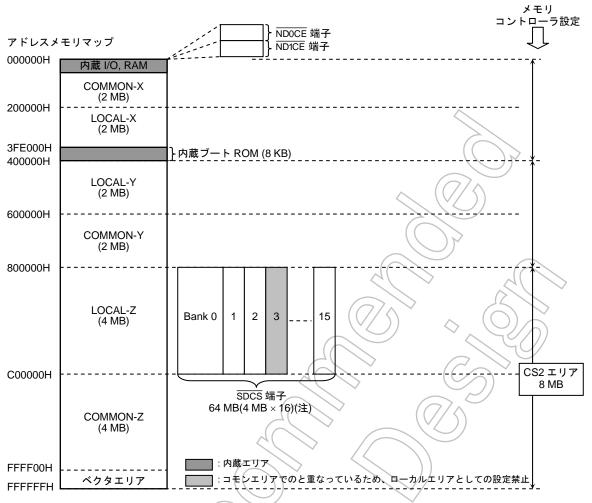

- (4) 外部メモリ拡張

- 3.1G バイト(プログラム,データ)まで拡張可能

- 外部データバス 8/16 ビット幅共存可能 …ダイナミックデータバスサイジング

- セパレートバスシステム

- (5) メモリコントローラ

- チップセレクト出力: 4チャネル

- 4 チャネルの内、1 チャネルは、詳細な AC 設定が可能

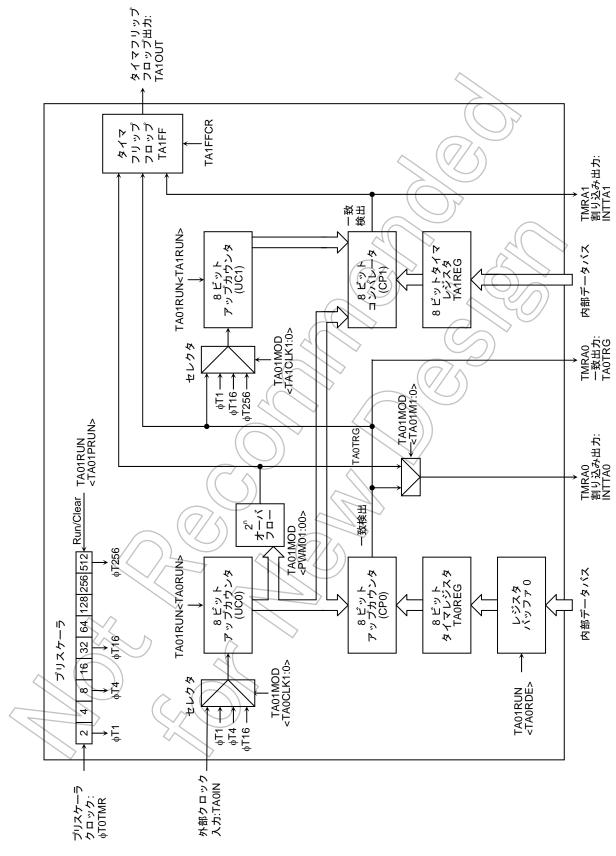

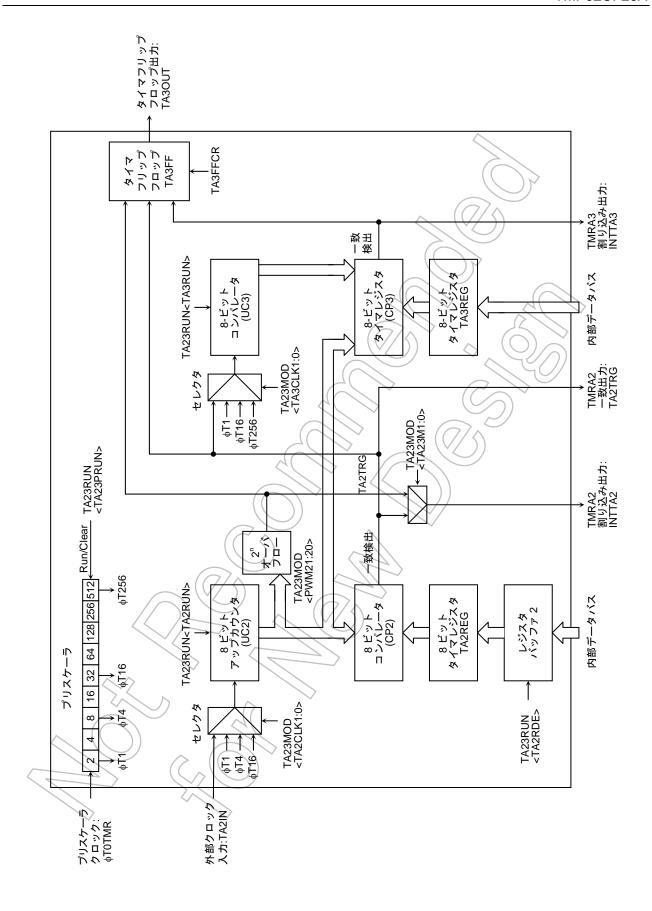

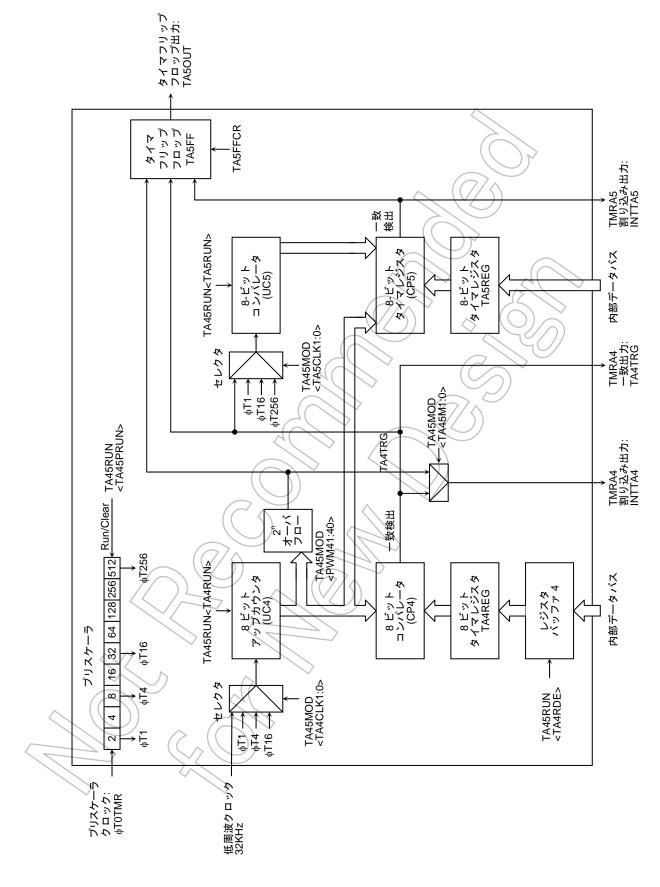

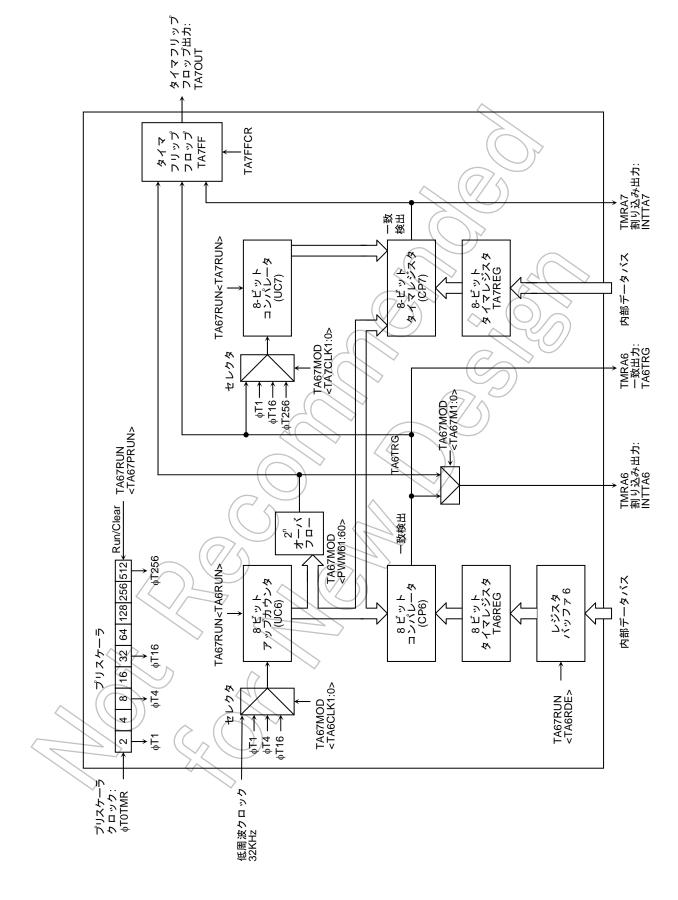

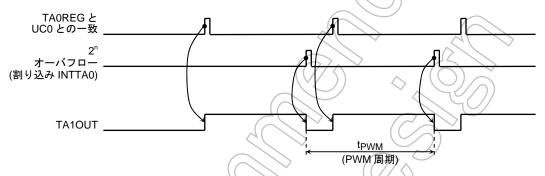

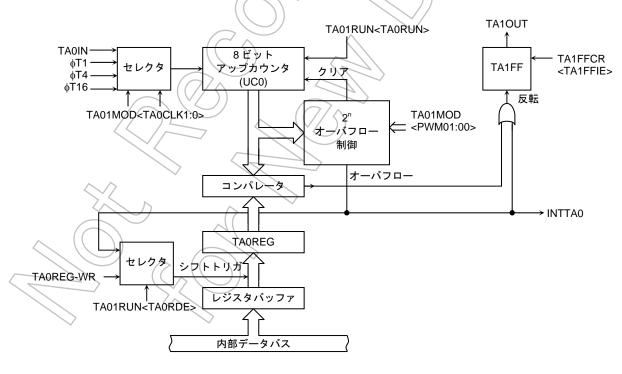

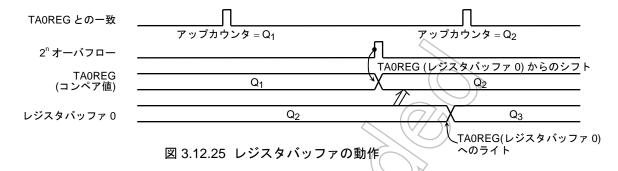

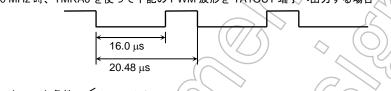

- (6) 8ビットタイマ:8チャネル

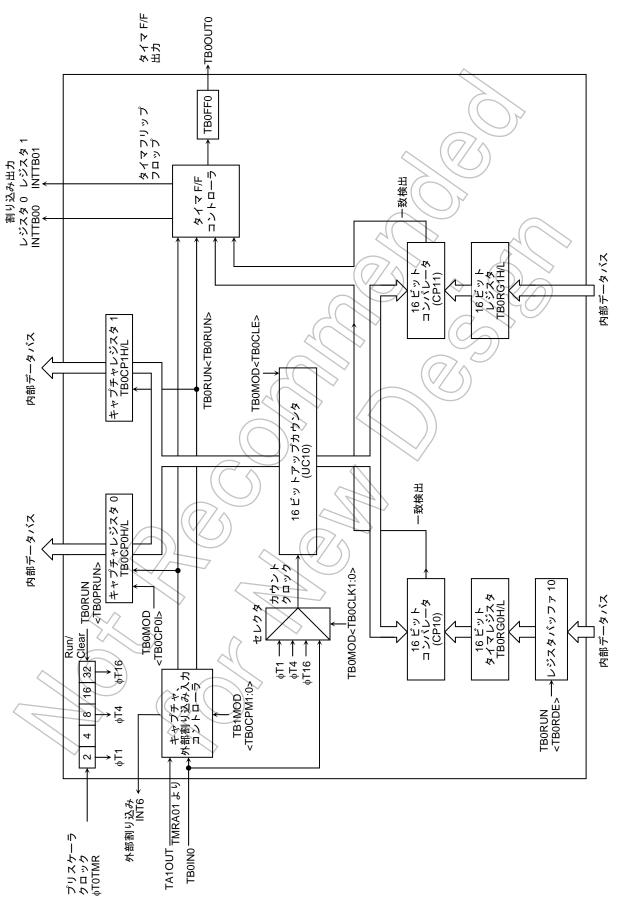

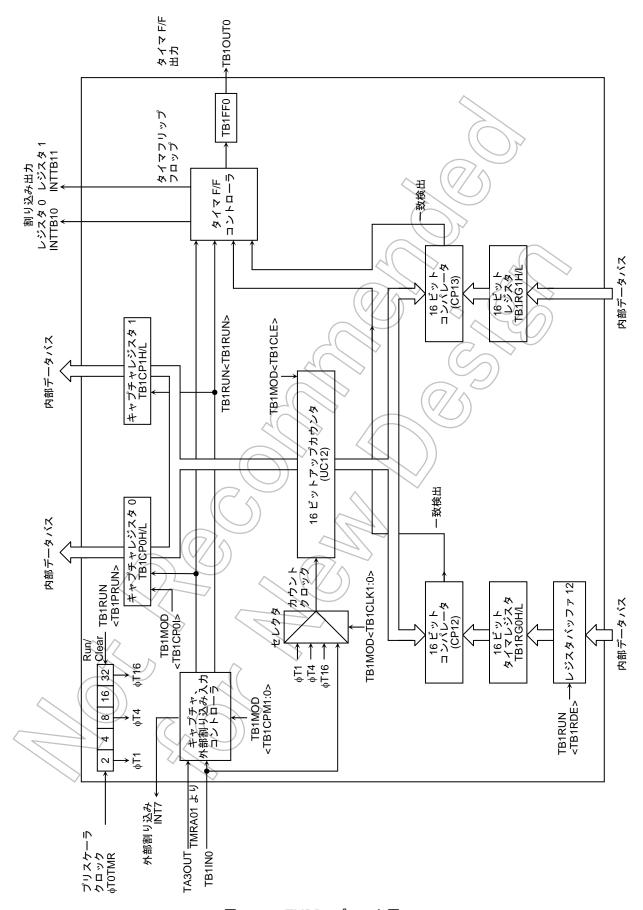

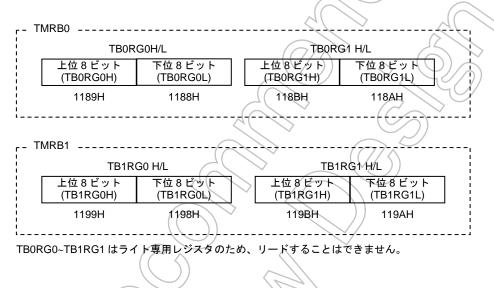

- (7) 16 ビットタイマ/イベントカウンタ: 2 チャネル

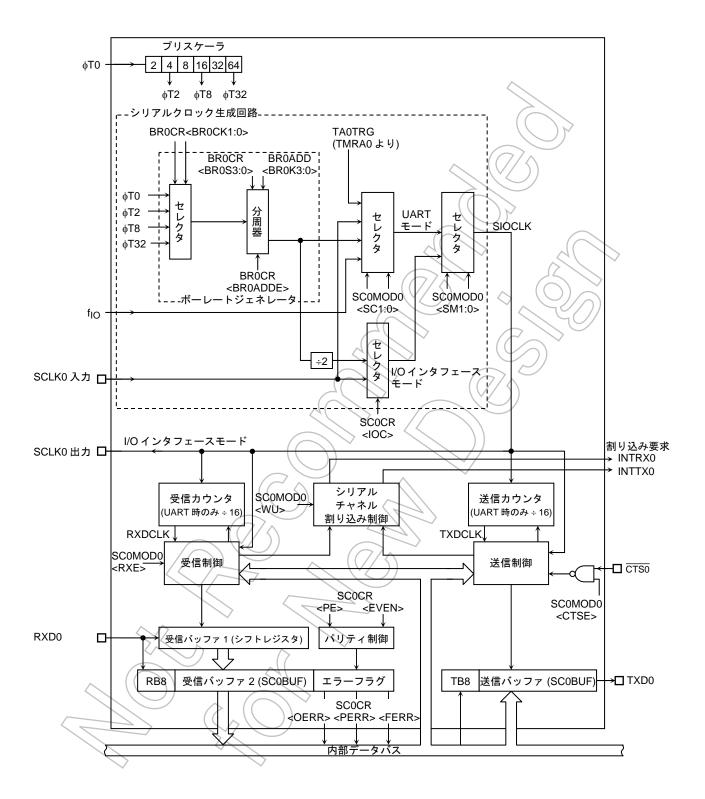

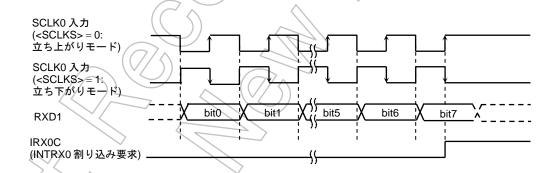

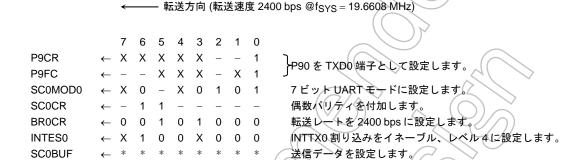

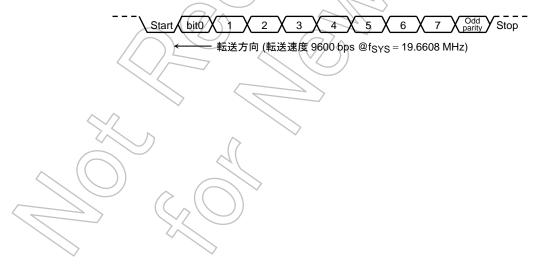

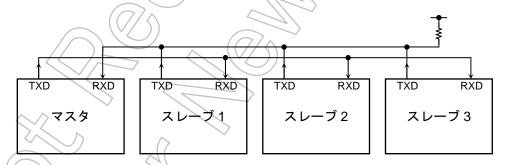

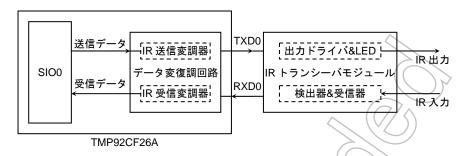

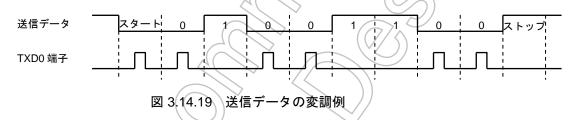

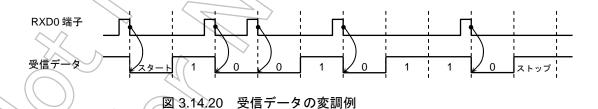

- (8) 汎用シリアルインタフェース:1 チャネル

- UART/同期両モード対応

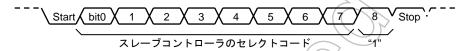

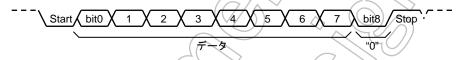

- IrDA ver1.0 (115.2 kbps) 対応モード選択可能

(ほかの機能との併用仕様の場合、設定できるボーレートに制約があります)

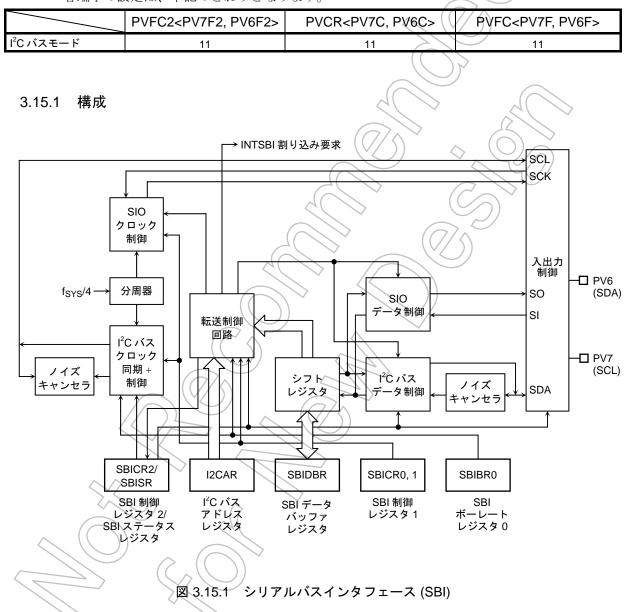

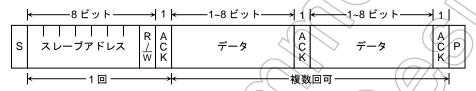

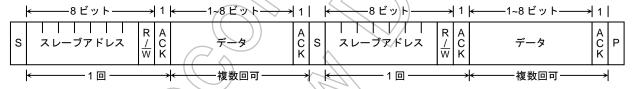

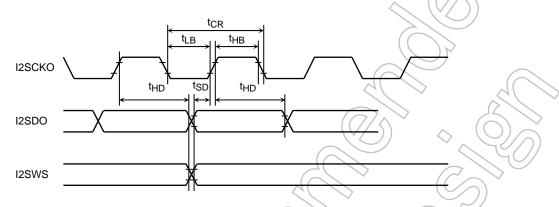

- (9) シリアルバスインタフェース:1チャネル

- I<sup>2</sup>C バスモードのみ対応

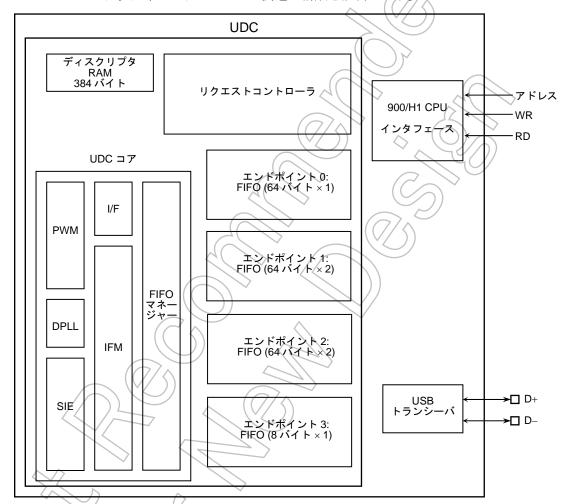

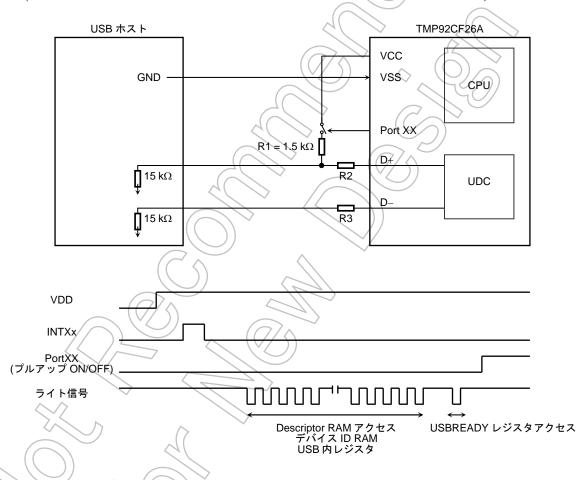

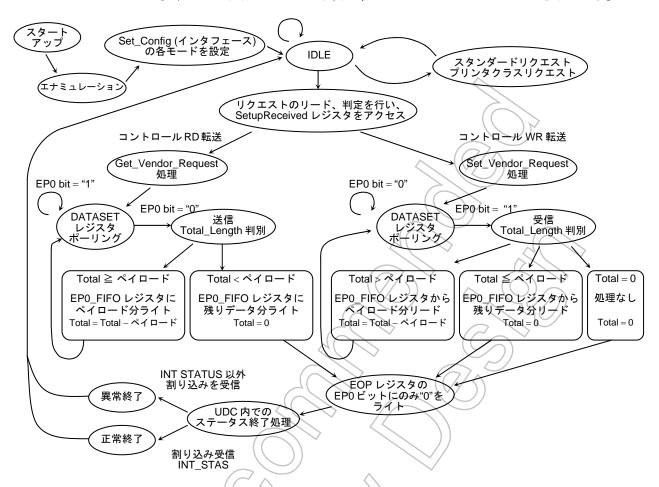

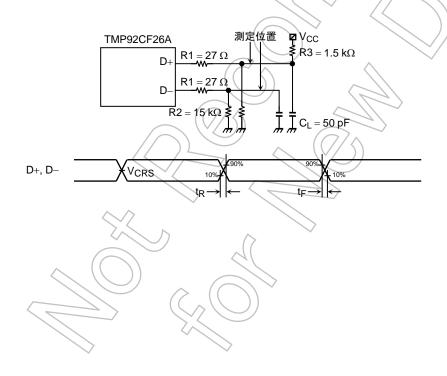

- (10) USB コントローラ: 1 チャネル

- USB(REV1.1)に対応

- フル・スピード(12Mbps)対応(低速には非対応)

- エンド・ポイント 0: コントロール 64 バイト× 1-FIFO

エンド・ポイント 1: バルク出力 64 バイト× 2-FIFO

エンド・ポイント 2: バルク入力 64 バイト× 2-FIFO

エンド・ポイント 3: 割り込み 8 バイト× 1-FIFO

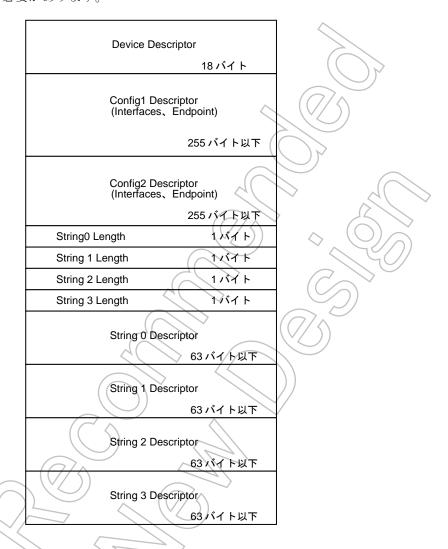

- ディスクリプタ RAM: 384 バイト

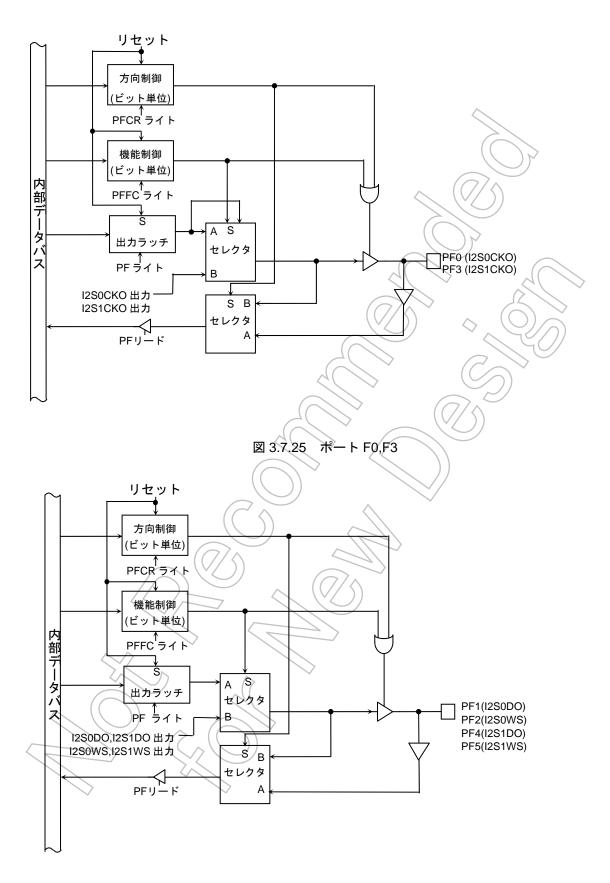

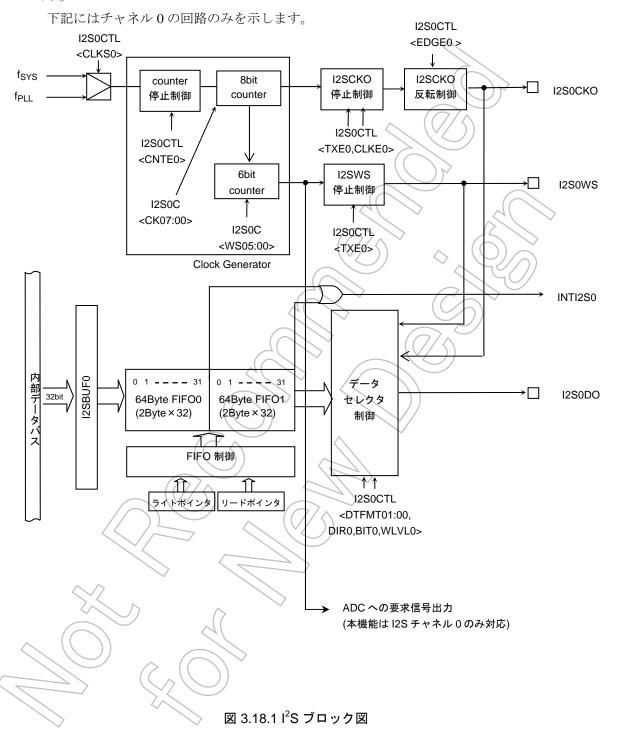

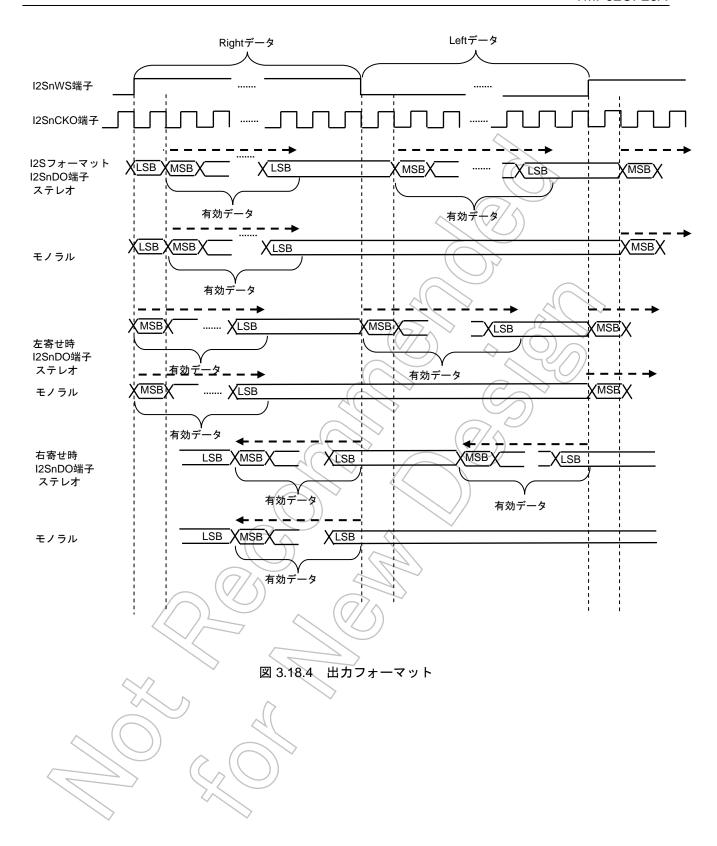

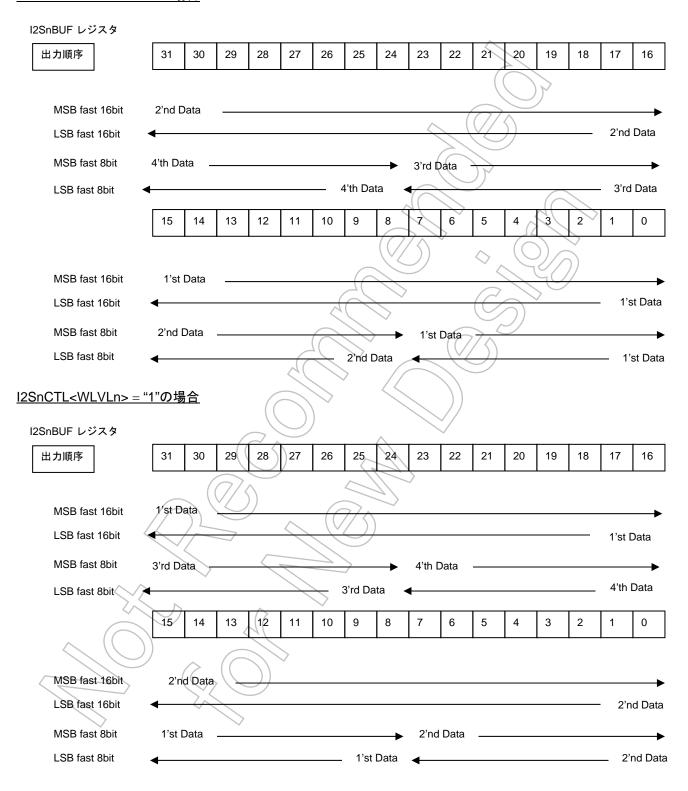

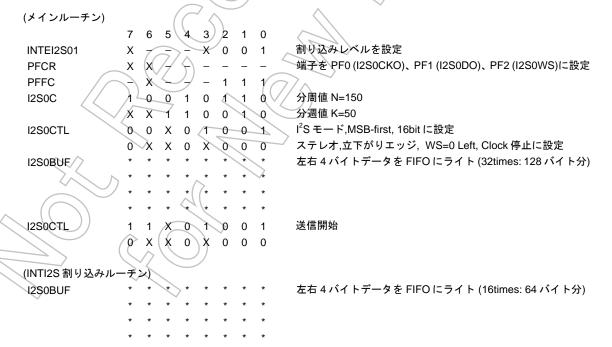

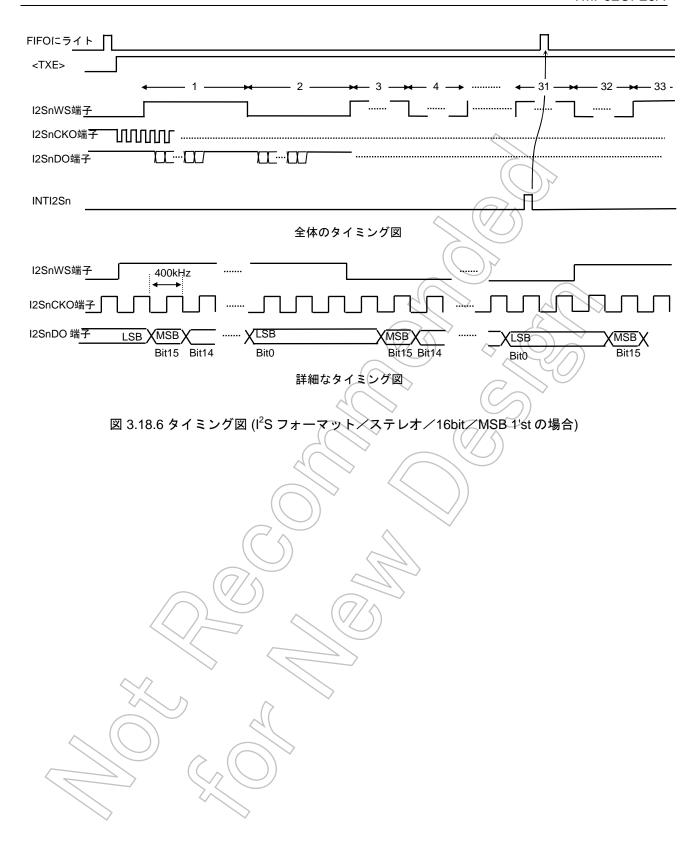

- (11) I<sup>2</sup>S(Inter-IC Sound)インターフェース: 2 チャネル

- I2Sバスモード(マスタ、送信のみに対応)

- Data Format は Left/Right Justify 両対応

- チャネルごとに、128 バイト(64 バイト×2)の FIFO バッファ内蔵

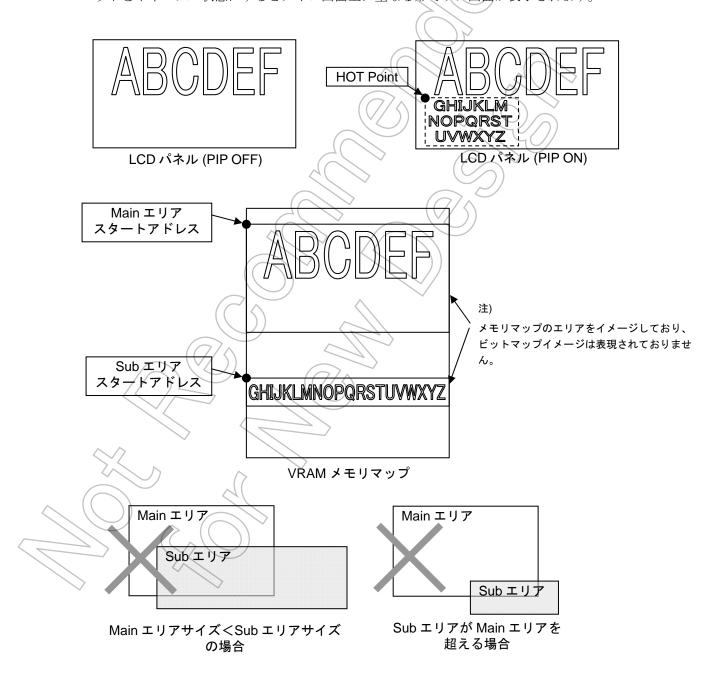

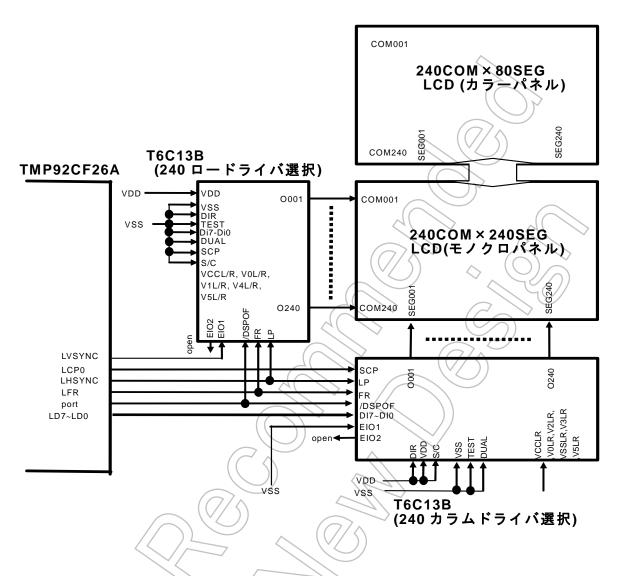

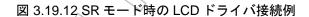

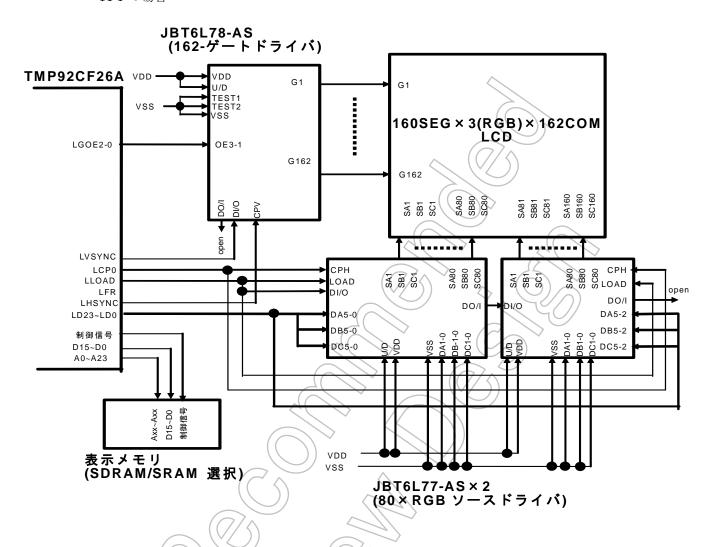

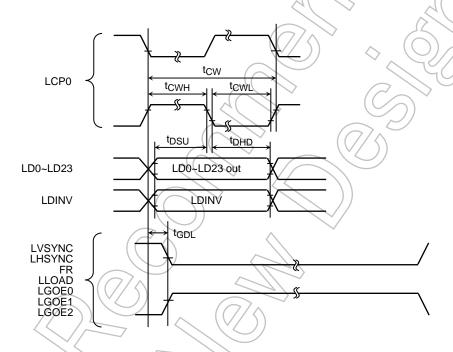

- (12)LCD コントローラ

- STN はモノクロ、4, 16, 64 階調、256/4096/65536/262144 カラーに対応

- TFT は、4096/65536/262144/16777216 カラーに対応

- PIP (Picture In Picture Display)に対応

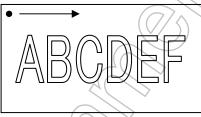

- 各種 LCDM に対応するための、H/W Rotation 機能対応

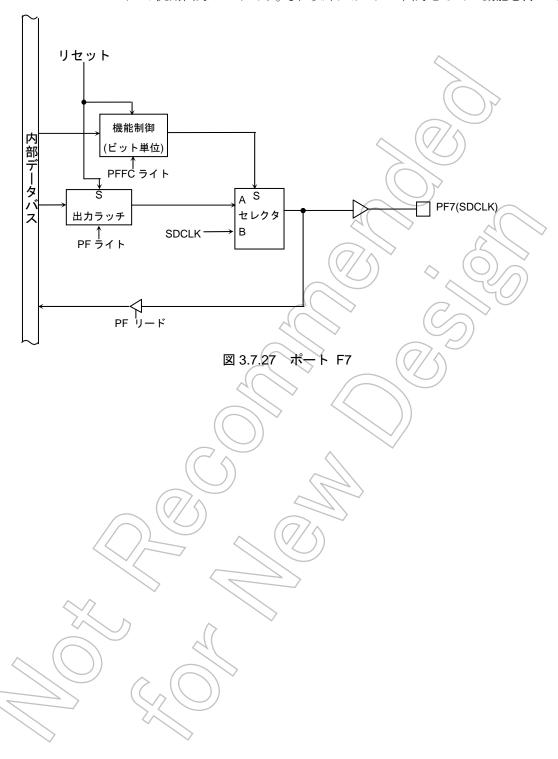

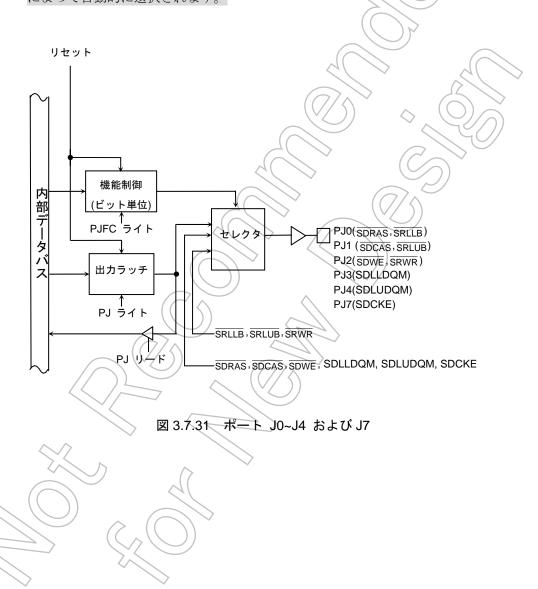

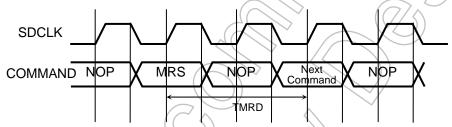

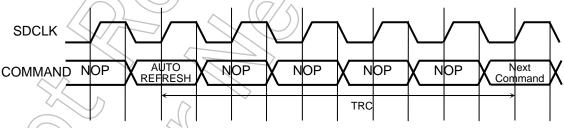

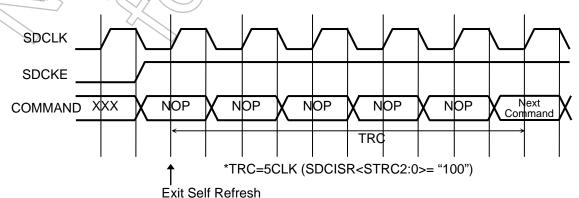

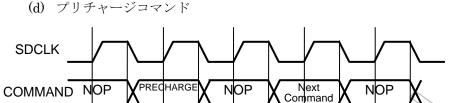

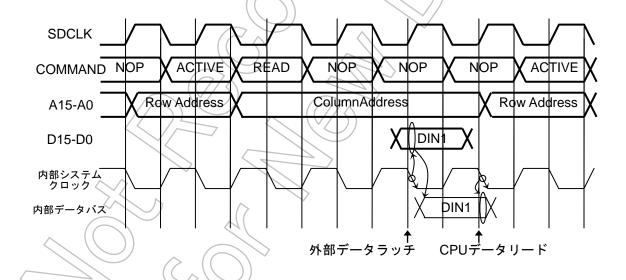

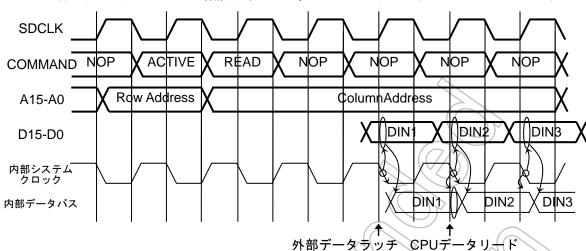

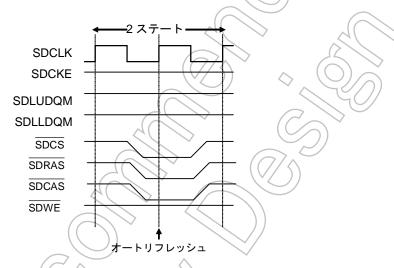

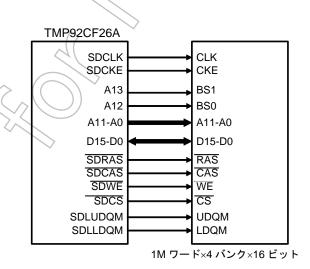

- (13) SDRAM コントローラ:1 チャネル

- 16M、64M、128M、256M および512M ビットの SDR(Single-data-rate)SDRAM に対応

- LCD表示用RAM、データRAMとしてだけでなく、SDRAMからプログラムの動作が可能

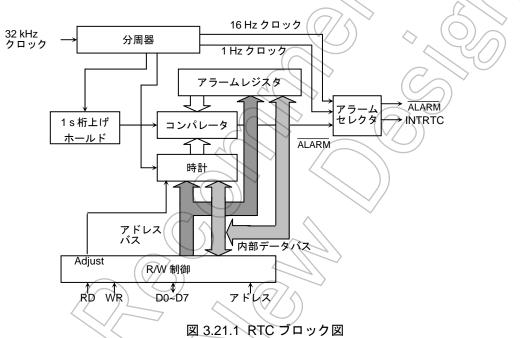

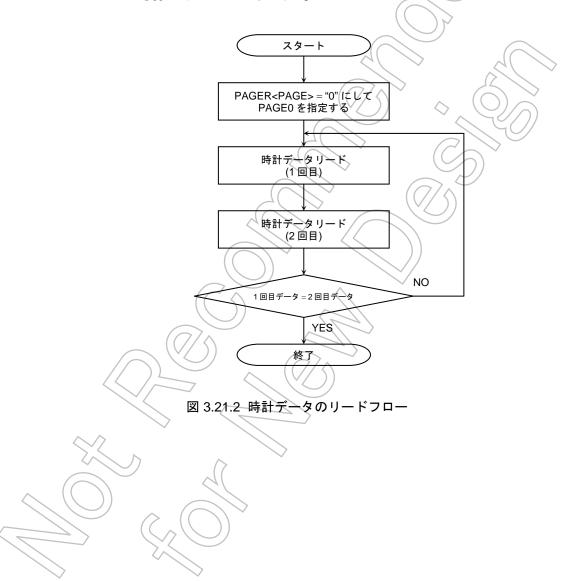

- (14) RTC(リアルタイムクロック)

- TC8521A を基本とした仕様

- (15)キーオンウェイクアップ(キー入力割込み)

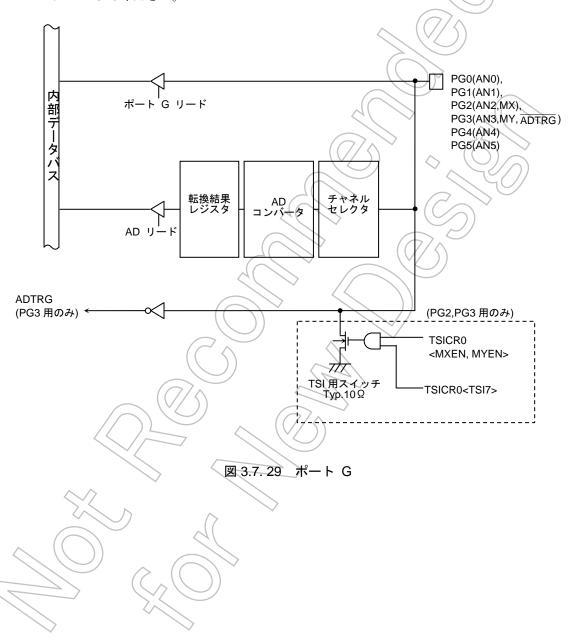

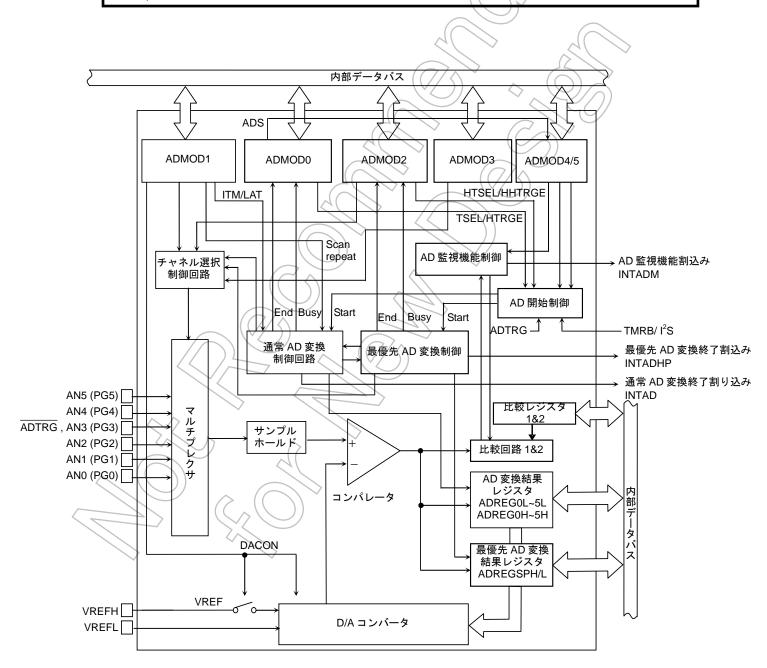

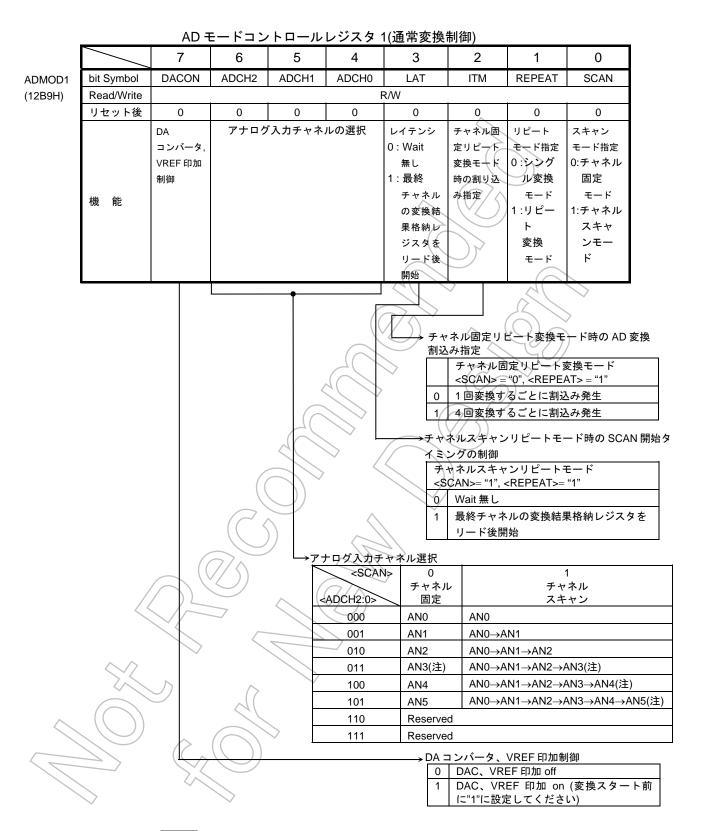

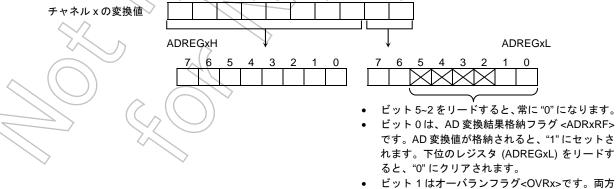

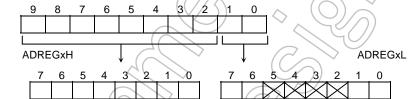

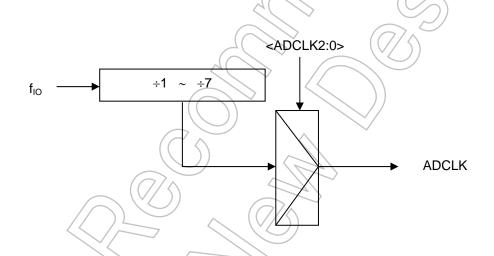

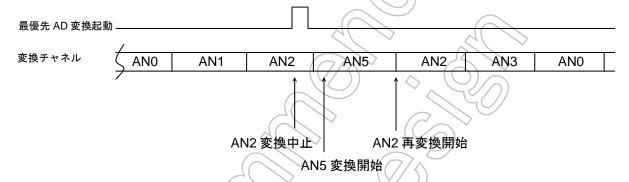

- (16)10ビットAD コンバータ (サンプルホールド回路内蔵):6チャネル

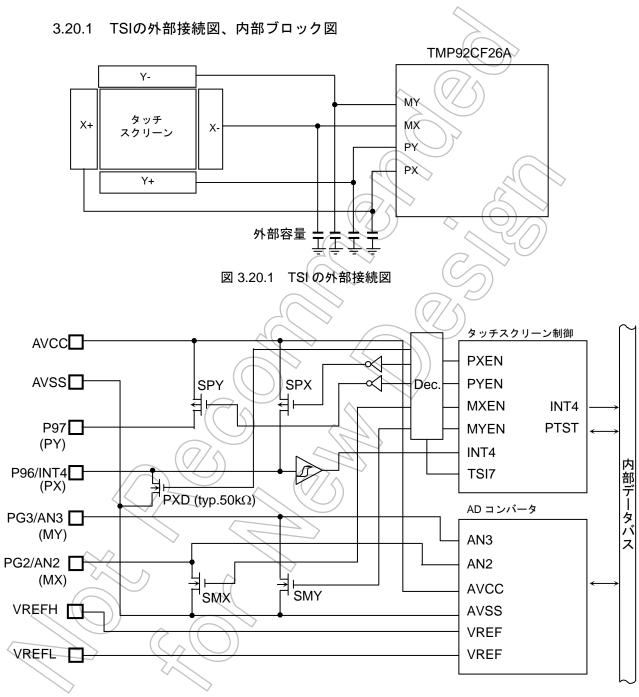

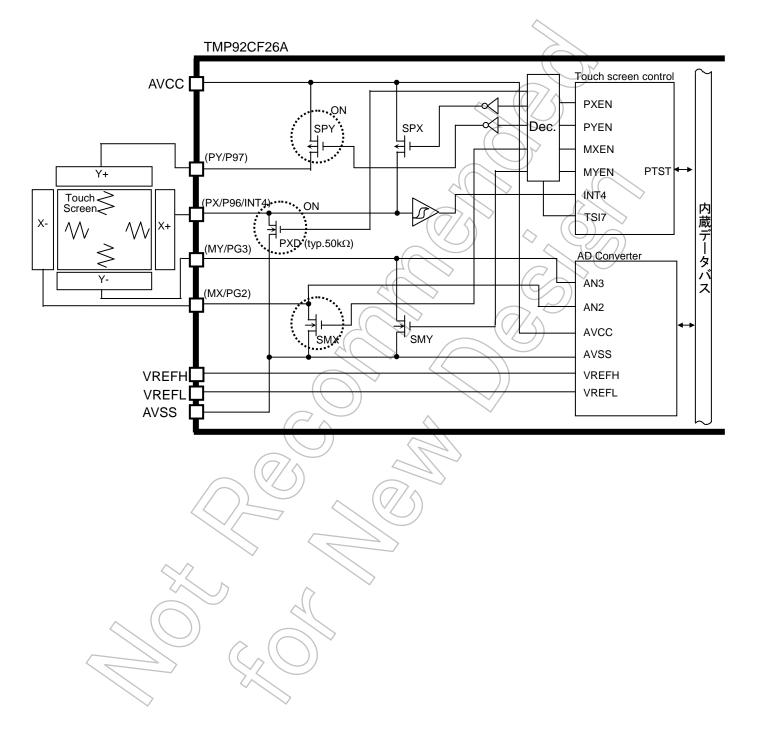

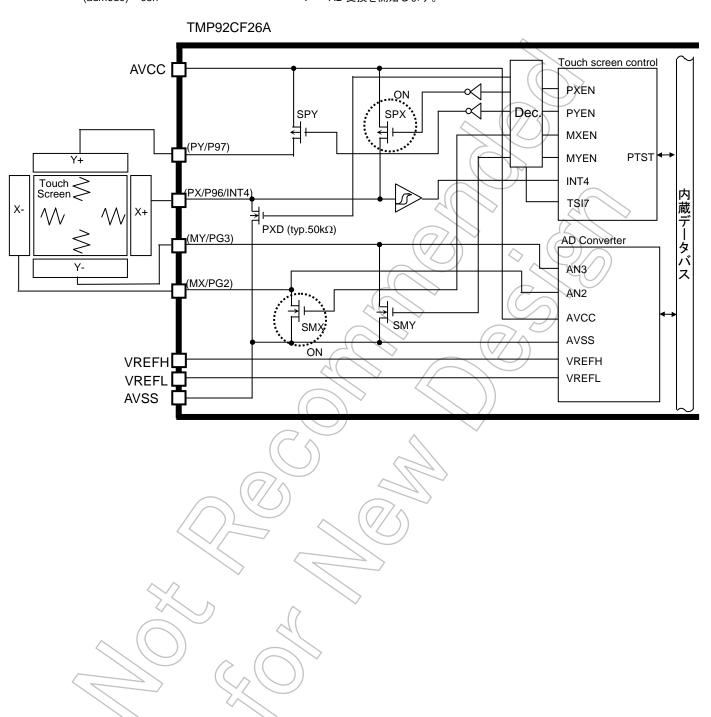

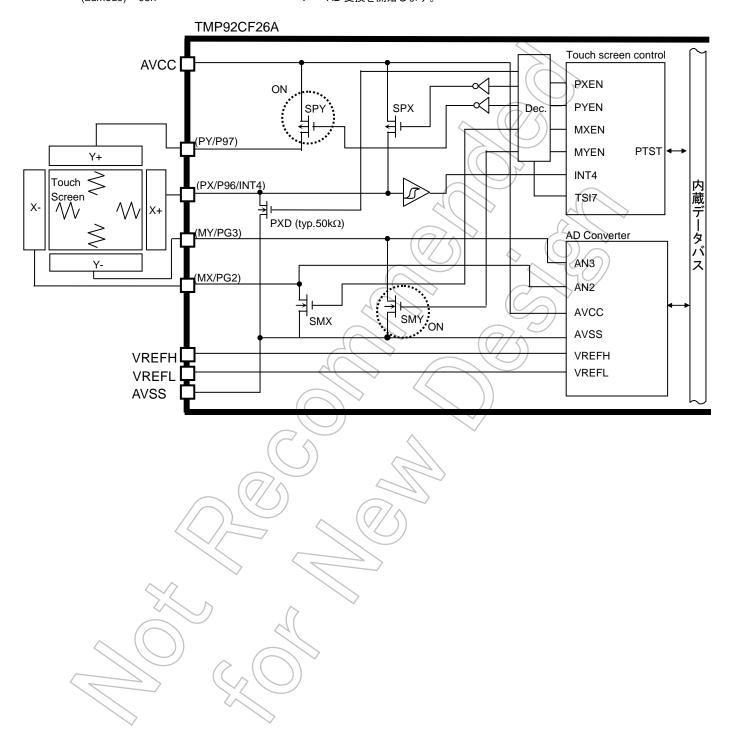

- (17) タッチスクリーンインターフェースに対応

- 低抵抗のスイッチを内蔵し、縦横切り替え用の外付け部品を削除可能

- (18) ウォッチドッグタイマ

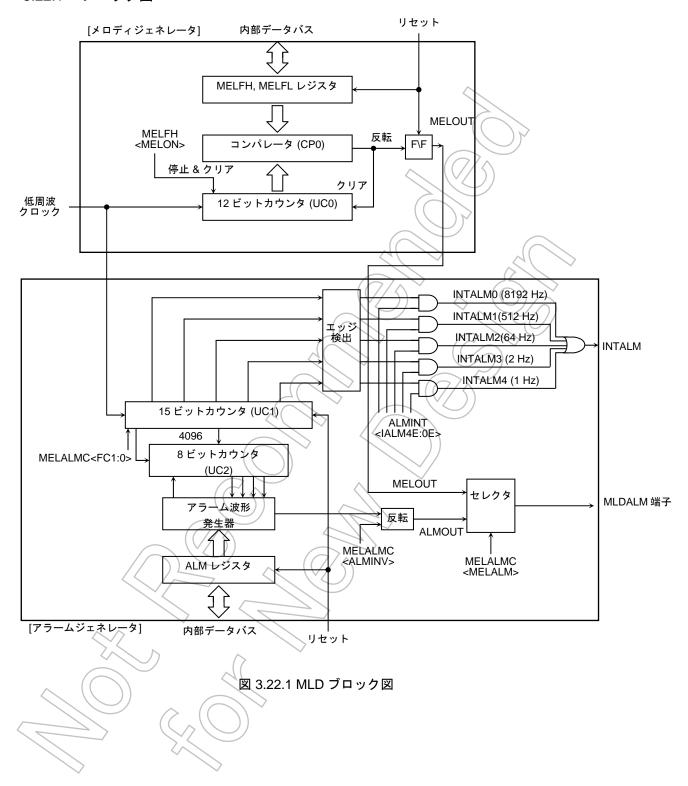

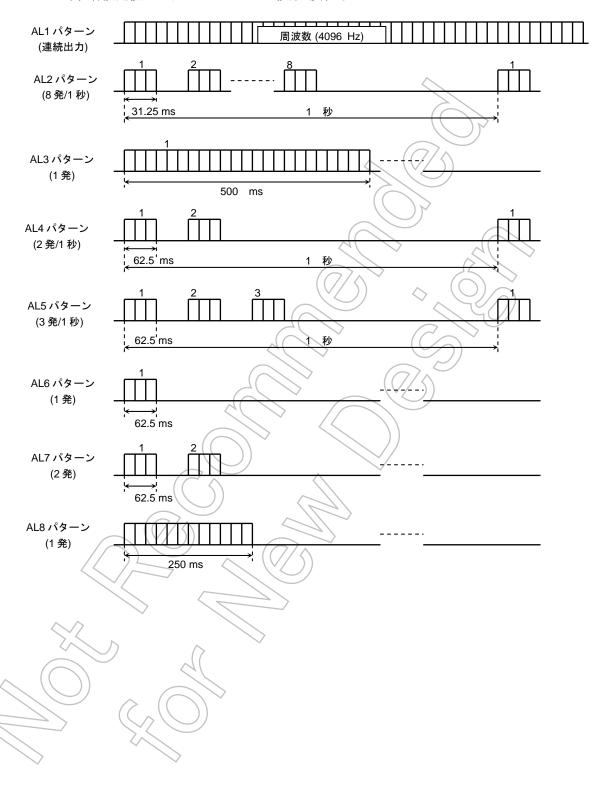

- (19) メロディアラームジェネレータ

- メロディ: 4~5461Hz のクロックを出力

- アラーム: 8 種類のアラームパターンを出力

- 5種類のインターバル割込みを出力

- (20) MMU

- 3 ローカルエリア/8 バンク方式により 3.1G バイトまで拡張可能

- 各々のローカルエリアごとにプログラム、リードデータ、ライトデータ、DMAC のソース、 デスティネーション(偶数チャネル/奇数チャネル)および LCD 表示データのバンク設定が可能

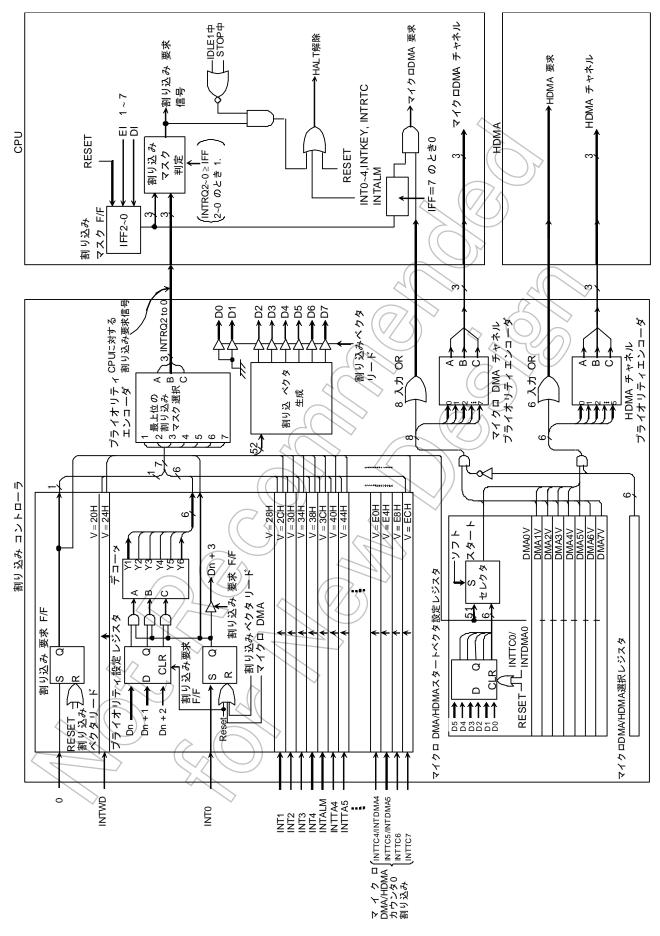

### (21)割り込み機能: 56本

• CPU 9本 …… ソフトウエア割り込み命令、未定義命令実行違反

• 内部 38本 …… 7レベルの優先順位の設定が可能

• 外部 9本 …… 7レベルの優先順位の設定が可能

(8本はエッジの極性選択可能)

### (22) DMAC 機能:6 チャネル

• マイクロ DMA 機能との切り替えによる制御で、より高速なデータ転送が可能

(23) 入出力ポート: 136 端子(データバス 16 ビット、アドレスバス 24 ビット、RD 端子を除く)

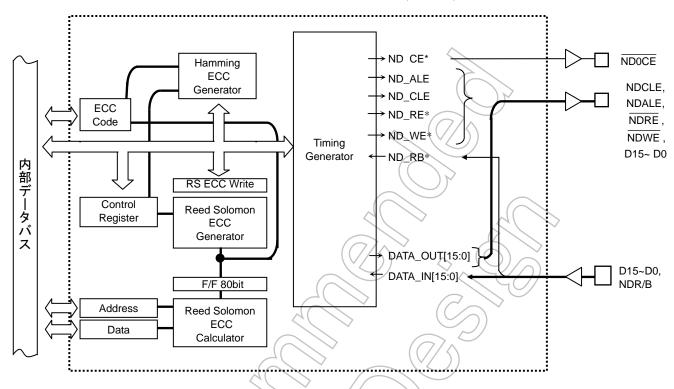

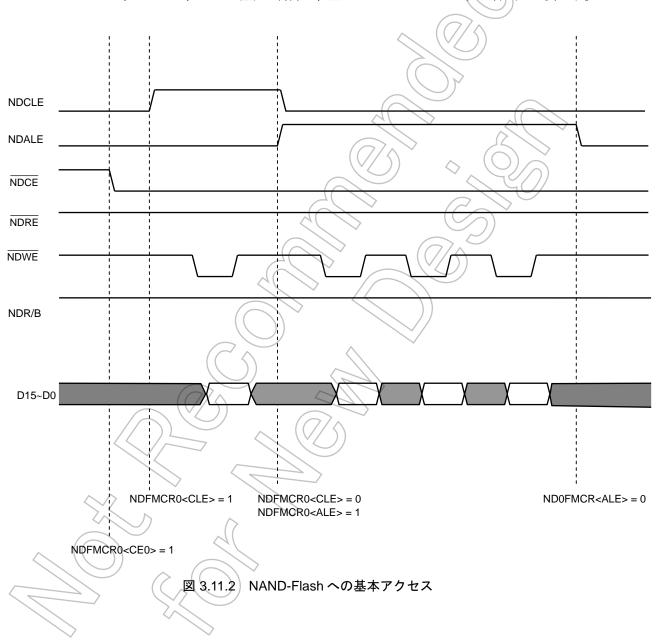

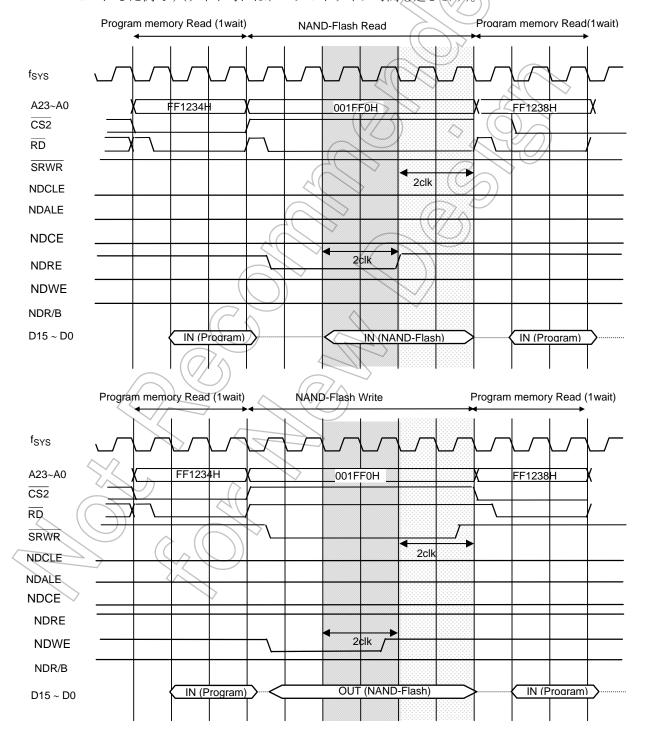

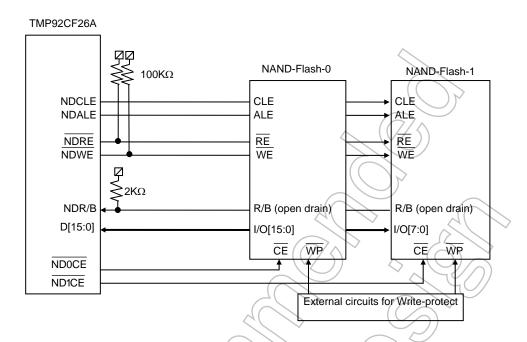

### (24) NAND - Flash メモリのインターフェース:2 チャネル

- NAND Flash メモリへの接続が容易

- SLC、MLC 両タイプに対応

- Data Bus 8/16Bit、Page Size 512/2048Byte に対応

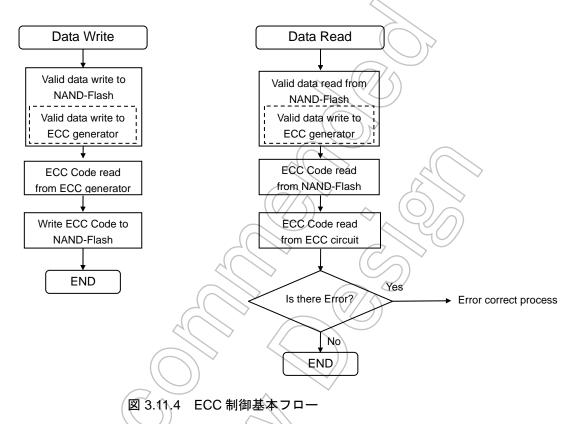

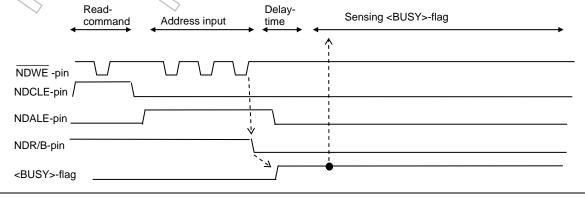

- 4-address 訂正、5-address 以上のエラー検出が可能な、Reed Solomon 演算回路内蔵

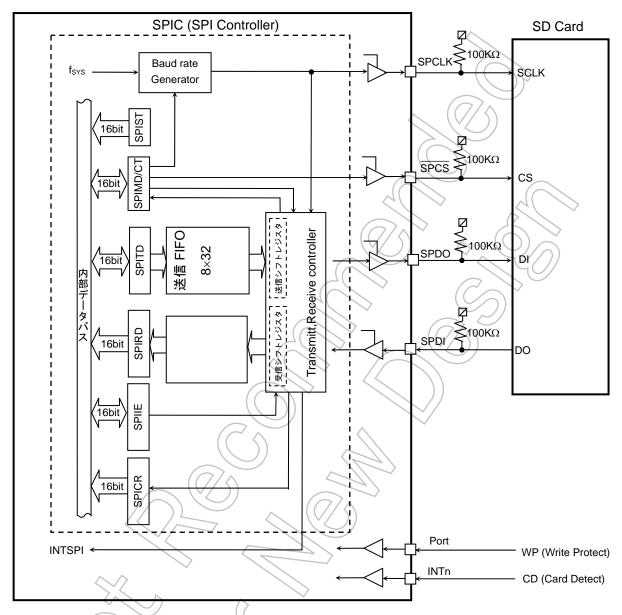

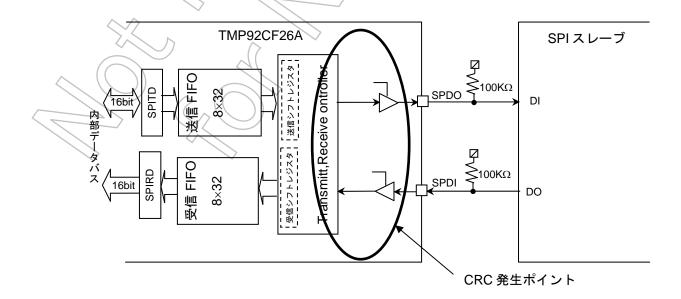

### (25) SPI コントローラ: 1 チャネル

- SD カード、および MMC カードの SPI モード対応

- 入出力に各々32 バイトの FIFO バッファを内蔵

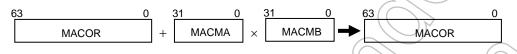

### (26) 積和演算器 (Multiply and Accumulate Calculate unit): 1 チャネル

- 3種類の演算をサポート  $64 + 32 \times 32 = 64$ ,  $64 32 \times 32 = 64$ ,  $32 \times 32 64 = 64$

- I/O 方式

- 符号付き計算対応

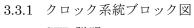

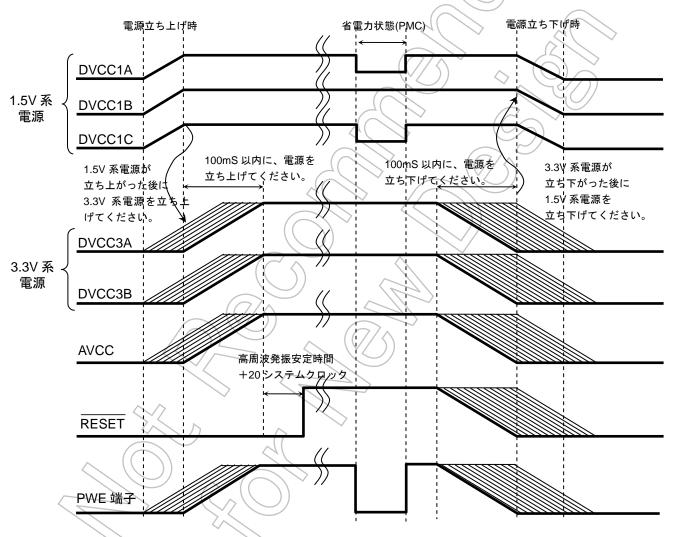

### (27) スタンバイ機能

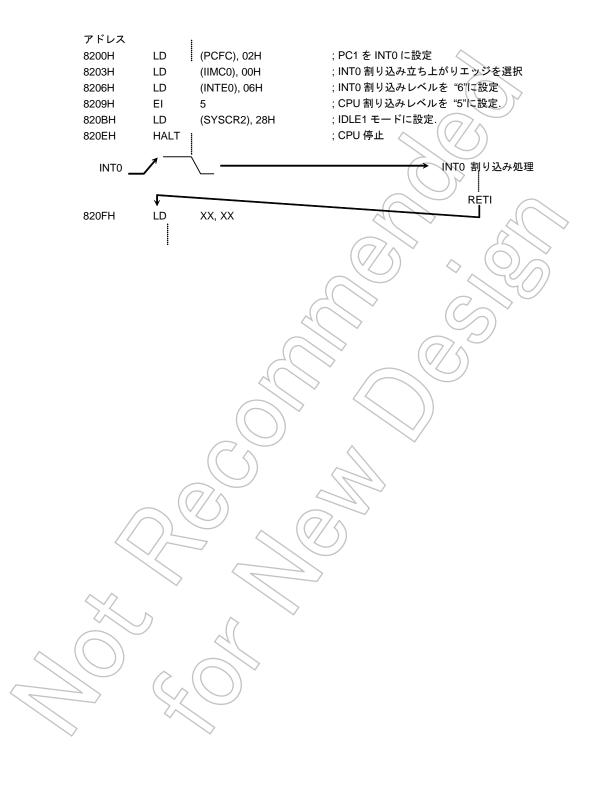

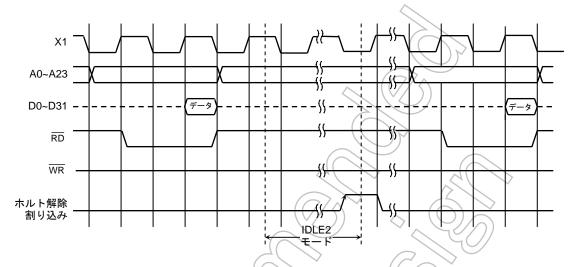

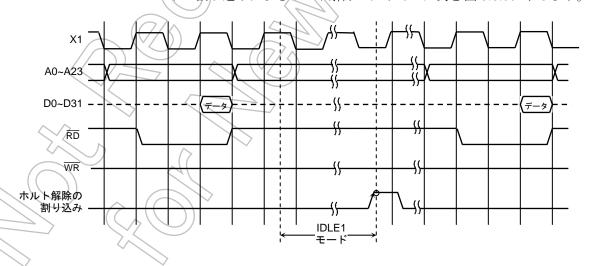

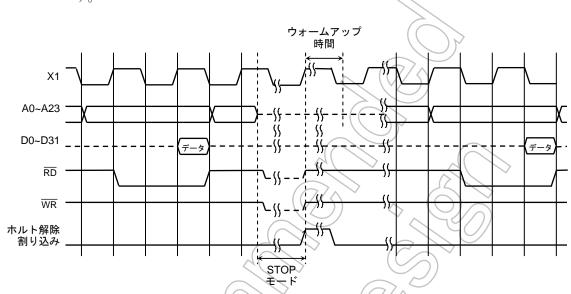

- 3種類の HALT モード …IDLE2(プログラマブル), IDLE1, STOP

- スタンバイモード時における各端子の状態をビット単位にて設定可能

- リーク(漏れ)電流を対策するための電源管理回路(PMC)を内蔵

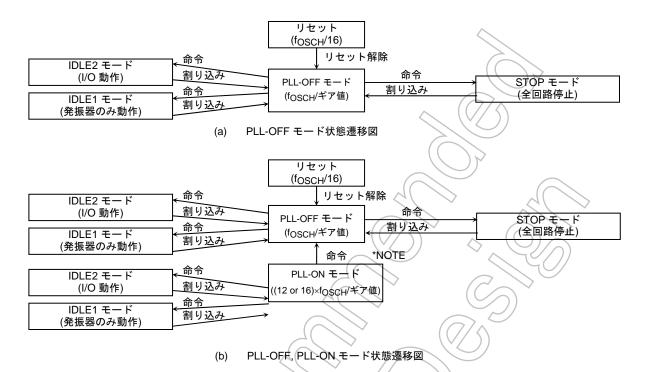

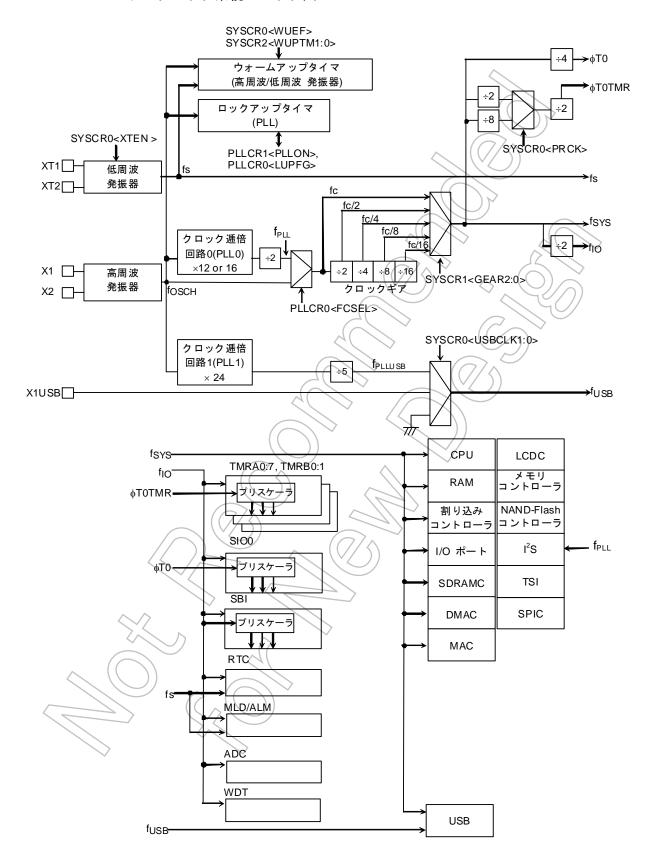

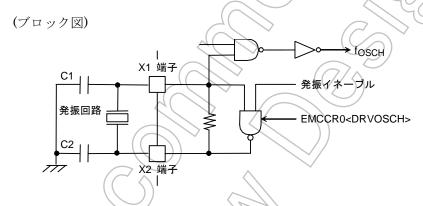

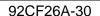

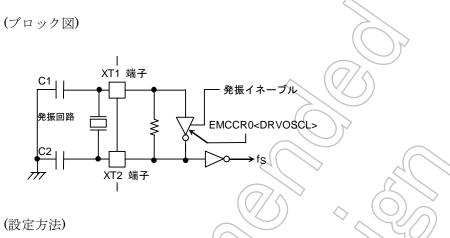

### (28) クロック制御機能

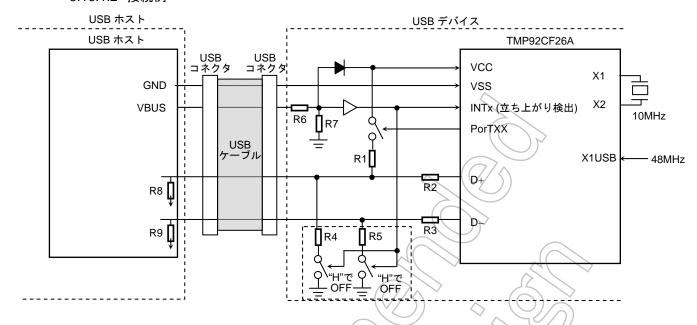

- クロック逓倍回路 (PLL) を 2 ブロック内蔵し、外付け 10MHz の発振子から USB クロック 48MHz と CPU へのクロック 80MHz の供給が可能

- クロックギア機能: 高周波クロック fc ~ fc/16 まで切り替え可能

- 時計用タロック (fs = 32.768 kHz)

## (29)動作電圧

- 內部 V<sub>CC</sub> = 1.5V、外部 I/O Vcc=3.0 ~ 3.6 V

- 2 電源対応(内部電源(1.4~1.6)、外部電源(3.0~3.6))

### (30) パッケージ

• 228 ピン FBGA: FBGA228-P-1515-0.80A5

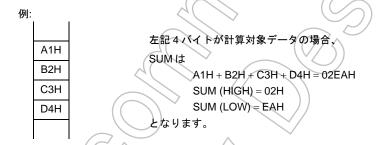

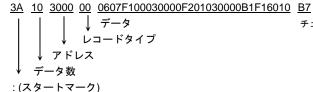

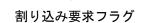

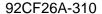

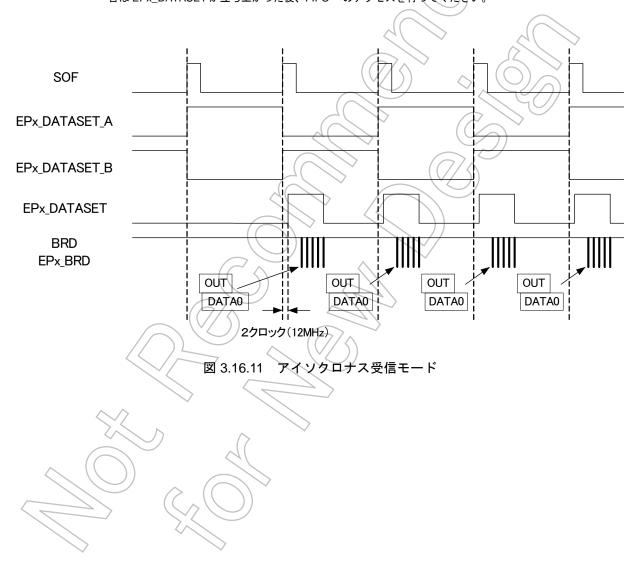

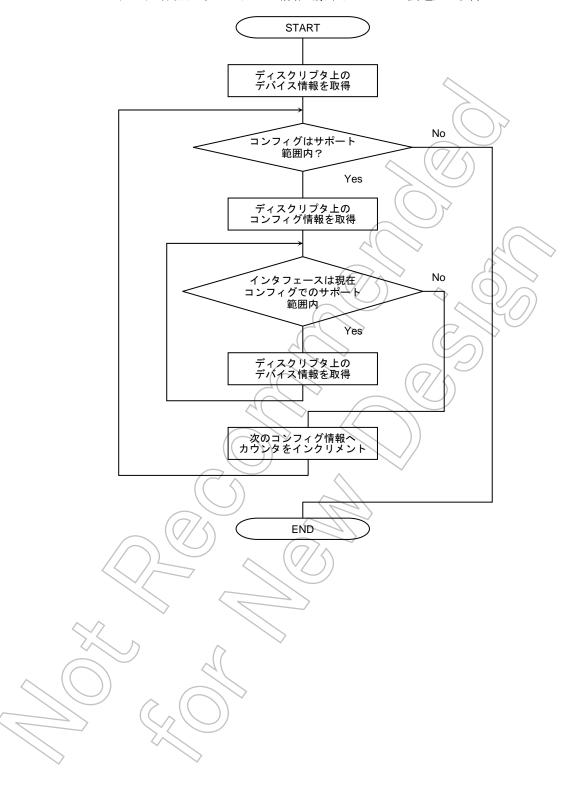

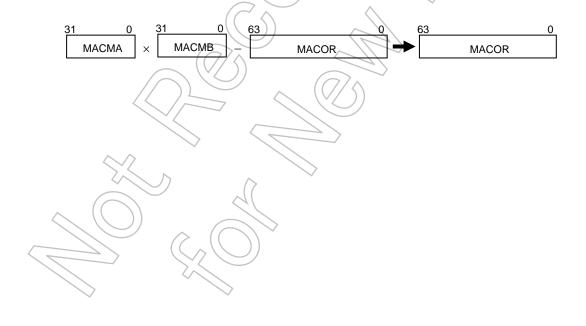

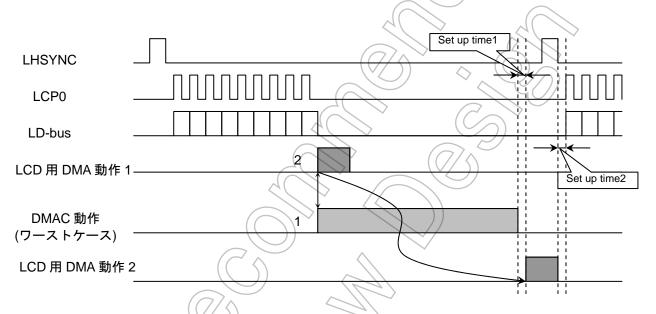

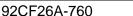

TOSHIBA TMP92CF26A **DVCC3A** [12] (AN0 to AN1)PG0 to PG1 DVCC3B [1] 10-bit 6ch (AN2, MX)PG2 DVCC1A [5] 900/H1 CPU AD (AN3, MY, ADTRG)PG3 DVCC1B[1] コンバータ (AN4 to AN5)PG4 to PG5 DVSSCOM DVCC1C [1] AVCC, AVSS PLI VREFH, VREFL W Α **XWA** X1 X2 H-OSC タッチ (PX, INT4)P96-**XBC** В C スクリーン l/F クロックギア (PY)P97 (TSI) **XDE** D Ε XT1 L-ØSC (TXD0)P90 ◄ XHL SERIAL I/O Н XT2 (RXD0)P91 RESET SIO<sub>0</sub> XIX IX (CTS0, SCLK0)P92 ◄ **DBGE** (I2S0CKO)PF0 -AM [1:0] XIY ΙY  $I^2S$ (I2S0DO)PF1 -PZ0 (EI PODDATA) (I<sup>2</sup>S0)XIZΙZ (I2S0WS)PF2 **◄** PZ1 (EI\_SYNCLK) (I2S1CKO)PF3 -PZ2 (EI\_PODREQ)  $I^2S$ XSP SP (I2S1DO)PF4 -PZ3(EI\_REFCLK) (I<sup>2</sup>S1)PZ4(EI\_TRGIN) 32bit (I2S1WS)PF5 ◄ DSU PZ5(EI\_COMRESET) (SDA)PV6 <del><</del> F SR ➤ PZ6(EO\_MCUDATA) SBI(I<sup>2</sup>Cbus) (SCL)PV7 ➤ PZ7(EO\_MCUREQ) D+ P C **USB** PM7 (PWE) >PMC Controller (X1USB) PX5 割り込み PC0 (INT0) **8BIT TIMER** WATCH-DOG TIMER (TA0IN, INT1)PC1 ◄ PC2 (INT2) (TMRA0) コントロー **8BIT TIMER** ➤ D0 to D7 (TA1OUT, MLDALM)PM1 ◀ (TMRA1) MMU PORT1 → P10 to P17 (D8 to D15) 8BIT TIMER (TA2IN, INT3)PC3 ◄ (TMRA2) → P40 to P47 (A0 to A7) PORT4 8BIT TIMER MAC (TA3OUT)PP1 ← → P50 to P57 (A8 to A15) (TMRA3) PORT5 **8BIT TIMER** P60 to P67 (A16 to A23) PORT6 (TMRA4) DMAC **8BIT TIMER** P70 (RD) (TA5OUT)PP2 ≺ (TMRA5) P73 (EA24) PORT7 P74 (EA25) **8BIT TIMER** (TMRA6)  $P75(R/\overline{W}, NDR/\overline{B})$ **8BIT TIMER** P76 (WAIT) (TA7OUT, INT5)PP3 ◄ P80 (CS0) (TMRA7) (TB0IN0, INT6)PP4<del><</del> **16BIT TIMER** P81 (CS1, SDCS) PORT8 P82 (CS2, CSZA, SDCS) (TMRB0) (TB0OUT0)PP6<del><</del> 16BIT TIMER P83 (CS3, CSXA) (TB1IN0, INT7)PP5≺ (TMRB1) P84 ( CSZB ) (TB1OUT0)PP7≺ P85 (CSZC) (SPDI)PR0 SPI P71 (WRLL, NDRE) (SPDO)PR1≺ コントロ (SPCS ) PR2≺ P72 (WRLU, NDWE) NAND-FLASH (SPCLK)PR3<del>≺</del> 144KB RAM P86 (CSZD, ND0CE) P87 (CSXB, ND1CE) I/F(2ch) (LCP0)PK0< PJ5 (NDALE) (LLOAD)PK1<del><</del> PJ6 (NDCLE) (LFR)PK2<del><</del> PA0 to PA7 (KI0 to KI7) (LVSYNC)PK3< **KEY-BOARD** ➤ PN0 to PN7 (KO0 to KO7) LCD (LHSYNC)PK4~ I/F → PC7 (KO8) (LGOE2 to 0)PK7 to 5€ コントロ ラ (LD7 to 0)PL7 to 0< **BOOT ROM 8KB** ► PM2 ( ALARM , MLDALM ) **RTC** (LD15 to 8)PT7 to 0< (LD22 to 16)PU6 to 0< MELODY/ (LD23, EO\_TRGOUT)PU7~ ALARM-OUT (CLKOUT, LDIV)PX4~ ►PV3 **PORTV →**PV4 (SDRAS, SRLLB)PJ0 (SDCAS, SRLUB)PJ1

図 1.1 TMP92CF26A ブロック図

**SDRAM**

コントローラ

(SDWE, SRWR)PJ2

(SDLLDQM)PJ3

(SDLUDQM)PJ4 <del><</del>

(SDCKE)PJ7<del><</del>

(SDCLK)PF7 <del><</del>

►PV0 (SCLK0)

PC4 (EA26)

PC5 (EA27) PC6 (EA28)

→PV1

→PV2

➤ PW7 to 0

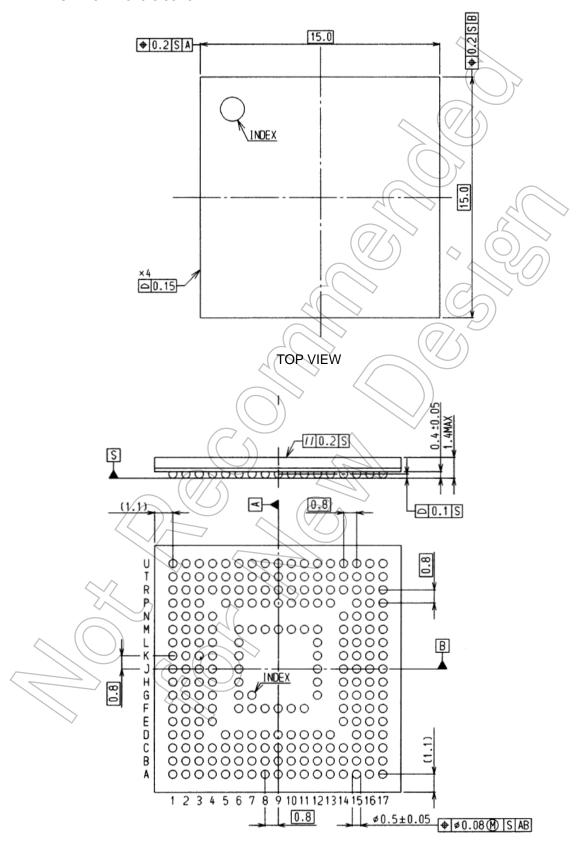

## 2. ピン配置とピン機能

TMP92CF26Aのピン配置図および入出力ピンの名称と概略機能を示します。

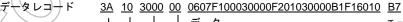

# 2.1 ピンの配置図 (Top View)

TMP92CF26Aピン配置図は、図 2.1.1のとおりです。

| A1 | A2 | А3 | A4 | A5 | A6 | A7 | A8                                      | A9    | A10          | A11 | A12 | A13      | A14 | A15  | A16 | A17 |

|----|----|----|----|----|----|----|-----------------------------------------|-------|--------------|-----|-----|----------|-----|------|-----|-----|

| B1 | B2 | ВЗ | B4 | B5 | B6 | В7 | B8                                      | В9    | B10          | B11 | B12 | B13      | B14 | B15  | B16 | B17 |

| C1 | C2 | C3 | C4 | C5 | C6 | C7 | C8                                      | C9    | C10          | C11 | C12 | C13      | Ç14 | C15  | C16 | C17 |

| D1 | D2 | D3 |    | D5 | D6 | D7 | D8                                      | D9    | D10          | D11 | D12 | D13      | ))  | D15  | D16 | D17 |

| E1 | E2 | E3 | E4 |    |    |    |                                         |       |              |     |     |          | E14 | E15  | E16 | E17 |

| F1 | F2 | F3 | F4 |    | F6 | F7 | F8                                      | F9    | F10          | F11 |     | <u> </u> | F14 | F15  | F16 | F17 |

| G1 | G2 | G3 | G4 |    | G6 | G7 |                                         |       |              |     | G12 | ~        | G14 | G15  | G16 | G17 |

| H1 | H2 | НЗ | H4 |    | H6 |    | $\overline{}$ $\bigcirc$ ( $\bigcirc$ / |       |              | H12 | 4   | H14      | H15 | H16  | H17 |     |

| J1 | J2 | J3 | J4 |    | J6 | 7  | MP9                                     | 92CI  | <b>726</b> A |     | J12 |          | J14 | J15  | J16 | J17 |

| K1 | K2 | K3 | K4 |    | K6 |    | FI                                      | BGA22 | 28           |     | K12 | (        | K14 | K15  | K16 | K17 |

| L1 | L2 | L3 | L4 |    | L6 |    | то                                      | PVIE  | ₹W           | 7   | L12 |          | L14 | 1/15 | L16 | L17 |

| M1 | M2 | МЗ | M4 |    | M6 | M7 | M8                                      | М9    | M10          | M11 | M12 | (//      | M14 | M15  | M16 | M17 |

| N1 | N2 | N3 | N4 |    |    | <  | 4(                                      |       |              |     |     |          | N14 | N15  | N16 | N17 |

| P1 | P2 | P3 |    | P5 | P6 | P7 | P8                                      | P9    | P10          | P11 | P12 | P13      |     | P15  | P16 | P17 |

| R1 | R2 | R3 | R4 | R5 | R6 | R7 | R8                                      | R9    | R10          | R11 | R12 | /R13     | R14 | R15  | R16 | R17 |

| T1 | T2 | Т3 | T4 | T5 | T6 | TŻ | T8                                      | Т9    | T10          | T11 | T12 | T13      | T14 | T15  | T16 | T17 |

| U1 | U2 | U3 | U4 | U5 | U6 | U7 | U8                                      | U9    | U10          | U11 | U12 | U13      | U14 | U15  | U16 | U17 |

図 2.1.1 ピン配置図 (FBGA228)

本 BGA パッケージにおける、最外周の 4 隅の Ball(A1,A17,U1,U17)は Dummy Ball です。内部の LSI チップとは電気的に接続されていません。

A1 と U1、A17 と U17 がパッケージの内部でショートされています。本製品を、お客様のターゲット基板への実装する際に実装の OPEN チェックに利用することを推奨いたします。

例) ターゲット基板上で U1 と U17 をショートしておき、A1 から信号(または電圧)を印加し、A17 の電圧を確認すれば、A1-U1-U17-A17 を経由した信号(または電圧)を確認することが出来ます。

表 2.1.1ピン番号とピン名称

| Ball<br>No. | ピン名称                 | Ball<br>No. | ピン名称               | Ball<br>No. | ピン名称               | Ball<br>No. | ピン名称            |

|-------------|----------------------|-------------|--------------------|-------------|--------------------|-------------|-----------------|

| A1          | Dummy1               | D9          | P73,EA24           | J15         | PT5,LD13           | P15         | PK4,LHSYNC      |

| A2          | PG2,AN2, MX          | D10         | PF4,I2S1DO         | J16         | P47,A7             | P16         | P13,D11         |

| А3          | PA6,KI6              | D11         | PF7,SDCLK          | J17         | P46,A6             | P17         | P14,D12         |

| A4          | PA5,KI5              | D12         | PJ4,SDLUDQM        | K1          | PN3,KO3            | R1          | X2              |

| A5          | PA3,KI3              | D13         | P85, CSZC          | K2          | PN4,KO4            | R2          | PC7,KO8         |

| A6          | PA1,KI1              | D15         | PU6,LD22           | K3          | PN5,KO5            | R3          | PC3,INT3,TA2IN  |

| A7          | DVCC1A5              | D16         | P61,A17            | K4          | PN6,KO6            | R4          | PX5,X1USB       |

| A8          | PF1,I2S0DO           | D17         | P60,A16            | K6          | DVCC3A2            | R5          | PP7,TB1OUT0     |

| A9          | PJ6,NDCLE            | E1          | P96,PX,INT4        | K12         | DVCC3A7 (V/)       | R6          | PP1,TA3OUT      |

| A10         | PJ1, SDCAS, SRLUB    | E2          | PW1                | K14         | PT4,LD12           | R7          | PP3,INT5,TA7OUT |

| A11         | P87, CSXB, ND1CE     | E3          | PW2                | K15         | PT3,LD11           | R8          | PP5,INT7,TB1IN0 |

| A12         | P83, CS3, CSXA       | E4          | PW3                | K16         | P45,A5             | R9          | PR2, SPCS       |

| A13         | P81, CS1, SDCS       | E14         | PU7,LD23,EO_TRGOUT | K17         | P44,A4             | R10         | PX7             |

| A14         | P72, WRLU, NDWE      | E15         | PU4,LD20           | L1          | PK2,LFR            | R11         | PZ0,EI_PODDATA  |

| A15         | P70, RD              | E16         | P57,A15            | L2          | PN7,KO7            | R12         | PZ2,EI_PODREQ   |

| A16         | P65,A21              | E17         | P56,A14            | L3          | PM1,MLDALM,TA1OUT  | R13         | PZ4,EI_TRGIN    |

| A17         | Dummy3               | F1          | DVCC1B1            | L4 (        | PM7,PWE            | R14         | PZ6,EO_MCUDATA  |

| B1          | VREFH                | F2          | PW6                | L6          | DVSS3              | R15         | PZ7,EO_MCUREQ   |

| B2          | PG5,AN5              | F3          | PW5                | L12         | DVSS7              | R16         | P15,D13         |

| В3          | PG3,AN3,MY, ADTRG    | F4          | PW4                | _L(14       | PT2,LD10           | R17         | DVCC1A3         |

| B4          | PA7,KI7              | F6          | DVCC3A12           | 115         | PT1,LD9            | T1          | X1              |

| B5          | PA2,KI2              | F7          | DVCC3A11           | L16         | P43,A3             | ) T2        | AM0             |

| B6          | PA0,KI0              | F8          | DVSS11             | L17.        | P42,A2             | /T3         | AM1             |

| B7          | PF2,I2S0WS           | F9          | DVCC3A10           | M1          | PK3,LVSYNC         | T4          | PP6,TB0OUT0     |

| B8          | PF0,I2S0CKO          | F10         | DVSS10             | M2          | PC0,INT0           | T5          | PL0,LD0         |

| B9          | PJ5,NDALE            | F11         | DVCC3A9            | M3          | PM2, ALARM, MLDALM | T6          | PL2,LD2         |

| B10         | PJ2, SDWE , SRWR     | F14         | PU5,LD21           | M4          | P90,TXD0           | T7          | PL4,LD4         |

| B11         | PJ0, SDRAS, SRLLB    | F15         | PU2,LD18           | M6          | DVCC3A3            | Т8          | PL5,LD5         |

| B12         | P86. CSZD, ND0CE     | F16         | P55,A13            | M7          | DVSS4              | T9          | PR1,SPDO        |

| B13         | P82, CS2, CSZA, SDCS | F17         | P54,A12            | M8          | DVCC3A4            | T10         | PL6,LD6         |

| B14         | P75,R/W,NDR/B        | G1          | DVCC3B1            | M9          | DVSS5              | T11         | PK1,LLOAD       |

| B15         | P71, WRLL, NDRE      | G2          | PW7                | M10         | DVCC3A5            | T12         | D0              |

| B16         | P64,A20              | G3 /        | PV0, SCLK0         | M11         | DVSS6              | T13         | D2              |

| B17         | DVCC1A4              | G4 (        | PV1                | M12         | DVCC3A6            | T14         | D4              |

| C1          | AVCC                 | G6          | DVSS1              | M14         | PK7,LGOE2          | T15         | D6              |

| C2          | VREFL                | G7          | DVSS12             | M15         | PT0,LD8            | T16         | P11,D9          |

| C3          | PG4,AN4              | G12         | DVSS9              | M16         | P41,A1             | T17         | P12,D10         |

|             |                      | /           | PU3,LD19           |             | P40,A0             |             | Dummy2          |

| C4<br>C5    | PG1,AN1<br>PA4,KI4   | G14<br>G15  | PU0,LD16           | M17<br>> N1 | DVCC1A1            | U1<br>U2    | RESET           |

| C6          | PC5,EA27             | G16         | P53,A11            | N2          | PC1,INT1,TA0IN     | U3          | D+              |

| C7          | P76, WAIT            | G17         | P52,A10            | N3          | P91,RXD0           | U4          | D-              |

| C8          | PF5,I2S1WS           | H1          | PV7,SCL            | N4          | DVSS1C             | U5          | DVCC1A2         |

| C9          | PF3,I2S1CKO          | H2          | PV6,SDA            | N14         | PK6,LGOE1          | U6          | PL1,LD1         |

| C10         | PJ7,SDCKE            | H3          | PV3                | N15         | PK5,LGOE0          | U7          | PL3,LD3         |

| C11         | PJ3,SDLLDQM          | H4          | PV2                | N16         | P17,D15            | U8          | XT1             |

| C12         | P84, CSZB            | / ₩6        | DVCC3A1            | N17         | P16,D14            | U9          | XT2             |

| C12         | P80, CS0             | H12         | DVCC3A8            | P1          | DVCC1C             | U10         | PL7, LD7        |

| C14         | P67,A23              | H14         | PU1,LD17           | P2          | PC2,INT2           | U11         | PK0,LCP0        |

| C15         | P66,A22              | H15         | PT7,LD15           | P3          | P92,SCLK0, CTS0    | U12         | D1              |

| C16         | P63,A19              | H16         | P51,A9             | P5          | PX4,CLKOUT, LDIV   | U13         | D3              |

| C17         | P62,A18              | H17         | P50,A8             | P6          | PP2,TA5OUT         | U14         | D5              |

| D1          | P97,PY               | J1          | PN2,KO2            | P7          | PP4,INT6,TB0IN0    | U15         | D7              |

| D2          | AVSS                 | J2          | PN1,KO1            | P8          | PR0,SPDI           | U16         | P10,D8          |

| D3          | PW0                  | J3          | PN0,KO0            | P9          | PR3,SPCLK          | U17         | Dummy4          |

| D5          | PG0,AN0              | J4          | PV4                | P10         | DBGE               | 017         | - willing 1     |

| D6          | PC6,EA28             | J6          | DVSS2              | P11         | PZ1,EI_SYNCLK      |             |                 |

| D7          | PC4,EA26             | J12         | DVSS8              | P12         | PZ3,EI_REFCLK      |             |                 |

| D8          | P74,EA25             | J14         | PT6,LD14           | P13         | PZ5,EI_COMRESET    |             |                 |

| 00          | 1 1 T,L/1LU          | UIT         | 1 10,0017          | 1 10        | · 20,EI_OOWINEOET  |             |                 |

注 1) P96,P97,PG0~PG5 は AVCC 電源で動作します。

92CF26A-6

注 2) PW0~PW7 および PV0~PV7 は DVCC3B 電源で動作します。

注 3) X1 および X2 は DVCC1C 電源で動作します。

# 2.2 ピン名称と機能

入出力ピンの名称と機能は次のとおりです。

表 2.2.1ピン名称と機能(1/6)

| ピン名称             | ピン数    | 入出力     | 機能                                             |

|------------------|--------|---------|------------------------------------------------|

| D0 ~ D7          | 8      | 入出力     | データ: データバス D0~D7                               |

| P10 ~ P17        |        | 入出力     | ポート 1: ビット単位で入出力の設定可能な入出力ポート                   |

| D8 ~ D15         | 8      | 入出力     | データ: データバス D8~D15                              |

| P40 ~ P47        |        | 出力      | ポート 4: 出力ポート                                   |

| A0 ~ A7          | 8      | 出力      | アドレス: アドレスバス A0~A7                             |

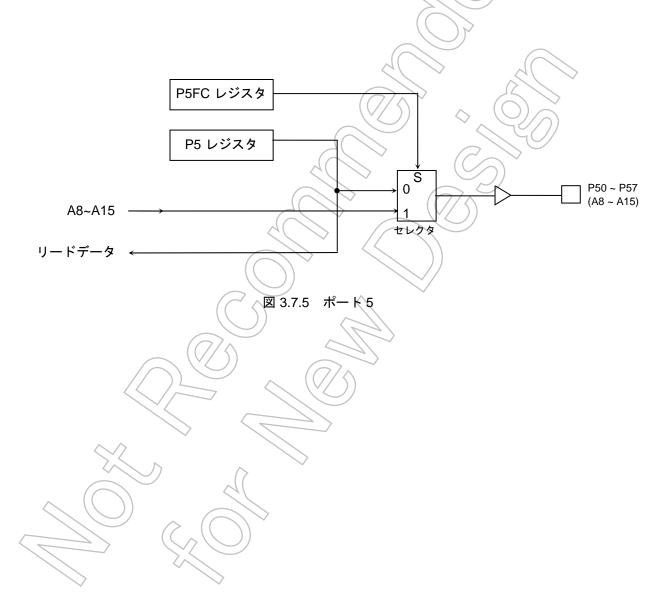

| P50 ~ P57        |        | 出力      | ポート 5: 出力ポート                                   |

| A8 ~ A15         | 8      | 出力      | アドレス: アドレスバス A8~A15                            |

| P60 ~P67         |        | 入出力     | ポート 6: ビット単位で入出力の設定可能な入出力ポート                   |

| A16 ~ A23        | 8      | 出力      | アドレス: アドレスバス A16~A23                           |

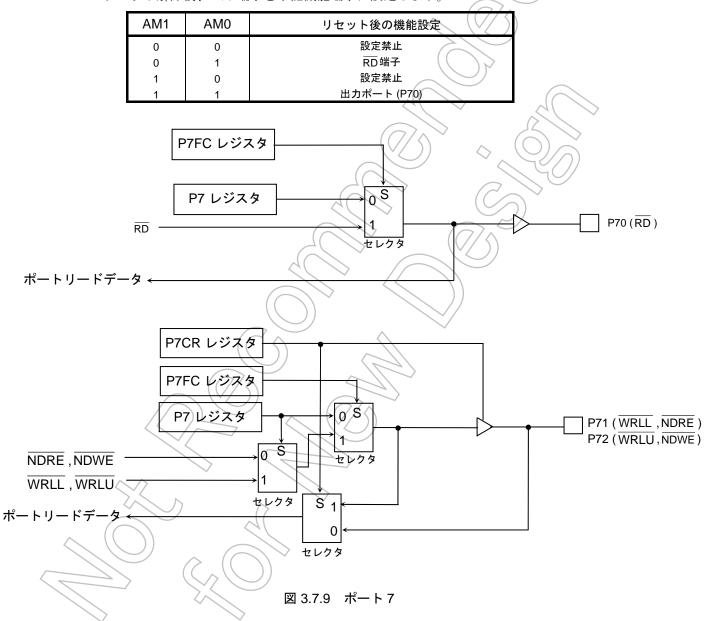

| P70              | 4      | 出力      | ポート 70:出力ポート                                   |

| RD               | 1      | 出力      | リード: 外部メモリをリードするためのストローブ信号                     |

| P71              |        | 入出力     | ポート 71:入出力ポート                                  |

| WRLL             | 1      | 出力      | ライト: D0~D7 端子のデータをライトするためのストローブ信号              |

| NDRE             |        | 出力      | NAND-Flash リード: 外部 NAND-Flash をリードするためのストローブ信号 |

| P72              |        | 入出力     | ポート 72: 入出力ポート                                 |

| WRLU             | 1      | 出力      | 上位ライト: D8~D15 端子のデータをライトするためのストローブ信号           |

| NDWE             |        | 出力      | NAND-Flash 用ライトイネーブル                           |

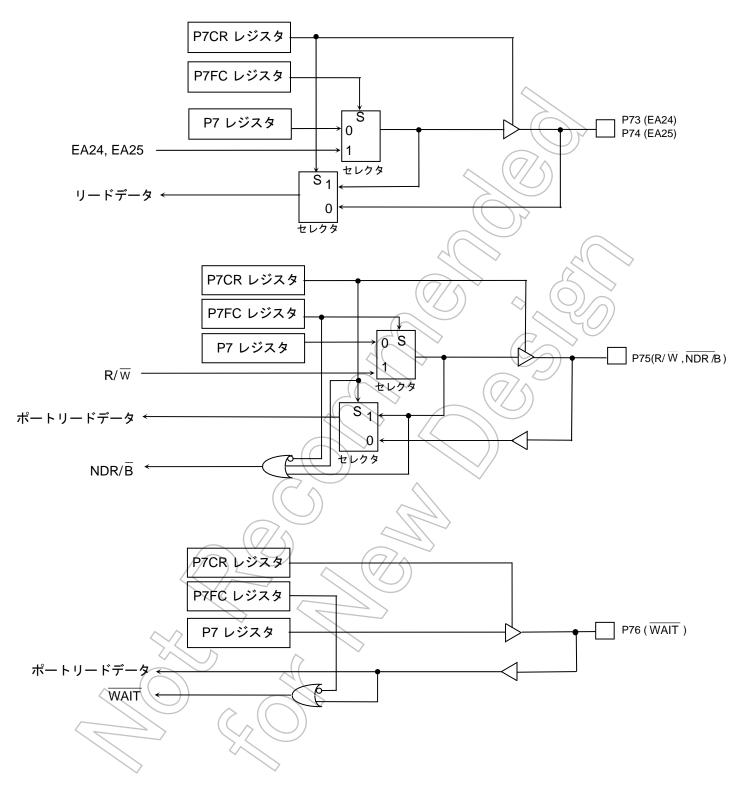

| P73              | 1      | 入出力     | ポート 73: 入出力ポート                                 |

| EA24             | ļ      | 出力      | 拡張用アドレス EA24                                   |

| P74              | 1      | 入出力     | ポート 74: 入出力ポート                                 |

| EA25             | '      | 出力      | 拡張用アドレス EA25                                   |

| P75              |        | 入出力     | ポート 75: 入出力ポート                                 |

| $R/\overline{W}$ | 1      | 出力      | リード/ライト: 1 はリード,ダミーサイクルを、0 はライトサイクルを表す         |

| NDR/B            |        | 入力      | NAND-Flash Ready(1)/Busy(0)入力                  |

| P76              | 1      | 入出力     | ポート76: 入出力 ポート                                 |

| WAIT             | ļ      | 入力      | ウエイト:バスウェイトの要求入力.                              |

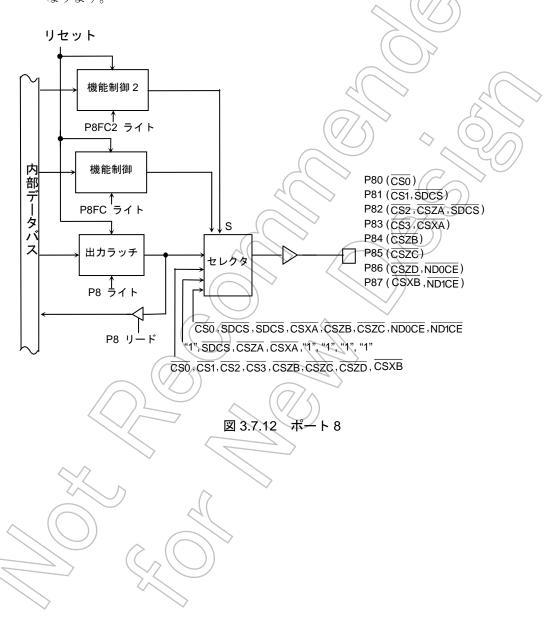

| P80              | 1      | 出力      | ポート80:出力ポート                                    |

| CS0              | '      | 出力      | チップセレクト 0: アドレスが指定したアドレス領域内なら"Low"を出力          |

| P81              |        | 出力      | ポート/81: 出力ポート                                  |

| CS1              | 1 /    | // 出力 ― | チップセレクト 1: アドレスが指定したアドレス領域内なら"Low"を出力          |

| SDCS             |        | 出力      | SDRAM チップセレクト: アドレスが SDRAM アドレス領域内なら "0" を出力   |

| P82              |        | 出力      | ポート 82: 出力ポート                                  |

| CS2              | 1      | 出力      | チップセレクト 2: アドレスが指定したアドレス領域内なら "Low" を出力        |

| CSZA             |        | 出力      | 拡張チップセレクト ZA: アドレスが特定のアドレス領域内なら "0" を出力        |

| SDCS             |        | 出力      | SDRAM チップセレグト: アドレスが SDRAM アドレス領域内なら "0" を出力   |

| P83              |        | 出力      | ポート 83:出力ポート                                   |

| CS3              | ((1)   | 出力      | チップセレクト 3: アドレスが指定したアドレス領域内なら "Low" を出力        |

| CSXA             |        | 出力      | 拡張チップセレクト XA: アドレスが特定のアドレス領域内なら "0" を出力        |

| P84              |        | 出力      | ポート 84: 出力ポート                                  |

| CSZB             |        | 出为      | ' 拡張チップセレクト ZB: アドレスが特定のアドレス領域内なら "0" を出力      |

| P85              | 1      | 出力〈/    | ポート 85: 出力ポート                                  |

| CSZC             | $\vee$ | 出力      | 拡張チップセレクト ZC: アドレスが特定のアドレス領域内なら "0" を出力        |

92CF26A-7

表 2.2.1 ピン名称と機能(2/6)

| P86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ピン名称    | ピン数  | 入出力      | 機能                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|----------|--------------------------------------------------|

| NAND-Flash0 チップセレクト: NAND-Flash0 が許可されるとき"0"を出力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P86     |      | 出力       | ポート 86: 出力ポート                                    |

| P87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CSZD    | 1    | 出力       | 拡張チップセレクト ZD: アドレスが特定のアドレス領域内なら "0" を出力          |

| SSNB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ND0CE   |      | 出力       | NAND-Flash0 チップセレクト : NAND-Flash0 が許可されるとき"0"を出力 |

| NAND-Flash1 チップセレクト: NAND-Flash1 が許可されるときでを出力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P87     |      | 出力       | ポート 87: 出力ポート                                    |

| P90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CSXB    | 1    | 出力       | 拡張チップセレクト XB: アドレスが特定のアドレス領域内なら "0" を出力          |

| TXDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ND1CE   |      | 出力       |                                                  |

| TXDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P90     | 1    | 入出力      | ポート 90: 入出力ポート                                   |

| RXDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TXD0    | Į.   | 出力       | シリアル 0 送信 データ: プログラマブルオープンドレイン 出力                |

| RXDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P91     | 1    | 入出力      | ポート 91: 入出力ポート (シュミット入力)                         |

| SCLK0<br>CTS0         1         入出力<br>シリアル0ラータ 送信可能(送信 クリア)           P96<br>INT4         1         入力<br>大力<br>別り込み要求端子 4:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子<br>とブラス: タッチスクリーンパネル用 X+ 接続端子           P87<br>P97<br>P1         1         入力<br>ボート 97: 入力ポート<br>(シュミット入力)           PY<br>PA0-PA7<br>KI0-KI7         8         入力<br>オート A0-A7 ボート 入力 ボート専門端子<br>(シュミット入力)           PC0<br>INT0         1         入力<br>オート C0: 入出力ボート<br>入力<br>割り込み要求端子 0:レベル/立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子<br>(シュミット入力)           PC1<br>INT1         1         入力<br>カカ<br>タイマ入力: 8 ピットタイマ 0の入力端子<br>トラスク 2、入出力ボート<br>シュミット入力)           PC2<br>A出力<br>INT2         1         入力<br>カカ<br>タイマ入力: 8 ピットタイマ 0の入力端子<br>トラスク 2、入出力ボート<br>シュミット入力)           PC3<br>INT3         1         入力<br>カカ<br>カカ<br>カカ         大ート C3: 入出力ボート<br>シュミット入力)           INT3<br>INT3         1         入力<br>カカ<br>カイマ入力: 8 ピットタイマ2の入力端子<br>トライマ入力: 8 ピットタイマ2の入力端子<br>トライマ入力: 8 ピットタイマ2の入力端子<br>トライマ入力: 8 ピットタイマ2の入力端子<br>トライマスカ: 8 ピットタイマ2の入力端子<br>・ボート C6: 入出力ボート<br>は張用アドレス EA26<br>カ 出力<br>ボート C6: 入出力ボート<br>は張用アドレス EA28           PC6<br>EA27         1         出力<br>ボート C6: 入出力ボート<br>は張用アドレス EA28<br>カ 出現 ボート C7: 入出力ボート           PC7         1         入力<br>ボート C7: 入出力ボート                                                                                                                                                                                                                                                                                                                                                                                                                                         | RXD0    | Į.   | 入力       | シリアル 0 受信 データ                                    |

| CTSO   入力   シリアル 0 データ 送信可能 (送信 グリア)     P96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P92     |      | 入出力      | ポート 92: 入出力ポート (シュミット入力)                         |

| P96         1         入力         ボート 96: 入力ポート         (シュミット入力, ブルダウン抵抗付き)           INT4         入力         割り込み要求端子 4:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子           P97         1         入力         ボート 97: 入力ポート         (シュミット入力)           P97         1         入力         ボート 97: 入力ポート         (シュミット入力)           PY・プラス: タッチスクリーンパネル用 Y+ 接続端子         ボート A0-A7 ボート 入力 ボート 接続端子           PA0-PA7         A)         ボート A0-A7 ボート 入力 ボート 接続端子           PC0         1         入出力         ボート C0: 入出力ボート         (シュミット入力)           INT0         1         入力         割り込み要求端子 0: ンペル/立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子           PC1         入出力         ボート C1: 入出力ボート         (シュミット入力)           INT1         1         入力         割り込み要求端子 1:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子           PC2         1         入出力         ボート C2: 入出力ボート         (シュミット入力)           INT2         1         入力         割り込み要求端子 2:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子           PC3         入出力         ボート C3: 入出力ボート         (シュミット入力)           INT3         1         入力         割り込み要求端子 2:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子           PC4         1         出力         ボート C3: 入出力ボート           BA26         1         出力         ボート C6: 入出カボー                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SCLK0   | 1    |          |                                                  |

| INT4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CTS0    |      | 入力       |                                                  |

| PX         出力         X.プラス: タッチスクリーンパネル用 X+ 接続端子           P97         1         入力         ポート 97: 入力ポート         (シュミット入力)           PY         出力         パート 97: 入力ポート         (シュミット入力)           PAO-PA7<br>KIO-KI7         8         入力         ポート AO-A7 ポート 入力 ボート専用端子<br>トカ カーア: キーオンウェイクアップ 0-7 用端子 (シュミット入力, ブルアップ抵抗付き)           PC0         1         入力         ボート C0: 入出力ボート<br>(シュミット入力)         (シュミット入力)           INT0         1         入力         割り込み要求端子 (シュミット入力)           INT1         1         入力         割り込み要求端子 (シュミット入力)           INT2         1         入力         オート C2: 入出力ポート<br>(シュミット入力)           INT3         1         入力         割り込み要求端子 2:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子           PC3         入出力         ボート C3: 入出力ポート<br>(シュミット入力)           INT3         1         入力         割り込み要求端子 3:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子           PC4         1         入力         ボート C5: 入出力ボート           EA26         1         出力         ボート C5: 入出カボート           EA27         1         出力         ボート C6: 入出カボート           EA28         1         出力         ボート C7: 入出カボート           EA28         1         出力         ボート C7: 入出カポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P96     | 1    | 入力       |                                                  |

| P97         1         入力         ボート 97: 入力ボート (シュミット入力)           PY         出力         Y-ブラス: タッチスクリーンパネル用 Y+ 接続端子           PA0-PA7 KI0-KI7         8         入力         ボート A0-A7 ボート: 入力 ボート専用端子 キー入力 0-7: キーオンウェイクアップ 0-7 用端子 (シュミット入力) ブルアップ抵抗付き)           PC0 1NT0         入出力         ボート C0: 入出力ボート (シュミット入力) 割り込み要求端子 0・レベル/立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子 1・立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子 7 A0IN         カカカカカカカカカカカカカカカカカカカカカカカカカカカカカカカカカカカカ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | INT4    |      | 入力       |                                                  |

| PY         出力         Y・プラス:タッチスクリーンパネル用 Y+ 接続端子           PAO-PA7 KIO-KI7         8         入力         ポート AO-A7 ポート・入力 ポート専用端子 キー入力 0・7: キーオンウェイクアップ 0・7 用端子 (シュミット入力, プルアップ抵抗付き)           PC0 1 NT0         1         入力         割り込み要求端子 0・レベルウェトがり/立ち下がりエッジをプログラム可能な割込み要求端子 0・レベルウェトがり/立ち下がりエッジをプログラム可能な割込み要求端子 0・レベルウェトがり/立ち下がりエッジをプログラム可能な割込み要求端子 0・レベルウェトがり/立ち下がりエッジをプログラム可能な割込み要求端子 0・レベルウェトがり/立ち下がりエッジをプログラム可能な割込み要求端子 0・レベルウェール 0・シュミット入力)           INT1 1 ハカ タイマ入力:8 ピットタイマ 0の入力端子 0・シュミット入力)         カカ オート C2・入出力ポート (シュミット入力)           INT2 1 入力 割り込み要求端子 2・立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子 0・レス・アンカン カンク・アンカン 3・アントス・アントス・アンカン 3・アントス・アンカンカンカン・アントス・アンカンカン・アントス・アンカン 3・アントス・アンカン 3・アントス・アンカンカ 3・アントス・アンカンカンド・クログラム可能な割込み要求端子 2・アンカンカッド・クログラム可能な割込み要求端子 クイマカン・8・ビットタイマ 2の入力端子 カンカン・アントス・アンカンカンド・クログラム可能な割込み要求端子 か 1 出力 拡張用アドレス EA26           PC5 2 1 日力 ボート C6: 入出力ポート 拡張用アドレス EA27         1           PC6 2 1 日力 ボート C6: 入出力ポート 拡張用アドレス EA28         1           EA28 日か                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PX      |      | 出力       |                                                  |

| PAO-PA7 KIO-KI7         8         入力 ポート AO-A7 ポート: 入力 ボート専用端子 (シュミット入力, ブルアップ抵抗付き)           PC0 INTO         1         入出力 ポート CO: 入出力ポート (シュミット入力) 割り込み要求端子 (シュミット入力) 別がて 2         1         入力 割り込み要求端子 (シュミット入力) カカ オート C3: 入出力ポート (シュミット入力) 割り込み要求端子 (シュミット入力) 割り込み要求端子 (シュミット入力) 割り込み要求端子 (シュミット入力) 割り込み要求端子 (シュミット入力) カカ (カカート C4: 入出力ポート は張用アドレス EA26 カカボート C4: 入出力ポート 拡張用アドレス EA26 カカボート 広張用アドレス EA27 上力 拡張用アドレス EA28。 アC7 人出力 ポート C6: 入出力ポート 拡張用アドレス EA28。 アC7 人出力ポート 拡張用アドレス EA28。 アC7 人出力 ポート C7: 入出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P97     | 1    |          |                                                  |

| KIO-KI7         8         入力         キー入力 0-7: キーオンウェイクアップ 0-7 用端子 (シュミット入力, ブルアップ抵抗付き)           PC0         1         入出力         ボート CO: 入出力ポート (シュミット入力)           INT0         1         入力         割り込み要求端子 0:レベル/立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子           PC1         入出力         ボート C1: 入出力ポート (シュミット入力)           INT1         1         入力         割り込み要求端子 1:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子 74つ入力: 8 ピットタイマ 0の入力端子           PC2         1         入出力         ポート C2: 入出力ポート (シュミット入力)           INT2         1         入力         ポート C3: 入出力ポート (シュミット入力)           INT3         1         入力         割り込み要求端子 2:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子 74つ入力: 8 ピットタイマ 2の入力端子 74つ入力: 8 ピット 24の入力端子 74つ入力: 8 ピット 24の入力ボート 14の力ポート 14 | PY      |      | 出力       | Y-プラス: タッチスクリーンパネル用 Y+ 接続端子                      |

| RIO-KI7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PA0~PA7 | 8    |          |                                                  |

| NATO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | KI0~KI7 | Ů    | 入力       |                                                  |

| NTO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PC0     | 1    | 入出力      |                                                  |

| INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | INT0    | '    |          |                                                  |

| TAOIN         入力         タイマ入力: 8 ビットタイマ 0 の入力端子           PC2 1 入出力         ポート C2: 入出力ポート (シュミット入力)           INT2 1 入力         割り込み要求端子 2:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子           PC3 1 入出力         ポート C3: 入出力ポート (シュミット入力)           INT3 1 入力         割り込み要求端子 3:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子 7A2IN           PC4 日本         1 大出力           EA26 1 出力         ポート C4: 入出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PC1     |      |          |                                                  |

| PC2       1       入出力       ポート C2: 入出力ポート (シュミット入力)         INT2       1       入力       割り込み要求端子 2:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子         PC3       入出力       ポート C3: 入出力ポート (シュミット入力)         INT3       1       入力       割り込み要求端子 3:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子         TA2IN       入力       タイマ入力: 8 ビットタイマ 2 の入力端子         PC4       1       出力       ポート C4: 入出力ポート         EA26       1       入出力       ポート C5: 入出力ポート         EA27       1       入出力       ポート C6: 入出力ポート         EA28       1       出力       ボート C6: 入出力ポート         EA28       1       ルカ       ボート C7: 入出力ポート         1       入出力       ポート C7: 入出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | 1    |          |                                                  |

| INT2     入力     割り込み要求端子 2:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子       PC3     入出力     ポート C3: 入出力ポート     (シュミット入力)       INT3     1     入力     割り込み要求端子 3:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子 74マ入力: 8 ビットタイマ 2の入力端子       PC4     1     入出力     ポート C4: 入出力ポート       EA26     1     出力     ボート C5: 入出力ポート       EA27     1     入出力     ボート C5: 入出力ポート       EA27     1     カート C6: 入出力ポート       EA28     1     カート C6: 入出力ポート       EA28     1     カート C7: 入出力ポート       BC7     入出力     ポート C7: 入出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TA0IN   |      |          |                                                  |

| INT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PC2     | 1    |          |                                                  |

| INT3     1     入力     割り込み要求端子 3:立ち上がり/立ち下がりエッジをプログラム可能な割込み要求端子 タイマ入力: 8 ビットタイマ 2 の入力端子       PC4     1     入出力     ポート C4: 入出力ポート 出力 拡張用アドレス EA26       PC5     1     入出力     ポート C5: 入出力ポート 出張用アドレス EA27       PC6     1     入出力     ポート C6: 入出力ポート 出力 拡張用アドレス EA28       PC7     入出力     ポート C7: 入出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | INT2    | '    |          |                                                  |

| TA2IN     入力 タイマ入力: 8 ビットタイマ 2 の入力端子       PC4     入出力     ポート C4: 入出力ポート       EA26     1     本一ト C5: 入出力ポート       PC5     1     カート C5: 入出力ポート       EA27     1     カート C6: 入出力ポート       PC6     入出力     ポート C6: 入出力ポート       EA28     1     カート C7: 入出力ポート       PC7     入出力     ポート C7: 入出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PC3     |      |          |                                                  |

| PC4     1     入出力     ポート C4: 入出力ポート       EA26     1     加力     拡張用アドレス EA26       PC5     1     入出力     ポート C5: 入出力ポート       EA27     出力     ポート C6: 入出力ポート       PC6     入出力     ポート C6: 入出力ポート       EA28     出力     拡張用アドレス EA28       PC7     入出力     ポート C7: 入出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | 1    | /        | / / / ^                                          |

| EA26     1     出力     拡張用アドレス EA26       PC5     入出力     ポート C5: 入出力ポート       EA27     出力     拡張用アドレス EA27       PC6     入出力     ポート C6: 入出力ポート       EA28     出力     拡張用アドレス EA28       PC7     入出力     ポート C7: 入出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |      |          |                                                  |

| EA26       出力 拡張用アドレス EA26         PC5       入出力 ポート C5: 入出力ポート         EA27       出力 拡張用アドレス EA27         PC6       入出力 ポート C6: 入出力ポート         EA28       出力 拡張用アドレス EA28         PC7       入出力 ポート C7: 入出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PC4     | 1    | / / ) ]  |                                                  |