# TOSHIBA

# 32Bit TX System RISC TX19A Family Architecture

$\operatorname{Rev} 1$  .0

# TOSHIBA CORPORATION

**Semiconductor Company**

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its

use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or the third

parties. 021023\_C

- The products described in this document are subject to foreign exchange and foreign trade control laws. 060925\_E

- MIPS16, Application Specific Extensions & R3000A are trademarks of MIPS Group , a division of Silicon Graphics, Inc.

# Preface

This manual describes the architecture of the Toshiba TX19A family.

| Contents                                                                              |

|---------------------------------------------------------------------------------------|

| Chapter 1: Introduction                                                               |

| Outline of TX19A                                                                      |

| Chapter 2: CPU Architecture Overview                                                  |

| -Data load in the CPU registers and memory                                            |

| -Overview of the functionality of the registers                                       |

| Chapter 3: 32-Bit ISA Summary and Programming Tips                                    |

| -Summary of the 32-bit instruction set architecture (ISA)                             |

| Chapter 4: 16-Bit ISA Summary and Programming Tips                                    |

| -Summary of the 16-bit ISA                                                            |

| Chapter 5: CPU Pipeline                                                               |

| -Information about the instruction pipeline                                           |

| Chapter 6: Memory Management                                                          |

| -The virtual and physical address spaces and these mapping manners                    |

| Chapter 7: Internal I/O Bus Operation                                                 |

| -Outlines of the Harvard architecture and the protocols for internal bus transactions |

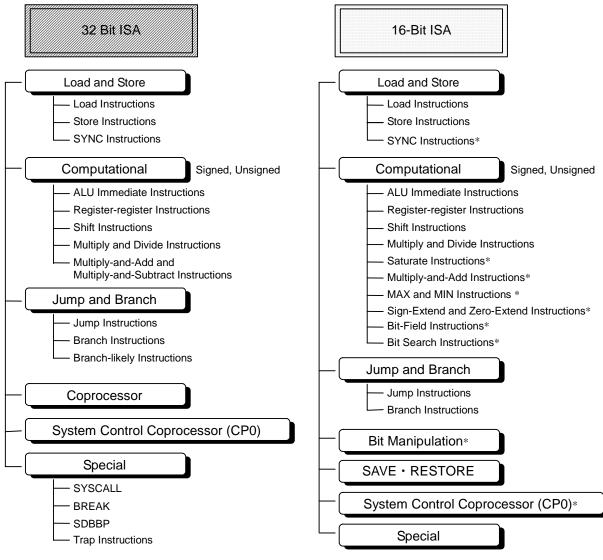

| Chapter 8: System Control Coprocessor (CP0) Registers                                 |

| -A group of registers associated with system configuration and exception processing   |

| Chapter 9: CPU Exception Processing                                                   |

| -The events that cause exceptions and the sequences to be handled                     |

| Chapter 10: Power Consumption Management                                              |

| -The methods of dynamically controlling power consumption during operation            |

| Appendix A: 32-Bit ISA Details                                                        |

| -Detailed description of each instruction available in 32-bit ISA mode                |

| Appendix B: 16-Bit ISA Details                                                        |

| -Detailed description of each instruction available in 16-bit ISA mode                |

| Appendix C: Programming Restrictions                                                  |

| -The restrictions need to be observed in writing assembly-language programs           |

| Appendix D: Compatibility Among TX19, TX19A and TX39 Architectures                    |

| -Provides comparisons among the three RISC processor families                         |

| Appendix E: 32-Bit ISA Instruction Bit Encoding                                       |

| -The opcode bit encoding for the 32-bit ISA                                           |

| Appendix F: 16-Bit ISA Instruction Bit Encoding                                       |

| -the opcode bit encoding for the 16-bit ISA                                           |

### Readers

This manual is written for software and hardware developers who want to develop products using TX19A processors and controllers.

RISC processors including TX19A have a number of features that make them stand out from CISC processors. If you are unfamiliar with RISC architecture, Chapter 1 should be useful for you. Please note that RISC processors have a small instruction set. There are no complex instructions such as LDIR (block transfer), CPIR (block search), BS1B (bit scan). Since RISC has very few instructions, a programmer or a compiler needs to implement additional instructions by using available RISC instructions.

Chapter 2, the architecture overview, should help programmers who can use a high-level language such as C in developing software.

Assembly language programmers must be well versed in the intricacies of the machine architecture. The performance of software systems is drastically affected by how well software designers understand the basic hardware technologies at work in a system. Therefore, we recommend assembly language programmers to read the entire manual that gives a detailed description of the TX19A architecture for overall understanding.

# **Related Document**

Semiconductor Reliability Handbook (Integrated Circuits)

This book describes the methodology used by Toshiba to achieve robust semiconductor designs before market introduction and to ensure high quality and reliability in volume production phase.

# **Chapter 1 Introduction**

This chapter provides the features of the TX19A and a general description of how the TX19A RISC design differs from CISC processors such as the Toshiba 900/L1.

### **1.1 Processor General Features**

The TX19A, a high quality 32-bit RISC processor, is created based on MIPS Technologies Inc.'s R3000A architecture that contains reduced code size of 16 bit architecture "MIPS16e-TX". The instruction set of the TX19A includes the 32-bit instructions of the TX39 as a subset. Thus the TX19A software preserves upward compatibility with TX39 and TX19.

The TX19A family of integrated processors and controllers is built on the TX19A core processor, an on-chip bus and a selection of intelligent peripherals appropriate for specific applications. The TX19A is available as an ASIC-ready core and a family of standard ASSP products.

#### Instruction sets of MIPS 16e-TX and MIPS S32

- MIPS16e-TX instruction sets are object-code compatible with MIPS16 ASE except for the area that Toshiba extended MIPS16 ASE with permission of MIPS Technologies, Inc. Note: The TX19A does not provide support for MIPS16 ASE instructions for 64-bit operations.

- The 32-bit instructions are object-code compatible with the high-performance TX39 family. -Switchable run-time between 16-bit and 32-bit ISA modes through an instruction. These conditions are respectively called as 16 bit ISA mode and 32 bit ISA mode.

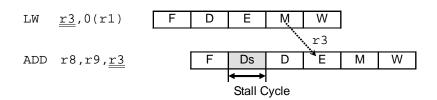

-Hardware interlocks enables to send an instruction to refer the data loaded in register immediately after the load instruction. This eliminates the need to insert a NOP (No Operation) instruction.

-Branch-likely instructions allow the processor to execute the instruction at the target location immediately after the branch instruction. This eliminates the need to insert a NOP instruction.

#### **High Performance**

- Single clock cycle execution for most instructions

- 3-operand computational instructions

- Full 32-bit operations: Contains 32-bit general-purpose registers and a 32-bit program counter.

- 8 sets of 32 general-purpose registers (shadow register sets): Automatically switched on entry to an interrupt, based on its priority level.

- 5-stage pipeline

- Independent on-chip instruction and data memory with an access time of one clock cycle applicable

- An on-chip write buffer applicable

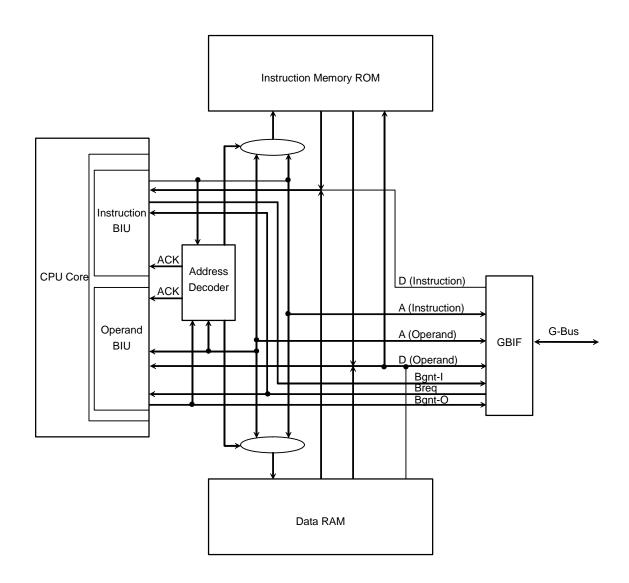

- Harvard architecture

The TX19A uses separate buses for code and data operands. In the TX19A, there are four sets of buses: a data bus for carrying data (operands) in and out of the processor core, an address bus for

accessing data operands, a bus to carry the opcodes and an address bus to access the opcodes. The ability to access code and data simultaneously through separate buses increases instruction throughput.

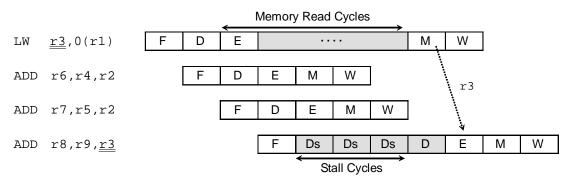

- Nonblocking loads function enables to execute the subsequent instruction in a load delay slot in case a large latency appeared during data loading from external memory.

- On-chip multiplier/accumulator (MAC): Executes a (32-bit x 32-bit + 64-bit) and (64-bit –

32-bit x 32-bit) operations in a single clock cycle.

- 4-Gbyte virtual address space

- Integrated coprocessor: The TX19A contains the system control coprocessor (CP0) for system configuration, exception handling and memory management.

#### Low Power

• Power-optimized design

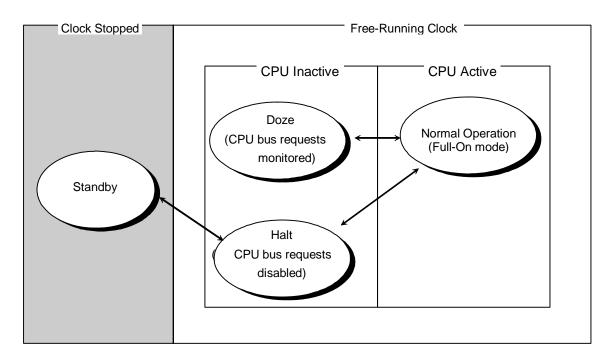

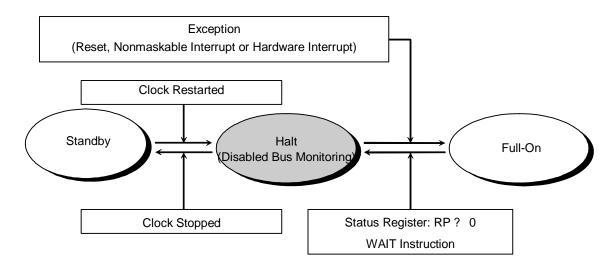

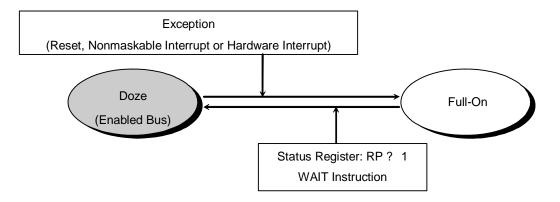

Programmable power management modes (Halt and Doze): In Doze mode, the processor senses external bus requests.

#### Real-Time Interrupt Response

- Distinct starting locations for each interrupt service routine

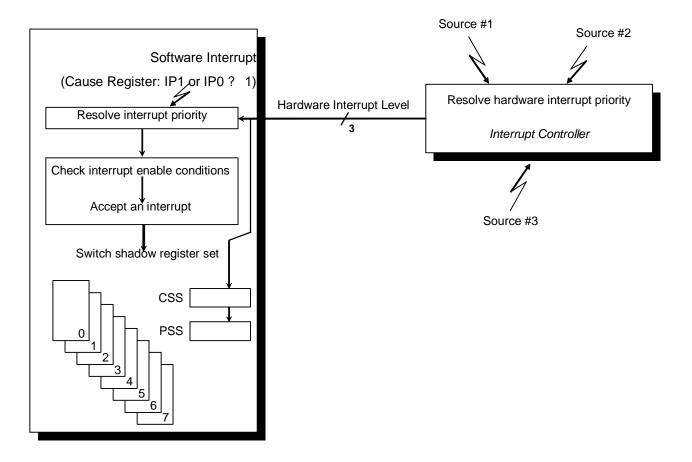

- Automatically generated vectors for each interrupt source: Interrupt priorities are resolved upon reading the exception vector. Interruption exception is executed when its priority level is higher than the current one. It makes the TX19A effective for quick response to an interrupt request that needs immediate action.

- On an interrupt, register sets are automatically switched based on its priority level.

#### **Processor Core for System ASIC Applications**

- Unified manufacturing process and development environment as ASIC

- Compact core design

- The processor core can be directly connected to the G-Bus, the standard on-chip bus for the TX series.

#### System Development Environments

- Language tools: C compilers and assemblers

Both Toshiba's proprietary and third-party tools are offered.

- Real-time operating systems

Both Toshiba's proprietary ([ITRON) and third-party real-time operating systems are offered.

- Debug support systems

Both Toshiba's proprietary and third-party real-time emulators are offered to support source-level debugging.

-Support for utility software to insert debug support unit (DSU) circuitry into an ASIC design.

# 1.2 What Is RISC?

Until the early 1980s, all CPUs followed the complex instruction set computer (CISC) design philosophy. To preserve compatibility with the existing pool of software, CISC processors evolved by adding new types of machine instructions and more intricate operations. Generally, CISC refers to CPUs with hundreds of instructions designed for every possible situation. Designing CPUs with hundreds of instructions not only requires many transistors but is also very complicated, timing consuming and expensive.

In the early 1980s, a controversy broke out in the computer design community. Proponents of a new type of computer design argued that no one was using so many instructions. As it was developed, it came to be known as reduced instruction set computer (RISC). RISC concepts emerged by statistical analysis of how software actually uses the resources of a processor. According to experiments, many of the complex instructions were never used by programmers and compilers. The huge costs of implementing numerous instructions made some designers think of streamlining the instruction set.

#### ■ Feature 1 Simple instructions

RISC processors have a small instruction set. For example, there are no such complex instructions as block transfer, block search, bit scan and so forth.

Additionally, RISC uses the load/store architecture. In CISC processors, data can be manipulated while it is still in memory. For example, "ADD A, (1000H)" contained in 16-bit CISC processor TLCS-900/L1, is an instruction to bring the contents memory location 1000H into the CPU, sum it up with data in register A and store the total in A. RISC did away with this kind of instructions. In RISC, a single instruction can either load from memory into a register or store from a register into memory. In other words, all operations are performed on operands held in CPU registers. Since CISC processors have a large number of instructions, each with so many different addressing modes, microcode is used to implement all of them. This feature of CISC makes the job of programmers easy and helps to reduce code size. However, the implementation of microcode requires more space on chip, creating a bottleneck in an effort to improve processor performance.

#### ■ Feature 2 Fixed instruction size

RISC processors have a fixed instruction size. In a CISC microprocessor, instructions can be 1, 2 or even 7 bytes at the maximum. This variable instruction size makes the task of the instruction decoder very complicated since the size of the incoming instruction can never be known. In the TX19A microprocessor, the instruction size is fixed at 32 bits. The fixed instruction size enables the CPU to decode instructions quickly.

#### ■ Feature 3 Heavily pipelined

Since RISC has only a limited number of simple instructions, most of the instructions can be executed in one clock cycle. Therefore, RISC is easier to pipeline than CISC that requires a different number of clock cycles for each instruction in pipeline. Generally, RISC processors are heavily pipelined.

# 1.3 Features of the TX19A

The previous section provided an overview of the RISC features which are different from CISC processors. In this section, we explore how the instruction set architecture (ISA) is implemented in the TX19A in comparison to the 870/X and the 900/L1, 8-bit and 16-bit CISC processors from Toshiba.

The TX19A has two ISA modes, 16-bit and 32-bit. The condition that each mode is executed is respectively called as 16 bit ISA mode and 32 bit ISA mode. It provides for efficient run-time switching between 16-bit and 32-bit ISA modes through an instruction. The 16-bit instruction set (MIPS16e+) is not a separate instruction set indeed but a 16-bit extension of the full 32-bit MIPS architecture. The 32-bit ISA has 103 instructions, the 16-bit ISA 128 instructions. Programs will consist of procedures in 16-bit mode for density or in 32-bit mode for performance. On the other hand, the 870/X and the 900/L1 are both CISC processors having nearly 1000 types of instructions and many addressing modes. CISC processors are, in general, excel in code efficiency.

# 1.3.1 Instruction Set Architecture

#### • The TX19A did away with complex instructions.

The TX19A has only the basic instructions such as load, store, add, subtract, multiply, divide, AND, OR, XOR, shift, jump and branch. There are no complex instructions like LDIR (block transfer) and CPIR (block search) available with the 900/L1. It is the responsibility of the compiler (or the programmer) to generate software routines to perform complex instructions that are done in hardware by CICS processors. As exceptions, are the multiply-and-add (MADD and MADDU) and multiply-and-subtract (MSUB and MSUBU) instructions that require very fast processing are included in instruction sets (these instructions are executed by the dedicated MAC circuitry.)

# • The TX19A did away with instructions that can be implemented by some other instructions

To reduce the size of the instruction set, the TX19A aggressively eliminated the instructions that can be implemented using other instructions. For example, the TX19A does not have the NOP (No Operation), INC (Increment) and DEC (Decrement) instructions. Instead of NOP, a shift instruction can be used as shown below for TX19A processors:

SLL r0,r0,0

In the TX19A, register r0 is hardwired to a constant value of 0. The above instruction actually shifts the contents of r0 by zero bits and places the result back in r0. (The assembler permits NOP as a

ADDIU rt,rs,1

In this condition, *rt* and *rs* are the target and source registers respectively. Likewise, a register decrement can be implemented as follows:

ADDIU *rt,rs*,-1

#### • The TX19A discarded instructions synthesizable from two or more simple instructions

The TX19A further pared down the instruction set by discarding the instructions that can be performed by two or more simple instructions. For example, the TX19A does not have the POP and the PUSH instructions for accessing the stack. In CISC processors, as a PUSH instruction is executed, the contents of a register is saved on the stack and the stack pointer register is decremented by the amount of the register size. In the TX19A, one of the 32 general-purpose registers is used as a stack pointer; pushing onto the stack is accomplished by executing an add instruction on the stack pointer and a store instruction.

#### • The TX19A uses the load/store architecture

In CISC processors such as the 870/X and the 900/L1, data can be manipulated while it is still in memory, like ADD A, (1000H). The TX19 did away with this kind of instructions; in the TX19, the load and store instructions are the only instructions that move data between memory and CPU general registers. However, the TX19A enhanced the capability of the TX19 by adding a group of instructions that manipulate a specific bit in memory or add an immediate to a value in memory.

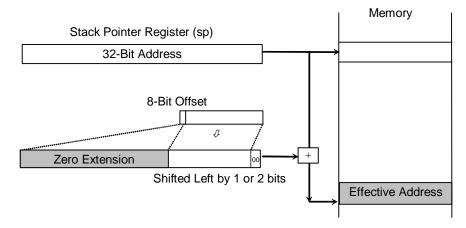

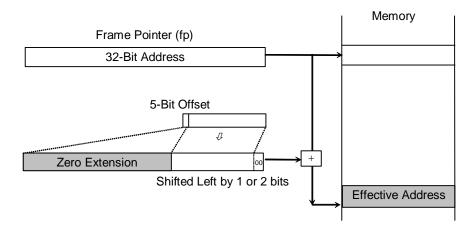

#### • The TX19A has only a few memory addressing modes

The 900/L1 and the 870/X1 have seven or more addressing modes for memory accesses. For example, there are register indirect, register indirect with autoincrement, indexed relative, based indexed relative, etc. These versatile addressing modes are very useful for assembly language programmers and contribute to a reduction in code size.

In contrast, in 32-bit ISA mode, the TX19A has only one addressing mode for accessing memory locations in order to simplify hardware implementation: i.e., based relative. In 16-bit ISA mode, the TX19A has three more addressing modes called PC-relative, SP-relative and FP-relative; only three 16-bit instructions can use PC-and SP-relative addressing modes, however.

#### • The TX19A has three-operand computational instructions 3

In the TX19A, many computational instructions use triadic format. In triadic instruction format, there are two source registers and one destination register. An example of triadic format is:  $ADD \quad rd.rs1.rs2$

This instruction adds the contents of two source registers, rs1 and rs2, and stores the results in rd. On the other hand, the 900/L1 adds the contents of XWA and XBC and puts the result in XWA. ADD XWA,XBC

#### • The TX19A does not have a flag register

The TX19A does not have a dedicated flag register with the carry, overflow and sign bits. For example, in the 900/L1, the carry flag is used to indicate whether or not there was a carry from an addition or a borrow as a result of subtraction. It is widely used in multibyte additions and subtractions. The 900/L1 has the ADC instruction to add the carry bit to the sum of two registers.

On the other hand, the TX19A can perform 32-bit additions at a time; so the flag bit is rarely needed. To perform an add-with-carry, a routine must first explicitly determine whether the addition has resulted in a carry, and then record the occurrence of a carry in a register. When doing multiword additions, two different code sequences are required: one for adding with a carry-in and one for adding without a carry-in.

Additionally, the 900/L1 CP (compare) instruction uses the carry flag to indicate whether or not there was a borrow as a result of subtraction. In the TX19A, the result of compare instructions such as SLT (Set On Less Than) is placed into a general register.

#### **1.3.2** Instruction Format

The TX19A has two ISA modes, 16-bit and 32-bit. All the instructions for the 32-bit ISA mode, as the name suggests, consist of 32 bits. All the instructions for the 16-bit ISA mode consist of 16 bits, with a few exceptions. The 870/C instructions have the variable length: 1, 2, 3, 4, 5 and 6 bytes. Furthermore, the 900/L1 covers 7 byte-instruction as the longest. This variable instruction length is useful to reduce code size; however, it makes the task of the instruction decoder very complicated and slow.

#### **1.3.3 Instruction Pipelines**

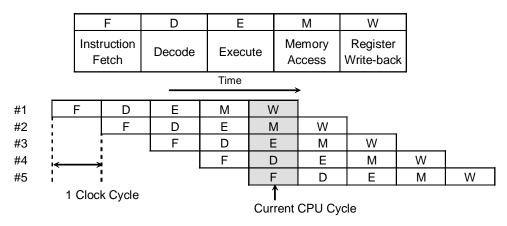

The TX19A has a five-stage pipeline. The five-stage pipeline divides the execution of each instruction into five discrete portions and executes up to five instructions simultaneously. Each stage takes one clock cycle.

The major characteristics of the TX19A is that the execution of most instructions requires a uniform number of clock cycles; thus the TX19A is relatively easy to pipeline. The TX19A achieves an instruction execution rate approaching one instruction per clock cycle.

If the instruction stream includes a variety of different instruction lengths as in CISC processors, pipeline management becomes very complicated. Moreover, such a varied, complex instruction stream makes it almost impossible for a compiler to schedule instructions to reduce or eliminate pipeline stalls.

# **Chapter 2 CPU Architecture Overview**

This chapter outlines the TX19A architecture, data formats, programming model, ISA modes, coprocessors, instruction pipeline and memory management.

# 2.1 Data Formats

This section describes the organization of data in registers and memory and how operands are signor zero-extended for operations.

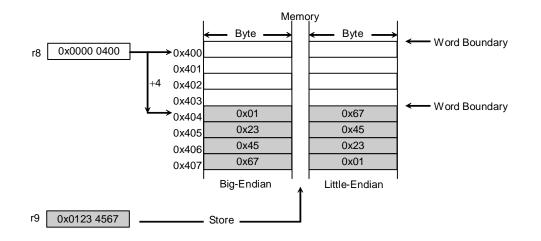

# 2.1.1 Byte Ordering

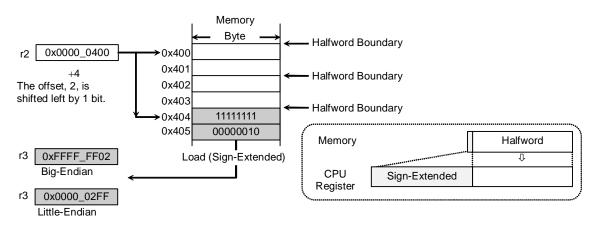

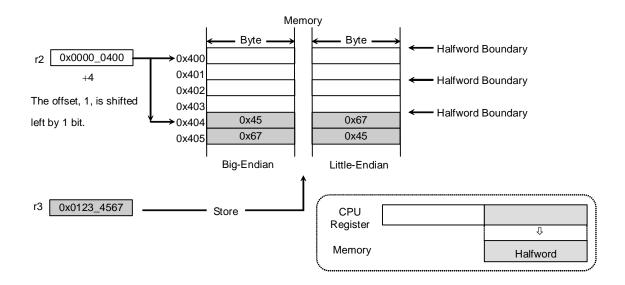

The TX19A supports many data types including 8-bit, 16-bit, 32-bit and 64 bit. A byte is defined as 8 bits. A halfword is two bytes, or 16 bits. A word is four bytes, or 32 bits. A doubleword is two words, or 64 bits.

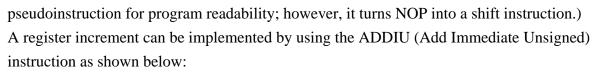

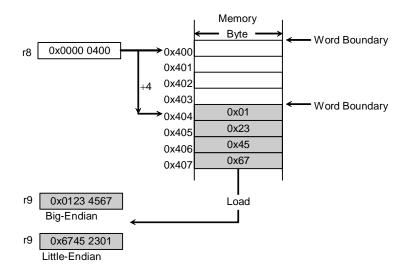

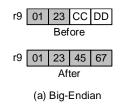

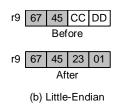

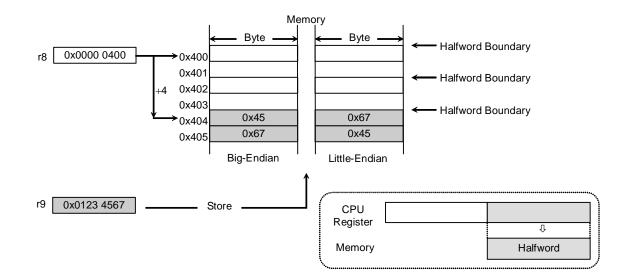

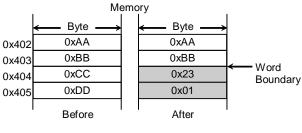

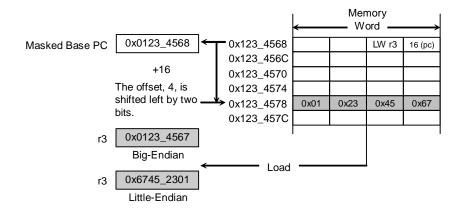

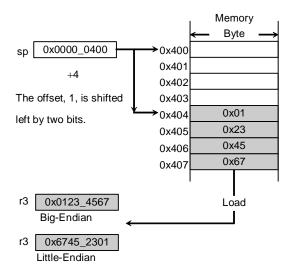

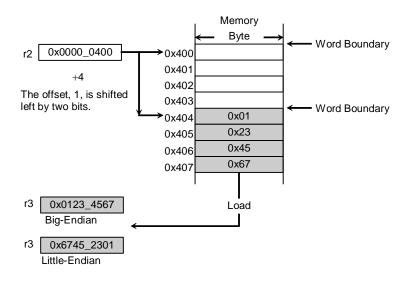

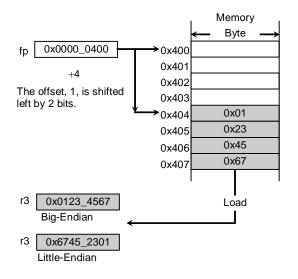

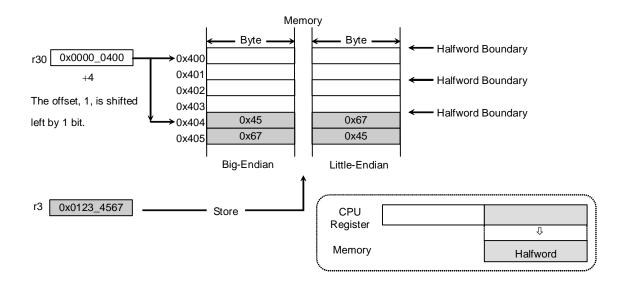

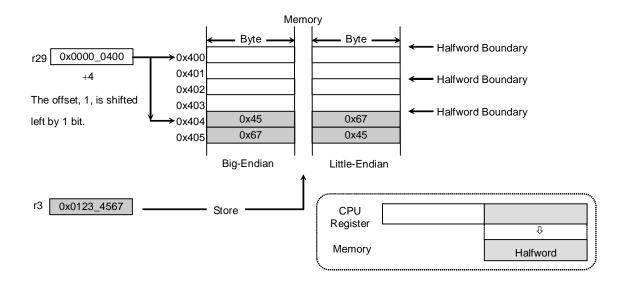

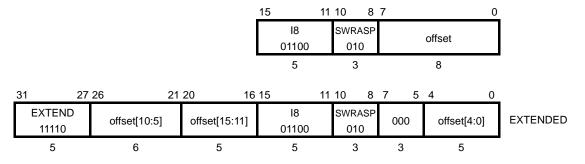

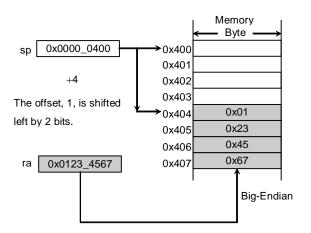

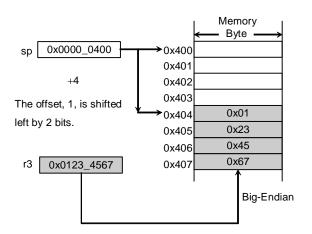

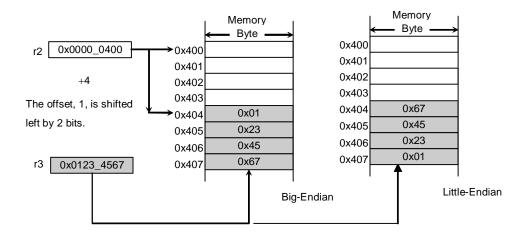

For multibyte data types, the TX19A supports both big-endian and little-endian formats. Byte ordering (endianness) can be set through the ENDIAN input pin during a reset sequence. (In some TX19A components, byte ordering is fixed to either big-endian or little-endian.) Figure 2-1 shows the ordering of bytes in a word for big-endian and little-endian formats. The TX19A processor uses a byte addressing. The big-endian ordering assigns the lowest address to the highest-order (leftmost) byte. The little-endian ordering assigns the lowest address to the lowest-order (rightmost) byte. Notice that, in the little-endian format, each byte of a multibyte integer is placed in the same memory location regardless of whether the integer is defined as a halfword or a word in size.

(b) Little-Endian

Figure 2-1 Byte Ordering

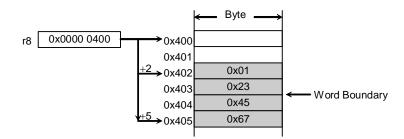

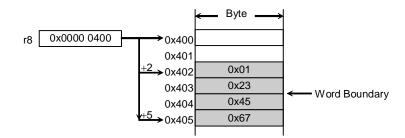

# 2.1.2 Aligned and Misaligned Accesses

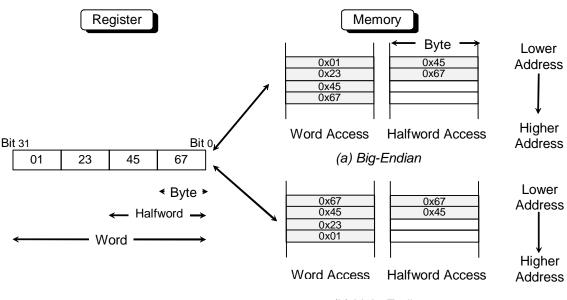

The TX19A uses byte addressing for byte, halfword and word accesses. The address of a multibyte data item is the address of the lowest memory location for that data item; i.e. the address of the most-significant byte on a big-endian configuration and the address of the least-significant byte on a little-endian configuration.

Memory access instructions have a natural alignment boundary equal to the operand length (see fig. 2-2). In other words, the natural address of an operand is an integer multiple of the operand length. A memory operand is aligned if its address is a multiple of two for halfword accesses or a multiple of four for word accesses.

Figure 2-2 Aligned Data Items

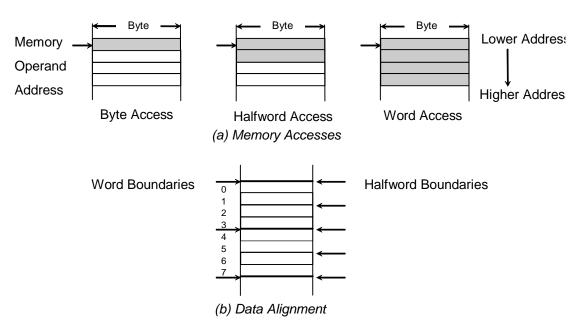

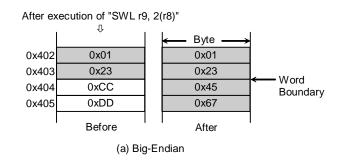

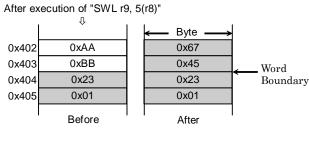

Most instructions require their memory operands to be aligned because alignment affects performance. Special instructions are provided for addressing words that cross a boundary between two words: LWL (Load Word Left), LWR (Load Word Right), SWL (Store Word Left) and SWR (Store Word Right). These instructions are used in pairs. Figure 2-3 illustrates how a word of aligned and misaligned data is loaded from memory into a CPU register.

#### Figure 2-3 Aligned and Misaligned Accesses

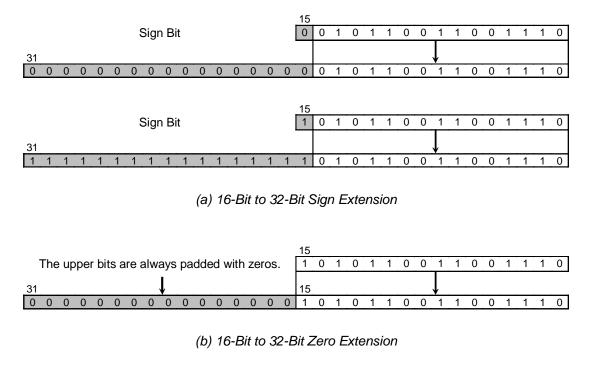

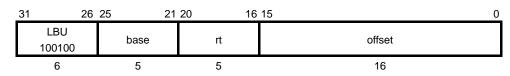

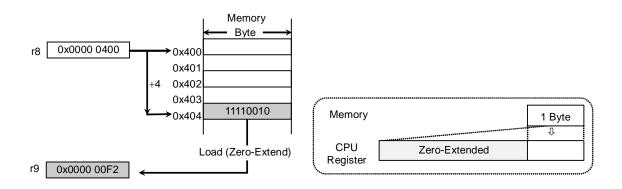

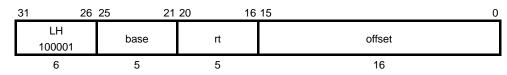

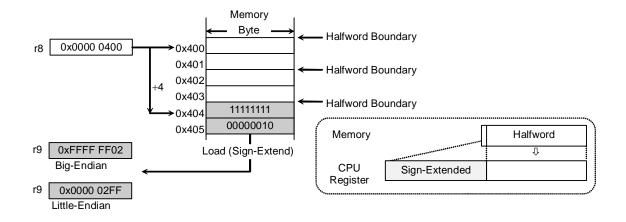

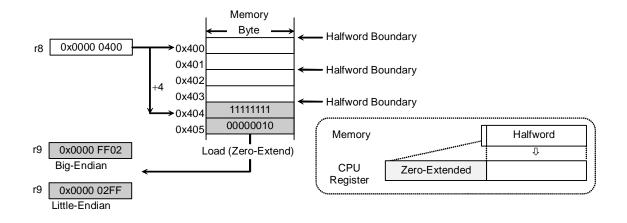

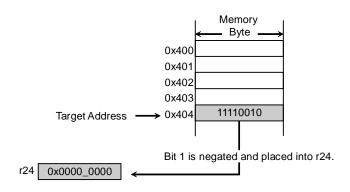

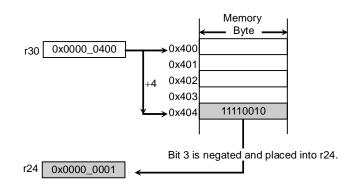

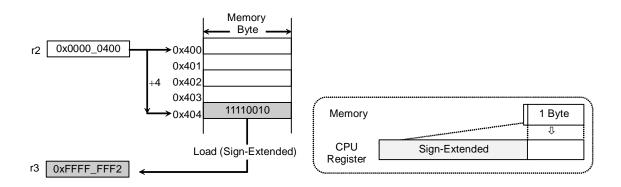

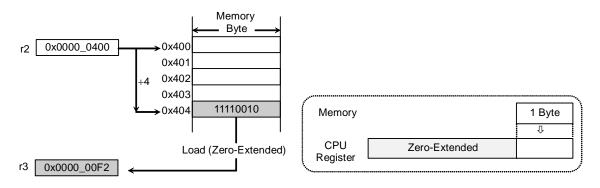

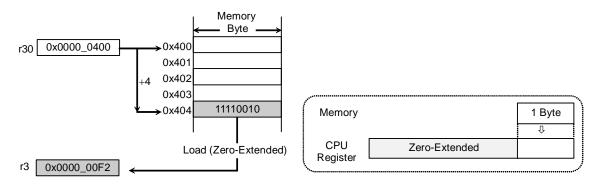

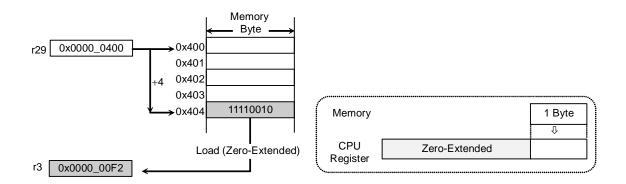

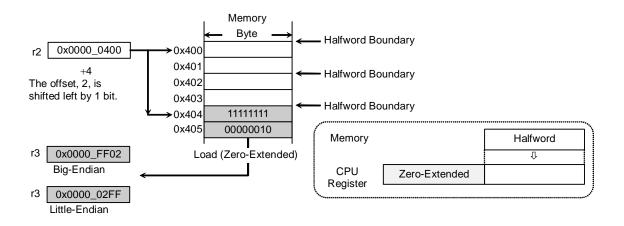

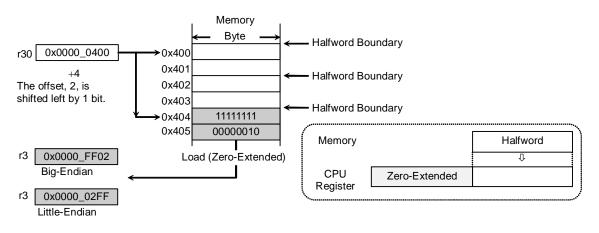

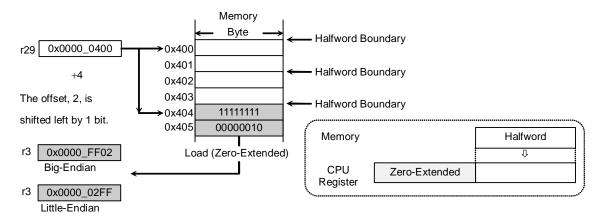

#### 2.1.3 Data Extensions

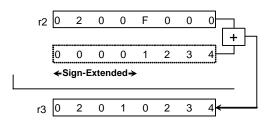

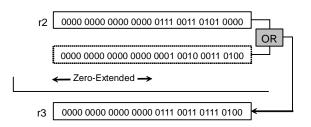

Figure 2-4 illustrates sign extension and zero extension. In signed numbers, the most-significant bit is the sign and the remaining bits are set aside for the magnitude of the number. Sign extension copies the most-significant bit (i.e., sign bit) of a 16-bit immediate or the loaded byte or halfword into the upper bits. Zero extension fills unused bits in a word with zeros irrespective of the value of the most-significant bit of a 16-bit immediate or the loaded byte or halfword.

Sign extension is typically used to avoid problems associated with arithmetic operations. For example, the ADDI (Add Immediate Signed) instruction only can take a 16-bit immediate. The instruction "ADDI r3, r1, 0x1234" sign extends 0x1234 and adds it to the contents of register r1 to form a 32-bit result. The result is placed into register r3.

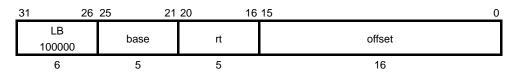

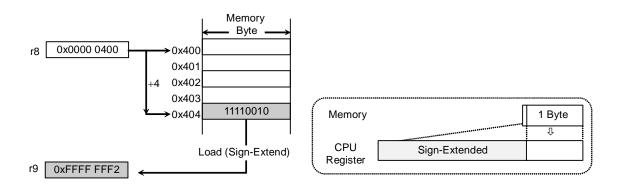

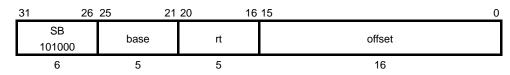

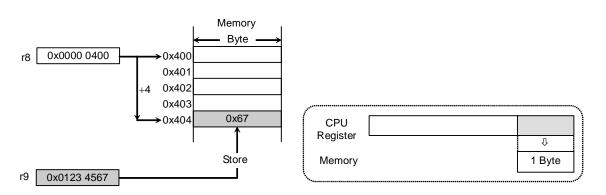

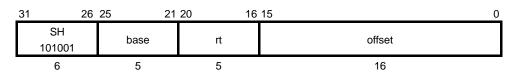

The TX19A also applies sign extension to such instructions as LB (Load Byte), LBU (Load Byte Unsigned) LH (Load Halfword), LHU (Load Halfword Unsigned) LW (Load Word), SB (Store Byte), SH (Store Halfword), SW (Store Word) since the only addressing mode supported is base register plus 16-bit immediate (i.e., offset). For example, the instruction "LB r9, 4(r8)" sign-extends the offset (4 or binary 0100) and adds it to the contents of the base address held in r8 to form an effective address. The word in the addressed memory location is loaded into r9.

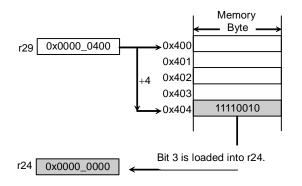

To load byte data and halfword data in register, sign extension or zero extension is selected depend on the instructions. Therefore, the LB and LH instructions sign- extend the loaded byte and put it in the target register; the LBU instruction zero-extends the loaded byte.

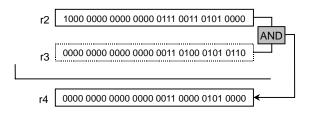

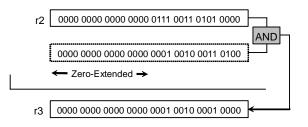

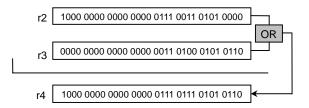

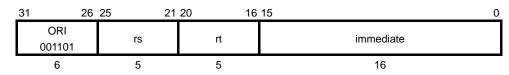

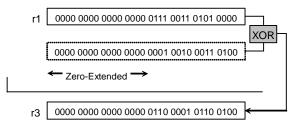

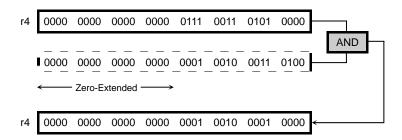

Additionally, there are two types of logical AND and logical OR instructions each, AND/ANDI and OR/ORI. The AND and OR instructions perform AND and OR operations with word data whereas the ANDI (AND Immediate) and ORI (OR Immediate) perform AND and OR operations with word data and halfword data. ANDI and ORI zero-extends a 16-bit immediate and combine it with the contents of a general register in a bitwise logical AND or OR operation.

# 2.2 Programming Model

The TX19A programming model consists of two groups of registers: CPU registers and system control coprocessor (CP0) registers.

# 2.2.1 CPU Registers

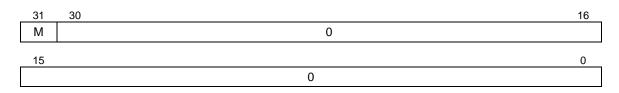

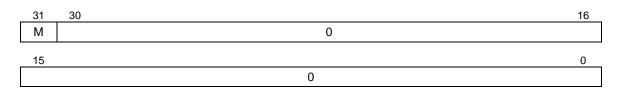

Figure 2-5 shows the CPU registers. The TX19A has eight sets of 32 general-purpose registers (GPRs) called shadow sets for a total of 256 GPRs, a program counter (PC) register and two special registers (HI/LO) that hold the results of integer multiply and divide operations. All CPU registers are 32 bits in length.

#### (a) General-Purpose Registers

(b) Multiply/Divide Registers

HI

LO

| Shadow   | 0        | 1        | 2        | 3        | 4        | 5        | 6        | 7        |  |

|----------|----------|----------|----------|----------|----------|----------|----------|----------|--|

| Register | r0       |          |          |          |          |          |          |          |  |

| Set No.  | r26 (k0) |          |          |          |          |          |          |          |  |

|          | r27 (k1) |          |          |          |          |          |          |          |  |

|          | r28 (gp) |          |          |          |          |          |          |          |  |

|          | r29 (sp) | r29 (sp) |          |          |          |          |          |          |  |

|          | r1 (at)  |  |

|          | r2 (v0)  |  |

|          | r3 (v1)  |  |

|          | r4 (a0)  | r3 (a0)  | r4 (a0)  |  |

|          | r5 (a1)  |  |

|          | r6 (a2)  |  |

|          | r7 (a3)  |  |

|          | r8 (t0)  |  |

|          | r9 (t1)  |  |

|          | r10 (t2) |  |

|          | r11 (t3) |  |

|          | r12 (t4) |  |

|          | r13 (t5) |  |

|          | r14 (t6) |  |

|          | r15 (t7) |  |

|          | r16 (s0) |  |

|          | r17 (s1) |  |

|          | r18 (s2) |  |

|          | r19 (s3) |  |

|          | r20 (s4) |  |

|          | r21 (s5) |  |

|          | r22 (s6) |  |

|          | r23 (s7) |  |

|          | r24 (t8) |  |

|          | r25 (t9) |  |

|          | r30 (fp) |  |

|          | r31 (ra) |  |

#### (c) Program Counter

Figure 2-5 CPU Registers

#### ■ General-Purpose Registers

The TX19A core processor contains eight sets of general-purpose registers known as the "Shadow Register Sets" numbered 0 to 7. Each shadow set consists of 32 registers (r0 to r31), except that all the shadow sets have r0, r26, r27 and r28 in common and that shadow sets 1 to 7 have r29 in common. All the other general-purpose registers are available in each shadow set. Switching to a new shadow set is automatically done by processor hardware via interrupt or can be done with an instruction (MTC0).

The 32-bit ISA instructions can use any of the general-purpose registers shown in Figure 2-5. The general registers are numbered from r0 to r31. The general registers except r0 have symbol names (software names) like v0-v1, a0-a3, and so on that are used by an assembler. The 32-bit ISA instructions treat the general registers symmetrically, with the exception of r0 and r31. r0 is hardwired to a value of 0. As such, r0 can be used by any instruction as a target register when the result of an operation is to be discarded or as a source register when a zero value is necessary. r31 (ra: return address) is a link register used by Jump-and-Link, Branch-and-Link and Branch-Likely and-Link instructions. These instructions are to store an address, which shows the restarting point after a subroutine has been executed, in r31.

In the 16-bit instructions, only eight of the 32 general-purpose registers are normally visible, r2 to r7, r16 and r17. Since the processor includes the full 32 registers of the 32-bit ISA mode,

MIPS16e+ contains move instructions to copy values between the eight MIPS16e+ registers and the remaining 24 registers of the full MIPS architecture. Additionally, specific instructions implicitly reference r24 (t8), r28 (gp), r29 (sp), r30 (fp) and r31 (ra). r24 serves as a special condition code register for handling compare results. r28 is the global pointer register. r29 maintains the program stack pointer. r30 is the frame pointer register. r31 is the link register.

Note: Please do not use r1 while programming since r1 is reserved as a register for assembler.

#### HI and LO Registers

The HI and LO registers hold the results of integer multiply, divide, multiply-and-add and multiply-and-subtract operations. Integer multiply, multiply-and-add and multiply-and-subtract operations store the doubleword, 64-bit result, in the HI and LO registers. Integer divide operations store the quotient in the LO register and the remainder in the HI register. The MFHI, MFLO, MTHI and MTLO instructions are used to move data between the HI and the LO registers and the general registers.

#### Program Counter (PC)

The least-significant bit of the program counter is the ISA mode bit that determines the ISA mode instructions: 0 means 32-bit ISA and 1 means 16-bit ISA. ISA mode bit is not considered as a part of the address. The address of the on-going instruction is the total value of the entire 32 bit after erasing the least-significant bit.

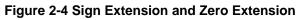

# 2.2.2 System Control Coprocessor (CP0) Registers

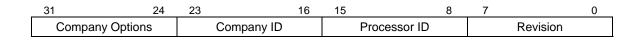

The system control coprocessor, CP0, is an integral part of the TX19A processor. It has 17 user-accessible registers shown in Figure 2-6.

The CP0 registers are classified into three groups: system configuration registers, general exception handling registers and debug exception handling registers. When the processor is in Kernel mode, the system control coprocessor instructions can always use the CP0 registers regardless of the setting of the CU0 bit in the Status register. If the processor is in User mode, the CP0 registers are accessible only when the CU0 bit is 1. Operating modes are explained in Section 2.7, *Memory management Summary*.

| Register Name                      | Description                                                                        |

|------------------------------------|------------------------------------------------------------------------------------|

| Comfit、Config1、<br>Config2、Config3 | System configurations, such as EJTAG and 16-bit ISA mode and cache configurations. |

#### Table 2-1 System Configuration Register

#### Table 2-2 General Exception Handling Registers

| Register Name | Description                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------|

| BadVAddr      | Bad virtual address that caused a virtual-to-physical address translation error.<br>Read-only                                |

| Status        | Processor status, e.g., operating mode (User/Kernel), interrupt enable and other states.                                     |

| Cause         | Cause of the last exception                                                                                                  |

| EPC           | Exception program counter. Upper 31 bits of the address of the exception-causing instruction combined with the ISA mode bit. |

| ErrorEPC      | Similar to the EPC register, except that ErrorEPC is used on Reset and NMI exceptions.                                       |

| Count         | Acts as a timer, incrementing at 1/2 the rate of CPUCLK.                                                                     |

| Compare       | Maintains a constant value compared against the Count register value.                                                        |

| PRId          | Processor revision identifier. Read-only                                                                                     |

| IER           | Manipulates the interrupt enable/disable bit in the Status register.                                                         |

| SSCR          | Indicates the previous and current shadow register sets.                                                                     |

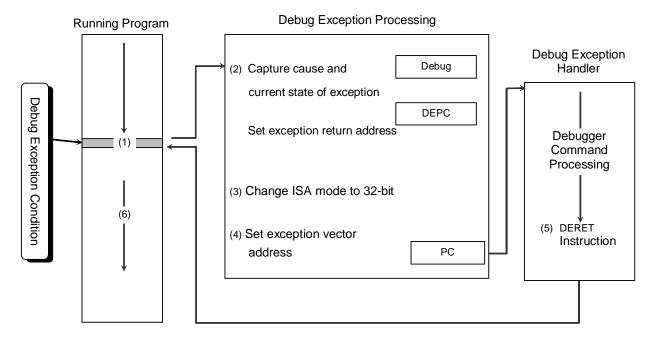

#### Table 2-3 Debug Exception Handling Registers

| Register Name | Description                                                                            |

|---------------|----------------------------------------------------------------------------------------|

| Debug         | Cause and current status of a debug exception                                          |

| DEDC          | Debug exception program counter. Upper 31 bits of the address of the instruction that  |

| DEPC          | caused a debug exception, combined with the ISA mode bit.                              |

| DESAVE        | Scratchpad register to save one of the general-purpose registers for context-switching |

#### 2.3 32-Bit and 16-Bit ISA Modes

The TX19A has two ISA modes, 16-bit and 32-bit. These operating conditions are respectively called as 16 bit ISA mode and 32 bit ISA mode. It provides an efficient run-time switching between 16-bit and 32-bit ISA modes through an instruction. Programs will consist of procedures in 16-bit mode for density or in 32-bit mode for performance.

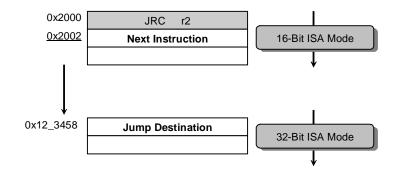

The least-significant bit of the program counter (PC) is the ISA mode bit that determines the width of instructions: 0 means 32-bit ISA and 1 means 16-bit ISA. The JALX, JR, JRC or JALRC instructions can be used to switch from 32-bit mode to 16-bit mode or vice versa.

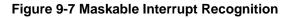

When an exception occurs while the processor is in 16-bit mode, the processor automatically switches to 32-bit mode and saves the return address together with the ISA mode bit to the EPC, ErrorEPC or the DEPC register. The ERET instruction is used to jump back to the return address contained in the EPC or ErrorEPC register. In case of a debug exception, the DERET instruction is used to jump back to the return address contained in the DEPC register.

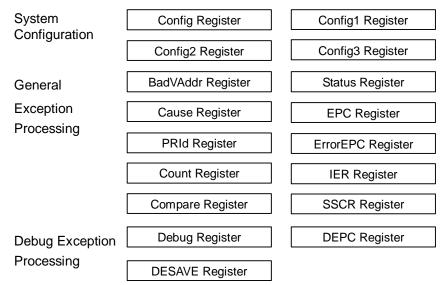

The instruction set can be divided into the groups shown in Figure 2-7.

\* New instructions in the TX19A

Figure 2-7 32-Bit and 16-Bit Instructions

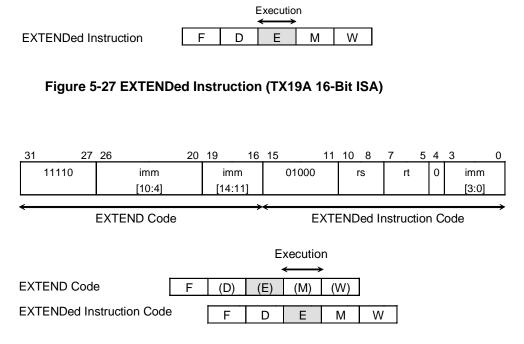

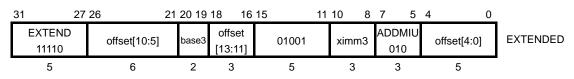

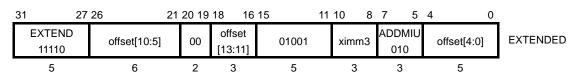

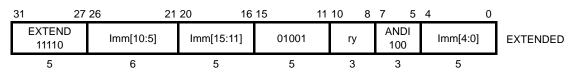

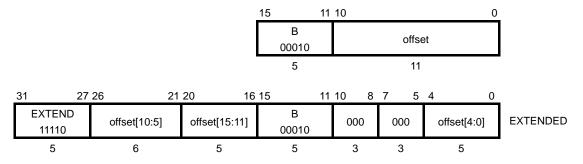

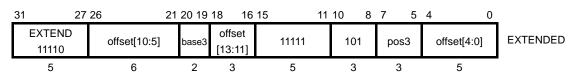

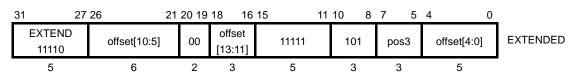

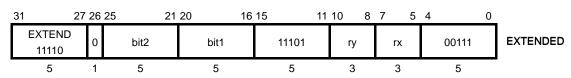

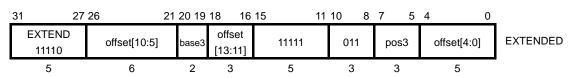

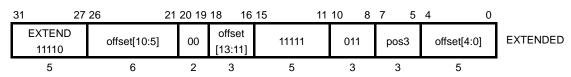

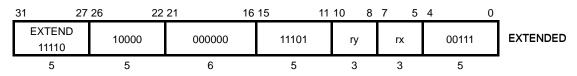

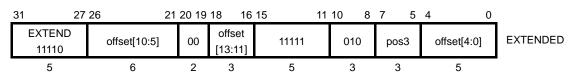

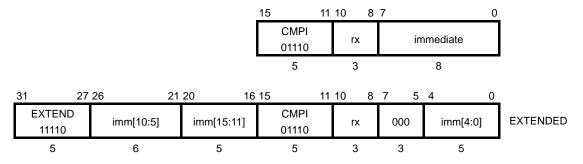

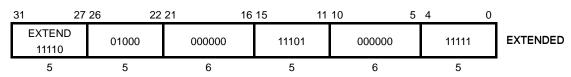

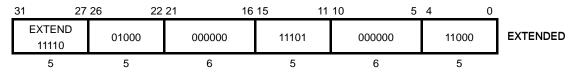

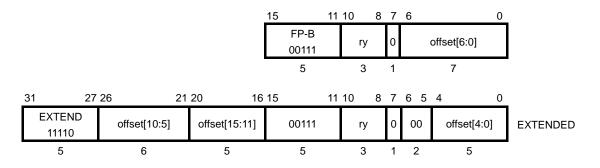

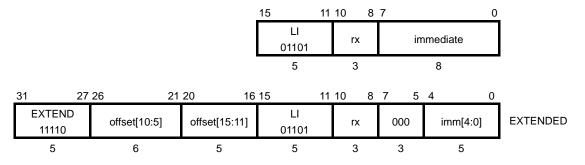

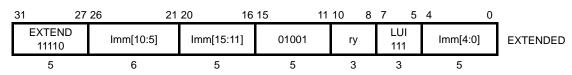

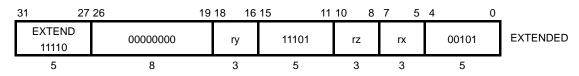

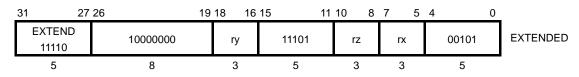

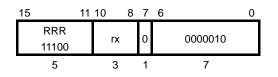

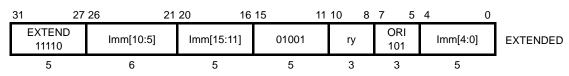

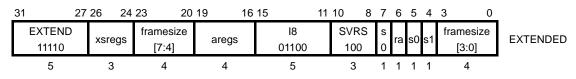

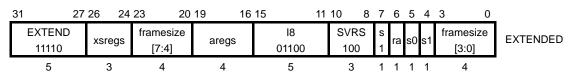

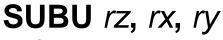

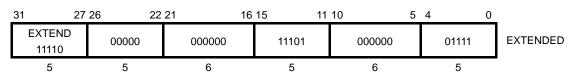

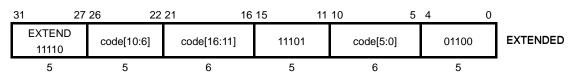

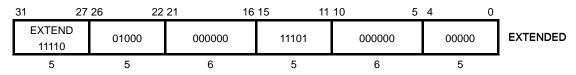

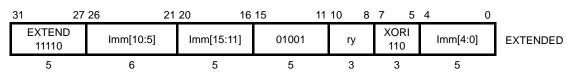

All the instruction length of 32-bit ISA is set as 32 bit. As a general rule, the instruction length of 16-bit ISA is set as 16 bit; however, it can be changed into 32 bit with a EXTEND instructions. The EXTEND instructions, of which bit size is 16, are consist of 5-bit opcodes and 11-bit immediate. In some cases, the 11-bit immediate field is replaced with an opcode. The EXTEND does not

generate a MIPS machine instruction on its own, but16-bit immediate can be used by concatenating its immediate and an immediate of a subsequent instruction.

The 16-bit ISA instruction with 32-bit instruction length is called EXTENDed instructions. The SYNC, ERET, DERET, WAIT, BS1F, MAX and MIN instructions are EXTENDed instructions and have no 16-bit equivalents.

#### 2.4 Coprocessors

Coprocessors are secondary processors used to speed up operations by handling some of workload of the main CPU.

The TX19A contains a system control coprocessor, CP0, which handles system configuration, exception handling and memory management. The basic capabilities of CP0 are incorporated into the processor core and the extended capabilities into the memory management unit (MMU). The CU0 bit in the Status register controls the usability of CP0 instructions in User mode. Coprocessor Unusable exception occurs due to CP0 instruction execution during a user-mode program when the CU0 bit is cleared. In Kernel and Debug modes, all CP0 instructions can be executed regardless of the setting of the CU0 bit.

The CU [3:1] bits in the Status register control accesses to the respective coprocessors in User mode or in Kernel mode. Attempted execution of a coprocessor instruction causes a Coprocessor Unusable exception when its CU bit is cleared.

The system control coprocessor (CP0) provides 17 user-visible registers. Chapter 8 gives a complete description of them.

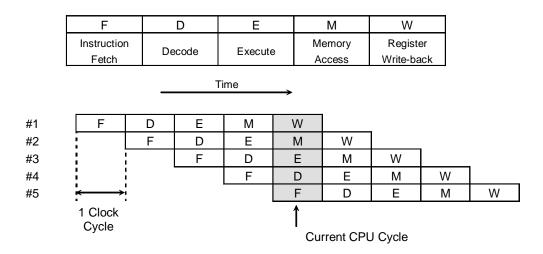

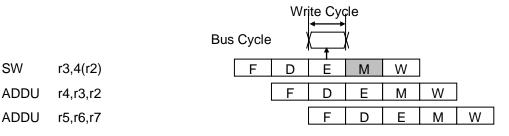

# 2.5 Pipeline Architecture

The TX19A has a five-stage pipeline. That is, the execution of each instruction consists of five primary stages. Each stage takes approximately one clock cycle; thus the execution of each instruction takes at least five cycles. (The JAL and JALX instructions in the 16-bit ISA mode take longer.) The five-stage pipeline divides the execution of each instruction into five discrete portions and executes up to five instructions simultaneously, as shown in Figure 2-8. The five pipe stages are Fetch (F), Decode (D), Execute (E), Memory Access (M) and Register Write-back (W). The TX19A achieves an instruction execution rate approaching one instruction per clock cycle.

Figure 2-8 TX19A Pipeline

#### 2.6 Write Buffer

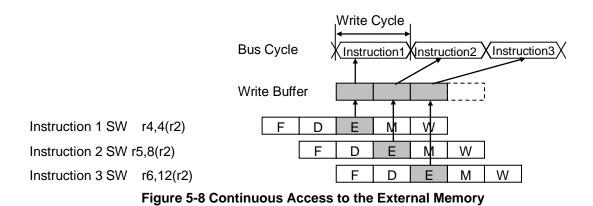

A write buffer is a FIFO buffer with 4 entries. As explained in the previous chapter, each pipeline stage takes one clock cycle if the ongoing instruction requires writing areas other than the on-chip memory. Bus cycle for writing to the area other than the on-chip memory not always takes only one clock. The write buffer function can improve performance during the program operation by coordinate the speed differences.

#### 2.6.1 Instructions for Write Buffer

Here are the instructions for the write buffer which generates write bus cycle to memory.

- All the store instructions

32ISA: SW / SH / SB / SWL / SWR

16ISA: SW / SH / SB

- A part of bit computational instructions, memory operand addition 32ISA: none 16ISA: BCLR / BSET / BINS

- Others 32ISA: none 16ISA: ADDMIU / SAVE

Note: Please refer to Appendix A"32-Bit ISA Details" and Appendix B "16-Bit ISA Details" for further details.

#### 2.6.2 Instruction Procedure

At the execution of the instruction to use the write buffer, a bus operation required for executing the instruction is placed in the write buffer. We call it as "entry in the write buffer". The entry in the write buffer is executed in the order corresponding to instruction execution.

When the write buffer has free space, it enters the bus operation if the instruction to use the write buffer is in the Execute (E) stage. The bus cycle and the entry in the write buffer starts simultaneously if there is no bus cycle executed in operand bus at that time, which means operand bus has free space. When the write buffer has no free space, the instruction stalls in the E stage until it gains appropriate free space.

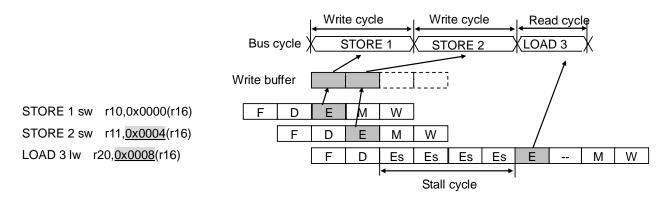

The earlier the operation is entered in the write buffer, the earlier it is executed when there is a free operand bus. The order will never be changed in the write buffer. The write bus cycle cannot be executed when there is no free operand bus. In case a subsequent instruction such as the LOAD requests the read bus cycle, the instruction stalls in the E stage until all the operations entered in the write buffer are completed.

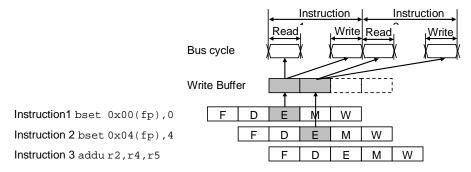

Figure 2-9 shows the procedure of the write buffer instruction. In this case, the third one is the LOAD instruction. Therefore the read bus cycle caused by the LOAD will not be executed as long as the write cycle during the write buffer operation is completed.

Figure 2-9 The procedure of the write buffer instruction

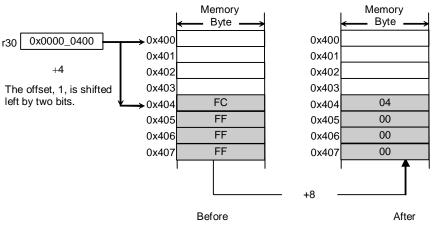

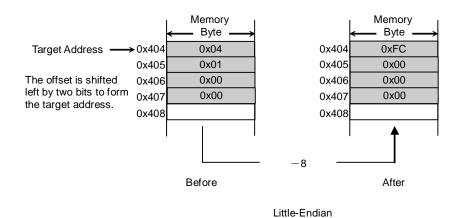

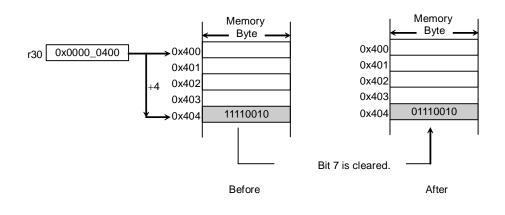

#### 2.6.3 Bit Computational Instructions/ ADDMIU Instructions

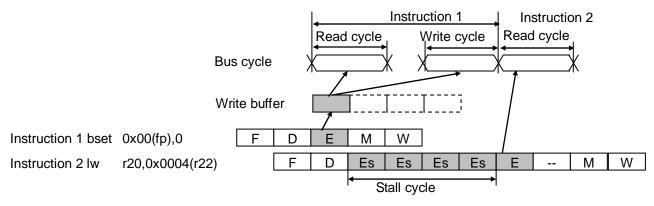

The instructions accompanied by an operand read such as a bit computational or an ADDMIU instructions initiate the operand read bus cycle. The read bus cycle and the write bus cycle are always executed in succession since these cycles must be united as a read modify write operation.

In this case, the write cycle of the bit computation gets priority over the subsequent instructions.

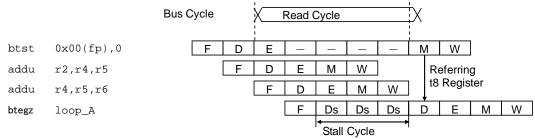

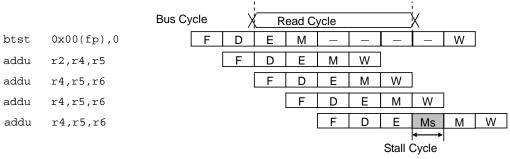

Figure 2-10 shows the procedure of the bit computational instruction.

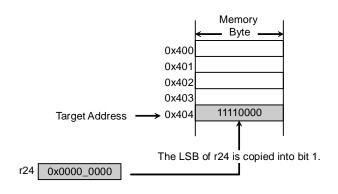

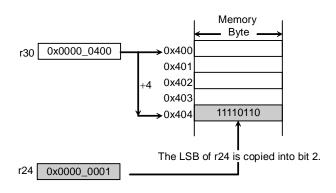

Figure 2-10 The procedure of the bit computational instruction

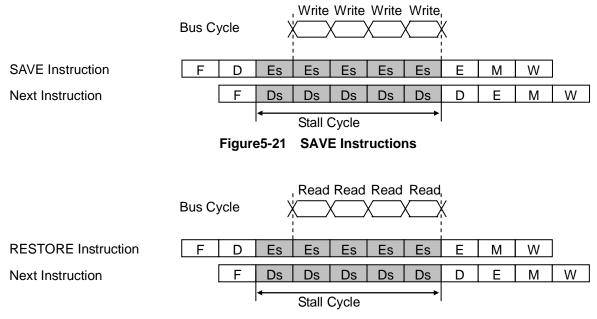

#### 2.6.4 SAVE Instruction

The SAVE instruction can generate multiple stores. The write buffer starts to enter the save instructions from the earlier store. In the meantime, the SAVE instruction can occupy the execution stage; that is to say no operation caused by other instructions will be entered in the write buffer.

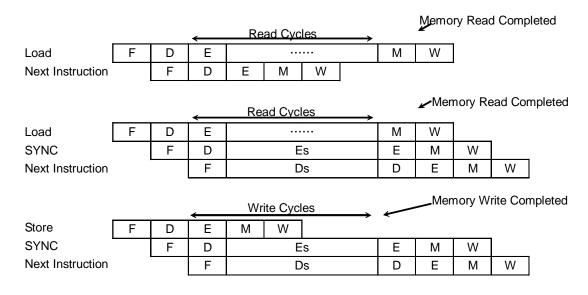

#### 2.6.5 SYNC Instructions

With the SYNC instruction, all the write bus operations entered in the write buffer to maintain the consistency of memory data are executed. The SYNC instruction is effective to synchronize the condition of memory or IO with the instruction operation since this instruction stalls until all the bus cycle caused by the entered operations are completed.

The contents in the write buffer are never automatically flashed when Interrupt/ Exception takes place or bus is opened. Consistency must be maintained by the SYNC instruction depend on the situation.

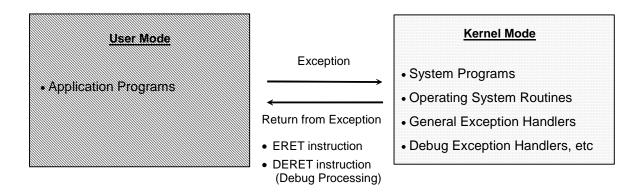

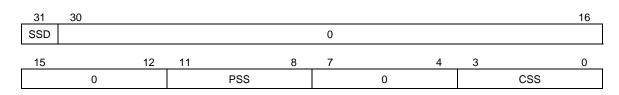

#### 2.7 Memory Management Summary

The TX19A has two modes of operation, User mode and Kernel mode. The TX19A enters Kernel mode whenever an exception is taken. Since a reset exception occurs when a system is reset, the TX19A wakes up in Kernel mode. The processor switches to User mode when the ERET (Exception Return) or DERET (Debug Exception Return) instruction is executed.

Figure 2-11 Operating Modes

The operating mode determines the addresses, registers and instructions that are available to a program. Kernel mode has higher privileges than User mode. Kernel-mode programs are permitted to use all addresses, registers and instructions, but a User-mode program's use of them are restricted. Operating system routines, general exception handlers and debug exception handlers are executed in Kernel mode. This scheme allows the kernel to protect system resources from uncontrolled access.

Note: TX19A only allows using Kernel mode.

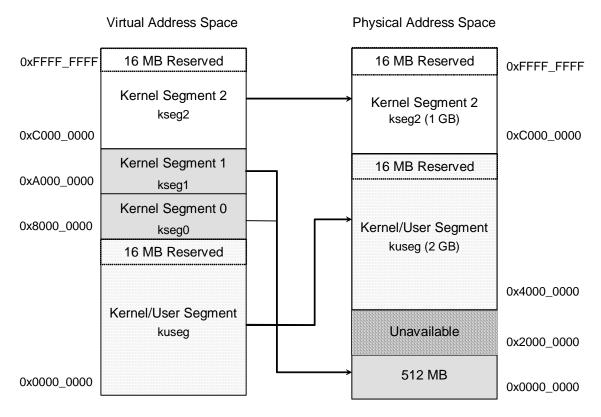

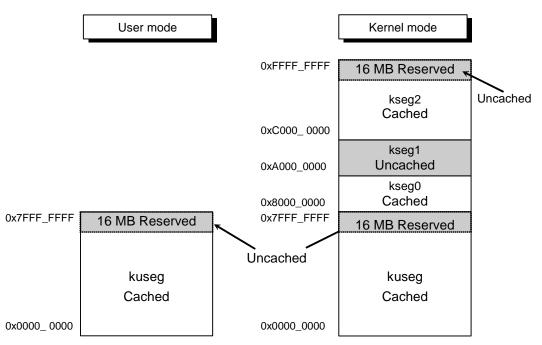

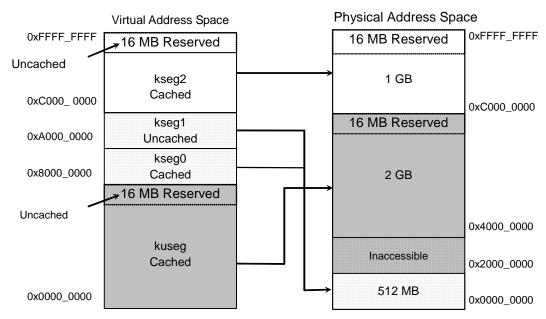

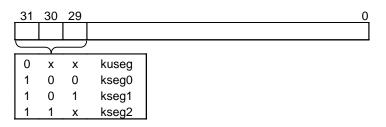

The TX19A does not contain a translation lookaside buffer (TLB). Instead, the memory management unit (MMU) of the TX19A uses the direct segment mapping method. The mapping of virtual addresses to physical addresses is shown in Figure 2-12. The virtual address space is partitioned into four, fixed-size segments. kuseg is designed to be used by User-mode programs while it is accessible in Kernel mode. The other three segments, kseg0, kseg1 and kseg2, are available only to Kernel-mode programs. Chapter 6 describes the memory management features in greater details.

Figure 2-12 Virtual-to-Physical Address Mapping

# **Chapter 3 32-Bit ISA Summary and Programming Tips**

This chapter gives an overview of the instructions and addressing modes supported by the TX19A in 32-bit ISA mode. This chapter also presents many programming tips using 32-bit instructions. Instructions are grouped into the following categories:

- Load and store instructions

- Computational instructions

- Jump, branch and branch-likely instructions

- System control coprocessor (CP0) instructions

- Special instructions

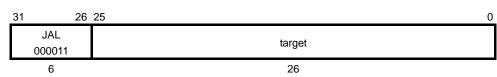

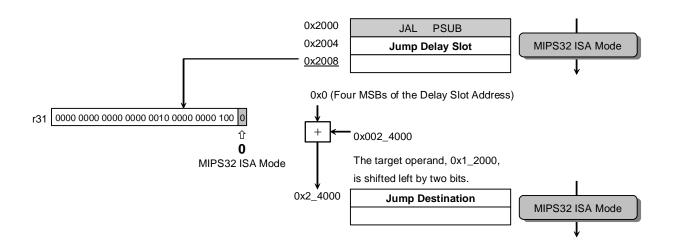

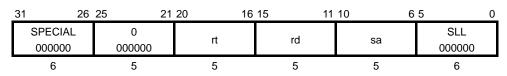

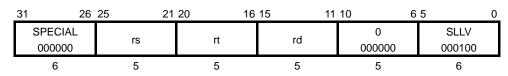

# 3.1 Instruction Formats

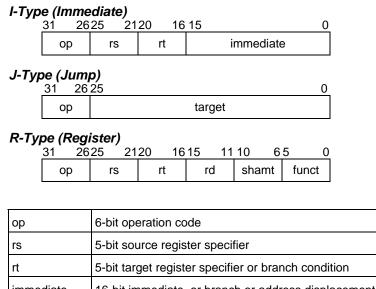

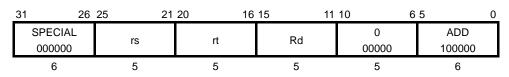

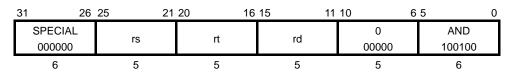

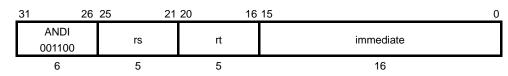

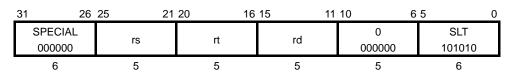

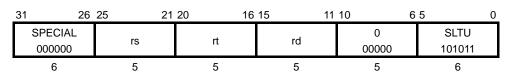

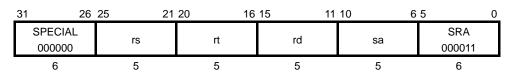

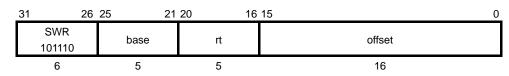

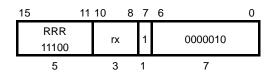

All TX19A instructions for the 32-bit ISA mode are 32-bits wide. There are three instruction formats as shown in Figure 3-1. Limiting instruction formats to these three dramatically simplifies instruction decoding. More complex instructions are synthesized by the compiler. All the 32-bit instructions must be aligned on a word boundary.

| rt        | 5-bit target register specifier or branch condition          |

|-----------|--------------------------------------------------------------|

| immediate | 16-bit immediate, or branch or address displacement (offset) |

| target    | 26-bit jump target address                                   |

| rd        | 5-bit destination register specifier                         |

| shamt     | 5-bit shift amount                                           |

| funct     | 6-bit function code                                          |

**Figure 3-1 Instruction Formats**

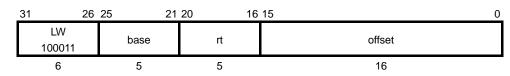

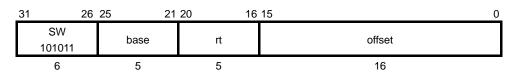

### 3.2 Load and Store Instructions

Load and store instructions move data between memory and CPU general registers. Load and store instructions can only load from memory into registers or store registers into memory locations. There is no direct way of doing arithmetic or logical operations between registers and the contents of memory.

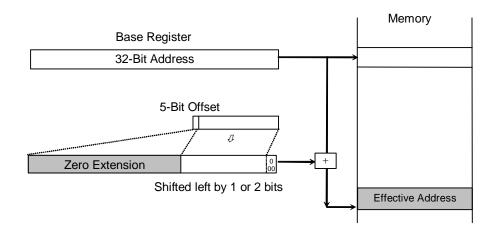

#### 3.2.1 Load and Store Address Calculation

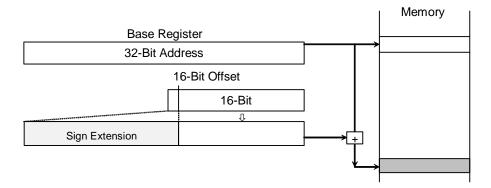

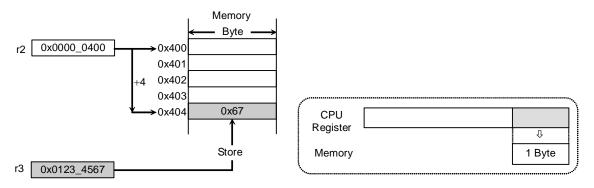

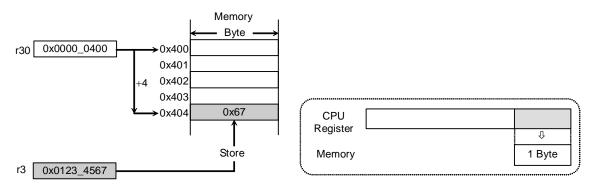

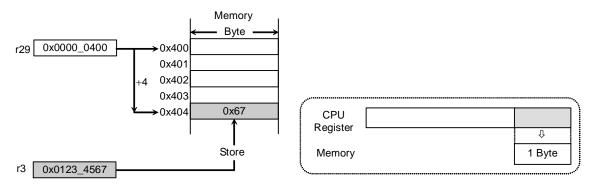

In 32-bit ISA mode, all load and store instructions are encoded as I-type instructions. They generate effective addresses using register indirect with offset addressing mode, as shown in Figure 3-2. The 16-bit immediate is sign-extended to 32 bits and added to the contents of a general-purpose register to generate the effective address. For example, in the instruction LW r9, 4(r8)

4 (binary 0100) is the offset, r8 is a general-purpose register containing the base address, and r9 is the target register.

This addressing mode shown in figure 3-2 can be used to implement immediate addressing using r0 as the base register or register direct addressing using an offset value of zero.

Figure 3-2 Register Indirect with Offset Addressing

# 3.2.2 Load and Store Instructions for Aligned Accesses

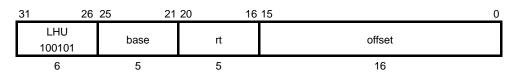

Table 3-1 gives the load and store instructions to perform byte, halfword and word accesses. The LB and LH instructions sign-extend the loaded byte and halfword. The LBU and LHU instructions, which have the "U" (unsigned) suffix, zero-extend the loaded byte and halfword.

| Data Type | Unsigned Load | Signed Load | Store |  |

|-----------|---------------|-------------|-------|--|

| Byte      | LBU           | LB          | SB    |  |

| Halfword  | LHU           | LH          | SH    |  |

| Word      | LW            | _           | SW    |  |

Table 3-1 Load and Store Instructions for Aligned Accesses

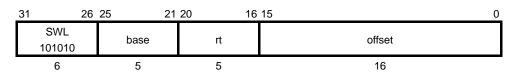

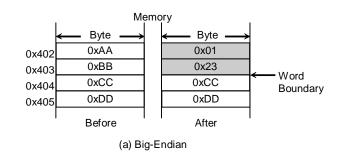

# 3.2.3 Load and Store Instructions for Misaligned Accesses

An Address Error exception occurs when an instruction to load or store halfword or word that is not aligned on the natural alignment boundary is executed. Table 3-2 gives the instructions to perform loads and stores when the bytes in a word cross the natural boundary between two words. The LWL (Load Word Left) and LWR (Load Word Right) instructions are used in a pair. Likewise, the SWL (Store Word Left) and SWR (Store Word Right) instructions are used in a pair. These instructions provide a more efficient way of dealing with misaligned data than using a sequence of load/store and shift operations. They are useful for reusing old programs written for 8- and 16-bit machines.

Table 3-2 Load and Store Instructions for Misaligned Accesses

|                     | Signed Load | Store |  |  |

|---------------------|-------------|-------|--|--|

| Left (Upper Bytes)  | LWL         | SWL   |  |  |

| Right (Lower Bytes) | LWR         | SWR   |  |  |

# 3.2.4 Memory Synchronization Instruction

The memory synchronization instruction, SYNC, guarantees the sequence of memory references by interlocking the instruction pipeline until loads, stores and instruction fetches performed prior to the present instruction are completed before loads or stores after this instruction are allowed to start.

# 3.2.5 32-Bit Address Generation

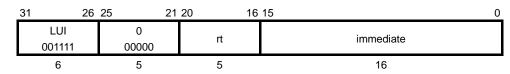

In 32-bit ISA mode, load and store instructions can only take a 16-bit signed immediate as an offset. The most-significant bit is the sign. A total of 15 bits designate the magnitude. This gives a range of -32768 to +32767. If the offset is outside this range, you must put it in a general register prior to the load or store instruction. Three examples are given below.

• Example 1: Base address + 32-bit offset

In the example below, the ADDU (Add Unsigned) instruction is used to add the offset held in register r5 to the base address in register r4. The result is placed back into r4. Then the LW instruction uses r4 as the base register to address a memory location.

```

ADDU r4,r4,r5

LW r6,0(r4)

```

• Example 2: Base address + 32-bit offset

In the example below, the LUI (Load Upper Immediate) instruction loads the 16-bit immediate (in this case, the upper 16 bits of the offset) into the upper 16 bits of register r5. The lower 16 bits of r5 are filled with zeros. Then ADDU (Add Unsigned) instruction is used to add r5 to the base address in r4. This way, the LW instruction can address a desired memory location by only using the lower 16 bits of the offset.

```

LUI r5,0x12

ADDU r4,r4,r5

LW r6,0x3454(r4)

```

• Example 3: Arbitrary 32-bit absolute address

In the example below, the LUI (Load Upper Immediate) instruction loads the 16-bit immediate into the upper 16 bits of register r4. The ADDIU (Add Immediate Unsigned) instruction adds r4 to the lower 16 bits of the offset, 0x3456. The LW instruction can then use r4 to directly address the desired memory location, with an offset of zero.

```

LUI r4,0x12

ADDIU r4,r4,0x3456

LW r6,0(r4)

```

LUI r4,0x1

| 2     | 0 | 0 | 1 | 2 | 0 | 0 | 0 | 0 |

|-------|---|---|---|---|---|---|---|---|

|       | 0 | 0 | 0 | 0 | 3 | 4 | 5 | 6 |

| ADDIU |   |   |   |   |   |   |   |   |

|       | 0 | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

# 3.3 Computational Instructions

This section describes the computational instructions available in the 32-bit ISA. Section 3.3.1 provides a category of computational instructions. Section 3.3.2 discusses computations that involve the use of 32-bit constants. Section 3.3.3 gives program examples to illustrate how to perform 64-bit addition and subtraction. In Section 3.3.4, we observe how to detect the integer overflow without using exception. In Section 3.3.5, we look at ways to execute a 64-bit x 64-bit multiply operation. Section 3.3.6 describes how to implement rotate operations using available instructions.

# 3.3.1 Overview of Computational Instructions

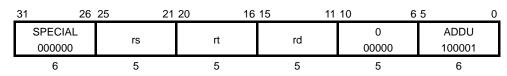

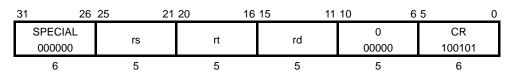

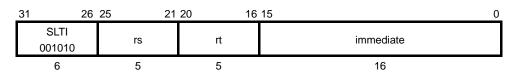

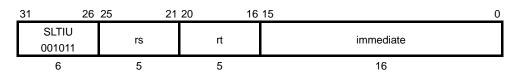

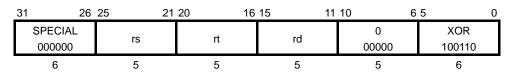

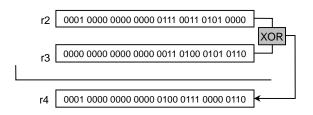

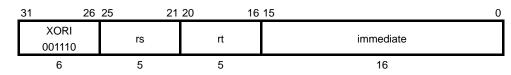

Computational instructions in the 32-bit ISA are categorized into five groups shown in Table 3-3. They consist of arithmetic, compare, logical, shift, multiply, divide and multiply-and-add instructions. Computational instructions use I-type format in which one operand is a 16-bit immediate or R-type format which take two or three register operands.

| Category             | Instructions          | Opcode                    |  |  |

|----------------------|-----------------------|---------------------------|--|--|

| ALU Immediate        | Add                   | ADDI · ADDIU              |  |  |

|                      | Set On Less Than      | SLTI · SLTIU              |  |  |

|                      | Logical AND           | ANDI                      |  |  |

|                      | Logical OR            | ORI                       |  |  |

|                      | Logical XOR           | XORI                      |  |  |

|                      | Load Upper Immediate  | LUI                       |  |  |

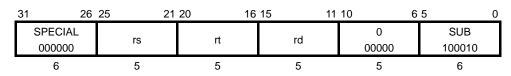

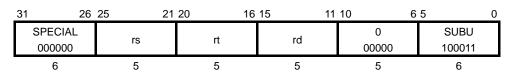

| 2- and 3-Operand     | Add                   | ADD · ADDU                |  |  |

| Register-Type        | Subtract              | SUB · SUBU                |  |  |

|                      | Set On Less Than      | SLT · SLTU                |  |  |

|                      | Logical AND           | AND                       |  |  |

|                      | Logical OR            | OR                        |  |  |

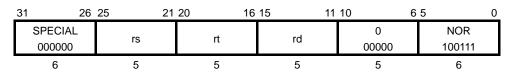

|                      | Logical XOR           | XOR                       |  |  |

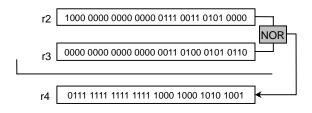

|                      | Logical NOR           | NOR                       |  |  |

|                      | Count                 | CLO · CLZ                 |  |  |

|                      | Conditional Move      | MOVN · MOVZ               |  |  |

| Shift                | Logical Shift         | SLL · SLLV · SRL · SRLV   |  |  |

|                      | Arithmetic Shift      | SRA · SRAV                |  |  |

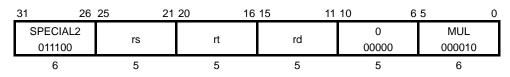

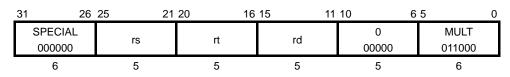

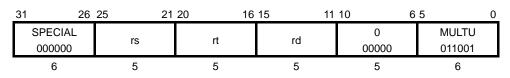

| Multiply and Divide  | Multiply              | MULT • MULTU • MUL        |  |  |

|                      | Divide                | DIV • DIVU                |  |  |

|                      | Move From/To HI/LO    | MFHI · MFLO · MTHI · MTLO |  |  |

| Multiply-and-Add and | Multiply-and-Subtract | MADD·MADDU·MSUB·MSUBL     |  |  |

**Table 3-3 Computational Instructions**

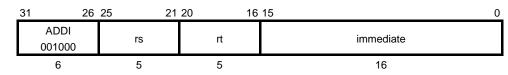

In ALU immediate instructions, the source operands are a general-purpose register and a 16-bit signed immediate. For example, the Add Immediate instruction, "ADDI rd, rs, *immediate*," adds the contents of the source register (rs) and the sign-extended immediate, then places the result into the destination register (rd).

Two- and three-operand Register-type instructions manipulate the values held in two general purpose registers and place the result into a general-purpose register.

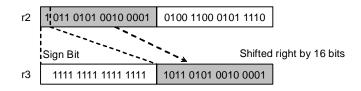

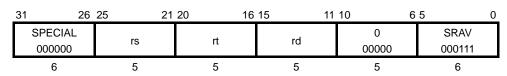

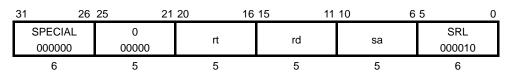

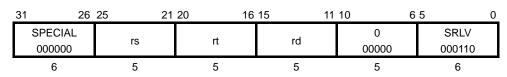

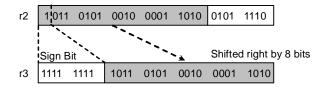

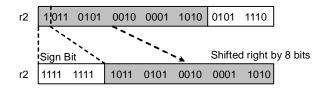

Shift instructions shift the contents of a general-purpose register right or left by the specified

number of bits. There are two kinds of shift: logical and arithmetic. The Shift Variable instructions (SLLV, SRLV, and SRAV) do not have the shift amount (*shamt*) field; instead they specify a general purpose register containing a desired shift amount.

Multiply and divide instructions operate on integer values in two general-purpose registers and place the result into special registers HI and LO. Generally, CPU instructions do not have access to the HI and LO registers. In the MIPS architecture, the MFHI, MFLO, MTHI and MTLO instructions are always required to move data between a general-purpose register and the HI or LO register. However, the TX19A provides an extension to the MIPS architecture to allow the lower 32 bits of the product to be placed into both the LO register and a general-purpose register at a time. Section 3.3.5, *64-Bit x 64-Bit Multiplication*, presents an application example of this extension.

Multiply-and-add and multiply-and-subtract instructions multiply two 32-bit numbers, followed by the addition/subtraction of this product to/from the 64-bit value in the HO/LO registers. The lower 32 bits of the result can be optionally copied into a general-purpose register simultaneously. The MAC unit executes the integer multiply-and-add and multiply-and-subtract operations at an accelerated speed. It is designed to provide a common set of digital signal processing (DSP) operations.

# 3.3.2 32-Bit Constants

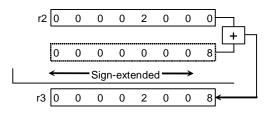

The immediate field in the I-type instructions is only 16-bits long. If the immediate value is greater than 16 bits, you need to use two instructions to create a 32-bit constant and put it in a general register temporarily. In the example below, the LUI (Load Upper Immediate) instruction loads the immediate value into the upper 16 bits of r4 and fills the lower 16 bits with zeros. The ORI (OR Immediate) instruction zero-extends the immediate value, logical-ORs it with the contents of r4 and places the result back into r4.

```

LUI r4,0x12

ORI r4,r4,0x3456

```

LUI r4,0x12

|   | 0 | 0 | 1 | 2    | 0 | 0 | 0 | 0 |

|---|---|---|---|------|---|---|---|---|

| 1 | 0 | 0 | 0 | 0    | 3 | 4 | 5 | 6 |

|   |   |   | С | DRI, | 7 |   |   |   |

|   | 0 | 0 | 1 | 2    | 3 | 4 | 5 | 6 |

The following is an example of adding a 32-bit constant to the contents of a general register. The LUI instruction loads the upper 16 bits of r5 with 0x1234 and sets the lower 16 bits to 0x0000. Adding it to 0x5678 with the ADDIU (Add Immediate Unsigned) instruction gives 0x12345678 that is placed back into r5. Finally, the ADDU (Add Unsigned) instruction adds the contents of r4 and r5 together

and puts the result in r6.

```

LUI r5,0x1234

ADDIU r5,r5,0x5678

ADDU r6,r4,r5

```

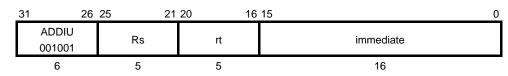

**Note**: The ADDI and SLTI instructions sign-extend the immediate value to 32 bits. Although ADDIU and SLTIU stand for Add Immediate *Unsigned* and Set On Less Than Immediate *Unsigned*, they also *sign*-extend the immediate value to 32 bits. The only difference between the ADDI and ADDIU instructions is that ADDIU never causes an overflow exception. Therefore, you can use the ADDIU instruction to add a negative number to the contents of a general register without being worried about a possible overflow. It is useful since there is no Subtract Immediate instruction in the instruction set. The only difference between the SLTI and SLTIU instructions is that SLTI compares two values (*rs* and sign-extended *immediate*) as signed integers while SLTIU compares two values (*rs* and sign-extended *immediate*) as unsigned integers.

# 3.3.3 64-Bit Addition and Subtraction

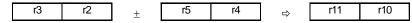

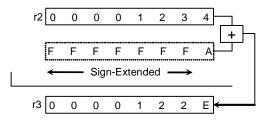

In some cases, the numbers being added or subtracted can be more than 32-bits long. Since general purpose registers are only 32-bits wide, it is the job of the programmer (or the compiler) to write the code to break down large numbers into smaller chunks to be processed by the CPU. Figure 3–3 illustrates this. In Figure 3–3, r3 contains the upper 32 bits of a 64-bit constant, and r2 contains the lower 32 bits of that 64-bit constant. Likewise, r5 and r4 together contain a 64-bit constant.

#### Figure 3-3 64-Bit Addition and Subtraction

#### Add with Carry

Below is an example of code to add two 64-bit constants together:

```

ADDU r10,r2,r4 \# r10 \leftarrow r2 + r4

SLTU r11,r10,r2 \# r11=1 if r10 (sum) is less than r2

ADD(U) r11,r11,r3 \# r11 \leftarrow r11 (carry) + r3

ADD(U) r11,r11,r5 \# r11 \leftarrow r11 + r5

```

The first ADDU instruction adds the lower 32 bits of two constants together and puts the result in r10. The TX19A architecture does not provide a flag bit to indicate whether an arithmetic operation results in a carry-out. Therefore, it is necessary to somehow record an occurrence of a carry-out resulting from an addition. In the case of two positives together, a carry-out occurred if the sum is less than one of the operands added. Then the next SLTU (Set on Less Than Unsigned) instruction sets r11 to 1 if r10 is less than r2. The following two ADD(U) instructions add the carry-out bit (1 or 0) and the upper

32 bits of the two 64-bit constants.

The last two instructions can be either ADD or ADDU. The only difference between these two instructions is that ADDU (Add Unsigned) never causes an integer overflow exception. When you use the ADDU instruction, you need to write the code to explicitly test for an occurrence of the overflow condition. This is discussed in the next section.

#### Subtract with Borrow

In 64-bit subtraction, the code must take care of the borrow of the lower operand. The technique for performing subtract-with-borrow is quite similar to add-with-carry. Below is an example of code to subtract a 64-bit constant from a 64-bit constant.

```

SLTU r8,r2,r4 \# r8=1 if r2 is less than r4

SUBU r10,r2,r4 \# r10 \leftarrow r2 - r4

SUB(U) r11,r3,r5 \# r11 \leftarrow r3 - r5

SUB(U) r11,r11,r8 \# r11 \leftarrow r11 - r8 (borrow)

```

First of all, the SLTU instruction checks if r2 (minuend) is smaller than r4 (subtrahend). If it is, r8 is set to 1. That is, if there is a borrow resulting from the subtraction of the lower 32 bits, its occurrence is recorded in r8. The content of r8 is subtracted in the last SUB(U) instruction.

Again, the only difference between the SUB and SUBU instructions is that SUBU (Subtract Unsigned) never causes an integer overflow exception.

#### 3.3.4 Testing for an Integer Overflow

As explained in the previous section, the signed add and subtract instructions, ADD and SUB, generate an overflow exception if the addition/subtraction resulted in a two's-complement overflow. On the other hand, the unsigned add and subtract instructions, ADDU and SUBU, never cause an overflow exception. If it is necessary to detect signed overflow without using exceptions or to detect overflow for unsigned operations, you need to write a software routine to check for overflow. It should be observed that, during addition, overflow occurs if the signs of the operands are the same and the sign of the sum is different. Below is an example of code that checks for overflow resulting from signed addition:

No\_Ov:

During subtraction, overflow occurs if the signs of the operands are not the same and the sign of the remainder is not the same as the sign of the minuend. Below is an example of code that checks for overflow resulting from signed subtraction:

#### 3.3.5 64-Bit x 64-Bit Multiplication

In multiplying two integer numbers in the TX19A, they must be in general-purpose registers. In doubleword-by-doubleword multiplication, each 64-bit operand takes two registers since all general purpose registers are only 32-bits wide.

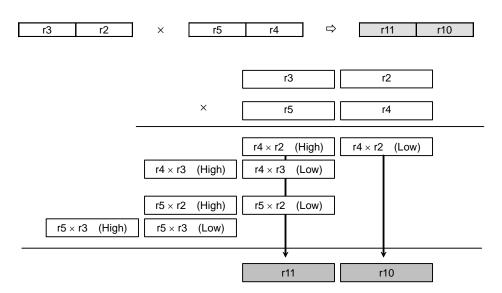

In Figure 3-4, the upper 32 bits of the multiplicand is placed in r3 and the lower 32 bits of it is in r2. Likewise, the multiplier is put in r5 and r4.

Figure 3-4 64-Bit x 64-Bit Multiplication

The following shows an example of code that performs 64-bit by 64-bit multiplication. Although the product can be a maximum of 128-bits long, the code below only deals with the lower two words of the product for the sake of simplicity.

```

MULTU r10,r2,r4 \# r4 x r2, Copy low word of product to r10

MFHI r11 \# Copy high word of product to r11

MULTU r9,r3,r4 \# r3 x r4, Copy low word of product to r9

ADDU r11,r11,r9 \# r11 \leftarrow r11 + r9

```

MULTU r9,r2,r5 # r5 x r1, Copy low word of product to r9 ADDU r11,r11,r9 # r11  $\leftarrow$  r11 + r9

Note that there is a slight difference in the functionality of the MULTU (Multiply Unsigned) instruction between the MIPS and the TX19A architectures. In the MIPS processor, MULTU is a two-operand instruction that specifies two source registers holding the multiplicand and the multiplier. The 64-bit doubleword product is placed into the HI and LO registers. In the TX19A, however, the MULTU can take a third operand. In the TX19A, MULTU can optionally copy the low-order word of the product to a general-purpose register. This eliminates the need to use the MFLO (Move From LO) instruction to move the contents of the LO register to a general register. The MFHI (Move From HI) instruction moves the contents of the HI register, i.e., the high-order word of the product, to a general register.

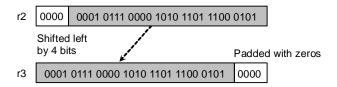

#### 3.3.6 Rotate Instructions

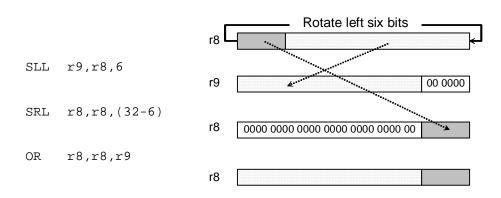

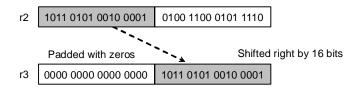

In the TX19A, there are no rotate instructions at the machine level although it has the shift instructions instead. In shift left, bits that exit the left end (the right end in the case of shift right) are discarded and zeros are supplied to the vacated bits on the right (on the left in the case of shift right). In rotate left, as bits are shifted from right to left (from left to right in the case of rotate right), they exit from the left end, MSB, and enter the right end, LSB, (the left end in the case of rotate right). In the TX19A, a rotate operation must be implemented using shift and logical-OR instructions. Figure 3-5illustrates how to do this.

Figure 3-5 Rotate Left by 6 Bits

In Figure 3-5, the SLL (Shift Left Logical) instruction shifts the contents of r8 left by six bits and puts the result in r9. The low-order bits are filled with zeros. Next, the SRL (Shift Right Logical) instruction is used to shift r8 right by 26 (32-6) bits. Finally, the OR instruction logical-ORs the contents of r8 and r9 and puts the result back in r8. The outcome is equivalent to rotating r8 by six bits.

### 3.4 Jump, Branch and Branch-Likely Instructions

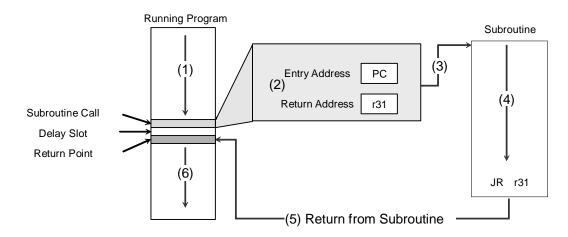

It is often necessary to transfer program control to a different location in the sequence of instructions. There are many instructions to achieve this. The TX19A provides jump, branch and branch-likely instructions. Section 3.4.1 overviews these instructions. Section 3.4.2 describes the addressing modes supported by the jump, branch and branch-likely instructions. Section 3.4.3 explains how to switch from 32-bit ISA mode to 16-bit ISA mode, or vice versa. In Section 3.4.4, the differences between regular branch instructions and branch-likely instructions are explained. Section 3.4.5 provides programming tips for branching on arithmetic comparisons. Section 3.4.6 describes a technique for jumping to 32-bit addresses. Section 3.4.7 describes subroutine calls and returns.

### 3.4.1 Overview of Jump, Branch and Branch-Likely Instructions

In the TX19A, jump instructions are used to unconditionally transfer program control to the target location whereas branch and branch-likely instructions are what many microprocessors call conditional jumps and are used to transfer control to a new location only when a certain condition is met. Table 3-4 and Table 3-5 show the opcodes of the jump, branch and branch-likely instructions in the 32-bit ISA.

| Opcode | Name                   | Addressing        | Format |

|--------|------------------------|-------------------|--------|

| J      | Jump                   | Paged absolute    | I-type |

| JAL    | Jump And Link          | Paged absolute    | I-type |

| JALX   | Jump And Link exchange | Paged absolute    | I-type |

| JR     | Jump Register          | Register indirect | R-type |

| JALR   | Jump And Link Register | Register indirect | R-type |

Table 3-4 Jump Instructions (32-Bit ISA)

| Opcode    | Name                                                      | Condition      | Addressing  | Format |

|-----------|-----------------------------------------------------------|----------------|-------------|--------|

| В         | Unconditional Branch                                      | always         | PC-relative | I-type |

| BAL       | Branch And Link                                           | always         | PC-relative | I-type |

| BEQ(L)    | Branch On Equal (Likely)                                  | rs = rt        | PC-relative | I-type |

| BNE(L)    | Branch On Not Equal (Likely)                              | rs≠rt          | PC-relative | I-type |

| BGTZ(L)   | Branch On Greater Than Zero (Likely)                      | <i>r</i> s > 0 | PC-relative | I-type |

| BGEZ(L)   | Branch On Greater Than or Equal To Zero (Likely)          | <i>r</i> s ≥ 0 | PC-relative | I-type |

| BLTZ(L)   | Branch On Less Than Zero (Likely)                         | <i>r</i> s < 0 | PC-relative | I-type |

| BLEZ(L)   | Branch On Less Than or Equal To Zero (Likely)             | <i>r</i> s ≤ 0 | PC-relative | I-type |

| BLTZAL(L) | Branch On Less Than Zero And Link (Likely)                | <i>r</i> s < 0 | PC-relative | I-type |

| BGEZAL(L) | Branch On Greater Than or Equal To Zero And Link (Likely) | <i>r</i> s ≥ 0 | PC-relative | I-type |

Table 3-5 Branch and Branch-Likely Instructions (32-Bit ISA)

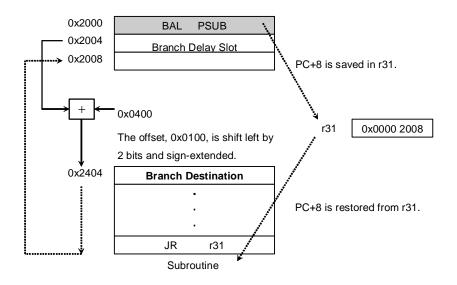

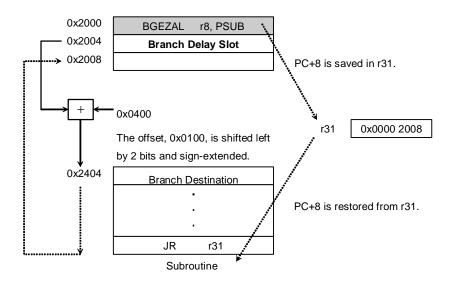

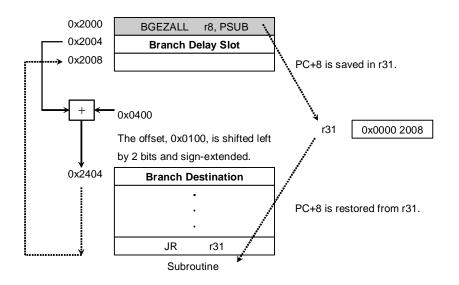

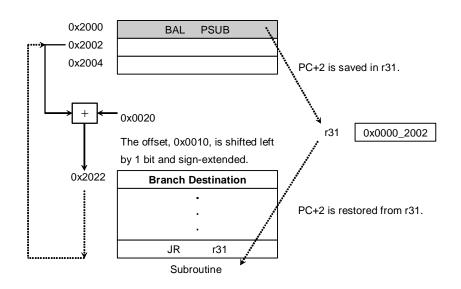

Jump-and-link instructions and branch-and-link instructions save a return address in register r31. They are typically used for subroutine calls.

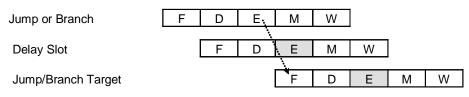

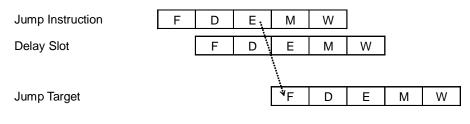

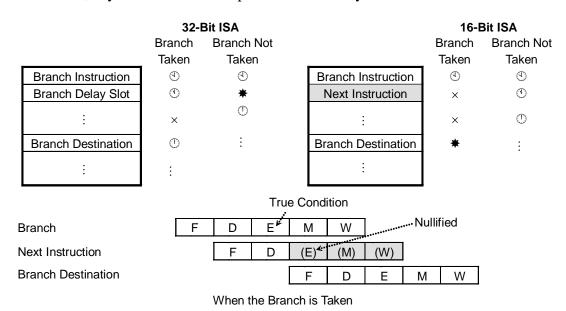

With the jump and regular branch instructions, the instruction immediately following the jump or branch is always executed while the target instruction is being fetched from memory. This is true to all regular branch instructions regardless of whether the branch is to be taken or not. On the other hand, branch-likely instructions execute the instruction in the delay slot only when the branch is taken; if the branch is not taken, the instruction in the delay slot is nullified. For the jump and branch delay slots, see Chapter 5, *CPU Pipeline*.

### 3.4.2 Jump and Branch Address Calculation

As shown in Table 3-4 and Table 3-5, jump, branch and branch-likely instructions compute the effective address of the next instruction using the following addressing modes.

- Paged absolute

- Register indirect

- PC-relative with offset

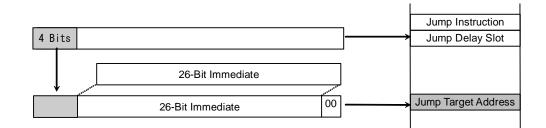

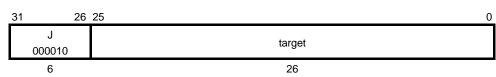

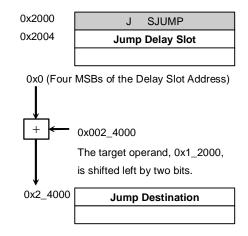

#### Paged Absolute Addressing

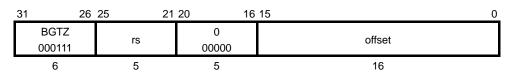

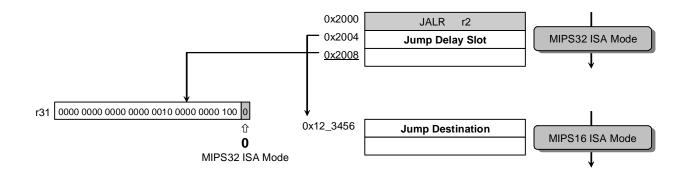

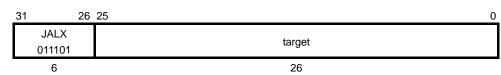

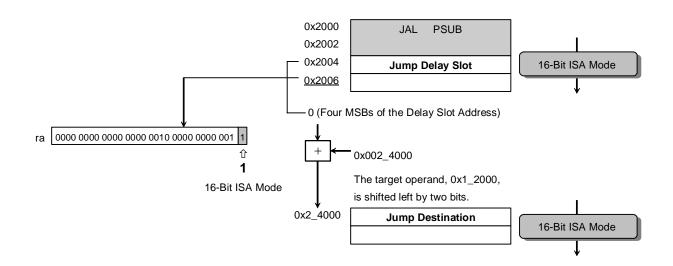

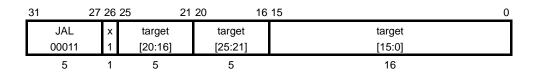

The J, JAL and JALX instructions unconditionally transfer program control to a target address using paged absolute addressing. They generate the next instruction address by shifting the 26-bit immediate operand by two bits and merging the resultant value with the four most-significant bits of the program counter (PC). Figure 3-6 shows how the jump target address is generated by paged absolute addressing. The target address for a jump is computed from the

address of the instruction immediately following the jump instruction, i.e., the address of the jump delay slot. The four most-significant bits of the PC indicate a specific page in a 16-page address space.

#### Figure 3-6 Paged Absolute Addressing (32-Bit ISA Mode)

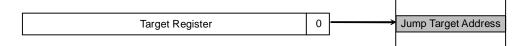

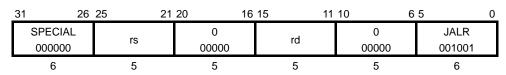

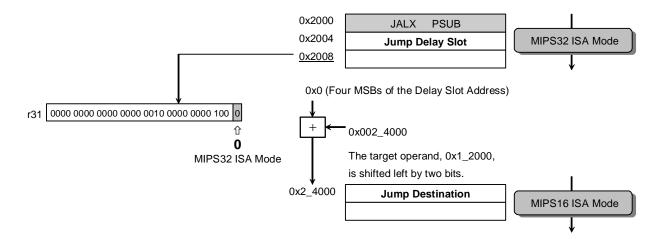

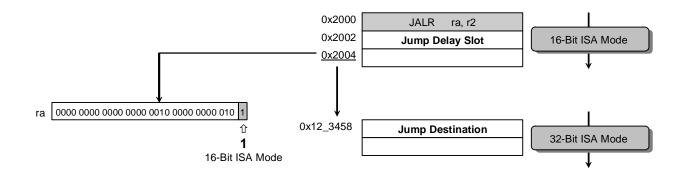

#### Register Indirect Addressing

The JR and JALR instructions unconditionally transfer program control to a target address using a 32-bit absolute address held in a general-purpose register. The effective address is generated by clearing the least-significant bit of the specified target register to zero. Since instructions must be word-aligned, the JR and JALR instructions must specify a target register of which two least-significant

bits are zero.

Figure 3-7 Register Indirect Addressing (32-Bit ISA Mode)

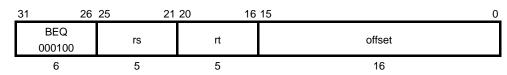

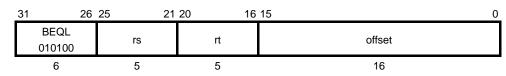

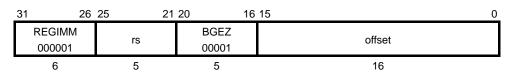

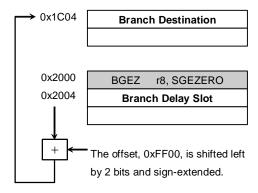

#### PC-Relative with Offset Addressing

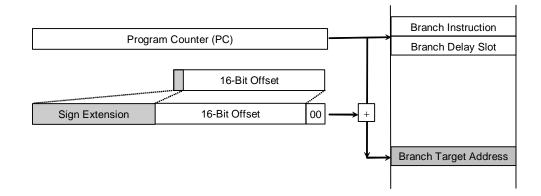

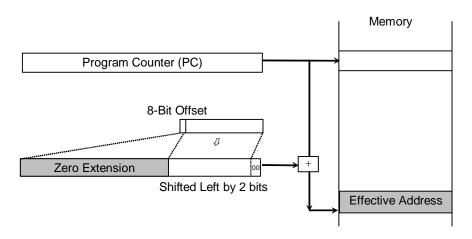

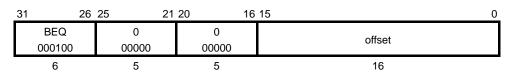

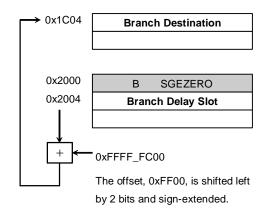

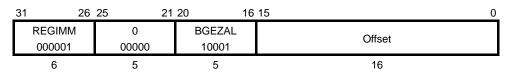

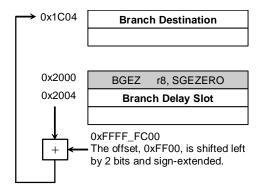

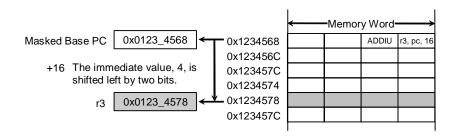

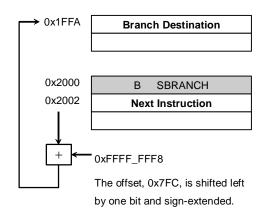

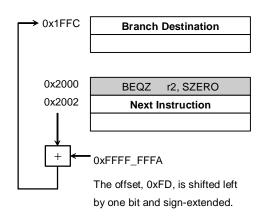

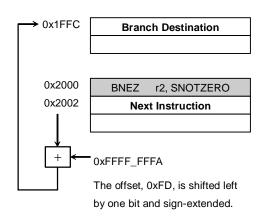

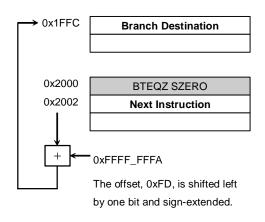

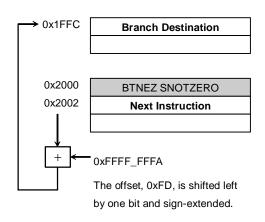

All the branch and branch-likely instructions transfer program control to a target address using a PC-relative address. They generate the next instruction address by sign-extending and appending b'00 to the 16-bit immediate displacement (offset) operand, and adding the resultant value to the contents of the program counter (PC). Figure 3-8 shows how the branch target address is generated. The target address for a branch is computed from the address of the instruction immediately following the branch instruction, i.e., the address of the branch delay slot.

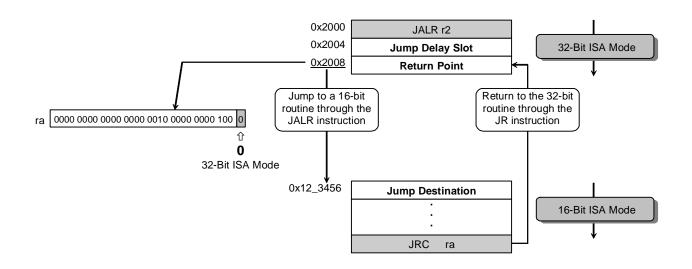

### 3.4.3 Run-Time Switching of the ISA Modes

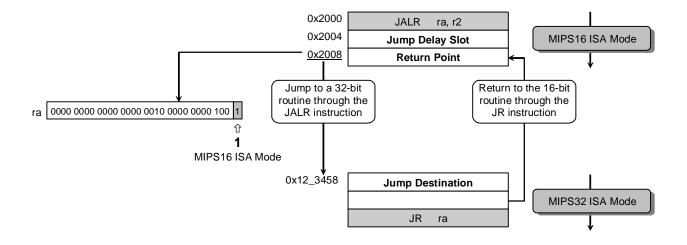

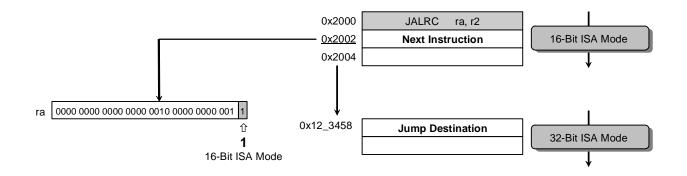

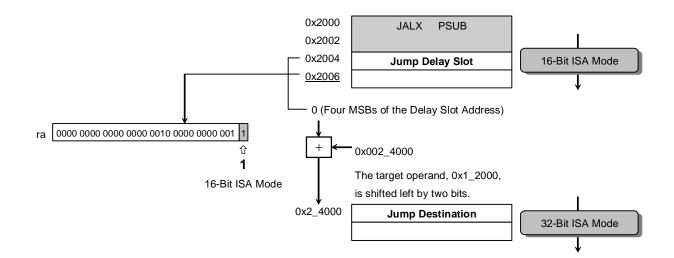

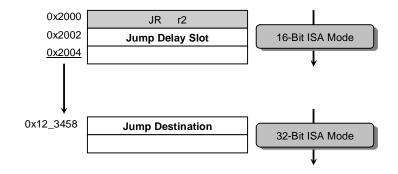

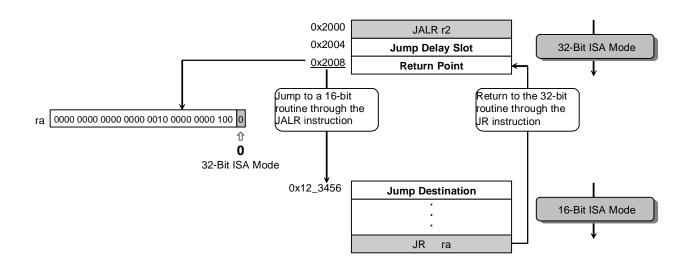

The TX19A has two ISA modes, 16-bit ISA and 32-bit ISA. The TX19A provides for efficient runtime switching between 16-bit and 32-bit ISA modes through the JALX, JR and JALR instructions.

The least-significant bit of the program counter (PC) is the ISA mode bit: 0 for the 32-bit ISA and 1 for the 16-bit ISA. The JALX instruction unconditionally toggles the ISA mode bit (the least-significant bit) of the PC to switch to the other ISA. The JR and JALR instructions set the ISA mode bit from the least-significant bit of the register containing the jump address; a jump address is generated by masking off the ISA mode bit to zero.

In 32-bit ISA mode, instructions must be word-aligned. Thus, when switching from 16-bit ISA mode to 32-bit ISA mode, the JR and JALR instructions must specify a target register of which two least-significant bits are zero. If these bits are one-zero (10), an Address Error exception will occur when the jump target instruction is fetched.

In a jump delay slot of the JRLX, JR or JALR instruction, the instruction in the previous ISA mode is executed.

Link instructions save the return address in either register r31 (ra) or another destination register (*rd*) specified. Its least-significant bit keeps the ISA mode in which processing resumes after a subroutine has been executed. Then the same ISA mode as the one prior to the subroutine is set after returning from subroutine.

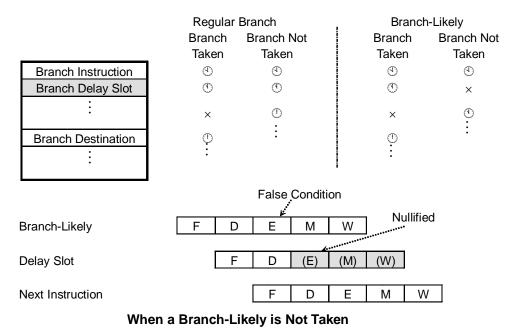

### 3.4.4 Branch-Likely Instructions

All the jump and branch instructions occur with a delay of one instruction (two pipeline cycles) before the program flow can change because the processor must calculate the effective destination of the jump or branch and fetch that instruction. This delay is called jump or branch delay. The TX19A architecture gives responsibility of dealing with delay slots to software. The compiler or the assembler makes an attempt to reorder instructions to execute the instruction immediately following

the jump or branch while the target instruction is being fetched from memory.

There is no problem in the case of jump instructions since jumps "always" transfer program control to the target instruction; the instruction immediately following the jump can always fill the delay slot. However, with branch instructions, the processor never knows whether the branch will be taken or not; so the instruction in the delay slot must be the one that logically precedes the branch instruction. If the delay slot can not be filled with any useful instruction, a NOP (No Operation) instruction must be inserted to keep the instruction pipeline filled. (NOP is a pseudoinstruction accepted by the assembler; the assembler actually turns it into a shift instruction to r0 register with a shift amount of zero as described in Chapter 1.)

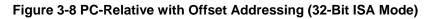

The code in Figure 3-9 implements the task of setting register r2 to 1 or 0, depending on whether the value of r8 is equal to 0 or not. Because the ADDI instruction can not logically precede the BEQ instruction, a NOP instruction is required immediately following BEQ.

Figure 3-9 Regular Branch Instruction

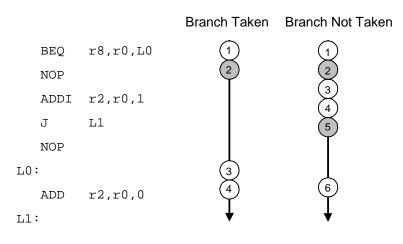

Contrast this to the code in Figure 3-10 in which the branch-likely version of Branch On Equal (BEQL) is used instead of BEQ. If a branch-likely is taken, the instruction in the delay slot is executed. If a branch-likely is not taken, the instruction in the delay slot is nullified, or killed. This eliminates the need to insert a NOP instruction in the delay slot, and thus helps to reduce code size and speed up branch processing.

Figure 3-10 Branch-Likely Instruction

### 3.4.5 Branching on Arithmetic Comparisons

The Branch On Equal (BEQ) and Branch On Not Equal (BNE) instructions, and their branch-likely versions (BEQL/BNEL) are the branch instructions that execute a branch based on the magnitude of two values in registers. For example,

BEQ r2,r3,Equal

compares the contents of registers r2 and r3 and branches to Equal if they are equal. However, there is no instruction to branch based on whether r2 is greater than r3. To perform such an arithmetic comparison on a pair of registers or between a register and an immediate value, you must use a sequence of two instructions. Three examples are given below: set-on-less-than instructions comparing two registers or a register and an immediate and a comparison between a register and an immediate. (Some assemblers provide macro instructions for branching on arithmetic comparisons. The assembler expands macro instructions into a sequence of machine instructions.)

• Example 1: Branch if r6 ε r7

The following sequence of instructions checks if the contents of r6 is equal to or greater than the contents of r7. If the contents of r6 is less than that of r7, the SLT (Set On Less Than) instruction sets r24 to 1.

Otherwise, r24 is set to 0. The BEQ instruction branches for magnitude relation by detecting r24 value with BEC instruction (Remember r0 is

hardwired to a constant value of zero).

```

SLT r24,r6,r7

BEQ r24,r0,Label

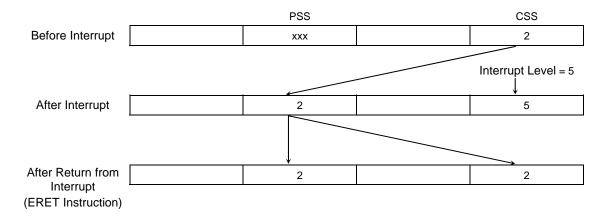

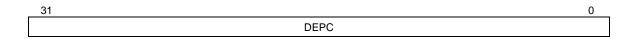

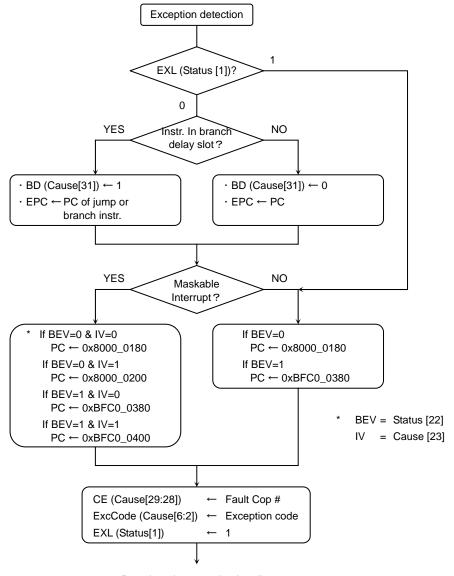

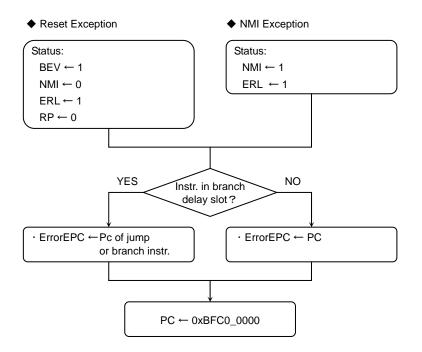

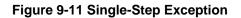

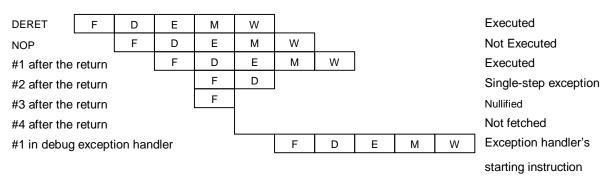

```