### **TOSHIBA**

TOSHIBA Original CMOS 32-Bit Microcontroller

TLCS-900/H1 Series

TMP92CF26AXBG

### **TOSHIBA CORPORATION**

Semiconductor Company

## Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions".

# CMOS 32-Bit Microcontroller TMP92CF26AXBG

### Outline and Features

The TMP92CF26A is a high-speed advanced 32-bit microcontroller developed for controlling equipment which processes mass data.

The TMP92CF26AXBG is housed in a 228-pin BGA package.

- (1) CPU: 32-bit CPU (High-speed 900/H1 CPU)

- Compatible with TLCS-900/L1 instruction code

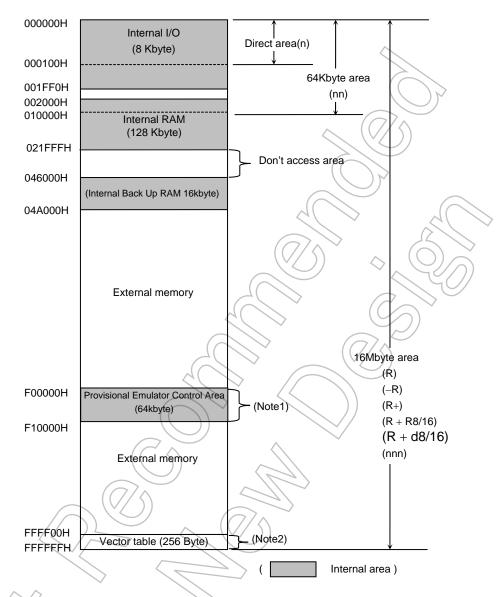

- 16 Mbytes of linear address space

- General-purpose register and register banks

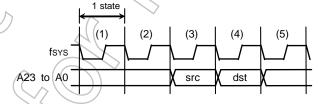

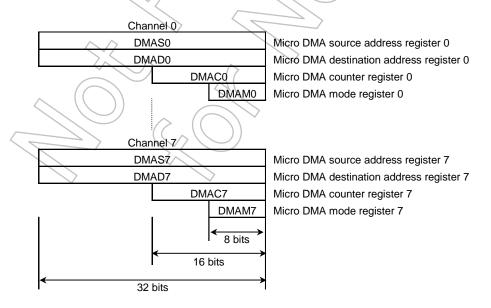

- Micro DMA: 8channels (62.5 ns/4 bytes at f<sub>SYS</sub> = 80 MHz, best case)

- (2) Minimum instruction execution time: 12.5 ns (at fsys = 80 MHz)

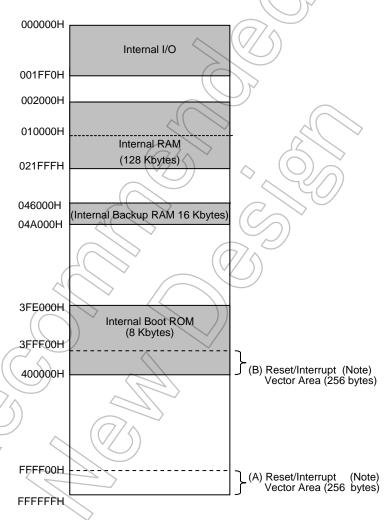

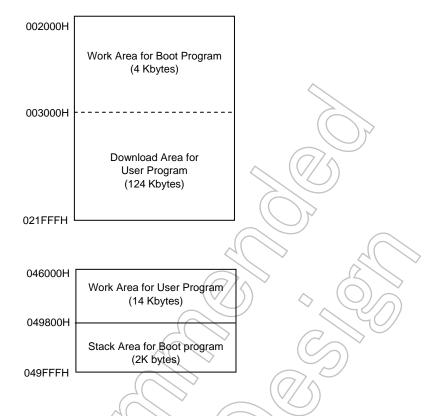

- (3) Internal RAM: 144 Kbytes (can be used for program, data and display memory)

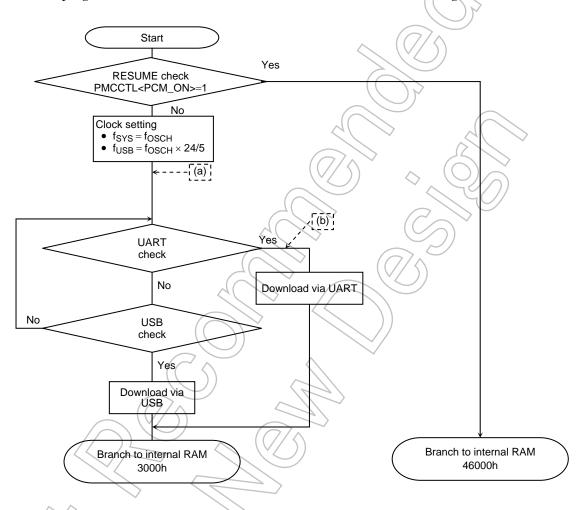

Internal ROM: 8 Kbytes (memory for Boot only)

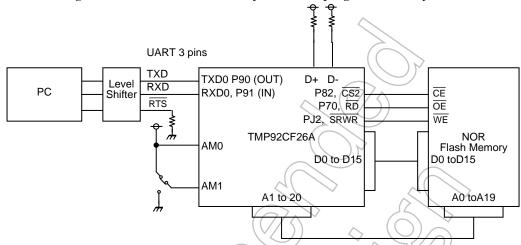

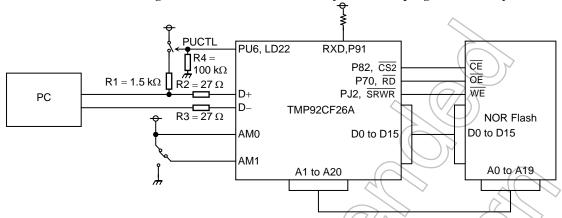

Possible downloading of user program through either USB, UART

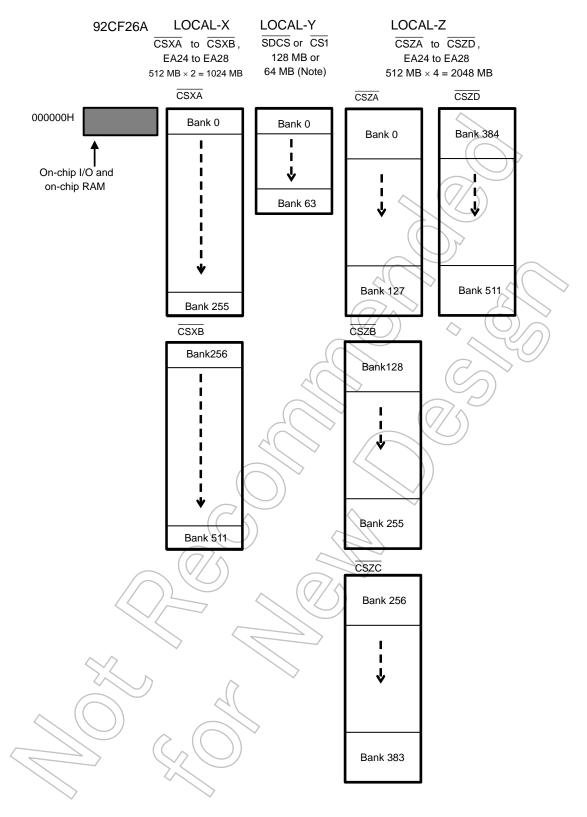

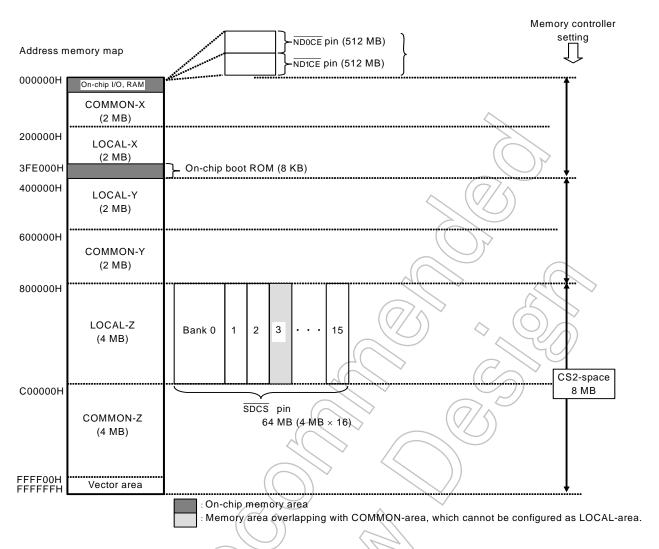

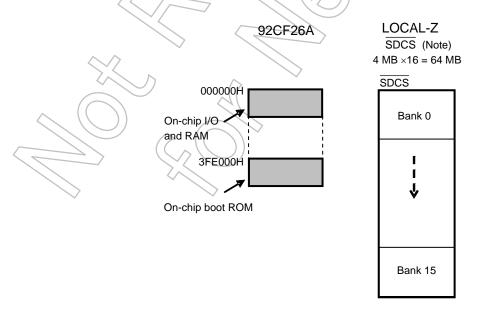

- (4) External memory expansion

- Expandable up to 3.1 Gbytes (shared program/data area)

- Can simultaneously support 8 and 16-bit width external data buses ...... Dynamic data bus sizing

- Separate bus system

- (5) Memory controller

- Chip select output: 4 channels

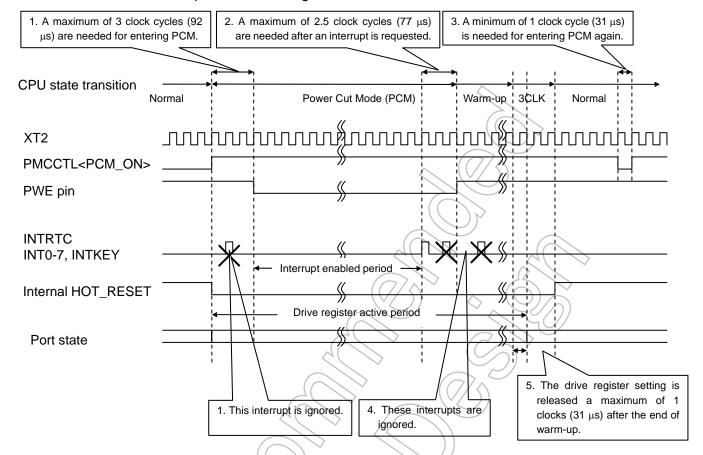

- One channel in 4 channels is enabled detailed AC enable setting

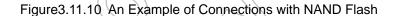

- (6) 8-bit timers: 8 channels

- (7) 16-bit timer/event counter: 2 channels

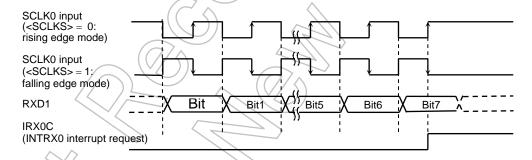

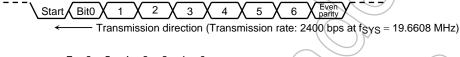

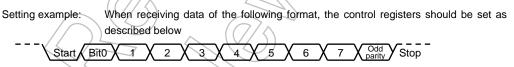

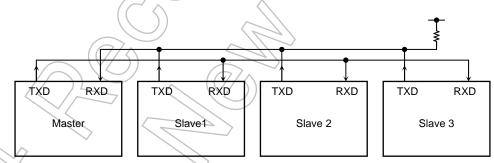

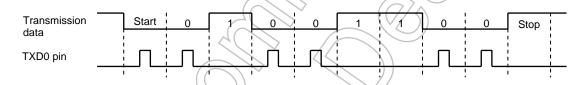

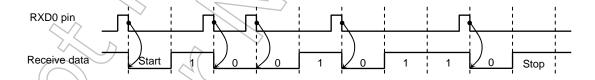

- (8) General-purpose serial interface: 1 channel

- UART/synchronous mode

- IrDA ver.1.0 (115.2 kbps) selectable

(There is the restriction in the setting baud rate when use this function together other functions)

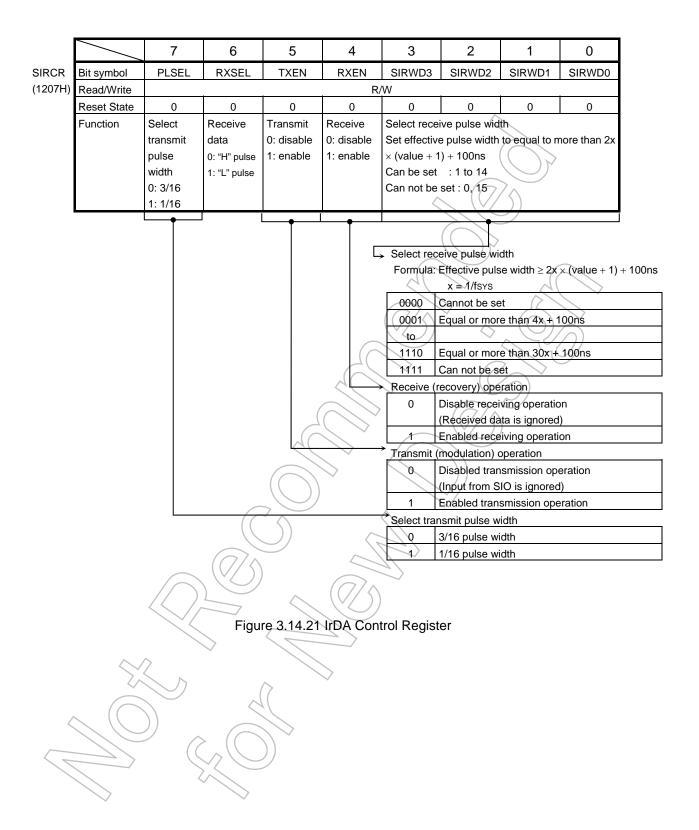

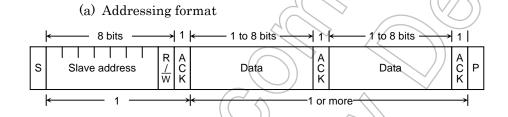

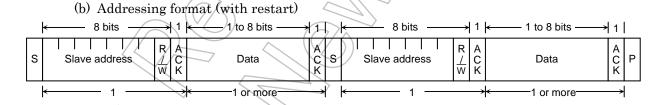

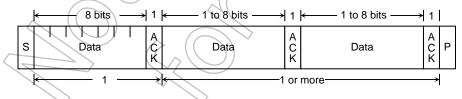

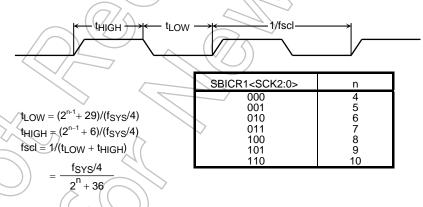

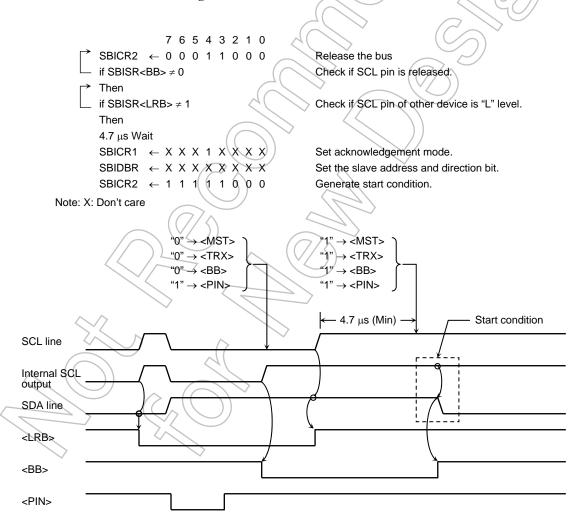

- (9) Serial bus interface: 1 channel

- I<sup>2</sup>C bus mode only

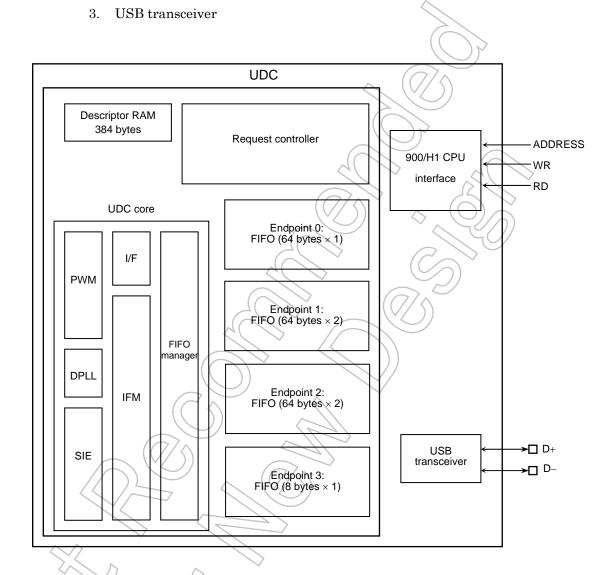

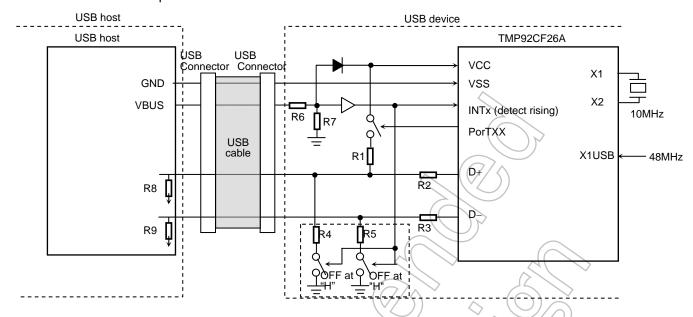

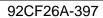

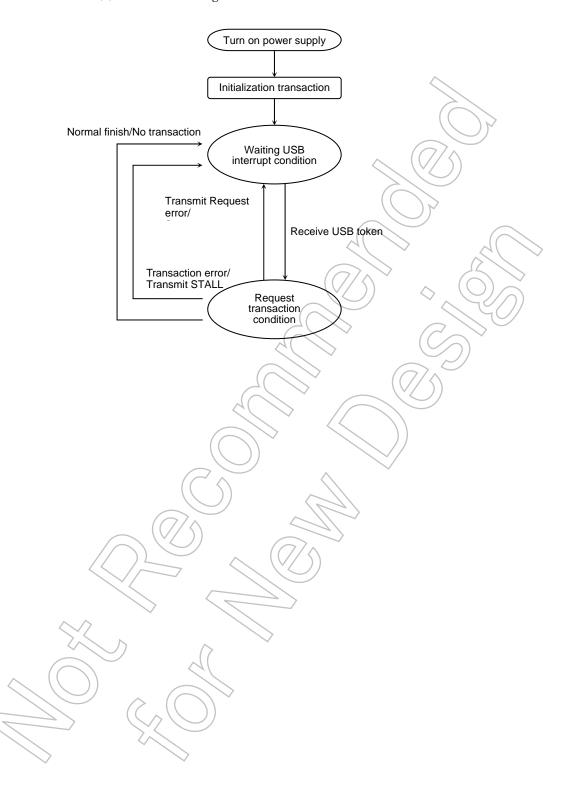

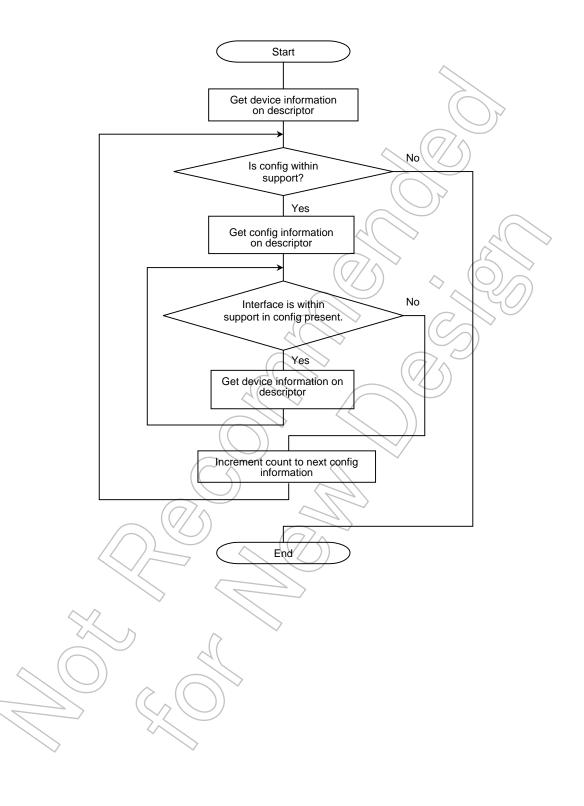

### (10) USB (universal serial bus) controller: 1 channel

- Supports USB (ver.1.1)

- Full-speed (12 Mbps) (Low-speed is not supported.)

- Endpoint 0: Control 64 bytes × 1 FIFO

- Endpoint 1: BULK (output) 64 bytes × 2 FIFOs

- Endpoint 2: BULK (input) 64 bytes × 2 FIFOs

- Endpoint 3: Interrupt (input) 8 bytes × 1 FIFO

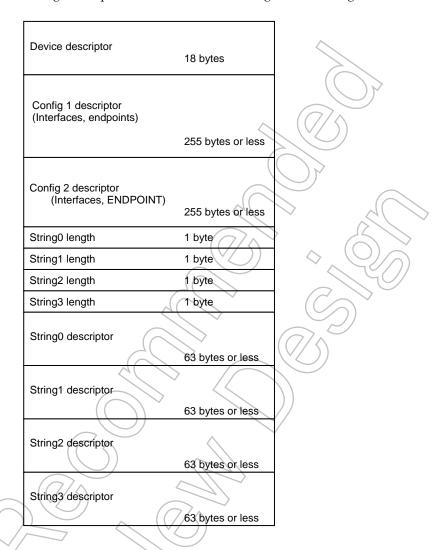

- Descriptor RAM: 384 bytes

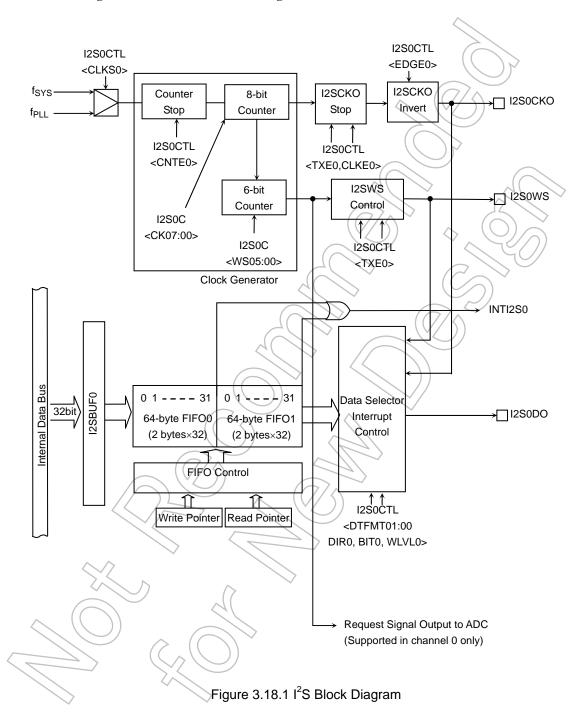

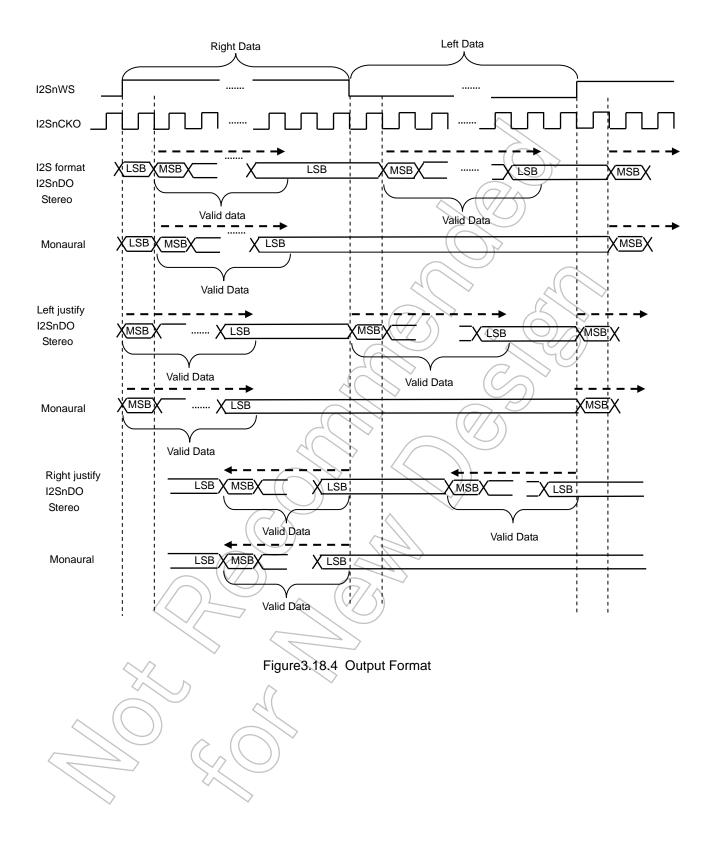

### (11) I2S (Inter-IC Sound)interface: 2 channels

- I2S bus mode selectable (Master, transmission only)

- Data Format is supported Left/Right Justify

- 128-byte FIFO buffer (64 bytes × 2) per channel

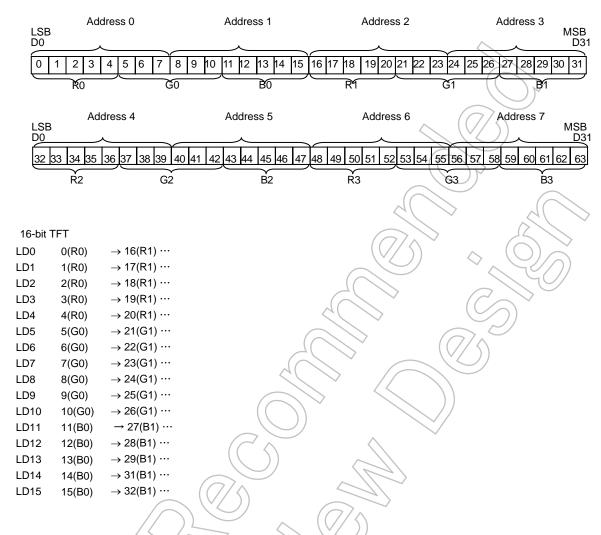

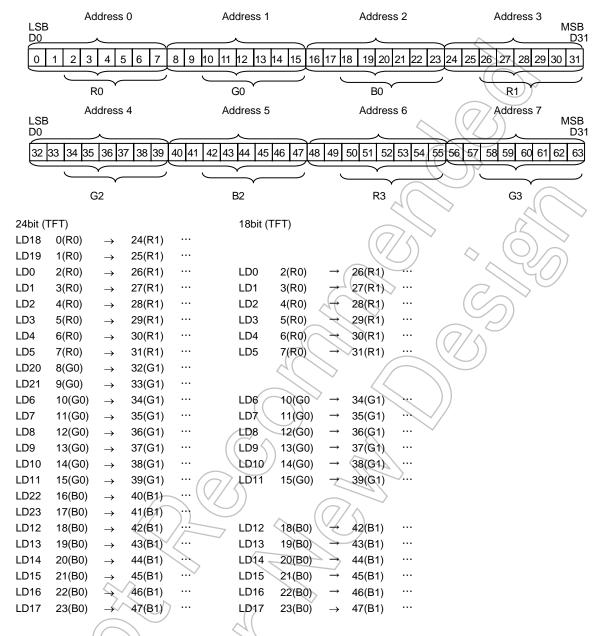

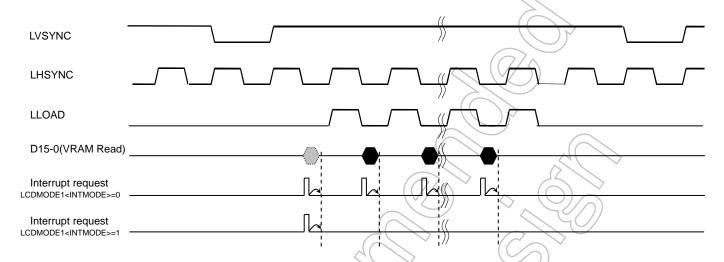

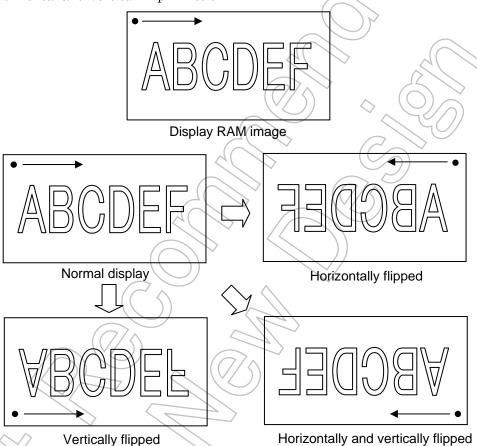

#### (12) LCD controller

- Supports monochrome, 4, 16 and 64 gray levels and 256/4096/65536 colors for STN

- Supports 4096/65536/262144/16777216 colors for TFT

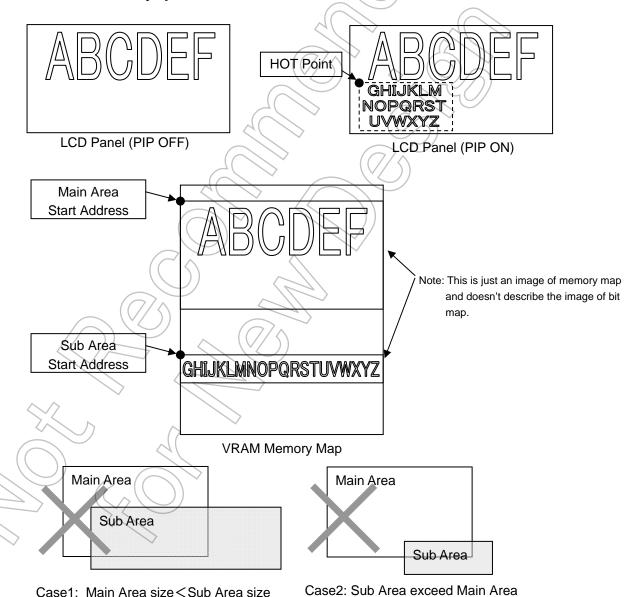

- Supports PIP (Picture In Picture Display)

- Supports H/W Rotation function for support to various LCDM

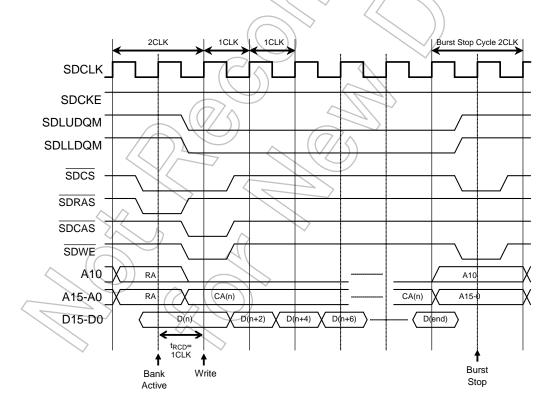

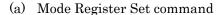

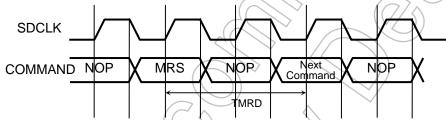

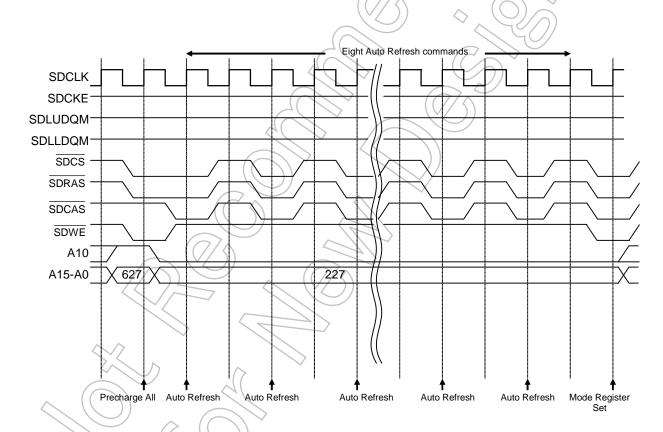

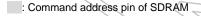

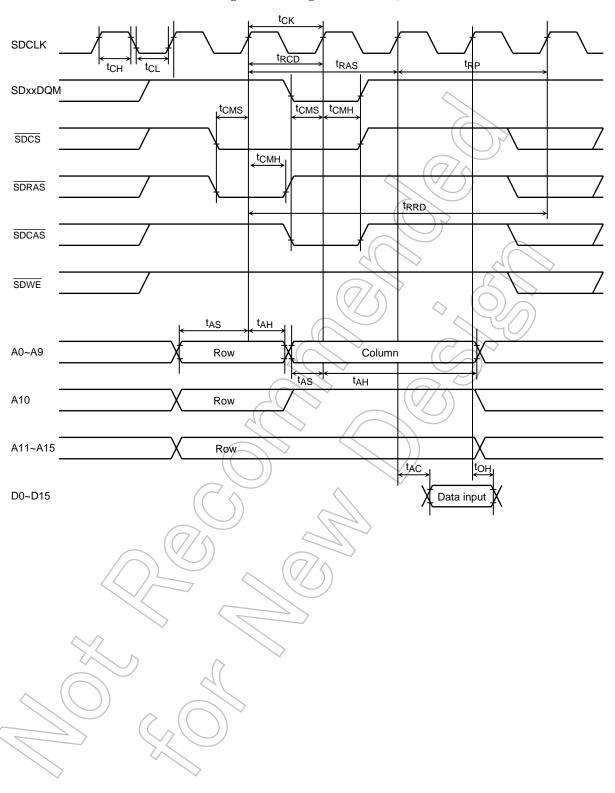

#### (13) SDRAM controller:1 channel

- Supports 16-Mbit, 64-Mbit, 128-Mbit, 256-Mbit and 512-Mbit SDR (Single-data-rate) SDRAM

- Possible to execute instruction on SDRAM

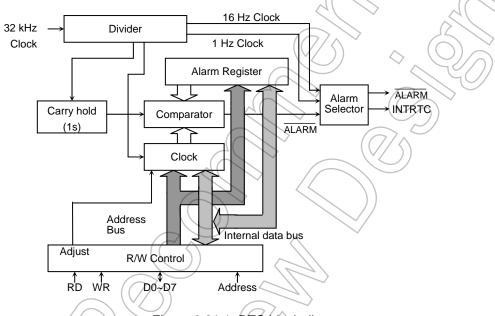

#### (14) Timer for real-time clock (RTC)

- Based on TC8521A

- (15) Key-on wakeup (Interrupt key input)

- (16) 10-bit A/D converter (Built in Sample Hold circuit): 6 channels

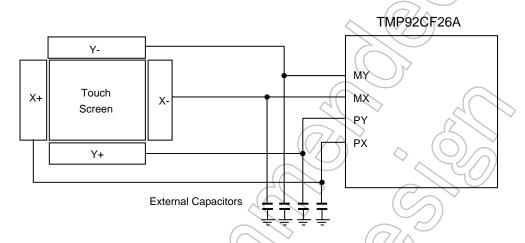

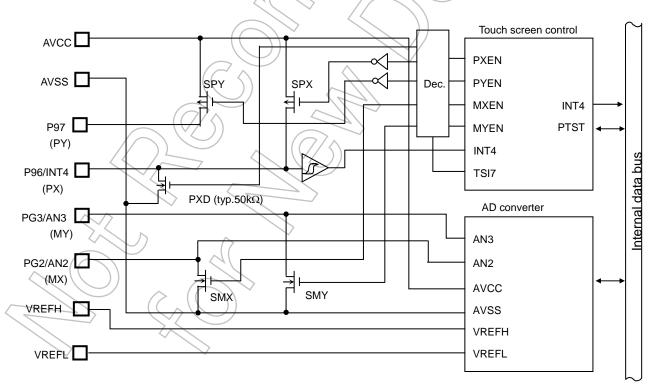

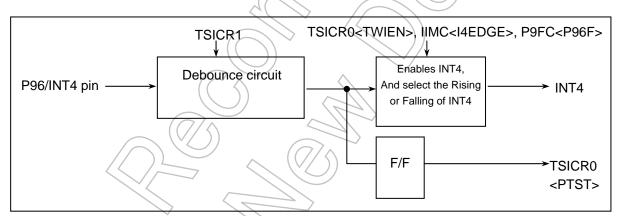

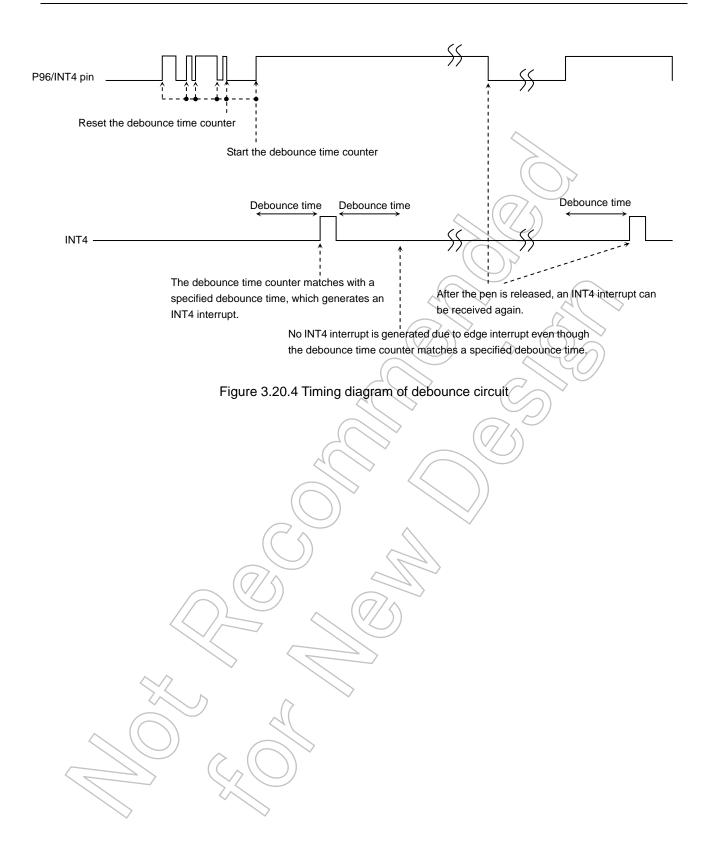

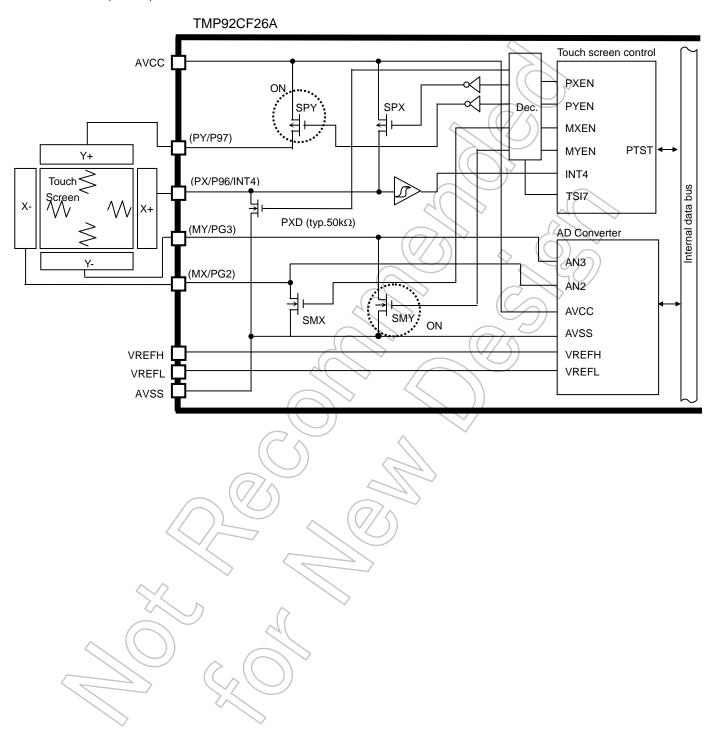

- (17) Touch screen interface

- Built-in Switch of Low-resistor, and available to reduce external components for shift change row/column

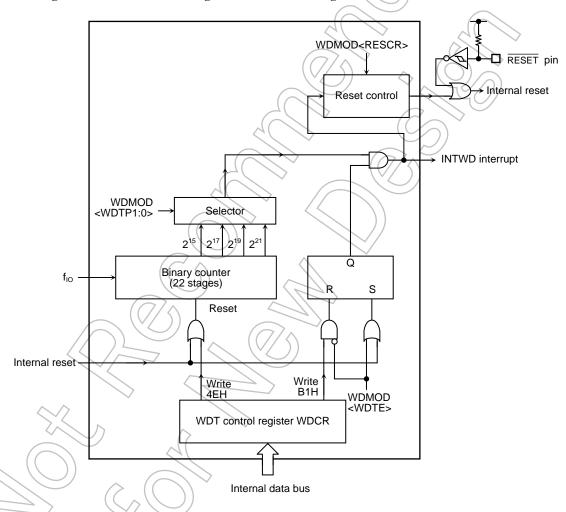

### (18) Watchdog timer

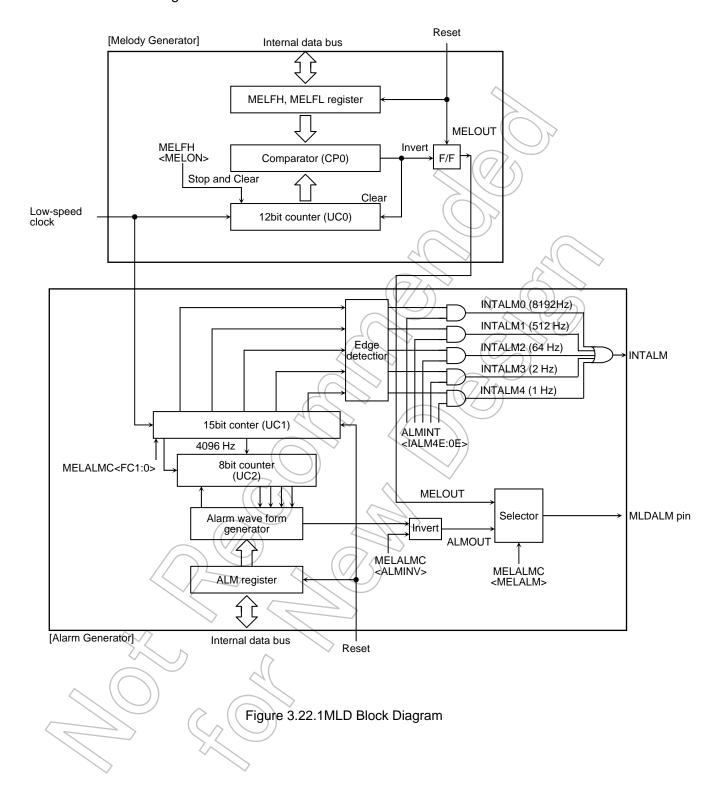

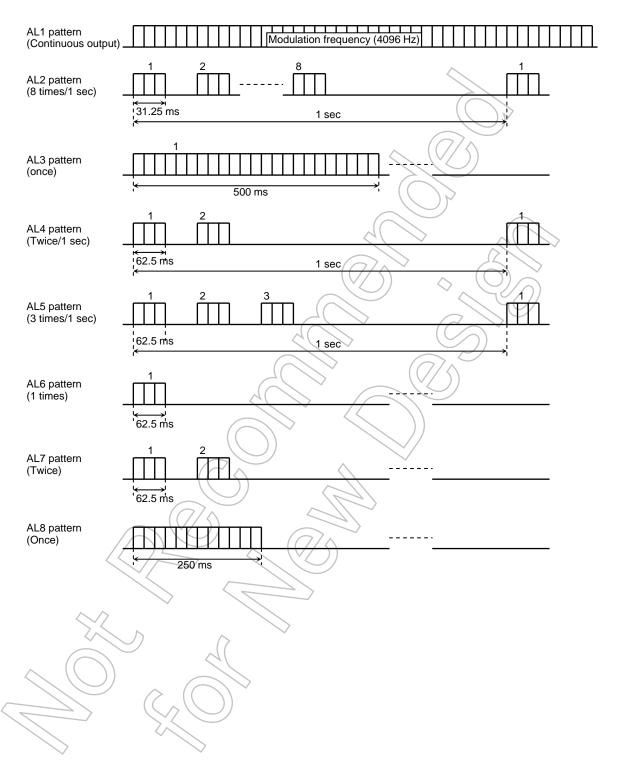

- (19) Melody/alarm generator

- Melody: Output of a clock 4 to 5461-Hz clock

- Alarm: Output of 8 kinds of alarm pattern

- 5 kinds of interval interrupt

#### (20) MMU

- Expandable up to 3.1 Gbytes (3 local area/8 bank method)

- Independent bank for each program, read data, write data, source and destination of DMAC (Odd channel/Even channel) and LCD display data

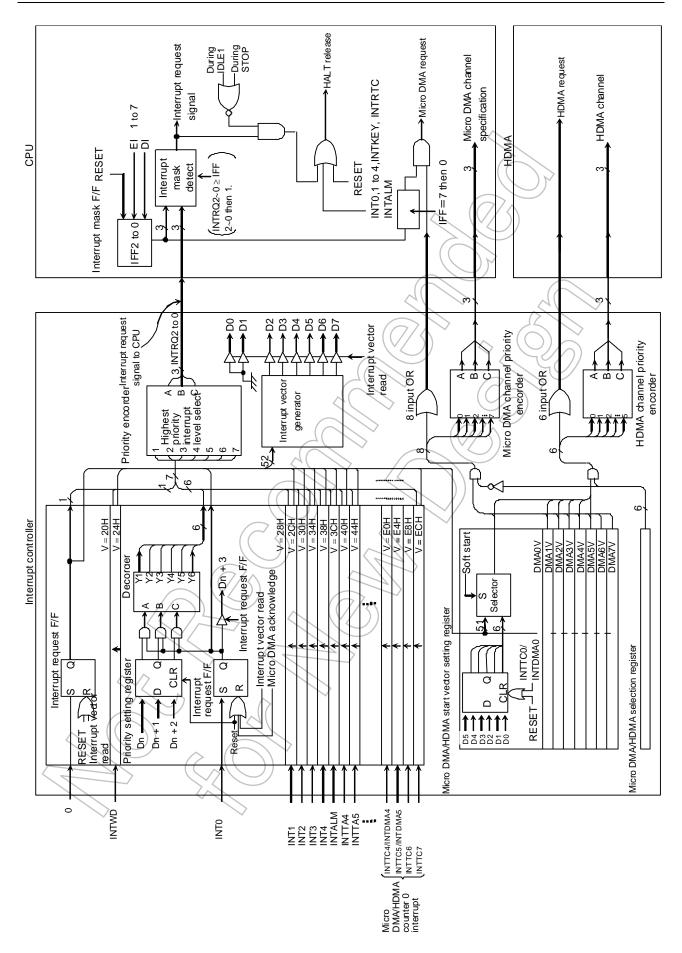

#### (21) Interrupts: 56 interrupts

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 38 internal interrupts: Seven selectable priority levels

- 9 external interrupts: Seven selectable priority levels (8-edge selectable)

### (22) DMAC function: 6 channels

High-speed data transfer enable by controlling which convert micro DMA function and this function

(23) Input/Output ports: 136 pins (Except Data bus (16bit), Address bus (24bit) and RD pin)

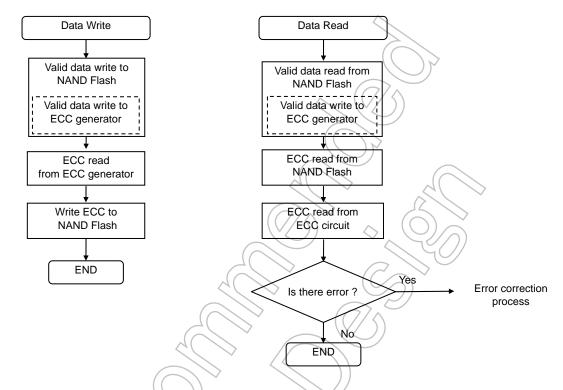

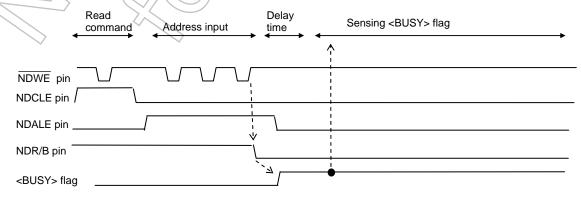

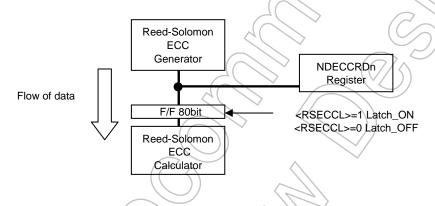

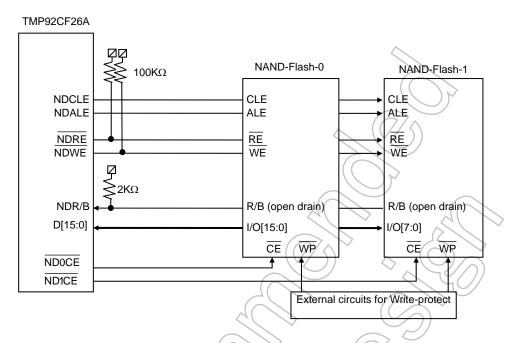

### (24) NAND Flash interface: 2 channels

- Direct NAND flash connection capability

- Supports SLC type and MLC type

- Supports Data Bus 8/16 bits, Page Size 512/2048 bytes

- Built-in Reed Solomon calculation circuits which enabled correct 4-address, and detect error more than 5-address

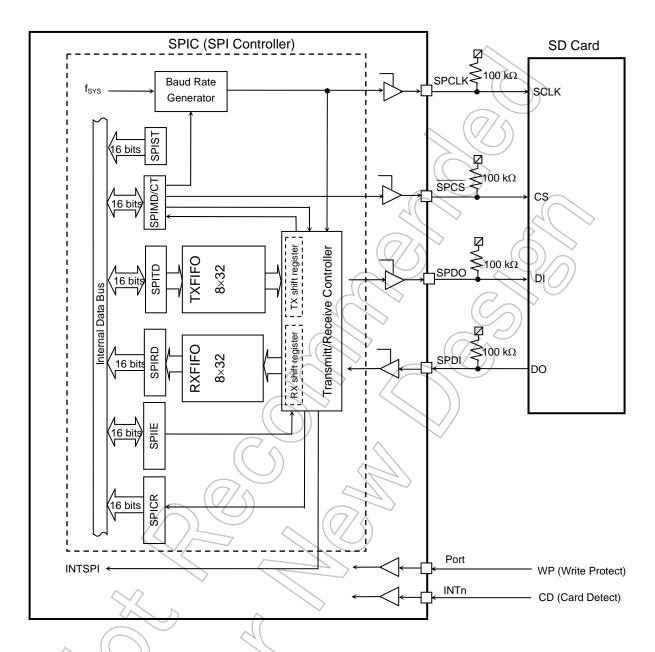

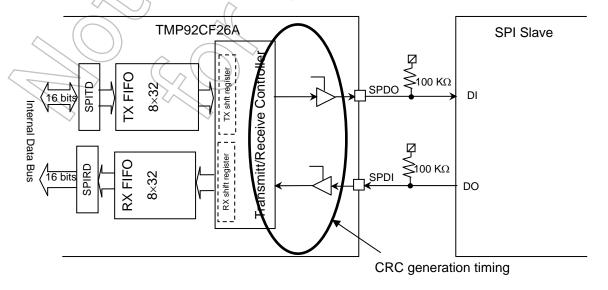

#### (25) SPI controller: 1 channel

- Supports SPI mode of SD card and MMC card

- Built-in FIFO buffer of 32 bytes to each Input/Output

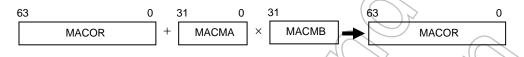

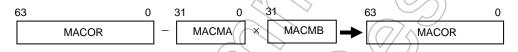

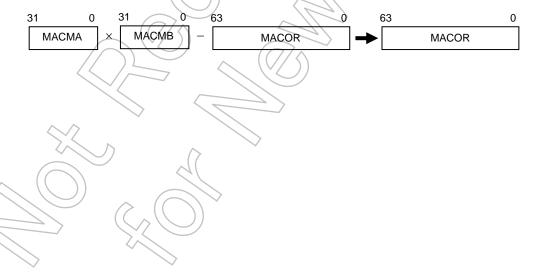

### (26) Product/Sum calculation: 1 channel

- Supports calculation  $32 \times 32 + 64 = 64$  bits,  $64 32 \times 32 = 64$  bits and  $32 \times 32 64 = 64$  bits

- I/O method

- Supports Signed calculations

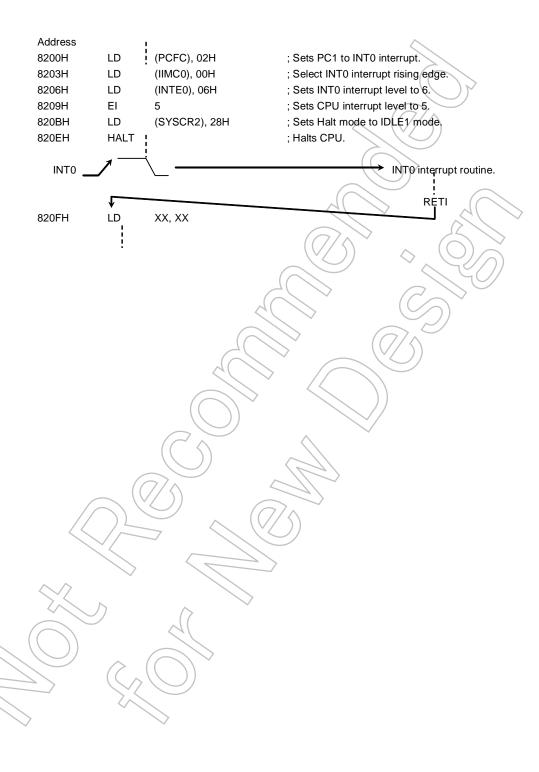

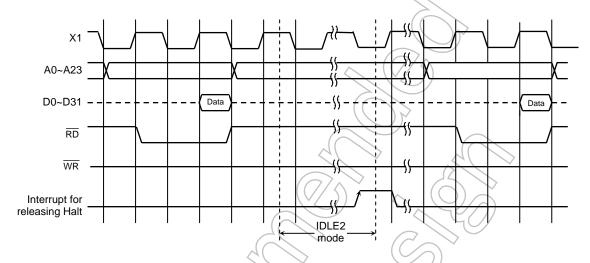

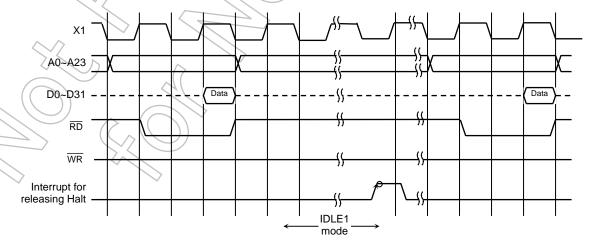

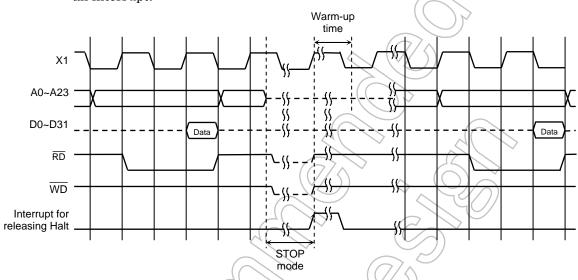

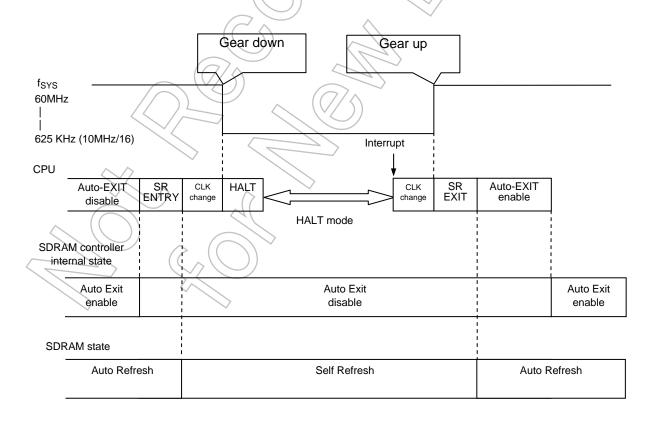

### (27) Standby function

- Three Halt modes: IDLE2 (programmable), IDLE1, STOP

- Each pin status programmable for standby mode

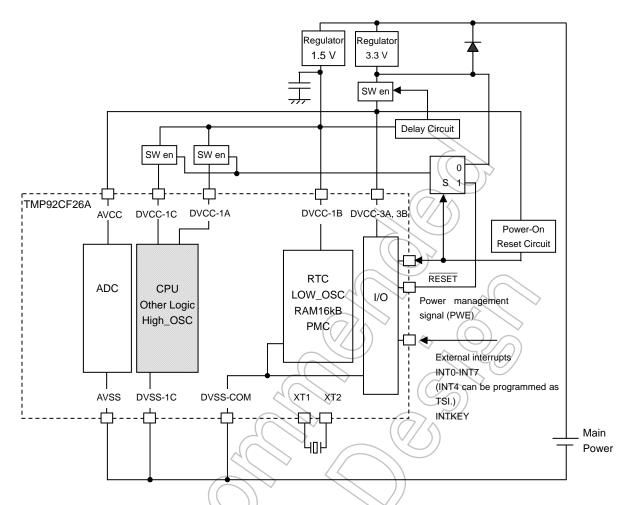

- Built-in power supply management circuits (PMC) for leakage current provision

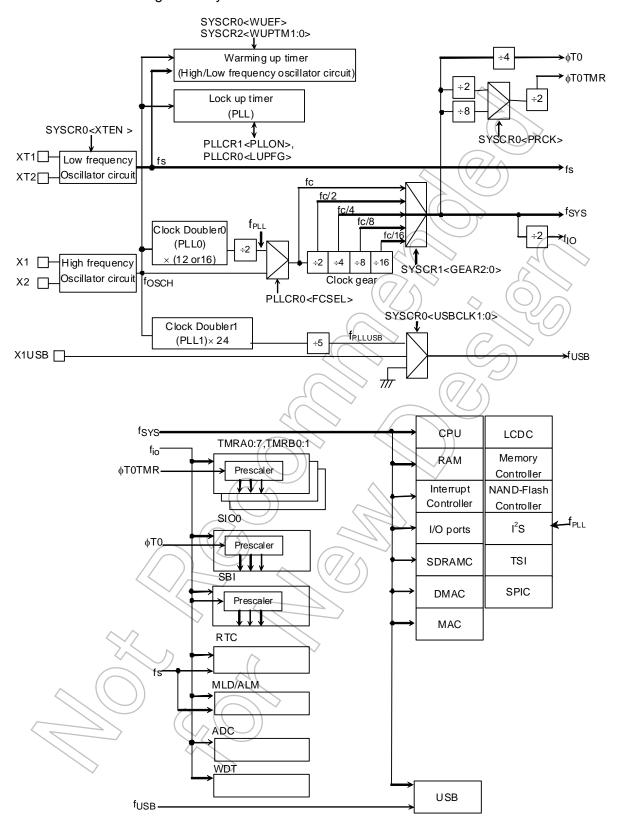

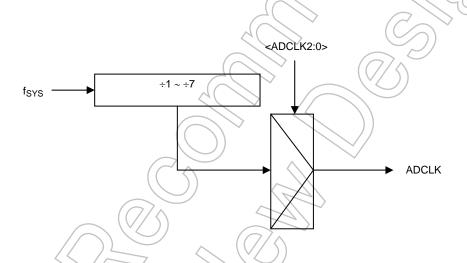

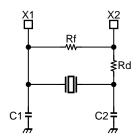

#### (28) Clock controller

- Two blocks of clock doubler (PLL) supplies 48 MHz for USB and 80 MHz for CPU from 10 MHz

- Clock gear function: Selectable high-frequency clock fc to fc/16

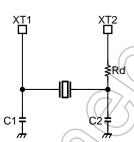

- Clock for Timer (fs = 32.768 kHz)

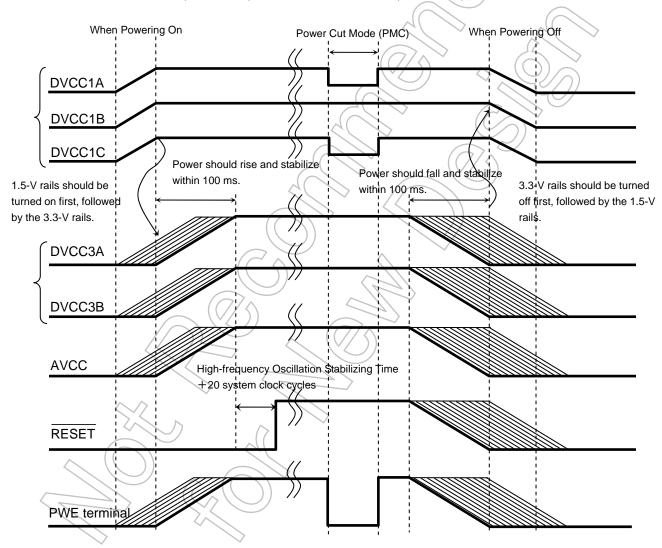

### (29) Operating voltage:

- Internal  $V_{CC}$ = 1.5 V, External I/O  $V_{CC}$  = 3.0 to 3.6 V

- 2 power supplies (Internal power supply (1.4 to 1.6 V), External power supply (3.0 to 3.6 V)

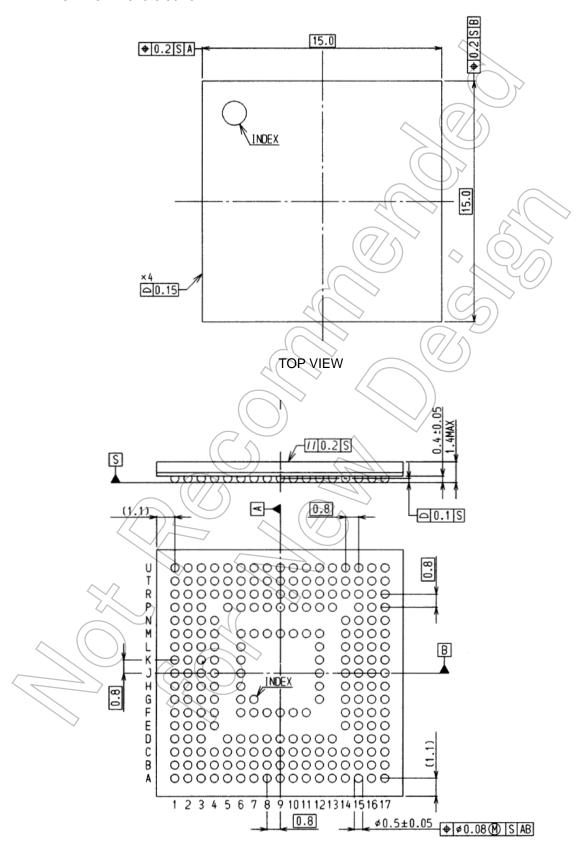

### (30) Package

• 228-pin FBGA: FBGA228-P-1515-0.80A5

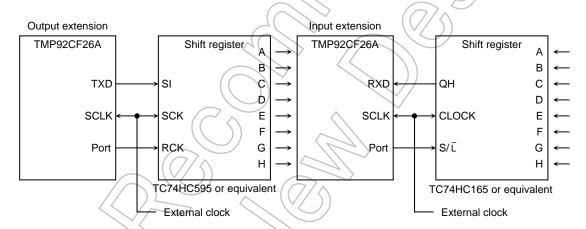

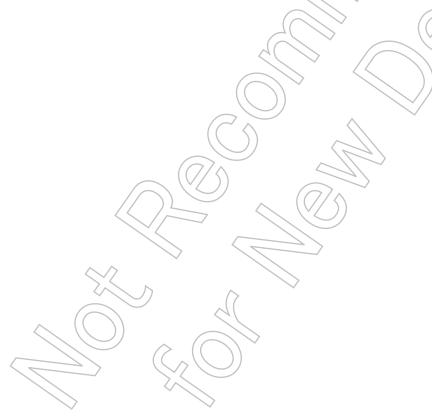

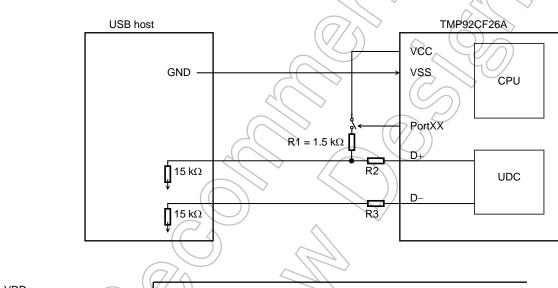

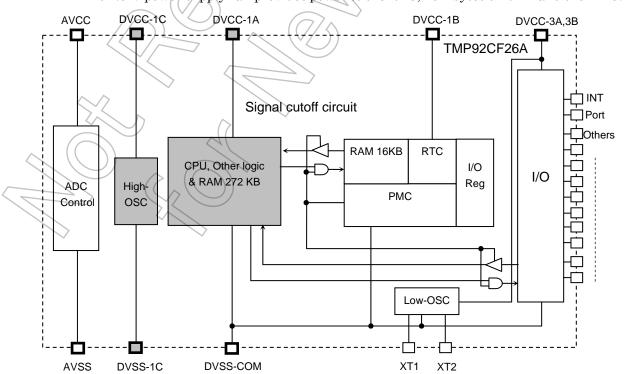

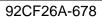

TOSHIBA TMP92CF26A **DVCC3A** [12] (AN0 to AN1)PG0 to PG1 10-bit 6ch DVCC3B [1] (AN2, MX)PG2 DVCC1A [5] 900/H1 CPU AD (AN3, MY, ADTRG)PG3 DVCC1B [1] Converter (AN4 to AN5)PG4 to PG5 DVSSCOM DVCC1C [1] AVCC, AVSS PLL VREFH, VREFL W **XWA** Α X1 H-OSC Touch Screen X2 (PX, INT4)P96-**XBC** В С Clock gear (PY)P97 (TSI) Е D **XDE** XT1 L-ØSC (TXD0)P90 ◄ Н SERIAL I/O XHL L XT2 (RXD0)P91 SIO<sub>0</sub> RESET XIX IX (CTS0, SCLK0)P92 **DBGE** (I2S0CKO)PF0 -AM [1:0] XIY ΙY I<sup>2</sup>S (I2S0DO)PF1 PZ0 (EI PODDATA)  $(I^2S0)$ XIZ ΙZ (I2S0WS)PF2 < PZ1 (EI\_SYNCLK) (I2S1CKO)PF3-PZ2 (EI\_PODREQ)  $I^2S$ **XSP** SP (I2S1DO)PF4 -PZ3(EI\_REFCLK) (I<sup>2</sup>S1)32bit PZ4(EI\_TRGIN) (12S1WS)PF5 < DSU PZ5(EI\_COMRESET) (SDA)PV6 ₹ SR F SBI (I2Cbus) ➤ PZ6(EO\_MCUDATA) (SCL)PV7 ➤ PZ7(EO\_MCUREQ) P C **USB** D. >PMC PM7 (PWE) Controller (X1USB) PX5≺ 8BIT TIMER (TMRA0) PC0 (INT0) Interrupt (TA0IN, INT1)PC1 ◄ WATCH-DOG TIMER Controller PC2 (INT2) 8BIT TIMER D0 to D7 (TA1OUT, MLDALM)PM1 -(TMRA1) MMD PORT/1 P10 to P17 (D8 to D15) **8BIT TIMER** (TA2IN, INT3)PC3 (TMRA2) ➤ P40 to P47 (A0 to A7) PORT4 **8BIT TIMER** MAC (TA3OUT)PP1 ← (TMRA3) → P50 to P57 (A8 to A15) PORT5 8BIT TIMER (TMRA4) PORT6 P60 to P67 (A16 to A23) DMAC **8BIT TIMER** P70 (RD) (TA5OUT)PP2 ≺ (TMRA5) P73 (EA24) 8BIT TIMER (TMRA6) PORT7 P74 (EA25) P75(R/W, NDR/B) 8BIT TIMER P76 (WAIT) (TA7OUT, INT5)PP3 -(TMRA7) P80 (CS0) (TB0IN0, INT6)PP4< **16BIT TIMER** P81 (CS1, SDCS) PORT8 (TMRB0) P82 ( CS2 , CSZA , SDCS ) (TB0OUT0)PP6<del><</del> 16BIT TIMER (TMRB1) P83 (CS3, CSXA) (TB1IN0, INT7)PP5◀ P84 ( CSZB ) (TB1OUT0)PP7◀ P85 (CSZC) (SPDI)PR0≺ SPI P71 (WRLL, NDRE) (<u>SPDO</u>)PR1≺ (SPCS) PR2≺ Controller P72 (WRLU, NDWE) NAND-FLASH (SPCLK)PR3 144KB RAM P86 (CSZD, ND0CE) I/F (2ch) P87 (CSXB, ND1CE) (LCP0)PK0<del><</del> PJ5 (NDALE) (LLOAD)PK1< PJ6 (NDCLE) (LFR)PK2<del><</del> PA0 to PA7 (KI0 to KI7) (LVSYNC)PK3≺ KEY-BOARD ➤ PN0 to PN7 (KO0 to KO7) LCD (LHSYNC)PK4 I/F PC7 (KO8) (LGOE2 to 0)PK7 to 5€ Controller (LD7 to 0)PL7 to 0≺ **BOOT ROM 8KB** PM2 ( ALARM , MLDALM ) **RTC** (LD15 to 8)PT7 to 0< (LD22 to 16)PU6 to 0 MELODY/ (LD23, EO\_TRGOUT)PU7~ ALARM-OUT (CLKOUT, LDIV)PX4≺ ➤PV3 PX7<del><</del> **PORTV** ►PV4 (SDRAS, SRLLB)PJ0 PV0 (SCLK0) (SDCAS, SRLUB)PJ1 ◄ **SDRAM** →PV1 (SDWE, SRWR)PJ2 ◄ → PV2 Controller (SDLLDQM)PJ3 -→ PW7 to 0 (SDLUDQM)PJ4 ◄ PC4 (EA26) (SDCKE)PJ7≺ → PC5 (EA27) (SDCLK)PF7◄ PC6 (EA28)

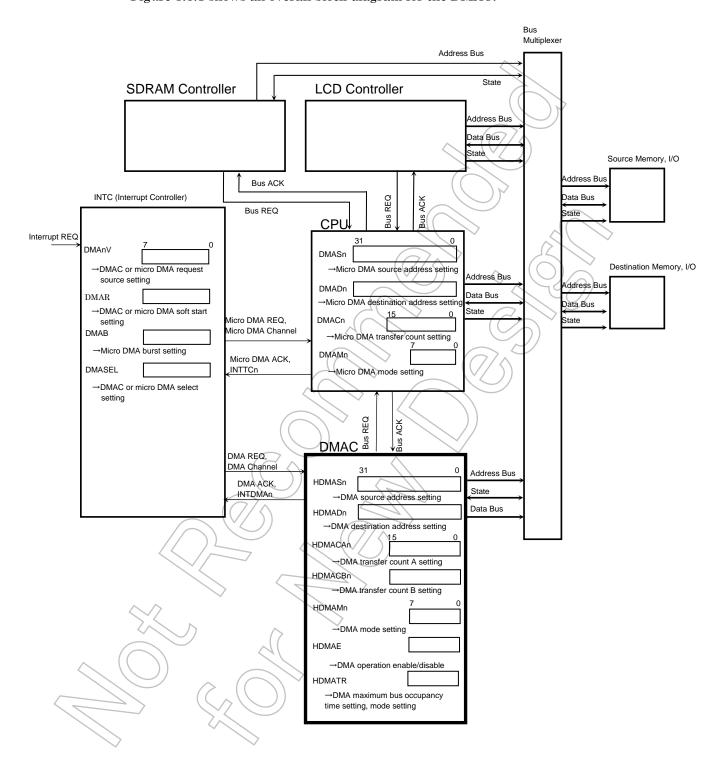

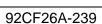

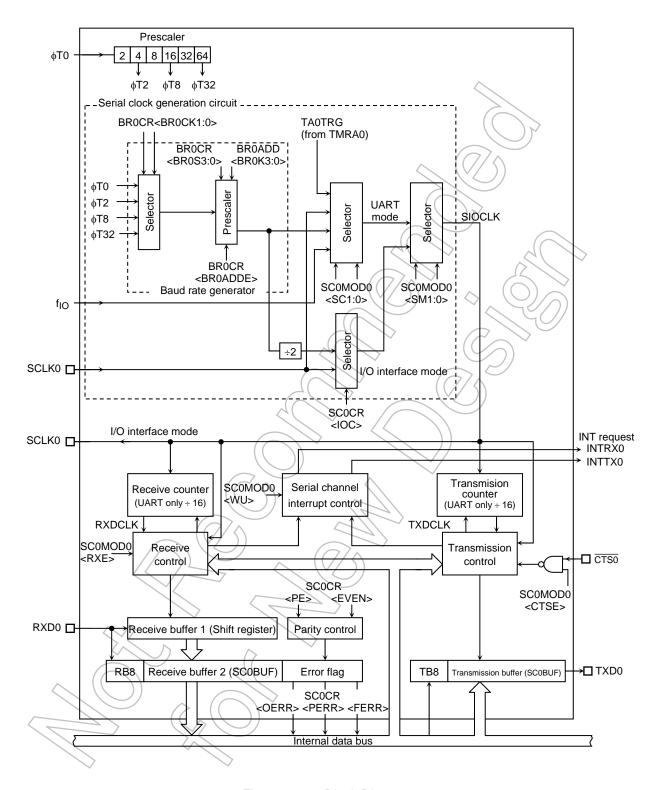

Figure 1.1 Block Diagram of TMP92CF26A

### 2. Pin Assignment and Pin Functions

The assignment of input/output pins for TMP92CF26A, their names and functions are as follows;

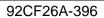

### 2.1 Pin Assignment Diagram (Top View)

Figure 2.1.1 shows the pin assignment of the TMP92CF26A.

|    |    |    |    |     |    |    |            |            |             |     |     |     |            | $\overline{}$ |     |     |

|----|----|----|----|-----|----|----|------------|------------|-------------|-----|-----|-----|------------|---------------|-----|-----|

| A1 | A2 | А3 | A4 | A5  | A6 | A7 | A8         | А9         | A10         | A11 | A12 | A13 | A14        | A15           | A16 | A17 |

| B1 | B2 | ВЗ | B4 | B5  | B6 | В7 | B8         | В9         | B10         | B11 | B12 | B13 | B14        | B15           | B16 | B17 |

| C1 | C2 | СЗ | C4 | C5  | C6 | C7 | C8         | <b>6</b> 9 | C10         | C11 | C12 | C13 | <b>614</b> | C15           | C16 | C17 |

| D1 | D2 | D3 |    | D5  | D6 | D7 | D8         | D9         | D10         | D11 | D12 | D13 | /2         | D15           | D16 | D17 |

| E1 | E2 | E3 | E4 |     |    |    |            |            |             | (   |     |     | E14        | E15           | E16 | E17 |

| F1 | F2 | F3 | F4 |     | F6 | F7 | F8         | F9         | F10         | F11 |     |     | F14        | F15           | F16 | F17 |

| G1 | G2 | G3 | G4 |     | G6 | G7 |            |            | (           | 77  | G12 |     | G14        | G15           | G16 | G17 |

| H1 | H2 | НЗ | H4 |     | H6 |    | $\bigcirc$ |            |             | V.  | H12 | 4   | H14        | H15           | H16 | H17 |

| J1 | J2 | J3 | J4 |     | J6 | 7  |            |            | <b>26</b> A |     | J12 |     | J14        | J15           | J16 | J17 |

| K1 | K2 | K3 | K4 |     | K6 |    | FI         | 3GA22      | 28          | >   | K12 | (   | K14        | K15           | K16 | K17 |

| L1 | L2 | L3 | L4 |     | L6 |    | TÓ         | PVIE       | €W>         |     | L12 | (7) | L14        | L15           | L16 | L17 |

| M1 | M2 | М3 | M4 |     | M6 | М7 | M8         | M9         | M10         | M11 | M12 | V   | M14        | M15           | M16 | M17 |

| N1 | N2 | N3 | N4 |     |    |    |            | >          | 4           |     |     |     | N14        | N15           | N16 | N17 |

| P1 | P2 | P3 |    | P5  | P6 | P7 | P8         | P9         | P10         | P11 | P12 | P13 |            | P15           | P16 | P17 |

| R1 | R2 | R3 | R4 | R5  | R6 | R7 | R8         | R9         | R10         | R11 | R12 | R13 | R14        | R15           | R16 | R17 |

| T1 | T2 | Т3 | T4 | T5  | T6 |    | T8         | Т9         | T10         | IN  | T12 | T13 | T14        | T15           | T16 | T17 |

| U1 | U2 | U3 | U4 | U5  | U6 | U7 | U8         | U9         | U10         | Ų11 | U12 | U13 | U14        | U15           | U16 | U17 |

|    |    |    |    | \ / | // |    |            |            | -           | /   |     |     |            |               |     |     |

Figure 2.1.1 Pin assignment diagram (FBGA228)

4 balls of A1, A17, U1 and U17 (most outside 4 corner of BGA package) are Dummy Balls. These balls are not connected with internal LSI chip, electrical characteristics.

A1 and U1, A17 and U17 are shorted in internal package. It is recommended that using to OPEN check of mounting if mounting this LSI to Target board.

Example: If checking signal (or voltage) via A1-U1-U17-A17, short U17 and U1 on Target board beforehand, and input signal (or voltage) from A1, and check voltage of A17.

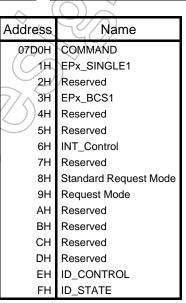

Table 2.1.1 Pin number and the name

|             |                              |             | Table 2.1.1 Pin nur | HDCI        | and the name                     |             |                 |

|-------------|------------------------------|-------------|---------------------|-------------|----------------------------------|-------------|-----------------|

| Ball<br>No. | Pin name                     | Ball<br>No. | Pin name            | Ball<br>No. | Pin name                         | Ball<br>No. | Pin name        |

| A1          | Dummy1                       | D9          | P73,EA24            | J15         | PT5,LD13                         | P15         | PK4,LHSYNC      |

| A2          | PG2,AN2, MX                  | D10         | PF4,I2S1DO          | J16         | P47,A7                           | P16         | P13,D11         |

| А3          | PA6,KI6                      | D11         | PF7,SDCLK           | J17         | P46,A6                           | P17         | P14,D12         |

| A4          | PA5,KI5                      | D12         | PJ4,SDLUDQM         | K1          | PN3,KO3                          | R1          | X2              |

| A5          | PA3,KI3                      | D13         | P85, CSZC           | K2          | PN4,KO4                          | R2          | PC7,KO8         |

| A6          | PA1,KI1                      | D15         | PU6,LD22            | K3          | PN5,KO5                          | R3          | PC3,INT3,TA2IN  |

| A7          | DVCC1A5                      | D16         | P61,A17             | K4          | PN6,KO6                          | R4          | PX5,X1USB       |

| A8          | PF1,I2S0DO                   | D17         | P60,A16             | K6          | DVCC3A2                          | R5          | PP7,TB1OUT0     |

| A9          | PJ6,NDCLE                    | E1          | P96,PX,INT4         | K12         | DVCC3A7                          | R6          | PP1,TA3OUT      |

| A10         | PJ1, SDCAS, SRLUB            | E2          | PW1                 | K14         | PT4,LD12                         | R7          | PP3,INT5,TA7OUT |

| A11         | P87, CSXB, ND1CE             | E3          | PW2                 | K15         | PT3,LD11                         | R8          | PP5,INT7,TB1IN0 |

| A12         | P83, CS3, CSXA               | E4          | PW3                 | K16         | P45,A5                           | R9          | PR2, SPCS       |

| A13         | P81, CS1, SDCS               | E14         | PU7,LD23,EO_TRGOUT  | K17         | P44,A4                           | R10         | PX7             |

| A14         | P72, WRLU , NDWE             | E15         | PU4,LD20            | L1          | PK2,LFR                          | R11         | PZ0,EI_PODDATA  |

| A15         | P70, RD                      | E16         | P57,A15             | L2          | PN7,KO7                          | R12         | PZ2,EI_PODREQ   |

| A16         | P65,A21                      | E17         | P56,A14             | L3          | PM1,MLDALM,TA1OUT                | R13         | PZ4.EI TRGIN    |

| A17         | Dummy3                       | F1          | DVCC1B1             | L4          | PM7,PWE                          | R14         | PZ6,EO_MCUDATA  |

| B1          | VREFH                        | F2          | PW6                 | L6          | DVSS3                            | R15         | PZ7,EO_MCUREQ   |

|             |                              |             |                     |             | DVSS7                            |             |                 |

| B2          | PG5,AN5<br>PG3,AN3,MY, ADTRG | F3          | PW5                 | L12         |                                  | R16         | 107 //          |

| B3          |                              | F4          | PW4                 | L14         | PT2,LD10                         | R17         | DVCC1A3         |

| B4          | PA7,KI7                      | F6          | DVCC3A12            | L15\        | PT1,LD9                          | T1          | X1              |

| B5          | PA2,KI2                      | F7          | DVCC3A11            | L16         | P43,A3                           | T2          | AM0             |

| B6          | PA0,KI0                      | F8          | DVSS11              | L'17        | P42,A2                           | T3/         | AM1             |

| B7          | PF2,I2S0WS                   | F9          | DVCC3A10            | M1          | PK3,LVSYNC                       | -T4         | PP6,TB0OUT0     |

| B8          | PF0,I2S0CKO                  | F10         | DVSS10              | M2          | PC0,INT0                         | T5          | PL0,LD0         |

| B9          | PJ5,NDALE                    | F11         | DVCC3A9             | M3          | PM2, ALARM, MLDALM               | T6          | PL2,LD2         |

| B10         | PJ2, SDWE , SRWR             | F14         | PU5,LD21            | M4          | P90,TXD0                         | T7          | PL4,LD4         |

| B11         | PJ0, SDRAS, SRLLB            | F15         | PU2,LD18            | M6          | DVCC3A3                          | T8          | PL5,LD5         |

| B12         | P86. CSZD , ND0CE            | F16         | P55,A13             | M7          | DVSS4                            | T9          | PR1,SPDO        |

| B13         | P82, CS2, CSZA, SDCS         | F17         | P54,A12             | M8          | DVCC3A4                          | T10         | PL6,LD6         |

| B14         | P75,R/W,NDR/B                | G1          | DVCC3B1             | M9          | DVSS5                            | T11         | PK1,LLOAD       |

| B15         | P71, WRLL, NDRE              | G2          | PW7                 | M10         | DVCC3A5                          | T12         | D0              |

| B16         | P64,A20                      | G3          | PV0,SCLK0           | M11/        | DVSS6                            | T13         | D2              |

| B17         | DVCC1A4                      | G4          | PV1                 | M12         | DVCC3A6                          | T14         | D4              |

| C1          | AVCC                         | G6          | DVSS1               | M14         | PK7,LGOE2                        | T15         | D6              |

| C2          | VREFL                        | G7          | DVSS12              | M15         | PT0,LD8                          | T16         | P11,D9          |

| C3          | PG4,AN4                      | G12         | DVSS9               | M16         | P41,A1                           | T17         | P12,D10         |

| C4          | PG1,AN1                      | G14         | PU3,LD19            | M17         | P40,A0                           | U1          | Dummy2          |

| C5          | PA4,KI4                      | <b>G</b> 15 | PU0,LD16            | N1          | DVCC1A1                          | U2          | RESET           |

| C6          | PC5,EA27                     | G16         | P53,A11             | N2          | PC1,INT1,TA0IN                   | U3          | D+              |

| C7          | P76, WAIT                    | G17         | P52,A10             | N3          | P91,RXD0                         | U4          | D-              |

| C8          | PF5,I2S1WS                   | H1          | PV7,SCL             | N4          | DVSS1C                           | U5          | DVCC1A2         |

| C9          | PF3,I2S1CKO                  | H2          | PV6,SDA             | N14         | PK6,LGOE1                        | U6          | PL1,LD1         |

| C10         | PJ7,SDCKE                    | /нз         | PV3                 | N15         | PK5,LGOE0                        | U7          | PL3,LD3         |

| C11         | PJ3,SDLLDQM                  | H4          | PV2                 | N16         | P17,D15                          | U8          | XT1             |

| C12         | P84, CSZB                    | H6          | DVCG3A1             | N17         | P16,D14                          | U9          | XT2             |

| C13         | P80,CS0                      | H12         | DVCC3A8             | P1          | DVCC1C                           | U10         | PL7.LD7         |

| C14/        | P67,A23                      | H14         | PU1,LD17            | P2          | PC2,INT2                         | U11         | PK0,LCP0        |

| C15         | P66,A22                      | H15         | PT7,LD15            | P3          | P92,SCLK0, CTS0,                 | U12         | D1              |

| C16         | P63,A19                      | H16         | P51,A9              | P5          | PX4,CLKOUT, LDIV                 | U13         | D3              |

| C17         | P62,A18                      | H17         | P50,A8              | P6          | PP2,TA5OUT                       | U14         | D5              |

| D1          | P97,PY                       | J1          | PN2,KO2             | P7          | PP4,INT6,TB0IN0                  | U15         | D7              |

| D2          | AVSS                         | J2          | PN1,KO1             | P8          | PR0,SPDI                         | U16         | P10,D8          |

| D3          | PW0                          | J3          | PN0,KO0             | P9          | PR3,SPCLK                        | U17         | Dummy4          |

| D5          | PG0,AN0                      | J4          | PV4                 | P10         | DBGE                             |             | y .             |

| D6          | PC6,EA28                     | J6          | DVSS2               | P11         | PZ1,EI_SYNCLK                    |             |                 |

| D7          | PC4,EA26                     | J12         | DVSS8               | P12         | PZ3,EI_REFCLK                    |             |                 |

| D8          | P74,EA25                     | J14         | PT6,LD14            | P13         | PZ5,EI_REPCLK<br>PZ5,EI_COMRESET |             |                 |

| ᄱ           | 1 1+,LMZJ                    | J14         | 1 10,6014           | ГΙЭ         | I ZU,LI_COIVIINESEI              |             |                 |

Note1: The P96, P97 and PG0~PG5 operate with the AVCC power supply.

Note2: The PW0~PW7 and PV0~PV7 operate with the DVCC3B power supply.

Note3: The X1 and X2 operate with the DVCC1C power supply.

### 2.2 Pin names and Functions

The names of the input/output pins and their functions are described below.

Table 2.2.1 Pin names and functions (1/6)

| Pin name         | Number of Pins      | I/O    | Functions                                                                          |

|------------------|---------------------|--------|------------------------------------------------------------------------------------|

| D0 to D7         | 8                   | I/O    | Data: Data bus D0 to D7                                                            |

| P10 to P17       |                     | I/O    | Port 1: I/O port input or output specifiable in units of bits                      |

| D8 to D15        | 8                   | I/O    | Data: Data bus D8 to D15                                                           |

| P40 to P47       |                     | Output | Port 4: Output port                                                                |

| A0 to A7         | 8                   | Output | Address: Address bus A0 to A7                                                      |

| P50 to P57       |                     | Output | Port 5: Output port                                                                |

| A8 to A15        | 8                   | Output | Address: Address bus A8 to A15                                                     |

| P60 to P67       |                     | I/O    | Port 6: I/O port input or output specifiable in units of bits                      |

| A16 to A23       | 8                   | Output | Address: Address bus A16 to A23                                                    |

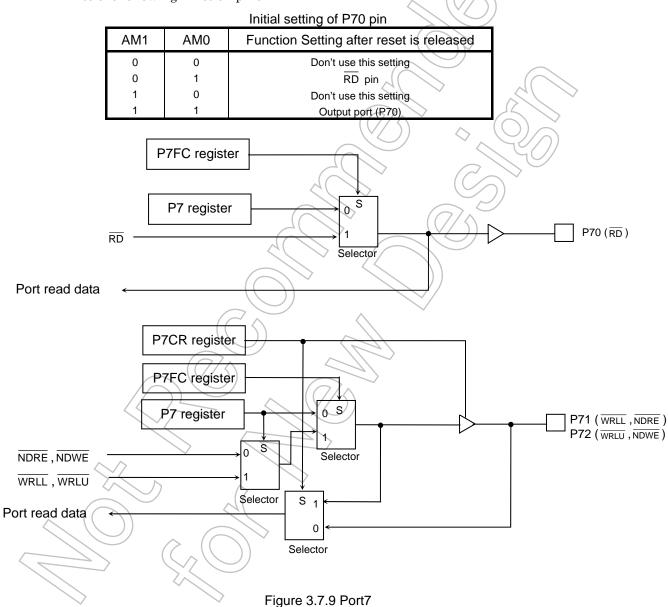

| P70              | 1                   | Output | Port 70: Output port                                                               |

| $\overline{RD}$  |                     | Output | Read: Outputs strobe signal to read external memory                                |

| P71              | 1                   | I/O    | Port 71: Output port                                                               |

| WRLL             |                     | Output | Write: Outputs strobe signal for writing data on pins D0 to D7                     |

| NDRE             |                     | Output | NAND Flash read: Outputs strobe signal to read external NAND-Flash                 |

| P72              | 1                   | I/O    | Port 72: I/O port                                                                  |

| WRLU             |                     | Output | Write: Outputs strobe signal for writing data on pins D8 to D15                    |

| NDWE             |                     | Output | NAND Flash write: Write enable for NAND Flash                                      |

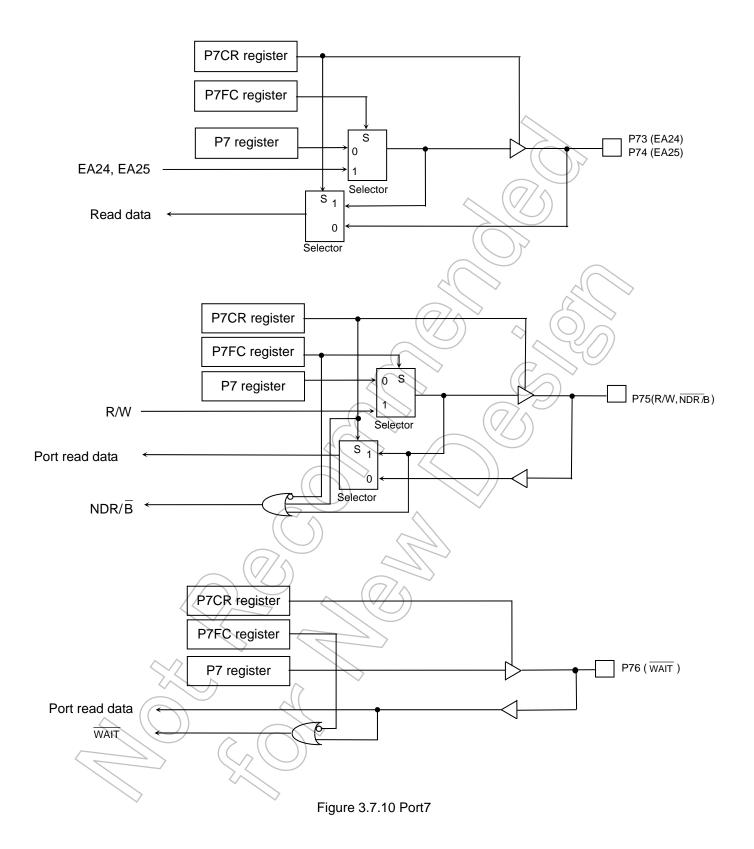

| P73              | 1                   | I/O    | Port 73: I/O port                                                                  |

| EA24             |                     | Output | Expanded address 24                                                                |

| P74              | 1                   | I/O    | Port 74: I/O port                                                                  |

| EA25             |                     | Output | Expanded address 25                                                                |

| P75              | 1                   | I/O    | Port 75: I/O port                                                                  |

| $R/\overline{W}$ |                     | Output | Read/Write: "High" represents read or dummy cycle; "Low" represents write cycle    |

| NDR/B            |                     | Input  | NAND Flash Ready(1) / Busy(0) input                                                |

| P76              | _                   | 1/0    | Port 76: I/O port                                                                  |

| WAIT             | 1                   | Input  | Wait: Signal used to request CPU bus wait                                          |

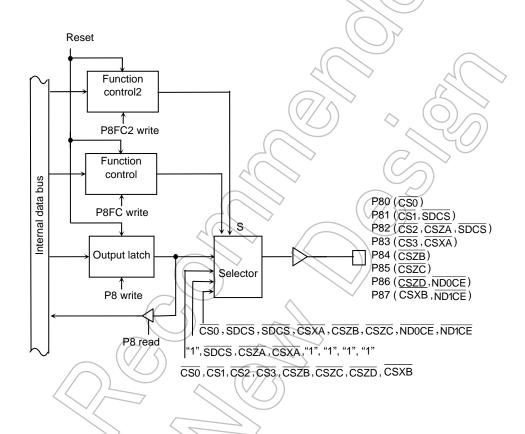

| P80              |                     | Output | Port 80: Output port                                                               |

| CS0              | 1 /                 | Output | Chip select 0: Outputs "Low" when address is within specified address area         |

| P81              | 1                   | Output | Port 81: Output port                                                               |

| CS1              |                     | Output | Chip select 1: Outputs "Low" when address is within specified address area         |

| SDCS             |                     | Output | Chip select for SDRAM: Outputs "Low" when the address is within SDRAM address area |

| P82              | $\langle 1 \rangle$ | Output | Port 82: Output port                                                               |

| CS2              |                     | Output | Chip select 2: Outputs "Low" when address is within specified address area         |

| CSZA             |                     | Output | Expanded address ZA: Outputs "Low" when address is within specified address area   |

| SDCS             |                     | Output | Chip select for SDRAM: Outputs "Low" when the address is within SDRAM address area |

| P83              |                     | Output | Port 83: Output port                                                               |

| CS3              |                     | Output | Chip select 3: Outputs "Low" when address is within specified address area         |

| CSXA             |                     | Output | Expanded address XA: Outputs "Low" when address is within specified address area   |

| P84              | 1                   | Output | Port 84: Output port                                                               |

| CSZB             | $\supset$           | Output | Expanded address ZB: Outputs "Low" when address is within specified address area   |

| P85              | 1                   | Output | Port 85: Output port                                                               |

| CSZC             |                     | Output | Expanded address ZC: Outputs "Low" when address is within specified address area   |

Table 2.2.1 Pin names and functions (2/6)

| P86   CSZD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin name   | Number of Pins                         | I/O      | Functions                                                                                   |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------|----------|---------------------------------------------------------------------------------------------|--|--|--|--|--|

| NDOCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P86        |                                        | Output   | Port 86: Output port                                                                        |  |  |  |  |  |

| P87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CSZD       | 1                                      | Output   | Expanded address ZD: Outputs "Low" when address is within specified address area            |  |  |  |  |  |

| P87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ND0CE      |                                        | Output   | Chip select for NAND Flash 0: Outputs "Low" when NAND Flash 0 is enable                     |  |  |  |  |  |

| NDICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P87        |                                        | Output   |                                                                                             |  |  |  |  |  |

| P90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CSXB       | 1                                      | Output   | Expanded address XB: Outputs "Low" when address is within specified address area            |  |  |  |  |  |

| P90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ND1CE      |                                        | Output   | Chip select for NAND Flash 1: Outputs "Low" when NAND Flash 1 is enable                     |  |  |  |  |  |

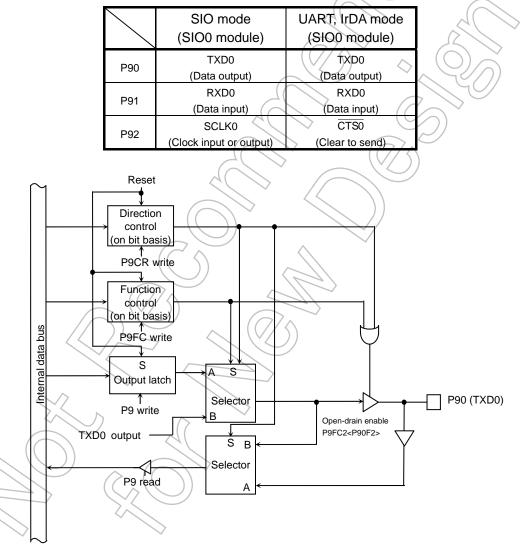

| TXD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P90        | _                                      | I/O      | 1/7/                                                                                        |  |  |  |  |  |

| RXD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TXD0       | 1                                      | Output   | Transmit data for serial 0: programmable Open-drain output                                  |  |  |  |  |  |

| RXD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P91        |                                        | I/O      | Port 91: I/O port (Schmitt-input)                                                           |  |  |  |  |  |

| SCLK0 CTS0 Input Enable to send data for serial 0 Enable to send data for serial 0 (Clear to send)  P96 Intraction Input Input Input Input Input Interrupt request pin 4: Interrupt request pin with programmable rising/falling edge  X-Plus: Pin connected to X+ pin for Touch Screen I/F  PA0 to PA7 KI0 to KI7 Input Input Input Input Input Interrupt request pin 0 to 7: Pin used for key on wake-up 0 to 7 (Schmitt-input, with pull-up resistor)  PC0 INT0 Input Input Input Interrupt request pin 0: Interrupt request pin with programmable rising/falling edge  PC1 I/O POrt C1: I/O port (Schmitt-input) Intraction Input Interrupt request pin 0: Interrupt request pin with programmable rising/falling edge  PC2 Input Input Input Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge  PC3 I/O POrt C2: I/O port (Schmitt-input) Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge  PC3 I/O POR C2: I/O port (Schmitt-input) Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  PC3 I/O POR C3: I/O port (Schmitt-input) Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  PC3 I/O POR C3: I/O port (Schmitt-input) Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  PC3 I/O POR C3: I/O port (Schmitt-input) Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  PC4 Input Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  PC4 Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  PC5 I/O POR C4: I/O port Expanded address 28  PC6 I/O POR C6: I/O port Expanded address 28  PC7 I/O POR C7: I/O port PC6: I/O port Expanded address 28  PC7 I/O POR C7: I/O port                                                                                                                                                                                                                               | RXD0       | 1                                      | Input    |                                                                                             |  |  |  |  |  |

| CTS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P92        |                                        | I/O      | Port 92: I/O port (Schmitt-input)                                                           |  |  |  |  |  |

| P96 1 Input  | SCLK0      | 1                                      | I/O      | Clock I/O for serial 0                                                                      |  |  |  |  |  |

| INT4 PX Output Output Output PX Output Output Output PY Output PY Output PY Output POrt 97: Input port (schmitt input) PY-Plus: Pin connected to X+ pin for Touch Screen I/F PAO to PA7 RIO to KI7 PO Input POrt A0 to A7: Input port Rey input 0 to 7: Pin used for key on wake-up 0 to 7 (Schmitt-input, with pull-up resistor) PCO Input Input Interrupt request pin 0: Interrupt request pin with programmable rising/falling edge PC1 I/O Port C1: I/O port (Schmitt-input) Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge Input Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge Input Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge Input Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge Input Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge Input Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge Input  | CTS0       |                                        | Input    | Enable to send data for serial 0 (Clear to send)                                            |  |  |  |  |  |

| PX Output X-Plus: Pin connected to X+ pin for Touch Screen I/F  P97 1 Input Output Y-Plus: Pin connected to Y+ pin for Touch Screen I/F  PA0 to PA7 8 Input Port A0 to A7: Input port  KI0 to KI7 8 Input Input Input Input Port Co: I/O port (Schmitt-input)  PC0 1 I/O Port Co: I/O port (Schmitt-input)  INT0 1 Input Interrupt request pin 0: Interrupt request pin with programmable rising/falling edge  PC1 I/O Port C1: I/O port (Schmitt-input)  INT1 1 Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge  PC2 1 I/O Port C2: I/O port (Schmitt-input)  INT2 1 Input Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge  PC3 I/O Port C3: I/O port (Schmitt-input)  INT3 1 Input Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge  PC3 I/O Port C3: I/O port (Schmitt-input)  INT3 1 Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  PC4 1 I/O Port C4: I/O port  EA26 1 Output Expanded address 26  PC5 1 I/O Port C5: I/O port  EA27 0 Output Expanded address 27  PC6 1 I/O Port C6: I/O port  EA28 Output Expanded address 28  PC7 I/O Port C7: I/O port  Expanded address 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P96        | 1                                      | Input    | Port 96: Input port (schmitt-input, with pull-up resistor)                                  |  |  |  |  |  |

| PX Output X-Plus: Pin connected to X+ pin for Touch Screen I/F  P97 1 Input Output Y-Plus: Pin connected to Y+ pin for Touch Screen I/F  PA0 to PA7 8 Input Port A0 to A7: Input port  KI0 to KI7 8 Input Input Input Input Port Co: I/O port (Schmitt-input)  PC0 1 I/O Port Co: I/O port (Schmitt-input)  INT0 1 Input Interrupt request pin 0: Interrupt request pin with programmable rising/falling edge  PC1 I/O Port C1: I/O port (Schmitt-input)  INT1 1 Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge  PC2 1 I/O Port C2: I/O port (Schmitt-input)  INT2 1 Input Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge  PC3 I/O Port C3: I/O port (Schmitt-input)  INT3 1 Input Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge  PC3 I/O Port C3: I/O port (Schmitt-input)  INT3 1 Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  PC4 1 I/O Port C4: I/O port  EA26 1 Output Expanded address 26  PC5 1 I/O Port C5: I/O port  EA27 0 Output Expanded address 27  PC6 1 I/O Port C6: I/O port  EA28 Output Expanded address 28  PC7 I/O Port C7: I/O port  Expanded address 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | INT4       |                                        | Input    | Interrupt request pin 4: Interrupt request pin with programmable rising/falling edge        |  |  |  |  |  |

| P97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PX         |                                        | Output   |                                                                                             |  |  |  |  |  |

| PA0 to PA7 KI0 to KI7  8  Input Input Input Key input 0 to 7: Pin used for key on wake-up 0 to 7 (Schmitt-input, with pull-up resistor)  PC0 INT0  1  IND Input Input Interrupt request pin 0: Interrupt request pin with programmable rising/falling edge  PC1 INT1  1 Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge  Input Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge  Input Input Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge  PC3 INT2  Input Input Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge  PC3 INT3  I Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  Input Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  Input Input Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  Input pin for 8 bit timer 2  PC4 Input Input Input Input Input Input pin for 8 bit timer 2  PC5 Input Input Input Input Input Input pin for 8 bit timer 2  PC6 Input Input Input Input Input Input pin for 8 bit timer 2  PC7 I/O Port C6: I/O port Input Inpu | P97        | 1                                      | Input    |                                                                                             |  |  |  |  |  |

| Kilo to Ki7   S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PY         |                                        | Output   | Y-Plus: Pin connected to Y+ pin for Touch Screen I/F                                        |  |  |  |  |  |

| RIO to KI7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PA0 to PA7 | •                                      | Input    | Port A0 to A7: Input port                                                                   |  |  |  |  |  |

| INTO  Input Interrupt request pin 0: Interrupt request pin with programmable rising/falling edge  PC1 INT1 Input Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge Input Timer A0 input: Input pin for 8 bit timer 0  PC2 INT2 Input Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge  PC3 INT3 Input Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge  PC3 INT3 Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  Input Input pin for 8 bit timer 2  PC4 EA26 IOUtput Expanded address 26  PC5 IOUtput Expanded address 27  PC6 EA27 Output Expanded address 27  PC6 EA28 Output Expanded address 28  PC7 I/O Port C7: I/O port  Expanded address 28  PC7 I/O Port C7: I/O port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | KI0 to KI7 | 8                                      | Input    | Key input 0 to 7: Pin used for key on wake-up 0 to 7 (Schmitt-input, with pull-up resistor) |  |  |  |  |  |

| INTO Input Interrupt request pin 0: Interrupt request pin with programmable rising/falling edge  PC1 INT1 1 Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge  INT1 Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge  Input Input Input pin for 8 bit timer 0  PC2 INT2 INT2 Input Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge  PC3 INT3 I Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  Input Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge  Input Input Input pin for 8 bit timer 2  PC4 I I/O Port C4: I/O port  EA26 I Output Expanded address 26  PC5 I Output Expanded address 27  PC6 EA28 Output Expanded address 28  PC7 I/O Port C6: I/O port  Expanded address 28  PC7 I/O Port C7: I/O port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PC0        |                                        | I/O      | Port C0: I/O port (Schmitt-input)                                                           |  |  |  |  |  |

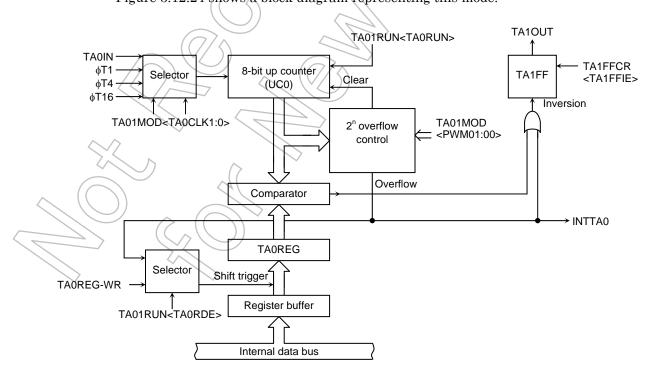

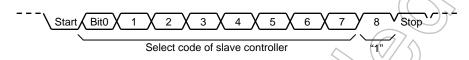

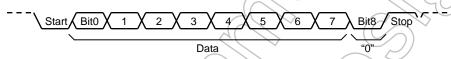

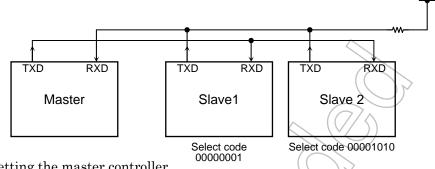

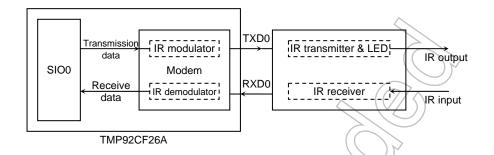

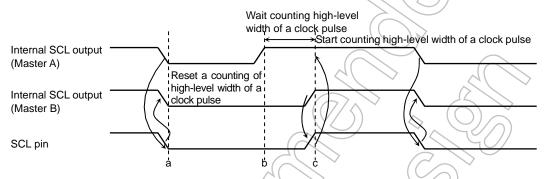

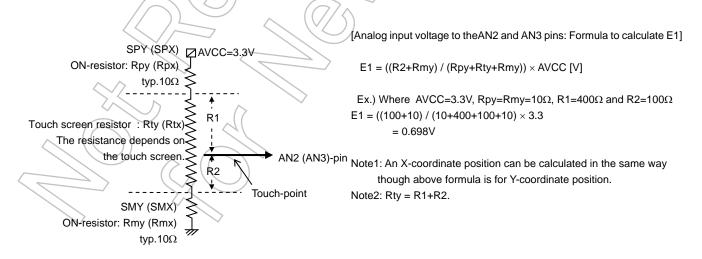

| INT1 1 Input Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge  TA0IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | INT0       | 1                                      | Input    | Interrupt request pin 0: Interrupt request pin with programmable rising/falling edge        |  |  |  |  |  |