# **TOSHIBA CORPORATION**

Semiconductor Company

# **Document Change Notification**

The purpose of this notification is to inform customers about the launch of the Pb-free version of the device. The introduction of a Pb-free replacement affects the datasheet. Please understand that this notification is intended as a temporary substitute for a revision of the datasheet.

Changes to the datasheet may include the following, though not all of them may apply to this particular device.

- 1. Part number

- Example: TMPxxxxxF TMPxxxxxFG

All references to the previous part number were left unchanged in body text. The new part number is indicated on the prelims pages (cover page and this notification).

2. Package code and package dimensions

Example: LQFP100-P-1414-0.50C LQFP100-P-1414-0.50F

All references to the previous package code and package dimensions were left unchanged in body text. The new ones are indicated on the prelims pages.

3. Addition of notes on lead solderability

Now that the device is Pb-free, notes on lead solderability have been added.

4. RESTRICTIONS ON PRODUCT USE

The previous (obsolete) provision might be left unchanged on page 1 of body text. A new replacement is included on the next page,

5. Publication date of the datasheet

The publication date at the lower right corner of the prelims pages applies to the new device.

#### 1. Part number

#### 2. Package code and dimensions

| Previous Part Number<br>(in Body Text) | Previous Package Code<br>(in Body Text) | New Part Number | New Package Code   | OTP         |

|----------------------------------------|-----------------------------------------|-----------------|--------------------|-------------|

| TMP87CM53F                             | QFP80-P-1420-0.80B                      | TMP87CM53FG     | QFP80-P-1420-0.80B | TMP87PM53FG |

\*: For the dimensions of the new package, see the attached Package Dimensions diagram.

#### 3. Addition of notes on lead solderability

The following solderability test is conducted on the new device.

#### Lead solderability of Pb-free devices (with the G suffix)

| Test          | Test Conditions                                                                                                                                                                                                                                                                                                                                                   | Remark                                                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Solderability | <ul> <li>(1) Use of Lead (Pb)</li> <li>solder bath temperature = 230°C</li> <li>dipping time = 5 seconds</li> <li>the number of times = once</li> <li>use of R-type flux</li> <li>(2) Use of Lead (Pb)-Free</li> <li>solder bath temperature = 245°C</li> <li>dipping time = 5 seconds</li> <li>the number of times = once</li> <li>use of R-type flux</li> </ul> | Leads with over 95% solder coverage<br>till lead forming are acceptable. |

# 4. RESTRICTIONS ON PRODUCT USE

The following replaces the "RESTRICTIONS ON PRODUCT USE" on page 1 of body text.

# RESTRICTIONS ON PRODUCT USE

20070701-EN

The information contained herein is subject to change without notice.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its

use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third

parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

## 5. Publication date of the datasheet

The publication date of this datasheet is printed at the lower right corner of this notification.

(Annex)

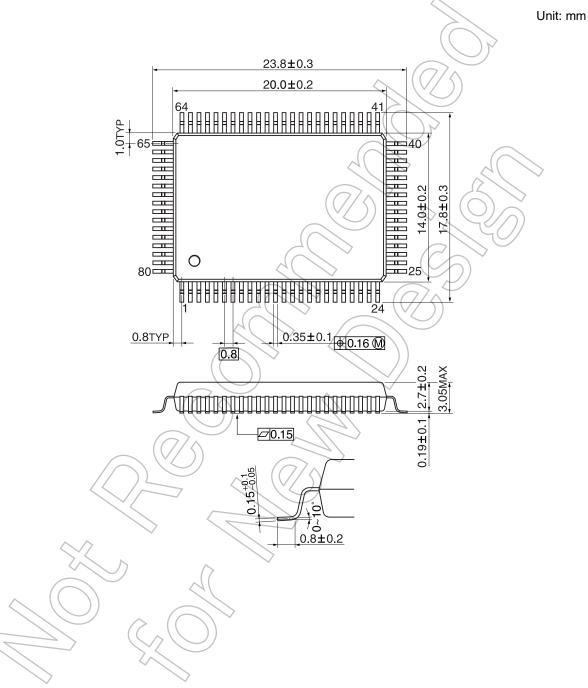

Package Dimensions

QFP80-P-1420-0.80B

#### CMOS 8-Bit Microcontroller

TMP87CM53F

The 87CM53 is the high speed and high performance 8-bit single chip microcomputers. These MCU contain CPU core, ROM, RAM, input/output ports, an A/D converter, DTMF generator, multi-function timer/counters, two serial interfaces, and two clock generators on a chip. The 87CM53 provides high current output capability for LED direct drive.

| Part No.   | ROM          | RAM          | Package OTP MCU               |

|------------|--------------|--------------|-------------------------------|

| TMP87CM53F | 32 K x 8-bit | 1024 × 8-bit | P-QFP80-1420-0.80B TMP87PM53F |

|            |              |              |                               |

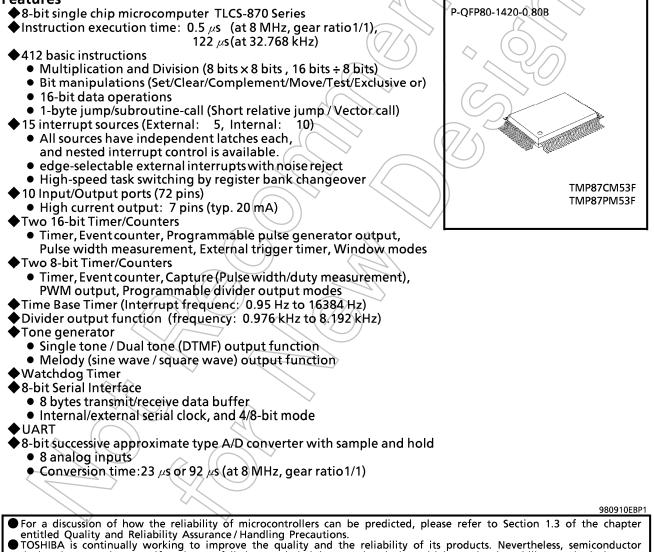

#### **Features**

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others. The information contained herein is subject to change without notice.

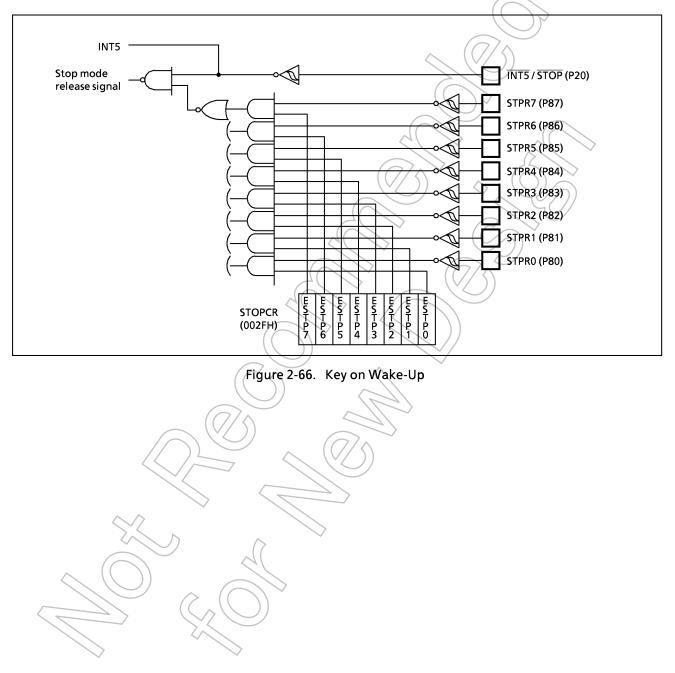

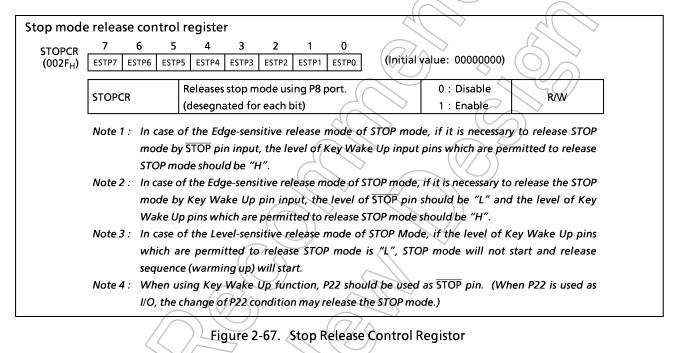

- Key on Wake-Up

- Dual clock operation

- ◆Internal clock select mode (fc, fc/2, fc/4, fc/8) Initial fc/8 operation

- Five Power saving operating modes

- STOP mode: Oscillation stops. Battery/Capacitor back-up. Port output hold/high-impedance.

- SLOW mode: Low power consumption operation using low-frequency clock (32.768kHz).

- IDLE1 mode: CPU stops, and Peripherals operate using high-frequency clock. Release by interrupts.

- IDLE2 mode: CPU stops, and Peripherals operate using high and low frequency clock. Release by interrupts.

- SLEEP mode: CPU stops, and Peripherals operate using low-frequency clock. Release by interrupts.

- ♦ Wide operating voltage: 2.2 to 5.5 V at [3.58 MHz] [3.84 MHz] [4.0 MHz] [4.19 MHz] / 32.768 kHz,

- 4.5 to 5.5 V at 8 MHz / 32.768 kHz ◆Emulation Pod: BM87CM53F0A

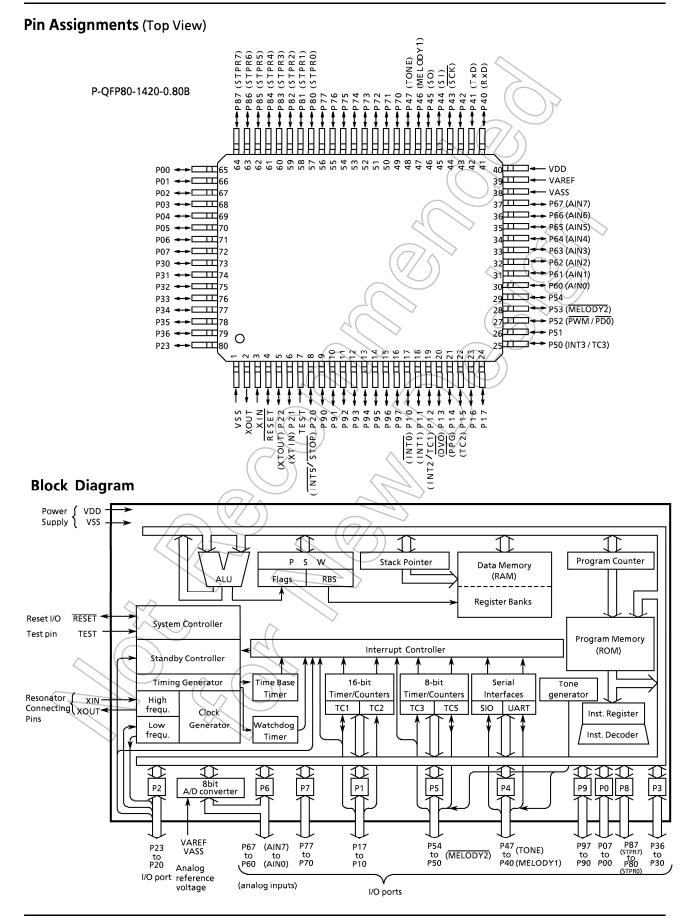

# **Pin Function**

| Pin Name         | Input / Output | Func                                                                                         | tion                                                               |

|------------------|----------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

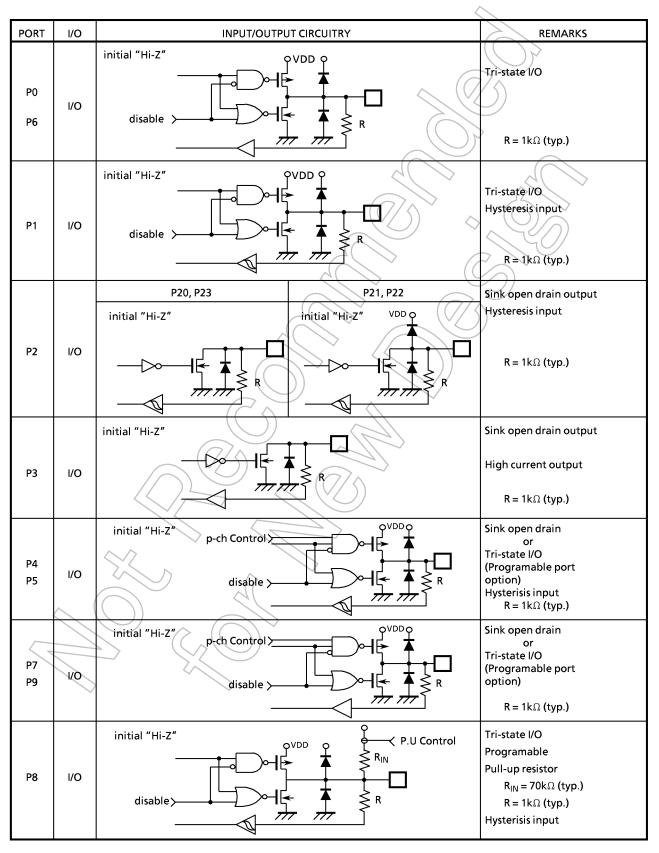

| P07 to P00       | I/O            | Two 8-bit programmable input/output                                                          |                                                                    |

| P17, P16         | I/O            | ports (tri-state).                                                                           |                                                                    |

| P15 (TC2)        | l/O (Input)    | Each bit of these ports can be individually configured as an input or an output              | Timer/Counter 2 input                                              |

| P14 (PPG)        |                | under software control.                                                                      | Programmable pulse generator output                                |

| P13 (DVO)        | I/O (Output)   | During reset, all bits are configured as                                                     | Divider output                                                     |

| P12 (INT2 / TC1) |                | input.                                                                                       | External interrupt input 2 or<br>Timer/Counter 1 input             |

| P11 (INT1)       | I/O (Input)    | When used as a divider output or a PPG                                                       | External interrupt input 1                                         |

| P10 (INTO)       |                | output, the latch must be set to "1".                                                        | External interrupt input 0                                         |

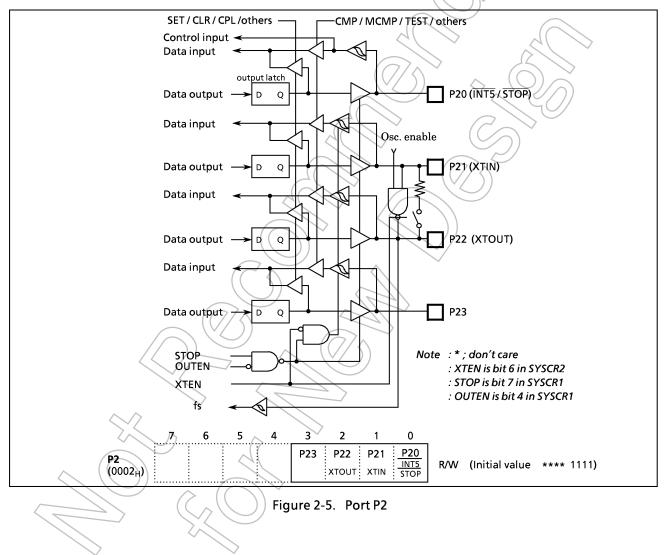

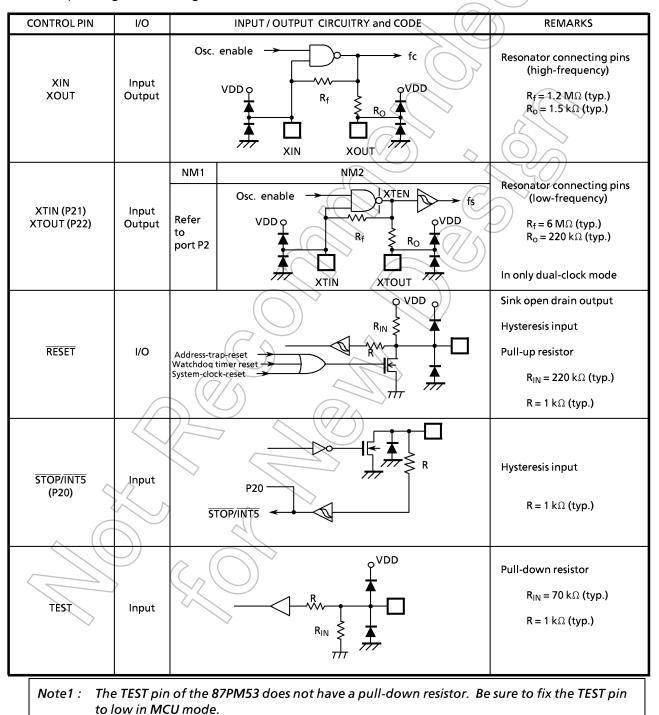

| P23              | I/O            | (7)                                                                                          |                                                                    |

| P22 (XTOUT)      | I/O (Output)   | 4-bit input/output port with latch.                                                          | Resonator connecting pins (32.768kHz).                             |

| P21 (XTIN)       | "o (output)    | When used as an input port, the latch                                                        | For inputting external clock, XTIN is used<br>and XTOUT is opened. |

| P20 (INT5/STOP)  | l/O (Input)    | must be set to "1".                                                                          | External interrupt input 5 or STOP mode<br>release signal input    |

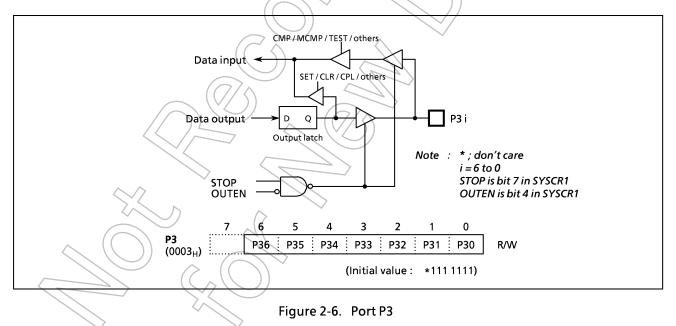

| P36 to P30       | 1/0            | 7-bit input/output port (high current output<br>When used as an input port, the latch must l | t) with latch.                                                     |

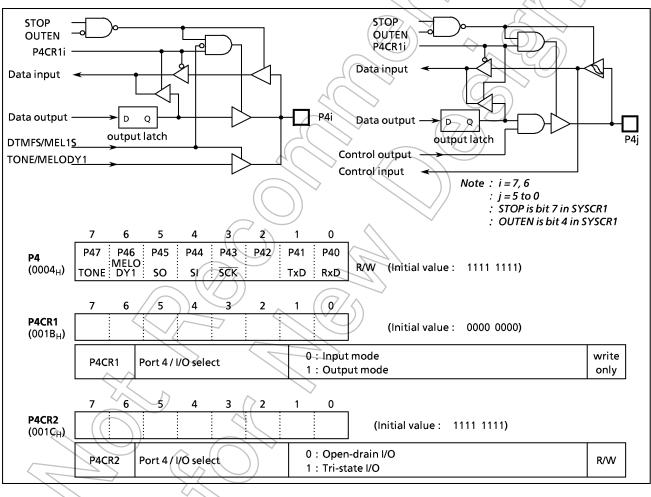

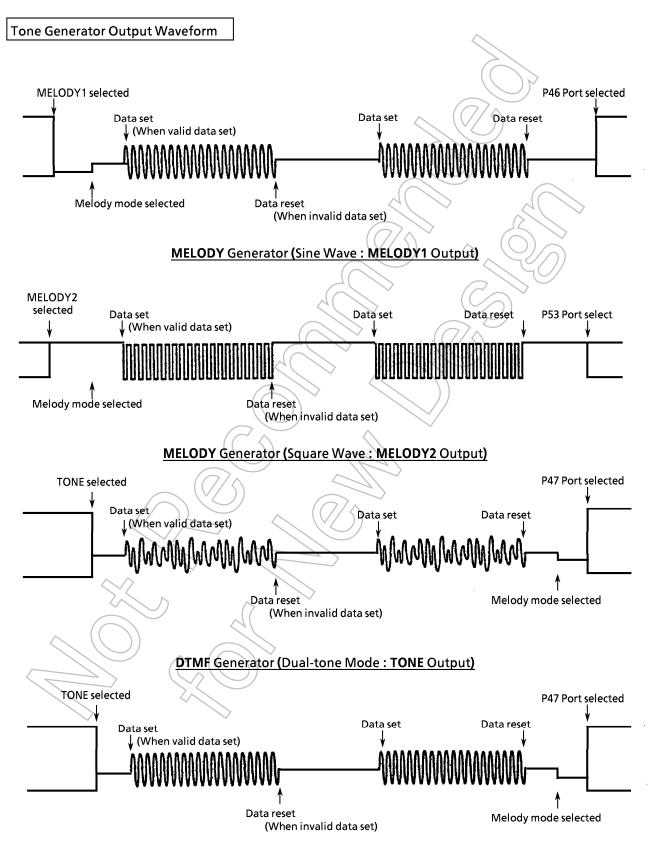

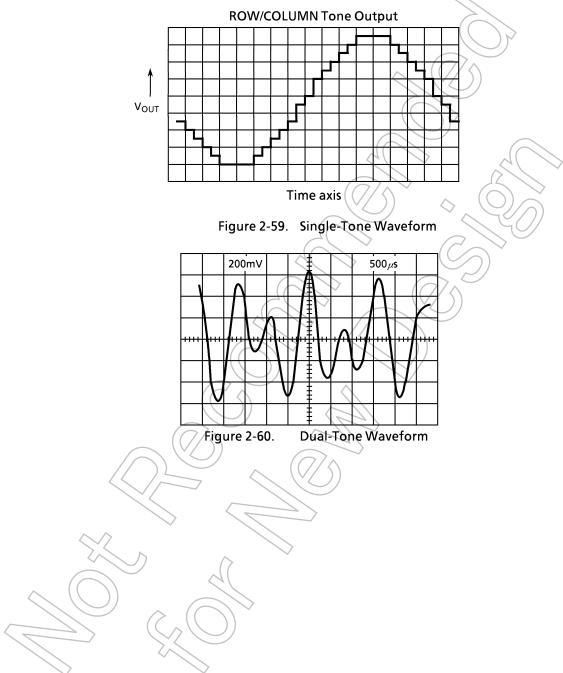

| P47 (Tone)       | I/O (Output)   | 8-bit programmable input/output port                                                         | Tone output                                                        |

| P46 (Melody1)    | I/O (Output)   | (tri-state). Each bit of the port can be                                                     | Melody1 output (sine wave)                                         |

| P45 (SO)         | I/O (Output)   | individually configured as an input or an                                                    | SIO serial data output                                             |

| <br>P44 (SI)     | I/O (Input)    | output or a port option under software control. During reset, all bits are                   | SIO serial data input                                              |

| P43 (SCK)        | I/O (I/O)      | configured as input.                                                                         | SIO serial clock input/output                                      |

| P42              | I/O            |                                                                                              |                                                                    |

| P41 (TxD)        | I/O (Output)   | When used as an input port or a SIO                                                          | SIO serial data output                                             |

| P40 (RxD)        | I/O (Input)    | input/output, the latch must be set to "1".                                                  | (asynchronous only)<br>SIO serial data input                       |

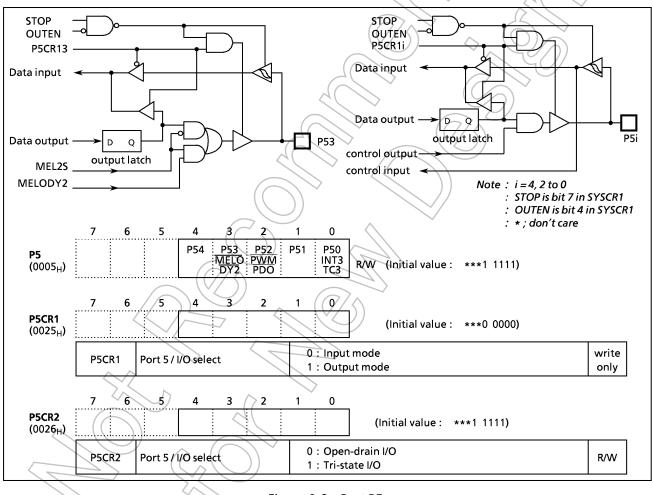

| P54              | 1/0            | 5-bit programmable input/output port                                                         | (asynchronous only)                                                |

|                  | I/O (Output)   | (tri-state). Each bit of the port can be<br>individually configured as an input or an        | Melody2 output (square wave)                                       |

| P53 (Melody2)    |                | output or a port option under software control. During reset, all bits are                   | 8-bit PWM output or                                                |

| P52 (PWM/PDO)    | I/O (Output)   | configured as input.                                                                         | 8-bit programmable divider output                                  |

|                  |                | When used as an inp <u>ut port, an</u> external interrupt input, or a PWM/PDO output,        | External interrupt input 3 or                                      |

| P50 (INT3/TC3)   | I/O (Input)    | the latch must be set to "1".<br>8-bit programmable input/output port                        | Timer/Counter 3 input                                              |

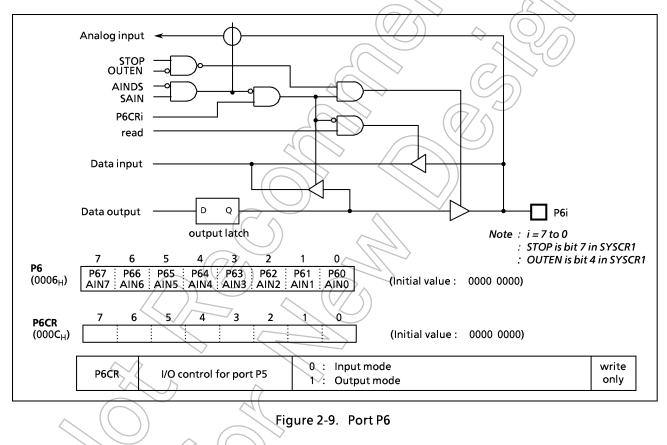

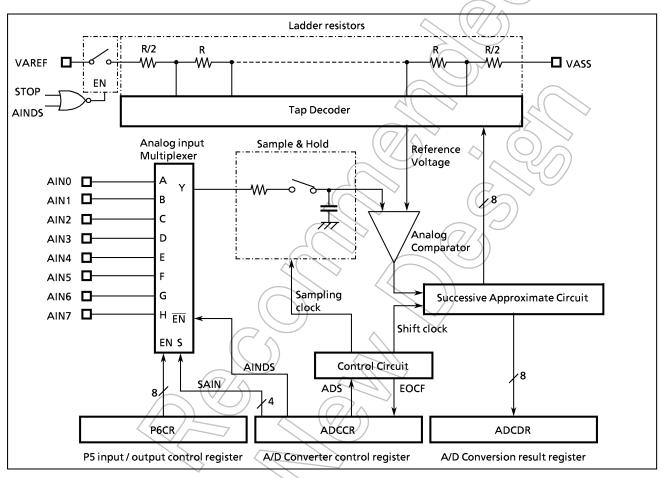

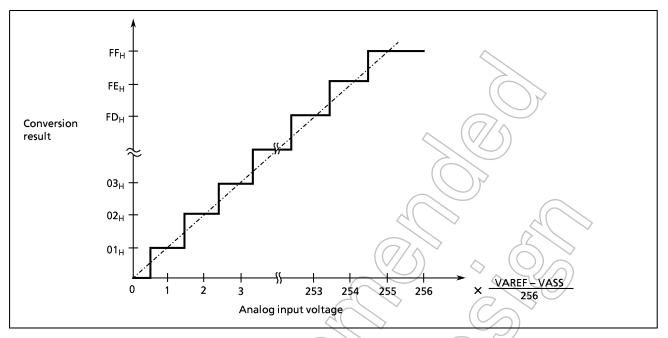

| P67 (AIN7)       | I/O (Input)    | (tri-state). Each bit of the port can be<br>individually configured as an input or an        | A/D converter analog inputs                                        |

| to P60 (ÁIN0)    |                | output under software control.                                                               | toto). Foch bit of the port can be                                 |

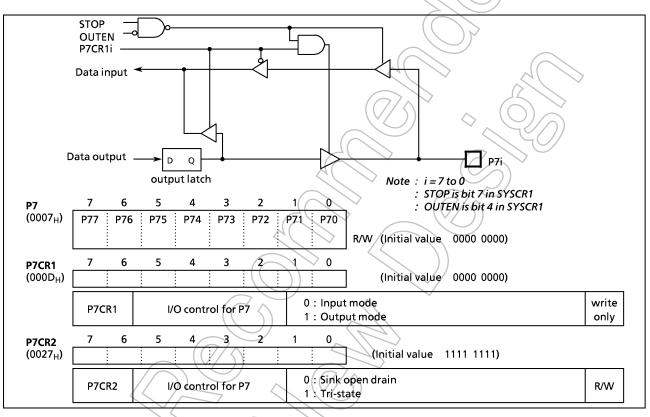

| P77 to P70       | I/Q            | 8-bit programmable input/output port (tri-s<br>individually configured as an input or an ou  | tput or a port option under software                               |

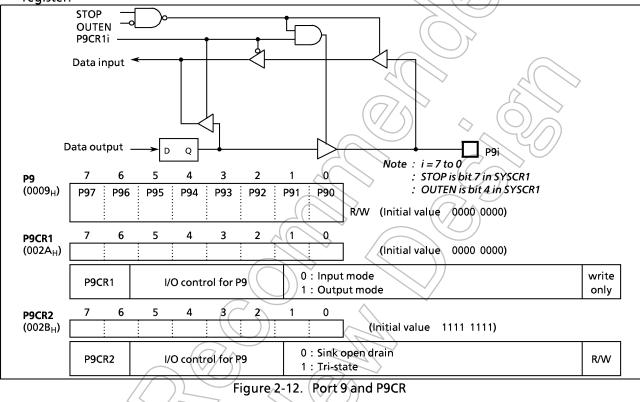

| P97 to P90       | 1/0            | control. During reset, all bits are configure                                                | •                                                                  |

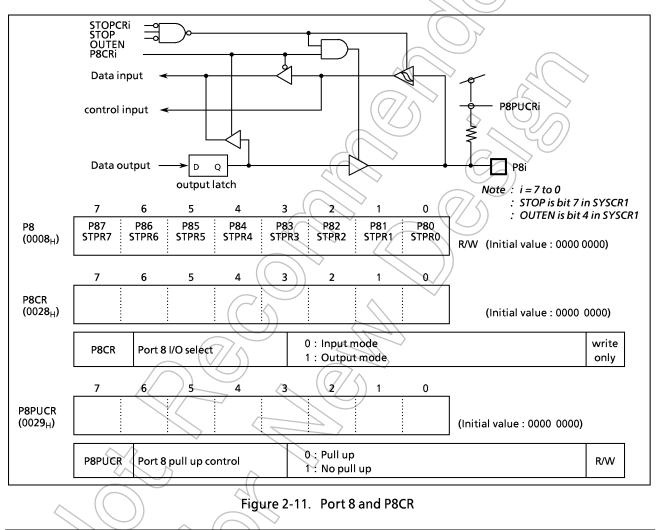

| P87 (STPR7)      | I/O (Input)    | 8-bit programmable input/output port (tri-s<br>individually configured as an input or an ou  | tput or a pull-up resister under software                          |

| to P80 (STPR0)   |                | control. During reset, all bits are configared                                               | 1                                                                  |

| XIN, XOUT        | Input, Output  | Resonator connecting pins for high-frequen<br>For inputting external clock, XIN is used and  | XOUT is opened.                                                    |

| RESET            | I/O            | Reset signal input or watchdog timer outpur reset output.                                    | vadaress-trap-reset output/system-clock-                           |

| TEST             | Input          | Test pin for out-going test. Be tied to low.                                                 |                                                                    |

| VDD, VSS         | Bower Supply   | + 5 V, 0 V (GND)                                                                             |                                                                    |

| VAREF, VASS      | Power Supply   | Analog reference voltage inputs (High, Low                                                   | )                                                                  |

1999-08-23

# **OPERATIONAL DESCRIPTION**

# 1. CPU CORE FUNCTIONS

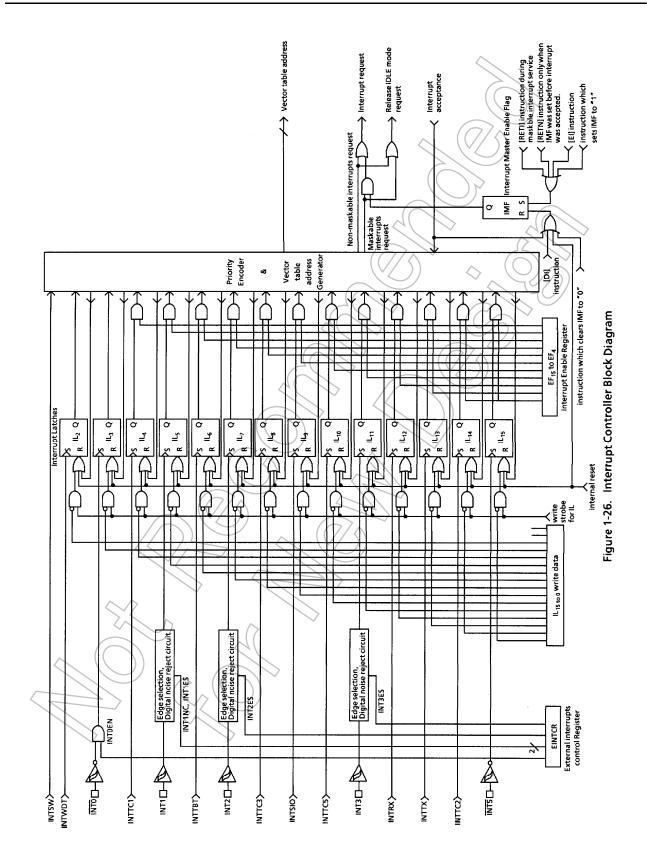

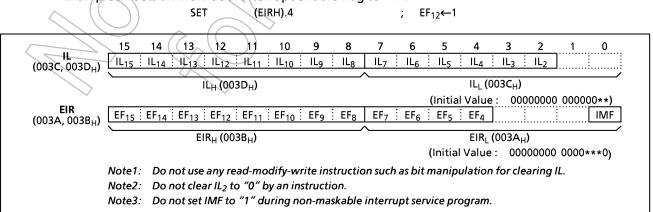

The CPU core consists of a CPU, a system clock controller, an interrupt controller, and a watchdog timer. This section provides a description of the CPU core, the program memory (ROM), the data memory (RAM), and the reset circuit.

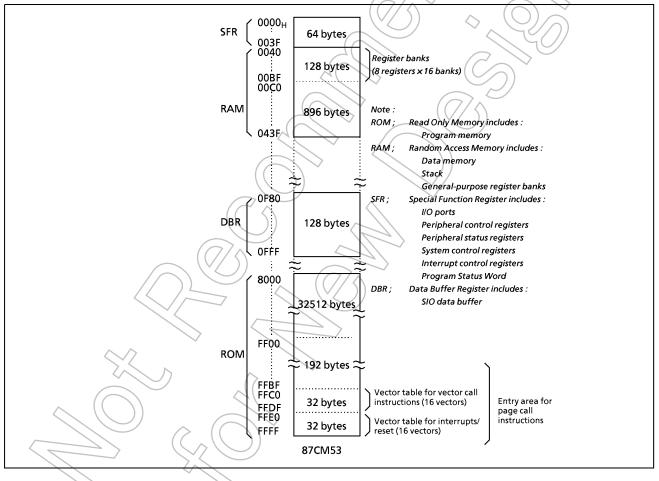

## 1.1 Memory Address Map

The TLCS-870 Series is capable of addressing 64K bytes of memory. Figure 1-1 shows the memory address maps of the 87CM53. In the TLCS-870 Series, the memory is organized 4 address spaces (ROM, RAM, SFR, and DBR). It uses a memory mapped I/O system, and all I/O registers are mapped in the SFR/DBR address spaces. There are 16 banks of general-purpose registers. The register banks are also assigned to the first 128 bytes of the RAM address space.

Figure 1-1. Memory Address Maps

# 1.2 **Program Memory (ROM)**

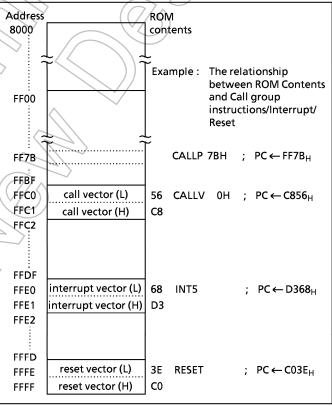

The 87CM53 has a 32K x 8-bit (address  $8000_{\text{H}}$ -FFFF<sub>H</sub>) of program memory (mask programmed ROM). Addresses FF00<sub>H</sub>-FFFF<sub>H</sub> in the program memory can also be used for special purposes.

- Interrupt / Reset vector table (addresses FFE0<sub>H</sub>-FFFF<sub>H</sub>) This table consists of a reset vector and 15 interrupt vectors (2 bytes/vector). These vectors store a reset start address and interrupt service routine entry addresses.

- (2) Vector table for vector call instructions (addresses FFC0<sub>H</sub>-FFDF<sub>H</sub>)

This table stores call vectors (subroutine entry address, 2 bytes/vector) for the vector call instructions [CALLV n]. There are 16 vectors. The CALLV instruction increases memory efficiency when utilized for frequently used subroutine calls (called from 3 or more locations).

(3) Entry area (addresses FF00<sub>H</sub>-FFFF<sub>H</sub>) for **page call** instructions This is the subroutine entry address area for the page call instructions [CALLP n]. Addresses FF00<sub>H</sub>-FFBF<sub>H</sub> are normally used because address FFC0<sub>H</sub>-FFFF<sub>H</sub> are used for the vector tables.

Programs and fixed data are stored in the program memory. The instruction to be executed next is read from the address indicated by the current contents of the program counter (PC). There are relative jump and absolute jump instructions. The concepts of page or bank boundaries are not used in the program memory concerning any jump instruction.

- Example: The relationship between the jump instructions and the PC.

- ① 5-bit PC-relative jump [JRS cc, \$ + 2 + d] E8C4H: JRS T, \$ + 2 + 08HWhen JF = 1, the jump is made to E8CE<sub>H</sub>, which is 08<sub>H</sub> added to the contents of the PC. (The PC contains the address of the instruction being executed + 2; therefore, in this case, the PC contents are E8C4<sub>H</sub> + 2 = E8C6<sub>H</sub>.)

- 8-bit PC-relative jump [JR cc, \$+2+d] E8C4H : JR Z, \$+2+80H

When ZF = 1, the jump is made to E846<sub>H</sub>, which is FF80<sub>H</sub> (-128) added to the current contents of the PC.

- ③ 16-bit absolute jump [JP a] E8C4H : JP 0C235H

- An unconditional jump is made to address  $C235_{H}$ . The absolute jump instruction can jump anywhere within the entire 64K-bytes space.

Figure 1-2. Program Memory Map

In the TLCS-870 Series, the same instruction used to access the data memory (e.g. [LD A, (HL)]) is also used to read out fixed data (ROM data) stored in the program memory. The register-offset PC-relative addressing (PC + A) instructions can also be used, and the code conversion, table look-up and n-way multiple jump processing can easily be programmed.

| Example 1 :  | Loads the ROM contents at the address specified by the HL register pair contents into the accumulator (HL $\geqq$ 8000 <sub>H</sub> ): |                            |                                                                    |                              |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------|------------------------------|--|--|

|              | LD                                                                                                                                     | A, (HL)                    | ; A←ROM (HL)                                                       |                              |  |  |

| Example 2 :  | output                                                                                                                                 | to port P6 after e         | ent code (common anode LED). M<br>executing the following program: |                              |  |  |

|              | ADD                                                                                                                                    | A, TABLE – \$ – 4          | ; P6 $\leftarrow$ ROM (TABLE + A)                                  |                              |  |  |

|              | LD                                                                                                                                     | (P6), (PC + A)             |                                                                    | <u></u>                      |  |  |

|              | JRS                                                                                                                                    | T, SNEXT                   |                                                                    | f 🖉 g 🖉 b                    |  |  |

| TABLE :      | DB                                                                                                                                     | 0C0H, 0F9H, 0A4            | н, овон, 99н, 92н, 82н, ор8н, 80н, 9                               | <sup>8H</sup> e <b>ð Á</b> c |  |  |

| SNEXT :      |                                                                                                                                        |                            |                                                                    | e an an                      |  |  |

| Notes : "\$  | ‴ is a head                                                                                                                            | er address of ADD in:      | struction.                                                         | d                            |  |  |

| DI           | B is a byte o                                                                                                                          | lata difinition instruc    | ction.                                                             | SHLC A                       |  |  |

| Example 3 :  | N-way r                                                                                                                                | nultiple jump in           | accordance with the contents of                                    | JP (PC + A) -                |  |  |

|              | accumu                                                                                                                                 | lator ( $0 \le A \le 3$ ): | $(\langle / \rangle)$                                              |                              |  |  |

|              | SHLC                                                                                                                                   | А                          | ; if $A = 00_H$ then $PC \leftarrow C234_H$                        | C2<br>78                     |  |  |

|              | JP                                                                                                                                     | (PC + A)                   | if $A = 01_H$ then $PC \leftarrow C378_H$                          |                              |  |  |

|              |                                                                                                                                        |                            | if $A = 02_H$ then PC $\leftarrow$ DA37                            |                              |  |  |

|              |                                                                                                                                        |                            | if $A = 03_{H}$ then $PC \leftarrow E1B0_{H}$                      |                              |  |  |

|              | DW                                                                                                                                     | 0C234H, 0C378              | BH, ODA37H, OE1B0H                                                 | ВО                           |  |  |

| Note : DW is | a word dat                                                                                                                             | a definition instruct      |                                                                    | E1                           |  |  |

| L            |                                                                                                                                        | ~(                         |                                                                    |                              |  |  |

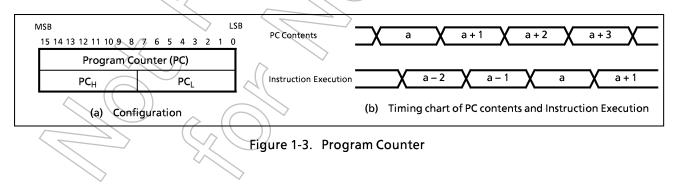

# **1.3 Program Counter (PC)**

The program counter (PC) is a 16-bit register which indicates the program memory address where the instruction to be executed next is stored. After reset, the user defined reset vector stored in the vector table (addresses  $FFF_H$  and  $FFFE_H$ ) is loaded into the PC; therefore, program execution is possible from any desired address. For example, when  $CO_H$  and  $3E_H$  are stored at addresses  $FFFF_H$  and  $FFFE_H$ , respectively, the execution starts from address  $CO3E_H$  after reset.

The TLCS-870 Series utilizes pipelined processing (instruction pre-fetch); therefore, the PC always indicates 2 addresses in advance. For example, while a 1-byte instruction stored at address C123<sub>H</sub> is being executed, the PC contains C125<sub>H</sub>.

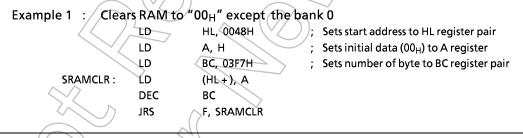

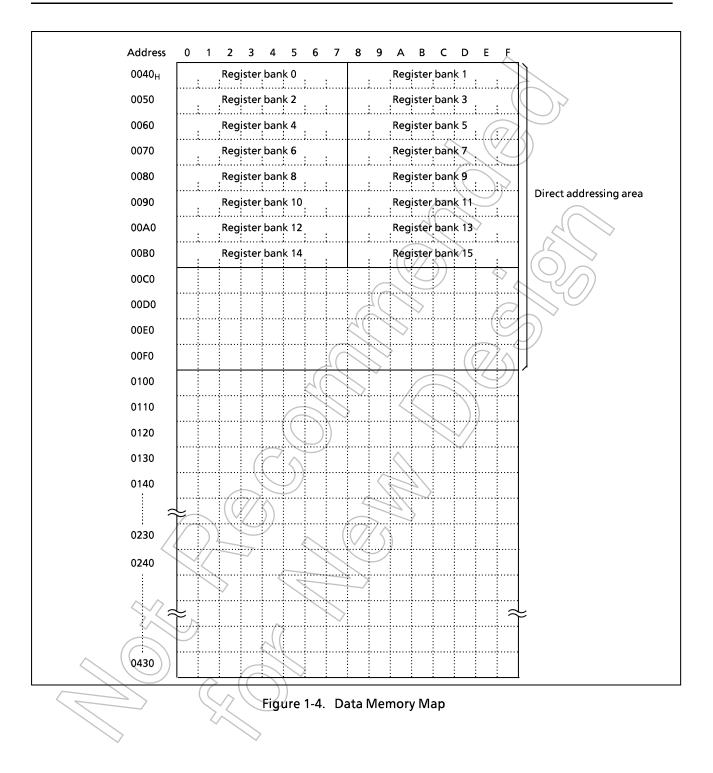

## 1.4 Data Memory (RAM)

The 87CM53 has a 1K  $\times$  8-bit (addresses 0040<sub>H</sub>-043F<sub>H</sub>) of data memory (static RAM). Figure 1-4 shows the data memory map.

Addresses  $0000_{\text{H}}$ -00FF<sub>H</sub> are used as a direct addressing area to enhance instructions which utilize this addressing mode; therefore, addresses  $0040_{\text{H}}$ -00FF<sub>H</sub> in the data memory can also be used for user flags or user counters.

Example 1 : If bit 2 at data memory address  $00C0_H$  is "1",  $00_H$  is written to data memory at address  $00E3_H$ ; otherwise, FF<sub>H</sub> is written to the data memory at address  $00E3_H$ .

|         | TEST | (00C0H).2     | ; if $(00C0_{H})_{2} = 0$ then jump      |

|---------|------|---------------|------------------------------------------|

|         | JRS  | T,SZERO       |                                          |

|         | CLR  | (00E3H)       | ; (00E3 <sub>H</sub> ) ← 00 <sub>H</sub> |

|         | JRS  | T,SNEXT       | $\leq \langle \rangle >$                 |

| SZERO : | LD   | (00E3H), 0FFH | ; (00E3 <sub>H</sub> ) ← FF <sub>H</sub> |

| SNEXT : |      |               | $(7/5)$ $\sim$ (C                        |

Example 2 : Increments the contents of data memory at address 00F5<sub>H</sub>, and clears to 00<sub>H</sub> when 10<sub>H</sub> is exceeded.

| exceeded. |          |       | $\sim$                   |                                                  |

|-----------|----------|-------|--------------------------|--------------------------------------------------|

| INC       | (00F5H)  |       | (00F5 <sub>H</sub> ) ← ( | 00F5 <sub>H</sub> ) + 1                          |

| AND       | (00F5H), | OFH ; | (00F5 <sub>H</sub> ) ← ( | 00F5 <sub>H</sub> ) <sub>Л</sub> 0F <sub>H</sub> |

|           |          |       |                          | $\langle - \rangle \subseteq$                    |

General-purpose register banks (8 registers  $\times$  16 banks) are also assigned to the 128 bytes of addresses 0040<sub>H</sub>-00BF<sub>H</sub>. Access as data memory is still possible even when being used for registers. For example, when the contents of the data memory at address 0040<sub>H</sub> is read out, the contents of the accumulator in the bank 0 are also read out. The stack can be located anywhere within the data memory except the register bank area. The stack depth is limited only by the free data memory size. For more details on the stack, see section "1.7 Stack and Stack Pointer".

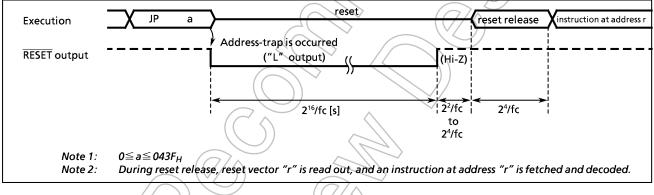

With the 87CM53, programs in data memory cannot be executed. If the program counter indicates a data memory address, an address-trap-reset is generated due to due to bus error. (Output from the RESET pin goes low.)

Note 1 : The data memory contents become unstable when the power supply is turned on; therefore, the data memory should be initialized by an initialization routine.

Note 2: The general-purpuse registers are mapped in the RAM ; therefore, do not clear RAM at the current bank addresses.

# **1.5 General-purpose Register Banks**

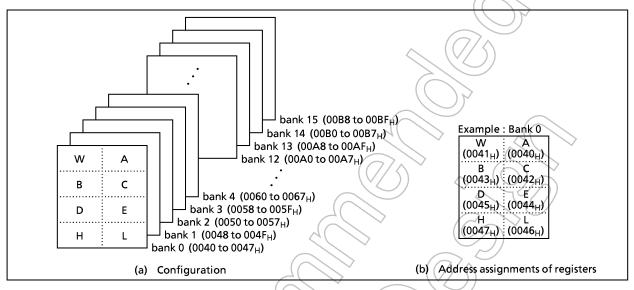

General-purpose registers are mapped into addresses  $0040_{H}$ - $00BF_{H}$  in the data memory as shown in Figure 1-4. There are 16 register banks, and each bank contains eight 8-bit registers W, A, B, C, D, E, H, and L. Figure 1-5 shows the general-purpose register bank configuration.

Figure 1-5. General-purpose Register Banks

In addition to access in 8-bit units, the registers can also be accessed in 16-bit units as the register pairs WA, BC, DE, and HL. Besides its function as a general-purpose register, the register also has the following functions:

#### (1) **A, WA**

The A register functions as an 8-bit accumulator and WA the register pair functions as a 16-bit accumulator (W is high byte and A is low byte). Registers other than A can also be used as accumulators for 8-bit operations.

| Examples : ( | D ADD | А, В | ; Adds B contents to A contents and stores the result into A.                       |

|--------------|-------|------|-------------------------------------------------------------------------------------|

| (a           | SUB   | WA,  | 1234H ; Subtracts 1234 <sub>H</sub> from WA contents and stores the result into WA. |

|              | SUB   | Ε, Α | ; Subtracts A contents from E contents, and stores the result into E.               |

(2) HL, DE

The HL and DE specify a memory address. The HL register pair functions as data pointer (HL) /index register (HL + d) /base register (HL + C), and the DE register pair function as a data pointer (DE). The HL also has an auto-post- increment and auto-pre-decrement functions. This function simplifies multiple digit data processing, software LIFO (last-in first-out) processing, etc.

| Example 1 : | 1 | LD | A, (HL)       | ; | Loads the memory contents at the address specified by HL into A.                                                                  |

|-------------|---|----|---------------|---|-----------------------------------------------------------------------------------------------------------------------------------|

| $\sim$      | 2 | LD | A, (HL + 52H) | ; | Loads the memory contents at the address specified by the value obtained by adding $52_{\rm H}$ to HL contents into A.            |

|             | 3 | LD | A, (HL + C)   | ; | Loads the memory contents at the address specified by the value obtained by adding the register C contents to HL contents into A. |

|             | 4 | LD | A, (HL+)      | ; | Loads the memory contents at the address specified by HL into A.<br>Then increments HL.                                           |

|             | 5 | LD | A, (– HL)     | ; | Decrements HL. Then loads the memory contents at the address specified by new HL into A.                                          |

The TLCS-870 Series can transfer data directly memory to memory, and operate directly between memory data and memory data. This facilitates the programming of block processing.

|         | LD  | B, m       | ; $m = n - 1$ (n : number of bytes to transfer) |

|---------|-----|------------|-------------------------------------------------|

|         | LD  | HL, DSTA   | ; Sets destination address to HL                |

|         | LD  | DE, SRCA   | ; Sets source address to DE                     |

| SLOOP : | LD  | (HL), (DE) | ; HL←DE(//)                                     |

|         | INC | HL         | ; HL←HL+1                                       |

|         | INC | DE         | ; DE ← DE + 1                                   |

|         | DEC | В          | ; B←B-1                                         |

|         | JRS | F, SLOOP   | ; if B≧0 then loop                              |

|         |     |            |                                                 |

## (3) **B, C, BC**

Registers B and C can be used as 8-bit buffers or counters, and the BC register pair can be used as a 16-bit buffer or counter. The C register functions as an offset register for register-offset index addressing (refer to example 1 ③ above) and as a divisor register for the division instruction [DIV gg, C].

```

Example 1 : Repeat processing

Sets n as the number of repetitions to B

LD

B, n

processing

SREPEAT :

(n + 1 times processing)

DEC

R

JRS

F, SREPEAT

Example 2 :

Unsigned integer division (16-bit ÷ 8-bit)

; Divides the WA contents by the C contents, places the

DIV

WA, C

quotient in A and the remainder in W.

```

The general-purpose register banks are selected by the 4-bit register bank selector (RBS). During reset, the RBS is initialized to "0". The bank selected by the RBS is called the current bank. Together with the flag, the RBS is assigned to address  $003F_{\rm H}$  in the SFR as the program status word (PSW). There are 3 instructions [LD RBS, n], [PUSH PSW], [POP PSW] to access the PSW. The PSW can be also operated by the memory access instruction.

Highly efficient programming and high-speed task switching are possible by using bank changeover to save registers during interrupt and to transfer parameters during subroutine processing.

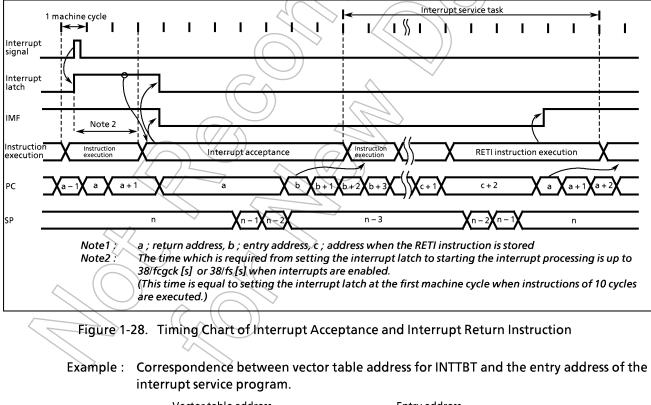

During interrupt, the PSW is automatically saved onto the stack. The bank used before the interrupt was accepted is restored automatically by executing an interrupt return instruction [RETI]/[RETN] ; therefore, there is no need for the RBS save/restore software processing.

The TLCS-870 Series supports a maximum of 15 interrupt sources. One bank is assigned to the main program, and one bank can be assigned to each source. Also, to increase the efficiency of data memory usage, assign the same bank to interrupt sources which are not nested.

Example: Saving /restoring registers during interrupt task using bank changeover.

| PINT1 : | LD      | RBS, n         | ; | RBS — n (Bank changeover)                  |

|---------|---------|----------------|---|--------------------------------------------|

|         | Interru | upt processing |   |                                            |

|         | RETI    |                | ; | Maskable interrupt return (Bank restoring) |

# 1.6 Program Status Word (PSW)

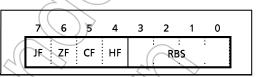

The program status word (PSW) consists of a register bank selector (RBS) and four flags, and the PSW is assigned to address  $003F_H$  in the SFR.

The RBS can be read and written using the memory access instruction (e. g. [LD A, (003FH)], [LD (003FH), A], however the flags can only be read. When writing to the PSW, the change specified by the instruction is made without writing data to the flags. For example, when the instruction [LD (003FH), 05H] is executed, "5" is written to the RBS and the JF is set to "1", but the other flags are not affected.

[PUSH PSW] and [POP PSW] are the PSW access instructions.

# 1.6.1 Register Bank Selector (RBS)

The register bank selector (RBS) is a 4-bit register used to select general-purpose register banks. For example, when RBS = 2, bank 2 is currently selected. During reset, the RBS is initialized to "0".

Figure 1-6. PSW (Flags, RBS) Configuration

## 1.6.2 Flags

The flags are configured with the upper 4 bits : a zero flag, a carry flag, a half carry flag and a jump status flag. The flags are set or cleared under conditions specified by the instruction. These flags except the half carry flag are used as jump condition "cc" for conditional jump instructions [JR cc, + 2 + d]/[JRS cc, + 2 + d]. After reset, the jump status flag is initialized to "1", other flags are not affected.

#### (1) Zero flag (ZF)

The ZF is set to "1" if the operation result or the transfer data is  $00_{\rm H}$  (for 8-bit operations and data transfers)/0000<sub>H</sub> (for 16-bit operations); otherwise the ZF is cleared to "0".

During the bit manipulation instructions [SET, CLR, and CPL], the ZF is set to "1" if the contents of the specified bit is "0"; otherwise the ZF is cleared to "0".

This flag is set to "1" when the upper 8 bits of the product are  $00_H$  during the multiplication instruction [MUL], and when  $00_H$  for the remainder during the division instruction [DIV]; otherwise it is cleared to "0".

(2) Carry flag (CF)

The CF is set to "1" when a carry out of the MSB (most significant bit) of the result occurred during addition or when a borrow into the MSB of the result occurred during subtraction; otherwise the CF is cleared to "0". During division, this flag is set to "1" when the divisor is  $00_H$  (divided by zero error), or when the quotient is  $100_H$  or higher (overflow error); otherwise it is cleared. The CF is also affected during the shift/rotate instructions [SHLC, SHRC, ROLC, and RORC]. The data shifted out from a register is set to the CF.

This flag is also a 1-bit register (a boolean accumulator) for the bit manipulation instructions. Set/clear/complement are possible with the CF manipulation instructions.

Example1 : Bit manipulation (The result of exclusive-OR between bit 5 content of address  $07_{\rm H}$  and bit 0 content of address  $9A_{\rm H}$  is written to bit 2 of address  $01_{\rm H}$ .)

LD CF, (0007H) . 5 ;  $(0001_H)_2 \leftarrow (0007_H)_5 \forall (009A_H)_0$ XOR CF, (009AH) . 0LD (0001H) . 2, CF

## (3) Half carry flag (HF)

The HF is set to "1" when a carry occurred between bits 3 and 4 of the operation result during an 8bit addition, or when a borrow occurred from bit 4 into bit 3 of the result during an 8-bit subtraction; otherwise the HF is cleared to "0". This flag is useful in the decimal adjustment for BCD operations (adjustments using the [DAA r], or [DAS r] instructions). Example : BCD operation

| (The A be | comes 47 <sub>H</sub> | l after executing th | ne | following program when $A = 19_H, B = 28_H$ )                    |

|-----------|-----------------------|----------------------|----|------------------------------------------------------------------|

|           | ADD                   | А, В                 | ;  | $A \leftarrow 41_{H}, HF \leftarrow 1, CF \leftarrow 0$          |

|           | ΠΔΔ                   | Δ                    |    | $\Delta \leftarrow 41_{11} + 06_{12} = 47_{12}$ (decimal-adjust) |

#### (4) Jump status flag (JF)

Zero or carry information is set to the JF after operation (e.g. INC, ADD, CMP, TEST).

The JF provides the jump condition for conditional jump instructions [JR T/F, +2+d], [JRS T/F, +2+d] (T or F is a condition code). Jump is performed if the JF is "1" for a true condition (T), or the JF is "0" for a false condition (F).

The JF is set to "1" after executing the load/exchange/swap/nibble rotate/jump instruction, so that [JRS T, \$ + 2 + d] and [JR T, \$ + 2 + d] can be regarded as an unconditional jump instruction.

Example : Jump status flag and conditional jump instruction

| INC | А          | (0/5)                                            |

|-----|------------|--------------------------------------------------|

| JRS | T, SLABLE1 | ; Jump when a carry is caused by the immediately |

| ÷   | (          | preceding operation instruction.                 |

| LD  | A, (HL)    |                                                  |

| JRS | T, SLABLE2 | ; JF is set to "1" by the immediately preceding  |

| ÷   |            | instruction, making it an unconditional jump     |

|     |            | instruction                                      |

Example : The accumulator and flags become as shown below after executing the following instructions when the WA register pair, the HL register pair, the data memory at address  $00C5_H$ , the carry flag and the half carry flag contents being "219AH", " $00C5_H$ ", " $D7_H$ ", "1" and "0", respectively.

| Ins  | truction | Acc. after<br>execution | Flag<br>JF |               | execution<br>CF HF |        | ĥ    | nstruction | Acc. after<br>execution | Flag<br>JF | after<br>ZF |   | ution<br>HF |

|------|----------|-------------------------|------------|---------------|--------------------|--------|------|------------|-------------------------|------------|-------------|---|-------------|

| ADDC | A, (HL)  | 72                      | 7          | 0             | 1 1                | 2      | TNC  | A          | 9B                      | 0          | 0           | 1 | 0           |

| SUBB | A, (HL)  | C2                      | 1          | 2             | 1 0                | 0      | ROLC | A          | 35                      | 1          | 0           | 1 | 0           |

| СМР  | A, (HL)  | 9A                      | 0          | 0             | 1 0                | $\leq$ | RORC | A          | CD                      | 0          | 0           | 0 | 0           |

| AND  | A, (HL)  | 92                      | 0          | o<            | + 0                |        | ADD  | WA, 0F508H | 16A2                    | 1          | 0           | 1 | 0           |

| LD   | А, (НЬ)  | D7                      | 1          | 0             | 1 0                |        | MUL  | W, A       | 13DA                    | 0          | 0           | 1 | 0           |

| ADD  | A, 66H   | 00                      | 1          | $\widehat{(}$ | 1 1                |        | SET  | A.5        | ВА                      | 1          | 1           | 1 | 0           |

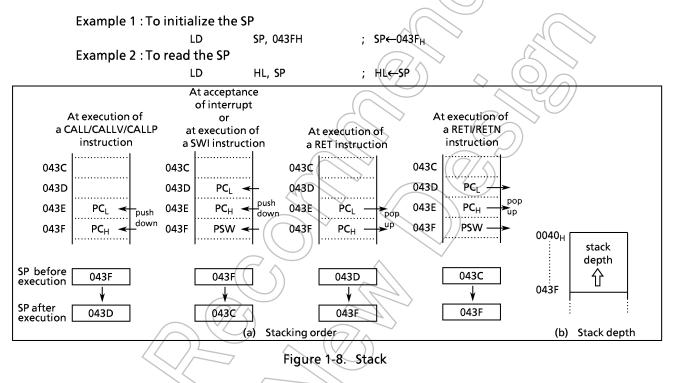

# 1.7 Stack and Stack Pointer

# 1.7.1 Stack

The stack provides the area in which the return address or status, etc. are saved before a jump is performed to the processing routine during the execution of a subroutine call instruction or the acceptance of an interrupt. On a subroutine call instruction [CALL a] / [CALLP n] / [CALLV n], the contents of the PC (the return address) is saved; on an interrupt acceptance, the contents of the PC and the PSW are saved (the PSW is pushed first, followed by PC<sub>H</sub> and PC<sub>L</sub>). Therefore, a subroutine call occupies two bytes on the stack; an interrupt occupies three bytes.

When returning from the processing routine, executing a subroutine return instruction [RET] restores the contents to the PC from the stack; executing an interrupt return instruction [RETI] / [RETN] restores the contents to the PC and the PSW (the PC<sub>L</sub> is popped first, followed by PC<sub>H</sub> and PSW).

The stack can be located anywhere within the data memory space except the register bank area, therefore the stack depth is limited only by the free data memory size.

## 1.7.2 Stack Pointer (SP)

The stack pointer (SP) is a 16-bit register containing the address of the next free locations on the stack.

The SP is post-decremented when a subroutine call or a push instruction is executed, or when an interrupt is accepted; and the SP is pre-incremented when a return or a pop instruction is executed. Figure 1-8 shows the stacking order.

MSB LSB 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 Stack Pointer (SP)

Figure 1-7. Stack Pointer

The SP is not initialized hardware-wise but requires initialization by an initialize routine (sets the highest stack address). [LD SP, mn], [LD SP, gg] and [LD gg, SP] are the SP access instructions (mn ; 16-bit immediate data, gg ; register pair).

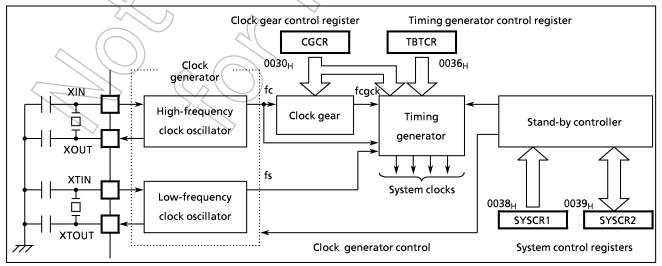

#### 1.8 System Clock Controller

The system clock controller consists of a clock generator, a timing generator, and a stand-by controller.

Figure 1-9. System Clock Controller

# 1.8.1 Clock Generator

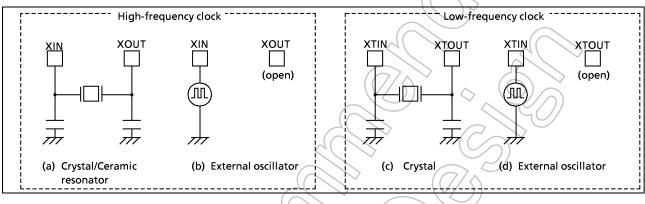

The clock generator generates the basic clock which provides the system clocks supplied to the CPU core and peripheral hardware. It contains two oscillation circuits: one for the high-frequency clock and one for the low-frequency clock. Power consumption can be reduced by switching of the system clock controller to low-power operation based on the low-frequency clock.

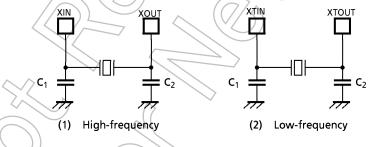

The high-frequency (fc) and low-frequency (fs) clocks can be easily obtained by connecting a resonator between the XIN/XOUT and XTIN/XTOUT pins, respectively. Clock input from an external oscillator is also possible. In this case, external clock is applied to the XIN/XTIN pin with the XOUT/XTOUT pin not connected. The 87CM53 is not provided an RC oscillation.

## Figure 1-10. Examples of Resonator Connection

Note: Accurate Adjustment of the Oscillation Frequency: Although no hardware to externally and directly monitor the basic clock pulse is not provided, the oscillation frequency can be adjusted by making the program to output fixed frequency pulses to the port while disabling all interrupts and the watchdog timer and monitoring this pulse. With a system requiring adjustment of the oscillation frequency, the adjusting program must be created beforehand.

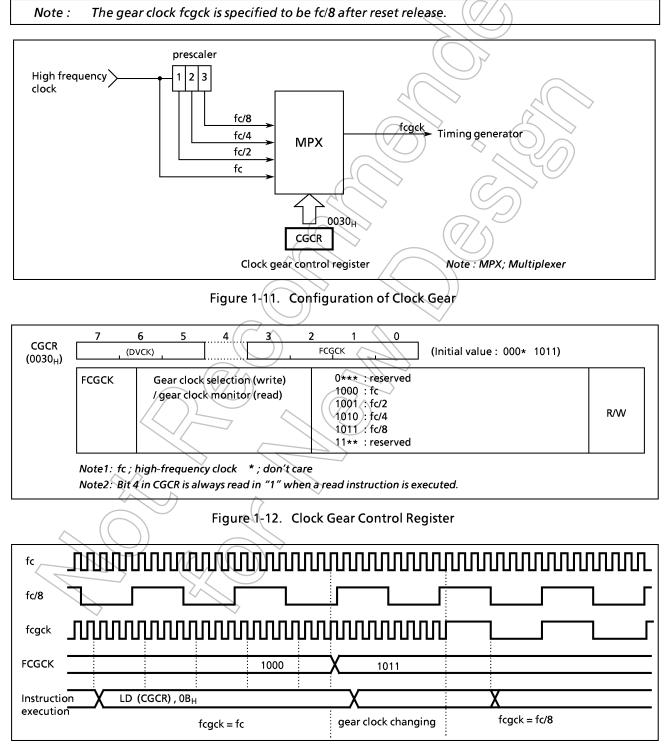

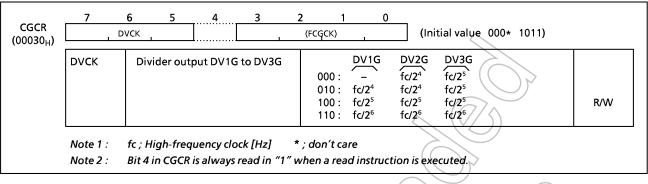

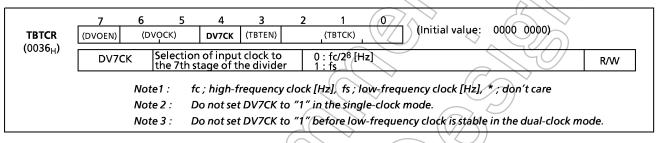

# 1.8.2 Clock Gear

The clock gear is a circuit to select a gear clock fcgck, that is the basis of the main system clock supplied to the timing generator, from high-frequency clock fc, or the divided clock fc/2, fc/4, or fc/8. Power consumption can be reduced by switching of the gear clock from fc to fc/2, fc/4, and fc/8 with the clock gear using.

The clock gear consists of a 3-stage prescaler with a multiplexer.

Figure 1-13. Example of Clock Exchangeable Timing by Clock Gear

# 1.8.3 Timing Generator

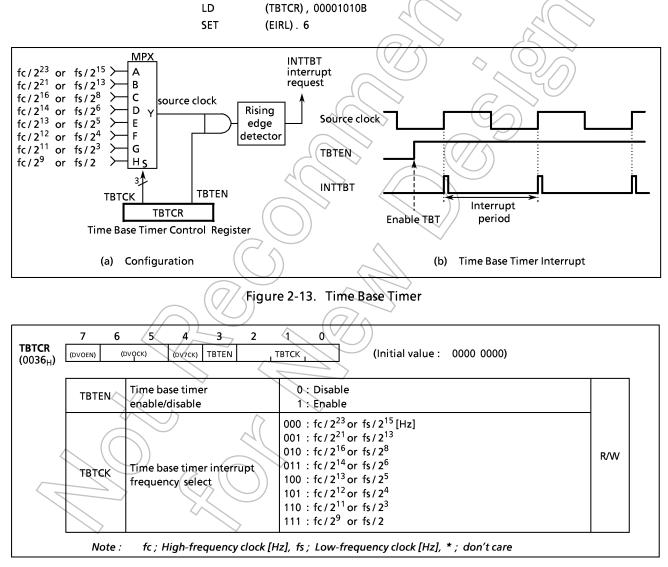

The timing generator generates the various system clocks supplied to the CPU core and peripheral hardware from the gear clock (fcgck) or the basic clock (fc or fs). The timing generator provides the following functions.

- ① Generation of main system clock (fm)

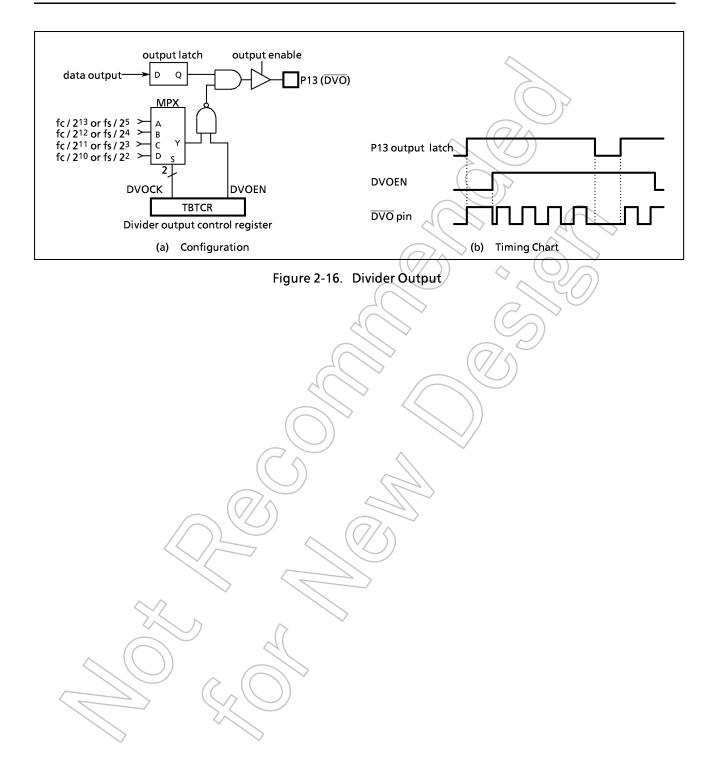

- ② Generation of divider output (DVO) pulses

- ③ Generation of source clocks for time base timer

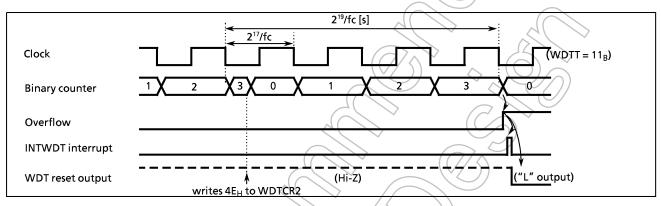

- ④ Generation of source clocks for watchdog timer

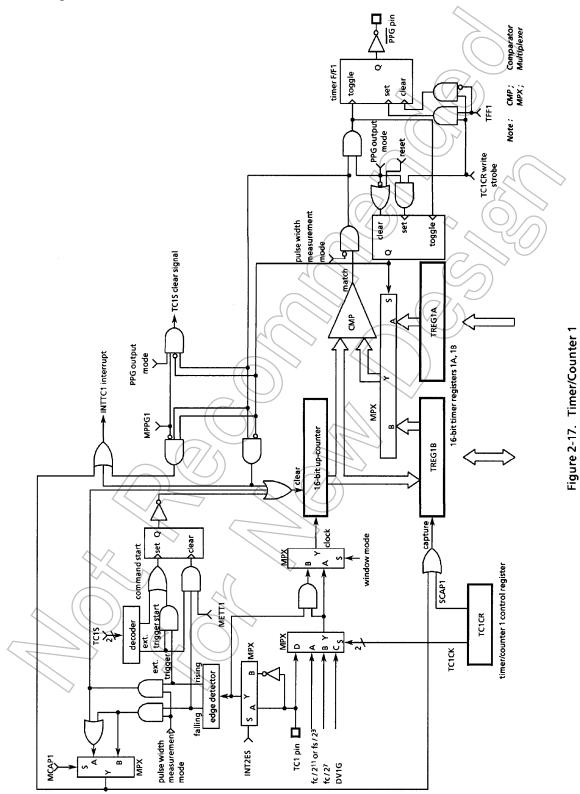

- ⑤ Generation of internal source clocks for timer / counters TC1-TC3, TC5

- **6** Generation of warm-up clocks for releasing STOP mode

- (1) Configuration of timing generator

The timing generator consists of a 2-stage prescaler, a 21-stage divider, a main system clock generator, and machine cycle counters.

The clock fc/4, that is output from the 2nd stage of the prescaler.

Even if the main system clock is changed by the clock gear, the output from the divider is not changed. The peripheral circuit using high-speed divider output (1st to 4th output) can not be used when the main system clock slows down. In this case, setting DVCK (bits 7, 6 and 5 in CGCR) can change high-speed divider output to low-speed divider output. The DVCK should be set according to the lowest speed of the clock gear and divider output used for the peripheral circuit prior to starting the peripheral circuits. Do not change the set value after setting.

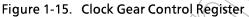

An input clock to the 7th stage of the divider depends on the operating mode, DV7CK(bit 4 in TBTCR), that is shown in Table 1-2. As reset and STOP mode started/canceled, The prescaler and the divider are cleared to "0".

| руск   | Gear clock frequency | Divider output capability |      |      |     |  |  |

|--------|----------------------|---------------------------|------|------|-----|--|--|

| DVCK   | deal clock irequency | DV1G                      | DV2G | DV3G | DV4 |  |  |

| (      | fcgck = fc           | Ð                         | ∕ E  | Е    | E   |  |  |

| 000    | fcgck = fc/2         | B                         | 6    | Е    | Е   |  |  |

| 000    | fcgck = fc/4         | $(D \land$                | D    | D    | E   |  |  |

|        | fcgck = fc/8         | (⊻∕Ď)                     | D    | D    | D   |  |  |

|        | fćgck = fc           | <u> </u>                  | Е    | Е    | Е   |  |  |

| 010    | fcgck = fc/2         | D                         | D    | Е    | E   |  |  |

| 010    | fcgck = fc/4         | D                         | D    | D    | E   |  |  |

| $\sim$ | fcgck = fc/8         | D                         | D    | D    | D   |  |  |

|        | fcgck = fc           | E                         | Е    | E    | E   |  |  |

| 人100   | fcgck = fc/2         | E                         | Е    | Е    | E   |  |  |

|        | fcgck = fc/4         | D                         | D    | D    | Е   |  |  |

|        | fcgck = fc/8         | D                         | D    | D    | D   |  |  |

|        | fcgck = fc           | E                         | E    | E    | E   |  |  |

| 1,10   | fcgck = fc/2         | E                         | Е    | Е    | Е   |  |  |

|        | fcgck = fc/4         | E                         | E    | E    | E   |  |  |

|        | fcgck = fc/8         | D                         | D    | D    | D   |  |  |

#### Table 1-1. Divider Output Capability

Note : D = disable, E = enable

| Table 1-2. | Input Clock to 7 | th Stage of the Divider |

|------------|------------------|-------------------------|

| Table L    | input ciden to / | thotage of the bitlact  |

|                                                             | Single-clock mode                                                                           |                                                                                                                          | Dual-clock mode                                                                                                  | $\land$                                                         |                                                               |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------|

|                                                             | NORMAL1, IDLE1 mode                                                                         | NORMAL2, IDLE2                                                                                                           | mode (SYSCK = 0)                                                                                                 | SLOW, SLEEP mode                                                |                                                               |

|                                                             | NORWALT, IDLET Mode                                                                         | DV7CK = 0                                                                                                                | DV7CK = 1                                                                                                        | (SYSCK = 1)                                                     |                                                               |

|                                                             | fc/2 <sup>8</sup>                                                                           | fc/2 <sup>8</sup>                                                                                                        | fs                                                                                                               | fs                                                              |                                                               |

|                                                             |                                                                                             |                                                                                                                          |                                                                                                                  |                                                                 |                                                               |

| No<br>No<br>No                                              |                                                                                             | LEEP mode, the<br>ed; output from<br>enable<br>DV1G TC5CK<br>DV1G SCK<br>(SIO)<br>-frequency clock<br>in the single-cloc | e input clock to<br>the 1st to 6th st<br>( 011 : DV1G<br>010 : DV3G<br>011 : DV2G<br>(fc/28) is input<br>k mode. | the 1st stage of<br>ages is also stopped<br>to the 7th stage of | <i>t</i> .                                                    |

|                                                             | can be selected either "fo<br>During SLOW or SLEEP m<br>clock to the 1st stage is st        | 2/28" or "fs" with<br>ode (SYSCK = 1)<br>opped ; output                                                                  | DV7CK.<br>, fs is automatica<br>from the 1st to                                                                  | ally input to the 7th                                           | stage. To input                                               |

| Gear clock fcgck >                                          | Main system clock                                                                           | elector                                                                                                                  | fs → Machine c                                                                                                   | ycle counters                                                   |                                                               |

| SYSCK ><br>DV7CK >                                          |                                                                                             |                                                                                                                          |                                                                                                                  |                                                                 |                                                               |

| High-frequency<br>clock fc ><br>Low-frequency<br>clock fs > |                                                                                             | │                                                                                                                        | Ô                                                                                                                | vider<br>14 15 16 17 18 19 20 21                                | • MPX<br>B0<br>B1                                             |

| DVCK >                                                      | 3<br>3<br>4<br>8<br>8<br>9<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |                                                                                                                          |                                                                                                                  |                                                                 | A0 Y0<br>A1 Y1<br>Stand-by<br>controller<br>Watchdog<br>Timer |

| Timer /<br>Counters                                         | DV1G                                                                                        |                                                                                                                          |                                                                                                                  |                                                                 | Time Base                                                     |

| [                                                           | <                                                                                           |                                                                                                                          |                                                                                                                  | Note : MPX; Mu                                                  | Divider<br>output<br>circuit                                  |

Figure 1-14. Configuration of Timing Generator

Figure 1-16. Timing Generator Control Register

#### (2) Machine Cycle

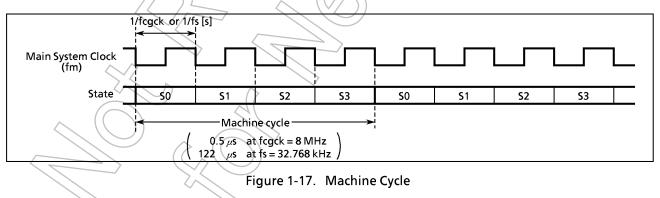

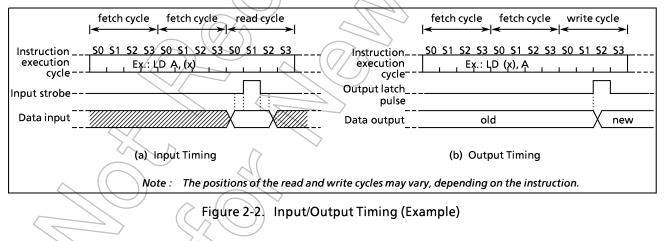

Instruction execution and peripheral hardware operation are synchronized with the main system clock. The minimum instruction execution unit is called an "machine cycle". There are a total of 10 different types of instructions for the TLCS-870 Series. ranging from 1-cycle instructions which require one machine cycle for execution to 10-cycle instructions which require 10 machine cycles for execution.

A machine cycle consists of 4 states (S0 - S3), and each state consists of one main system clock.

# 1.8.4 Stand-by Controller

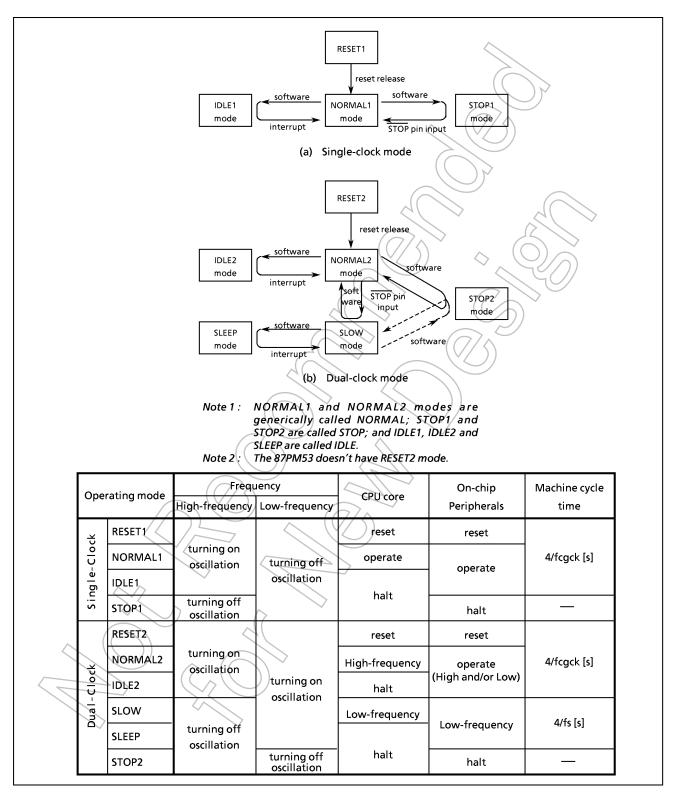

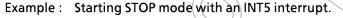

The stand-by controller starts and stops the oscillation circuits for the high-frequency and low-frequency clocks, and switches the main system clock. There are two operating modes: single-clock and dual-clock. These modes are controlled by the system control registers (SYSCR1, SYSCR2).

Figure 1-18 shows the operating mode transition diagram and Figure 1-19 shows the system control registers. Either the single-clock or the dual-clock mode can be selected by an option during reset.

# (1) Single-clock mode

Only the oscillation circuit for the high-frequency clock is used, and P21 (XTIN) and P22 (XTOUT) pins are used as input/output ports. In the single-clock mode, the machine cycle time is 4/fcgck [s].

1 NORMAL1 mode

In this mode, both the CPU core and on-chip peripherals operate using the high-frequency clock. In the case when the single-clock mode has been selected as an option, the 87CM53 is placed in this mode after reset.

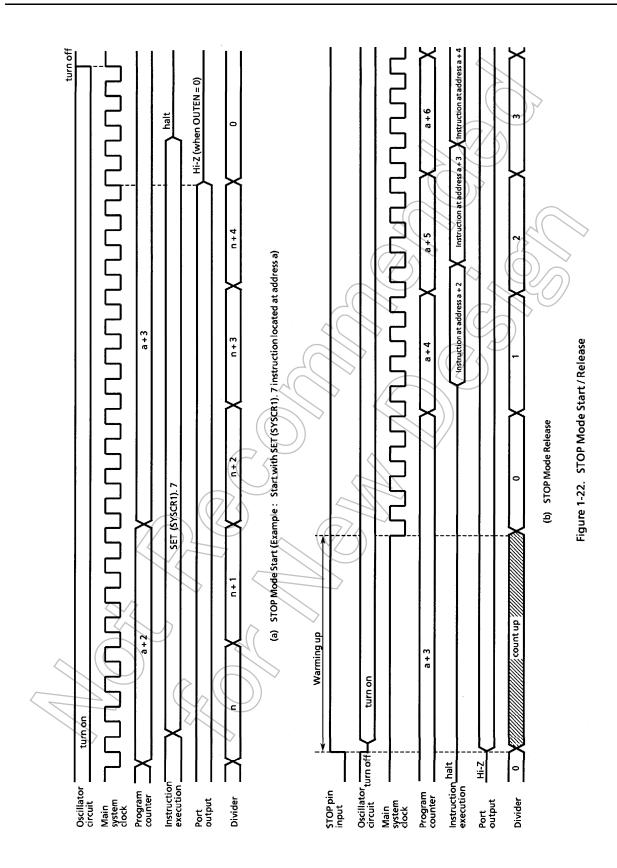

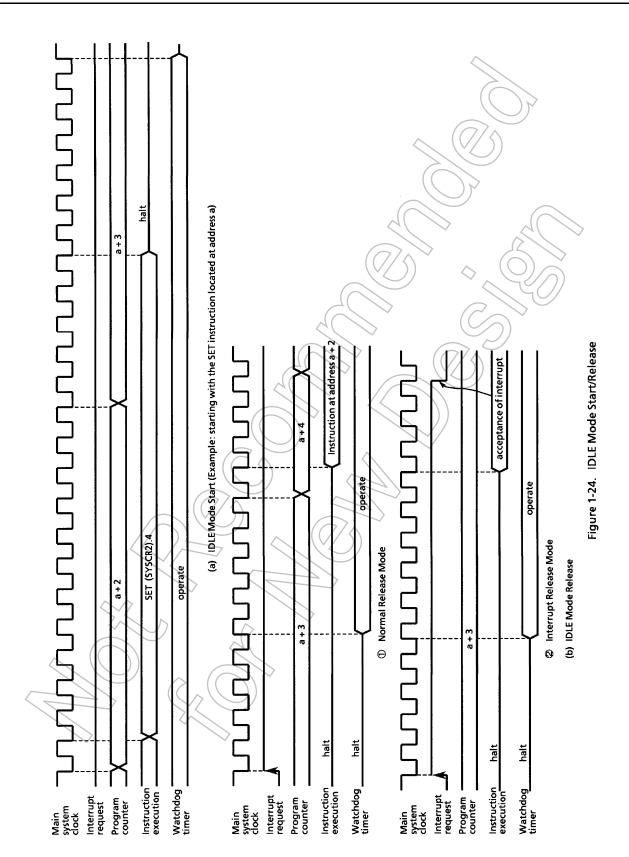

# ② IDLE1 mode

In this mode, the internal oscillation circuit remains active, and the CPU and the watchdog timer are halted; however, on-chip peripherals remain active (operate using the high-frequency clock). IDLE1 mode is started by setting IDLE bit in the system control register 2 (SYSCR2), and IDLE1 mode is released to NORMAL1 mode by an interrupt request from on-chip peripherals or external interrupt inputs. When IMF (interrupt master enable flag) is "1" (interrupt enable), the execution will resume upon acceptance of the interrupt, and the operation will return to normal after the interrupt service is completed. When IMF is "0" (interrupt disable), the execution will resume with the instruction which follows IDLE mode start instruction.

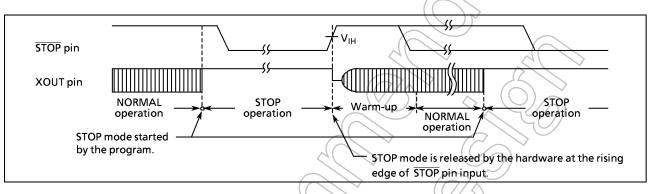

## ③ STOP1 mode

In this mode, the internal oscillation circuit is turned off, causing all system operations to be halted. The internal status immediately prior to the halt is held with the lowest power consumption during this mode. The output status of all output ports can be set to either output hold or high-impedance under software control.

STOP1 mode is started by setting STOP bit in the system control register 1 (SYSCR1), and STOP1 mode is released by an input (either level-sensitive or edge-sensitive can be programmably selected) to the STOP pin. After the warming-up period is completed, the execution resumes with the next instruction which follows the STOP mode start instruction.

#### (2) Dual-clock mode

Both high-frequency and low-frequency oscillation circuits are used in this mode. Pins P21 (XTIN) and P22 (XTOUT) cannot be used as input/output ports. The main system clock is obtained from the high-frequency clock in NORMAL2 and IDLE2 modes, and is obtained from the low-frequency clock in SLOW and SLEEP modes. The machine cycle time is 4/fcgck [s] (0.5  $\mu$ s at fcgck = 8 MHz) in NORMAL2 and IDLE2 modes, and 4/fs [s] (122  $\mu$ s at fs = 32.768 kHz) in SLOW and SLEEP modes.

Note : The 87PM53 is placed in the single-clock mode during reset. To use the dual-clock mode, the low-frequency oscillator should be turned on by executing [SET (SYSCR2).XTEN] instruction.

① NORMAL2 mode

In this mode, the CPU core operates using the high-frequency clock. On-chip peripherals operate using the high-frequency clock and/or low-frequency clock. In case that the dual-clock mode has been selected by an option, the 87CM53 is placed in this mode after reset.

② SLOW mode

This mode can be used to reduce power-consumption by turning off oscillation of the high-frequency clock. The CPU core and on-chip peripherals operate using the low-frequency clock.

Switching back and forth between NORMAL2 and SLOW modes is performed by the system control register 2.

③ IDLE2 mode

In this mode, the internal oscillation circuits remain active. The CPU and the watchdog timer are halted; however, on-chip peripherals remain active (operate using the high-frequency clock and/or the low-frequency clock). Starting and releasing of IDLE2 mode are the same as for IDLE1 mode, except that operation returns to NORMAL2 mode.

4 SLEEP mode

In this mode, the internal oscillation circuit of the low-frequency clock remains active. The CPU, the watchdog timer, and the internal oscillation circuit of the high- frequency clock are halted; however, on-chip peripherals remain active (operate using the low-frequency clock). Starting and releasing of SLEEP mode is the same as for IDLE1 mode, except that operation returns to SLOW mode.

⑤ STOP2 mode

As in STOP1 mode, all system operations are halted in this mode.

Figure 1-18. Operating Mode Transition Diagram

| System C                              | ontrol Reg                       | gister 1                                                                |                                                                                                                                   |        |

|---------------------------------------|----------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------|

| SYSCR1                                | 7 6                              | 5 4 3 2                                                                 | .1                                                                                                                                |        |

| (0038 <sub>H</sub> )                  | STOP REL                         | M RETM OUTEN WUT                                                        | (Initial value: 0000 00★★)                                                                                                        |        |

|                                       | STOP                             | STOP mode start                                                         | 0 : CPU core and peripherals remain active<br>1 : CPU core and peripherals are halted<br>(start STOP mode)                        |        |

|                                       | RELM                             | Release method<br>for STOP mode                                         | 0 : Edge-sensitive release<br>1 : Level-sensitive release                                                                         |        |

|                                       | RETM                             | Operating mode<br>after STOP mode                                       | 0 : Return to NORMAL mode<br>1 : Return to SLOW mode                                                                              |        |

|                                       | OUTEN                            | Port output control<br>during STOP mode                                 | 0 : High-impedance<br>1 : Remain unchanged                                                                                        | R/W    |

|                                       | WUT                              | Warming-up time at releasing STOP mode                                  | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                            |        |

|                                       | Note 1 :                         |                                                                         | transitting from NORMAL1 mode to STOP1 mode and from NOMA<br>set RETM to "1" when transitting from SLOW mode to STOP2 mod         |        |

|                                       | Note 2 :                         |                                                                         | vith RESET pin input, a return is made to NORMAL mode regardless                                                                  |        |

|                                       | Note 3 :                         | fc ; high-frequency clock [                                             | Hz] fs ; low-frequency clock [Hz] *; don't care                                                                                   |        |

|                                       | Note 4 :                         |                                                                         | in "1" data when a read instruction is executed.                                                                                  |        |

|                                       | Note 5 :                         | When the stop operation is set                                          | by OUTEN = "0", the internal input is fired to "0". Interrupts may                                                                | be     |

|                                       |                                  | set at the falling edge.                                                |                                                                                                                                   |        |

|                                       | Note 6 :                         | - / - / -                                                               | sed, the edge release can not function according to some condition                                                                | ns. It |

|                                       |                                  | is recommended to set the leve                                          | el release (RELM = "0").                                                                                                          |        |

| System                                | Control Re                       |                                                                         |                                                                                                                                   |        |

| <b>SYSCR2</b><br>(0039 <sub>H</sub> ) | 7 6<br>XEN XTE                   |                                                                         | (Initial value: 10/100 ****)                                                                                                      |        |

|                                       | XEN                              | High-frequency oscillator                                               | 0 : Turn off oscillation<br>1 : Turn on oscillation                                                                               |        |

|                                       | XTEN                             | Low-frequency oscillator<br>control                                     | 0 - Turn off oscillation<br>1 : Turn on oscillation                                                                               |        |

|                                       | SYSCK                            | Main system clock select<br>(write)/main system clock<br>monitor (read) | 0.: High-frequency clock<br>1 : Low-frequency clock                                                                               | R/W    |

| $\langle$                             | IDLE                             | IDLE mode start                                                         | 0 :CPU and watchdog timer remain active<br>1 :CPU and watchdog timer are stopped (start IDLE mode)                                |        |

|                                       | Note 1 :<br>Note 2 :<br>Note 3 : | Do not clear XEN to "0" when S<br>WDT; watchdog timer, * ; don          |                                                                                                                                   |        |

|                                       | Note 4 :<br>Note 5 :             | -                                                                       | read in as "1" when a read instruction is executed.<br>a selected for XTEN. Always specify when ordering ES (engineering          | 9      |

|                                       | Г                                | XTEN operating mode after r                                             | ecet                                                                                                                              |        |

|                                       | $\vdash$                         |                                                                         |                                                                                                                                   |        |

|                                       |                                  | 0 Single-clock mode (NC<br>1 Dual-clock mode (NC                        | RMAL1)<br>RMAL2)                                                                                                                  |        |

|                                       | Note 6 :                         |                                                                         | <i>Nasking Option (Operating Mode) is ES Order Sheet is described in Notice for Masking Option of TLCS-870 series" section 8.</i> |        |

# Figure 1-19. System Control Registers

# **1.8.5 Operating Mode Control**

#### (1) **STOP** mode (STOP1, STOP2)

STOP mode is controlled by the system control register 1 (SYSCR1) and the STOP pin input. The STOP pin is also used both as a port P20 and an INT5 (external interrupt input 5) pin. STOP mode is started by setting STOP (bit 7 in SYSCR1) to "1". During STOP mode, the following status is maintained.

- ① Oscillations are turned off, and all internal operations are halted.

- ② The data memory (except for DBR), registers (except for DBR) and port output latches are all held in the status in effect before STOP mode was entered. The port output can be select either output hold or high-impedance by setting OUTEN ( bit 4 in SYSCR1).

- ③ The divider of the timing generator is cleared to "0".

- The program counter holds the address of the instruction following the instruction which started the STOP mode.

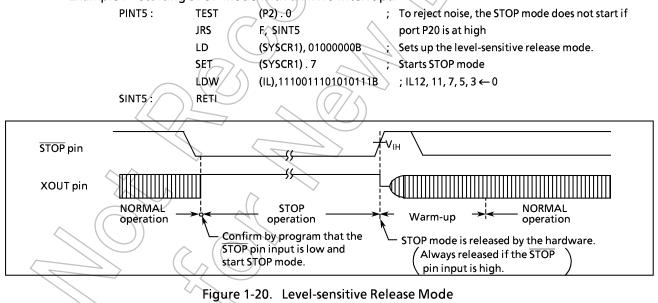

STOP mode includes a level-sensitive release mode and an edge-sensitive release mode, either of which can be selected with RELM (bit 6 in SYSCR1).

#### a. Level-sensitive release mode (RELM = 1)

In this mode, STOP mode is released by setting the STOP pin high. This mode is used for capacitor back-up when the main power supply is cut off and long term battery back-up.

When the STOP pin input is high, executing an instruction which starts the STOP mode will not place in STOP mode but instead will immediately start the release sequence (warm-up). Thus, to start STOP mode in the level-sensitive release mode, it is necessary for the program to first confirm that the STOP pin input is low. The following method can be used for confirmation:

• Using an external interrupt input INT5 (INT5 is a falling edge-sensitive input).

# Note 1: After warm-up start, even if STOP pin input is low again, STOP mode does not restart. Note 2: When changing to the level-sensitive release mode from the edge-sensitive release mode, the release mode is not switched until a rising edge of the STOP pin input is detected.

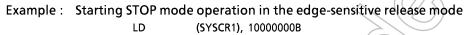

#### b. Edge-sensitive release mode (RELM = 0)

In this mode, STOP mode is released by a rising edge of the STOP pin input. This is used in applications where a relatively short program is executed repeatedly at periodic intervals. This periodic signal (for example, a clock from a low-power consumption oscillator) is input to the STOP pin.

In the edge-sensitive release mode, STOP mode is started even when the STOP pin input is high.

Figure 1-21. Edge-sensitive Release Mode

<u>STOP mode is released</u> by the following sequence:

- When returning to NORMAL2, both the high-frequency and low-frequency clock oscillators are turned on ; when returning to SLOW mode, only the low-frequency clock oscillator is turned on. When returning to NORMAL 1, only the high-frequency clock oscillator is turned on.

- ② A warming-up period is inserted to allow oscillation time to stabilize. During warm-up, all internal operations remain halted. Four (two in SLOW mode) different warming-up times can be selected with WUT (bits 2 and 3 in SYSCR1) as determined by the resonator characteristics.

- ③ When the warming-up time has elapsed, normal operation resumes with the instruction following the STOP mode start instruction (e.g. [SET (SYSCR1). 7]). The start is made after the divider of the timing generator is cleared to "0".

| $\geq$ |        | 17                    |                     |

|--------|--------|-----------------------|---------------------|

|        | WUT    | Warming-u             | p Time [ms]         |

|        | WUT    | Return to NORMAL mode | Return to SLOW mode |

|        | 00     | 24.576                | 750                 |

|        | ( 01 \ | 8.192                 | 250                 |

|        | 10     | 6.144                 | -                   |

|        | 11     | 2.048                 | _                   |

Table 1-3.

Warming-up Time (example at fcgck = 8 MHz, fs = 32.768 kHz)

Note: The warming-up time is obtained by dividing the basic clock by the divider: therefore, the warming-up time may include a certain amount of error if there is any fluctuation of the oscillation frequency when STOP mode is released. Thus, the warming-up time must be considered an approximate value.

STOP mode can also be released by setting the RESET pin low, which immediately performs the normal reset operation.

In this case, even if the setting is to return to the SLOW mode, it starts from the NORMAL mode. (If the initial XTEN of 87CM53 is set to "1" by mask option, they start from the NORMAL2 mode. In case of 87PM53, starts from NORMAL1 mode.)

3-53-25

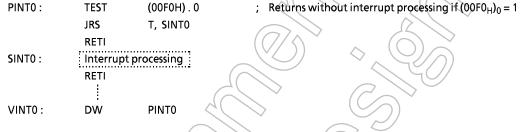

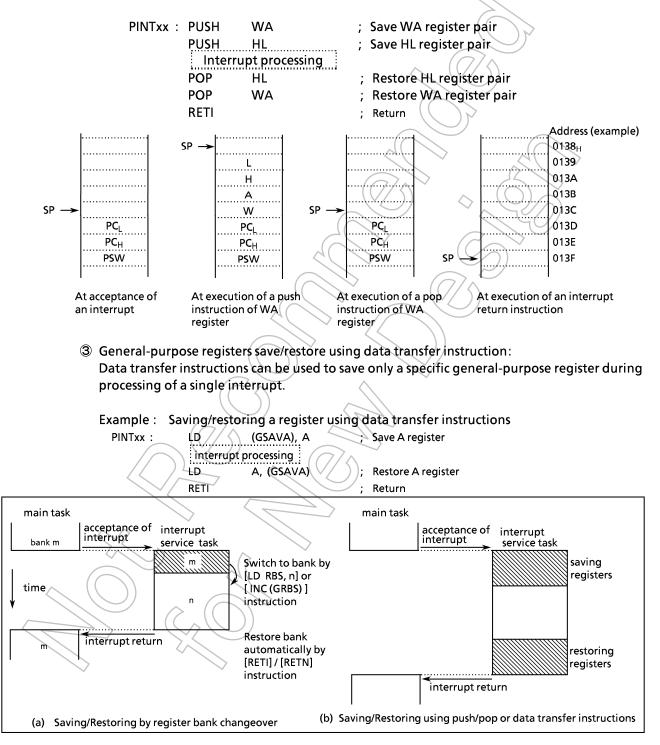

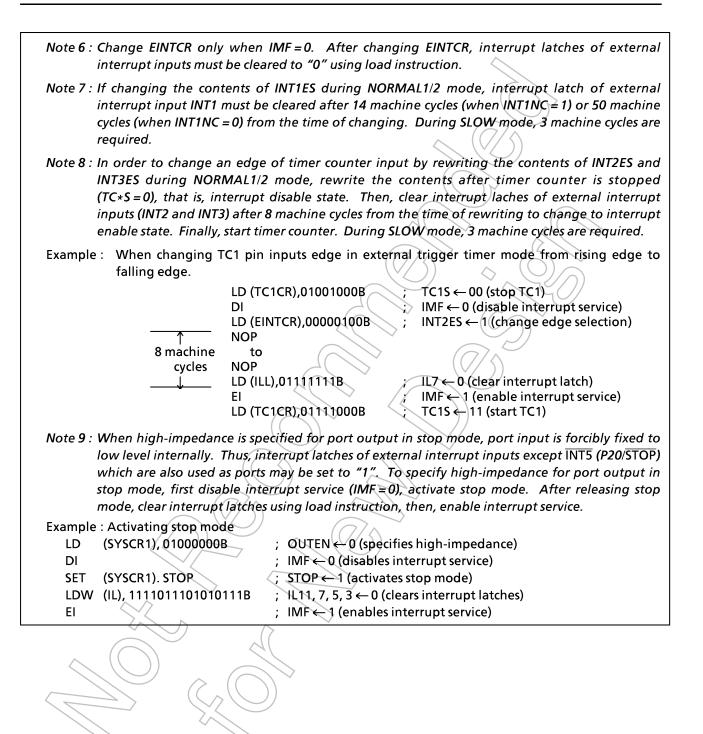

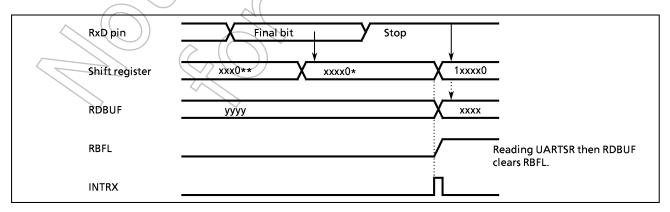

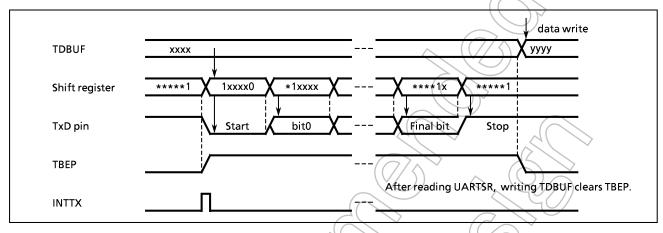

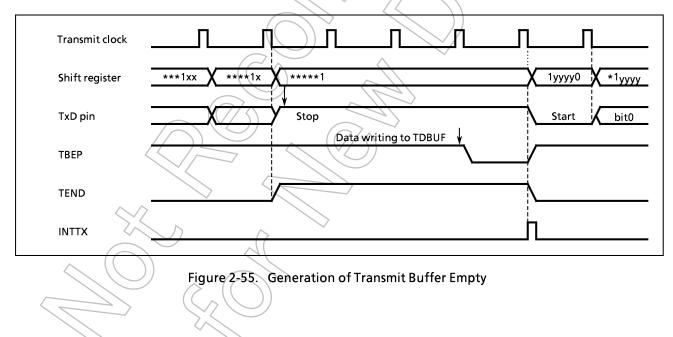

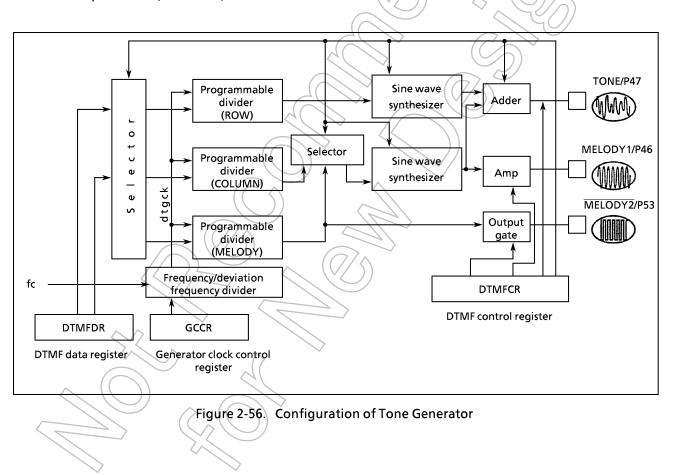

#### **TMP87CM53**