# TOSHIBA

Semiconductor Company

# Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions". Especially, take care below cautions.

## \*\*CAUTION\*\*

How to release the HALT mode

Usually, interrupts can release all halts status. However, the interrupts = (NMI, INTO), which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 3 clocks of X1) with IDLE1 or STOP mode (IDLE2 is not applicable to this case). (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

# **Document Change Notification**

The purpose of this notification is to inform customers about the launch of the Pb-free version of the device. The introduction of a Pb-free replacement affects the datasheet. Please understand that this notification is intended as a substitute for a revision of the datasheet.

Changes to the datasheet may include the following, though not all of them may apply to this particular device.

- 1. Part number

- Example: TMPxxxxxF  $\rightarrow$  TMPxxxxxFG

All references to the previous part number were left unchanged in body text. The new part number is indicated on the prelims pages (cover page and this notification).

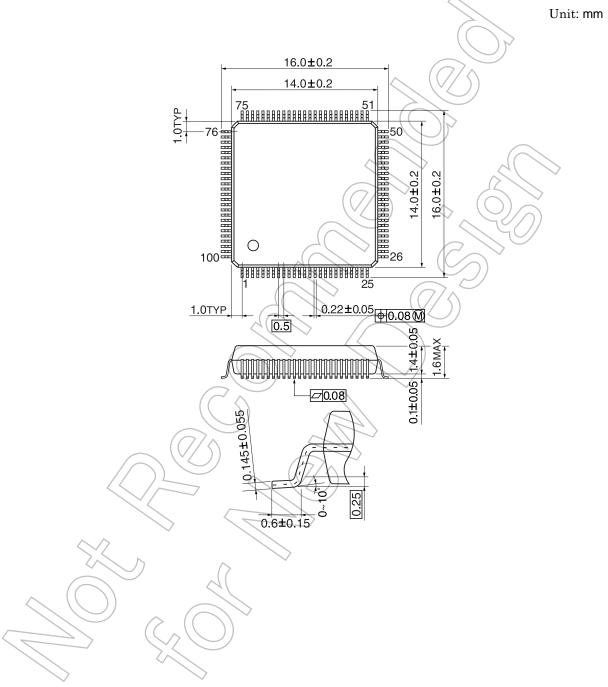

2. Package code and package dimensions

Example: LQFP100-P-1414-0.50C → LQFP100-P-1414-0.50F

All references to the previous package code and package dimensions were left unchanged in body text. The new ones are indicated on the prelims pages.

3. Addition of notes on lead solderability

Now that the device is Pb-free, notes on lead solderability have been added.

4. RESTRICTIONS ON PRODUCT USE

The previous (obsolete) provision might be left unchanged on page 1 of body text. A new replacement is included on the next page,

5. Publication date of the datasheet

The publication date at the lower right corner of the prelims pages applies to the new device.

#### 1. Part number

| Previous Part Number (in Body Text) | New Part Number |

|-------------------------------------|-----------------|

| TMP95CS66F                          | TMP95CS66FG     |

#### 2. Package code and dimensions

| Previous Package Code (in Body Text) | New Package Code     |

|--------------------------------------|----------------------|

| P-LQFP100-1414-0.50F                 | LQFP100-P-1414-0.50F |

\*: For the dimensions of the new package, see the attached Package Dimensions diagram.

#### 3. Addition of notes on lead solderability

The following solderability test is conducted on the new device.

Solderability of lead free products

| Test Parameter | Test Condition                                                                                                                                                                                                                                                                                                    | Note                                               |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Solderability  | Use of Sn-37Pb solder Bath<br>Solder bath temperature = 230°C, Dipping time = 5 seconds<br>The number of times = one, Use of R-type flux<br>Use of Sn-3.0Ag-0.5Cu solder bath<br>Solder bath temperature = 245°C, Dipping time = 5 seconds<br>The number of times = one, Use of R-type flux<br>(use of lead free) | Pass:<br>Solderability rate until forming<br>≥ 95% |

# 4. RESTRICTIONS ON PRODUCT USE

The following replaces the "RESTRICTIONS ON PRODUCT USE" on page 1 of body text.

#### RESTRICTIONS ON PRODUCT USE

• The information contained herein is subject to change without notice.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or tailure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

#### 5. Publication date of the datasheet

The publication date of this datasheet is printed at the lower right corner of this notification.

20070701-EN

(Annex)

# Package Dimensions

# LQFP100-P-1414-0.50F

#### CMOS 16-Bit Microcontrollers

# TMP95CS66F

#### 1. Outline and Features

TMP95CS66 is a high-speed 16-bit microcontroller designed for the control of various mid- to largescale equipment. This device is TNP95CS64 function cut. Otherwise, all the functions of the products are the same.

$TMP95CS66\ comes$  in a 100-pin flat package.

Listed below are the features.

- (1) High-speed 16-bit CPU (900/H CPU)

- Instruction mnemonics are upward-compatible with TLCS-90/900

- 16 Mbytes of linear address space

- General-purpose registers and register banks

- 16-bit multiplication and division instructions; bit transfer and arithmetic instructions

- Micro DMA: Four-channels (640 ns / 2 bytes at 25 MHz)

- (2) Minimum instruction execution time: 160 ns (at 25 MHz)

- (3) Built-in RAM: 2 Kbytes Built-in ROM: 64 Kbyte

- (4) External memory expansion

- Expandable up to 16 Mbytes (shared program/data area)

- External data bus width select pin (AM8/16)

- Can simultaneously support 8/16-bit width external data bus … Dynamic data bus sizing

- (5) 8-bit timers: 8 channels

- With event counter function: 2 channels

- (6) 16-bit timer/event counter: 2 channels

- (7) General-purpose serial interface: 1 channels

- (8) Watchdog timer

- (9) Chip select/wait controller: 4 blocks

The information contained herein is subject to change without notice.

<sup>000707</sup>EBP1

<sup>•</sup> For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

<sup>•</sup> The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

<sup>•</sup> The products described in this document are subject to the foreign exchange and foreign trade laws.

<sup>•</sup> The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- (10) Interrupts: 45 interrupts

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 21 internal interrupts:

- 10 external interrupts: Seven selectable priority levels

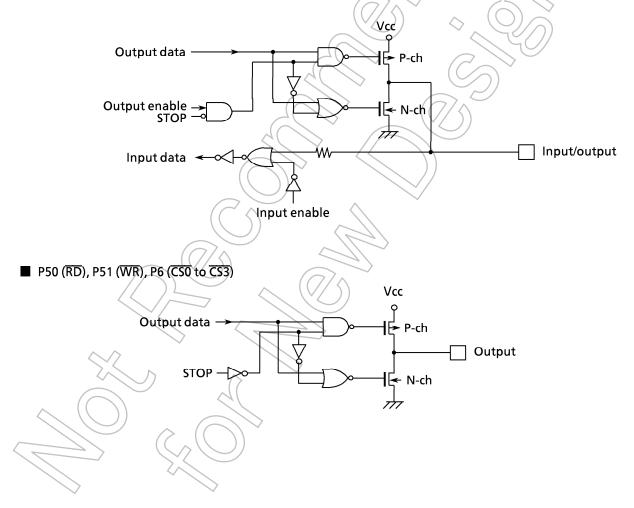

- (11) Input/output ports: 81 pins

- (12) Standby mode • Four HALT modes: RUN, IDLE2, IDLE1, STOP

- (13) Operating voltage •  $V_{CC} = 4.5 - 5.5 V$

- (14) Package: P-LQFP100-1414-0.50F

- (15) Differences between TMP95CS64F and TMP95CS66

|                      | TMP95CS64F                                                                                                                                   | TMP95CS66F                                                |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 10-bit A/D converter | 8 channels                                                                                                                                   |                                                           |

| 8-bit D/A converter  | 8 channels                                                                                                                                   | $\langle \rangle$                                         |

| Operating voltage    | $V_{CC} = 4.5 V \text{ to } 5.5 V (@f=8 \text{ to } 25 \text{ MHz})$<br>$V_{CC} = 2.7 V \text{ to } 3.3 V (@f=4 \text{ to } 10 \text{ MHz})$ | $V_{CC} = 4.5 V \text{ to } 5.5 V$<br>(@ f = 8 to 25 MHz) |

Figure 1 TMP95CS66 Block Diagram

### 2. Pin Assignment and Pin Functions

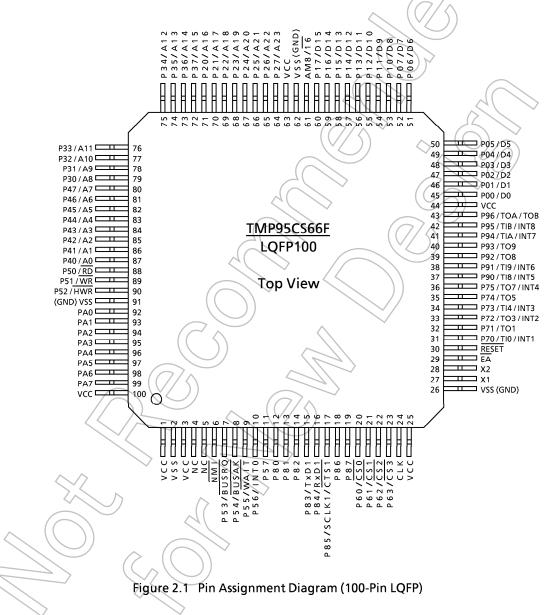

This section shows the TMP95CS66F pin assignment, and the names and an outline of the functions of the input/output pins.

#### 2.1 Pin Assignment Diagram

Figure 2.1 is a pin assignment diagram for TMP95CS66F.

### 2.2 Pin Names and Functions

Table 2.2 shows the names and functions of the input/output pins.

| Pin Name     | Number<br>of Pins | Input/Output | Function                                                                                                                                             |

|--------------|-------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00 to P07   | 8                 | Input/output | Port 0: I/O port. Input or output specifiable in units of bits                                                                                       |

| / D0 to D7   |                   | Input/output | Data: Data bus 0 to 7                                                                                                                                |

| P10 to P17   | 8                 | Input/output | Port 1: I/O port. Input or output specifiable in units of bits                                                                                       |

| / D8 to D15  |                   | Input/output | Data: Data bus 8 to 15                                                                                                                               |

| P20 to P27   | 8                 | Input/output | Port 2: I/O port. Input or output specifiable in units of bits                                                                                       |

| / A16 to A23 |                   | Output       | Address: Address bus 16 to 23                                                                                                                        |

| P30 to P37   | 8                 | Input/output | Port 3: I/O port. Input or output specifiable in units of bits                                                                                       |

| / A8 to A15  |                   | Output       | Address: Address bus 8 to 15                                                                                                                         |

| P40 to P47   | 8                 | Input/output | Port 4: I/O port. Input or output specifiable in units of bits                                                                                       |

| / A0 to A7   |                   | Output       | Address: Address bus 0 to 7                                                                                                                          |

| P50          | 1                 | Output       | Port 50: Output-only port                                                                                                                            |

| / RD         |                   | Output       | Read: Outputs strobe signal to read external memory (setting P5 $<$ P50 $> = 0$ and P5FC $<$ P50F $> = 1$ outputs strobe signal at all read timings) |

| P51          | 1                 | Output       | Port 51: Output-only port.                                                                                                                           |

| / WR         |                   | Output       | Write: Outputs strobe signal to write data on pins D0 to D7                                                                                          |

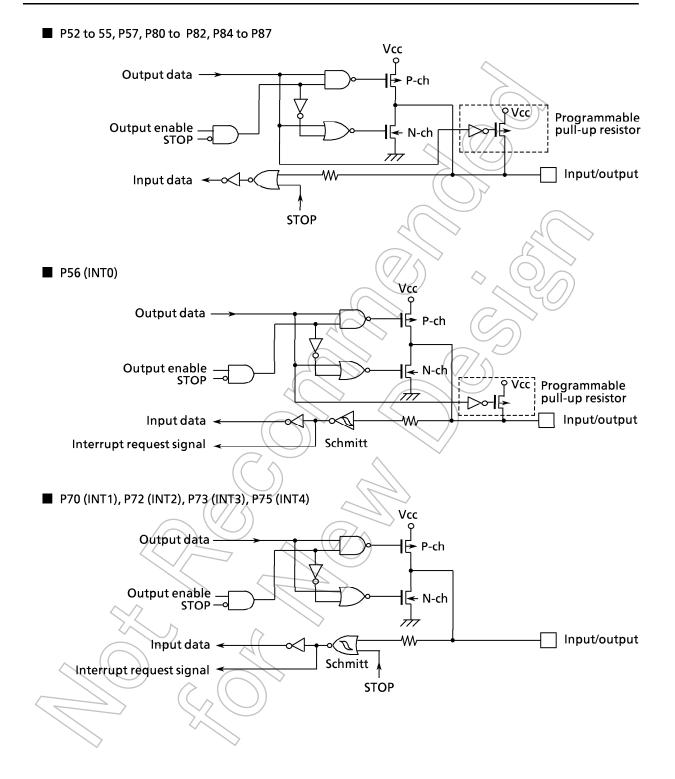

| P52          | 1                 | Input/output | Port 52: I/O port (with built-in pull-up resistor)                                                                                                   |

| / HWR        |                   | Output       | Upper write: Outputs strobe signal to write data on pins D8 to D15                                                                                   |

| P53          | 1                 | Input/output | Port 53: I/O port (with built-in pull-up resistor)                                                                                                   |

| / BUSRQ      |                   | Input        | Bus request; Input pin to request external bus release                                                                                               |

| P54          | 1//               | Input/output | Port \$4: I/O port (with built-in pull-up resistor)                                                                                                  |

| / BUSAK      |                   | Output       | Bus acknowledge: Output pin to acknowledge that CPU received                                                                                         |

|              |                   |              | BUSRQ and released external bus.                                                                                                                     |

| P55          | $\sim$            | Input/output | Port 55: I/O port (with built-in pull up resistor)                                                                                                   |

| / WAIT       |                   | / Input      | Wait: Bus wait request pin for CPU (Effective when 1 + N WAIT mode,                                                                                  |

| (            |                   |              | or 0 + NWAIT mode. Set using chip select/wait control register.)                                                                                     |

| P56          | ()                | Input/output | Port 56: I/O port (with built-in pull-up resistor)                                                                                                   |

| /INTO        |                   |              | Interrupt request pin 0: Interrupt request pin with programmable<br>level/rising edge.                                                               |

| P57          | 1                 | Input/output | Port 57: I/O port (with built-in pull-up resistor)                                                                                                   |

| Table 2.2 | Pin Names and Functions (1/3) |

|-----------|-------------------------------|

| 10010 2.2 | Third and a directions (1/3)  |

| Pin Name         | Number<br>of Pins | Input/Output | Function                                                              |

|------------------|-------------------|--------------|-----------------------------------------------------------------------|

| P60              | 1                 | Output       | Port 60: Output-only port                                             |

| / <u>CS0</u>     |                   | Output       | Chip select 0: Outputs 0 if address is within specified address range |

| P61              | 1                 | Output       | Port 61: Output-only port                                             |

| / <u>CS1</u>     |                   | Output       | Chip select 1: Outputs 0 if address is within specified address range |

| P62              | 1                 | Output       | Port 62: Output-only port                                             |

| / <u>CS2</u>     |                   | Output       | Chip select 2: Outputs 0 if address is within specified address range |

| P63              | 1                 | Output       | Port 63: Output-only port                                             |

| / <del>CS3</del> |                   | Output       | Chip select 3: Outputs 0 if address is within specified address range |

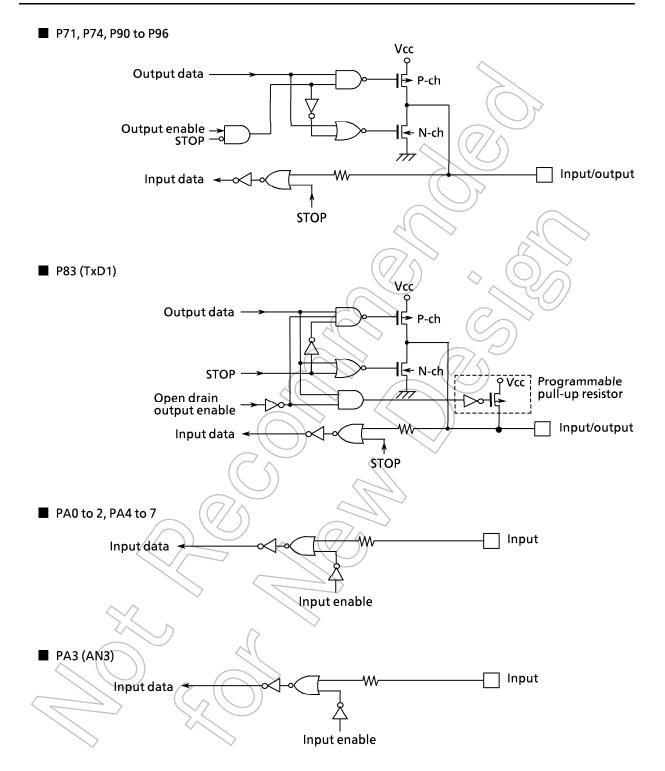

| P70              | 1                 | Input/output | Port 70: I/O port                                                     |

| / TIO            |                   | Input        | Timer input 0: Input pin for timer 0                                  |

| /INT1            |                   | Input        | Interrupt request pin 1: Rising-edge interrupt request pin 🤳          |

| P71              | 1                 | Input/output | Port 71: I/O port.                                                    |

| /TO1             |                   | Output       | Timer output 1. Output pin for timer 0 or 1                           |

| P72              | 1                 | Input/output | Port 72: I/O port                                                     |

| / TO3            |                   | Output       | Timer output 3: Output pin for timer 2 or 3                           |

| / INT2           |                   | Input        | Interrupt request pin 2. Rising-edge interrupt request pin 🤳          |

| P73              | 1                 | Input/output | Port 73: I/O port                                                     |

| / TI4            |                   | Input        | Timer input 4: Input pin for timer 4                                  |

| /INT3            |                   | Input        | Interrupt request pin 3: Rising-edge interrupt request pin 🥑          |

| P74              | 1                 | Input/output | Port 74: I/O port                                                     |

| / TO5            |                   | Output       | Timer output 5: Output pin for timer 4 or 5                           |

| P75              | 1                 | Input/output | Port 75: I/O port                                                     |

| / TO7            |                   | Output       | Timer output 7: Output pin for timer 6 or 7                           |

| /INT4            |                   | Input        | Interrupt request pin 4: Rising-edge interrupt request pin 🤳          |

| P80              | 1                 | Input/output | Port 80: I/O port (with built-in pull-up resistor)                    |

| P81              | 1                 | Input/output | Port 81: I/O port (with built-in pull-up resistor)                    |

| P82              |                   | Input/output | Port 82: 1/O port (with built-in pull-up resistor)                    |

| P83              | 1                 | Input/output | Port 83: I/O port (with built-in pull-up resistor)                    |

| /TxD1 ((         |                   | Output       | Serial transmission data 1                                            |

| P84              |                   | Input/output | Port 84: I/O port (with built-in pull-up resistor)                    |

| /RxD1            | 5                 | Input        | Serial receive data 1                                                 |

| P85              | 1                 | Input/output | Port 85: I/O port (with built-in pull-up resistor)                    |

| /SCLK1           |                   | Input/output | Serial clock input/output 1                                           |

| / CTS1           |                   | Input        | Serial data ready to send 1 (Clear-to-send)                           |

| P86              | 1                 | Input/output | Port 86: I/O port (with built-in pull-up resistor)                    |

| P87              | 1                 | Input/output | Port 87: I/O port (with built-in pull-up resistor)                    |

Table 2.2 Pin Names and Functions (2/3)

| Pin Name      | Number<br>of Pins | Input/Output | Function                                                          |

|---------------|-------------------|--------------|-------------------------------------------------------------------|

| P90           | 1                 | Input/output | Port 90: I/O port                                                 |

| / TI8         |                   | Input        | Timer input 8: Input pin for timer 8                              |

| / INT5        |                   | Input        | Interrupt request pin 5: Interrupt request pin with programmable  |

|               |                   |              | rising/falling edge                                               |

| P91           | 1                 | Input/output | Port 91: I/O port                                                 |

| / TI <b>9</b> |                   | Input        | Timer input 9: Input pin for timer 8                              |

| / INT6        |                   | Input        | Interrupt request pin 6: Rising edge interrupt request pin 🥑      |

| P92           | 1                 | Input/output | Port 92: I/O port                                                 |

| / TO8         |                   | Output       | Timer output 8: Output pin for timer 8                            |

| P93           | 1                 | Input/output | Port 93: I/O port                                                 |

| / TO9         |                   | Output       | Timer output 9: Output pin for timer 8                            |

| P94           | 1                 | Input/output | Port 94: I/O port                                                 |

| /TIA          |                   | Input        | Timer input A: Input pin for timer 9                              |

| / INT7        |                   | Input        | Interrupt request pin 7: Interrupt request pin with programmable  |

|               |                   |              | rising/fatting edge                                               |

| P95           | 1                 | Input/output | Port 95: I/O port                                                 |

| / TIB         |                   | Input        | Timer input B: Input pin for timer 9                              |

| /INT8         |                   | Input        | Interrupt request pin 8: Rising edge interrupt request pin 🥑      |

| P96           | 1                 | Input/output | Port 96: I/O port                                                 |

| /TOA          |                   | Output       | Timer output A: Output pin for timer 9                            |

| / TOB         |                   | Output       | Timer output B: Output pin for timer 9                            |

| PA0 to PA2    | 3                 | Input        | Port A0 to A2: Input-only port                                    |

| PA3           | 1//               | Input        | Port A3: Input-only port                                          |

| PA4 to PA7    | 4                 | Input        | Port A4 to A7: Input-only port                                    |

| NMI           | 1                 | Input        | Non-maskable interrupt request pin: Interrupt request pin with    |

|               |                   | $\sim$       | programmable falling edge or both falling and rising edge         |

|               |                   | 4            |                                                                   |

| CLK           |                   | Output       | Clock output: Outputs external clock divided by 4.                |

| $\sim$ ((     | $\square$         | $\langle$    | Pulled up during reset.                                           |

| EA            |                   | Input        | External access: Connect to VCC.                                  |

| AM8/16        | 1                 | Input        | Address mode: External data bus width select pin                  |

|               |                   |              | Connect this pin to VCC. Data bus width at external access can be |

| $\sim$        |                   | $\searrow$   | set by chip select/wait control register.                         |

| X1/X2         | 2                 | Input/output | Oscillator connecting pin                                         |

| VCC           | 5                 |              | Collector supply pin: Connect all VCC pins to power supply        |

| VSS           | 5                 |              | GND pin: Connect all VSS pins to GND (0 V)                        |

Table 2.2 Pin Names and Functions (3/3)

Note: Disconnect the pull-up resistors from pins other than  $\overline{\text{RESET}}$  pin by software.

#### 3. **Electrical Characteristics**

#### 3.1 **Absolute Maximum Ratings**

| Parameter                       | Symbol              | Rating             | Unit |

|---------------------------------|---------------------|--------------------|------|

| Power Supply Voltage            | V cc                | -0.5 to +6.5       | V    |

| Input Voltage                   | V IN                | - 0.5 to Vcc + 0.5 | V    |

| Output current (total)          | $\Sigma I_{OL}$     | +120               | mA   |

| Output current (total)          | Σloh                | - 120              | mA   |

| Power Dissipation (Ta = + 70°C) | Ρ <sub>D</sub>      | 600                | mW   |

| Soldering Temperature (10 s)    | T <sub>SOLDER</sub> | + 260              | °C   |

| Storage Temperature             | T <sub>STG</sub>    | -65 to +150        | °C   |

| Operating Temperature           | T <sub>OPR</sub>    | -20 to +70         | °C   |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

#### 3.2 **DC Electrical Characteristics**

#### (1) Vcc = +5 V ± 10%, Ta = -20 to +70°C (fc = 8 to 25 MHz)

| ···· ··· ···· ···· ·····                                                                           | _                       | (Typical v                                                                            | alues are for Ta =                             | = + 25°C, VCC = -                   | + 5 V.)                  |

|----------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------|--------------------------|

| Parameter                                                                                          | Symbol                  | Test Condition                                                                        | Min                                            | Max                                 | Unit                     |

| Input Low Voltage (D0 to 15)<br>Port 2 to A<br>(except P56, P70, P72, P73, P75)                    |                         |                                                                                       | -0.3<br>-0.3                                   | 0.8<br>0.3 Vcc                      | V<br>V                   |

| RESET, NMI, INTO to 4<br>EA, AM8/16<br>X1                                                          | V IL2<br>V IL3<br>V IL4 |                                                                                       | -0.3<br>-0.3<br>-0.3                           | 0.25 Vcc<br>0.3<br>0.2 Vcc          | V<br>  V<br>  V          |

| Input High Voltage (D0 to 15)<br>Port 2 to A<br>(except P56, P70, P72, P73, P75)                   | ViH<br>ViH1             |                                                                                       | 2.2<br>0.7 Vcc                                 | Vcc + 0.3<br>Vcc + 0.3              | V<br>V                   |

| RESET, NMI, INTO to 4<br>EA, AM8/16<br>X1                                                          | V IH2<br>V IH3<br>V IH4 |                                                                                       | 0.75 Vcc<br>Vcc – 0.3<br>0.8 Vcc               | Vcc + 0.3<br>Vcc + 0.3<br>Vcc + 0.3 | V<br>  V<br>  V          |

| Output Low Voltage                                                                                 | Vol                     | I <sub>OL</sub> = 1.6 mA                                                              |                                                | 0.45                                | V                        |

| Output High Voltage                                                                                | V он<br>V он1<br>V он2  | Ι <sub>ΟΗ</sub> = - 400 μΑ<br>Ι <sub>ΟΗ</sub> = - 100 μΑ<br>Ι <sub>ΟΗ</sub> = - 20 μΑ | 2.4<br>0.75 Vcc<br>0.9 Vcc                     |                                     | V<br>V<br>V              |

| Darlington Drive Current<br>(8 Output Pins max.)                                                   | IDAR                    | $V_{EXT} = 1.5 V$<br>R EXT = 1.1 k $\Omega$                                           | -1.0                                           | - 3.5                               | mA                       |

| Input Leakage Current<br>Output Leakage Current                                                    | 1-11<br>1-10            | 0.0≦Vin≦Vcc<br>0.2≦Vin≦Vcc – 0.2                                                      | 0.02 (Тур)<br>0.05 (Тур)                       | ±5<br>±10                           | μ <b>Α</b><br>μ <b>Α</b> |

| Operating Current (RUN)<br>IDLE2<br>IDLE1<br>STOP (Ta = - 20 to + 70°C)<br>STOP (Ta = 0 to + 50°C) |                         | fc = 25 MHz<br>$0.2 \le Vin \le Vcc - 0.2$<br>$0.2 \le Vin \le Vcc - 0.2$             | 40 (Typ)<br>30 (Typ)<br>3.5 (Typ)<br>0.5 (Typ) | 50<br>40<br>10<br>50<br>10          | mA<br>mA<br>μA<br>μA     |

| Power Down Voltage<br>(@STOP, RAM Back up)                                                         | V STOP                  | V <sub>IL2</sub> = 0.2 Vcc,<br>V <sub>IH2</sub> = 0.8 Vcc                             | 2.0                                            | 6.0                                 | V                        |

| Pull Up Registance                                                                                 | R <sub>RP</sub>         |                                                                                       | 45                                             | 160                                 | kΩ                       |

| Pin Capacitance                                                                                    | C IO                    | fc = 1 MHz                                                                            |                                                | 10                                  | pF                       |

| <u>Schmitt_Wi</u> dth<br>RESET, NMI, INT0 to 4                                                     | V <sub>TH</sub>         |                                                                                       | 0.4                                            | 1.0 (Typ)                           | V                        |

Note: IDAR guarantees up to eight pins from any output port.

#### 3.3 AC Electrical Characteristics

(1)  $Vcc = +5 V \pm 10\%$ , Ta = -20 to + 70°C

| 1)  | Vcc = +5 V ± 10%, Ta = -20 to +70°C                                                                                                                             |                  |           |                   | $\langle$     | (fc :                                   | = 8 MHz | to 25 l | MHz) |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|-------------------|---------------|-----------------------------------------|---------|---------|------|

| No. | o. Parameter                                                                                                                                                    |                  | Formula   |                   | 20 MHz        |                                         | 25 MHz  |         | Unit |

| NO. | Farameter                                                                                                                                                       | Symbol           | Min       | Max               | Min           | Max                                     | Min     | Max     | Unit |

| 1   | Oscillation cycle ( = x)                                                                                                                                        | tosc             | 40        | 125               | 50            |                                         | 40      |         | ns   |

| 2   | Clock pulse width                                                                                                                                               | t <sub>CLK</sub> | 2.0x – 40 | $\langle$         | 60            | ()                                      | 40      |         | ns   |

| 3   | A0 to 23 valid $\rightarrow$ Clock hold                                                                                                                         | t <sub>AK</sub>  | 0.5x – 20 |                   | 5             | Ľ                                       | 0       |         | ns   |

| 4   | Clock valid $\rightarrow$ A0 to 23 hold                                                                                                                         | t <sub>KA</sub>  | 1.5x – 60 |                   | 15            |                                         | 0       |         | ns   |

| 5   | A0 to 23 valid $\rightarrow \overline{RD}/\overline{WR}$ fall                                                                                                   | t <sub>AC</sub>  | 1.0x – 20 |                   | 30            |                                         | 20      |         | ns   |

| 6   | $\overline{\text{RD}}/\overline{\text{WR}}$ rise $\rightarrow$ A0 to 23 hold                                                                                    | t <sub>CA</sub>  | 0.5x – 20 | $\lambda$         | 5             |                                         |         |         | ns   |

| 7   | A0 to 23 valid $\rightarrow$ D0 to 15 input                                                                                                                     | t <sub>AD</sub>  |           | 3.5x-40           |               | 135                                     | $\sum$  | 100     | ns   |

| 8   | $\overline{\text{RD}}$ fall $\rightarrow$ D0 to 15 input                                                                                                        | t <sub>RD</sub>  | ((        | 2.5x-45           | ~             | 80                                      |         | 55      | ns   |

| 9   | RD low pulse width                                                                                                                                              | t <sub>RR</sub>  | 2.5x – 40 | $\bigcirc$        | 85            | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 60      |         | ns   |

| 10  | $\overline{\text{RD}}$ rise $\rightarrow$ D0 to 15 hold                                                                                                         | t <sub>HR</sub>  | 0         |                   | 0             | $\sim$                                  | 100     |         | ns   |

| 11  | WR low pulse width                                                                                                                                              | tww              | 2.5x - 40 | $\sim$            | 85            |                                         | 60      |         | ns   |

| 12  | D0 to 15 valid $\rightarrow \overline{WR}$ rise                                                                                                                 | t <sub>DW</sub>  | 2.0x – 40 |                   | 60            | $\mathcal{D}$                           | 40      |         | ns   |

| 13  | $\overline{WR}$ rise $\rightarrow$ D0 to 15 hold                                                                                                                | twp              | 0.5x – 10 | ()                | 7/5           |                                         | 10      |         | ns   |

| 14  | A0 to 23 valid $\rightarrow \overline{\text{WAIT}}$ input $\begin{pmatrix} 1 & \text{WAIT} \\ + n & \text{mode} \end{pmatrix}$                                  | taw              |           | 3.5x – 90         | $\mathcal{O}$ | 85                                      |         | 50      | ns   |

|     | A0 to 23 valid $\rightarrow \overline{\text{WAIT}}$ input $\begin{pmatrix} 0 + n \text{ WAIT} \\ \text{mode} \end{pmatrix}$                                     | taw              | >         | 1.5x – 40         |               | 35                                      |         | 20      | ns   |

| 15  | $\overline{\text{RD}}/\overline{\text{WR}}$ fall $\rightarrow \overline{\text{WAIT}}$ hold $\begin{pmatrix} 1 & \text{WAIT} \\ + n & \text{mode} \end{pmatrix}$ | tow              | 2.5x + 0  | $\langle \rangle$ | ) 125         |                                         | 100     |         | ns   |

|     | $\overline{\text{RD}}/\overline{\text{WR}} \text{ fall} \rightarrow \overline{\text{WAIT}} \text{ hold } (^{0+n}_{\text{mode}})$                                | tcw              | 0.5x + 0  |                   | 25            |                                         | 20      |         | ns   |

| 16  | $\overline{\mathrm{WR}}$ rise $\rightarrow$ PORT valid                                                                                                          | t <sub>CP</sub>  | $\land$   | 200               |               | 200                                     |         | 200     | ns   |

| 17  | CS Low pulse width (PSRAM mode)                                                                                                                                 | t <sub>CE</sub>  | 3.0x – 40 |                   | 110           |                                         | 80      |         | ns   |

| 18  | $\overline{\text{CS}}$ fall $\rightarrow$ D0 to 15 input (PSRAM mode)                                                                                           | t <sub>CEA</sub> |           | 3.0x – 60         |               | 90                                      |         | 60      | ns   |

| 19  | Address setup time<br>(PSRAM mode)                                                                                                                              | tpasc            | 0.5x-15   |                   | 10            |                                         | 5       |         | ns   |

| 20  | CS precharge time (PSRAM mode)                                                                                                                                  | tpp              | 1.0x – 10 |                   | 40            |                                         | 30      |         | ns   |

AC measuring conditions

• Output level: High 2.2 V/Low 0.8 V, CL = 50 pF

• Input level: High 2.4 V / Low 0.45 V (D0 to D15)

High 0.8 Vcc / Low 0.2 Vcc (except for D0 to D15)

# TOSHIBA

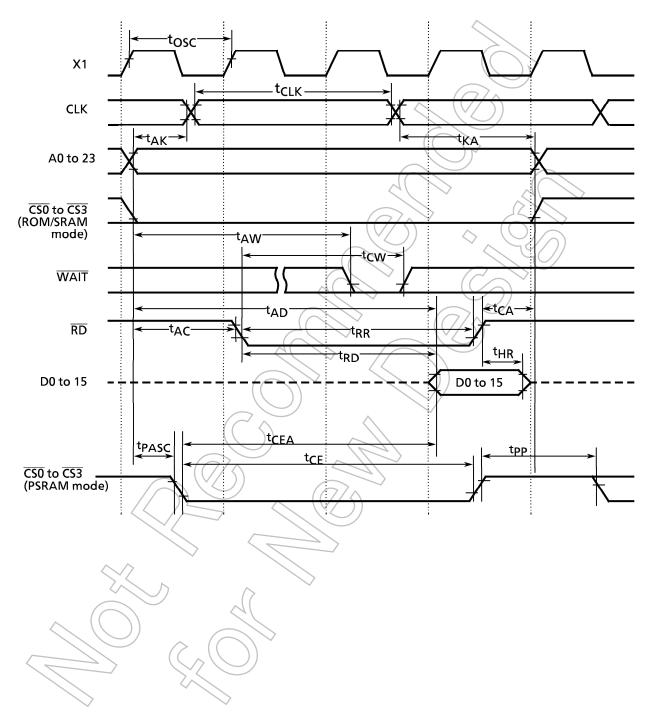

## (2) Read Cycle

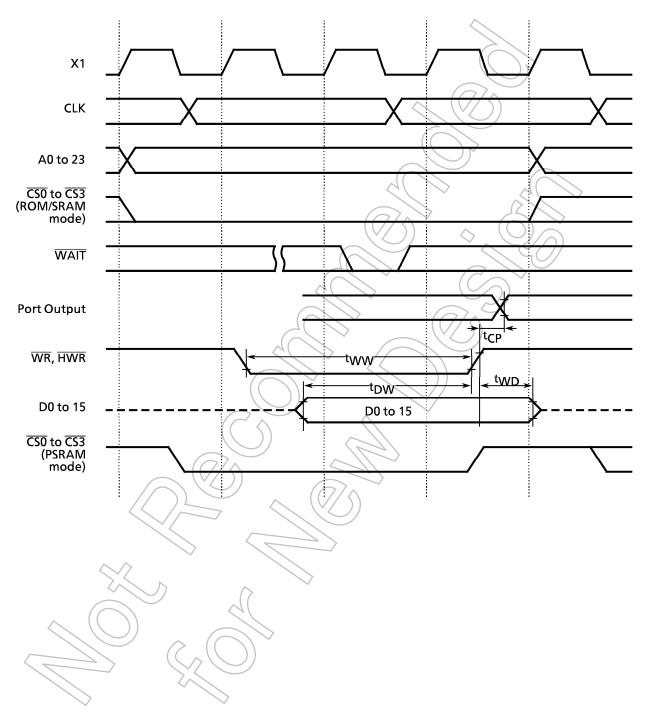

### (3) Write Cycle

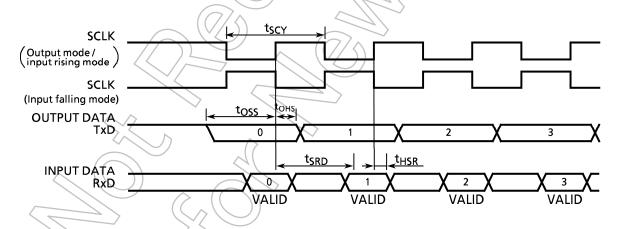

#### 3.4 Serial Channel Timing

- (1) I/O interface mode

- ① SCLK input mode

| Vcc = + 5 V ± 10%, Ta = - 20 to + 70°C (fc)=8 to 25 M |                  |                               |                             |      |        |        | VIHz)      |         |

|-------------------------------------------------------|------------------|-------------------------------|-----------------------------|------|--------|--------|------------|---------|

| Parameter                                             | Sumbol           | Form                          | 10                          | VIHz | 25 MHz |        | 11         |         |

| Parameter                                             | Symbol           | Min                           | Max 🔨                       | Min  | Max    | Min    | Max        | Unit    |

| SCLK cycle                                            | t <sub>SCY</sub> | 16x                           |                             | 1.6  | )      | 0.64   |            | $\mu$ S |

| Output Data $\rightarrow$ SCLK rise/fall*             | t <sub>OSS</sub> | t <sub>SCY</sub> /2 – 5x – 50 | (                           | 250  |        | 70     |            | ns      |

| SCLK rise/fall* $\rightarrow$ Output Data hold        | t <sub>OHS</sub> | 5x – 100                      |                             | 400  | 2      | 100    | )          | ns      |

| SCLK rise/fall*→input data hold                       | t <sub>HSR</sub> | 0                             |                             | P    |        | 0      | $\bigcirc$ | ns      |

| SCLK rise/fall* $\rightarrow$ valid data input        | t <sub>SRD</sub> |                               | t <sub>SCY</sub> – 5x – 100 |      | 1000   | $\sim$ | 340        | ns      |

\*) SCLK rise/fall: In SCLK rising edge mode, SCLK rising edge timing, in SCLK falling edge mode, SCLK falling edge timing

#### ② SCLK output mode

|                                                 |                  | Vcc =                       | + 5 V ± 10%, Ta             | = - 20 | to + 70' | ° <b>C (</b> fc = | 8 to 25 l | MHz) |

|-------------------------------------------------|------------------|-----------------------------|-----------------------------|--------|----------|-------------------|-----------|------|

| Parameter                                       | For              |                             | ula                         | 10 MHz |          | 25 MHz            |           | Unit |

| Faranteter                                      | Symbol           | Min                         | Max                         | Min    | Max      | Min               | Max       | Unit |

| SCLK cycle (programmable)                       | t <sub>SCY</sub> | 16x                         | 8192x                       | 1.6    | 819.2    | 0.64              | 327.6     | μs   |

| Output Data $\rightarrow$ SCLK rising edge      | t <sub>OSS</sub> | t <sub>SCY</sub> – 2x – 150 |                             | 1250   |          | 410               |           | ns   |

| SCLK rising edge $\rightarrow$ Output Data hold | tohs             | 2x - 80                     |                             | 120    |          | 0                 |           | ns   |

| SCLK rising edge $\rightarrow$ Input Data hold  | t <sub>HSR</sub> | )) o                        |                             | 0      |          | 0                 |           | ns   |

| SCLK rising edge $\rightarrow$ valid data input | t <sub>SRD</sub> |                             | t <sub>SCY</sub> – 2x – 150 |        | 1250     |                   | 410       | ns   |

|                                                 |                  | ~                           |                             |        |          |                   |           |      |

(2) UART Mode (SCLK1 External Input)

$Vcc = +5 V \pm 10\%$ , Ta =  $-20 to + 70^{\circ}C$  (fc = 8 to 25 MHz)

| Beremeter                   | Sumahal           | Form    | ula | 10 Г | ИНz | 25 P | ٧Hz | linit |

|-----------------------------|-------------------|---------|-----|------|-----|------|-----|-------|

| Parameter                   | Symbol            | Min     | Max | Min  | Max | Min  | Max | Unit  |

| SCLK cycle                  | t <sub>SCY</sub>  | 4x + 20 |     | 420  |     | 180  |     | ns    |

| Low-level SCLK pulse width  | t <sub>SCYL</sub> | 2x + 5  |     | 205  |     | 85   |     | ns    |

| High-level SCLK pulse width | t <sub>SCYH</sub> | 2x + 5  |     | 205  |     | 85   |     | ns    |

ns

#### Event Counter (External Input Clocks: TI0, TI4, TI8, TI9, TIA, TIB) 3.5

|                                             |                   | Calcu    | lator | 10 N | ЛНz | 25 N | 25 MHz |      |  |

|---------------------------------------------|-------------------|----------|-------|------|-----|------|--------|------|--|

| Parameter                                   | Symbol            | Min      | Max   | Min  | Max | Min  | Max    | Unit |  |

| External input clock cycle                  | t <sub>VCK</sub>  | 8x + 100 |       | 900  |     | 420  |        | ns   |  |

| External low-level input clock pulse width  | t <sub>VCKL</sub> | 4x + 40  |       | 440  | (77 | 200  |        | ns   |  |

| External high-level input clock pulse width | t <sub>VCKH</sub> | 4x + 40  |       | 440  |     | 200  |        | ns   |  |

#### $Vcc = +5 V \pm 10\%$ , Ta = 20 to + 70°C (fc = 8 to 25 MHz)

#### Interrupt Operation 3.6

INT5 to INT8 high-level pulse width

|                                       |                    |          | Vcc                    | = + 5 V ± 10 | 0%, Ta = −2 | 20 to +70°C | (fc = 8 to 2! | 5 MHz) |

|---------------------------------------|--------------------|----------|------------------------|--------------|-------------|-------------|---------------|--------|

| Parameter                             | Symbol             | Calcu    | lator                  | 101          | ЛНz         | 25 N        | (Hz           | Unit   |

| Parameter                             | Symbol             | Min      | Max                    | Mìn          | Max         | (Min        | Max           | Unit   |

| NMI, INT0 to 4 low-level pulse width  | t <sub>INTAL</sub> | 4x       | , ·                    | 400          | 7           | 160         | $\gamma$      | ns     |

| MMI, INT0 to 4 high-level pulse width | t <sub>INTAH</sub> | 4x       | $\left  \right\rangle$ | 400          | 7           | 160         | /             | ns     |

| INT5 to INT8 low-level pulse width    | t <sub>INTBL</sub> | 8x + 100 | $\langle \rangle$      | 900          |             | 420         |               | ns     |

900

8x + 100

t<sub>INTBH</sub>

420

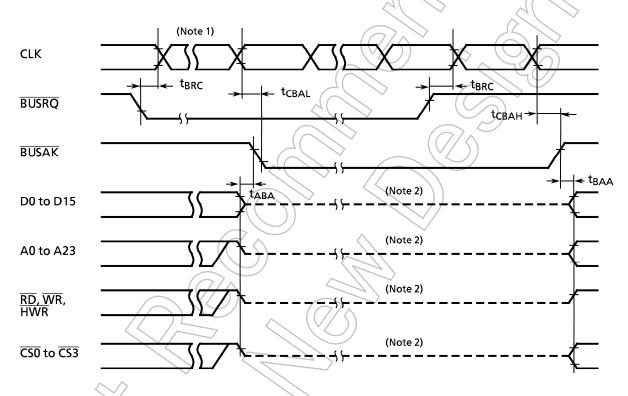

### 3.7 Bus Request/Bus Acknowledge Timing

|                                                      |                   | Vcc = | = +5V±10%, | Ta = <sub>7</sub> 2 | 20 to + 7 | ′0°C (fc = | = 8 to 25 | 5 MHz) |

|------------------------------------------------------|-------------------|-------|------------|---------------------|-----------|------------|-----------|--------|

| Parameter                                            | Symbol            | Ca    | alculator  | 10 MHz 25 MHz       |           | ЛНz        | Unit      |        |

| Falaneter                                            | Symbol            | Min   | Max        | Min                 | Max       | Min        | Max       | Unit   |

| BUSRQ setup time for CLK                             | t <sub>BRC</sub>  | 120   |            | 120                 |           | 120        |           | ns     |

| CLK→BUSAK fall                                       | t <sub>CBAL</sub> |       | 2.0x + 120 | (7/                 | 320       |            | 200       | ns     |

| $CLK \rightarrow \overline{BUSAK}$ rise              | t <sub>CBAH</sub> |       | 0.5x + 40  |                     | 90        |            | 60        | ns     |

| Time from output buffer off until BUSAK falling edge | t <sub>ABA</sub>  | 0     | 80         | 0                   | 80        | 0          | 80        | ns     |

| Time from BUSAK rising edge until output buffer on   | t <sub>BAA</sub>  | 0     | 80         | 0                   | 80        | 0          | 80        | ns     |

- Note 1: When BUSRQ goes to low level to request bus release, if the current bus cycle is yet complete due to a wait, the bus is not released until the wait completes.

- Note 2: The dotted line indicates only that the output buffer is off, not that the signal is at middle level. Immediately after bus release, the signal level prior to the bus release is held dynamically by the external load capacitance. Therefore, designs should allow for the fact that when using an external resistor or similar to fix the signal level while the bus is released, after bus release a delay occurs before the signal goes to its fixed level (due to the CR time constant). The internal programmable pullup resistor continues to function in accordance with the internal signal level.

#### 4. List of Special Function Registers (SFR)

The special function registers (SFR), which control the input/output ports and peripheral components, are allocated 160 bytes within the 000000H to 00009FH address range. The registers built into cannot be accessed from outside.

- (1) Input/output port

- (2) Input/output port control

- (3) Timer control

- (4) Serial channel control

- (5) Interrupt control

- (6) Watchdog timer control

- (7) Chip select/wait controller

- (8) D/A converter control

- (9) A/D converter control

#### <u>Table structure</u>

| Symbol | Name | Address | 7 6           | 1 0                                   | $\left( \right)$                     |

|--------|------|---------|---------------|---------------------------------------|--------------------------------------|

|        |      | <       |               |                                       | → bit Symbol                         |

|        | *    |         |               |                                       | → Read / Write                       |

|        |      |         | $\mathcal{D}$ |                                       | $\rightarrow$ Initial value at reset |

|        |      |         |               |                                       | → Remarks                            |

|        |      |         | 1 · · · (     | · · · · · · · · · · · · · · · · · · · | 1                                    |

(Supplement for symbols used in Table)

- 1 Read / Write /

- R/W: Both readable and writable

- R: Readable

- W: Writable

- \*R/W: Read-modify-write (RMW) instructions are prohibited for controlling ON/OFF of the pullup resistors.

- 2 RMW prohibited

- Cannot be read, modified, and written. (Cannot use the following instructions: EX, ADD, ADC, SUB, SBC, INC, DEC, AND, OR, XOR, STCF, RES, SET, CHG, TEST, RLC, RRC, RL, RR, SLA, SRA, SLL, SRL, RLD, RRD)

|             | Address       | Register Name | Address    | Register Name       | Address     | Register Name | Address        | Register Name |

|-------------|---------------|---------------|------------|---------------------|-------------|---------------|----------------|---------------|

| - F         | 000000H       | P0            | 30H        | TREG8L              | 60H         | (Reserved)    | 90H            | BOCS          |

|             | 1H            | P1            | 1H         | TREG8H              | 1H          | (Reserved)    | 14             | B1CS          |

|             | 2H            | POCR          | 2H         | TREG9L              | 2H          | (Reserved)    | 2H             | B2CS          |

|             | 3H            | (Reserved)    | 3H         | TREG9H              | 3H          | (Reserved)    | 3H             | B3CS          |

|             | 4H            | P1CR          | 4H         | CAP1L               | 4H          | (Reserved)    | 77_4H          | MSAR0         |

|             | 5H            | P1FC          | 5H         | CAP1H               | 5H          | (Reserved)    | ) )5н          | MAMR0         |

|             | 6H            | P2            | 6H         | CAP2L               |             | (Reserved)    | 6н             | MSAR1         |

|             | 7H            | P3            | 7H         | CAP2H               |             | (Reserved)    | 7н             | MAMR1         |

|             | 8H            | P2CR          | 8H         | T8MOD               | 8H          | (Reserved)    | 🖌 8н           | MSAR2         |

|             | 9Н            | P2FC          | 9Н         | T8FFCR              | 9Н          | (Reserved)    | 9н             | MAMR2         |

|             | AH            | P3CR          | АН         | T89CR               |             | SDMACR0       | АН             | MSAR3         |

|             | вн            | P3FC          | вн         | T16RUN              |             | SDMACR1       | ВН             | MAMR3         |

|             | СН            | P4            | СН         | )                   |             | SDMACR2       |                | BEXCS         |

|             | DH            |               | DH         |                     |             | SDMACR3       |                | (Reserved)    |

|             |               | P4CR          | EH         | > (Reserved)        | БН          | WDMOD         |                | (Reserved)    |

|             |               | P4FC          | FH         | )                   |             | WDCR          |                | (Reserved)    |

| F           |               | P5CR          |            | TREGAL              |             | INTEOAD       | $\sim$         |               |

|             |               | P5FC          |            | TREGAH              | _           | INTE12        | ( )            | $\sim$        |

|             | 2H            |               |            |                     |             | INTE34        | $\leq \rangle$ |               |

|             | 3H            |               |            | TREGBH              |             | INTE56        |                |               |

|             |               | (Reserved)    |            | CAP3L               | $\sim$      | INTE78        | $\land$        |               |

|             |               | P6FC          |            | САРЗН               | $\sim$      | INTET01       | ))             |               |

|             |               | P7CR          |            | CAP4L               |             | INTET23       |                |               |

|             |               | P7FC          |            | CAP4H               |             | INTET45       |                |               |

|             | 8H            |               |            | T9MOD               |             | INTET67       |                |               |

|             | 9H            |               |            | T9FFCR              |             | INTET89       |                |               |

|             |               | P8CR          |            | (Reserved)          |             | INTETAB       |                |               |

|             |               | P8FC          |            | (Reserved)          |             | NTETOV        |                |               |

|             |               | P9CR          |            | (Reserved)          |             | INTESO        |                |               |

|             |               | P9FC          |            | (Reserved)          |             | INTES1        |                |               |

|             |               | PA            |            | (Reserved)          |             | INTES2        |                |               |

|             |               | (Reserved)    | $\sqrt{2}$ | (Reserved)          |             | INTETC01      |                |               |

| Ŀ           |               | T8RUN         |            | SC1BUE              | $// \wedge$ | INTETC23      |                |               |

|             |               | TRDC          |            | SC1CR               |             |               |                |               |

|             |               | TREGO         | -          | SC1MOD              | 2H          |               |                |               |

|             |               | TREGI         |            | BR1CR               | 211<br>3H   |               |                |               |

|             |               | T01MOD        |            | (Reserved)          | 4H          |               |                |               |

|             | ~             | T02FFCR       |            | (Reserved)          | 5H          |               |                |               |

|             |               | TREG2         |            | (Reserved)          | 6H          |               |                |               |

|             |               | TREG3         |            | (Reserved)          | 7H          |               |                |               |

|             |               | T23MOD        |            | ODE                 | 8H          | ll            |                |               |

| 2           | $\wedge$ $()$ | TREG4         |            | IMC                 | оп<br>9Н    | A (Reserved)  |                |               |

|             |               | TREG5         |            | DMA0V               | эн<br>АН    |               |                |               |

| _           |               |               |            |                     |             |               |                |               |

| $\langle +$ |               | T45MOD        | /          | DMA1V               | BH          |               |                |               |

|             |               | T46FFCR       |            | DMA2V               | СН          |               |                |               |

|             |               | TREG6         |            | DMA3V<br>(Beconved) |             |               |                |               |

|             |               | TREG7         |            | (Reserved)          | EH          |               |                |               |

| L           | FH            | T67MOD        | FH         | (Reserved)          | FH          | 1             |                |               |

| Table 5 | List of TMP95CS64/265 | <b>Special Function</b> | <b>Register Addresses</b> |

|---------|-----------------------|-------------------------|---------------------------|

|         |                       |                         |                           |

## (1) Input/Output Ports

|          | Name                                                 | Address | 7                         | 6                               | 5                                                                                                            | 4                                                                                                                                                   | 3                                                                                                                                                                       | <2                                                                                                                       | 1                                                                                                  | 0                                                                              |

|----------|------------------------------------------------------|---------|---------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|          |                                                      |         | P07                       | P06                             | P05                                                                                                          | P04                                                                                                                                                 | P03                                                                                                                                                                     | P02                                                                                                                      | P01                                                                                                | P00                                                                            |

|          | Port 0                                               |         |                           |                                 |                                                                                                              | R                                                                                                                                                   | /W                                                                                                                                                                      |                                                                                                                          |                                                                                                    |                                                                                |

| P0       | Register                                             | 00H     |                           |                                 | Input mo                                                                                                     | de (output la                                                                                                                                       | tch register u                                                                                                                                                          | indefined)                                                                                                               | 75                                                                                                 |                                                                                |

|          |                                                      |         |                           |                                 |                                                                                                              |                                                                                                                                                     | th D7 to D0                                                                                                                                                             |                                                                                                                          | /                                                                                                  |                                                                                |

|          |                                                      |         | P17                       | P16                             | P15                                                                                                          | P14                                                                                                                                                 | R13 (                                                                                                                                                                   | P12                                                                                                                      | P11                                                                                                | P10                                                                            |

|          | Port 1                                               |         |                           |                                 |                                                                                                              | R                                                                                                                                                   | w 📝                                                                                                                                                                     |                                                                                                                          |                                                                                                    |                                                                                |

| P1       | Register                                             | 01H     |                           |                                 | Input mod                                                                                                    | de (output lat                                                                                                                                      | ch register cl                                                                                                                                                          | eared to 0)                                                                                                              |                                                                                                    |                                                                                |

|          |                                                      |         |                           |                                 | •                                                                                                            |                                                                                                                                                     | h D15 to D8                                                                                                                                                             | )2                                                                                                                       |                                                                                                    |                                                                                |

|          |                                                      |         | P27                       | P26                             | P25                                                                                                          | P24                                                                                                                                                 | P23                                                                                                                                                                     | P22                                                                                                                      | P21                                                                                                | P20                                                                            |

|          | Port 2                                               |         |                           |                                 |                                                                                                              | R.                                                                                                                                                  | M                                                                                                                                                                       |                                                                                                                          |                                                                                                    |                                                                                |

| P2       | Register                                             | 06H     |                           |                                 | Input mod                                                                                                    | de (output lat                                                                                                                                      | ch register cl                                                                                                                                                          | eared to 0)                                                                                                              | 21                                                                                                 | $\bigtriangledown$                                                             |

|          |                                                      |         |                           |                                 | •                                                                                                            | shared with                                                                                                                                         | 1 D23 to D16                                                                                                                                                            |                                                                                                                          | $\overline{\langle }$                                                                              |                                                                                |

|          |                                                      |         | P37                       | P36                             | P35                                                                                                          | : P34                                                                                                                                               | E P33                                                                                                                                                                   | P32 ( (                                                                                                                  | P31                                                                                                | P30                                                                            |

|          | Port 3                                               |         |                           |                                 | •                                                                                                            | R                                                                                                                                                   | NV                                                                                                                                                                      | $\mathcal{O}^{\mathcal{O}}$                                                                                              | ~///)                                                                                              |                                                                                |