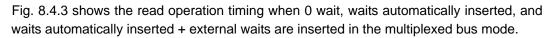

# **TOSHIBA**

Rev1.1

2008-3-28

# 32-Bit RISC Microprocessor TX19 Family TMP19A63F10XBG

#### Overview and features

TMP19A63 is equipped with the TX19A processor core that forms a high-performance 32-bit RISC processor series. The core was developed based on the MIPS32ISA that contains a 32-bit instruction set and the MIPS16eISA that contains an instruction set of high code efficiency. TOSHIBA uniquely integrated these two and the MIPS16e-TX <sup>TM</sup>ASE (Application Specific Extension), which includes an extended instruction set of high code efficiency.

TMP19A63 is a 32-bit RISC microprocessor with a TX19A processor core and various peripheral functions integrated into one package. It can operate at low voltage with low power consumption.

Features of TMP19A63 are as follows:

#### (1) TX19A processor core

- 1) Improved code efficiency and operating performance have been realized through the use of two ISA (Instruction Set Architecture) modes 16- and 32-bit ISA modes.

- The 16-bit ISA mode instructions are compatible with the MIPS16<sup>TM</sup>ASE instructions of superior code efficiency at the object level.

- The 32-bit ISA mode instructions are compatible with the TX39 instructions of superior operating performance at the object level.

#### **RESTRICTIONS ON PRODUCT USE**

Handbook" etc.

20070701-EN GENERAL

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its

use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third

parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS

compatibility. Please use these products in this document in compliance with all applicable laws and regulations that

regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring

as a result of noncompliance with applicable laws and regulations.

- 2) Both high performance and low power dissipation have been achieved.

- High performance

- Almost all instructions can be executed with one clock.

- High performance is possible via a three-operand operation instruction.

- 5-stage pipeline

- Built-in high-speed memory

- DSP function: A 32-bit multiplication and accumulation operation can be executed with one clock.

- •Low power consumption

- Optimized design using a low power consumption library

- Standby function that stops the operation of the processor core

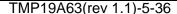

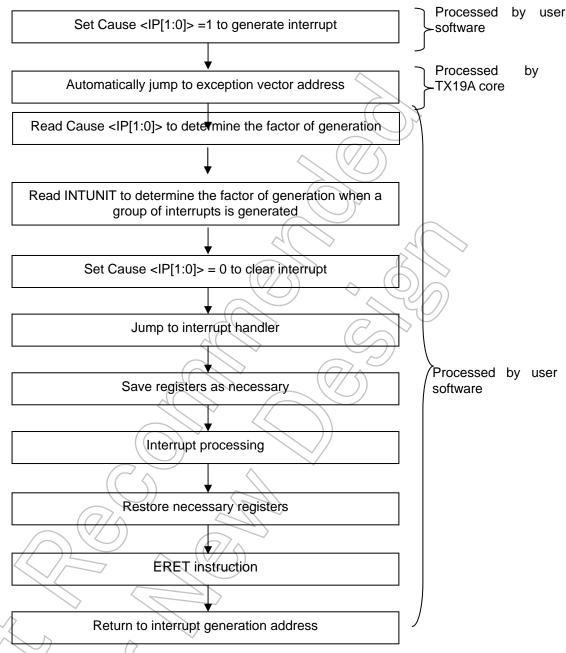

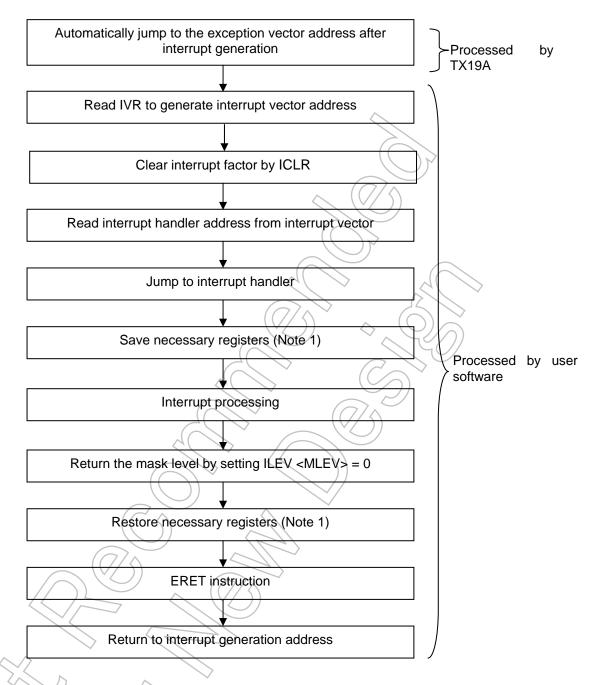

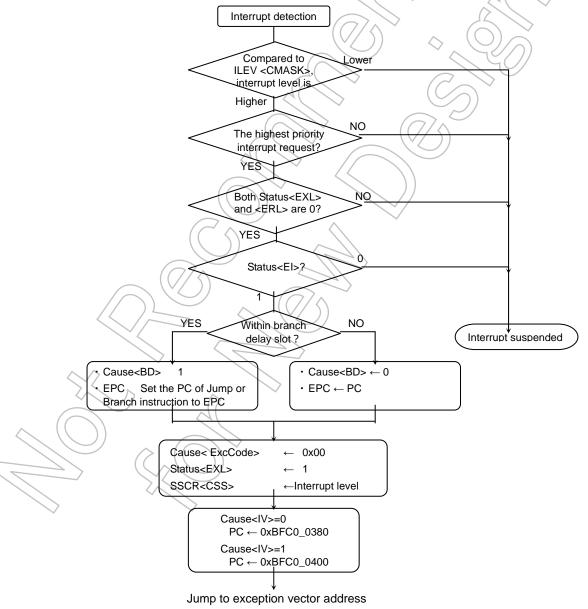

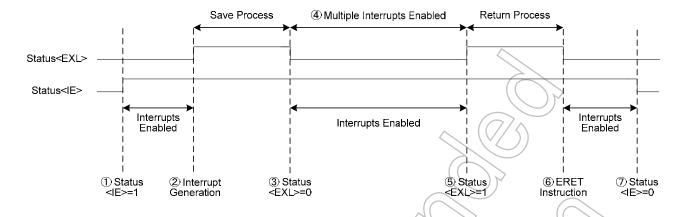

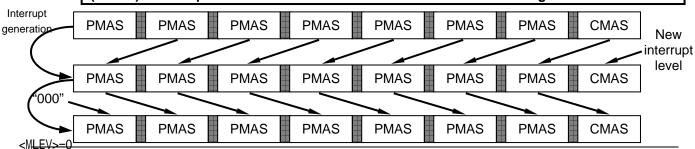

- 3) High-speed interrupt response suitable for real-time control

- Independency of the entry address

- Automatic generation of factor-specific vector addresses

- Automatic update of interrupt mask levels

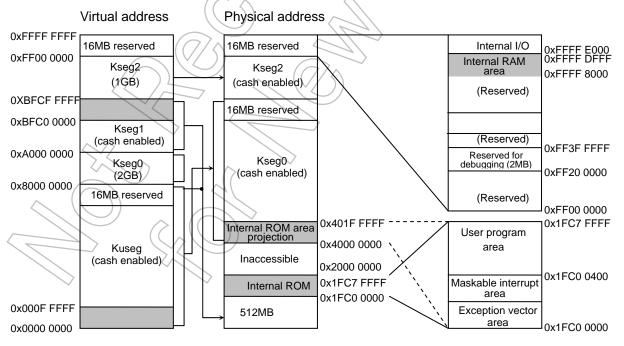

- (2) Internal program memory and data memory

| Product name   | Built-in ROM  | Built-in RAM |

|----------------|---------------|--------------|

| TMP19A63CDXBG  | 512Kbyte      | 24Kbyte      |

| TMP19A63F10XBG | 1Mbyte(Flash) | 48Kbyte      |

- ROM correction function: 8wordx12 block

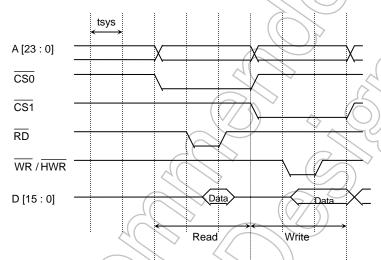

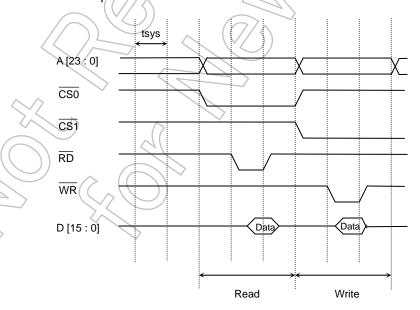

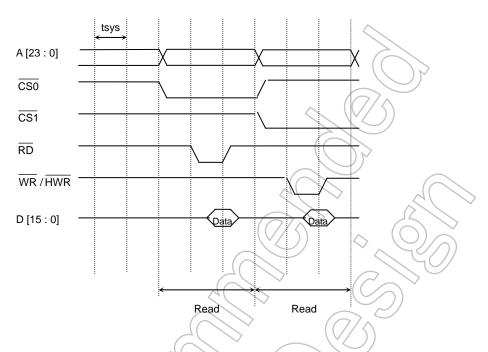

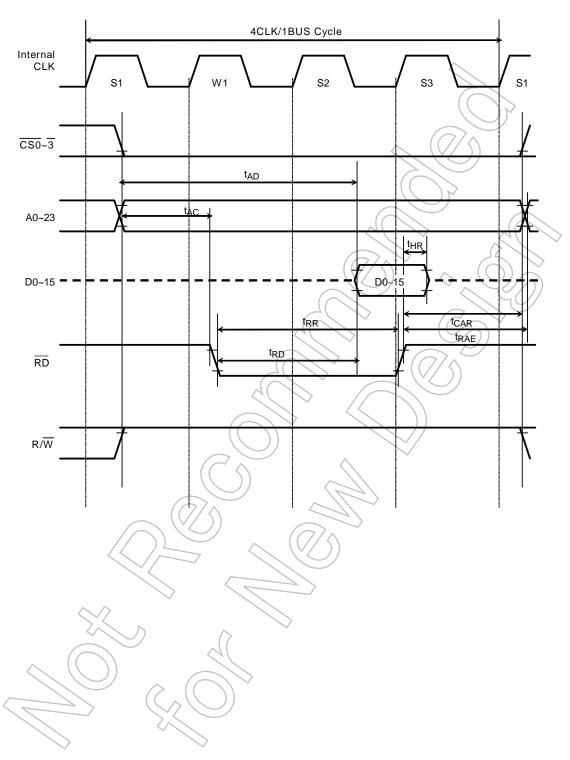

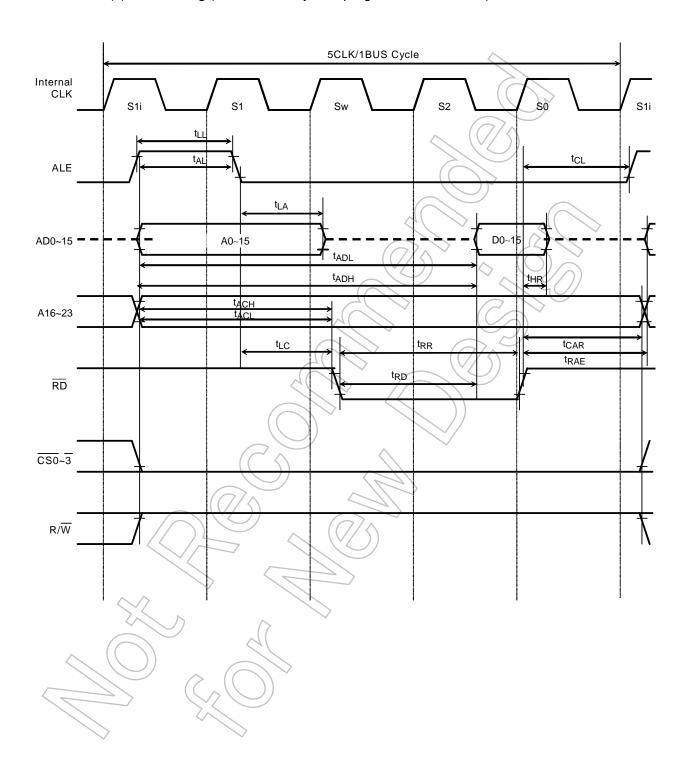

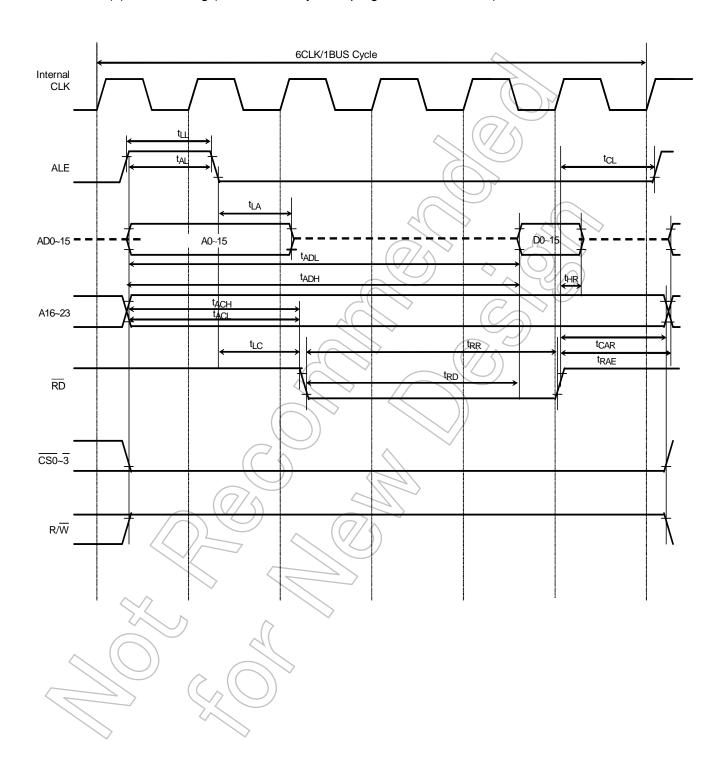

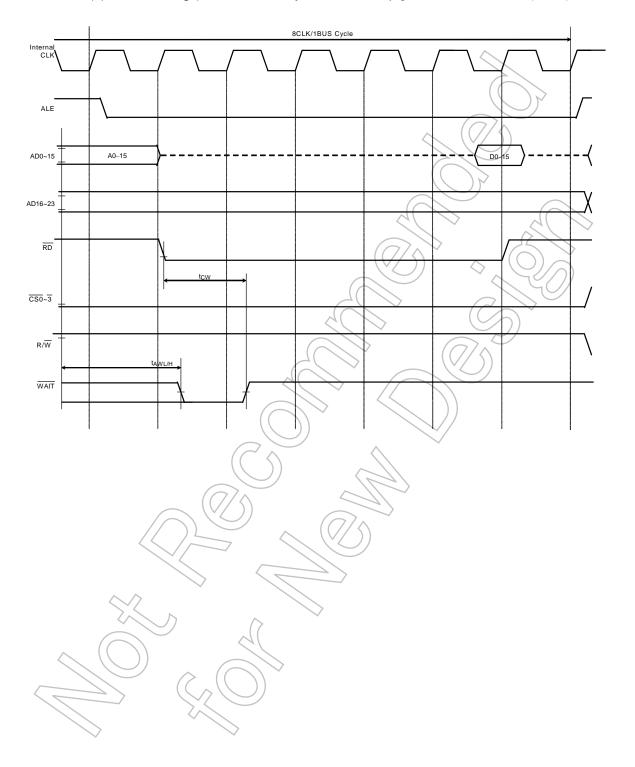

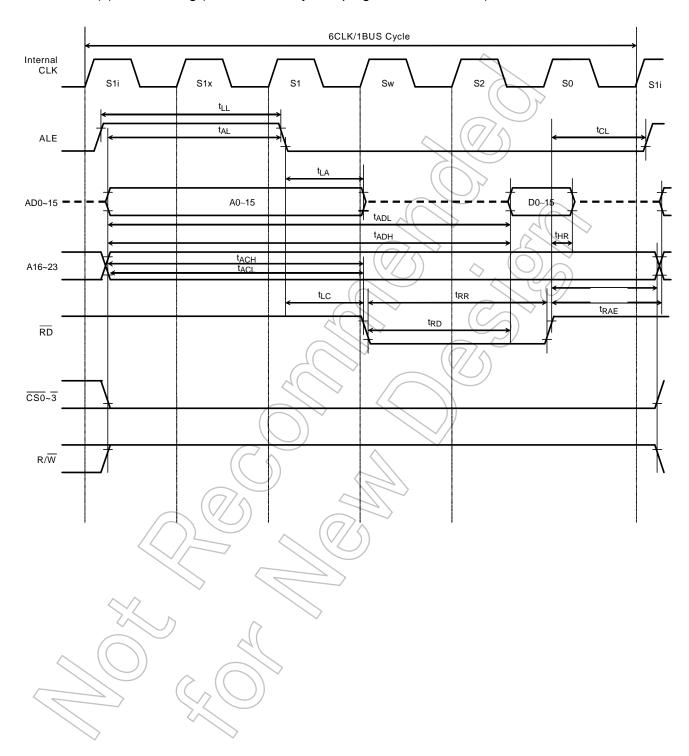

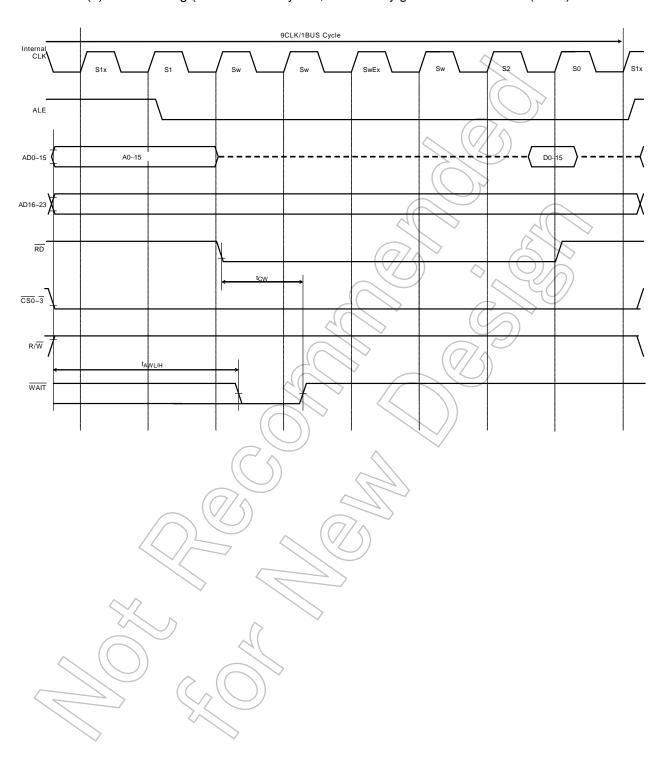

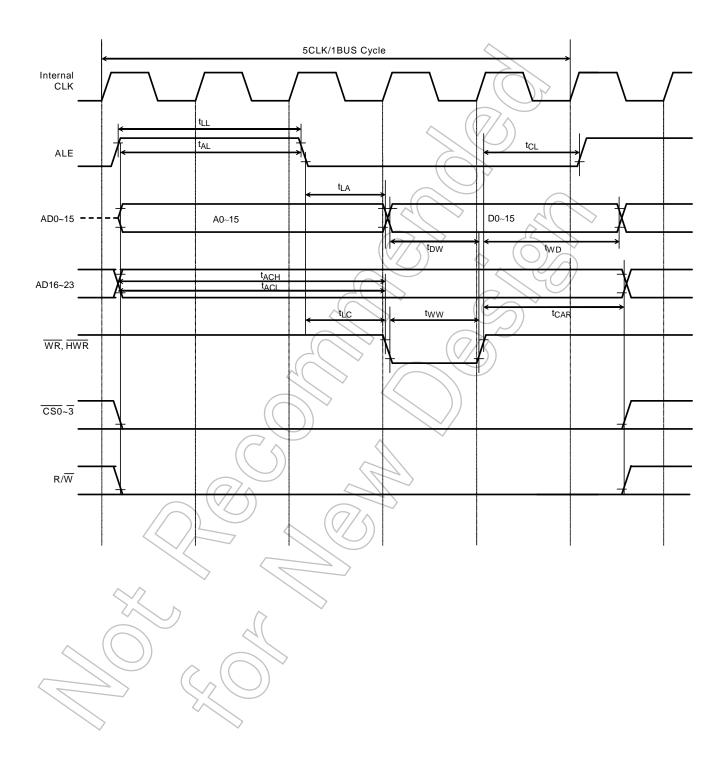

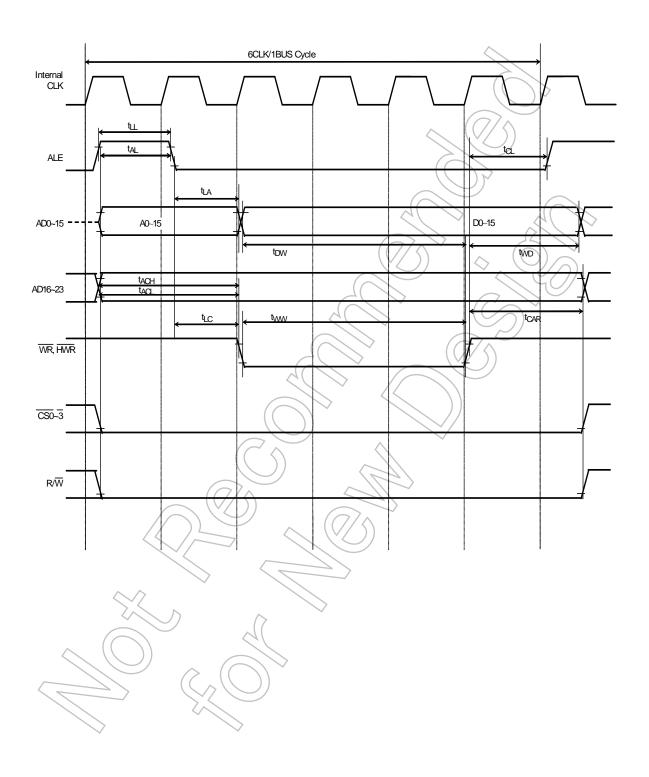

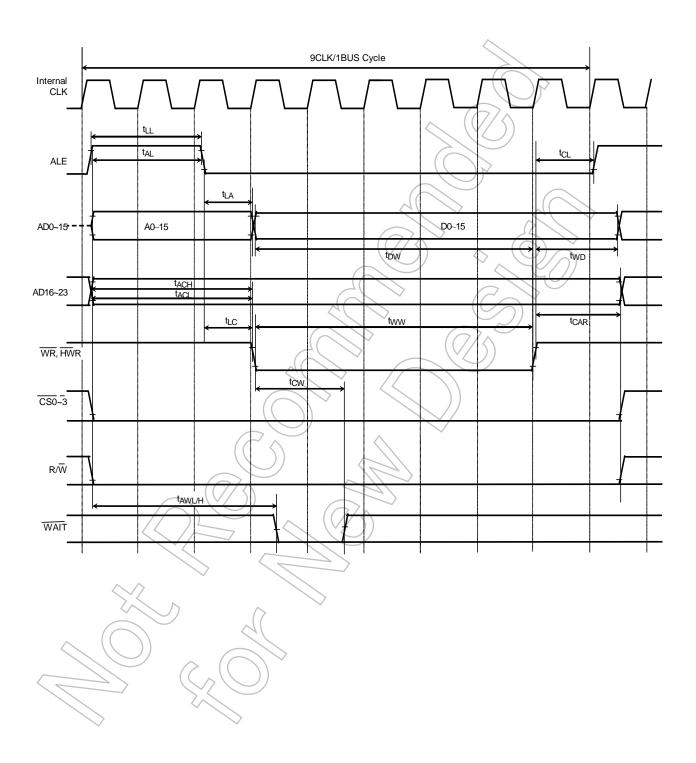

- (3) External memory expansion

- Expandable to 16 megabytes (for both programs and data)

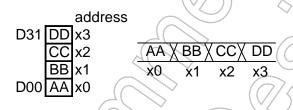

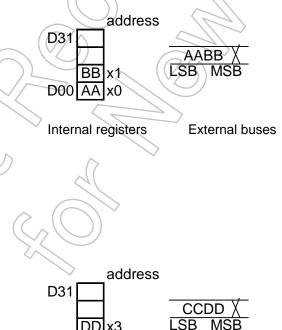

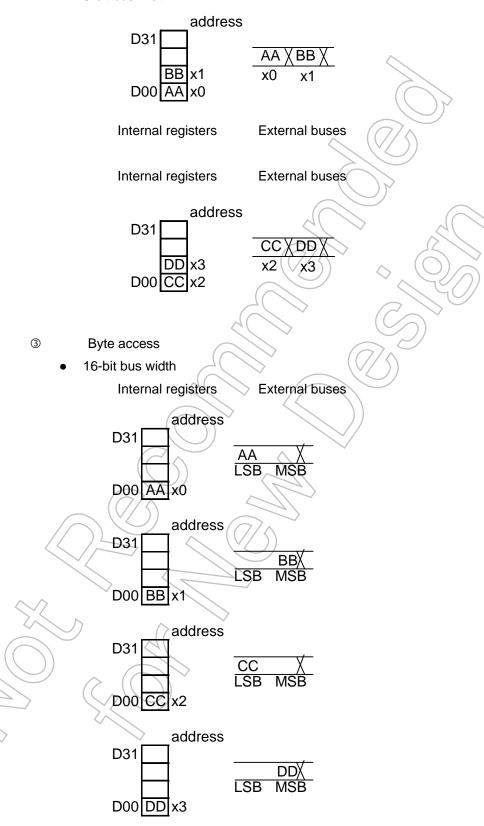

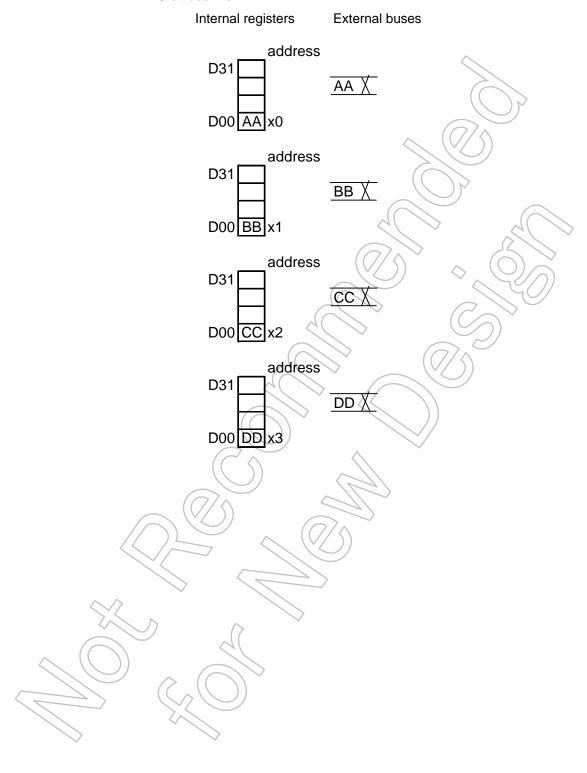

- External data bus:

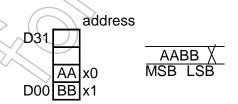

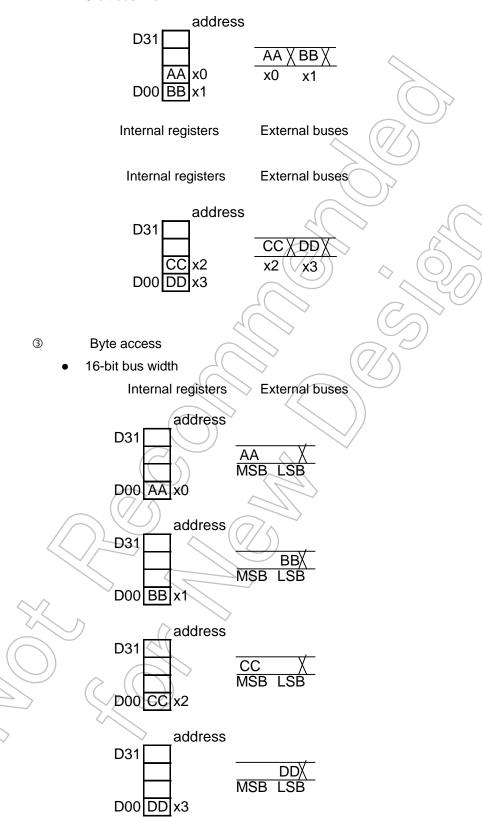

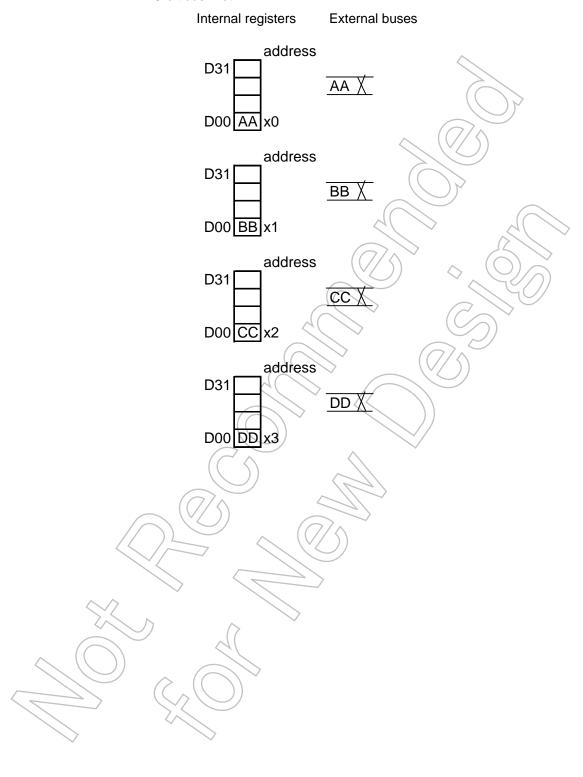

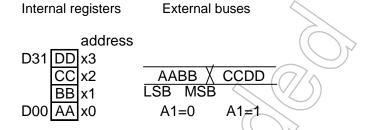

Separate bus/multiplexed bus : Coexistence of 8- and 16-bit widths is possible.

Chip select/wait controller: 4 channels

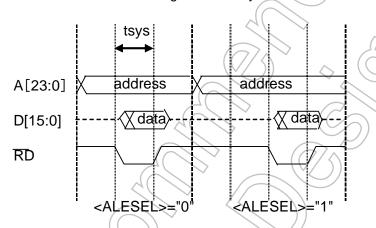

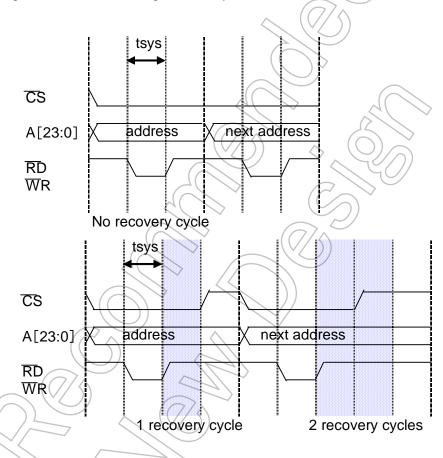

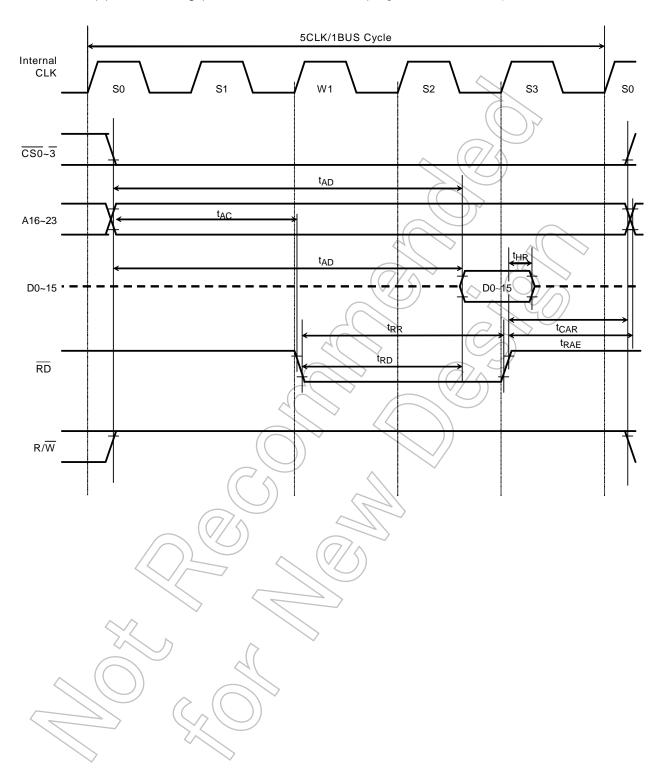

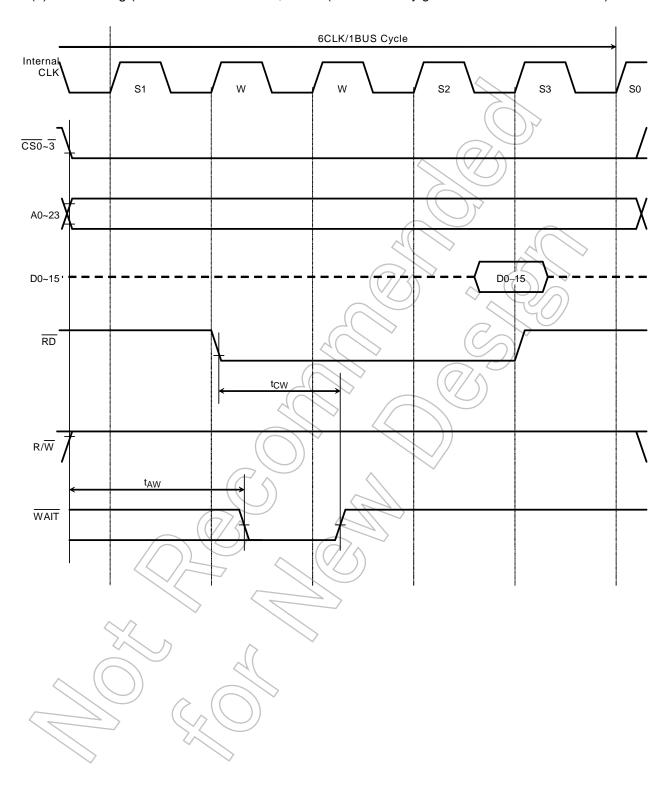

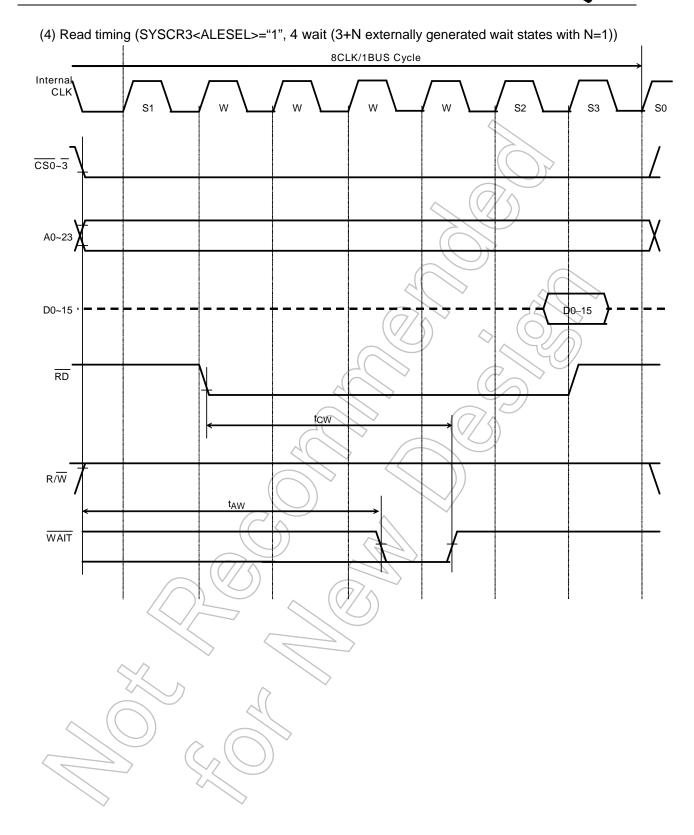

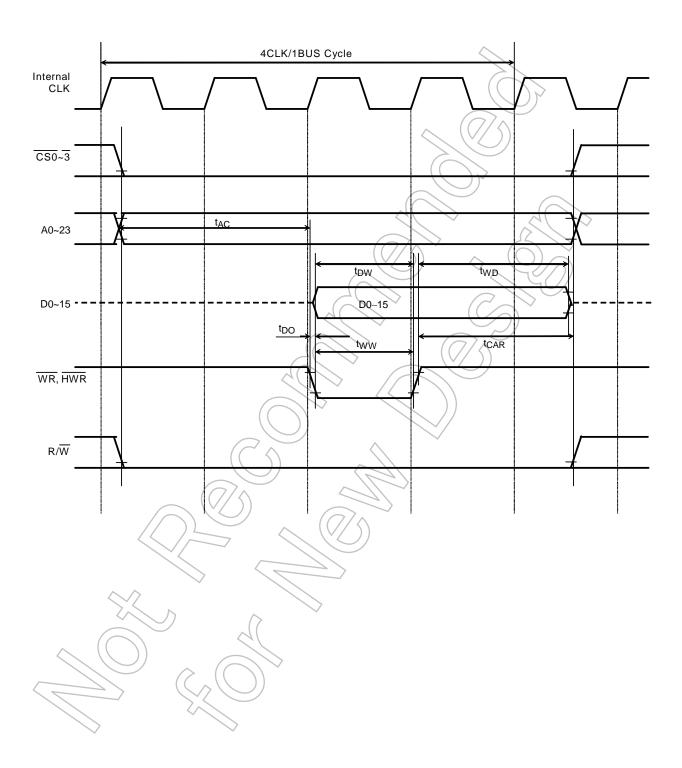

Added CS recovery function (wait is inserted within RD (WR)↑ - CS↑)

(For 1 clock)

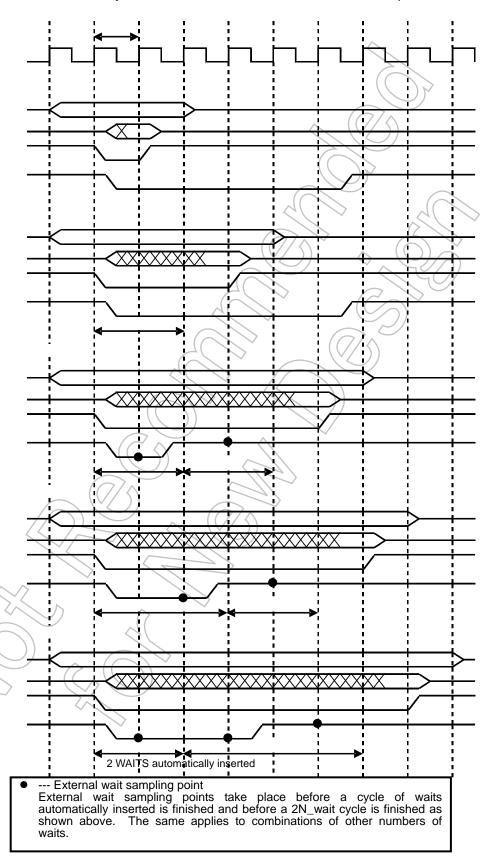

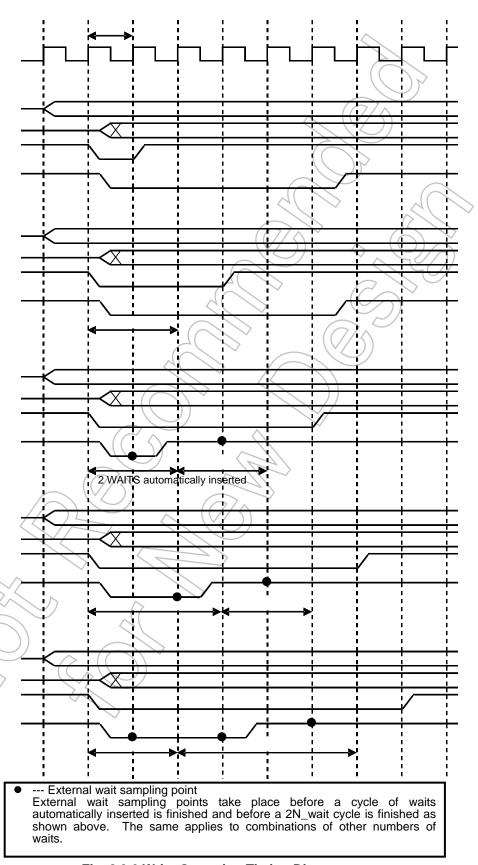

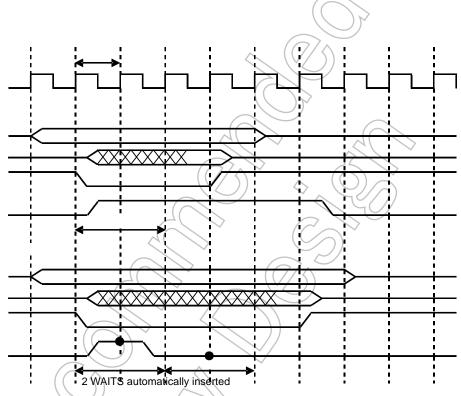

External wait X+2N-capable (X=2 to 7)

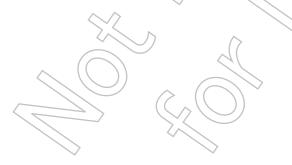

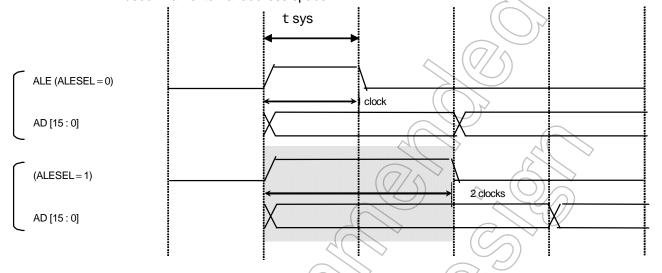

Changed ALE width

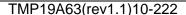

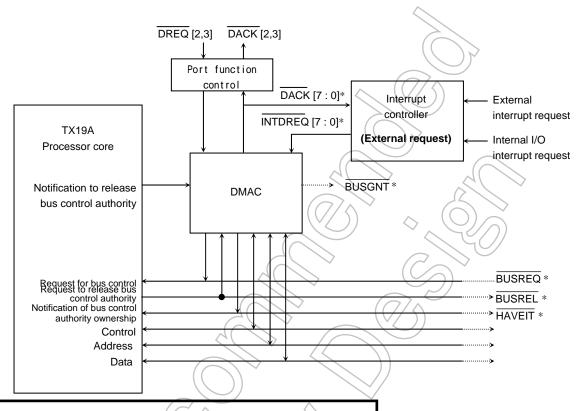

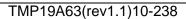

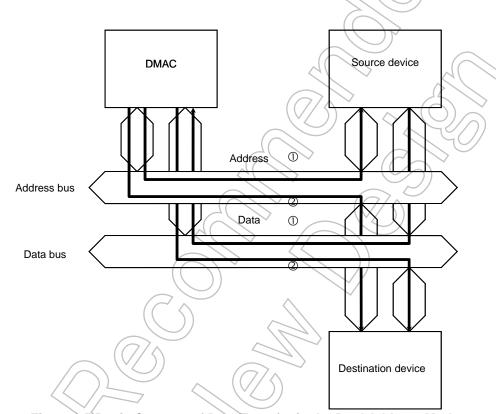

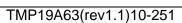

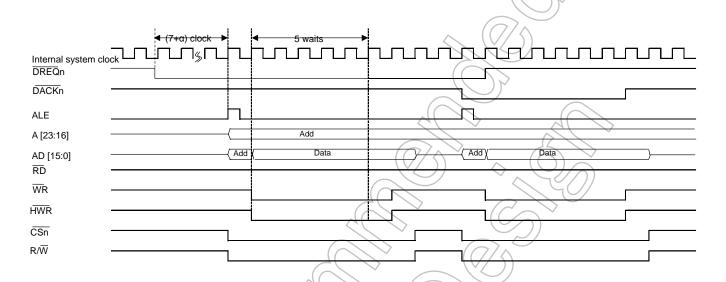

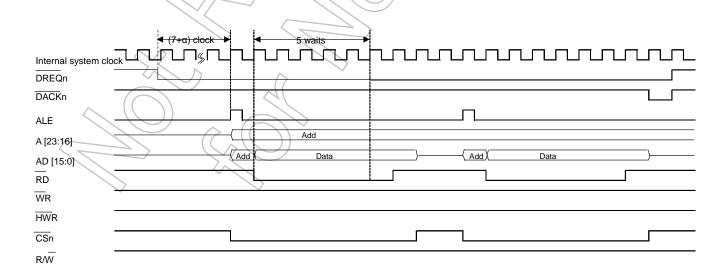

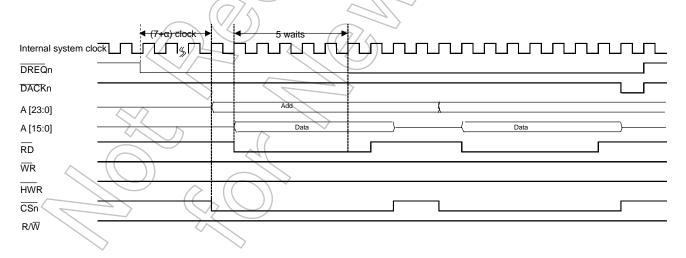

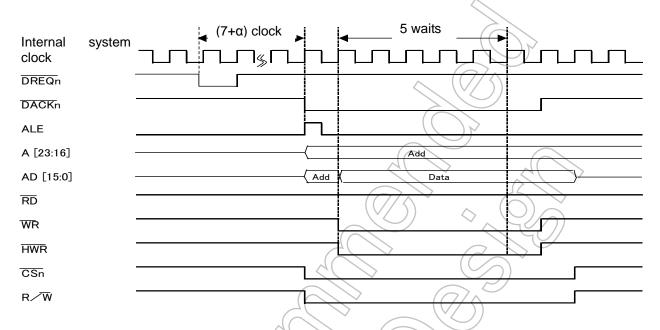

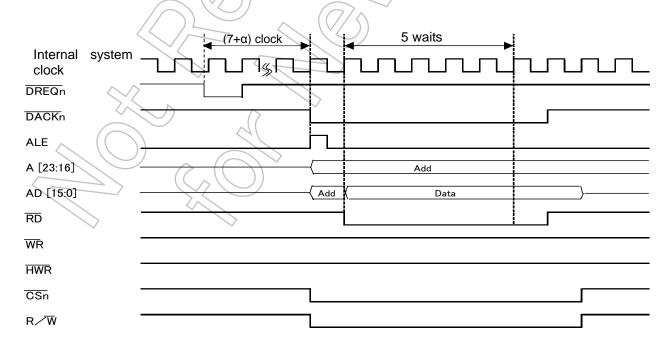

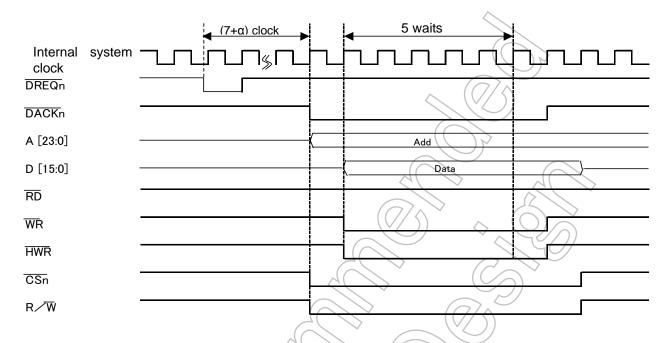

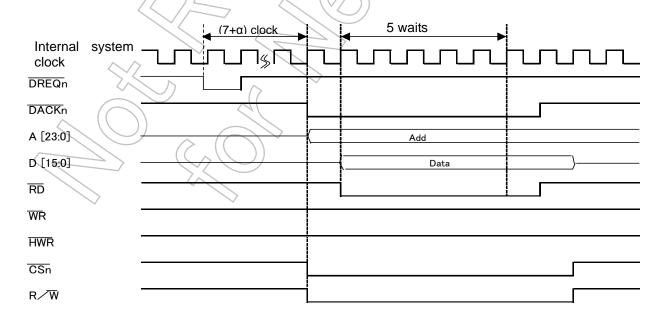

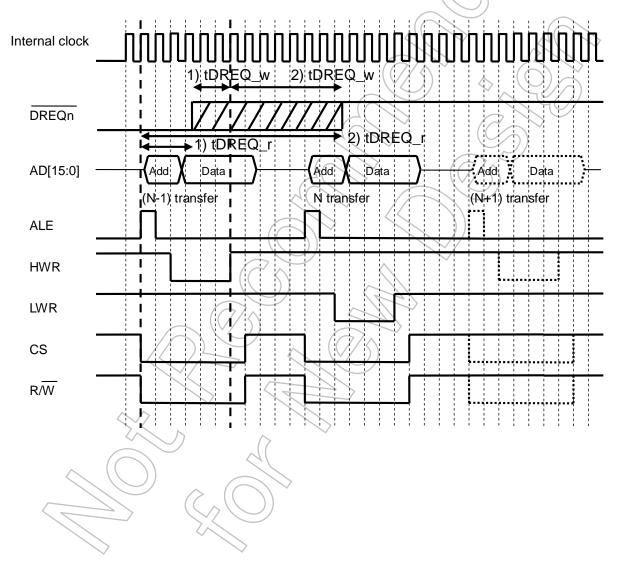

(4) DMA controller

: 8 channels

- Activated by an interrupt or software

- Data to be transferred to internal memory, internal I/O, external memory, and external I/O

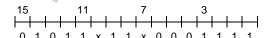

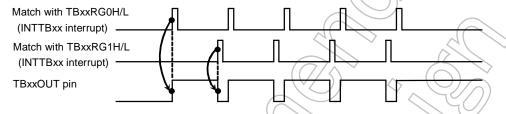

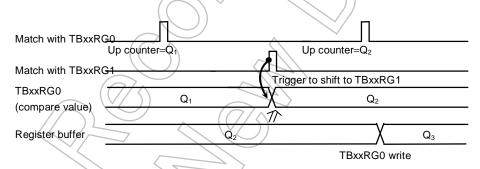

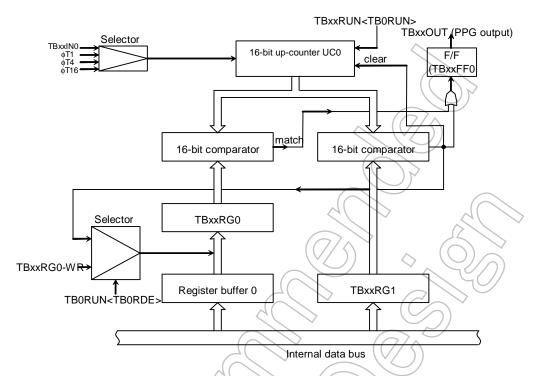

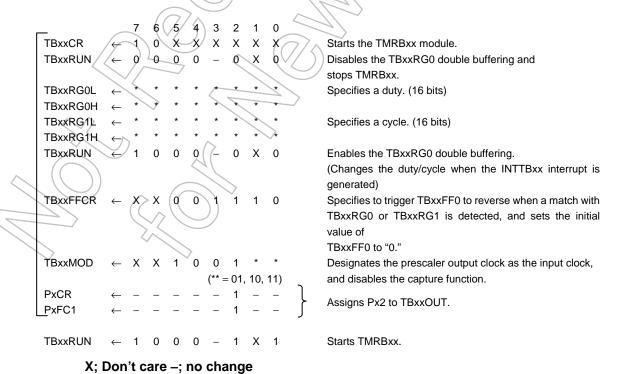

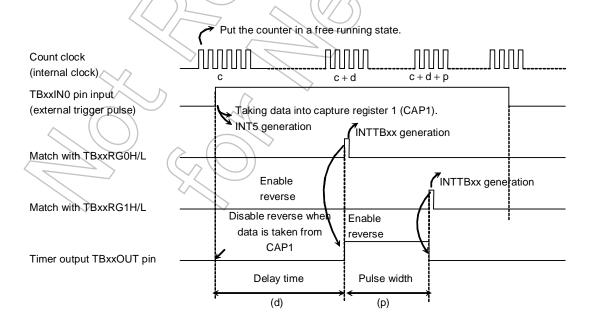

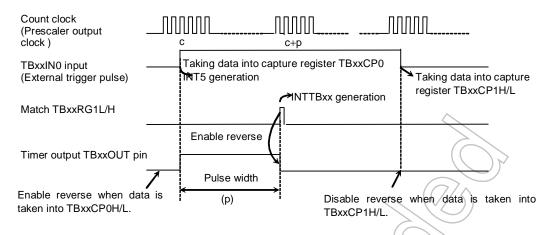

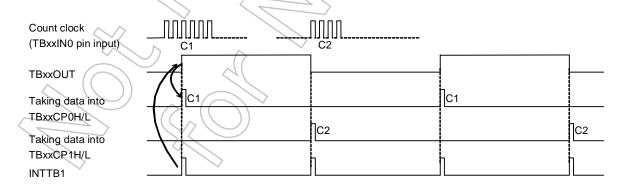

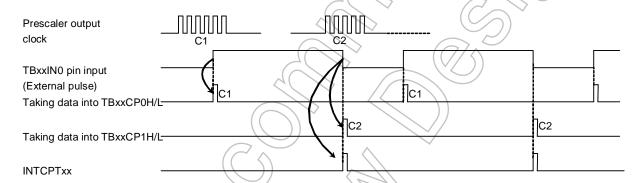

- (5)16-bit timer

: 36 channels

- 16-bit interval timer mode

- 16-bit event counter mode

- 16-bit PPG output

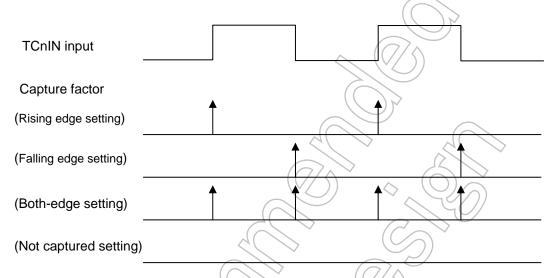

- Input capture function

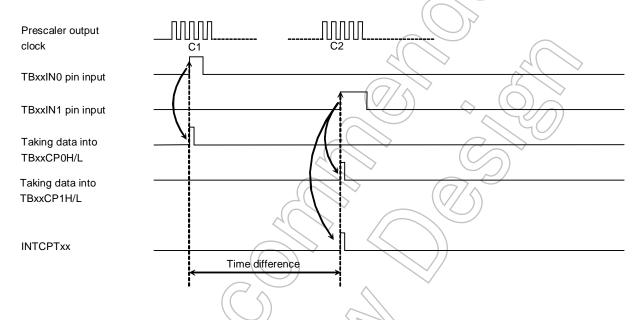

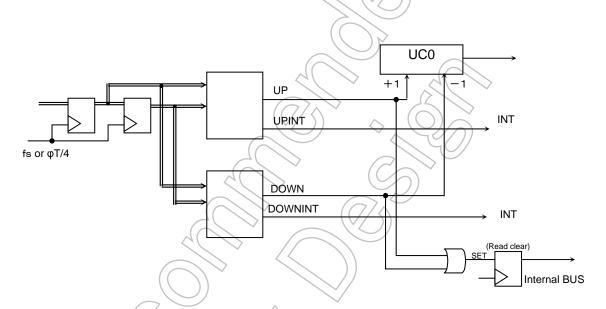

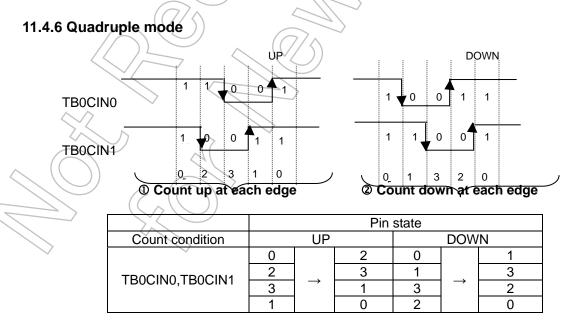

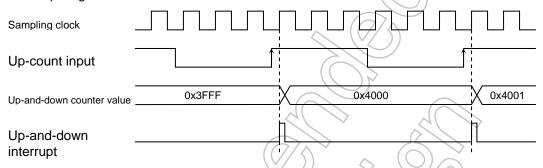

2-phase pulse input counter function (2 channels assigned to perform this function):

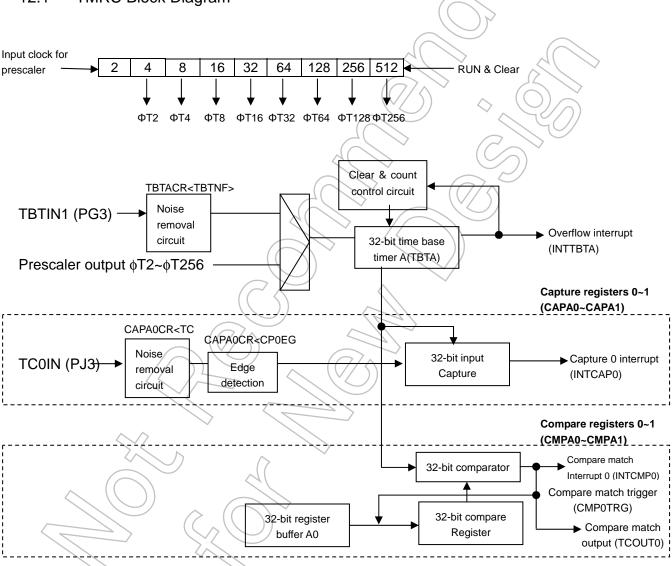

(6)32-bit timer

- 32-bit input capture register: 4 channels

- 32-bit compare register: 4 channels

- 32-bit time base timer: 2 channels

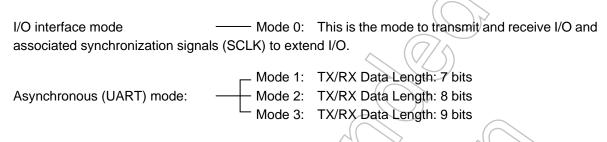

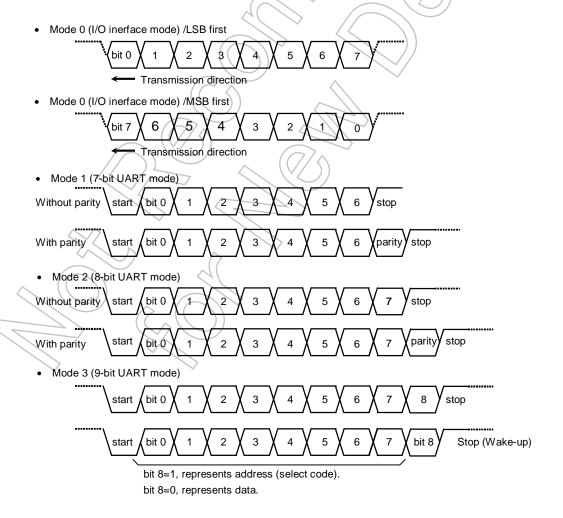

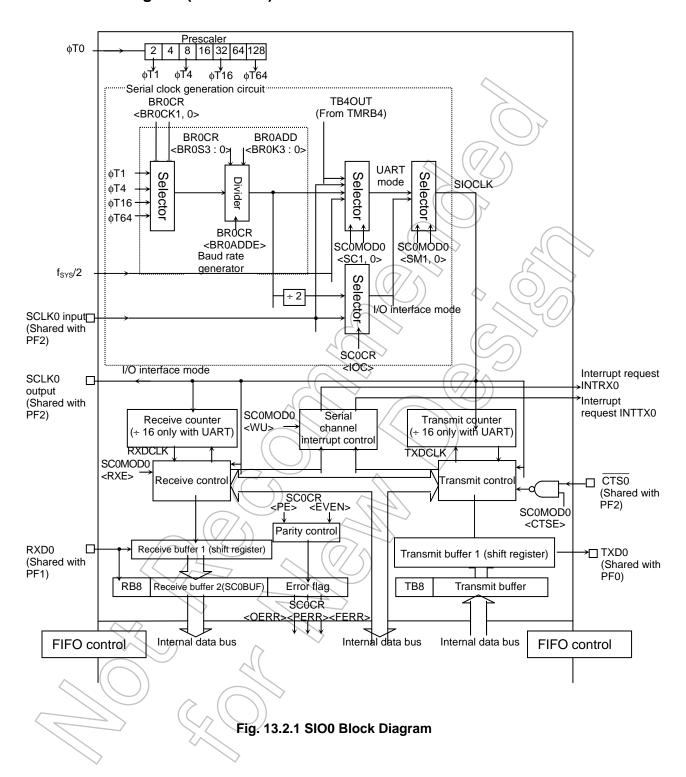

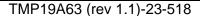

- (7) General-purpose serial interface: 11 channels

- Selectable between the UART mode and the synchronization mode

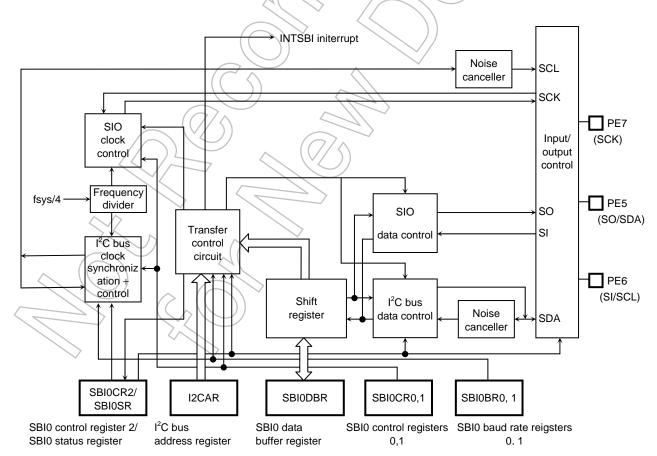

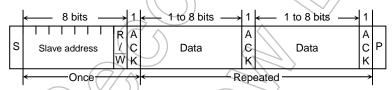

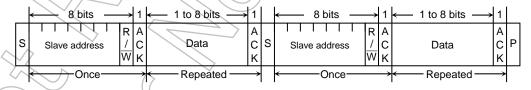

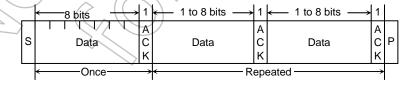

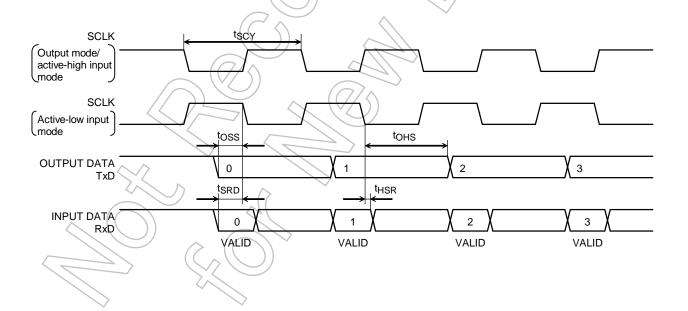

- (8) Serial bus interface: 2 channels

- Selectable between I<sup>2</sup>C bus mode/ the clock synchronization mode

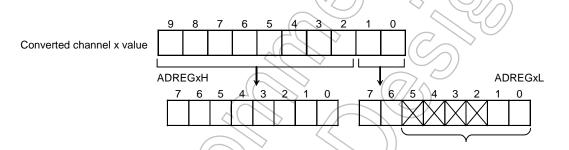

- (9) 10-bit A/D converter (with S/H): 32 channels

- An optional trigger by the internal timer

- Fixed channel/scan mode

- Single/repeat mode

- Top-priority conversion mode

- Timer monitor function

1.7usec@27MHz (at 54MHz) 1.15usec@40MHz (at 40MHz) (Consists of 2 units. Capable of simultaneous conversion. No definition for error between units)

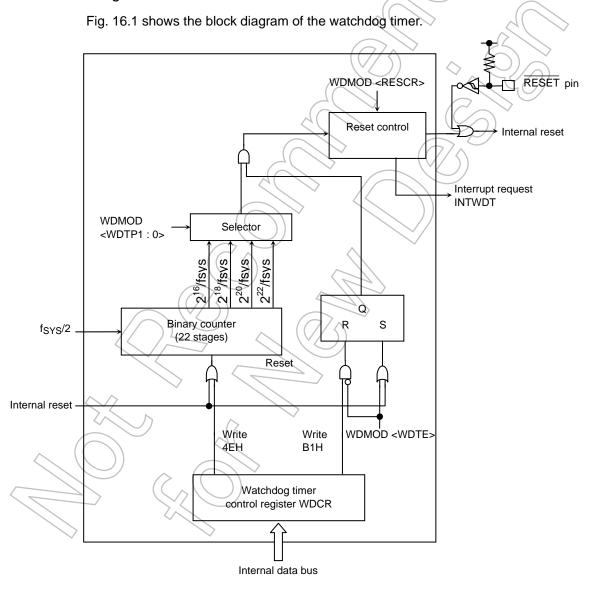

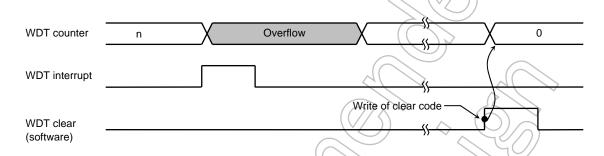

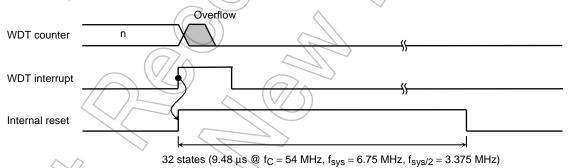

- (11) Watchdog timer: 1 channel

- (12) Chip select/ wait controller: 6 channels

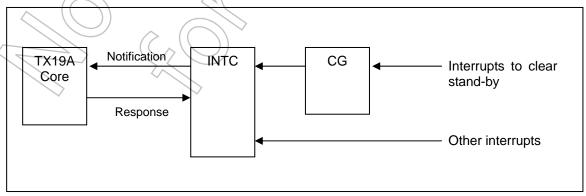

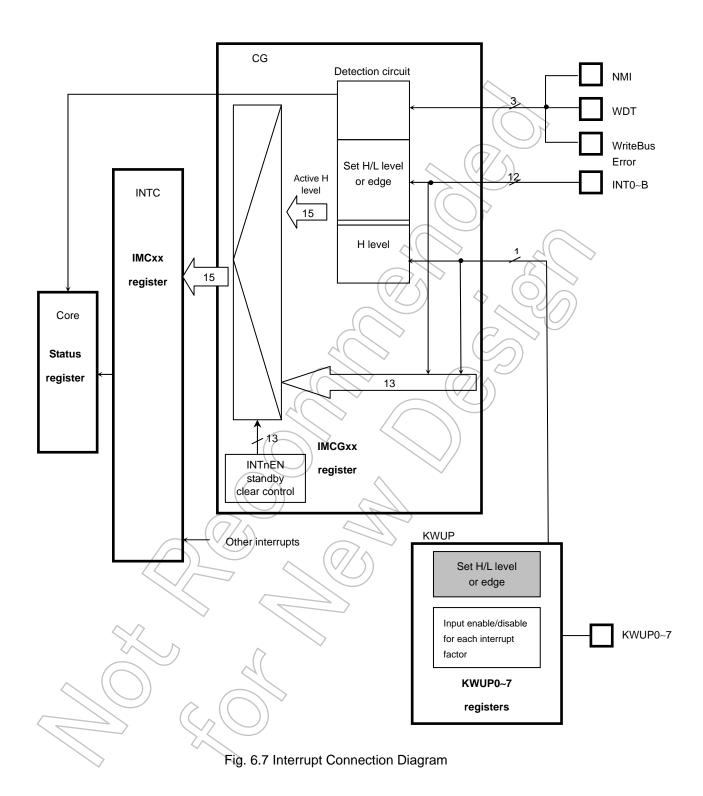

- (13) Interrupt function

- CPU: 2 factors ...software interrupt instruction

- Internal 83 factors...The order of precedence can be set over 7 levels (except the watchdog timer interrupt)

39- independent-interrupt factors are included.

• External: 20 factors...The order of precedence can be set over 7 levels.

(Except for NMI interrupt)

8 factors, which are KWUP, are united as an interrupt factor.

- (14) Input and output ports: 212 pins

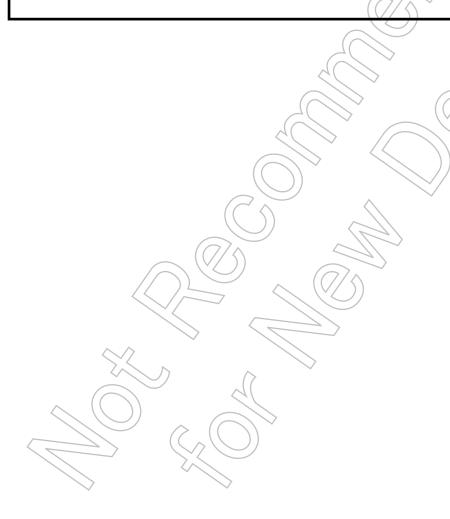

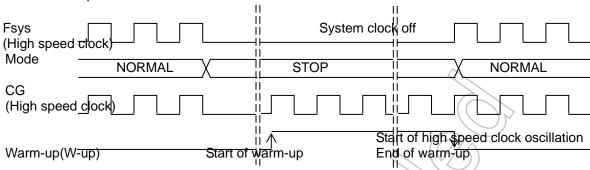

- (15) Standby function

- Two stand-by modes (IDLE, STOP)

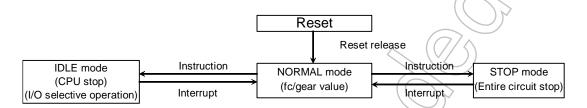

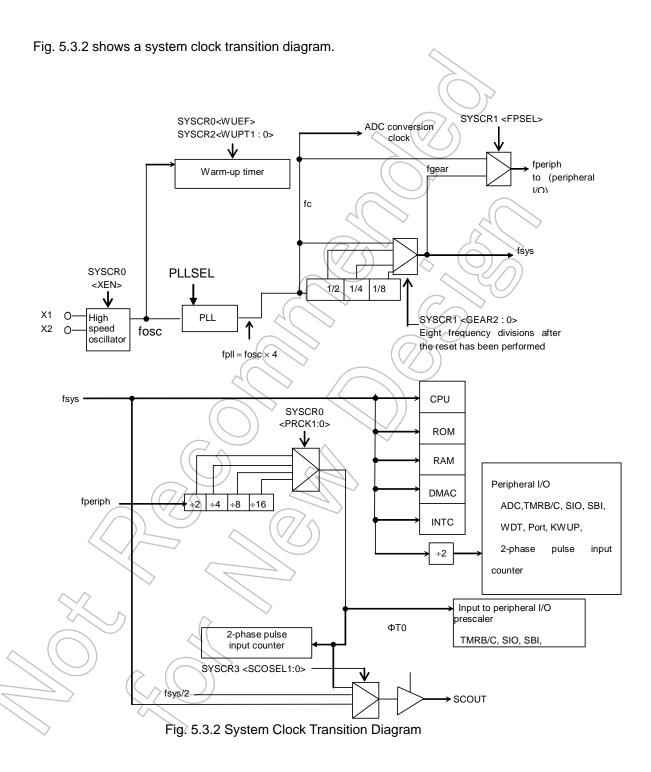

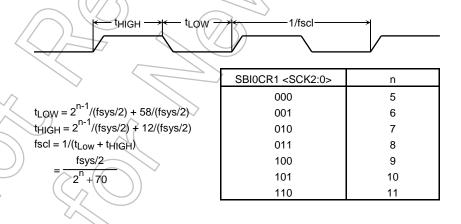

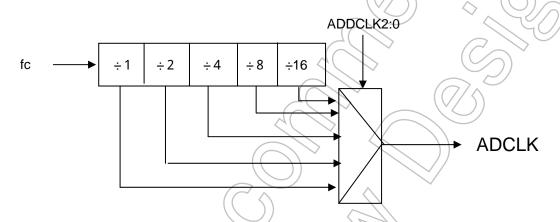

- (16) Clock generator

- Built-in PLL (multiplication by 4)

- Clock gear function: The high-speed clock can be divided into 1/1, 1/2, 1/4, 1/8.

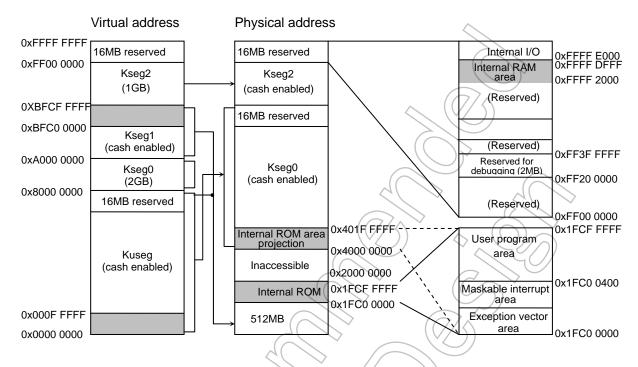

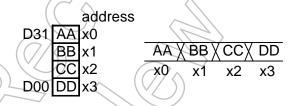

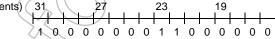

- (17) Endian: Bi-endian (big-endian/little-endian)

#### Big endian

| Upper address | 31 24 | 23 16 | 15 /8 | 7 0 | Word address |

|---------------|-------|-------|-------|-----|--------------|

| <b>↑</b>      | 8     | 9     | 10    | 11  | 8            |

|               | 4     | 5     | 6     | 1/  | 4            |

|               | 0     |       | 2     | 3   | 0            |

#### Lower address

- The most significant byte is 0 (bit 31-24)

- The address of the most significant byte specifies the word address.

#### Little endian

| Upper address | 31 24 | 23 16 | 15 8 | 7 0 | Word address |

|---------------|-------|-------|------|-----|--------------|

| $\uparrow$    | 11/   | 10    |      | 8   | 8            |

|               | 7     | 6     | 5    | 4   | 4            |

|               | √ 3   | 2     | 1    | 0   | 0            |

#### Lower address

- The least significant byte is 0 (bit 7-0).

- The address of the least significant byte specifies the word address.

- (18) Operating frequency

- 54MHz (DVCC15 = 1.35V-1.65V)

- (19) Operating voltage range

- Core: 1.35 1.65V

- I/O: 1.65 3.3 V

- ADC: 2.7 3.3 V

- (20) Temperature range

- -20°C-85°C

- 0°C -70°C (Flash W/E)

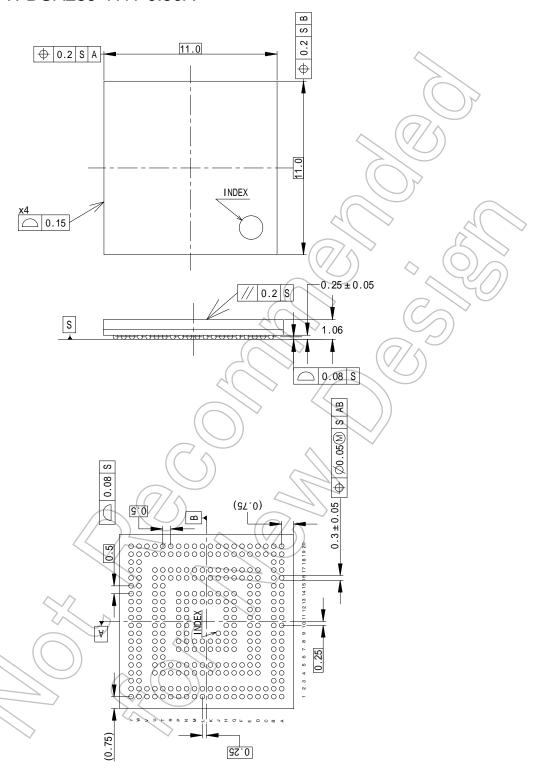

- (21) Package

- P-TFBGA289 (11mm×11mm, 0.5mm pitch)

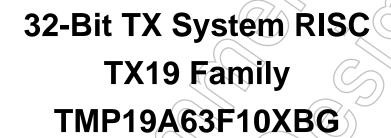

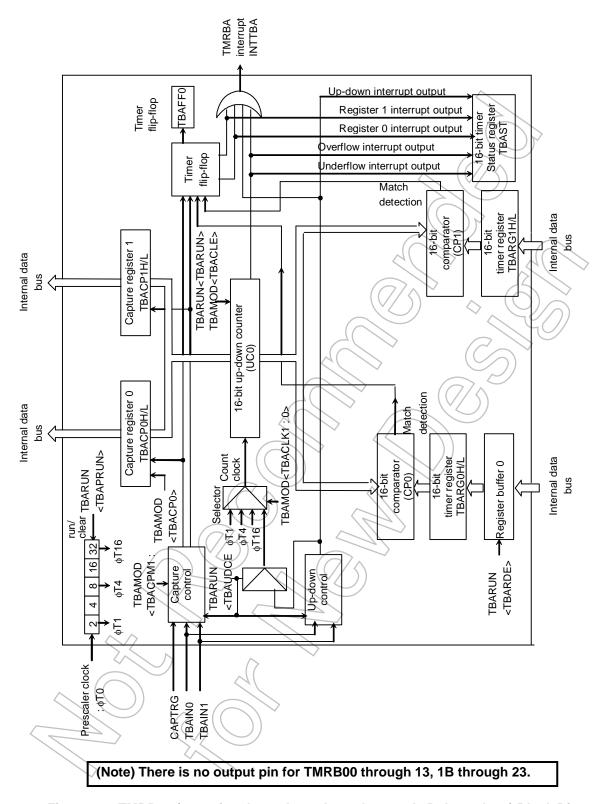

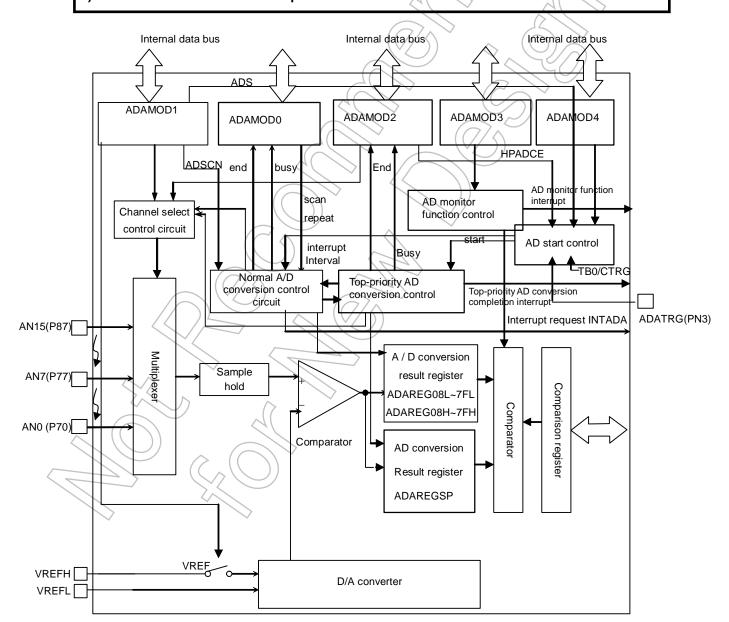

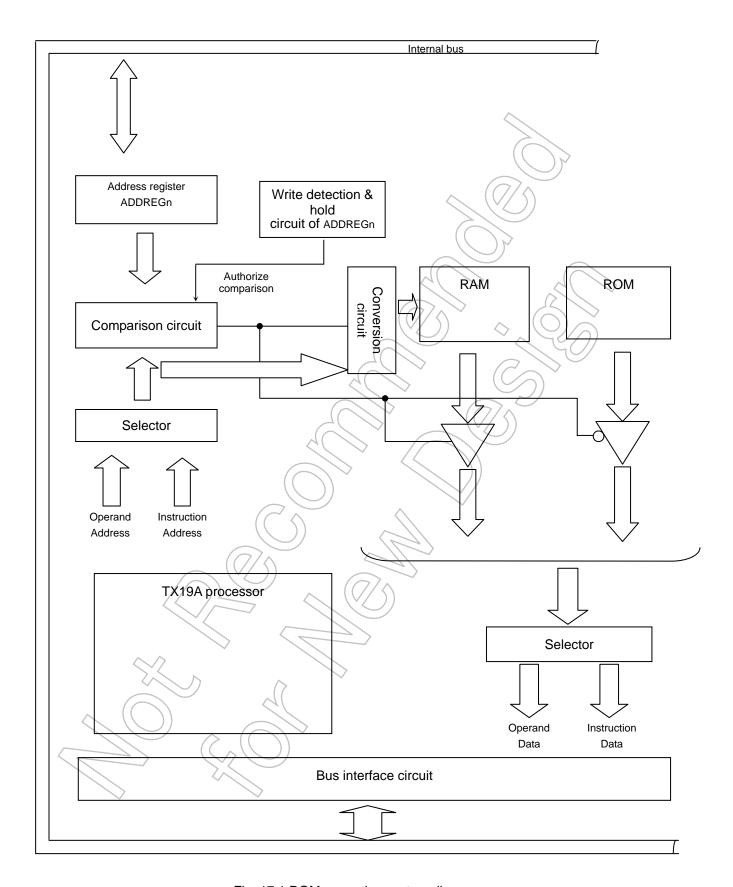

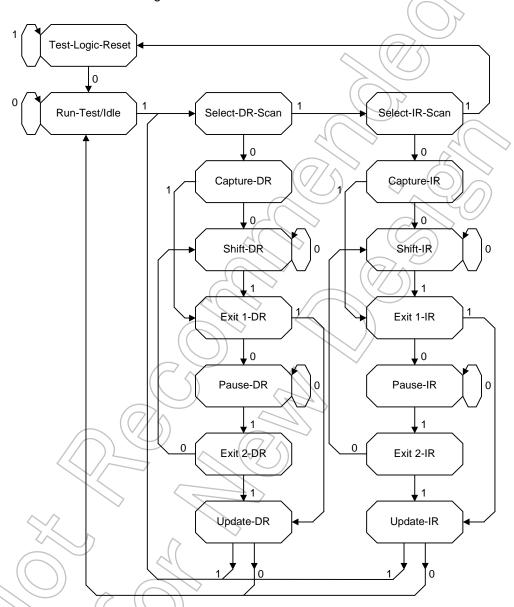

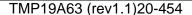

Fig. 1.1 TMP19A63F10XBG Block Diagram

# 2. Pin Layout and Pin Functions

This section shows the pin layout of TMP19A63 and describes the names and functions of input and output pins.

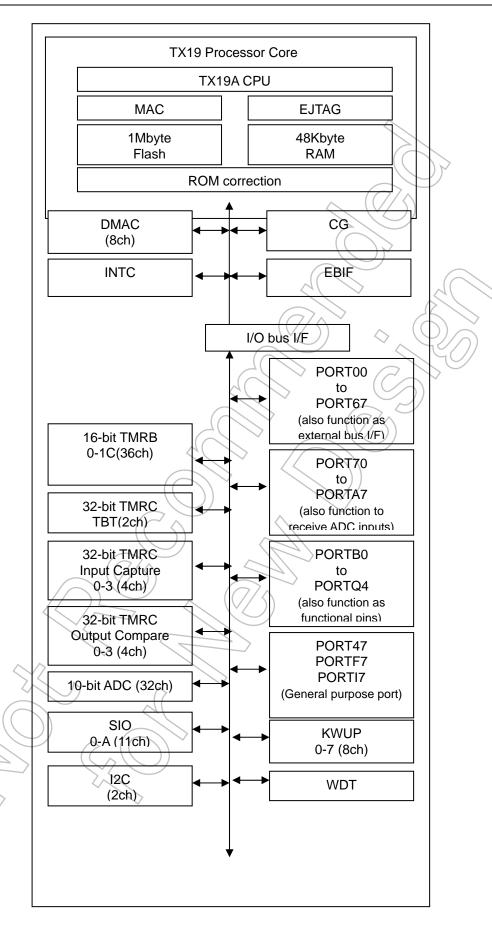

#### 2.1 Pin Layout (Top view)

Fig. 2.1.1 shows the pin layout of TMP19A63.

| A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |    |     |    |    |    |    |    |    |            |     |            |                  |          |     |                 |               |     |      |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|-----|----|----|----|----|----|----|------------|-----|------------|------------------|----------|-----|-----------------|---------------|-----|------|-----|

| C1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A1 | A2 | A3  | A4 | A5 | A6 | Α7 | A8 | A9 | A10        | A11 | A12        | A13              | A14      | A15 | A16             | A17           | A18 | A19  | A20 |

| D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B1 | B2 | B3  | В4 | B5 | B6 | В7 | B8 | B9 | B10        | B11 | B12        | B13              | B14      | B15 | B16             | (B17)         | B18 | B19  | B20 |

| E1         E2         E4         E5         E6         E7         E8         E9         E10         E11         E12         E13         E14         E15         E16         E17         F19         F20           F1         F2         F4         F5         F4         F5         F7         G8         G9         G10         G11         G12         G13         G14         G16         G17         G19         G20           H1         H2         H4         H5         H7         H8         H9         H10         H11         H12         H13         H14         H16         H17         H19         H20           J1         J2         J4         J5         J7         J8         J9         J13         J14         H16         H17         H19         H20           K1         K2         K4         K5         K7         K8         K7         K8         K13         K14         K16         K17         K19         K20           K1         L2         L4         L5         L7         L8         K13         K14         K16         K17         M19         M20           N1         N2         N4<                                                                                                                                                                                                                                                                 | C1 | C2 |     |    |    |    |    |    |    |            |     |            |                  |          |     |                 |               |     | C19  | C20 |

| F1         F2         F4         F5         G7         G8         G9         G10         G11         G12         G13         G14         G16         G17         G19         G20           H1         H2         H4         H5         H7         H8         H9         H10         H11         H12         H13         H14         H16         H17         H19         H20           J1         J2         J4         J5         J7         J8         J9         J13         J14         H16         H17         H19         H20           K1         K2         K4         K5         K7         K8         K7         K8         K13         K14         K16         K17         K19         L20           M1         M2         M4         M5         M7         M8         M7         M8         M13         M14         M16         M17         M19         M20           N1         N2         N4         N5         N7         N8         N9         N10         N11         N12         N13         N14         N16         N17         M19         N20           R1         R2         P4         P5         P7 </td <td>D1</td> <td>D2</td> <td></td> <td>D4</td> <td>D5</td> <td>D6</td> <td>D7</td> <td>D8</td> <td>D9</td> <td>D10</td> <td>D11</td> <td>D12</td> <td>D13</td> <td>D14</td> <td>D15</td> <td>Ø16</td> <td><b>P</b>17</td> <td></td> <td>D19</td> <td>D20</td> | D1 | D2 |     | D4 | D5 | D6 | D7 | D8 | D9 | D10        | D11 | D12        | D13              | D14      | D15 | Ø16             | <b>P</b> 17   |     | D19  | D20 |

| G1         G2         G4         G5         G7         G8         G9         G10         G11         G12         G13         G14         G16         G17         G19         G20           H1         H2         H4         H5         H7         H8         H9         H10         H11         H12         H13         H14         H16         H17         H19         H20           J1         J2         J4         J5         J7         J8         J9         J13         J14         H16         H17         H19         H20           K1         K2         K4         K5         K7         K8         K7         K8         K13         K14         K16         K17         K19         K20           L1         L2         L4         L5         L7         L8         K13         K14         K16         K17         K19         K20           M1         M2         M4         M5         M7         M8         N9         N10         N11         N12         N13         N14         N16         N17         N19         N20           P1         P2         P4         P5         P7         P8         P9 </td <td>E1</td> <td>E2</td> <td></td> <td>E4</td> <td>E5</td> <td>E6</td> <td>E7</td> <td>E8</td> <td>E9</td> <td>E10</td> <td>E11</td> <td>E12</td> <td>E13</td> <td>E14</td> <td>E15</td> <td>E16</td> <td>Æ17</td> <td></td> <td>E19</td> <td>E20</td>        | E1 | E2 |     | E4 | E5 | E6 | E7 | E8 | E9 | E10        | E11 | E12        | E13              | E14      | E15 | E16             | Æ17           |     | E19  | E20 |

| H1 H2 H4 H5 J7 J8 J9 H10 H11 H12 H13 H14 H16 H17 J19 J20 J19 J20 K1 K2 K4 K5 K7 K8 K7 K8 K7 K8 K13 K14 L16 L17 L10 L2 L4 L5 K7 K8 K7 K8 K7 K8 K13 K14 L16 L17 L10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | F1 | F2 |     | F4 | F5 |    |    |    |    |            |     |            |                  |          |     | F16             | F17           |     | F19  | F20 |

| J1         J2         K4         J5         K7         K8         J9         J13         J14         K16         K17         K19         J20           K1         K2         K4         K5         K7         K8         K7         K8         K13         K14         K16         K17         K19         K20           M1         M2         M4         M5         M7         M8         M7         M8         M13         M14         M16         M17         M19         M20           N1         N2         N4         N5         N7         N8         N9         N10         N11         N12         N13         N14         N16         N17         M19         N20           R1         R2         R4         R5         F7         P8         P9         P10         P11         P12         P13         P14         P16         P17         P19         P20           R1         R2         R4         R5         T1         T8         T9         T10         T11         T12         T13         T14         T15         T16         T17         T19         T20           V1         V2         V4         U5<                                                                                                                                                                                                                                                                 | G1 | G2 |     | G4 | G5 |    | G7 | G8 | G9 | G10        | G11 | G12        | G13              | G14      |     | G16             | G17           |     | G19  | G20 |

| K1         K2         K4         K5         K7         K8         K7         K8         K13         K14         K16         K17         K19         K20           L1         L2         L4         L5         L7         L8         L13         L14         L16         L17         L19         L20           M1         M2         M4         M5         M7         M8         M7         M8         M13         M14         M16         M17         M19         M20           N1         N2         N4         N5         N7         N8         N9         N10         N11         N12         N13         N14         N16         N17         N19         M20           R1         R2         R4         R5         P7         P8         P9         P10         P11         P12         P13         P14         P16         P17         P19         P20           R1         R2         R4         R5         T7         T8         T9         T10         T11         T12         T13         T14         T15         T16         T17         T19         T20           V1         V2         V4         U5         U6<                                                                                                                                                                                                                                                                 | H1 | H2 |     | H4 | H5 |    | H7 | Н8 | Н9 | H10        | H11 | H12        | H1,3             | <u> </u> | )   | H16             | H17           |     | H19  | H20 |

| L1         L2         L4         L5         L7         L8         L7         L8         L1         L1         L1         L16         L17         L9         L20           M1         M2         M4         M5         M7         M8         M7         M8         M13         M14         M16         M17         M19         M20           N1         N2         N4         N5         N7         N8         N9         N10         N11         N12         N13         N14         N16         N17         N19         N20           P1         P2         P4         P5         P7         P8         P9         P10         P11         P12         P13         P14         P16         P17         P19         P20           R1         R2         R4         R5         R5         R16         R17         R19         R20         R16         R17         T19         T20           U1         U2         U4         U5         U6         U7         U8         U9         U10         U11         U12         U13         U14         U15         U16         U17         U19         U20           V1         V2 </td <td>J1</td> <td>J2</td> <td></td> <td>J4</td> <td>J5</td> <td></td> <td>J7</td> <td>J8</td> <td>J9</td> <td></td> <td></td> <td></td> <td>J1(3)</td> <td>J14</td> <td></td> <td>J16</td> <td>J17</td> <td></td> <td>J19.</td> <td>J20</td>                   | J1 | J2 |     | J4 | J5 |    | J7 | J8 | J9 |            |     |            | J1(3)            | J14      |     | J16             | J17           |     | J19. | J20 |

| M1         M2         M4         M5         M7         M8         M9         N10         N11         N12         N16         N17         M19         M20           N1         N2         N4         N5         N7         N8         N9         N10         N11         N12         N13         N14         N16         N17         N19         N20           P1         P2         P4         P5         P7         P8         P9         P10         P11         P12         P13         P14         P16         P17         P19         P20           R1         R2         R4         R5         T4         T5         T6         T7         T8         T9         T10         T11         T12         T13         T14         T15         T16         T17         T19         T20           V1         V2         U4         U5         U6         U7         U8         U9         U10         U11         U12         U13         U14         U15         U16         U17         U19         U20           V1         V2         V3         W4         W5         W6         W7         W8         W9         W10         W1                                                                                                                                                                                                                                                         | K1 | K2 |     | K4 | K5 |    | K7 | K8 |    |            |     |            | K13              | K14      | ~   | K16             | K17           | 1   | K19  | K20 |

| N1         N2         N4         N5         N7         N8         N9         N10         N11         N12         N13         N14         N16         N17         N19         N20           P1         P2         P4         P5         P7         P8         P9         P10         P11         P12         P13         P14         P16         P17         P19         P20           R1         R2         R4         R5         T7         T8         T9         T10         T11         T12         T13         T14         T15         T16         T17         T19         T20           U1         U2         U4         U5         U6         U7         U8         U9         U10         U11         U12         U13         U14         U15         U16         U17         U19         U20           V1         V2         V2         V3         W4         W5         W6         W7         W8         W9         W10         W11         W12         W13         W14         W15         W16         W17         W18         W19                                                                                                                                                                                                                                                                                                                                                 | L1 | L2 |     | L4 | L5 |    | L7 | L8 |    |            |     |            | <u></u> 1√13/    | L14      |     | L16             | 四             |     | 19   | L20 |

| P1         P2         P4         P5         P7         P8         P9         P10         P11         P12         P13         P14         P16         P17         P19         P20           R1         R2         R4         R5         F16         R16         R17         R19         R20           T1         T2         T4         T5         T6         T7         T8         T9         T10         T11         T12         T13         T14         T15         T16         T17         T19         T20           U1         U2         U4         U5         U6         U7         U8         U9         U10         U11         U12         U13         U14         U15         U16         U17         U19         U20           V1         V2         V2         V3         W4         W5         W6         W7         W8         W9         W10         W11         W12         W13         W14         W15         W16         W17         W18         W19         W20                                                                                                                                                                                                                                                                                                                                                                                                           | M1 | M2 |     | M4 | M5 |    | М7 | M8 |    |            |     |            | M13              | M14      | <   | M16             | M17           | ))/ | M19  | M20 |

| R1 R2 R4 R5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | N1 | N2 |     | N4 | N5 |    | N7 | N8 | N9 | N10        | N1/ | N12        | ) <del>]</del> 3 | N14      |     | N16             | N17           |     | N19  | N20 |

| T1 T2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P1 | P2 |     | P4 | P5 |    | P7 | P8 | P9 | P10        | P11 | P12        | R13              | P14      |     | P16             | P17           |     | P19  | P20 |

| U1     U2     U4     U5     U6     U7     U8     U9     U10     U11     U12     U13     U14     U15     U16     U17     U19     U20       V1     V2       W1     W2     W3     W4     W5     W6     W7     W8     W9     W10     W11     W12     W13     W14     W15     W16     W17     W18     W19     W20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R1 | R2 |     | R4 | R5 |    |    |    |    |            |     |            | *                |          |     | R16             | R17           | ľ   | R19  | R20 |

| V1 V2 V19 V20<br>W1 W2 W3 W4 W5 W6 W7 W8 W9 W10 W11 W12 W13 W14 W15 W16 W17 W18 W19 W20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | T1 | T2 |     | T4 | T5 | Т6 | T7 | T8 | Т9 | T10        | ŢŲ  | T12        | T13              | T14      | T15 | <del>7</del> 16 | <i>1</i> 1/17 |     | T19  | T20 |

| W1 W2 W3 W4 W5 W6 W7 W8 W9 W10 W11 W12 W13 W14 W15 W16 W17 W18 W19 W20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U1 | U2 |     | U4 | U5 | U6 | U7 | U8 | U9 | <b>U10</b> | ΨĨ  | <b>U12</b> | U13              | U14/     | U15 | U16             | Ú17           |     | U19  | U20 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V1 | V2 | · · |    |    |    |    |    |    | 7          |     |            |                  |          |     | ))              |               | -   | V19  | V20 |

| Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9 Y10 Y11 Y12 Y13 Y14 Y15 Y16 Y17 Y18 Y19 Y20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | W1 | W2 | W3  | W4 | W5 | W6 | W7 | W8 | W9 | W10        | W11 | W12        | W13              | W14      | W15 | W16             | W17           | W18 | W19  | W20 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Y1 | Y2 | Y3  | Y4 | Y5 | Y6 | Y7 | Y8 | Y9 | Y10        | Y11 | Y12        | Y13              | Y14      | Y15 | Y16             | Y17           | Y18 | Y19  | Y20 |

Fig. 2.1.1 Pin Layout Diagram (P-FBGA289)

|         |                |            | /_/           |               | ^              |         |              |

|---------|----------------|------------|---------------|---------------|----------------|---------|--------------|

| PIN No. | PIN Name       | PIN No.    | PIN Name      | PIN No.       | PIN Name       | PIN No. | PIN Name     |

| A1      | N.C(GND)       | B1         | N.C(GND)      | C1            | PL0/TC4IN      | D1      | PL2          |

| A2      | N.C(GND)       | B2 /       | N.C(GND)      | C2            | PL1/TC5IN      | D2      | PL3/TCOUTB0  |

| A3      | RESET          | B3 ( (     | PC\$T0        |               | 1              |         |              |

| A4      | PCST1 /        | B4         | PCST2         |               | 7              | D4      | DVSS         |

| A5      | PCST3          | B5)        | PCST4         | $((//\wedge)$ |                | D5      | PQ0/DREQ2    |

| A6      | DCLK (         | B6         | TOVR          | (             |                | D6      | TCK          |

| A7      | TDO            | <b>B</b> 7 | TDI           |               |                | D7      | DINT         |

| A8      | PP6/TPC6/TPD6  | B8         | PP7/TPC7/TPD7 | / /           |                | D8      | PO6/TPD6     |

| A9      | PP4/TPC4/TPD4  | B9         | PP5/TPC5/TPD5 |               |                | D9      | PO4/TPD4     |

| A10     | PP2/TPC2/TPD2  | B10        | PP3/TPC3/TPD3 |               |                | D10     | PO2/TPD2     |

| A11     | PP0/TPC0/TPD0  | B11        | PP1/TPC1/TPD1 | >             |                | D11     | PO0/TPD0     |

| A12     | PJ4/TC1IN      | //B12      | PJ5/SO1/SDA1  |               |                | D12     | PJ6/SI1/SCL1 |

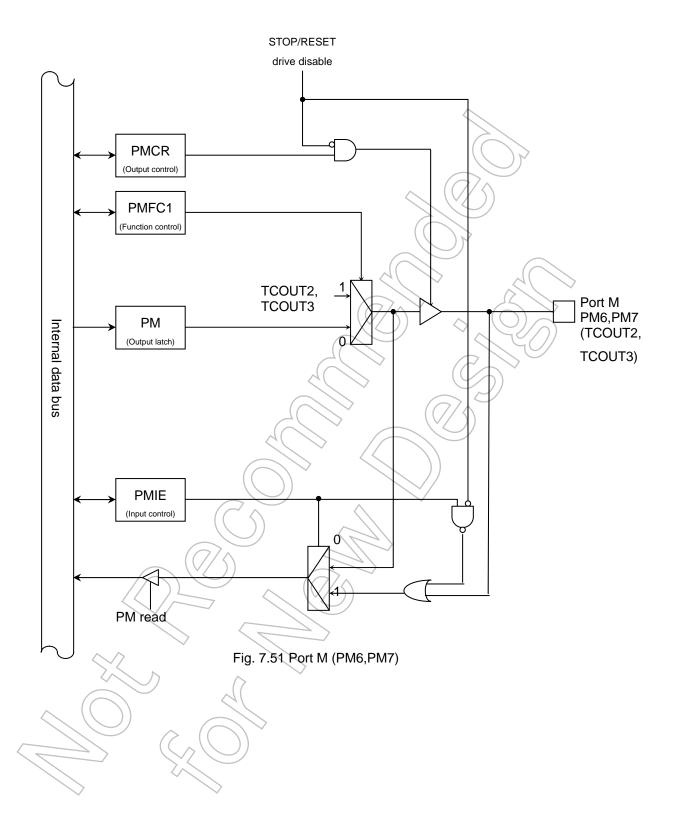

| A13     | PJ2/SCLK8/CTS8 | B13        | PJ3/TC0IN     |               |                | D13     | PM6/TCOUTA0  |

| A14     | PJ0/TXD8       | B14        | PJ1/RXD8      |               |                | D14     | PM4/INT4     |

| A15     | PF6/SCLK1/CTS1 | B15        | PF7           |               |                | D15     | PM2/INT2     |

| A16     | PF4/TXD1       | B16        | PF5/RXD1      |               |                | D16     | PM0/INT0     |

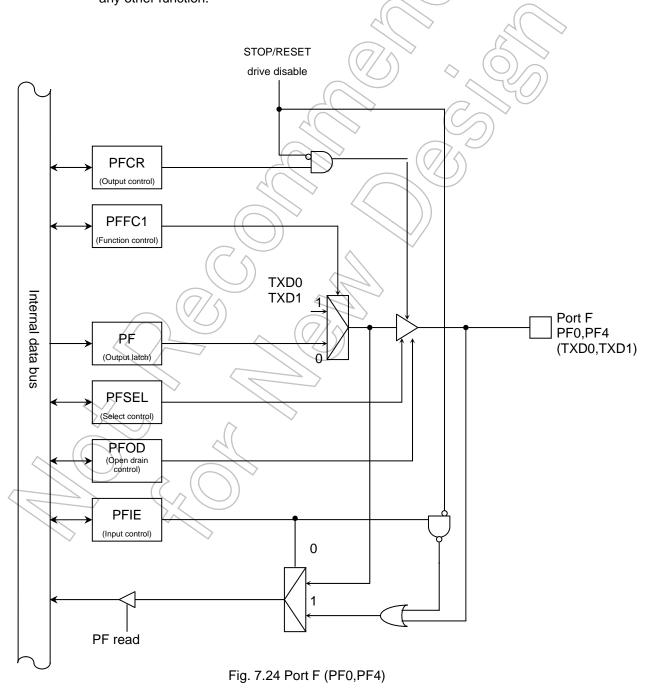

| A17     | PF2/SCLK0/CTS0 | B17/       | PF3           |               |                | D17     | PG5/RXD3     |

| A18     | PF0/TXD0       | B18        | PF1/RXD0      |               |                |         |              |

| A19     | N.C(GND)       | B19        | N.C(GND)      | C19           | PG7/TBTIN2     | D19     | PG4/TXD3     |

| A20     | N.C(GND)       | B20        | N.C(GND)      | C20           | PG6/SCLK3/CTS3 | D20     | PG3/TBTIN1   |

Table 2.1.1 Pin Names and Functions (1/3)

| PIN No.  | PIN Name                     | PIN No.  | PIN Name                             | PIN No.       | PIN Name             | PIN No.         | PIN Name                 |

|----------|------------------------------|----------|--------------------------------------|---------------|----------------------|-----------------|--------------------------|

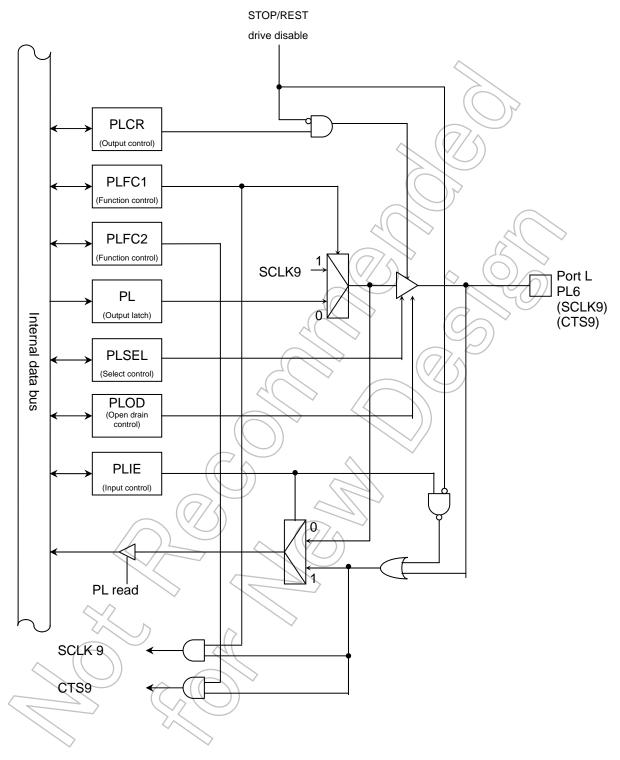

| E1       | PL4/TXD9                     | F1       | PL6/SCLK9/CTS9                       | G1            | P00/D0/AD0           | H1              | P02/D2/AD2               |

| E2       | PL5/RXD9                     | F2       | PL7/TCOUTB1                          | G2            | P01/D1/AD1           | H2              | P03/D3/AD3               |

|          |                              |          |                                      |               |                      |                 |                          |

| E4       | PQ1/DACK2                    | F4       | PQ2/DREQ3                            | G4            | PK0/KEY0             | H4              | PK2/KEY2                 |

| E5       | DVSS                         | F5       | PQ3/DACK3                            | G5            | PK1/KEY1             | H5              | PK3/KEY3                 |

| E6       | TRST                         |          |                                      |               | _                    |                 |                          |

| E7       | TMS                          |          |                                      | G7            | DVSSC                | H7              | PK4/KEY4                 |

| E8       | PO7/TPD7                     |          |                                      | G8            | EJE                  | H8              | DVSSD                    |

| E9       | PO5/TPD5                     |          |                                      | G9            | DVCC33               | H9              | FVCC30                   |

| E10      | PO3/TPD3                     |          |                                      | G10           | DVCC34               | H10             | FVCC31                   |

| E11      | PO1/TPD1                     |          |                                      | G11           | DVCC34               | ) H11           | FVCC15                   |

| E12      | PJ7/SCK1                     |          |                                      | G12           | DVCC34               | √\H12           | DVCC15                   |

| E13      | PM7/TCOUTA1                  |          |                                      | G13           | DVCC32               | <i>)</i> ⊬13    | AVSS1                    |

| E14      | PM5/INT5                     |          |                                      | G14           | AVSS0                | H14             | P85/ANA13                |

| E15      | PM3/INT3                     |          |                                      |               |                      |                 |                          |

| E16      | PM1/INT1                     | F16      | P77/ANA7                             | G16           | P87/ANA15            | H16             | P84/ANA12                |

| E17      | PG2/SCLK2/CTS2               | F17      | P76/ANA6                             | G17           | P86/ANA14            | H17             | P83/ANA11                |

|          |                              |          |                                      |               |                      | (               |                          |

| E19      | PG1/RXD1                     | F19      | P75/ANA5                             | G19           | P73/ANA3             | H19 📈           | P71/ANA1                 |

| E20      | PG0/TXD2                     | F20      | P74/ANA4                             | G20           | P72/ANA2             | H20>            | P70/ANA0                 |

| J1       | P04/D4/AD4                   | K1       | P06/D6/AD6                           | L1 (/         | P10/D8/AD8/A8        | M1              | P12/D10/AD10/A10         |

| J2       | P05/D5/AD5                   | K2       | P07/D7/AD7                           | L2 (\         | P11/D9/AD9/A9        | M2 )            | P13/D11/AD11/A11         |

|          |                              |          |                                      |               |                      | 7               | $\langle \wedge \rangle$ |

| J4       | P50/A0                       | K4       | P52/A2                               | L4            | P54/A4               | M4              | P56/A6                   |

| J5       | P51/A1                       | K5       | P53/A3                               | L5            | P55/A5               | M5              | P57/A7                   |

|          |                              |          |                                      |               | . ((                 | \(\frac{1}{2}\) |                          |

| J7       | PK5/KEY5                     | K7       | PK6/KEY6                             | L7 \          | PK7/KEY7             | M7              | BW0                      |

| J8       | DVCC30                       | K8       | DVCC30                               | 8.1           | DVCC30               | ∠M8             | DVCC15                   |

| J9       | DVSS                         |          |                                      |               |                      | \               |                          |

|          |                              |          |                                      |               | \\/                  | )               |                          |

| J13      | AVCC30                       | K13      | AVREFH0                              | L13           | AVREFH1              | M13             | AVCC31                   |

| J14      | P82/ANA10                    | K14      | PA7/ANB15                            | ✓ L14 /       | PA4/ANB12            | M14             | DVCC15                   |

|          | D01/41140                    | 144.0    |                                      |               |                      |                 | D.4.//41/D.0             |

| J16      | P81/ANA9                     | K16      | PA6/ANB14                            | L16           | PA3/ANB11            | M16             | PA1/ANB9                 |

| J17      | P80/ANA8                     | K17      | PA5/ANB13                            | L17           | PA2/ANB10            | M17             | PA0/ANB8                 |

| 140      | DOZ/ANDZ                     | 1/40     | P95/ANB5                             | 140           | DO2/AND2             | MAG             | DO4/AND4                 |

| J19      | P97/ANB7                     | K19      |                                      | L19           | P93/ANB3             | M19             | P91/ANB1                 |

| J20      | P96/ANB6<br>P14/D12/AD12/A12 | K20      | P94/ANB4<br>P16/D14/AD14/A14         | L20           | P92/ANB2             | M20             | P90/ANB0                 |

| N1<br>N2 | P15/D13/AD13/A13             | P1<br>P2 | P16/D14/AD14/A14<br>P17/D15/AD15/A15 | R1<br>R2      | P40/*CS0<br>P41/*CS1 | T1<br>T2        | P42/*CS2<br>P43/*CS3     |

| INZ      | P15/D13/AD13/A13             | PZ/      | P17/D15/AD15/A15                     | RZ            | P41/ C31             | 12              | P43/ CS3                 |

| N4       | P30/*RD                      | R4       | P32/*HWR                             | R4            | P34/*BUSRQ           | T4              | P36/R/*W                 |

| N5       | P31/*WR                      | P5       | P33/*WAIT/*RDY                       | / R5          | P35/*BUSAK           | T5              | P61/A9                   |

| IND      | F31/ WK                      | PO       | P33/ WAIT/ RDT                       | // ٢٥)        | F33/ BUSAN           | T6              | P63/A11                  |

| N7       | BW1                          | P7       | TEST2                                |               |                      | T7              | P65/A13                  |

| N8       | TEST1                        | P8       | TEST3                                |               |                      | T8              | PN1/INT7                 |

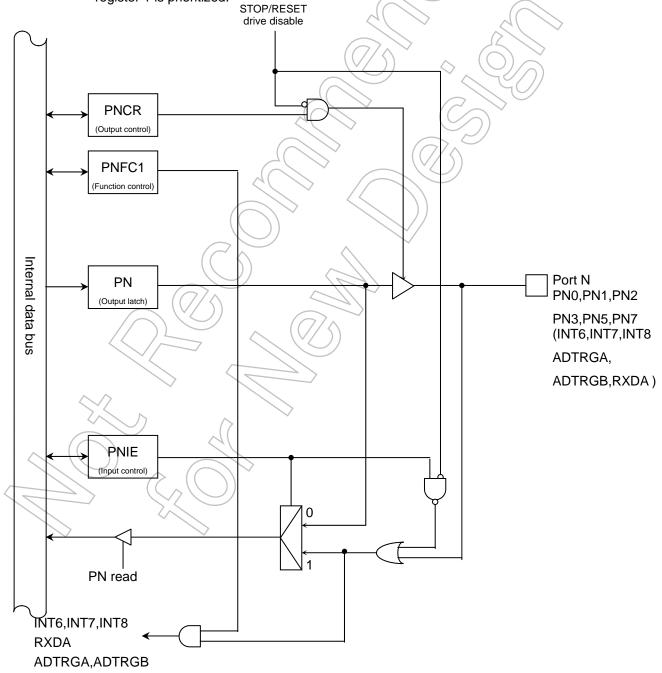

| N9       | BUSMD                        | P9       | ENDIAN                               | $\rightarrow$ |                      | T9              | PN3/ADTRG-A              |

| N10      | FVCC15 \                     | P10      | *NMI                                 |               |                      | T10             | PN5/RXDA                 |

| N11      | DVCC15                       | P11      | DVCC31                               |               |                      | T11             | PN7/ADTRG-B              |

| N12      | PLLSEL                       | ) P12    | DVCC31                               |               |                      | T12             | PH1/RXD4                 |

| N13      | DVSSF                        | P13      | CVSS                                 |               |                      | T13             | PH3/INT9                 |

| N14      | CVCC15                       | P14      | DVSS                                 |               |                      | T14             | PH5/RXD5                 |

| 1117     | 370019                       | 1 14     | 2100                                 |               |                      | T15             | PH7/INTA                 |

| N16      | PC7/TB0FIN1                  | P16      | PC5/TB0EIN1                          | R16           | PC3/TB0DIN1          | T16             | DVSSG                    |

| N17      | PC6/TB0FIN0                  | P17      | PC4/TB0EIN0                          | R17           | PC2/TB0DIN0          | T17             | PC1/TB0CIN1              |

| INI      | - COLLEGIAIAO                |          | - O-7/1-DOLINO                       | 13.17         | 1 OZ/ I DODINO       | 117             | 1 0 1/ 1 000 114 1       |

| N19      | PB7/TB0BIN1                  | P19      | PB5/TB0AIN1                          | R19           | PB3/TB9IN1           | T19             | PB1/TB8IN1               |

| N20      | PB6/TB0BIN0                  | P20      | PB4/TB0AIN0                          | R20           | PB2/TB9IN0           | T20             | PB0/TB8IN0               |

| IN∠U     | טאוומטפרו שם ד               | FZU 1    | 1 D4/ LDUAINU                        | NZU           | ו מצוווט וואט ו      | 120             | I DOLLOGINO              |

Table 2.1.1 Pin Names and Functions (2/3)

| PIN No. | PIN Name       | PIN No. | PIN Name    | PIN No. | PIN Name       | PIN No. | PIN Name       |

|---------|----------------|---------|-------------|---------|----------------|---------|----------------|

| U1      | P44/*CS4       | V1      | P46/SCOUT   | W1      | N.C(GND)       | Y1      | N.C(GND)       |

| U2      | P45/*CS5       | V2      | P47         | W2      | N.C(GND)       | Y2      | N.C(GND)       |

|         |                |         |             | W3      | P21/A17/A1/A17 | Y3      | P20/A16/A0/A16 |

| U4      | P37/ALE        |         |             | W4      | P23/A19/A3/A19 | Y4      | P22/A18/A2/A18 |

| U5      | P60/A8         |         |             | W5      | P25/A21/A5/A21 | Y5      | P24/A20/A4/A20 |

| U6      | P62/A10        |         |             | W6      | P27/A23/A7/A23 | ∠ Y6    | P26/A22/A6/A22 |

| U7      | P64/A12        |         |             | W7      | P67/A15        | YZ      | P66/A14        |

| U8      | PN0/INT6       |         |             | W8      | PI1/RXD6       | Y8      | PI0/TXD6       |

| U9      | PN2/INT8       |         |             | W9      | PI3/INTB       | (Y9     | PI2/SCLK6/CLS6 |

| U10     | PN4/TXDA       |         |             | W10     | PI5/RXD7       | Y10     | PI4/TXD7       |

| U11     | PN6/SCLKA/CTSA |         |             | W11     | PI7            | Y11_    | PI6/SCLK7/CTS7 |

| U12     | PH0/TXD4       |         |             | W12     | PE1/TB17OUT    | // Y12  | PE0/TB16OUT    |

| U13     | PH2/SCLK4/CTS4 |         |             | W13     | PE3/TB19OUT    | Y1/3    | PE2/TB18OUT    |

| U14     | PH4/TXD5       |         |             | W14     | PE5/SO0/SCA0   | Y14     | PE4/TB1AOUT    |

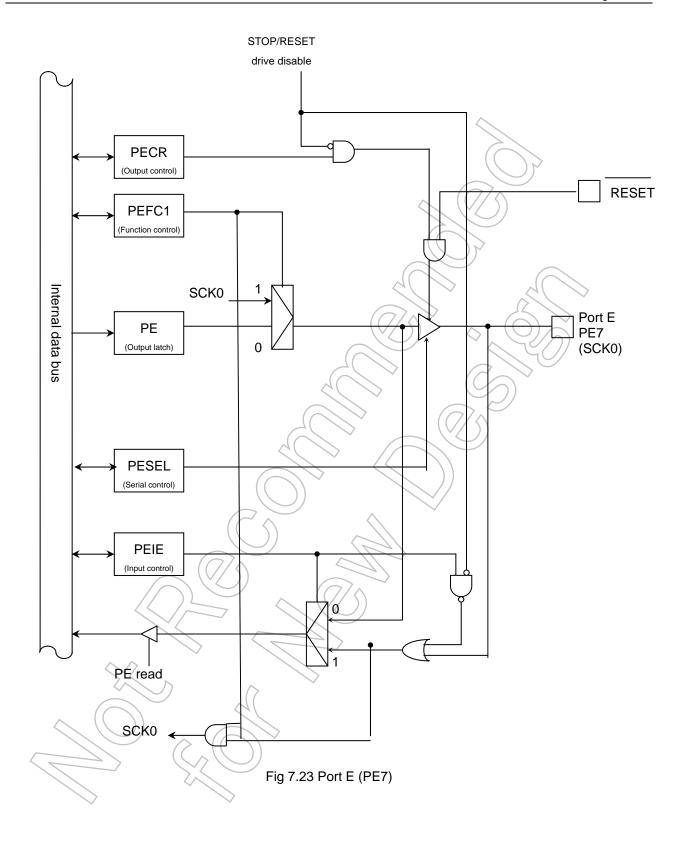

| U15     | PH6/SCLK5/CTS5 |         |             | W15     | PE7/SCK0       | Y15     | PE6/SI0/SCL0   |

| U16     | PD2/TB11IN0    |         |             | W16     | PD1/TB10IN1    | √ Y16   | PD0/TB10IN0    |

| U17     | DVSSH          |         |             | W17     | PD4/TB12IN0    | Y17     | PD3/TB11IN1    |

|         |                |         |             | W18     | PD6/TB14OUT    | Y18     | PD5/TB12IN1    |

| U19     | PC0/TB0CIN0    | V19     | PD7/TB15OUT | W19     | N.C(GND)       | Y19 /   | N.C(GND)       |

| U20     | X2             | V20     | X1          | W20     | N.C(GND)       | Y20 /   | N.C(GND)       |

Table 2.1.1 Pin Names and Functions (3/3)

## 2.3 Pin Names and Functions

Tables 2.3 show the names and functions of input and output pins.

Table 2.3 Pin Names and Functions (1/8)

| Pin name | No. of pins | Input or output | Function                                                                                         |

|----------|-------------|-----------------|--------------------------------------------------------------------------------------------------|

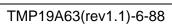

| P00~P07  | 8           | Input/output    | Port 0: Input/output port that allows input/output to be set in units of bits                    |

| D0~D7    |             | Input/output    | Data (lower): Data bus 0~7 (separate bus mode)                                                   |

| AD0~D7   |             | Input/output    | Address data (lower): Address data bus 0~7 (multiplexed bus mode)                                |

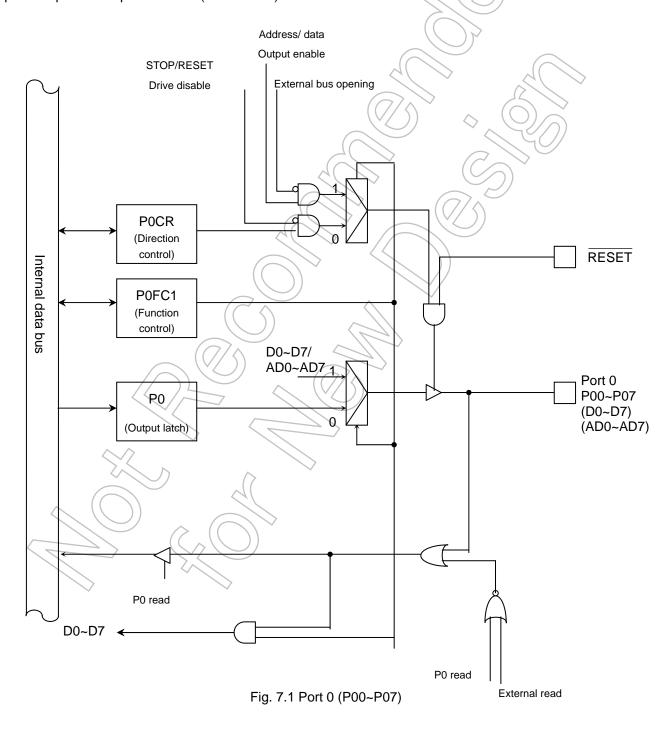

| P10~P17  | 8           | Input/output    | Port 1: Input/output port that allows input/output to be set in units of bits                    |

| D8~D15   |             | Input/output    | Data (upper): Data bus 8~15: (separate bus mode)                                                 |

| AD8~AD15 |             | Input/output    | Address data (upper): Address data bus 8~15 (multiplexed bus mode)                               |

| A8~A15   |             | Output          | Address: Address bus 8~15 (multiplexed bus mode)                                                 |

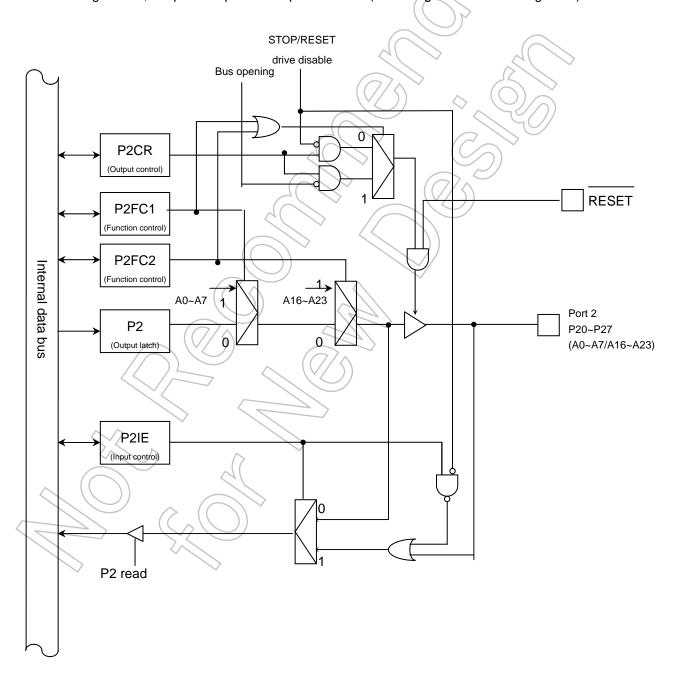

| P20~P27  | 8           | Input/output    | Port 2: Input/output port that allows input/output to be set in units of bits                    |

| A16~A23  |             | Output          | Address: Address bus 16~23 (separate bus mode)                                                   |

| A0~A7    |             | Output          | Address: Address bus 0~7 (multiplexed bus mode)                                                  |

| A16~A23  |             | Output          | Address: Address bus 16~23 (multiplexed bus mode)                                                |

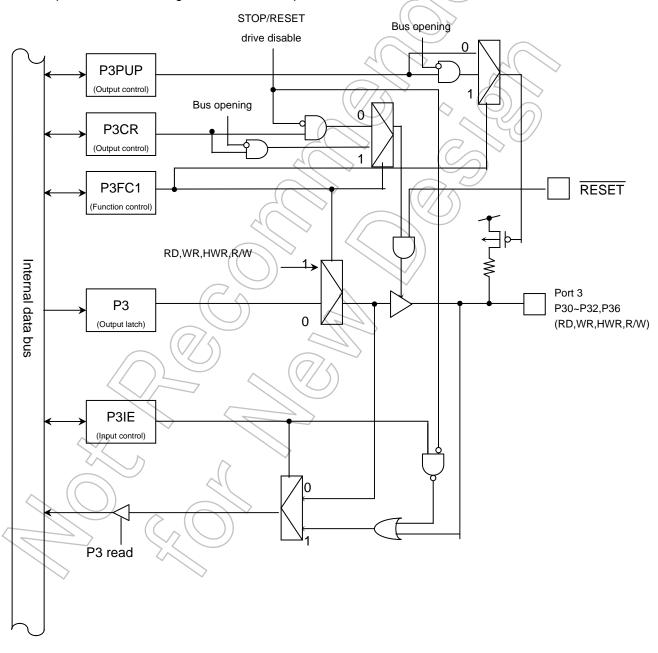

| P30      | 1           | Input/output    | Port 30:Input/output port (with pull-up)                                                         |

| *RD      |             | Output          | Read: Strobe signal for reading external memory                                                  |

| P31      | 1           | Input/output    | Port 31:Input/output port (with pull-up)                                                         |

| *WR      |             | Output          | Write: Strobe signal for writing data of D0 to D7 pins                                           |

| P32      | 1           | Input/output    | Port 32:Input/output port (with pull-up)                                                         |

| *HWR     |             | Output          | Write upper-pin data: Strobe signal for writing data of D8 to D15 pins                           |

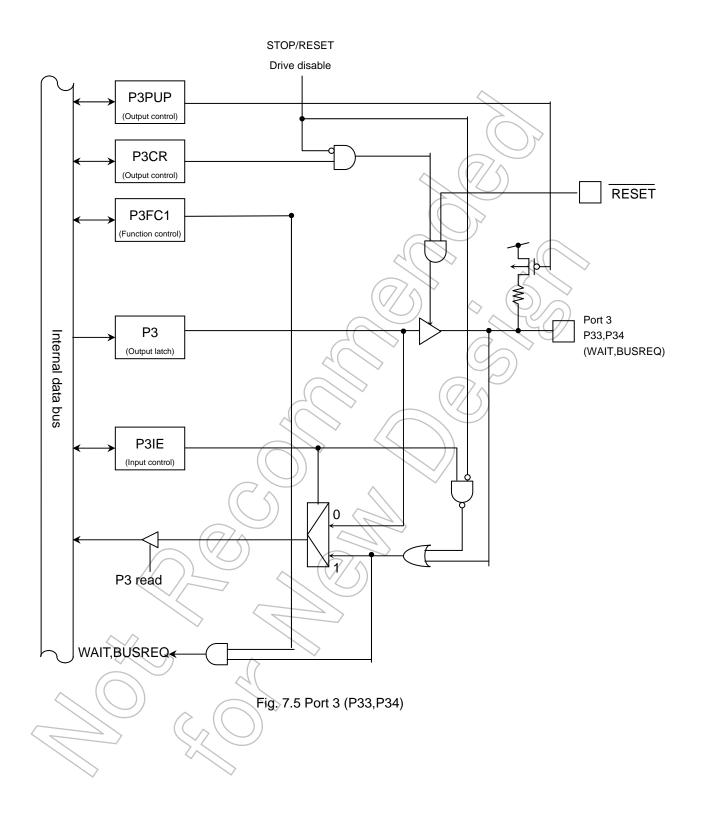

| P33      | 1           | Input/output    | Port 33:Input/output port (with pull-up)                                                         |

| *WAIT    |             | Input           | Wait: Pin for requesting CPU to put a bus in a wait state                                        |

| *RDY     |             | Input           | Ready: Pin for notifying CPU that a bus is ready                                                 |

| P34      | 1           | Input/output    | Port 34:Input/output port (with pull-up)                                                         |

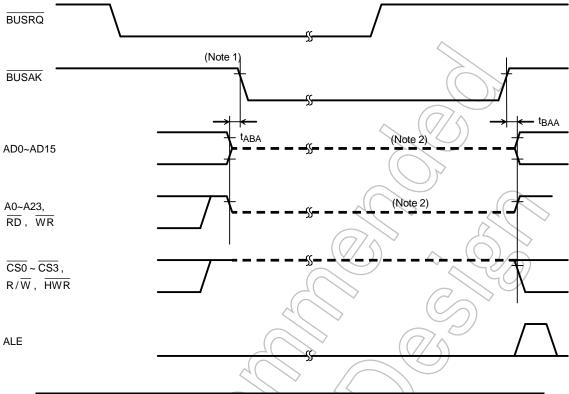

| *BUSRQ   |             | Input           | Bus request: Signal requesting CPU to allow an external master to take the bus control authority |

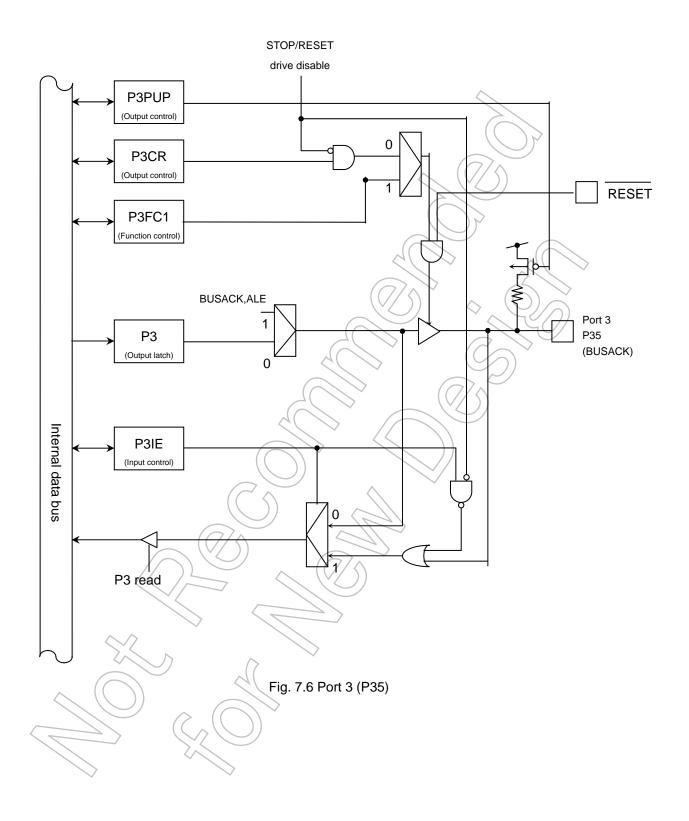

| P35      | 1           | Input/output    | Port 35:Input/output port (with pull-up)                                                         |

| *BUSAK   |             | Output          | Bus acknowledge: Signal notifying that CPU has released the bus control authority in response    |

| 200/     |             | o a.pa.         | to *BUSREQ                                                                                       |

| P36      | 1           | Input/output    | Port 36:Input/output port (with pull-up)                                                         |

| R/*W     |             | Output          | Read/write: "1" shows a read cycle or a dummy cycle. "0" shows a write cycle.                    |

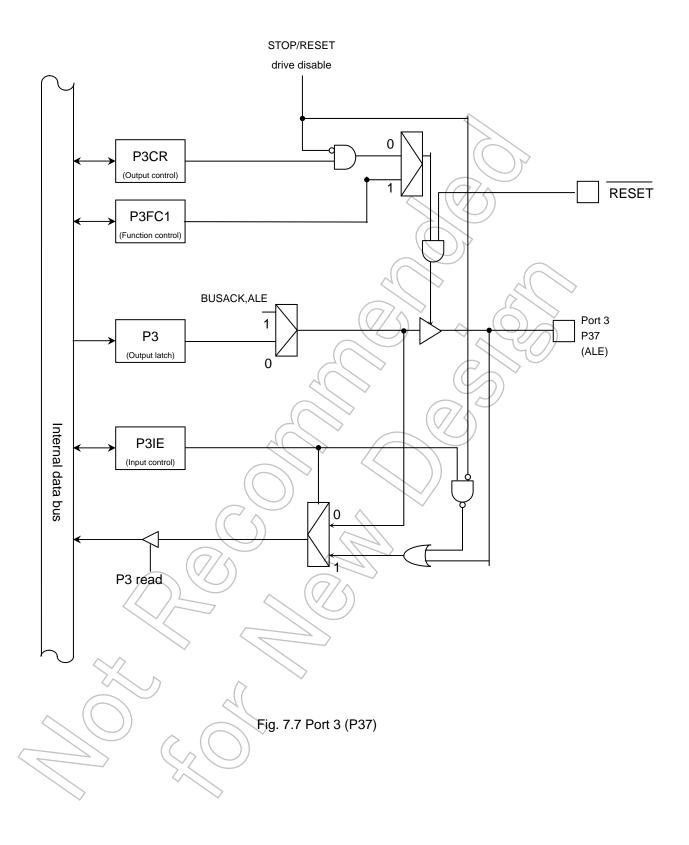

| P37      | 1           | Input/output    | Port 37:: Input/output port                                                                      |

| ALE      |             | Output          | Address latch enable (address latch is enabled only if access to external memory is taking       |

|          |             | 1               | place, that is multiplex bus mode)                                                               |

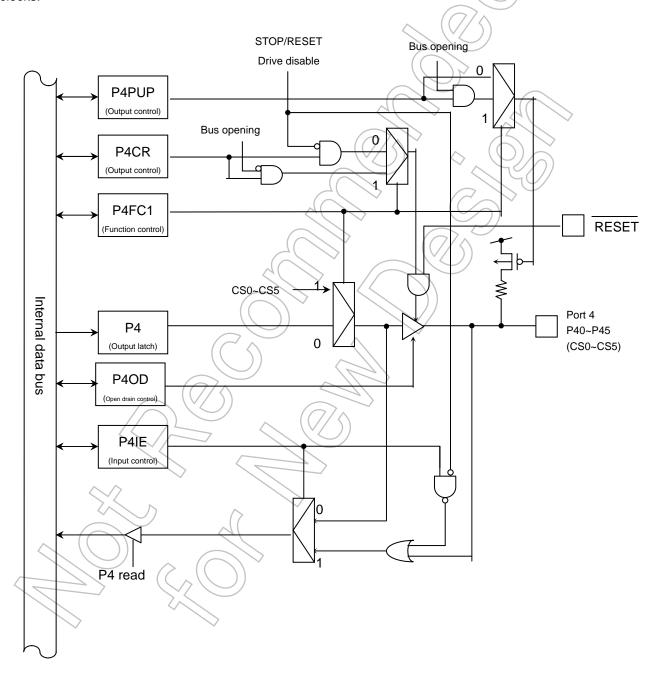

| P40      | 1           | Input/output    | Port 40:Input/output port (with pull-up)                                                         |

| *CS0     | ^ ^         | Output          | Chip select 0:"0" is output if the address is in a designated address area.                      |

| P41      | 7.<         | Input/output    | Port 41:Input/output port (with pull-up)                                                         |

| *CS1     |             | Output          | Chip select 1:"0" is output if the address is in a designated address area.                      |

| P42      | 1           | Input/output    | Port 42:Input/output port (with pull-up)                                                         |

| *CS2     |             | Output          | Chip select 2:"0" is output if the address is in a designated address area.                      |

| P43      |             | Input/output    | Port 43:Input/output port (with pull-up)                                                         |

| *CS3     |             | Output          | Chip select 3:"0" is output if the address is in a designated address area.                      |

| P44      | 1           | Input/output    | Port 44:Input/output port (with pull-up)                                                         |

| *CS4     |             | Output          | Chip select 4:"0" is output if the address is in a designated address area.                      |

| P45      | 1           | Input/output    | Port 45:Input/output port (with pull-up)                                                         |

| *CS5     |             | Output          | Chip select 5:"0" is output if the address is in a designated address area.                      |

Table 2.3 Pin Names and Functions (2/8)

| Pin name                 | No. of pins | Input or output                | Function                                                                                                                                                                                                          |

|--------------------------|-------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

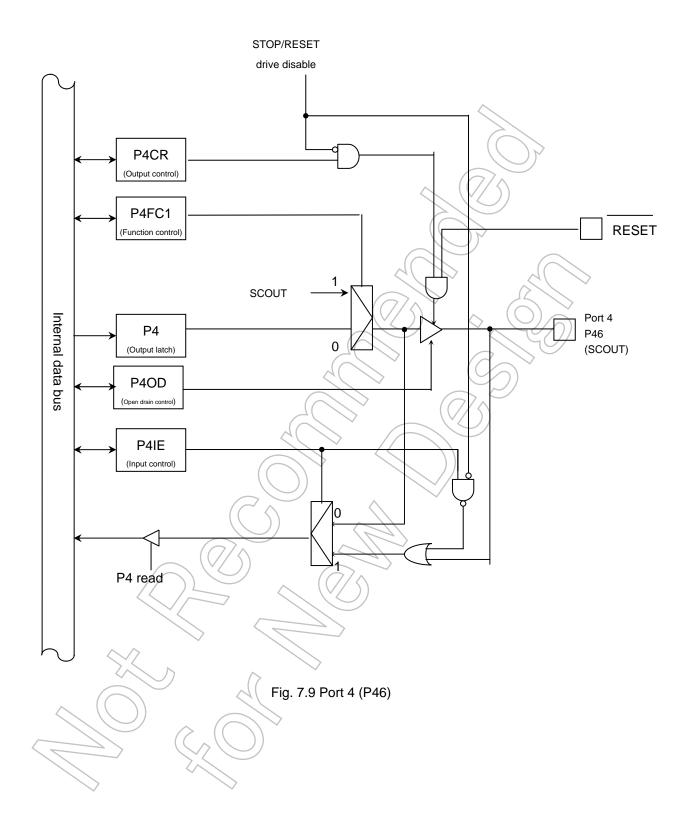

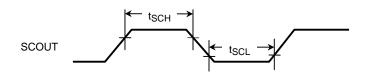

| P46<br>SCOUT             | 1           | Input/output<br>Output         | Port 46: Input/output port System clock output: Selectable between high- and low-speed clock outputs, as in the case of CPU                                                                                       |

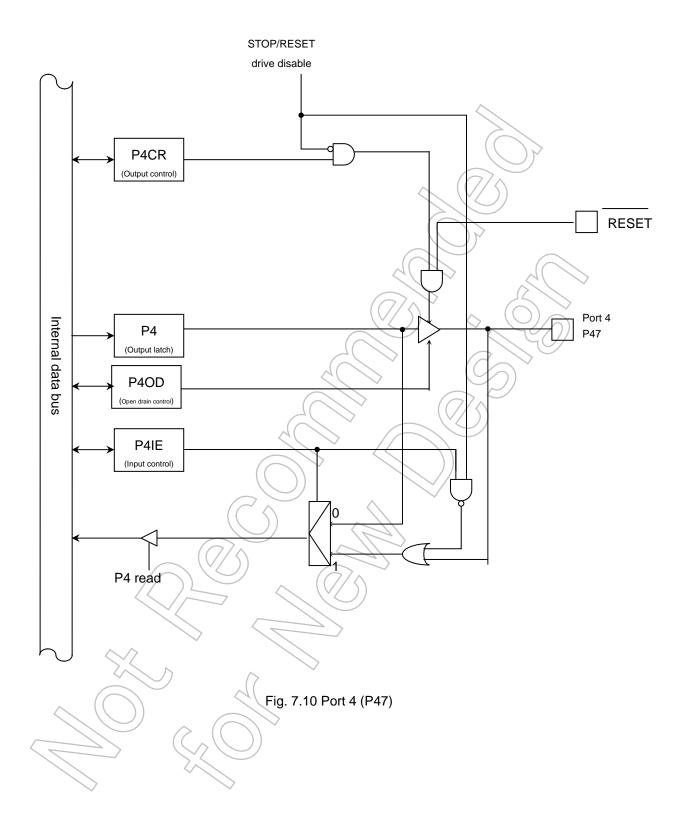

| P47                      | 1           | Input/output                   | Port 47: Input/output port                                                                                                                                                                                        |

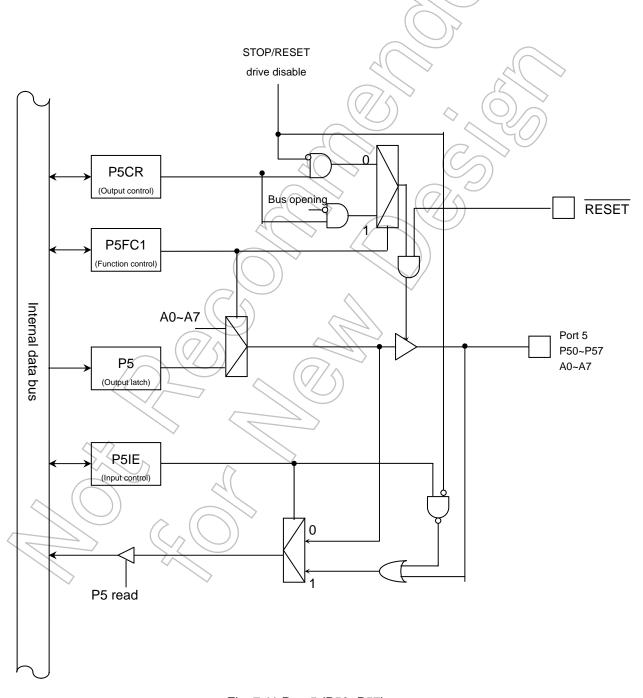

| P50~P57<br>A0~A7         | 8           | Input/output Output            | Port 5: Input/output port that allows input/output to be set in units of bits Address: Address bus 0~7 (separate bus mode)                                                                                        |

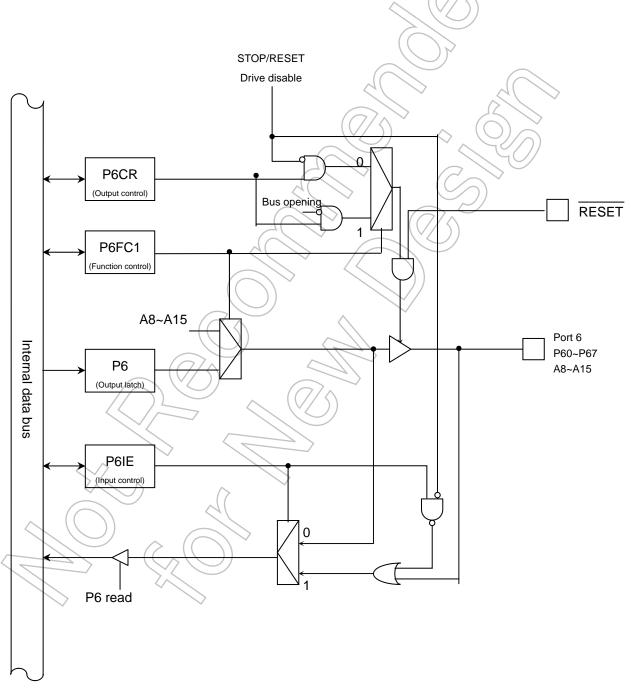

| P60~P67<br>A8~A15        | 1           | Input/output Output            | Port 60 ~67 :Input/output port Address: Address bus 4 (separate bus mode)                                                                                                                                         |

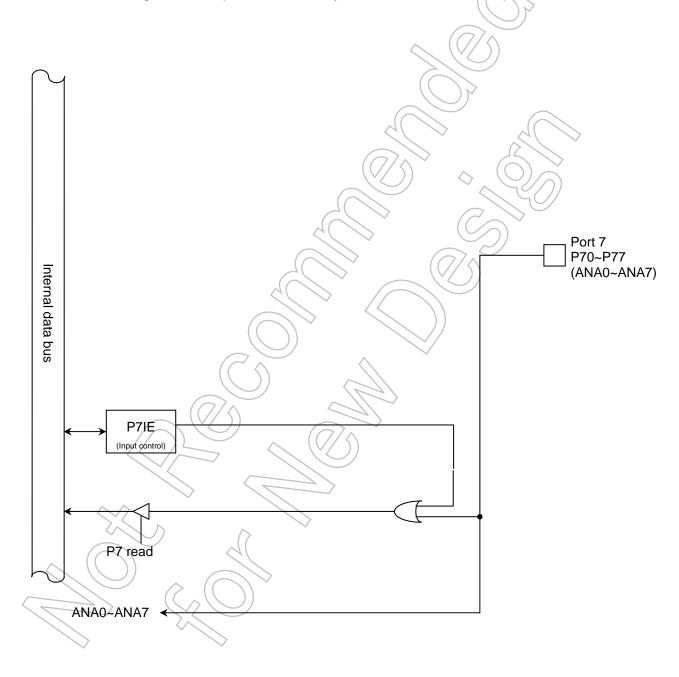

| P70~P77<br>ANA0~ANA7     | 8           | Input<br>Input                 | Port 7:Port used exclusively for input Analog input: Input from A/D converter                                                                                                                                     |

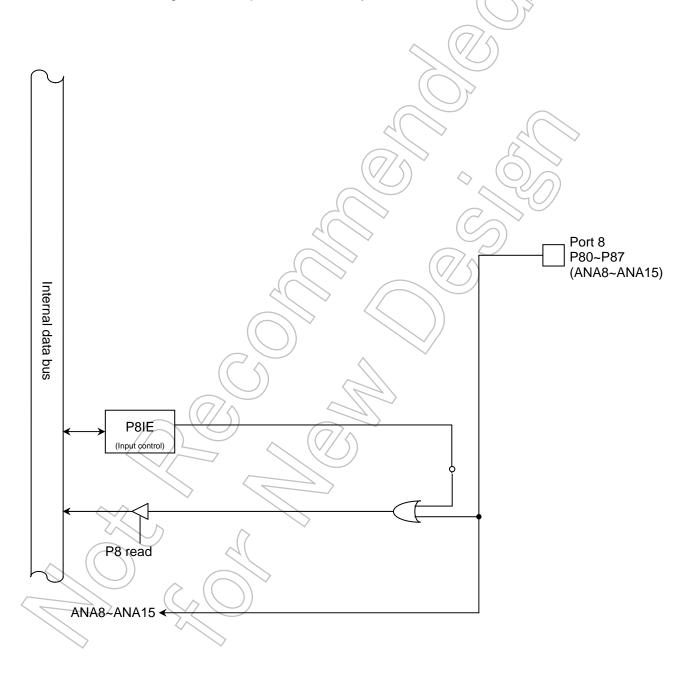

| P80~P87<br>ANA8~ANA15    | 8           | Input<br>Input                 | Port 8:Port used exclusively for input Analog input: Input from A/D converter                                                                                                                                     |

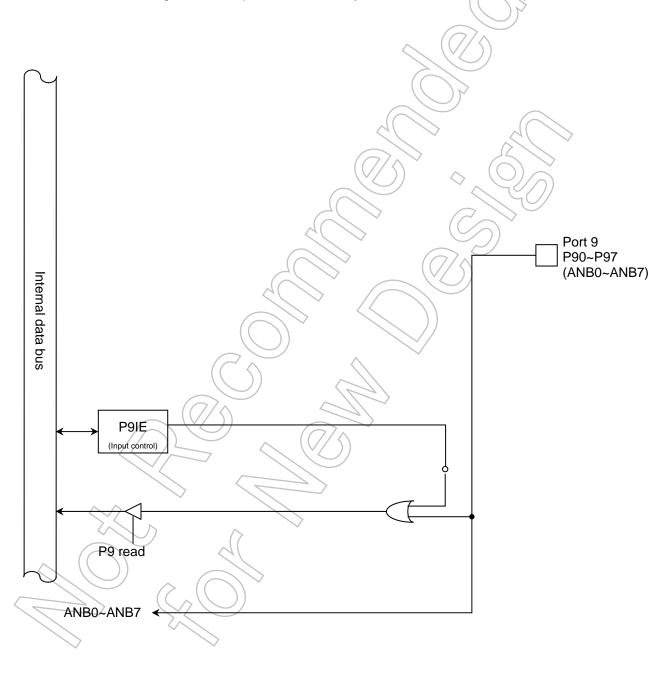

| P90~P97<br>ANB0~ANB7     | 8           | Input                          | Port 9:Port used exclusively for input Analog input: Input from A/D converter                                                                                                                                     |

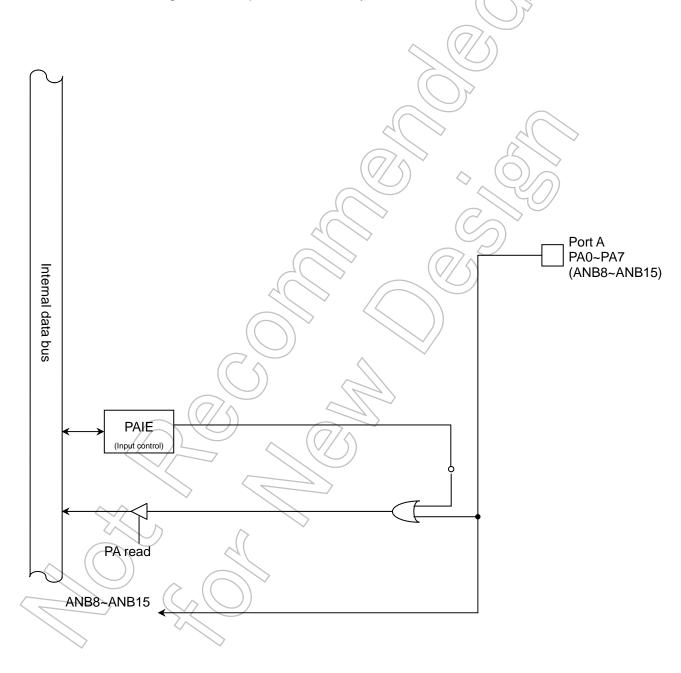

| PA0~PA7                  | 8           | Input<br>Input                 | Port A: Port used exclusively for input                                                                                                                                                                           |

| ANB8~ANB15<br>PB0        | 1           | Input<br>Input/output          | Analog input: Input from A/D converter  Port B0:Input/output port                                                                                                                                                 |

| TB8IN0<br>PB1            | 1           | Input<br>Input/output          | 16-bit timer 8 input 0:For inputting the capture trigger of a 16-bit timer 8  Port B1:Input/output port                                                                                                           |

| TB8IN1<br>PB2            | 1           | Input<br>Input/output          | 16-bit timer 8 input 1:For inputting the capture trigger of a 16-bit timer 8  Port B2:Input/output port                                                                                                           |

| TB9IN0<br>PB3            | 1           | Input Input/output             | 16-bit timer 9 input 0:For inputting the capture trigger of a 16-bit timer 9  Port B3:Input/output port                                                                                                           |

| TB9IN1<br>PB4            | 1           | Input Input/output             | 16-bit timer 9 input 1:For inputting the capture trigger of a 16-bit timer 9  Port B4:Input/output port                                                                                                           |

| TBAIN0<br>PB5            | 1           | Input Input/output             | 16-bit timer A input 0:For inputting the capture frigger of a 16-bit timer A  Port B5:Input/output port                                                                                                           |

| TBAIN1<br>PB6            | 1           | Input Input/output             | 16-bit timer A input 1:For inputting the capture trigger of a 16-bit timer A  Port B6:Input/output port                                                                                                           |

| TBBIN0<br>PB7            | 1           | Input Input/output             | Port B7:Input/output port                                                                                                                                                                                         |

| TBBIN1<br>PC0<br>TBCIN0  | 1 <         | Input<br>Input/output<br>Input | 16-bit timer B input 1:For inputting the capture trigger of a 16-bit timer B  Port C0:Input/output port  16-bit timer C input 0:For inputting the capture trigger of a 16-bit timer C/Two-phase counter input pin |

| PC1<br>TBCIN1            | 1/2         | Input/output<br>Input          | Port C1:Input/output port  16-bit timer C input 1:For inputting the capture trigger of a 16-bit timer C/Two-phase counter input pin                                                                               |

| PC2<br>TBDINO            |             | Input/output<br>Input          | Port C2:Input/output port 16-bit timer D input 0:For inputting the capture trigger of a 16-bit timer D                                                                                                            |

| PC3<br>TBDIN1            | 7           | Input/output<br>Input          | Port C3:Input/output port 16-bit timer D input 1:For inputting the capture trigger of a 16-bit timer D                                                                                                            |

| PC4<br>TBEIN0            | 1           | Input/output                   | Port C4:Input/output port  16-bit timer E input 0:For inputting the capture trigger of a 16-bit timer E                                                                                                           |

| PC5<br>TBEIN1            | 1           | Input/output Input             | Port C5:Input/output port  16-bit timer E input 1:For inputting the capture trigger of a 16-bit timer E                                                                                                           |

| PC6<br>TBFIN0            | 1           | Input/output Input             | Port C6:Input/output port  16-bit timer F input 0:For inputting the capture trigger of a 16-bit timer F                                                                                                           |

| PC7                      | 1           | Input/output                   | Port C7:Input/output port                                                                                                                                                                                         |

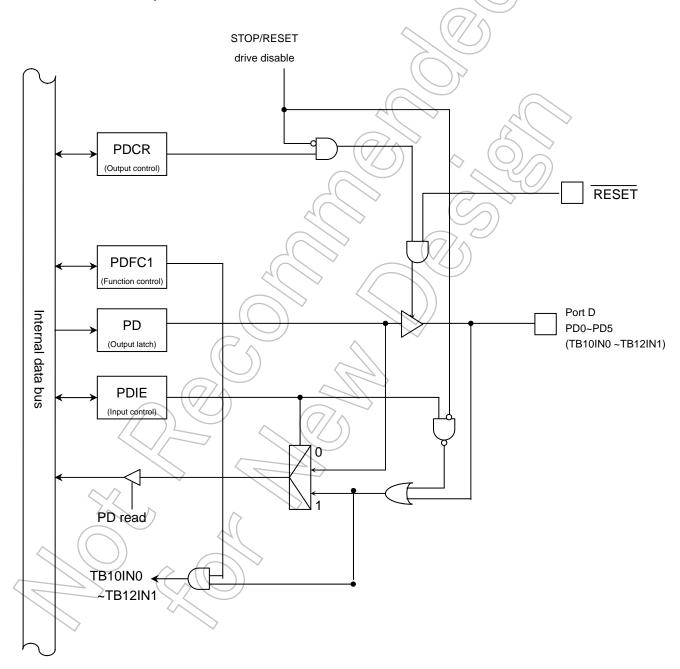

| TBFIN1<br>PD0<br>TB10IN0 | 1           | Input Input/output Input       | 16-bit timer F input 1:For inputting the capture trigger of a 16-bit timer 10  Port D0:Input/output port  16-bit timer 10 input 0:For inputting the capture trigger of a 16-bit timer 10                          |

Table 2.3 Pin Names and Functions (3/8)

| Pin name | No. of pins                                        | Input or output | Function                                                                                                    |

|----------|----------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------|

| PD1      | 1                                                  | Input/output    | Port D1:Input/output port                                                                                   |

| TB10IN1  |                                                    | Input           | 16-bit timer 10 input 1:For inputting the capture trigger of a 16-bit timer 10                              |

| PD2      | 1                                                  | Input/output    | Port D2:Input/output port                                                                                   |

| TB11IN0  |                                                    | Input           | 16-bit timer 11 input 0:For inputting the capture trigger of a 16-bit timer 11                              |

| PD3      | 1                                                  | Input/output    | Port D3:Input/output port                                                                                   |

| TB11IN1  |                                                    | Input           | 16-bit timer 11 input 1:For inputting the capture trigger of a 16-bit timer 11                              |

| PD4      | 1                                                  | Input/output    | Port D4:Input/output port                                                                                   |

| TB12IN0  |                                                    | Input           | 16-bit timer 12 input 0:For inputting the capture trigger of a 16-bit timer 12 /Two-phase counter input pin |

| PD5      | 1                                                  | Input/output    | Port D5:Input/output port                                                                                   |

| TB12IN1  |                                                    | Input           | 16-bit timer 12 input 1:For inputting the capture trigger of a 16-bit timer 12 /Two-phase                   |

|          |                                                    |                 | counter input pin                                                                                           |

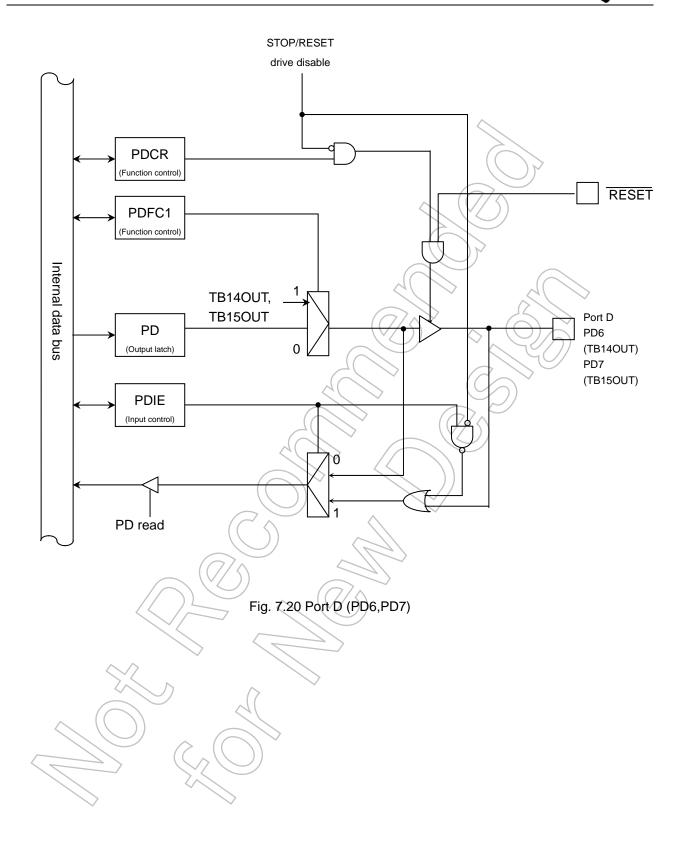

| PD6      | 1                                                  | Input/output    | Port D6:Input/output port                                                                                   |

| TB14OUT  |                                                    | Output          | 16-bit timer 14 output :16bit timer 14 variable PPG output                                                  |

| PD7      | 1                                                  | Input/output    | Port D7:Input/output port                                                                                   |

| TB15OUT  |                                                    | Output          | 16-bit timer 15 output :16bit timer 15 variable PPG output                                                  |

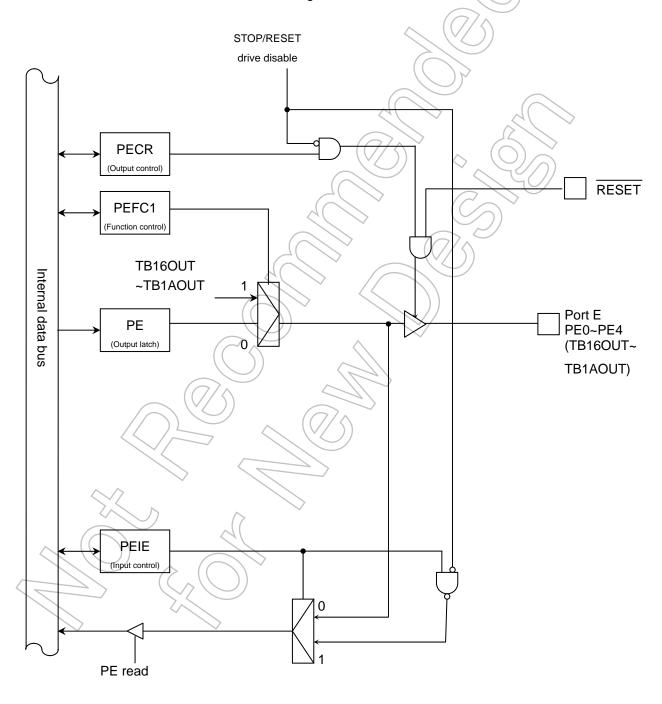

| PE0      | 1                                                  | Input/output    | Port E0:Input/output port                                                                                   |

| TB16OUT  |                                                    | Output          | 16-bit timer 16 output :16bit timer 16 variable PPG output                                                  |

| PE1      | 1                                                  | Input/output    | Port E1:Input/output port                                                                                   |

| TB17OUT  |                                                    | Output          | 16-bit timer 17 output :16bit timer 17 variable PPG output                                                  |

| PE2      | 1                                                  | Input/output    | Port E2:Input/output-port                                                                                   |

| TB18OUT  |                                                    | Output          | 16-bit timer 18 output :16bit timer 18 variable PPG output                                                  |

| PE3      | 1                                                  | Input/output    | Port E3:Input/output port                                                                                   |

| TB19OUT  |                                                    | Output          | 16-bit timer 19 output :16bit timer 19 variable PPG output                                                  |

| PE4      | 1                                                  | Input/output    | Port E4:Input/output port                                                                                   |

| TB1AOUT  |                                                    | Output          | 16-bit timer 1A output :16bit timer 1A variable PPG output                                                  |

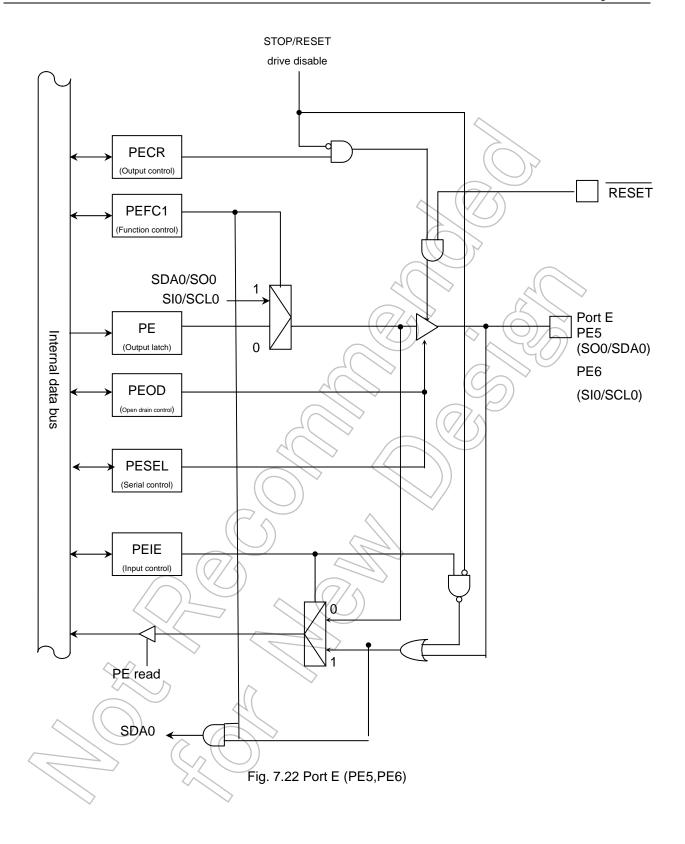

| PE5      | 1                                                  | Input/output    | Port E5:Input/output port                                                                                   |

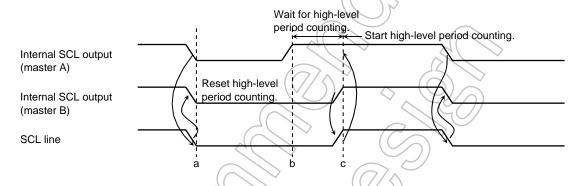

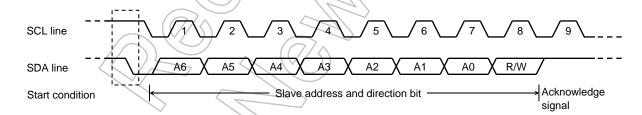

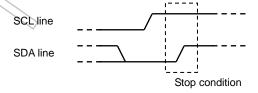

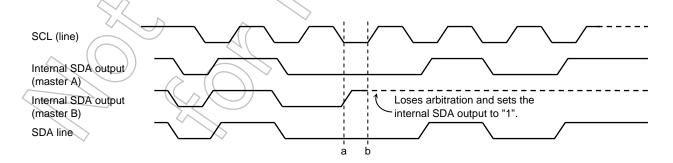

| SO0      |                                                    | Output          | Pin for sending data if the serial bus interface operates in the SIO mode                                   |