# Basic Characteristics and Application Circuit Design of Transistor Couplers

### Outline

This document outlines the basic characteristics and application design of general-purpose transistor output photocouplers (optical isolators).

| Contents                                                               |

|------------------------------------------------------------------------|

| 1. Basic Characteristics ····································          |

| 1-1. Current Transfer Ratio (CTR) ···································· |

| (1)CTR degradation                                                     |

| (2)CTR - I <sub>F</sub> dependency                                     |

| (3)CTR - Ta dependency                                                 |

| (4) CTR-V <sub>CE</sub> dependency                                     |

| 1-2. Switching Time                                                    |

| 2. How to Use Transistor Couplers                                      |

| 2–1. LED Control Circuits                                              |

| 2-1-1. DC drive                                                        |

| 2-1-2. Reverse Voltage Protection                                      |

| 2-1-3. Threshold Voltage                                               |

| 2-1-4. Driving by Transistor or IC                                     |

| 2-1-5. AC Drive                                                        |

| 2-2. Examples of Application to Signal Transmission8                   |

| 2-3. Transistor Coupler Circuit Design for Signal Transmission9        |

| 2-4. Design Example for Interface Circuit Using Transistor Coupler     |

| 2-4-1. Setting of Forward Current I <sub>F</sub>                       |

| 2-4-2. Setting of the $I_F$ Limiting Resistance $R_D$                  |

| 2-4-3. Setting of Pull-up Resistance R <sub>C</sub> (max)              |

| 2-4-4. Setting of Pull-up Resistance R <sub>C</sub>                    |

| 3.Terms                                                                |

Photocouplers optically links, via transparent isolating material, a light emitter and a photodetector. Used as an interface between circuits with different ground potentials, photocouplers replace isolation transformers and electromagnetic relays. Traditionally, relays or transformers have been used for isolation interfaces between logic circuits and power line load circuits. Photocouplers not only replace these devices, but also have merits such as elimination of impedance mismatching, improvement in isolation capability between input and output, and ease of noise cutoff. Moreover, while circuits nowadays consist of many more LSIs and microcomputers than before, additional merits of photocouplers include reduction in the area occupied on the printed circuit board, and maintenance-free operation due to improvement in reliability. This section outlines the basic characteristics and application design of general-purpose transistor output photocouplers (optical isolators).

### 1. Basic Characteristics

### 1-1. Current Transfer Ratio (CTR)

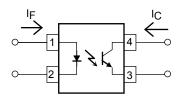

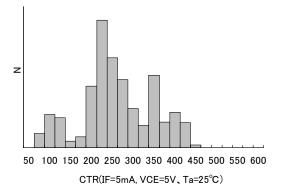

Figure 1.1 shows the pin configuration of TLP785. CTR is defined as the ratio  $I_C/I_F$  (expressed as a percentage) of the output-side transistor collector current  $I_C$  to the current  $I_F$  flowing in the input-side LED. Figure 1.2 shows the CTR distribution for TLP785. CTR varies with  $I_F$ . At standard conditions of  $I_F$  = 5 mA and  $V_{CE}$  = 5 V, CTR is designed to be between 50% to 600%.

CTR =  $100 \times I_C / I_F$  [%]

### Figure 1.1 Pin Configuration of TLP785

When using transistor couplers, it is necessary to pay particular attention to the following. The section 2-4 shows the example of circuit design for transistor couplers.

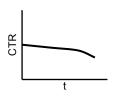

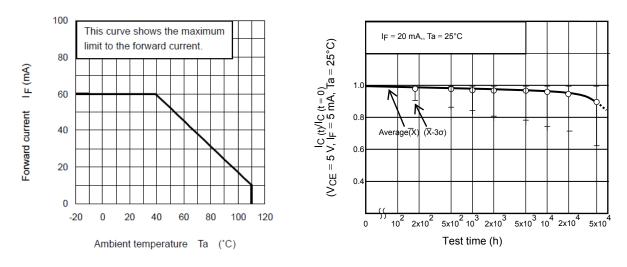

### (1)CTR degradation

Light output of the LED in the photocoupler decreases gradually over time, contributing to CTR degradation. It is, therefore, advisable to provide a design margin to offset this anticipated CTR degradation.

### (2)CTR - I<sub>F</sub> dependency

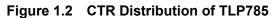

When a transistor coupler is used with low input current, its CTR drops as shown in Figure 1.3. This effect should also be considered during circuit design.

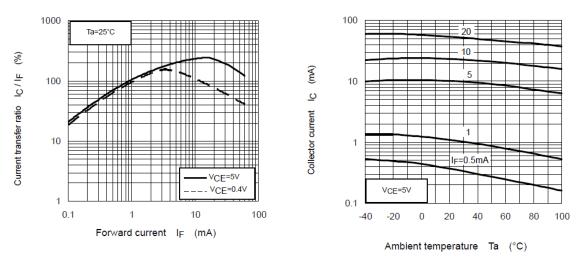

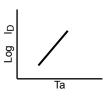

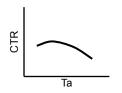

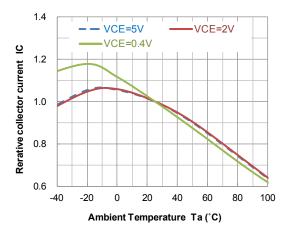

### (3)CTR - Ta dependency

At high temperatures, the decrease in LED light emission efficiency is dominant over the increase in  $h_{FE}$ , resulting in a reduction of the CTR. Attention should also be paid to this effect during circuit design.(Figure 1.4)

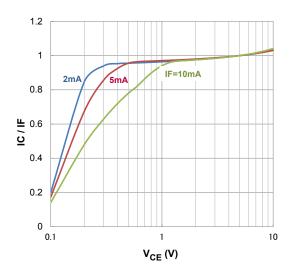

### (4) CTR-V<sub>CE</sub> dependency

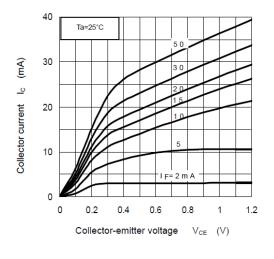

As with hFE of general transistors, the rate of change of collector current decreases at saturation. (Figure 1.5)

Figure 1.5 I<sub>C</sub> -V<sub>CE</sub>

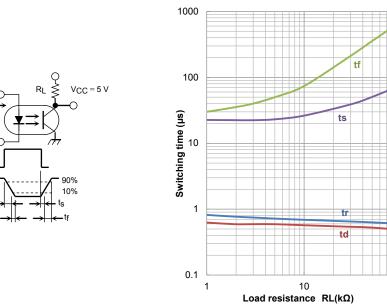

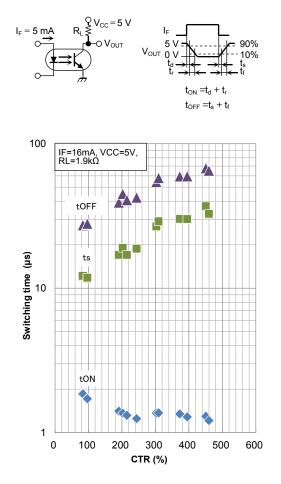

### 1-2. Switching Time

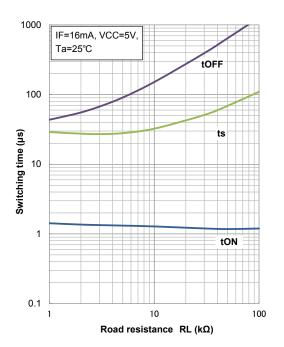

When the phototransistor is used in a saturated switching mode, the switching time must be considered. Among a phototransistor's switching time characteristics, fall time (tf), being the longest in duration, is the most significant. It is represented approximately by

tf to 2.2  $\times$  Cob  $\times$  hFE  $\times$  RL.

Where,

Cob: collector-to-base capacitance

5 mA

hFE: DC current gain

RL: load resistance

Switching time of TLP785 is shown in Figure 1.6. Thus, if an application requires a response speed of 1 kbit/s and above, the design must take into account the transistor coupler's  $R_L$  dependency.

Switching time (saturation, representative sample)

Switching Time - RL Figure 1.6

100

### 2. How to Use Transistor Couplers

### 2-1. LED Control Circuits

### 2-1-1. DC drive

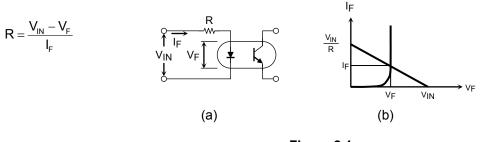

Figure 2.1(a) shows an example of controlling LED drive current by switching the supply voltage  $V_{\text{IN}}$  on and off.

Figure 2.1(b) indicates a load line in the (a) circuit.

In this case, the resistor R is as follows.

Figure 2.1

For example, when I<sub>F</sub> = 10 mA, V<sub>F (max)</sub> = 1.35 V, and V<sub>IN</sub> = 5 V,

$$R = \frac{(5 - 1.35) V}{10 mA} = 365 \Omega$$

Therefore, the resistor should be selected as R = 360  $\Omega$ . In the case where V<sub>F</sub> = 0.9 V due to the variation in different samples or the influence of operating temperature, the value of I<sub>F</sub> is 11.4 mA.

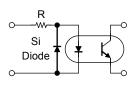

### 2-1-2. Reverse Voltage Protection

To prevent a reverse surge voltage in the LED, a Si diode (for example, 1SS352) should be connected in reverse parallel with the LED, as shown in Figure 2.2, so that the reverse surge voltage bypasses the LED.

Figure 2.2

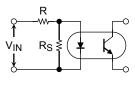

#### 2-1-3. Threshold Voltage

When the input voltage  $V_{IN}$  is not absolutely zero or some unnecessary current flow is in the data transmission line, the threshold voltage of the LED should be raised up to a certain level by connecting a resistor in parallel with the light-emitting diode. (Figure 2.3)

Figure 2.3

If the forward voltage of the LED in the zero-light-emission state V<sub>T</sub>, the OFF-level input voltage V<sub>IN (OFF)</sub>, and the OFF-level input current I<sub>IN (OFF)</sub> are given as follows.

$$\begin{split} V_{\text{IN(OFF)}} &\simeq V_{\text{T}} + R \cdot \frac{V_{\text{T}}}{R_{\text{S}}} = \left(1 + \frac{R}{R_{\text{S}}}\right) V_{\text{T}} \\ I_{\text{IN(OFF)}} &\simeq \frac{V_{\text{T}}}{R_{\text{S}}} \end{split}$$

In the case of the Toshiba infrared LED for transistor couplers), the value of V<sub>T</sub> is 0.5 V.

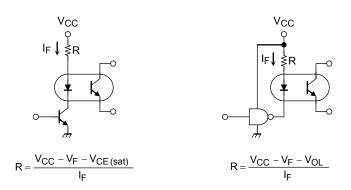

#### 2-1-4. Driving by Transistor or IC

Figure 2.4 shows examples of LED drive circuits controlled by (a) a transistor and (a) an IC.

(a) LED Drive Circuit Controlled by a Transistor (b) LED Drive Circuit Controlled by an IC

Figure 2.4

#### 2-1-5. AC Drive

In this case, a bridge rectifier is used as shown in Figure 2.5.

Figure 2.5

### 2-2. Examples of Application to Signal Transmission

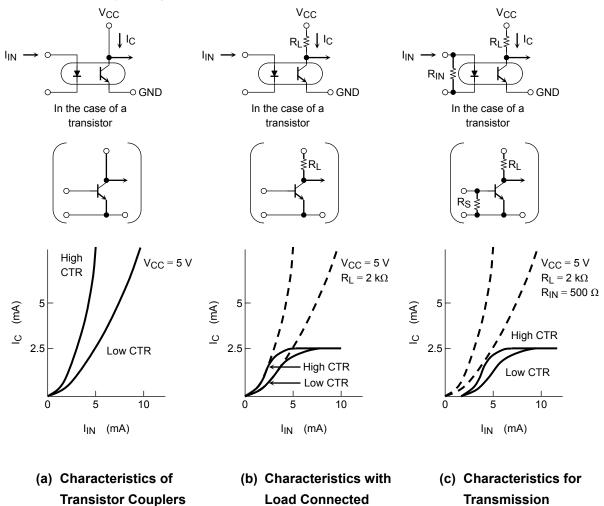

Transistor couplers which have high photosensitivity and high current-transfer ratios are effective as interfaces for signal transmission. However, transmission lines are generally subjected to all kinds of noises, and it is therefore necessary to take countermeasures against these noises at the receiving side. In many cases, transistor couplers designed in a circuit similar to that shown in Figure 2.6 (b). However, this circuit design is vulnerable to certain kinds of interference in signal transmission. While common-mode noise do not pose a problem because of the isolation characteristics of transistor couplers, no measures have been taken against differential noise. Figure 2.6 (c) is an example of a circuit useful for eliminating differential noise. This circuit is the same as that of general-purpose transistors, with the addition of a resistor inserted between the base and the emitter.

High CTR transistor couplers are more effective in signal transmission applications. It can be seen from the graph that for a high CTR product, the cut-off area and the saturation area are closer than that of a low-CTR product. Because of this, it is possible to specify the threshold output voltage level with sufficient margin to allow for ease and flexibility in design. This circuit is recommended for that purpose.

Figure 2.6 Load Characteristics of Transistor Couplers

### 2-3. Transistor Coupler Circuit Design for Signal Transmission

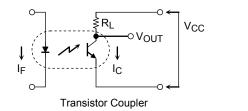

Figure 2.7 shows a basic transistor coupler interface circuit, where collector current  $I_C$  flows on the output side as LED current  $I_F$  is applied on the input side.

The following points are important in determining the values of the various parameters in the circuit:

(1)  $I_{IN} = I_F = 0$  (OFF state)

Only a dark current  $I_D(I_{CEO})$  flow at the output transistor in this state. In order to maintain the OFF state, the output voltage  $V_{OUT (OFF)}$  should be higher than  $V_H$  (the required high level voltage) as follows:

$V_{CC} - I_D \times R_L = V_{OUT (OFF)} > V_H$

Where, V<sub>CC</sub>: Applied voltage (supply voltage)

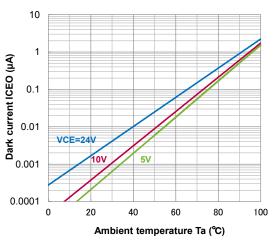

The leakage current ID increases as the ambient temperature rises (see Figure 2.8  $I_D$  vs. Ta), so the  $I_D$  value will have to be considered at the worst case, here being the maximum operating temperature.

As such, the value of  $\mathsf{R}_{\mathsf{L}}$  should meet the following formula:

$$\mathsf{R}_{\mathsf{L}} < \frac{\mathsf{V}_{\mathsf{CC}} - \mathsf{V}_{\mathsf{H}}}{\mathsf{I}_{\mathsf{D}}}$$

(2)  $I_{IN} = I_F$  (ON state)

When the collector current  $I_{C (ON)}$  flows on the output side of the transistor coupler, output  $V_{OUT (ON)}$  has to be less than  $V_L$  (the required low level voltage) as follows:

$$V_{CC} - I_{C (ON)} \times R_{L} = V_{OUT (ON)} < V_{L}$$

Therefore,

$$\mathsf{R}_{\mathsf{L}} > \frac{\mathsf{V}_{\mathsf{CC}} - \mathsf{V}_{\mathsf{L}}}{\mathsf{I}_{\mathsf{C}(\mathsf{ON})}}$$

Generally when the  $R_L$  value is large, the switching response time increases, so the  $R_L$  value should be kept as small as possible.

Figure 2.7 Transistor Coupler

Figure 2.8 I<sub>D</sub> vs.Ta

(3) Considerations for input current  $I_{IN}$  in the "ON" state

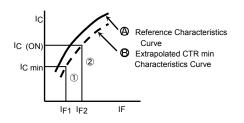

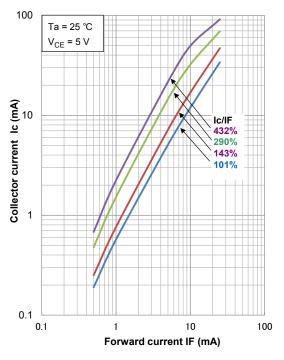

The characteristic curves of  $I_C$  vs.  $I_F$ , CTR vs. Ta, and CTR vs. t as shown in Figure 2.9, Figure 2.10 and Figure 2.11 respectively can be found in the product technical data sheet.

The transistor coupler CTR test is performed at the specific point ① in Figure 2.9. This point ① is not always the same as the actual operating point, so some compensation work is required to be done by the following procedure;

i) Draw the extrapolated CTR min curve (B) in parallel with the reference curve (A).

The point of intersection 1 shows the "CTR min" specification value.

Where, CTR =  $I_C/I_F$ ,  $I_C$  min = CTR min ×  $I_{F1}$

ii) Determine  $I_{F2}$  from the intersection point of  $I_C = I_C$  (ON) with curve (B).

$I_{F2}$  indicates the minimum input current at Ta = 25°C and operating time t = 0 hour. When considering the relationship between CTR and Ta (Figure 2.10), as well as CTR degradation (Figure 2.11), the minimum input current  $I_{IN}$  has to conform to the following formula.;

$$I_{IN} > I_{F2} \times \frac{1}{D_{Ta}} \times \frac{1}{D_t} \times \alpha$$

Where,  $D_{Ta}$ : Rate of CTR fluctuation within the operating temperature range

Dt: CTR degradation rate after "t" hours of operation

α: System design margin

Figure 2.9 I<sub>C</sub> vs. I<sub>F</sub>

Figure 2.10 CTR vs. Ta

Figure 2.11 CTR vs.t

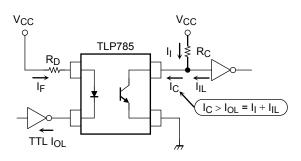

### 2-4. Design Example for Interface Circuit Using Transistor Coupler

Figure 2.12 shows a circuit using a DIP 4 pin transistor coupler as an interface between TTLs. In order to ensure absolute ON/OFF operation of the TTL, the LED current  $I_F$  should be set to satisfy  $I_{OL}$  which is determined by  $R_C$  and  $I_{IL}$ .

Example of Design Specifications

Operating temperature  $T_{opr}$  : 0 to 70°C Data transmission rate : 5 kbit/s Supply voltage :  $V_{CC}$  = 5 V ± 5% Operating life : 10 years (88,000 hours) System working ratio: 50%

TLP785 with CTR free rank is used. Specifications of products TLP785 for designing interface circuits are shown in Table 2.1.

Figure2.12

Interface Circuit between TTLs Using a 4pin Transistor Coupler

| ltem                                       | Symbol                                | Test Condition (Ta = 25°C)                            |         | min | typ. | max | Unit |

|--------------------------------------------|---------------------------------------|-------------------------------------------------------|---------|-----|------|-----|------|

| Forward voltage                            | V <sub>F</sub>                        | I <sub>F</sub> = 10 mA                                |         | 1.0 | 1.15 | 1.3 | V    |

| Collector to emitter<br>Breakdown voltage  | V <sub>(BR)</sub> CEO                 | I <sub>C</sub> = 0.5 mA                               |         | 80  | _    | _   | V    |

| Emitter to collector<br>Breakdown voltage  | V <sub>(BR) ECO</sub>                 | I <sub>E</sub> = 0.1 mA                               |         | 7   | _    | _   | V    |

| Collector dark current                     | ICEO                                  | $I_F = 0, V_{CE} = 24 V$                              |         | _   | 0.01 | 0.1 | μA   |

|                                            |                                       | I <sub>F</sub> = 0, V <sub>CE</sub> = 24 V, Ta = 85°C |         | _   | 0.6  | 50  | μA   |

| Current transfer ratio                     | CTR (I <sub>C</sub> /I <sub>F</sub> ) |                                                       | free    | 50  | —    | 600 |      |

|                                            |                                       | I <sub>F</sub> = 5 mA<br>V <sub>CE</sub> = 5 V        | GB rank | 100 | _    | 600 | %    |

|                                            |                                       |                                                       | GR rank | 100 | _    | 300 |      |

|                                            |                                       |                                                       | BL rank | 200 | _    | 600 |      |

| Collector to emitter<br>Saturation voltage | V <sub>CE (sat)</sub>                 | $I_{\rm F}$ = 8 mA, $I_{\rm C}$ = 2.4 mA              |         | _   | 0.2  | 0.4 | V    |

### Table 2.1 Principal Characteristics of TLP785

### 2-4-1. Setting of Forward Current IF

The maximum forward current I<sub>F</sub> is typically 16 mA for TTL I<sub>OL</sub>, and is subjected to the constrain I<sub>F</sub>≤I<sub>OL</sub>. The

maximum allowable value of I<sub>F</sub> found from Figure 2.13 is 38 mA. However, I<sub>F</sub> should be kept as small as possible because CTR degradation increases with the increase of forward current. Figure 2.14 shows the degradation of CTR. In order to realize the design of continuous operating life of 10 years (approximately 88,000 hours, 44,000 at system working ratio 50%), consider the degradation of CTR to be 50% (D<sub>t</sub> =0.5). The CTR measurement condition of TLP785 is at I<sub>F</sub> =5mA, so forward current should be set at I<sub>F</sub> = 5 / 0.5 = 10 mA for the initial design.

### Figure 2.13 Ambient Temperature vs. Allowable Forward Current (TLP785)

# Figure 2.14 Lifetime Test Data \* (CTR degradation)

\*This data shows an example of the CTR degradation curve.

Please design the circuit after confirming the reliability information on individual products.

### 2-4-2. Setting of the $I_{\text{F}}$ Limiting Resistance $R_{\text{D}}$

Forward current (typ.) is expressed by the following formula:

$$I_{F(typ.)} = \frac{V_{CC} - V_{F(typ.)} - V_{OL}}{R_{D(typ.)}}$$

where  $V_{F\ (typ.)}$  is obtained from the technical datasheet. For TLP785,

$$V_{F (typ.)} = 1.15 V (I_F = 10 mA)$$

R<sub>D</sub> is determined as follows:

$$R_{\rm D} = \frac{5V - 1.15V - 0.4V}{10mA}$$

**= 345** Ω

Therefore, R\_D = 330  $\Omega\pm$  5% will be optimum.

Then  $I_{F (min)}$  and  $I_{F (max)}$  should be checked to make sure that actual values of  $I_{F}$  will remain within allowable tolerances:

$$\begin{split} I_{F(min)} &= \frac{V_{CC(min)} - V_{F(max)} - V_{OL}}{R_{D(max)}} \\ &= \frac{4.75V - 1.3V - 0.4V}{347\Omega} \\ &= 8.8 \text{ mA} \\ I_{F(max)} &= \frac{V_{CC(max)} - V_{F(min)} - V_{OL}}{R_{D(min)}} \\ &= \frac{5.25V - 1.0V - 0.4V}{314\Omega} \\ &= 12.3 \text{ mA} \end{split}$$

### 2-4-3. Setting of Pull-up Resistance R<sub>C (max)</sub>

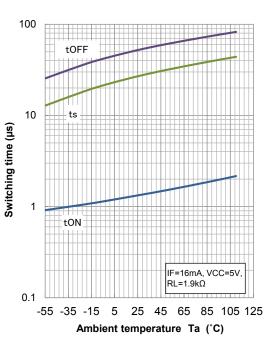

$R_{C\ (max)}$  should be set according to the switching time and dark current  $I_{CEO\ (max)}$  at the maximum operating temperature of the transistor coupler. Since the design specification for data transmission rate is 5 kbit/s, the total switching time should satisfy the below condition.

T = tr + td + tf + ts≤200 μs

Switching time changes with various conditions, such as CTR (current transfer ratio), R<sub>L</sub> (load resistance), and Ta (ambient temperature). R<sub>L</sub> should be designed to accommodate these changes in these conditions. Please check the technical datasheet for the influence of change in I<sub>F</sub>, V<sub>CC</sub> etc. Here, T(max) is set at T≤100 µs taking into consideration of a variation margin for I<sub>F</sub>, V<sub>CC</sub> etc.

The switching time  $t_{OFF}$  (= $t_s + t_f$ ) increases as the CTR rises (see Figure 2.15 CTR vs. Switching time), this is because the  $h_{FE}$  of photo-transistor tends to increase as the CTR rises. Therefore, it will be desirable to choose a product with a small CTR rank when a maximum switching time is specified.

Products of CTR free rank (50 to600%) seem suitable for satisfying the condition T≤100  $\mu$ s. However, we can see from Figure 2.15 that switching time for products of similar rank can vary slightly (t<sub>OFF</sub> has a difference for about 10  $\mu$ s on the similar CTR=200% samples). Therefore GR rank (100 to 300%) is selected taking into consideration such variation in characteristics and influences due to other parameter change (Ta, R<sub>L</sub> etc).

Next, refer to Figure 2.16 Ta vs. switching time (CTR=300% sample). Switching time is increased by 40% when Ta is raised from 25°C to 70°C. Therefore at Ta=70°C, T= 100 /  $1.4 < 70 \mu s$ .

## Figure 2.15 CTR vs. Switching time (saturated)

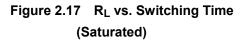

The load resistance R<sub>L</sub> is obtained from the switching time characteristic (for saturated operation) in Figure 2.17. Reading off the graph, for T≤70  $\mu$ s, load resistance should satisfy R<sub>L</sub>≤3 kΩ. R<sub>L</sub> can be expressed in terms of R<sub>C</sub> and the parallel resistance of the standard TTL input resistance R<sub>IN</sub> (Figure 2.18). R<sub>c(max)</sub> is obtained as follows;

$$R_L = R_C / / R_{IN}$$

$R_L = 1 / ((1 / R_C) + (1 / R_{IN})) ≤ 3kΩ$

As,  $R_{IN} = 4kΩ$

$R_C ≤ 12kΩ$

Next, check R<sub>C (max)</sub> with regards to the dark current I<sub>CEO</sub> (max). The relation between I<sub>CEO</sub> (max) and R<sub>C</sub> (max) is shown below;

$$\mathsf{R}_{\mathsf{C}(\mathsf{max})} = \frac{\mathsf{V}_{\mathsf{CC}(\mathsf{min})} - \mathsf{V}_{\mathsf{IH}}}{\mathsf{I}_{\mathsf{CEO}}}$$

VIH is high level input voltage for TTL.

Here,  $I_{CEO(max)}$  is estimated at Ta = 70°C. Temperature dependencies of  $I_{CEO(typ.)}$  at alternative parameter values of  $V_{CE}$  = 5 V, 10 V, and 24 V are shown in Figure 2.19.

In the case of the TLP785 transistor coupler,

$I_{CEO}$  (max) = 50 µA at Ta = 85°C and  $V_{CE}$  = 24 V (technical datasheet specifications). Taking  $V_{CE}$  dependency and Ta dependency into consideration using Figure 2.19,  $I_{CEO}$  (max) is estimated at Ta = 70°C and  $V_{CE}$  = 5 V.

$V_{CE}$  dependency:  $I_{CEO}$   $_{(typ.)}$  is reduced by 1/3 when  $V_{CE}$  is varied from 24 to 5 V.

Ta dependency:  $I_{CEO}~(\mbox{typ.})$  is reduced by 1/4 when Ta is varied from 85 to 70°C.

Therefore,  $I_{CEO\ (max)}$  at Ta = 70°C and  $V_{CE}$  = 5 V is estimated to be,

$$I_{CEO} = 50\mu A \times \frac{1}{3} \times \frac{1}{4} = 4.2\mu A$$

At  $I_{IH}$  = 40  $\mu$ A for general TTLs and R<sub>C</sub> (max) will be obtained as follows;

$$R_{C(max)} = \frac{4.75V - 2V}{4.2\mu A + 40\mu A} = 62 \, k\Omega$$

Figure 2.19 I<sub>CEO</sub> vs. Temperature

Since this is a larger value than  $12k\Omega$  set up from switching time, R<sub>C (max)</sub> is set at  $12k\Omega$ .

### 2-4-4. Setting of Pull-up Resistance Rc

Assuming the worst case scenario where the collector current  $I_c$  is at its minimum in Figure 2.18,  $R_C$  can be expressed by the following relation;

$$R_{\text{C}} \geq \frac{V_{\text{CC}(\text{max})} - V_{\text{OL}}}{\text{minI}_{\text{C}} - \text{I}_{\text{IL}}}$$

$minI_{C} = I_{C (min)} \times D_{IF} \times D_{t} \times D_{VCE} \times D_{Ta}$

Where,

$D_t$ :  $I_C$  degradation rate after a certain time has passed.

$\mathsf{D}_{\mathsf{IF}}: \mathsf{I}_{\mathsf{C}}$  change rate at an  $\mathsf{I}_{\mathsf{F}}$  setting for your designing.

$\mathsf{D}_{VCE}:$  I\_C drop rate under  $\mathsf{V}_{CE}$  (sat) condition.

$D_{\mbox{Ta}}{:}~I_{\mbox{C}}$  fluctuation rate with changes in the operating temperature  $T_{\mbox{opr}}.$

These values are obtained from technical data.

In the case of the TLP785:

From Figure 2.14,  $D_t = 0.5$  (t = 44,000 h, 50% operating ratio)

From Figure 2.20,  $D_{IF}$  = 2.3 (at  $I_F$  = 10 mA) From Figure 2.21,  $D_{VCE}$  = 0.7 (at  $V_{CE}$  = 0.4 V) From Figure 2.22,  $D_{Ta}$  = 0.75 (at Ta = 70°C)

Figure 2.20 I<sub>C</sub> vs. I<sub>F</sub> Curves Varying According to Different I<sub>C</sub>/I<sub>F</sub> Rations

On the other hand, GR rank is selected at section 2.4.3 as I<sub>C (min)</sub> = 5 mA (at I<sub>F</sub> = 5 mA  $\times$  I<sub>C</sub>/I<sub>F (min)</sub> = 100%), and

min I\_C = 5 mA

$$\times$$

2.3  $\times$  0.5  $\times$  0.7  $\times$  0.75

Accordingly,  $I_{IL}$  is 1.6 mA for general TTLs and  $R_C$  (min) can be obtained as follows:

$$R_{C(min)} = \frac{5.25V - 0.4V}{3.0mA - 1.6mA} \simeq 3.5k\Omega$$

In other words, R<sub>C</sub> can be set from 3.5 k $\Omega$  to 12 k $\Omega$ , but it is also necessary to consider the switching speed required by the system and the importance of absolute ON or OFF conditions. If the switching speed is considered to be relatively more important, R<sub>C</sub> should be set to a value close to R<sub>C</sub> (min). On the other hand, if the certainty of ON and OFF operation is considered to be the most important criterion, a value close to R<sub>C</sub> (max) should be selected (the operating life of the device may be defined as the period during which there is certainty of the ON and OFF conditions being properly set.). In this case, since D<sub>t</sub> is assumed to be 0.5 with a relatively high margin the switching speed should be considered to be more important. So, R<sub>C</sub> is set at 4.7 k $\Omega$ .

Figure 2.22 Collector Current vs. Ta

$R_D$  = 330  $\Omega$  and  $R_C$  = 4.7 k $\Omega$  are calculated values determined by the procedures above. Please perform a thorough check of the waveform and the operation with your system and redesign a  $R_D$  and  $R_C$  as necessary. When faster data speed is required for a system, you can also select an IC coupler with guarantee of the maximum switching time. When using a transistor coupler as an interface between CMOS, circuit design can also be conducted in the same way as the above TTLs. Please note that in the case of CMOS,  $I_{IL}$  and  $I_{IH}$  are smaller than TTLs. Also, the input voltage level of CMOS is different from that of TTLs. As such, please pay careful attention to the characteristics of CMOS during circuit design.

\*All of the electrical data on this document is a reference of a representative sample.

### 3.Terms

### (General terms)

| Term                                                  | Symbol           | Description                                                                 |  |  |  |  |

|-------------------------------------------------------|------------------|-----------------------------------------------------------------------------|--|--|--|--|

| Absolute Maximum Rating                               |                  | Maximum value that must not be exceeded even for an instant                 |  |  |  |  |

| Absolute Maximum Kating                               |                  | during operation                                                            |  |  |  |  |

| Isolation Voltage                                     | BVS              | Isolating voltage between input and output under the specified              |  |  |  |  |

| Isolation voltage                                     |                  | conditions                                                                  |  |  |  |  |

| Capacitance (Input to Output),                        |                  |                                                                             |  |  |  |  |

| Total Capacitance (Input to<br>Output)                | CS               | Electrostatic capacitance between the input and output pins                 |  |  |  |  |

| Capacitance (Input),                                  | CT               | Electrostatic capacitance between the anode and cathode pins                |  |  |  |  |

| Input Capacitance                                     | Ct               | of the LED                                                                  |  |  |  |  |

| Forward Current,                                      | T-               | Rated current that can flow continuously in the forward direction of        |  |  |  |  |

| Input Forward Current                                 | IF               | the LED                                                                     |  |  |  |  |

| Pulse Forward Current,                                | T                | Rated current that can flow momentarily in the forward direction of         |  |  |  |  |

| Input Forward Current (Pulsed)                        | I <sub>FP</sub>  | the LED                                                                     |  |  |  |  |

| Peak Transient Forward Current                        | I <sub>FPT</sub> | Rated current that can flow momentarily in the forward direction of the LED |  |  |  |  |

| Reverse Voltage,                                      |                  | Rated reverse voltage that can be applied across the LED's                  |  |  |  |  |

| Input Reverse Voltage                                 | VR               | cathode and anode                                                           |  |  |  |  |

| Reverse Current,                                      |                  | Leakage current flowing in the reverse direction of the LED (from           |  |  |  |  |

| Input Reverse Current                                 | Ι <sub>R</sub>   | cathode to anode)                                                           |  |  |  |  |

| Forward Voltage,                                      |                  | Voltage drop across the anode and cathode pins of the LED under             |  |  |  |  |

| Input Forward Voltage                                 | VF               | the specified forward-current condition                                     |  |  |  |  |

| LED Power Dissipaiton,                                |                  |                                                                             |  |  |  |  |

| Input Power Dissipaiton                               | PD               | Rated power that can be dissipated in the LED                               |  |  |  |  |

|                                                       | P <sub>T</sub>   | Total rated power that can be dissipated in both the input and              |  |  |  |  |

| Total Power Dissipaiton                               |                  | output devices                                                              |  |  |  |  |

|                                                       | R <sub>S</sub>   | Resistance between the input and output pins at the specified               |  |  |  |  |

| Isolation Resistance                                  |                  | voltage                                                                     |  |  |  |  |

| Junction Temperature                                  | Тj               | Permissible temperature of the junction of the photodetector or LED         |  |  |  |  |

| Operating Temperature                                 | T <sub>opr</sub> | Ambient temperature range in which the device can operate without           |  |  |  |  |

|                                                       | · opr            | loss of functionality                                                       |  |  |  |  |

| Lead Soldering Temperature                            | T <sub>sol</sub> | Rated temperature at which the device pins can be soldered without          |  |  |  |  |

|                                                       |                  | loss of functionality                                                       |  |  |  |  |

|                                                       | -                | Ambient temperature range in which the device can be stored                 |  |  |  |  |

| Storage Temperature                                   | T <sub>stg</sub> | without operation                                                           |  |  |  |  |

| Creepage Distance                                     |                  | Shortest distance along the surface of insulation between the path of       |  |  |  |  |

|                                                       |                  | two conductive parts (input and output)                                     |  |  |  |  |

| Clearance (Clearance Distance)                        |                  | Shortest distance through air between the path of two conductive            |  |  |  |  |

| Clearance(Clearance Distance)                         |                  | parts (input and output)                                                    |  |  |  |  |

| Internal Isolation Thickness                          |                  | Distance through insulation. Shortest thickness through internal            |  |  |  |  |

| Internal Isolation Thickness,<br>Insulation Thickness |                  | insulation between the path of two conductive parts (input and              |  |  |  |  |

|                                                       |                  | output)                                                                     |  |  |  |  |

### (Transistor output)

| Term                                                                 | Symbol                                  | Description                                                                                                                                         |  |  |  |

|----------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Collector Current                                                    | IC                                      | Rated current allowed to flow to collector                                                                                                          |  |  |  |

| Current Transfer Ratio                                               | I <sub>C</sub> /I <sub>F</sub><br>(CTR) | Ratio of output current, $I_C,$ to input current, $I_F \colon  I_C/I_F  \times  100$ (unit: %)                                                      |  |  |  |

| Collector Dark Current,                                              | I <sub>CEO</sub>                        | Leakage current flowing between collector and emitter                                                                                               |  |  |  |

| Dark Current                                                         | I <sub>DARK</sub>                       | Leakage current flowing between collector and emitter                                                                                               |  |  |  |

| OFF-state Collector Curreent                                         | I <sub>C(off)</sub>                     | Leakage current flowing between collector and emitter when Low voltage is applied to input                                                          |  |  |  |

| Current Gain Factor                                                  | h <sub>FE</sub>                         | h <sub>FE</sub> for phototransistor                                                                                                                 |  |  |  |

| Base Photo-Current                                                   | I <sub>PB</sub>                         | Photo-current generated by the specified input current, $\mathrm{I}_{\mathrm{F}}$ , in the phototransistor base block                               |  |  |  |

| Collector Power Dissipation                                          | PC                                      | Rated power that can be dissipated in collector                                                                                                     |  |  |  |

| Turn-On Time                                                         | t <sub>ON</sub><br>t <sub>on</sub>      | Time required for the output waveform to change from 100% (0%) to 10% (90%) when the input is turned off and back on under the specified conditions |  |  |  |

| Turn-Off Time                                                        | toff<br>t <sub>off</sub>                | Time required for the output waveform to change from 0% (100%) to 90% (10%) when the input is turned on and back off under the specified conditions |  |  |  |

| Storage Time                                                         | ts                                      | Time required for the output waveform to change from 0% (100%) to 10% (90%) when input is turned on and back off under the                          |  |  |  |

|                                                                      |                                         | specified conditions                                                                                                                                |  |  |  |

| Fall Time                                                            | t <sub>f</sub>                          | Time required for the output waveform to change from 90% to $10\%$                                                                                  |  |  |  |

| Rise Time                                                            | tr                                      | Time required for the output waveform to change from 10% to $90\%$                                                                                  |  |  |  |

| Collector-Emitter Saturation<br>Voltage                              | V <sub>CE(sat)</sub>                    | Voltage between collector and emitter under the specified saturation                                                                                |  |  |  |

|                                                                      |                                         | conditions                                                                                                                                          |  |  |  |

| Collector-Base Breakdown Voltage                                     | V <sub>(BR)</sub> CBO                   | Breakdown voltage between collector and base when emitter is open                                                                                   |  |  |  |

| Collector-Emitter Breakdown<br>Voltage                               | V <sub>(BR)CEO</sub>                    | Breakdown voltage between collector and emitter (when base is open)                                                                                 |  |  |  |

| Emitter-Base Breakdown Voltage                                       | V <sub>(BR)EBO</sub>                    | Breakdown voltage between emitter and base when collector is open                                                                                   |  |  |  |

| Emitter-Collector Breakdown<br>Voltage                               | V <sub>(BR)ECO</sub>                    | Breakdown voltage between emitter and collector (when base is open)                                                                                 |  |  |  |

| Collector-Base Voltage                                               | VCBO                                    | Rated voltage that can be applied across collector and base                                                                                         |  |  |  |

| Collector-Emitter Voltage                                            | VCEO                                    | Rated voltage that can be applied across collector and emitter                                                                                      |  |  |  |

| Emitter-Base Voltage                                                 | V <sub>EBO</sub>                        | Rated voltage that can be applied across emitter and base                                                                                           |  |  |  |

| Emitter-Collector Voltage                                            | V <sub>ECO</sub>                        | Rated voltage which can be applied across emitter and base                                                                                          |  |  |  |

| Capacitance (Collector to Emitter),<br>Collector-Emitter Capacitance | C <sub>CE</sub>                         | Electrostatic capacitance between the collector and emitter pins                                                                                    |  |  |  |

### **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- GaAs (Gallium Arsenide) is used in Product. GaAs is harmful to humans if consumed or absorbed, whether in the form of dust or vapor. Handle with care and do not break, cut, crush, grind, dissolve chemically or otherwise expose GaAs in Product.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without

limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile

technology products (mass destruction weapons). Product and related software and technology may be controlled under the

applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and

the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly

prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

### **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**