# **Basics of Low-Dropout (LDO) Regulator ICs**

### **Outline:**

LDO (low-drop-out) regulators, which are used as PoLs for mobile and IoT devices, are optimal power supply ICs for analog circuits that require high voltage accuracy and low noise. This document describes key features, the operation of the built-in protective function, and the efficiency.

# **Table of Contents**

| Outline:                                                                                    | 1  |

|---------------------------------------------------------------------------------------------|----|

| Table of Contents                                                                           | 2  |

| 1. Introduction                                                                             | 6  |

| 2. Electrical characteristics to be noted when selecting LDOs                               | 6  |

| 3. Power supply sequencing of LDOs                                                          | 10 |

| 3.1. Single-power-supply LDOs                                                               |    |

| 3.2. Dual-power-supply LDOs                                                                 |    |

| 4. External capacitors                                                                      | 11 |

| 4.1. Input capacitor, C <sub>IN</sub>                                                       | 11 |

| 4.2. Bias capacitor, C <sub>BIAS</sub>                                                      | 11 |

| 4.3. Output capacitor, C <sub>OUT</sub>                                                     |    |

| 4.4. Considerations for using ceramic capacitors                                            |    |

| 5. Overview of linear regulators                                                            | 12 |

| 5.1. What is a linear regulator?                                                            |    |

| 5.2. Dropout voltage of LDOs                                                                |    |

| 6. Major characteristics of LDOs                                                            | 16 |

| 6.1. Input voltage (V <sub>IN</sub> )                                                       |    |

| 6.2. Bias voltage (V <sub>BIAS</sub> , V <sub>BAT</sub> )                                   |    |

| 6.3. Output voltage accuracy, output voltage (V <sub>OUT</sub> )                            |    |

| 6.4. Adjustable voltage (V <sub>ADJ</sub> )                                                 |    |

| 6.5. Quiescent current (I <sub>B</sub> , I <sub>B(ON)</sub> )                               |    |

| 6.6. Quiescent current (I <sub>IN(ON)</sub> )                                               |    |

| 6.7. Standby current (I <sub>B(OFF)</sub> , I <sub>IN(OFF)</sub> , I <sub>BIAS(OFF)</sub> ) |    |

| 6.8. ADJ pin current (I <sub>ADJ</sub> )                                                    |    |

| 6.9. Control voltage (ON) (V <sub>CT(ON)</sub> )                                            |    |

| 6.10. Control voltage (OFF) (V <sub>CT(OFF)</sub> )                                         |    |

| 6.11. Control pull-down current (I <sub>CT</sub> )                                          |    |

| 6.12. Line regulation (Reg·line)                                                            |    |

| 6.13. Load regulation (Reg·load)                                                            |    |

| 6.14. Dropout voltage ( $V_{DO}$ ) (input-output voltage differential)                      |    |

| 6.15. Output Current limit (I <sub>CL</sub> )                                               |    |

| 6.16. Undervoltage lockout (V <sub>UVLO</sub> )                                             |    |

| 6.17. Temperature coefficient (T <sub>CVO</sub> )                                           |    |

| 6.18. Output noise voltage (V <sub>NO</sub> )                                               |    |

| 6.19. Ripple rejection ratio (R.R. (V <sub>IN</sub> ), R.R. (V <sub>BIAS</sub> ))           |    |

| 6.20. Load transient response ( $\Delta V_{OUT}$ )                                          |    |

| 6.21. Output discharge on-resistance (R <sub>SD</sub> )                                     |    |

# Basics of Low-Dropout (LDO) Regulator ICs

| -   | -        |      |

|-----|----------|------|

| App | lication | Note |

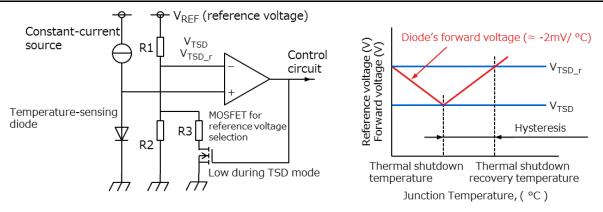

| 6.22. Thermal shutdown temperature $(T_{SD})$ , thermal shutdown temperature hysteresis ( | Т <sub>SDH</sub> ) 32 |

|-------------------------------------------------------------------------------------------|-----------------------|

| 6.23. Inrush current suppression (slew rate control)                                      |                       |

| 7. Setting the output voltage of an adjustable-output-voltage LDO                         |                       |

| 8. Efficiency of LDOs                                                                     | 35                    |

| 9. Calculating the power dissipation and junction temperature of an LDO                   |                       |

| 9.1. Calculating power dissipation                                                        |                       |

| 9.2. Calculating the junction temperature                                                 |                       |

| 10. LDO oscillation and countermeasures                                                   |                       |

| 11. Protection against reverse biasing of input and output                                | 40                    |

| 12. Conclusion                                                                            | 41                    |

| 13. Related Links                                                                         | 42                    |

| 14. RESTRICTIONS ON PRODUCT USE                                                           | 43                    |

|                                                                                           |                       |

# List of Figures

| Figure 2.1 Input voltage range and dropout voltage of linear regulators                    | 6    |

|--------------------------------------------------------------------------------------------|------|

| Figure 3.1 Power supply sequence of single-power-supply LDOs                               | . 10 |

| Figure 3.2 Power supply sequence of dual-power-supply LDOs                                 | . 10 |

| Figure 4.1 Example of a capacitance-vs-voltage curve of a ceramic capacitor                | . 12 |

| Figure 4.2 Example of a capacitance-vs-temperature curve of a ceramic capacitor            | . 12 |

| Figure 5.1 Operation of a linear regulator                                                 | . 12 |

| Figure 5.2 Dropout voltage of an LDO with a P-channel MOS pass transistor                  | . 13 |

| Figure 5.3 Regions of MOSFET operation                                                     | . 13 |

| Figure 5.4 Dropout voltage of a standard linear regulator with an N-channel MOS pass trans |      |

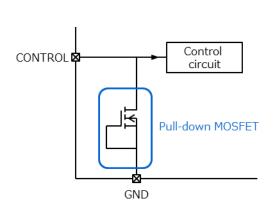

| Figure 6.1 Equivalent circuit for the internal circuitry of the CONTROL pin                |      |

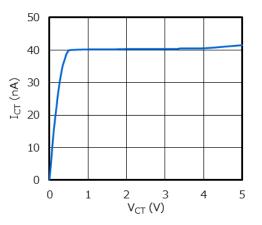

| Figure 6.2 $I_{CT}$ – $V_{CT}$ curve (reference)                                           | . 19 |

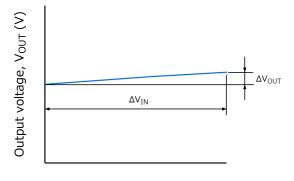

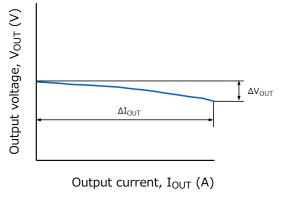

| Figure 6.3 Line regulation (Reg·line)                                                      | . 20 |

| Figure 6.4 Load regulation (Reg·load)                                                      | . 21 |

| Figure 6.5 Dropout voltage (V <sub>DO</sub> )                                              | . 22 |

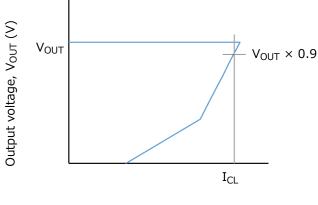

| Figure 6.6 Current limit ( $I_{CL}$ )                                                      | . 23 |

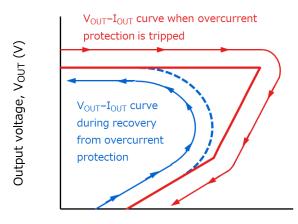

| Figure 6.7 Foldback current curves                                                         | . 23 |

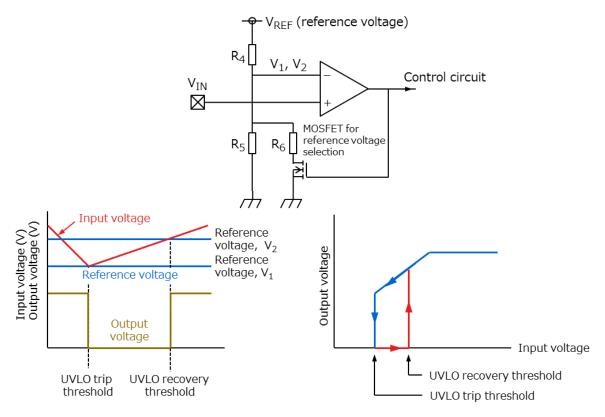

| Figure 6.8 Undervoltage lockout circuit                                                    | . 24 |

| Figure 6.10 Noise frequency characteristics                                                | . 26 |

| Figure 6.11 Ripple rejection                                                               | . 27 |

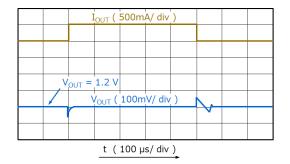

| Figure 6.12 $V_{OUT}$ waveform of an LDO with poor load transient response                 | . 28 |

| Figure 6.13 $V_{OUT}$ waveform of an LDO with good load transient response                 | . 28 |

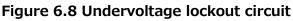

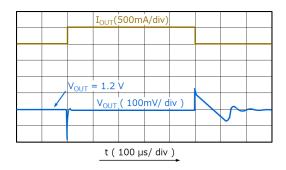

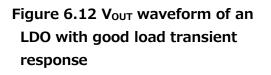

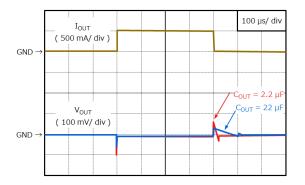

| Figure 6.14 Test circuit for load transient response and operating waveforms               | . 29 |

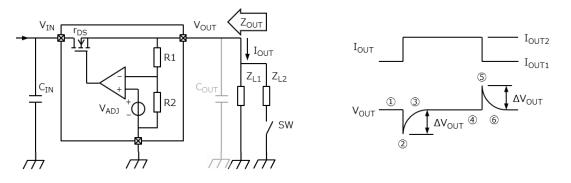

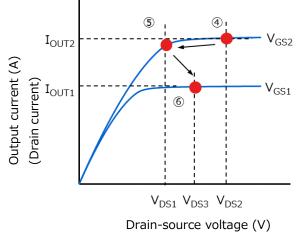

| Figure 6.15 Q points in the event of a sharp increase in output current                    | . 29 |

| Figure 6.16 Load transient response vs. output capacitor values                            | . 30 |

| Figure 6.17 Q points in the event of a sharp decrease in output current                    | . 31 |

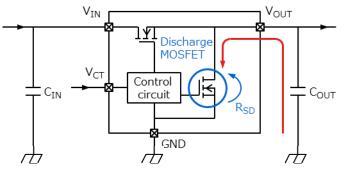

| Figure 6.18 Output discharge circuit                                                       | . 31 |

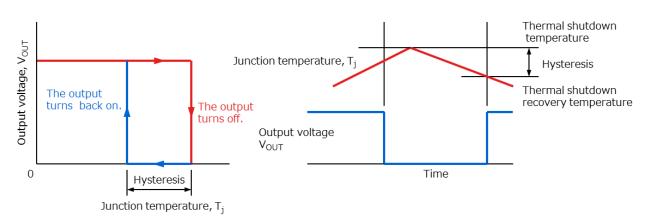

| Figure 6.19 Thermal shutdown temperature and thermal shutdown hysteresis                   | . 32 |

| Figure 6.20 TSD circuit and its principle of operation                                     | . 33 |

| Figure 10.1 Negative feedback loop of an LDO                                               | . 38 |

### Basics of Low-Dropout (LDO) Regulator ICs Application Note

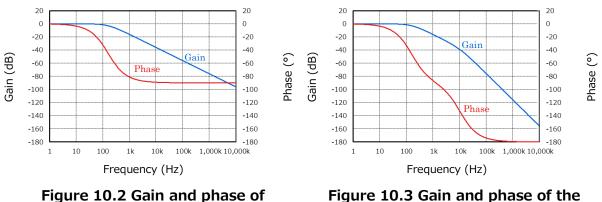

| Figure 10.2 Gain and phase of the primary time-delay circuit                  | . 38 |

|-------------------------------------------------------------------------------|------|

| Figure 10.3 Gain and phase of the secondary time-delay circuit                | . 38 |

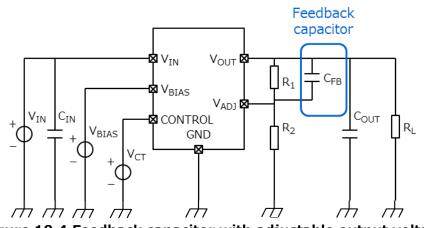

| Figure 10.4 Feedback capacitor with adjustable output voltage                 | . 40 |

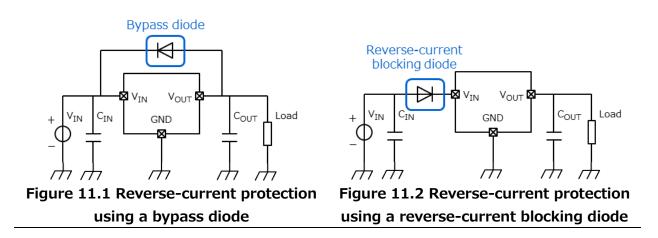

| Figure 11.1 Reverse-current protection using a bypass diode                   | . 40 |

| Figure 11.2 Reverse-current protection using a reverse-current blocking diode | . 40 |

# List of Tables

| Table 5 | 5.1 C | omparison o | of sir | ngle- and | dual-powe | er-supply | / LDC | )s |                           | .15 |

|---------|-------|-------------|--------|-----------|-----------|-----------|-------|----|---------------------------|-----|

| Table   | 7.1   | Examples    | of     | external  | resistor  | values    | for   | an | adjustable-output-voltage | LDO |

| (T      | CR15  | AGADJ)      |        |           |           |           |       |    |                           | .34 |

# 1. Introduction

Various semiconductor components are used to reduce the size and enhance the performance of increasingly sophisticated mobile and other electronic devices. To accommodate the need for these electronic devices, demand is growing for highly regulated low-noise and high-quality power supplies for semiconductor components.

Low-dropout regulator ICs (hereinafter "LDOs") are physically smaller, generate less noise, and are easier to design with than switched-mode DC-DC converters, making them ideal for use as point-of-load (POL) regulators that are placed in the vicinity of the target semiconductor components.

This application note describes the basics of LDOs, including their overview, electrical characteristics, and usage considerations.

Application notes that provide more details on the characteristics and applications of LDOs are also available to help you select and use LDOs properly.

# 2. Electrical characteristics to be noted when selecting LDOs

There are various guidelines for selecting LDOs that satisfy system requirements. The following describes major electrical characteristics to be noted when selecting LDOs.

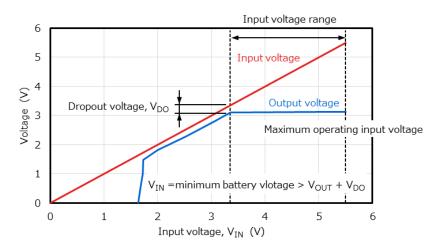

### (1) Input voltage

In the case of battery-operated devices, the battery voltage decreases as the battery supplies electricity to a load. It is necessary to select an LDO, taking the minimum battery voltage and dropout voltage into consideration, in order to ensure that the input voltage of the LDO remains higher than the sum of its output and dropout voltages even at the minimum battery voltage so that the following IC or circuitry is supplied with a regulated voltage.

(References: Input voltage range, dropout voltage)

Figure 2.1 Input voltage range and dropout voltage of linear regulators

| To perform a parametric search of low dropout voltage type LDOs $\rightarrow$            | Click Here |

|------------------------------------------------------------------------------------------|------------|

| To perform a parametric search of low input voltage type (up to 5.5V) LDOs $\rightarrow$ | Click Here |

| To perform a parametric search of high input voltage type (up to 36V) LDOs $ ightarrow$  | Click Here |

|                                                                                          |            |

### (2) Output voltage

Select LDOs that provide sufficient output voltage accuracy as well as an output voltage that falls within the operating voltage range of the IC or circuitry connected as a load even when the input voltage or output current varies.

(References: <u>Output voltage</u>, <u>output voltage accuracy</u>, <u>line regulation</u>, <u>load regulation</u>, <u>load transient response</u>)

### (3) Output current (load current)

It is necessary to select LDOs whose output current does not exceed the specified operating range even in the event of output current transients.

| To perform a parametric search of LDOs with an output current of 150 mA $\rightarrow$ Click Here  |

|---------------------------------------------------------------------------------------------------|

| To perform a parametric search of LDOs with an output current of 200 mA $\rightarrow$ Click Here  |

| To perform a parametric search of LDOs with an output current of 300 mA $\rightarrow$ Click Here  |

| To perform a parametric search of LDOs with an output current of 420 mA $\rightarrow$ Click Here  |

| To perform a parametric search of LDOs with an output current of 500 mA $\rightarrow$ Click Here  |

| To perform a parametric search of LDOs with an output current of 800 mA $\rightarrow$ Click Here  |

| To perform a parametric search of LDOs with an output current of 1300 mA $\rightarrow$ Click Here |

| To perform a parametric search of LDOs with an output current of 1500 mA $\rightarrow$ Click Here |

(4) Power dissipation and maximum junction temperature of LDOs

The power dissipation of an LDO is calculated as  $P_D = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{IN} \times I_B$ . Its maximum junction temperature is calculated as  $T_{j(max)} = P_D \times R_{th(j-a)} + Ta$ . It is necessary to ensure that both power dissipation and junction temperature do not exceed the absolute maximum rated values under actual usage conditions. Special care should be exercised as to junction temperature because thermal resistance depends on the mounting area and metal thickness of a printed circuit board. If the junction temperature exceeds the absolute maximum rated temperature, an LDO trips thermal shutdown (TSD), possibly becoming unable to provide a normal output level.

(References: Power dissipation and maximum junction temperature)

(5) Quiescent current and standby current

In battery-operated devices, the LDO consumes a small amount of standby current during standby mode, in addition to the bias current during operation mode. It is necessary to select LDOs with low quiescent and standby current in order to conserve battery life.

(References: Quiescent current, standby current)

To perform a parametric search of LDOs with low quiescent current  $\rightarrow$  Click Here

(6) Ripple rejection ratio, output noise voltage

If a system incorporates CMOS sensors and/or high-precision analog circuits, its performance is greatly affected by the quality of power supplies such as the amount of noise on the power supplies. For systems requiring low-noise power supplies, it is necessary to select LDOs with a high ripple rejection ratio and low output noise voltage.

(References: <u>Ripple rejection ratio</u>, <u>output noise voltage</u>)

To perform a parametric search of low-noise LDOs  $\rightarrow$  Click Here

To perform a parametric search of LDOs with a high ripple rejection ratio  $\rightarrow$  Click Here

(7) Control voltage

The control voltage is the voltage required to turn on the LDO. In recent years, low-voltage interface signals and control signals have been increasingly used to reduce the power consumption of devices. Our company offers a lineup of products with control voltages ranging from low control voltage products compatible with 1.2V I/O and a minimum of 0.8V, to products compatible with general-purpose lines of 1.8V and above.

To perform a parametric search of low control voltage LDOs  $\rightarrow$  Click Here

(8) Package

We offer a wide range of packages, including ultra-compact WCSP types with high power dissipation suitable for high-density mounting, as well as general-purpose types that are easy to handle, available in various sizes. You can select the most suitable option according to your usage conditions.

| To perform a parametric search of WCSP4E / 4F (0.645 mm x 0.645 mm) LDOs –   | Click Here |

|------------------------------------------------------------------------------|------------|

| To perform a parametric search of SDFN4 / 4E (0.8 mm x 0.8 mm) LDOs -        | Click Here |

| To perform a parametric search of DFN4D / 4E / 4F (1.0 mm x 1.0 mm) LDOs $-$ | Click Here |

| To perform a parametric search of WCSP6F (1.2 mm x 0.8 mm) LDOs –            | Click Here |

| To perform a parametric search of DFN5B (1.2 mm x 1.2 mm) LDOs –             | Click Here |

| To perform a parametric search of SOT-553 (ESV) (1.6 mm x 1.6 mm) LDOs $-$   | Click Here |

| To perform a parametric search of SOT-353F (UFV) (2.0 mm x 2.1 mm) LDOs $-$  | Click Here |

| To perform a parametric search of SOT-25 (SMV) (2.9 mm x 2.8 mm) LDOs –      | Click Here |

### **3.** Power supply sequencing of LDOs

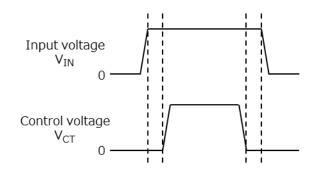

### 3.1. Single-power-supply LDOs

In the case of single-power-supply LDOs, the supply voltage from the  $V_{IN}$  pin is supplied to the internal control circuitry. For an LDO to work properly,  $V_{IN}$  must be fully powered up to a nominal voltage level prior to the application of control voltage ( $V_{CT}$ ). Power off the LDO in the order opposite to the power-up sequence. Also use the LDO within the operating voltage range so that  $V_{CT}$  does not exceed  $V_{IN}$ . The power supply sequence, the magnitude relationship between  $V_{IN}$  and  $V_{CT}$ , and the operating voltage range might differ from LDO to LDO. For details on power supply sequencing, see the datasheets for individual LDOs.

Figure 3.1 Power supply sequence of single-power-supply LDOs

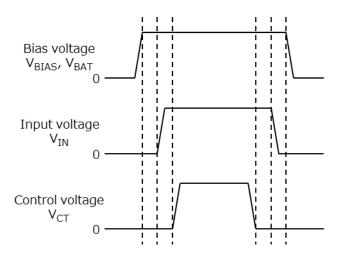

### 3.2. Dual-power-supply LDOs

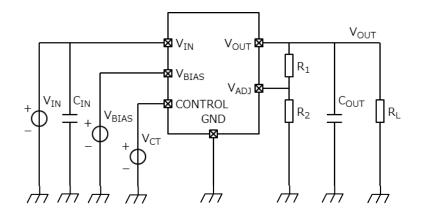

In the case of dual-power-supply LDOs, the supply voltage is supplied to the internal control circuitry from the bias voltage pin ( $V_{BIAS}$  or  $V_{BAT}$ ). Therefore,  $V_{BIAS}$  or  $V_{BAT}$  must be fully powered up to a nominal voltage level first, followed by the application of input voltage ( $V_{IN}$ ) and then control voltage ( $V_{CT}$ ). Power off the LDO in the order opposite to the power-up sequence. The power supply sequence might differ from LDO to LDO. For details on power supply sequencing, see the datasheets for individual LDOs.

Figure 3.2 Power supply sequence of dual-power-supply LDOs

## 4. External capacitors

An LDO requires external capacitors to remove noise and power supply ripple. These capacitors greatly affect an LDO's performance as a power supply, including load transient response and oscillation immunity. Therefore, care should be exercised as to the types and specifications of the capacitors. Toshiba's LDOs are designed for use with multilayer ceramic capacitors (MLCCs). In this section, the use of multilayer ceramic capacitors (hereinafter referred to as "ceramic capacitors") is assumed. Ensure that an LDO is stable when used with capacitors with capacitance values higher than those shown in the datasheet.

### 4.1. Input capacitor, C<sub>IN</sub>

The input capacitor ( $C_{IN}$ ) filters out the noise superimposed on the input voltage. In the event of a drop in the input voltage due to an instantaneous change in output current,  $C_{IN}$  also prevents the malfunction of an LDO and compensates for a loss of output current.

### 4.2. Bias capacitor, C<sub>BIAS</sub>

The bias capacitor ( $C_{BIAS}$ ) filters out the noise superimposed on bias voltage and helps supply stable voltage to the internal control circuitry of an LDO.

### 4.3. Output capacitor, COUT

The output capacitor ( $C_{OUT}$ ) compensates for a loss of output current in the event of an instantaneous change in output current, improving load transient response.  $C_{OUT}$  also provides phase compensation for a feedback loop.

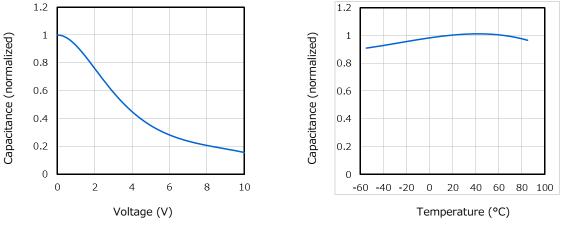

### 4.4. Considerations for using ceramic capacitors

Ceramic capacitors are ideal for use with LDOs since high-capacitance-value ceramic capacitors are becoming available with small size and low effective series resistance (ESR). However, the values of ceramic capacitors depend on voltage and temperature as shown in Figure 4.1 and Figure 4.2. In particular, the value of the output capacitor greatly affects the stability of an LDO. Be sure to fully evaluate ceramic capacitors, taking voltage and temperature into consideration.

Figure 4.1 Example of a capacitance-vs-voltage curve of a ceramic capacitor

### 5. Overview of linear regulators

### 5.1. What is a linear regulator?

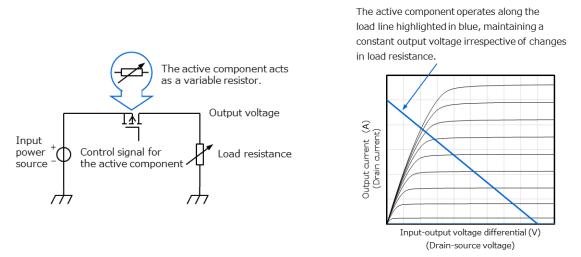

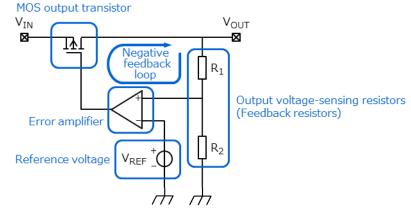

Also called series regulators, linear regulators incorporate an active component such as a pass transistor connected in series between an input power source and a load as shown in Figure 5.1. Controlled via a control signal, this active component acts as a variable resistor to maintain a constant output voltage.

### Figure 5.1 Operation of a linear regulator

### 5.2. Dropout voltage of LDOs

The input-output voltage differential of a linear regulator is called the dropout voltage. The input voltage necessary to obtain a regulated output voltage is expressed by Equation 5-1:

$$V_{IN} = V_{OUT} + V_{DROP} \tag{5-1}$$

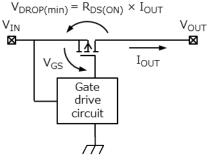

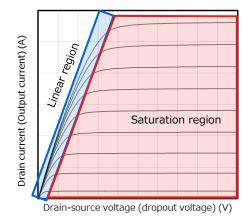

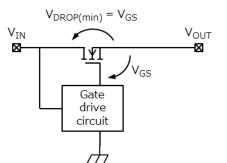

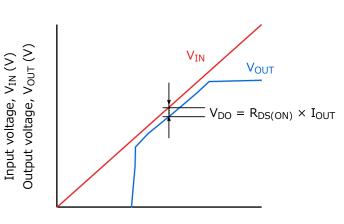

Generally, linear regulators with a dropout voltage of less than 1 V or so are called LDOs. Figure 5.2 shows an LDO with a P-channel MOS pass transistor. The gate-source voltage of the LDO can be up to  $V_{IN}$ . Since the LDO can operate in the linear region shown in Figure 5.3, the relationship between the input and output voltages can be expressed by Equation 5-2.

Figure 5.2 Dropout voltage of an LDO with a P-channel MOS pass transistor

$$V_{IN(min)} = V_{OUT} + V_{DROP(min)}$$

$$= V_{OUT} + R_{DS(ON)} \times I_{OUT}$$

Figure 5.3 Regions of MOSFET operation

Figure 5.4 shows a standard linear regulator with an N-channel MOS pass transistor. Equation 5-3 holds because  $V_{DROP(min)} = V_{GS}$ . Hence, the dropout voltage cannot be lower than  $V_{GS}$ .

$$V_{IN(min)} = V_{OUT} + V_{GS}$$

<sup>(5-3)</sup>

Figure 5.4 Dropout voltage of a standard linear regulator with an N-channel MOS pass transistor

As described above, in the case of single-power-supply LDOs, LDOs with a P-channel MOS pass transistor provide less dropout voltage than those with an N-channel MOS pass transistor.

However, since single-power-supply LDOs with a P-channel MOS pass transistor drive the gate of the MOS output transistor from  $V_{IN}$ , the gate drive voltage becomes insufficient at low  $V_{IN}$ , making it impossible to obtain a regulated output voltage. In contrast, dual-power-supply LDOs with the  $V_{IN}$  and  $V_{BIAS}$  pins incorporate an N-channel MOS output transistor that is more suitable for reducing on-resistance. Since these LDOs drive the gate of the MOS output transistor from the  $V_{BIAS}$  pin, the dropout voltage decreases because the gate voltage is independent of  $V_{IN}$ . This makes it possible to obtain a regulated output voltage even at low  $V_{IN}$ , considerably reducing power loss. Table 5.1 compares single- and dual-power-supply LDOs.

| Types of LDOs          | Single newer supply I DOs                    | Dual newer supply I DOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Single-power-supply LDOs                     | Dual-power-supply LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Polarity of the MOS    | P-channel MOSFET                             | N-channel MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| output transistor      |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power supplies         | Only V <sub>IN</sub>                         | V <sub>IN</sub> and V <sub>BIAS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| required               |                                              | VIN and VBIAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Dropout                | The gate voltage of the MOS output           | The gate voltage of the MOS output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| characteristics        | transistor is supplied from the $V_{IN}pin.$ | transistor is supplied from the $V_{BIAS}$ pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        |                                              | to reduce on-resistance and dropout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                        |                                              | voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | VIN Pch MOSFET Vour                          | CONTROL QUIC CONTR |

| Dropout voltage        | Dropout voltage vs. output current           | Dropout voltage vs. output current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| characteristics        | ∇ <sub>OUT</sub> =1.0V                       | $\searrow$ V <sub>OUT</sub> =1.0V, V <sub>BIAS</sub> =3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| When $V_{OUT} = 1.0 V$ | TCR3DM                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        | 0.0 age                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        | 0.4                                          | Considerably lower than                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                        | 0.6<br>0.4<br>0.2<br>0.2                     | Considerably lower than<br>single-power-supply LDOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                        | Drot                                         | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | 0 0.1 0.2 0.3 0.4 0.5                        | 0 0.1 0.2 0.3 0.4 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        | Output current (A)                           | Output current (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 5.1 Comparison of single- and dual-power-supply LDOs

# 6. Major characteristics of LDOs

This section describes each electrical characteristic of LDOs, referring to actual datasheets.

### 6.1. Input voltage (V<sub>IN</sub>)

$V_{IN}$  is the input voltage range in which an LDO is guaranteed to operate properly and provide the specified electrical characteristics. In the event of an input undervoltage condition, LDOs with the undervoltage lockout (UVLO) function shut down the output to prevent the subsequent IC or circuitry from malfunctioning in order to avoid system failure or instability.

### Datasheet example: TCR3UF series (300 mA LDO)

| Characteristics | Cumbol   | Test Condition          | $T_j = 25^{\circ}C$ |      |     | $T_j = -40$ to $85^{\circ}C$ |     | Unit |

|-----------------|----------|-------------------------|---------------------|------|-----|------------------------------|-----|------|

|                 | Symbol   | rest Condition          | Min                 | Тур. | Max | Min                          | Max | Unit |

| Input voltage   | $V_{IN}$ | I <sub>OUT</sub> = 1 mA | 1.5                 | -    | 5.5 | 1.5                          | 5.5 | V    |

### 6.2. Bias voltage (V<sub>BIAS</sub>, V<sub>BAT</sub>)

The bias voltage supplied via the  $V_{BIAS}$  pin is used as a power supply for the internal control and protection circuits of the LDO as well as for the gate drive of the MOS output transistor and the error amplifier for output voltage detection.  $V_{BIAS}$  and  $V_{BAT}$  are the bias voltage range in which these circuits are guaranteed to operate properly to provide the specified electrical characteristics. The  $V_{BIAS}$  pin does not incorporate an undervoltage lockout (UVLO) function. For the power-up and power-down sequence of  $V_{BIAS}$  and  $V_{IN}$ , see Section 3, "Power supply sequencing of LDOs."

### Datasheet example: TCR13AGADJ (1.3 A LDO)

| Characteristics | Symbol            | Test Condition                                              |                            | T <sub>j</sub> = 25°C |     | $T_j = -40$ to $85^{\circ}C$ |     | Unit |

|-----------------|-------------------|-------------------------------------------------------------|----------------------------|-----------------------|-----|------------------------------|-----|------|

|                 | Symbol            |                                                             | Min                        | Тур.                  | Max | Min                          | Max | Unit |

| Bias voltage    |                   | $V_{OUT} \le 1.1 \text{ V}, \text{ I}_{OUT} = 1 \text{ mA}$ | 2.5                        | -                     | 5.5 | 2.5                          | 5.5 |      |

|                 | V <sub>BIAS</sub> | $V_{OUT}$ > 1.1 V, $I_{OUT}$ = 1 mA                         | V <sub>OUT</sub><br>+1.4 V | -                     | 5.5 | V <sub>OUT</sub><br>+1.4 V   | 5.5 | V    |

### 6.3. Output voltage accuracy, output voltage (V<sub>OUT</sub>)

$V_{OUT}$  is the accuracy of output voltage regulation under the test conditions specified in a datasheet.

| Characteristics         | Svmbol           | Test Condition            |                                            | T <sub>j</sub> = 25°C |      |      | T <sub>j</sub> = -40 | Unit |      |

|-------------------------|------------------|---------------------------|--------------------------------------------|-----------------------|------|------|----------------------|------|------|

| Characteristics         | Symbol           |                           |                                            | Min                   | Тур. | Max  | Min                  | Max  | Unit |

|                         |                  |                           | $V_{OUT} < 1.8 V$                          | -18                   | -    | +18  | -                    | -    | mV   |

| Output voltage accuracy | V <sub>OUT</sub> | $I_{OUT} = 50 \text{ mA}$ | $1.8 \text{ V} \leq \text{V}_{\text{OUT}}$ | -1.0                  | -    | +1.0 | -                    | -    | %    |

Datasheet example: TCR8BM series (800 mA LDO)

### 6.4. Adjustable voltage (V<sub>ADJ</sub>)

$V_{ADJ}$  is specified for LDOs with adjustable output voltage.  $V_{ADJ}$  is the reference voltage for the error amplifier for output voltage detection. The error amplifier compares the reference voltage with the voltage at the midpoint of a resistor voltage divider between  $V_{OUT}$  and GND and accordingly controls the MOS output transistor so that the output maintains the regulated voltage. Among the TCR15AG series, the TCR15AGADJ is the adjustable output type.

### Datasheet example: TCR15AG series (1.5 A LDO)

| Chavastavistica    | cteristics Symbol Test Condition |   | T <sub>j</sub> = 25°C |      |       | $T_j = -40$ to $85^{\circ}C$ |     | Linit |

|--------------------|----------------------------------|---|-----------------------|------|-------|------------------------------|-----|-------|

| Characteristics    |                                  |   | Min                   | Тур. | Max   | Min                          | Max | Unit  |

| Adjustable voltage | V <sub>ADJ</sub>                 | - | 0.588                 | 0.60 | 0.612 | -                            | -   | V     |

### 6.5. Quiescent current (I<sub>B</sub>, I<sub>B(ON)</sub>)

$I_B$  and  $I_{B(ON)}$  are the quiescent current of the internal circuitry minus the pull-down current of the CONTROL pin flowing out of the GND pin when an LDO is operating under the test conditions specified in a datasheet.  $I_B$  and  $I_{B(ON)}$  are specified under a zero-load current ( $I_{OUT} = 0$  mA).

### Datasheet example: <u>TCR3UF series (300 mA LDO)</u>

| Characteristics   | Cumbol              | bol Test Condition -                                       | T <sub>j</sub> = 25°C |      |     | T <sub>j</sub> = -40 | Unit |      |

|-------------------|---------------------|------------------------------------------------------------|-----------------------|------|-----|----------------------|------|------|

| Characteristics   | Symbol              | Test Condition                                             | Min                   | Typ. | Max | Min                  | Max  | Unit |

|                   | I <sub>B(ON1)</sub> | $I_{OUT}$ = 0 mA, $V_{OUT} \le 1.5 \text{ V}$              | _                     | 0.34 | —   | _                    | 0.58 | μA   |

| Quiescent current | IB(ON2)             | I <sub>OUT</sub> = 0 mA,<br>1.5 V < V <sub>OUT</sub> ≤ 5 V | _                     | 0.38 | _   | _                    | 0.68 | μA   |

### 6.6. Quiescent current (I<sub>IN(ON)</sub>, I<sub>BIAS(ON)</sub>)

$I_{IN(ON)}$  and  $I_{BIAS(ON)}$  are the quiescent currents flowing into the V<sub>IN</sub> pin and V<sub>BIAS</sub> pin when an LDO is operating under the test conditions specified in a datasheet.  $I_{IN(ON)}$  and  $I_{BIAS(ON)}$  are specified under a zero-load current ( $I_{OUT} = 0$  mA).

### Datasheet example: TCR8BM series (800 mA LDO)

| Characteristics   | Symbol Test Condition — |                                    | T <sub>j</sub> = 25°C |      |     | T <sub>j</sub> = -40 | Unit |      |

|-------------------|-------------------------|------------------------------------|-----------------------|------|-----|----------------------|------|------|

| Characteristics   |                         |                                    | Min                   | Тур. | Max | Min                  | Max  | Unit |

| Quiescent current | I <sub>IN(ON)</sub>     | $I_{OUT} = 0 mA, V_{IN} current$   | -                     | 3    | -   | -                    | 6    | μA   |

| Quiescent current | I <sub>BIAS(ON)</sub>   | $I_{OUT} = 0 mA, V_{BIAS} current$ | Ι                     | 20   | -   | -                    | 36   | μA   |

### 6.7. Standby current $(I_{B(OFF)}, I_{IN(OFF)}, I_{BIAS(OFF)})$

$I_{B(OFF)}$ ,  $I_{IN(OFF)}$ , and  $I_{BIAS(OFF)}$  are the current flowing through the V<sub>IN</sub> and V<sub>BIAS</sub> pins when an LDO is in standby mode. LDOs in a battery-operated device draw standby current from a battery while it is in standby mode. Therefore,  $I_{B(OFF)}$ ,  $I_{IN(OFF)}$ , and  $I_{BIAS(OFF)}$  are important characteristics to conserve battery life.

#### Datasheet example: TCR3UM series (300 mA LDO)

| Characteristics | Cumphal                 | Symbol Test Condition                                  |     | T <sub>j</sub> = 25°C |     |     | $T_j = -40$ to $85^{\circ}C$ |      |  |

|-----------------|-------------------------|--------------------------------------------------------|-----|-----------------------|-----|-----|------------------------------|------|--|

| Characteristics | Symbol Test Condition — |                                                        | Min | Тур.                  | Max | Min | Max                          | Unit |  |

| Ctandhu aumont  | I <sub>B (OFF1)</sub>   | $V_{CT} = 0 V, V_{IN} = 2.5 V$                         | —   | 0.03                  | _   | -   | 0.16                         |      |  |

| Standby current | I <sub>B (OFF2)</sub>   | $V_{CT} = 0 \text{ V}, \text{ V}_{IN} = 5.5 \text{ V}$ | _   | 0.03                  |     | _   | 0.20                         | μA   |  |

### 6.8. ADJ pin current (I<sub>ADJ</sub>)

$I_{\text{ADJ}}$  is the input current to an error amplifier connected to the  $V_{\text{ADJ}}$  pin.

### Datasheet example: <u>TCR15AG series (1.5 A LDO)</u>

| Characteristics | Symbol                                | Symbol Tost Condition    |     | T <sub>j</sub> = 25°C |     |     | $T_j = -40$ to $85^{\circ}C$ |      |

|-----------------|---------------------------------------|--------------------------|-----|-----------------------|-----|-----|------------------------------|------|

| Characteristics | Characteristics Symbol Test Condition |                          | Min | Тур.                  | Max | Min | Max                          | Unit |