# IEGT (PPI)

(PPI: Press Pack IEGT)

アプリケーションノート

## 目次

| 1. | IEGT(PPI)の構造と特長               | 4  |

|----|-------------------------------|----|

|    | 1.1. 圧接型パッケージ                 | 4  |

|    | 1.2. IEGT の構造と特長              | 5  |

|    | 1.3. IGBT の断面構造と高耐圧化への問題点     | 6  |

|    | 1.4. IEGT のゲート構造の特長と IE 効果の適用 | 6  |

| 2. | 用語と特性                         | 7  |

|    | 2.1. 特性データの意味                 | 8  |

|    | 2.2. 各データの見方                  | 8  |

|    | 2.3. 絶対最大定格                   | 16 |

|    | 2.4. 電気的特性                    | 18 |

| 3. | 半導体製品採用にあたって                  | 20 |

|    | 3.1. IEGT(PPI)素子選定            | 20 |

|    | 3.2. 静電気対策 および ゲート保護          | 21 |

|    | 3.3. 保護回路の設計                  | 21 |

|    | 3.4. 放熱設計                     | 22 |

|    | 3.5. ドライブ回路の設計                | 22 |

|    | 3.6. 実装上の注意事項                 | 22 |

|    | 3.7. 保管、運搬上の注意事項              | 22 |

|    | 3.8. 信頼性上からの注意事項(寿命設計)        | 23 |

|    | 3.9. その他 実使用上の注意事項            | 23 |

| 4. | 保護回路の設計方法                     | 24 |

|    | 4.1. サージ電圧保護                  | 24 |

|    | 4.2. サージ電圧発生例(ダイオードの小電流の逆回復)  | 26 |

|    | 4.3. 短絡保護                     | 26 |

|    | 4.4. 放熱理論                     | 28 |

|    | 4.4.1. 熱等価回路                  | 28 |

|    | 4.4.2. 損失計算                   | 28 |

|    | 4.4.3. ジャンクション温度のパルス応答        | 29 |

|    | 4.4.4. 放熱フィンの設計               | 30 |

## **TOSHIBA**

|    | 4.4.5 | . 圧接状態の確認                                | 32 |

|----|-------|------------------------------------------|----|

|    | 4.4.6 | . IEGT(PPI)の最大許容印加パワー                    | 33 |

|    | 4.4.7 | . IEGT(PPI)の TFT 耐量と ΔTc                 | 33 |

| 5. | ゲー    | トドライバー回路設計                               | 34 |

| 6. | アプリ   | Jケーションの適用                                | 35 |

|    | 6.1.  | 直流送電変換機                                  | 35 |

|    | 6.2.  | 静止型無効電力補償装置(SVC: Static Var Compensator) | 35 |

|    | 6.3.  | 中電圧以上のインバーター装置(Medium Voltage Inverter)  | 36 |

| 7. | 信賴    | 9性に関する情報                                 | 36 |

|    | 7.1.  | 概要                                       | 36 |

|    | 7.2.  | パワーデバイスの信頼性                              | 36 |

|    | 7.3.  | 宇宙線耐量について                                | 37 |

|    | 7.4.  | SCFM (Short Circuit Failure Mode)        | 38 |

|    | 7.5.  | 代表的な信頼性試験                                | 40 |

|    | 7.6.  | IEGT(PPI)の信頼性要件                          | 41 |

|    | 7.7.  | IEGT(PPI)の熱疲労モード                         | 42 |

|    | 7.8.  | IEGT(PPI)の故障モード                          | 42 |

| 8. | トラス   | ブル発生時の対応                                 | 42 |

| 製  | 品取    | り扱い上のお願い                                 | 45 |

## 1. IEGT(PPI)の構造と特長

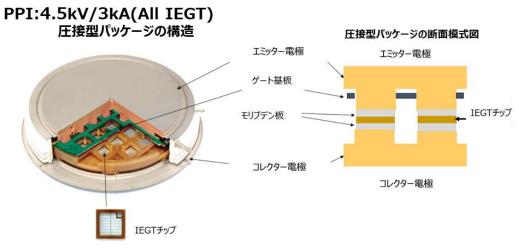

IEGT(PPI)は圧接型パッケージに IEGT(Injection Enhanced Gate Transistor:電子注入促進型絶縁ゲートトランジスター)チップを内蔵したハイパワーデバイスです。

#### 1.1. 圧接型パッケージ

図 1-1 は圧接型パッケージの構造図です。全ての電気的な接続を圧接により実現しています。ワイヤボンディングによる接続は使用していないため、熱疲労に対する高い信頼性が期待できます。万一、製品が電気的に故障破壊した場合でも、電極のコレクターとエミッター間は短絡状態となるため、多数の直列接続で使用する場合には冗長設計により、装置の運転を継続することができます。両面放熱構造を採用しているため、コレクター側、エミッター側の両面冷却が可能です。また、セラミックスと金属による気密封止構造により高い耐候性を持ち、冷却液に直接浸漬させることができるので効率のよい冷却も可能です。

圧接型パッケージの特長として以下があげられます。

● 電気的接続と放熱は圧接により実現 IEGT チップを同一平面状に、その上下にモリブデン板を配置しています。チップのコレクターとエミッターの電極は、このモリブデン板を介して、それぞれコレクターとエミッターの銅電極に機械的圧接力で接触させ、電気的接続と放熱を行います。

#### 気密封止構造による高耐候性

不活性ガスをデバイス内部に気密封止してチップ電極表面の酸化による劣化を防ぎ、環境的に高い信頼性を実現しています。

#### ● 優れた並列動作技術

並列接続された多数の IEGT チップが、スイッチング時に互いに干渉して発振しないように、ゲート基板内の配線を最適化して均一動作させています。

#### ● 破裂を抑えるパッケージ構造

IEGT チップをガイドする樹脂フレーム構造により、チップがスイッチング動作によって破壊溶融しても、パッケージが破裂しにくい構造となっています。

図 1-1 圧接型パッケージの構造

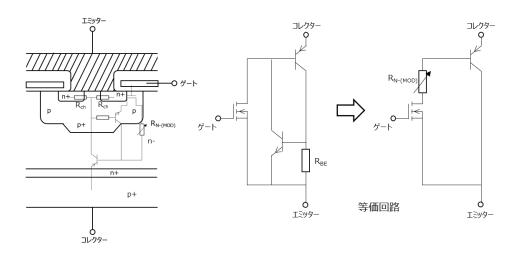

#### 1.2. IEGT の構造と特長

IEGT(Injection Enhanced Gate Transistor:電子注入促進型絶縁ゲートトランジスター)は、電圧駆動で大電流を制御できるパワーデバイスです。IGBT(Insulated Gate Bipolar Transistor:絶縁ゲート型トランジスター)を高耐圧化すると急激にオン電圧が増大する問題を、IEGTではエミッター側の素子構造を最適化することによって、低オン電圧特性を実現しています。 IEGT のベースとなる n チャネル IGBT の基本構造と等価回路を図 1-2 に示します。構造は MOSFETと類似であり、MOSFETが n<sup>+</sup>-n<sup>-</sup> 基板を使用しているのに対し、p<sup>+</sup>-n<sup>+</sup>-n<sup>-</sup> 基板を採用していることです。したがって基板以降の製造プロセスは基本的には MOSFETと類似プロセスです。等価回路上、PNP-NPNトランジスター結合によるサイリスターが形成されていますが、構造図に示すように NPNトランジスターのベースとエミッターは AI 配線で短絡し、できる限り動作しないよう設計され、IGBT の基本動作には無関係です。したがって n チャネル IGBT の等価回路および動作機構は、n チャネルエンハンスメント MOSFET を入力段に、PNPトランジスターを出力段に配した MOS 入力インバーテッドダーリントンと同じです。

IGBT の特徴は、等価回路から説明される動作だけでなく、MOSFET と PNP トランジスターがモノリシック構成であることによる n 一層の伝導度変調が重要です。 p + - n + 層から n ー層に注入されたホール(少数キャリアー)により n ー層に伝導度変調 (MOSFET のドレイン抵抗の減少)が起こります。 この伝導度変調機構により MOSFET の高耐圧素子では困難であった低飽和電圧特性が IGBT では得られます。

IGBT の飽和電圧 VCE(sat)を等価回路から見ると、

$V_{CE(sat)} = V_{BE} + I_{MOS}[R_{N-(MOD)} + R_{ch}]$

VBE: PNP トランジスターのベース-エミッター間電圧

I<sub>MOS</sub>: MOSFET のドレイン電流

$R_{N-(MOD)}$ : 伝導度変調後の  $n^-$ 層抵抗

R<sub>ch</sub>: MOSFET のチャネル抵抗

で表されます。また MOSFET と PNP トランジスター電流( $I_{C(PNP)}$ )、IGBT のトータル電流( $I_{IGBT}$ )の関係は、

$I_{MOS}=I_{C(PNP)}/h_{FE}$

$I_{IGBT}=I_{MOS}+I_{C(PNP)}$

で表され PNP トランジスターの h<sub>FE</sub>(直流電流増幅率)は IGBT の飽和電圧-スイッチング特性のトレードオフ関係を大きく左右します。

図 1-2 IGBT の基本構造と等価回路

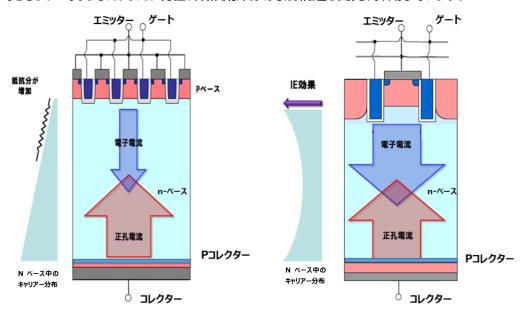

#### 1.3. IGBT の断面構造と高耐圧化への問題点

図 1-3 は、従来の IGBT の断面構造と n<sup>-</sup>ベース中のキャリアー分布を示しています。キャリアー分布は、コレクター電極側からエミッター電極側に近づくにつれて単調に減少しています。高耐圧化のためには、コレクター-エミッター間の n<sup>-</sup>ベース領域を広くする必要があるため、キャリアーの少ない領域が厚くなり、その抵抗分が増加して電圧降下が増大します。すなわち、オン電圧が大きくなるという問題がありました。

#### 1.4. IEGT のゲート構造の特長と IE 効果の適用

図 1-4 に、IEGT の断面構造と n<sup>-</sup>ベース中のキャリアー分布を示します。IGBT に比較して、エミッター構造を最適化する ことにより、エミッター電極へ抜ける抵抗が高くなり、キャリアーの抜けが抑制されます。その結果、キャリアーの蓄積が起き、n<sup>-</sup>ベースのキャリアー分布がエミッター電極側で増加します。このようにキャリアーが注入蓄積されたようにすることを IE 効果 (Injection Enhancement Effect)と呼んでいます。このエミッター側構造の採用により、高耐圧化しても電圧降下の増大を抑えることができるようになりました。また、現在、類似効果がある別構造も開発、採用しています。

図 1-3 IGBT 断面構造とキャリアー分布

図 1-4 IEGT 断面構造とキャリアー分布

IEGT の特長は下記のとおりです。

- 高耐圧、低オン抵抗

- IGBT 同等の広い安全動作領域(高 di/dt、dv/dt 耐量)、アノードリアクトルレス、スナバー回路の簡素化

- 電圧駆動による駆動回路の小型化

- 高速スイッチング動作

高耐圧、低オン抵抗の他、優れた遮断能力と高破壊耐量を備えているため、機器の小型、効率化に貢献します。産業用ドライブ装置、電力用変換装置など、社会インフラを支えている産業分野で性能を発揮します。複数の定格電流-電圧の製品を用意していますので、応用装置の電力容量や負荷特性に合わせて選択が可能です。

#### 2. 用語と特性

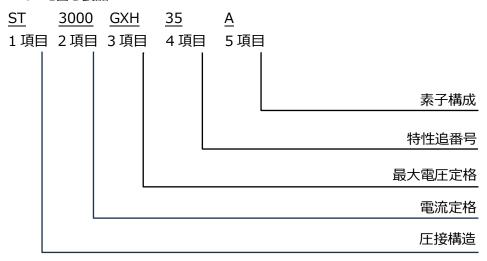

#### 製品名

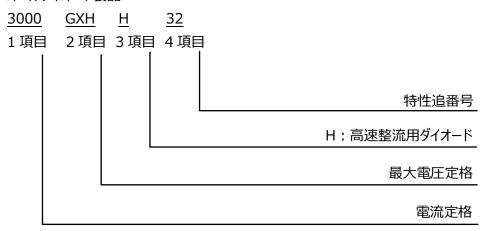

IEGT(PPI)の製品名は次のように構成されています。

IEGT を含む製品

オールダイオード製品

上記それぞれ3、2項目の文字の意味は下記のとおりです。

| 3、2項の文字 | 最大電圧(V) |

|---------|---------|

| GXH     | 4500    |

| JXH     | 6500    |

IEGT を含む製品の5項目は下記のとおりです。

A: IEGT を搭載しています。逆並列接続のフリーホイールダイオードは非搭載です。

記号無し:内部にIEGTと逆並列に接続したフリーホイールダイオードを搭載しています。

例:ST2000GXH32 フリーホイールダイオード入り 4500V/2000A IEGT(PPI)

#### 2.1. 特性データの意味

IEGT(PPI)は、全て IEGT が内蔵されているタイプ(ALL IEGT)、IEGT とフリーホイールダイオード(FWD)が内蔵されているタイプ、また全てフリーホイールダイオードが内蔵されているタイプがあります。 IEGT、FWD それぞれで素子が ON 状態にあるときの損失を導通損失といい、ON から OFF または OFF から ON 状態に変化する瞬間に発生する損失をスイッチング損失と言います。

導通損失に関係するデータは  $I_C$ - $V_{CE}$ 、出力特性、 $I_F$ - $V_F$ です。

スイッチング損失に関係するデータは  $E_{on}$ - $I_C$ 、 $E_{off}$ - $I_C$ 、 $E_{rr}$ - $I_F$ 、 $E_{on}$ - $R_{G(on)}$ 、 $E_{off}$ - $R_{G(off)}$ 、 $E_{rr}$ - $R_{G(on)}$ です。

IEGT のドライブ回路の容量設計に必要なデータは  $V_{GE}$ - $Q_g$  、 $C_{ies}$ , $C_{oes}$ , $C_{res}$ - $V_{CE}$  で、ドライブ回路に入力する ON 信号のタイミングに関係するデータは  $t_{d(on)}$ 、 $t_r$ 、 $t_{d(off)}$ 、 $t_f$ 、 $t_{rr}$  です。

放熱設計に関係するデータは Rth(i-f)-t です。

IEGT の OFF 動作時における安全動作領域を示すデータは RBSOA で、 FWD の逆回復動作時における安全動作領域を示すデータは RRSOA です。

#### 2.2. 各データの見方

IEGT(PPI)の特性を、ST2000GXH32の例にとり、データシートなどに記載されているデータについて以下で説明します。

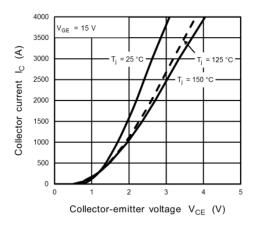

#### (1) Ic-VcE

図 2-1 は素子の G-E 間に+15V を印加し素子を ON させた状態で C-E 間に流れる電流( $I_C$ )と、その際 C-E 間に発生するドロップ電圧( $V_{CE}$ )の関係を示したデータです。ご使用時の通電電流  $I_C$ とその際のドロップ電圧( $V_{CE}$ )の積で素子の ON 時の導通損失( $P_{sat}$ )が計算できます。ご使用の際は素子の温度は上昇するので、適切な温度カーブを使って電力計算にご使用ください。

図 2-1 I<sub>C</sub>-V<sub>CE</sub>特性例

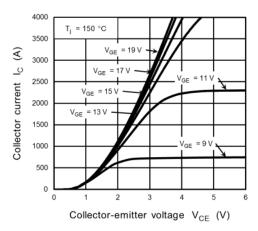

#### (2) 出力特性

図 2-2 は  $I_{C}$ - $V_{CE}$  特性のうち、 $T_{j}$ =150Cまたは  $T_{j}$ =125Cで G-E 間電圧( $V_{GE}$ )を振って  $I_{C}$ を可変し C-E 間電圧( $V_{CE}$ )を測定したものです。 ご使用の  $I_{C}$ 条件で、導通損失を下げる為に必要な  $V_{GE}$  電圧を求める為のデータです。

図 2-2 出力特性例

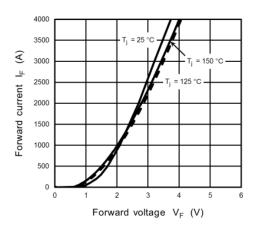

#### (3) $I_F-V_F$

図 2-3 は FWD に順方向電流( $I_F$ )を流した際のアノード-カソード間のドロップ電圧( $V_F$ )を示すデータです。  $I_{C^-}V_{CE}$  特性と同様に FWD の導通損失( $P_F$ )が計算できます。ご使用の際は素子の温度は上昇するので、適切な温度カーブを使って電力計算にご使用ください。

図 2-3 I<sub>F</sub>-V<sub>F</sub>特性例

#### (4) $E_{on}$ - $I_C$ , $E_{off}$ - $I_C$

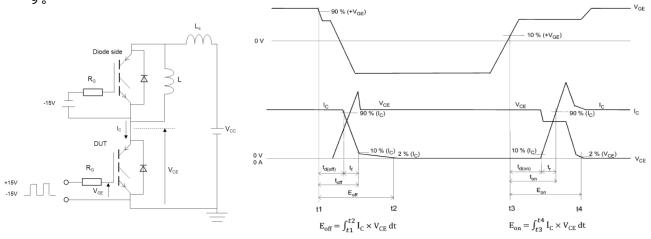

IEGT をスイッチングさせてご使用される場合の測定回路を図 2-4、各部の波形を簡略化したものが図 2-5 です。

図 2-4 誘導負荷スイッチング測定回路図

図 2-5 タイミングチャート (IEGT部)

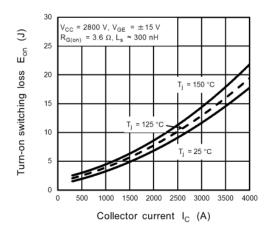

$E_{on}$  は図 2-4 の素子が ON する際に発生する電力損失で図 2-5 の電流波形( $I_{C}$ )と電圧波形( $V_{CE}$ )の積を  $E_{on}$  と記載した期間積分したエネルギーです。また、  $E_{on}$  を  $I_{C}$  可変して求めたデータが図 2-6 です。ご使用  $I_{C}$  時の  $E_{on}$  を求め、この値にご使用周波数を掛けるとターンオン損失( $P_{on}$ )が求められます。

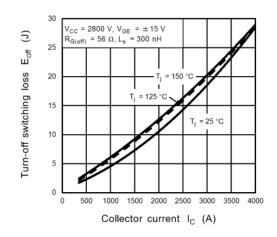

$E_{off}$ は図 2-4 の素子が OFF する際に発生する電力損失で図 2-5 の電流波形( $I_{C}$ )と電圧波形( $V_{CE}$ )の積を  $E_{off}$ と記載した期間積分したエネルギーです。また、 $E_{off}$ を  $I_{C}$  可変して求めたデータが図 2-7 です。ご使用  $I_{C}$  時の  $E_{off}$ を求め、この値にご使用周波数を掛けるとターンオフ電力損失( $P_{off}$ )が求められます。

図 2-6 Eon-Ic 特性例

図 2-7 Eoff-Ic 特性例

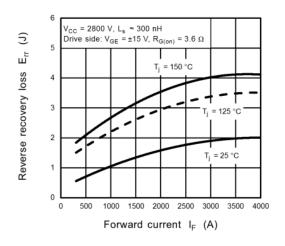

#### $(5) E_{rr}-I_{F}$

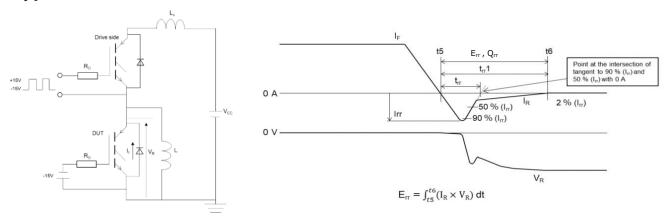

FWD をスイッチングさせてご使用される場合の測定回路を図 2-8、各部の波形を簡略化したものが図 2-9 です。

図 2-8 ダイオード測定回路図

図 2-9 タイミングチャート(FWD部)

図 2-9 の電流波形( $I_R$ )と電圧波形( $V_R$ )の積を  $E_{rr}$ と記載した期間積分したエネルギーが  $E_{rr}$ で、 $I_F$ を可変した際の  $E_{rr}$ のデータが図 2-10 です。ご使用  $I_F$ 時の  $E_{rr}$ を求め、この値にご使用周波数を掛けると FWD のスイッチング損失( $P_{rr}$ )が求められます。

図 2-10 E<sub>rr</sub>-I<sub>F</sub>特性例

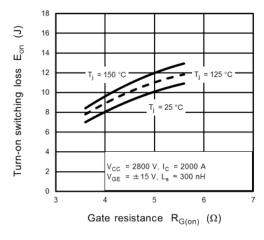

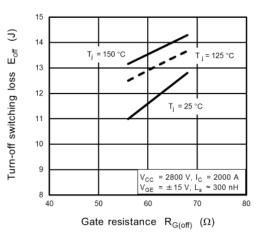

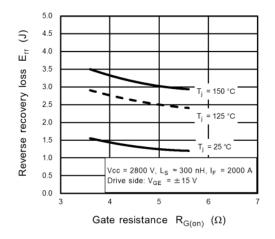

#### (6) $E_{on}$ - $R_{G(on)}$ , $E_{off}$ - $R_{G(off)}$ , $E_{rr}$ - $R_{G(on)}$

前記 E<sub>on</sub>、E<sub>off</sub>、E<sub>rr</sub>の測定条件のうち、図 2-4、図 2-8 の R<sub>G(on)</sub>、R<sub>G(off)</sub>を可変させたデータが図 2-11、図 2-12、図 2-13 です。IEGT はドライブ回路の R<sub>G</sub>を可変することによってスイッチング時間やスイッチング損失やスイッチング時に発生するサージ電圧が変化しますが、その際、スイッチング時間とスイッチング損失はサージ電圧と背反の関係にありますので、R<sub>G</sub>を決める際はそれらを考慮して最適値を決定することをお勧めします。

図 2-11 E<sub>on</sub>-R<sub>G(on)</sub>特性例

図 2-12 E<sub>off</sub>-R<sub>G(off)</sub>特性例

図 2-13 Err-R<sub>G(on)</sub>特性例

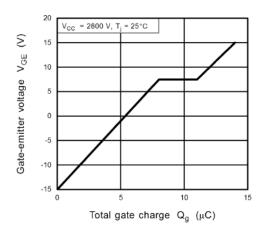

#### (7) V<sub>GE</sub>-Q<sub>g</sub>

IEGT のゲートドライブ回路を設計する際に必要な入力電荷量に関するデータを図 2-14 示します。この特性はゲート入力電荷量(Qg)に対するゲート-エミッター間電圧(VGE)の変化を示しています。IEGT を ON するのに必要なゲート容量への充電電荷量を示します。この値にご使用周波数を掛けるとドライブ回路に必要な電流供給能力が求められます。

図 2-14 V<sub>GE</sub>-Q<sub>g</sub> 特性例

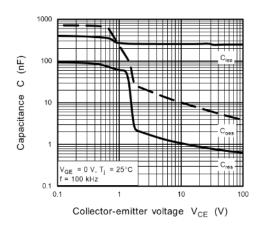

#### (8) Cies, Coes, Cres-VCE

IEGT はゲート-エミッター間、コレクター-エミッター間、コレクター-ゲート間に接合容量があります。具体的には C<sub>ies</sub> はゲート-エミッター間の入力容量、C<sub>oes</sub> はコレクター-エミッター間の出力容量、C<sub>res</sub> はコレクター-ゲート間の帰還容量です。コレクター-エミッター間電圧 V<sub>CE</sub> を変化させたときの各容量のデータを図 2-15 に示します。V<sub>GE</sub>-Q<sub>g</sub> 特性と併せてドライブ回路の設計に使用ください。

図 2-15 C<sub>ies</sub>, C<sub>oes</sub>, C<sub>res</sub>-V<sub>CE</sub> 特性例

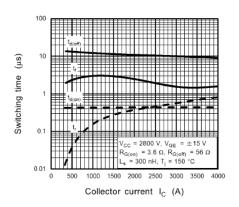

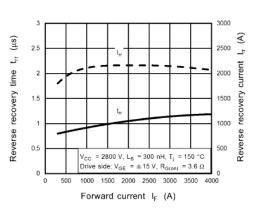

#### (9) $t_{d(on)}$ , $t_r$ , $t_{d(off)}$ , $t_f - I_c$ , $t_{rr}$ , $I_{rr} - I_F$

図 2-5 と図 2-9 で定義された項目の電流依存を取得したデータが図 2-16、図 2-17 です。上下直列接続された IEGT を ON、OFF させる際に、それらを同時に ON すると素子に主電源から過大な貫通電流が流れるので、損失の増大による発熱や、最悪の場合は破壊の可能性がある為、どちらの素子も ON しない休止期間を設ける必要があります。その際の各素子への入力信号のタイミング設計に使用するデータです。

図 2-16 t<sub>d(on)</sub>, t<sub>r</sub>, t<sub>d(off)</sub>, t<sub>f</sub> -I<sub>c</sub> 特性例

図 2-17 trr, Irr-IF 特性例

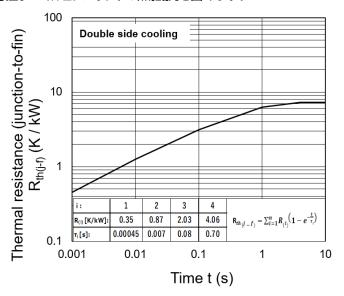

#### $(10) R_{th(j-f)}-t$

図 2-18 は放熱設計を行う為のデータです。一般に印加時間(t)の間に電力( $P_c$ )が印加された場合のチップの温度上昇は  $R_{th(j-f)}(t) \times P_C$ で示されます。 図 2-18 の  $R_{th(j-f)}$ は IEGT(PPI)のジャンクション(接合)と冷却フィン間の熱抵抗で、導電性サーマルコンパウントの熱抵抗を含みます。

図 2-18 R<sub>th(j-f)</sub>-t 特性例

図 2-18 中の表は n=4 の場合の Foster モデル(図 2-19)の各係数を示しています。 Rth(j-f)は抵抗 R と時定数  $\tau$  を用いて次式で表現されます。 この式を用いると任意の時間 t の Rth(j-f) をもとめることができます。

$$\begin{split} R_{th(j-f)} &= \Sigma_{i=1}^{n} R_{(i)} \left( 1 - e^{-\frac{t}{\tau_{i}}} \right) \\ \tau_{i} &= R_{(i)} c_{(i)} \end{split} \qquad \begin{matrix} T_{j} \\ \\ \\ n=1 \end{matrix} \qquad \begin{matrix} T_{j} \\ \\ n=2 \end{matrix} \qquad \begin{matrix} T_{j} \\ \\ n=3 \end{matrix} \qquad \begin{matrix} T_{f} \\ \\ n=4 \end{matrix} \qquad \begin{matrix} T_{f} \\ n=4 \end{matrix}$$

図 2-19 Foster モデル (n=4 の例)

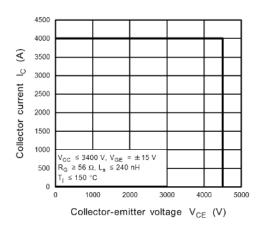

#### (11) RBSOA

IEGT が ON 状態から OFF 状態になった際に、回路の浮遊インダクタンスにより素子にサージ電圧が発生します。図 2-20 は OFF 時の遮断電流とその際に発生するサージ電圧をルーカスで示した場合の素子が破壊しない領域(安全動作領域)RBSOA を示したデータです。ご使用のターンオフ波形のルーカスがこの領域内に入るように設計(回路の浮遊インダクタンスの低減やサージ吸収回路の追加やターンオフ速度の緩和など)頂く必要があります。

図 2-20 RBSOA 特性例

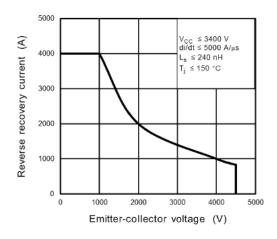

#### (12) RRSOA

FWD の逆回復動作(図 2-9 参照)時の逆回復電流とその際に素子に発生するエミッター-コレクター間電圧のルーカスの安全動作領域 RRSOA を示したデータが図 2-21 です。ご使用時の FWD の逆回復動作時の波形がこの範囲に収まるように設計(回路の浮遊インダクタンス低減やターンオン時間の緩和による di/dt の緩和など)頂く必要があります。

図 2-21 RRSOA 特性例

#### 2.3. 絶対最大定格

絶対最大定格として記載されている値は、動作中に瞬時といえども超えてはなりません。また絶対最大定格以内であっても 余裕ないご使用条件の場合、信頼性(素子寿命)に影響する場合がありますので、当社信頼性ハンドブックをご一読頂きご 要求寿命に適したディレーティングを実施願います。

| 安小村間に過じたテイレーティファ | 2 3.23,7.7 31.    | 定義 および 内容                                       |  |  |

|------------------|-------------------|-------------------------------------------------|--|--|

| 項目               | 記号                |                                                 |  |  |

|                  |                   | ゲート-エミッター間ゼロバイアス時(ゲート-エミッター間を短絡した状態)コレ          |  |  |

|                  |                   | クター・エミッター間に印加可能な最大電圧です。実使用時に発生するサ               |  |  |

| コレクター・エミッター間電圧   | $V_{CES}$         | ージによる電圧は VCES 値よりも低く個々の素子の RBSOA や RRSOA        |  |  |

|                  |                   | データを参考にサージ電圧の許容値を決める必要があります。                    |  |  |

|                  |                   | コレクター-エミッター間ゼロバイアス時(コレクター-エミッター間を短絡した状          |  |  |

|                  |                   | 態)でゲート-エミッター間に印加可能な最大電圧です。ただし、VGES 以            |  |  |

| ゲート-エミッター間電圧     | $V_{GES}$         | 下の電圧印加であっても長期間の電圧印加は IEGT のゲート酸化膜の              |  |  |

|                  |                   |                                                 |  |  |

|                  |                   | 寿命を考慮する必要があります。                                 |  |  |

|                  | .,                | FWD のカソード-アノード間に繰り返し印加可能な最大電圧です。実使              |  |  |

| ピーク繰り返し逆電圧       | $V_{RRM}$         | 用時に発生するサージによる電圧は VRRM 値よりも低く、個々の素子の             |  |  |

|                  |                   | RRSOAデータを参考にサージ電圧の許容値を決める必要があります。               |  |  |

|                  | I <sub>C</sub>    | コレクター電流に許容される最大直流電流です。ただし、素子の電力損                |  |  |

|                  |                   | 大や放熱条件で制限され、最大ジャンクション温度 T <sub>j</sub> を超えない条件で |  |  |

| コレクター電流          |                   | 使用する必要があります。                                    |  |  |

| 2000             | I <sub>CP</sub>   | コレクター電流に許容される最大パルス電流です。ただし、素子の電力損               |  |  |

|                  |                   | 失や放熱条件で制限され、最大ジャンクション温度 Tj を超えない条件で             |  |  |

|                  |                   | 使用する必要があります。                                    |  |  |

|                  |                   | FWD に許容される最大直流電流です。ただし、素子の電力損失や放熱               |  |  |

|                  | ${ m I}_{\sf F}$  | 条件で制限され、最大ジャンクション温度 Tj を超えない条件で使用する             |  |  |

| 順電流              |                   | 必要があります。                                        |  |  |

| 順 <b>竜</b> 流     |                   | FWD に許容される最大パルス電流です。ただし、素子の電力損失や放               |  |  |

|                  | ${ m I}_{\sf FP}$ | 熱条件で制限され、最大ジャンクション温度 Tj を超えない条件で使用す             |  |  |

|                  |                   | る必要があります。                                       |  |  |

|                  |                   | 指定された温度で、50 Hz または 60 Hz の商用正弦半波 1 サイク          |  |  |

| 非繰り返しピーク順電流      | I <sub>FSM</sub>  | ル、10 ms のパルス幅を持つ矩形波、または、指定された条件の電流を             |  |  |

|                  |                   | 順方向に流したときに FWD が破壊しない非繰り返し最大電流値です。              |  |  |

| <b></b>          | -2                | 10 ms 以下のパルス幅の単発正弦半波で、FWD 順方向に流すことの             |  |  |

| 電流2乗時間積          | I <sup>2</sup> t  | できる非繰り返しの最大電流値を算出するためのパラメーターです。                 |  |  |

|                  |                   |                                                 |  |  |

次ページに続く

| 項目              | 記号                  | 定義 および 内容                          |

|-----------------|---------------------|------------------------------------|

|                 |                     | (測定条件および規格値は各製品の個別データシートを参照願います)   |

|                 |                     | 1 素子に許容される最大電力損失です。ただし、保証値は素子のケース  |

| <br>  コレクター許容損失 | Pc                  | 温度=25℃に固定できた場合の理想的な理論値であり、実用時の有    |

| コレフノー計合領人       | PC                  | 限放熱条件ではディレーティングしてご使用頂く必要があります。(詳細は |

|                 |                     | 放熱設計の説明をご参照ください。)                  |

|                 |                     | 1 素子に許容される最大電力損失です。ただし、保証値は素子のケース  |

| <br>ダイオード許容損失   | P <sub>D</sub>      | 温度 = 25℃に固定できた場合の理想的な理論値であり、実用時の有  |

| グイオート計合損大       |                     | 限放熱条件ではディレーティングしてご使用頂く必要があります。(詳細は |

|                 |                     | 放熱設計の説明をご参照ください。)                  |

|                 | Tj                  | 正常に動作可能なチップ接合部(ジャンクション)温度の最大値です。ジャ |

| 接合温度            |                     | ンクション温度は信頼性に影響しますので、設計時の考慮が必要です。詳  |

|                 |                     | 細は信頼性ハンドブックをご参照願います。               |

|                 | T <sub>j(opr)</sub> | 継続した動作で、正常に動作可能なチップ接合部(ジャンクション)温度の |

| 動作接合温度          |                     | 最大値です。ジャンクション温度は信頼性に影響しますので、設計時の考  |

|                 |                     | 慮が必要です。詳細は信頼性ハンドブックをご参照願います。       |

| 保存温度            | T <sub>stg</sub>    | 素子に電気的な負荷を掛けずに保存や輸送する場合の温度範囲です。    |

| 圧接力             | -                   | 素子を圧接する際の圧接力範囲です。                  |

## 2.4. 電気的特性

|     |                                       | 記号                   | 定義 および 内容                                |  |  |

|-----|---------------------------------------|----------------------|------------------------------------------|--|--|

|     | 項目                                    |                      | (測定条件および規格値は各製品の個別データシートを参照願います)         |  |  |

|     |                                       |                      | ゲートとエミッターの電極を短絡し、コレクターとエミッターの間に指定の電圧を印   |  |  |

|     | コレクター・エミッター間遮断                        | $I_{CES}$            | 加した際に流れるコレクター電流値です。温度によって増加するため、必要に応     |  |  |

|     | 電流                                    |                      | じて損失として考慮が必要です。                          |  |  |

|     |                                       |                      | コレクターとエミッターの電極を短絡し、ゲートとエミッターの間に指定の電圧を印   |  |  |

|     | ゲート漏れ電流                               | ${ m I}_{\sf GES}$   | 加した際に流れるゲート電流値です。ゲート酸化膜の漏れ電流であるため、温      |  |  |

|     |                                       |                      | 度による増加は少ないです。                            |  |  |

|     |                                       |                      | 指定のコレクター-エミッター間電圧を印加し、指定のコレクター電流を流すための   |  |  |

|     | ゲート-エミッター間遮断電圧                        |                      | ゲート-エミッター間印加電圧値です。この値を超えるサージ電圧がゲート-エミッタ  |  |  |

| 軐   |                                       | $V_{GE(off)}$        | -間に発生すると素子が誤 ON する場合がある為、設計時のサージ電圧の確     |  |  |

| 静特性 |                                       |                      | 認が必要です。                                  |  |  |

| ### |                                       |                      | ゲート-エミッター間に指定の電圧を印加しコレクターに指定の電流を流した際の    |  |  |

|     | コレクター・エミッター間飽和                        | V <sub>CE(sat)</sub> | コレクター・エミッター間の電圧値です。素子の導通損失に影響する重要特性の     |  |  |

|     | 電圧                                    | ▼ CE(Sat)            | ため、この値が十分低くて安定になるように VGES 以下でゲート-エミッター間に |  |  |

|     |                                       |                      | 電圧を印加する必要があります。                          |  |  |

|     | 入力容量                                  | C <sub>ies</sub>     | コレクター-エミッター間とゲート-エミッター間に指定の電圧を印加した際のゲート- |  |  |

|     | 7030±                                 |                      | エミッター間の静電容量値です。                          |  |  |

|     | 出力容量                                  | C <sub>oes</sub>     | コレクター-エミッター間とゲート-エミッター間に指定の電圧を印加した際のコレクタ |  |  |

|     |                                       |                      | ー-エミッター間の静電容量値です。                        |  |  |

|     | 帰還容量                                  | C <sub>res</sub>     | コレクター-エミッター間とゲート-エミッター間に指定の電圧を印加した際のコレクタ |  |  |

|     |                                       |                      | ー-ゲート間の静電容量値です。                          |  |  |

|     | 順電圧                                   | V <sub>F</sub>       | FWD に指定の順バイアス電流を流した際のアノード-カソード間の電圧値です。   |  |  |

|     | ····································· | ۷F                   | 素子の導通損失に影響する重要特性です。                      |  |  |

|     | ターンオン遅延時間                             | <b>+</b>             | IEGT がターンオンする際にゲート電圧の設定値の 10%時点からコレクター   |  |  |

|     | ノ フバフ圧延り回                             | t <sub>d(on)</sub>   | 電流が設定値の 10%になるまでの時間です。                   |  |  |

|     | 上昇時間                                  |                      | IEGT がターンオンする際にコレクター電流が設定値の 10%から 90%にな  |  |  |

|     | 工并的间                                  | t <sub>r</sub>       | るまでの時間です。                                |  |  |

|     | ターンオン時間                               | t <sub>on</sub>      | IEGT がターンオンする際にゲート電圧の設定値の 10%時点からコレクター   |  |  |

| 軐   | ケーンハン・叮旧                              |                      | 電流が設定値の 90%になるまでの時間です。                   |  |  |

| 動特性 | ターンオフ遅延時間                             | _                    | IEGT がターンオフする際にゲート電圧が設定最大値の 90%時点からコレ    |  |  |

| пшп | アーノバノ圧延时间                             | t <sub>d(off)</sub>  | クター電流が設定値の 90%になるまでの時間です。                |  |  |

|     | 下降時間                                  | +-                   | IEGT がターンオフする際にコレクター電流が設定値の 90%時点から 10%  |  |  |

|     | 1、14世41日1                             | t <sub>f</sub>       | になるまでの時間です。                              |  |  |

|     | ターンオフ時間                               |                      | IEGT がターンオフする際にゲート電圧が設定最大値の 90%時点からコレ    |  |  |

|     | ターノハノ吋旧                               | t <sub>off</sub>     | クター電流が設定値の 10%になるまでの時間です。                |  |  |

|     | 短絡耐量                                  |                      | IEGT が指定された条件で短絡動作した際の素子が破壊しないパルス幅で      |  |  |

|     | (パルス幅)                                | $t_{psc}$            | す。                                       |  |  |

|     | -                                     |                      | <u> </u>                                 |  |  |

次ページに続く

| 項目                       |                               | 記号                   | 定義 および 内容<br>(測定条件および規格値は各製品の個別データシートを参照願います)                                               |

|--------------------------|-------------------------------|----------------------|---------------------------------------------------------------------------------------------|

|                          | 逆回復電流                         | I <sub>rr</sub>      | FWD に逆バイアス電圧を印加した際に蓄積されたキャリアーによって流れる電流です。                                                   |

|                          | 逆回復時間 t <sub>rl</sub>         |                      | FWD の逆回復電流 Irrが 0A 時点を起点として、最小電流値に到達後に<br>再び 0A 戻る Irrの 90%-50%の接線が 0A になるまでの時間です。          |

|                          | 逆回復電荷量  Q <sub>rr</sub>       |                      | FWD の逆回復電流 Irrが OA 時点を起点として、最小電流値に到達後に再び OA に戻る逆回復電流が 2%になるまでの FWD の電荷量(逆回復電流と時間の積の積分値)です。  |

| 動特性                      | ターンオンスイッチング損失 E <sub>on</sub> |                      | IEGT がターンオンする際にゲート電圧の設定値の 10%時点からコレクター電圧が設定値の 2%になるまでの時間のコレクター電流とコレクター電圧の積の積分値です。           |

|                          | ターンオフスイッチング損失                 | E <sub>off</sub>     | IEGT がターンオフする際にゲート電圧が設定最大値の 90%時点から、コレクター電流が設定値の 2%になるまでの時間のコレクター電流とコレクター電圧の積の積分値です。        |

|                          | 逆回復損失 E <sub>rr</sub>         |                      | FWD の逆回復電流 Irrが OA 時点を起点として、最小電流値に到達後に再び OA に戻る逆回復電流が 2%になるまでの時間の逆回復電流と FWD に掛かる電圧の積の積分値です。 |

|                          | ゲート充電電荷量                      | Qg                   | IEGT をターンオンさせる為にゲートへ供給が必要な充電電荷量(ターンオフさせる場合は同じ量の放電が必要)です。                                    |

| 熱抵抗 R <sub>th(j-f)</sub> |                               | R <sub>th(j-f)</sub> | IEGT または FWD の等価回路上の 1 素子でのジャンクション-冷却フィン間の飽和熱抵抗値です。                                         |

#### 3. 半導体製品採用にあたって

## 3.1. IEGT(PPI)素子選定

#### (1) 電圧定格

IEGT(PPI)の電圧定格は、適用する装置の入力電源およびその安定度、使用回路定数を考慮する必要があります。目的に応じた素子の選定をお願いします。一般的に定常時には、

● ピーク電圧:素子定格(VCES)の80%以下

● 直流電圧:素子定格(V<sub>CES</sub>)の50~60%以下

で使用することを推奨しています。

非定常時においても素子定格(VCES)の90%以下、で使用されることを推奨しています。

インバーター応用時の素子電圧定格と電源電圧(入力 AC ライン電圧)の関係は次式にまとめられます。

素子定格電圧(V<sub>CES</sub>) = [入力電圧] + [サージ電圧] + [電圧変動分] + [マージン]

入力電圧:交流の場合は√2を掛ける

サージ電圧:回路インダクタンスなどによる跳ね上がり分の最大値

電圧変動分:電力回生などに伴う電圧上昇分

マージン : 安全係数分

#### (2) 電流定格

IEGT(PPI)のコレクター電流が大きくなると V<sub>CE(sat)</sub>が上昇し、発生する導通損失が大きくなります。また、同時にスイッチング損失も増大し素子の発熱が大きくなります。

IEGT(PPI)はその IEGT,FWD の接合部温度( $T_j$ )が最大接合温度  $T_{j(max)}$ 以下となるように使用する必要があります。この選定を誤ると素子破壊、あるいは長期信頼性の低下を招くことがありますので注意が必要です。

インバーター応用の場合は過負荷が設定されていることも多いため一般的には、

- 定常時:素子定格電流の50~60%以下

- 非定常時(最大時):素子定格電流内(かつ接合温度も最大接合温度以下)

で使用することを推奨しています。 なお、素子規格における I<sub>CP</sub> は FWD 逆回復時の逆回復電流を含むピーク値 および各種保護動作時などの事故時を想定した値となっている点に注意願います。(先に記載のとおり最大接合温 度を超えるような繰り返しでの使用はできません。)

一般的なインバーター応用時の電流選定は以下の式で考えることができます。

ピーク電流(I<sub>p</sub>) = [インバーター容量] × [過負荷率] / [交流電圧] / √3 ×√2 × [電流リップル率] 素子定格電流(I<sub>c</sub>) = I<sub>p</sub> / ディレーティング率

インバーター容量: 出力負荷(W) / 効率

交流電圧: 実効値

しかしながら定格電流の選定に関しては、装置の運転条件や放熱条件に依存しますので、その装置での発生損失と温度上昇を確認した上で、電流定格の選定をお願いします。

#### 3.2. 静電気対策 および ゲート保護

IEGT(PPI)の  $V_{GE}$ の保証値は一般的に最大 $\pm 20V$ です(保証値はデータシートに記載されていますので確認願います)。  $V_{GES}$  保証値を超える電圧が G-E 間に印加された場合、IEGT(PPI)のゲートに不具合を起こす危険があります。 G-E 間には保証値を超える電圧が印加されないよう注意、保護をお願いします。

また、IEGT(PPI)のゲートは静電気などに対しても注意が必要なため取り扱いの際には以下の注意点を守って製品を取り扱うようお願いします。

- (1) IEGT(PPI)を取り扱う際には、人体や衣服に帯電した静電気をアースバンドなどで放電させた上で、接地された導電性マット上で作業をしてください。

- (2) IEGT(PPI)の端子部に直接触れずに、パッケージ本体を持って取り扱ってください。この時エミッター、コレクター銅電極部 に汚れなどを付けない様、手袋を着用してください。

- (3) IEGT(PPI)の電極、端子へ配線部材(ブスバー、ワイヤなど)を接続、固定する際には(1)と同様、静電気が IEGT(PPI)に加わらないように、使用材料が帯電しないよう配慮をお願いします。

- (4) IEGT(PPI)は、銅ワイヤ、銅テープなどの導電性材料で G-E 間、C-E 間を静電対策した状態で出荷されています。この 導電性材料は製品の電気的配線直前に取り外してください。

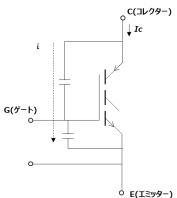

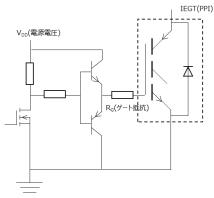

また、ゲート-エミッター間がオープン状態でコレクター-エミッター間に電圧を印加すると、IEGT(PPI)が破壊する可能性があります。これはコレクター電位の変化により図 3-1 に示すように電流(i)が流れてゲート電位が上昇し、IEGT がオンして、コレクター電流が流れる事が原因です。

製品が装置に組み込まれたときに、ゲート回路の故障、あるいはゲート回路が正常に動作しない状態(ゲートがオープン状態)で主回路に電圧が印加されると上記の理由により IEGT(PPI)は破壊することがあります。この破壊防止のためにゲート回路の電源が入っていない状態ではゲート-エミッター間をショート状態にする、ゲート回路電源が入っていること(ゲート-エミッター間に負バイアスとなっていること)が確認できないと主回路が加電できないようにする、など保護回路を付加することを推奨します。

図 3-1 G-E 間オープン状態での IEGT(PPI)の動作

#### 3.3. 保護回路の設計

IEGT(PPI)は、過電流、過電圧といった異常現象により破壊する可能性があります。これらから素子を保護するためにスナバー回路などの保護回路を付加する場合があります。保護回路は、素子の特性および回路動作を十分に理解した上で、素子の特性にマッチングするように設計することが重要です。このマッチングが取れていないと保護回路が付いていても効果が薄く、希望する結果が得られないことがあります。その一例として、過電流保護をかけるときの遮断時間が長過ぎ SOA を逸脱し破壊、スナバー回路のコンデンサー容量が小さくて過大なスパイク電圧が発生することなどが挙げられます。これら過電流、過電圧保護方法は、第4章「保護回路の設計方法」に詳しく説明されていますので、そちらを参照願います。

#### 3.4. 放熱設計

IEGT(PPI)には、許容できる最大接合部温度  $T_{j(max)}$ が決められており、この温度以下になるような放熱設計が必要です。 放熱設計を行なう際には IEGT(PPI)が適用されるアプリケーション動作を十分に考慮した上での設計をお願い致します。 放熱設計が十分でない場合、実機運転中などに素子の許容温度を超え破壊するといった問題が発生する可能性があります。

放熱設計を行なうためには、まず素子の発生損失を算出し、その損失をもとに許容温度以下となるような放熱フィンの選定 を行ないます。この点については第 4.4.4 節「放熱フィンの設計」に詳しい記載がしてありますので、そちらを参照願います。

## 3.5. ドライブ回路の設計

素子の性能を十分に引き出すためにはドライブ回路の設計が重要となります。また、保護回路の設計とも密接に関わっています。

ドライブ回路は、素子をターンオンさせるための順バイアス回路と、素子のオフ状態を安定に保ち、かつターンオフを正確に行うための逆バイアス回路からなり、それぞれの条件設定により素子の特性が変わってきます。また、ドライブ回路の位置、配線方法によっては素子が誤動作するといった問題もでてきます。

最適なドライブ回路を設計することは非常に重要であり、第 5 章「ゲートドライバー回路設計」に記載してありますので、参 照願います。

#### 3.6. 実装上の注意事項

IEGT(PPI)を実装する場合、特に次の事に注意してください。

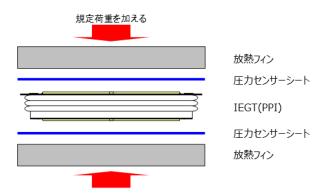

- (1) IEGT(PPI)は主電極間に圧力をかけることで電気的接続と放熱経路とするため、この圧接状態(圧接力、面内の圧接力均一性)が重要となります。また、素子電極面と放熱フィン間には導電性のサーマルコンパウンドを塗布した上で規定の圧接力を印加してください。

- (2) 素子に印加する負荷による温度変化で素子自身が膨張、圧接力が上がることが考えられます。 そのような状態でも圧接力が均一に保てるよう皿ばねなどの併用をお願いします。詳細な説明は、第4章、第 7章を参照願います。

## 3.7. 保管、運搬上の注意事項

#### 保管

- (1) 半導体デバイスを保管しておく場所の温度は5~35℃、湿度は45~75%が望ましいです。

- (2) 腐食性ガスを発生する場所や塵埃の多いところは避けてください。素子納入時の包装箱はダンボールが主材のため長期の保管については適しておりません。保管が長期に及ぶ場合は保管用に別の包装を検討願います。

- (3) 急激な温度変化のある所では、半導体デバイス表面に結露が起こることがあります。このような環境を避けて、 温度変化の少ない場所に保管してください。

- (4) 保管状態では、半導体デバイスに外力または荷重がかからないようにしてください。特に積み重ねた状態では思わぬ荷重がかかることがあります。

- (5) 半導体デバイスを仮置きなどするときの容器は、静電気を帯びにくいものを選定してください。

#### 運搬

- (1) 素子定格-構造上重量が重いものが多くあります。素子の落下により人体にけがをしないよう注意してください。

- (2) 製品の運搬時に衝撃を与えたり、落下させたりしないでください。

- (3) 多数の半導体デバイスを箱に入れて運搬するときは、接触電極面などを傷つけないようにやわらかいスペーサーを素子相互間に入れてください。

## 3.8. 信頼性上からの注意事項(寿命設計)

一般的にインバーターをはじめとする電力変換装置の運転時には、それに組み込まれている IEGT(PPI)は温度の上昇と 下降が繰り返されます。この温度変化により IEGT(PPI)は熱ストレスを受けるため、その運転条件に応じた寿命があります。 それゆえ装置の要求寿命に対して設計寿命を長く設計する必要があります。

このような寿命設計を行なうためには、IEGT(PPI)の温度変化を確認し、熱疲労耐量から寿命設計を行なうのが一般的です。寿命設計が十分に考慮されていない場合、要求寿命に対してその寿命が短くなり、信頼性が確保されないといった問題が発生する可能性があります。それゆえ信頼性を踏まえた寿命設計は重要となります。この点については第7章「信頼性に関する情報」に詳しく記載していますので、参照願います。

#### 3.9. その他 実使用上の注意事項

- (1) 電気的特性の測定時は適切な圧接状態で測定してください。詳細はデータシートの圧接力の項目、第 4.4.5 節、「圧接状態の確認」を参照ください。

- (2) ドライブ電圧(V<sub>GE</sub>)はデバイスの端子部で測定し、所定の電圧が印加されていることをご確認ください(ドライブ 回路端で測定すると駆動回路終端に使用するトランジスターなどの電圧ドロップの影響を受けない電圧になりますので、IEGT(PPI)に所定の V<sub>GE</sub> が印加されていなくてもその不具合に気がつかず、素子破壊に至るという可能性があります)。

- (3) ターンオン-ターンオフ時のサージ電圧などの VCE 測定は製品の電極部で測定してください。

- (4) 製品は絶対最大定格(電圧,電流,温度など)の範囲内でご使用ください。絶対最大定格を超えて使用すると、製品が破壊する場合があります。特に、V<sub>CES</sub>を超えた電圧が印加された場合素子破壊する場合があります。V<sub>CE</sub> は必ず絶対最大定格の範囲内でご使用ください。

- (5) 万一の不慮の事故で素子が破壊した場合を考慮し、主回路コンデンサーと半導体デバイスの間に適切な容量のヒューズまたは故障検出回路を設けて2次破壊を防いでください。

- (6) 製品の使用環境を十分に把握し、製品の信頼性寿命が満足できるか検討の上、適用してください。製品の 信頼性寿命を超えて使用した場合、装置の目標寿命より前に素子が破壊する場合があります。

- (7) 本製品は熱疲労寿命以下で使用ください。熱疲労寿命には短周期パワーサイクル耐量と TFT(Thermal Fatigue Test) 耐量(または長周期パワーサイクル耐量)の大きく 2 通りあり、前者が ΔΤ<sub>j</sub> による場合、後者が ΔΤ<sub>c</sub> による場合となります。ただし、IEGT(PPI)は TFT 耐量のみになります。これらは、本製品をご使用する際の放熱設計に依存します。接合温度の上昇下降のみではなくケース温度の上昇下降についても十分留意してご使用ください。

- (8) 酸、有機物、腐食性ガス(硫化炭素、亜硫酸ガスなど)を発生する場所での使用は避けてください。酸、有機物、腐食性ガス(硫化炭素、亜硫酸ガスなど)を含む環境下で使用された場合、製品機能、外観などの保証は致しかねます。

- (9) 製品を装置に実装する際などで、圧接電極部に過大な応力を与えないでください。電極部の変形により、均一な圧接状態が維持できずデバイスの破壊などを引き起こす場合があります。推奨圧接力は製品仕様書を参照ください。

- (10) FWD のみ使用し、IEGT を使用しないとき(例えばチョッパー回路などへの適用時)は、使用しない IEGT の G-E 間に-5V 以上(推奨-15V、最大-20V)の逆バイアスをかけてください。 逆バイアスが不足すると IEGT が FWD の逆回復時の dv/dt によって誤点弧を起こし、破壊する可能性があります。

- (11) ターンオン dv/dt が高いと対向アームの IEGT が誤点弧を起こす可能性があります。 誤点弧を起こさない為の最適なドライブ条件( $+V_{GE}$ 、 $-V_{GE}$ 、 $R_G$ 、 $C_{GE}$ )でご使用ください。

- (12) 制御端子に過大な静電気が印加された場合、素子が破壊する場合があります。取り扱うときは静電気対策 を実施してください。

- (13) 素子を放熱フィンに取り付ける際には、熱伝導を確保するためのコンパウンドなどをご使用ください。また、塗布量が不足したり、塗布方法が不適だったりすると熱伝導性が低下し、信頼性が低下しますので、コンパウンドを塗布する際には、製品全面にコンパウンドが広がっている事を確認してください。(実装した後に素子を取り外すとコンパウンドの広がり具合を確認することができます。)

- (14) 仕様書に記載の外付け抵抗 R<sub>G</sub> はスイッチング損失を最小化するための推奨抵抗を記載していますが、最適な R<sub>G</sub> は使用される回路構成や使用環境によって変わります。したがって外付け抵抗 R<sub>G</sub> の決定に際しては、IEGT 素子が使用される回路構成や使用環境で、スイッチング損失、EMC/EMI、スパイク電圧、サージ電流や予期しない振動などの特性を十分検討した上で、仕様書に記載の内容から逸脱しないように選定する必要がありますので、ご注意ください。

- (15) 本節では主な実使用上の注意点を記載していますが、詳細につきましては個々の製品の仕様書に記載の 注意、警告内容を遵守いただきますようお願い致します。

#### 4. 保護回路の設計方法

#### 4.1. サージ電圧保護

IEGT のスイッチング時間は数 µs と短いため、高速スイッチングの分野で威力を発揮します。しかし、この高速スイッチング特性のために、回路的な工夫がないと配線インダクタンス Ls によるサージ電圧が IEGT に印加されます。その大きさ V<sub>surge</sub>は、

$$V_{surge} = -L_s \times di/dt + V_{cc}$$

となります。この値がデータシートに記載の主端子間絶対最大定格電圧より十分小さくなるように主回路設計してください。 V<sub>surge</sub> の低減方法は di/dt や配線インダクタンスを小さくすることですが、di/dt を小さくすることは IEGT の高速スイッチング 特性を犠牲にするため、配線インダクタンスを低減する必要があります。例えばワイヤの代わりにはり合わせた銅板を用いると、インダクタンスを大幅に低減させることができます。発生したサージ電圧を低減させるには、スナバー回路を入れることが有効です。

#### スナバー回路の例

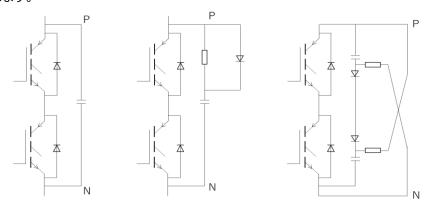

図 4-1 にスナバー回路例を示します。スナバー回路によりサージ電圧を吸収することができますが、IEGT のスイッチング特性、主回路配線構成によりサージ電圧が変わるため、スナバー回路の特性をよく理解した上で回路構成を選択し、実験的に定数を決める必要があります。

(a)P-N 間スナバー

(b)非充電型 RDC スナバー

(c)充電型 RDC スナバー

図 4-1 スナバー回路例

ここでは、(c)充電型 RDC スナバーについて簡単に解説します。 図 4-2 に充電型 RDC スナバーとその時のターンオフ波形 例を示します。  $\Delta V_1$  は、スナバー回路のインダクタンス  $L_2$  のために吸収できない電圧(サージ電圧)です。 つまり、ターンオフ時の di/dt× $L_2$ で発生するターンオフ電圧です。  $C_s$  は次式より設定します。

$$1/2 \times L_1 \times (I_c)^2 = 1/2 \times C_s \times (\Delta V_2)^2$$

ここで L<sub>1</sub>は主配線のインダクタンス、L<sub>2</sub>はスナバー回路のインダクタンス、R<sub>5</sub>はスナバー抵抗、D<sub>5</sub>はスナバーダイオードです。

図 4-2 充電型 RDC スナバー回路とターンオフ波形例

P-N 間に過大なサージ電圧が発生している場合は P-N 間にコンデンサーが必要です。特に大容量素子では、 図 4-1 の(a)P-N 間にスナバーと(c)充電型 RDC スナバー回路が併用されることがあります。

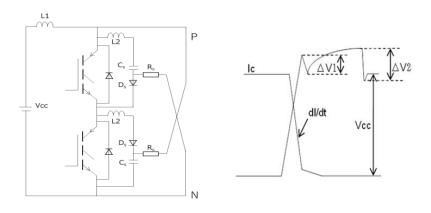

## 4.2. サージ電圧発生例(ダイオードの小電流の逆回復)

IEGT とフリーホイールダイオード(FWD)を用いた PWM 制御のインバーターなどの応用回路では、FWD に小電流が短時 間流れたとき、対向側の IEGT がオンして FWD が逆回復するモードがあります。 この時、順方向のキャリアー蓄積が少ない ため逆回復時 FWD 内の空乏層が急激に広がり、図 4-3 の様な急激なピーク電圧が発生します。 これを防ぐには小電流 または短時間での動作確認を行い、サージ電圧を少なくすようにゲート抵抗やスナバー回路を工夫する必要があります。ま た、サージ電圧が発生しにくい FWD を選定することも対処法の 1 つです。

図 4-3 FWD 小電流の逆回復時のサージ電圧

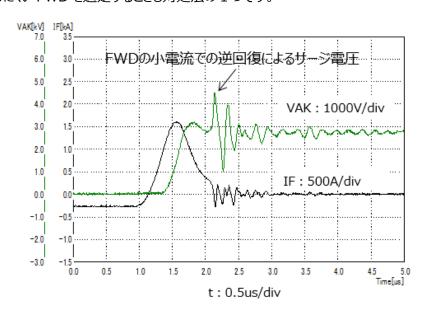

#### 4.3. 短絡保護

IEGT が短絡状態になるとコレクター-エミッター間に電源電圧付近の高い電圧が印加された状態で、コレクター電流が急増 し、その後一定の値以下に抑制されますが、IEGT には高電圧-大電流が印加された状態になりますので、可能な限り短時 間でこの高電圧-大電流の状態を取り除く必要があります。しかしながら、IEGT には短絡の状況が発生してから電流を遮断 するための時間に制約があります。これは、短絡耐量と呼ばれ、図 4-4 のように短絡電流の流れ始めから破壊に至るまでの 時間で規定されます。それゆえ短絡発生時には規定の短絡耐量内で遮断する必要があります。 短絡耐量はコレクター・エミッ ター間電圧  $V_{CE}$  やゲート-エミッター間の印加電圧  $V_{GE}$ 、接合温度  $T_i$ などの条件に依存します。

一般に短絡耐量は電源電圧 Vcc が高い程、また、接合温度が高い程、小さくなります。なお、データシートには IEGT が指 定された条件で短絡動作した際の素子が破壊しないパルス幅: tnscとして記載しておりますのでご確認ください。

(a) 短絡測定回路図

(b) 短絡波形例(左:非破壊波形、右:破壊波形)

図 4-4 短絡測定回路図と短絡波形例

短絡保護過電流検出は CT(Current Transformer)や CE 間電圧などで行ない、過電流検出後、速やかにターンオフ を行なう。電流検出のみで短絡保護が可能であるが、使用状況によっては、(1) 短絡ターンオン時のサージ電流大、(2) 短 絡ターンオフ時のサージ電圧が大きくなる可能性があり、注意が必要です。

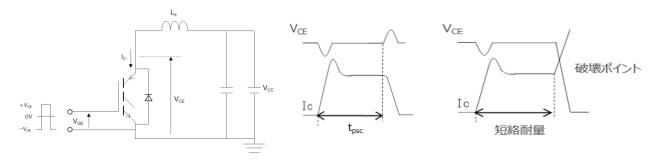

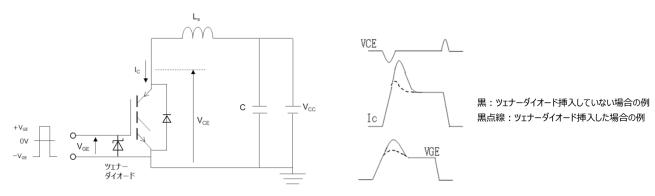

#### (1) 短絡ターンオン時のサージ電流抑制方法の例

ゲート-エミッター間電圧が持ち上がると短絡ターンオン時のサージ電流が大きくなり破壊に至る場合がある。サージ 電流抑制するにはゲート電圧の持ち上がりを抑制する必要があり、一般的な方法としてゲート-エミッター間に(16~ 17V)ツェナーダイオードを挿入する方法がある(図 4-5)。ただし、ツェナーダイオードの電圧が低過ぎると通常ターン オン/ターンオフ時のゲート電圧が不十分となりターンオン損失/ターンオフ損失を増大させる可能性がある。また、 ツェナーダイオードの電圧が高過ぎるとゲート電圧抑制効果が低減するため、波形を確認しながら適切なツェナーダ イオードの電圧を選定してください。

(a) ツェナーダイオード挿入回路図例

(b) ツェナーダイオード挿入有無の短絡波形例

#### 図 4-5 ツェナーダイオードを挿入した場合の回路図と波形例

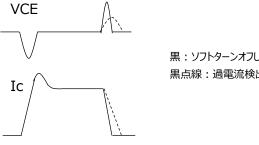

#### (2) 短絡ターンオフ時のサージ電圧

回路の主配線が長い場合、短絡ターンオフ時のサージ電圧が大きくなり、破壊に至る場合がある。サージ電圧を 抑制する方法として、過電流検出または CE 間電圧(VCE)で短絡状態を検知後に、ゲート抵抗を大きくする方法 やゲート出力電圧を抑制する方法でソフトターンオフさせる方法が一般的にとられる(図 4-6、別回路が必要)。た だし、あらゆる動作モードでのターンオフ動作で、誤検出しないように留意する必要があり、波形を確認しながら適切 な短絡保護回路を選定してください。

黒:ソフトターンオフしない場合

黒点線:過電流検出を行ない、ゲート抵抗を大きくして、ソフトターンオフした場合

図 4-6 ゲート抵抗によるソフトターンオフした場合の短絡波形例

#### 4.4. 放熱理論

#### 4.4.1. 熱等価回路

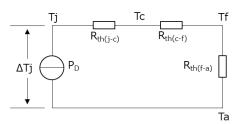

熱の移動を電流に置き換えると、熱が外部に伝導される経路は電気回路で表すことができます。IEGT (PPI)のジャンクション部から外気への熱伝導は、この回路から、熱抵抗と熱容量で決まります。図 4-7 は、熱的に定常な状態における放熱等価回路です。

R<sub>th(i-c)</sub>: ジャンクション-ケース間熱抵抗

R<sub>th(c-f)</sub>: ケース-フィン間熱抵抗

Rth(f-a):フィン-周囲温度熱抵抗

図 4-7 放熱等価回路

ジャンクション部から外気までの全熱抵抗 Rth(j-a) は図 4-7 の等価回路から (1) 式で与えられます。

$$R_{th(j-a)} = R_{th(j-c)} + R_{th(c-f)} + R_{th(f-a)}$$

......(1)

素子での発生損失を Poとすると、ジャンクション温度 T₁は(2)式で与えられます

$$T_j = \Delta T_j + T_a = P_D \times R_{th(j-a)} + T_a \qquad \dots (2)$$

(2)式で表される  $T_j$  がいかなる場合でもデータシートの絶対最大定格  $T_{j(max)}$  を超えないようにフィンの放熱設計をしてください。

#### 4.4.2. 損失計算

IEGT(PPI)で発生する損失は式(3)で表すことができます。

$$P_D = P_{sat} + P_{OFF} + P_{ON} + P_F + P_{rr}$$

(3)

Psat: IEGT 部の導通損失POFF: IEGT のターンオフ損失PON: IEGT のターンオン損失PF: ダイオード部の導通損失Prr: ダイオードの逆回復損失

$P_{\text{sat}}$ は  $I_c$ - $V_{\text{CE}}$ カーブ、 $P_F$ は  $I_F$ - $V_F$ カーブから計算することができます。 $P_{\text{OFF}}$ 、 $P_{\text{ON}}$ 、 $P_{\text{rr}}$ はそれぞれ  $E_{\text{on}}$ - $I_c$ 、 $E_{\text{off}}$ - $I_c$ 、 $E_{\text{rr}}$ - $I_F$ カーブを用途に合致した回路、ドライブ条件で測定し、計算に用いてください。 データシートには代表的なドライブ条件の場合のスイッチング損失カーブが記載されています。 いずれの場合も  $T_j$  が  $T_{j(\text{max})}$ を超えないよう、発生損失に対して余裕を持って放熱設計を行ってください。

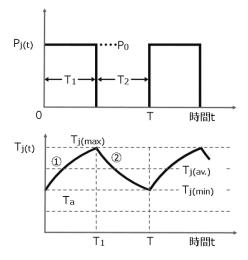

## 4.4.3. ジャンクション温度のパルス応答

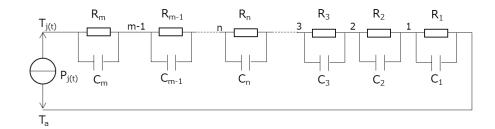

一般にパワー半導体の熱インピーダンスは、図 4-8 のような分布定数回路で与えられます。

図 4-8 パワー半導体の熱インピーダンス

通常のパワー半導体ではm=4程度を考えることにより、ほぼ実際の値に近似することができますが、C、R の値が明確でない場合は  $T_j$  の値を算出することは困難です。そこで、一般的には過渡熱抵抗カーブを使用して  $T_{j(max)}$  を推定します。

まず単発パルスについてです。単発方形波パルス (パルス幅 T1、尖頭値 P0) が印加された場合、パルス幅  $T_1$  に対する過渡熱抵抗  $R_{th\ (T1)}$  を求め、 $T_{i(max)}$  は、(4)式で与えられます。

$$T_{j(max)} = R_{th(T1)} \times P_0 + T_a \qquad (4)$$

インバーター動作ではスイッチングを繰り返すたびに損失がパルス状に発生するので、図 4-9 に示すようにジャンクションの温度変化を生じます。この場合、発生損失を一定周期の方形波パルスで近似し、過渡熱抵抗曲線を使用して温度のピーク値(T<sub>j(max)</sub>)を推定することができます。

図 4-9 のような周期 T,  $T_1 = T_2$  の連続パルスが印加された場合、熱的安定状態で  $T_{j(max)}$  は (4) 式で与えられます。パワー半導体の放熱設計では (4) 式の  $T_{j(max)}$  がパワー半導体の絶対最大定格を超えないよう十分注意する必要があります。

図 4-9 パルス損失が印加された場合の温度変化

#### 4.4.4. 放熱フィンの設計

熱または機械的ストレスを加えずに十分な放熱効果を得るために、IEGT(PPI)を放熱フィンに取り付ける際は以下の点に注意してください。

#### ● 導電性グリスの塗布

IEGT(PPI)とフィンの間の熱抵抗改善のために、IEGT(PPI)とフィンの間に導電性グリスを塗布してください。この場合、導電性グリスは薄く均一に塗布してください。非揮発性の導電性サーマルコンパウンドが適しています。(揮発性の導電性グリスを使用した場合、長期的にグリスにクラックが入り、放熱-導電効果が低下します)

#### ● フィンへの取り付け

十分な放熱効果を得るために、IEGT(PPI)の電極を直接フィンにマウントしてください。この場合、フィンは電気的接続をとるための電極としても用いられます。

#### ● 冷却システムの選定

IEGT(PPI)の発熱量に対して適切な冷却器を選定してください。空冷式の冷却器には安価なアルミフィン、銅ラミネートフィンなどがあります。クランプ治具は絶縁体のチューブで覆って、フィンに触れないようにしてください。圧接力は絶縁体を介して与え、治具がフレームやグラウンドに電気的に接続しないようにしてください。ばねには皿ばねが適しています。皿ばねは規定の圧力で飽和するので、温度や気圧が変化しても一定の圧力を保つことができます。

より大きなパワーを扱う場合は、冷却効果の大きい水冷システムが適しています。冷却液で冷却された放熱フィンを IEGT(PPI)の上下に設置し、プレス装置やボルトで素子を規定の圧接力になるまでプレスしてください。図 4-10 に示すように、電極となる水冷式放熱フィンの他に、クランプ治具、ばね(機械的圧力の元になります)、ボール(素子に均一に圧力を伝えるため)が必要です。水冷式冷却システムを使用する場合、電極内部の腐食を防ぎ、放熱フィン間の絶縁を確保するために電気抵抗の高い高品質の水(純水)を使用してください。また、それぞれの放熱フィンの熱抵抗は放熱フィンのメーカーにお問い合わせください。

株式会社 TMEIC 様 提供

図 4-10 IEGT(PPI)の水冷式フィンへのマウントの例

IEGT(PPI)の最も重要なポイントは均一に圧接することです。放熱フィンを設計する際には以下のことにご注意ください。

- 放熱フィンが図 4-11 のスペックを満たしていること

- 動作中の環境(温度、気圧など)が変化した場合でもトータル圧力が規定値範囲に入っていること。

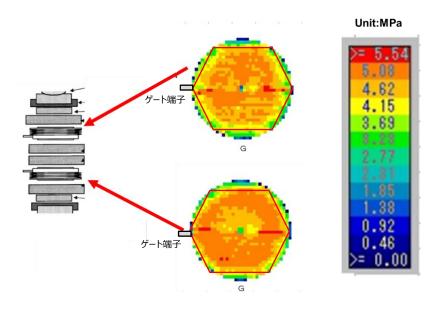

- IEGT(PPI)の部分的な圧力密度差が平均圧力密度(トータル圧力/圧接面積)の 20%以下であること(図 4-12 参照)

| 項目          | フィンの圧接面での値 |

|-------------|------------|

| 平面度 (フィン全体) | 10µm 以下    |

| 平坦度(Rz)     | 3µm 以下     |

| 平行度         | 100µm 以下   |

| 硬度(ビッカース硬度) | 100∼120HV  |

図 4-11 IEGT(PPI)用 Cu 放熱フィンの推奨スペック

基準:内接する六角形内で圧力ばらつき 20%以内

図 4-12 圧力測定システムによる圧力分布の例

#### 4.4.5. 圧接状態の確認

スタックした状態での個々の IEGT(PPI)が均一に圧接されていることを確認してください。

IEGT(PPI)と放熱フィンの間に圧力センサーシートなどを挿入した状態でスタックした後に荷重を加えて、IEGT(PPI)の主電極面における圧力分布を確認する方法があります。圧力センサーシートは、IEGT(PPI)の主電極面に加わる圧力に応じた適切な仕様のものを選択してください(図 4-13 参照)。

図 4-13 圧力センサーシートの使用法

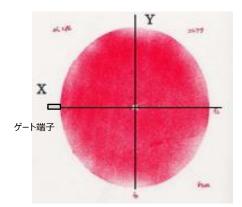

図 4-14 は、富士フィルム(株)のプレスケール(LW)で確認した実施例です。均一な圧接の基準は、内接する六角形内で圧力ばらつきが 20%以内です。図 4-15 は矢印に圧力抜けのある偏圧接の例です。

基準:内接する六角形内で圧力ばらつき 20%以内

ゲート端子

基準外:内接する六角形内で圧力ばらつき 20%以上

図 4-14 正常な圧接状態

図 4-15 圧力抜けがある圧接状態

## 4.4.6. IEGT(PPI)の最大許容印加パワー

IEGT(PPI)の最大許容印加パワーは、TFT 耐量(注)によって決まります。最大許容印加パワーは、T<sub>j</sub> 最大値の制限として 25℃では(5)式のように算出できます。しかし、実使用で寿命を決めていく TFT 耐量が印加パワーに依存するため、特に、PPI では図 4-16 のような最大許容印加パワーを推奨しています。

(注)TFT(Thermal Fatigue Test)、長周期サーマルサイクリング試験とも呼ぶ。第 3.9 節、「その他実使用上の注意事項(7)」、第 7.5 節、「代表的な信頼性試験」参照

単純な最大許容印加パワーの算出(Tc=25℃時): (Ti最大値 - 25℃)/ 熱抵抗[K/W] ......(5)

最大許容印加パワー(TFT 耐量からの推奨値、下記記載ない製品はお問い合わせください。)

| 製品名                        | IEGT 側(W) | ダイオード側(W) |

|----------------------------|-----------|-----------|

| ST3000GXH31A, ST3000GXH35A | 7000      | -         |

| ST2000GXH32                | 4500      | 2000      |

| ST1000GXH35                | 2000      | 750       |

| ST1500GXH35A               | 5000      | -         |

| 3000GXHH32                 | -         | 5000      |

図 4-16 最大許容印加パワー推奨値

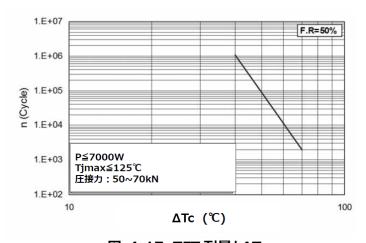

## 4.4.7. IEGT(PPI)の TFT 耐量とΔTc

図 4-17 は ST3000GXH35A の例であるが、ΔTc を小さくすることによって寿命を長くすることができます。

図 4-17 TFT 耐量とΔTc

#### 5. ゲートドライバー回路設計

ゲートドライバーはドライバーIC、フォトカプラー、ハイブリッド IC などを使って、アプリケーションの用途別に設計します。以下設計にあたってのポイントを示します。

#### ゲート電圧

ゲートドライバーを設計する場合、ゲート順バイアスの推奨値は+15V、ゲート逆バイアスの推奨値は-15V です。順バイアス、逆バイアスの電源電圧の変動は±10%以下にしてください。

#### ゲート抵抗

ゲート抵抗はターンオンの di/dt を調整し、またターンオフ時のサージ電圧を低くするために、実機動作で検証して抵抗値を最適化してください。ゲート抵抗を小さくするとスイッチング損失が小さくなり、抵抗を大きくするとスイッチング損失が増加するため、適切なゲート抵抗値を選定してください。

## デッドタイム

IEGT(PPI)でインバーター回路を構成する場合は、上下アームの短絡を防止するために、デッドタイムを設けてください。デッドタイムとは上下アームの両方にゲートドライバーがオフ信号を出力している期間です。デッドタイムは、誤点弧を生じないように実機回路で検証の上適切な値を設定してください

#### ゲート配線

ゲートドライバーから IEGT(PPI)までの配線は電磁ノイズなどによる誤動作を防止するため、できるだけ短くしてください。ゲート配線に同軸ケーブルを使用する、縒り線(ツイスト線)を使用するなどの対策で外部からのノイズの影響を減らすことできます。IEGT(PPI)に印加されるゲート電圧がデータシートに記載のゲート絶対最大定格(20V)を超える場合は、ツェナーダイオードなどで適切な保護をしてください。

図 5-1 ゲートドライブ回路例

Power Integrations から、IEGT(PPI)用のゲートドライバーを販売しています。詳細は、お問い合わせをお願いします。

#### 6. アプリケーションの適用

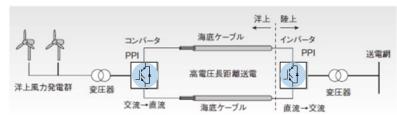

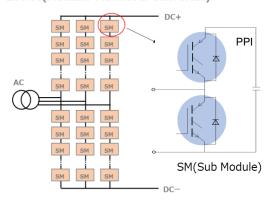

#### 6.1. 直流送電変換機

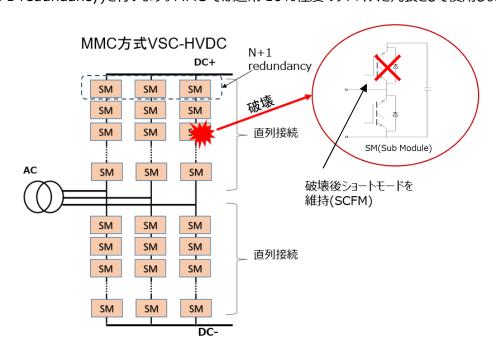

直流送電は、洋上などで風力発電した電力を効率的に需要地に運ぶため、発電した交流電力を一度直流電力に変換し て長距離、あるいは海底を送電するときに使用されます。この時、高電圧の変換に直列接続対応、両面冷却の特長を生か した IEGT(PPI)が使用されます。 また、高電圧、大容量の直流送電のコンバーター(交流を直流に変換)、インバーター(直 流を交流に変換)は MMC(Modular Multilevel Converter)の回路方式が多く使用されています。 MMC は IEGT スイッ チとコンデンサーで構成された Sub Module(SM)と呼ばれる単位変換器を構成要素とし、Sub Module が多数直列に接 続されたアームで DC-AC および AC-DC 変換を行います。 IEGT(PPI)は直列接続が容易で SCFM(Short Circuit Failure Mode、第7.4節参照)を持つことから、MMC に適しています。

■海底送電システム

洋上風力発電機

■MMC(Modular Multilevel Converter)

## 6.2. 静止型無効電力補償装置(SVC: Static Var Compensator)

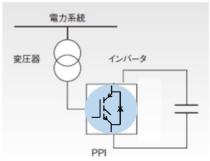

電力系統などに設置され、力率改善などの電力の質の向上に用いられる設備です。能動型 SVC には、SVG(Static Var Generator)や STATCOM(Static Synchronous Compensator)などがあり、高電圧大容量の変換デバイスとして直 列接続対応、両面冷却の特長を生かした IEGT(PPI)が適しています。

変電所

電力系統

■SVGインバータ回路

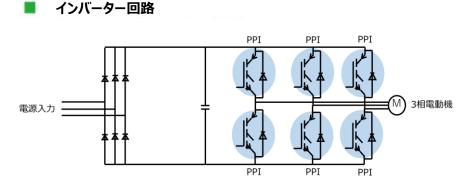

## 6.3. 中電圧以上のインバーター装置(Medium Voltage Inverter)

大容量のインバーター装置には、直列接続対応、両面冷却の特長を生かした IEGT(PPI)が適しています。

電気推進船

#### 7. 信頼性に関する情報

#### 7.1. 概要

工業生産の始まりから、企業では製品に対する信頼性を高めるため、製品の品質として耐久性、寿命、安全性、サービス性というような形で信頼性が取り上げられてきました。しかし信頼性が組織的に取り上げられるようになったのは 1950 年代からで、機器の高度化や複雑化、化学プラントや電力システムのようにシステム化の進展にともない、故障による社会的影響や損害の増大をきたすようになり、信頼性が重要な品質特性としてクローズアップされてきました。このため、信頼性という抽象的な概念から、もっと定量的な表現を見つけ出し、実際のシステムや製品の信頼性をはかり、改善し、管理するという動きが活発になってきました。JIS では「信頼度」として「アイテムが与えられた条件で規定の期間中、要求された機能を果たす確率」と定義し定量化を図っています。ここでは主に、パワーデバイスの信頼性に関する内容について取り上げます。なお、信頼性の考え方、詳細については東芝デバイス&ストレージ製品信頼性情報ホームページをご確認ください。

< https://toshiba.semicon-storage.com/jp/semiconductor/knowledge/reliability.html >

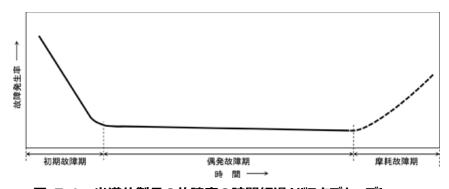

## 7.2. パワーデバイスの信頼性

一般にパワーデバイスの故障率は、図 7-1 に示すバスタブカーブの様な形状を示します。パワーデバイス適用当初の初期 故障期、その後の偶発故障期-磨耗故障期となります。パワーデバイスの選定に際しては、適用アプリケーションおよび、故障 率カーブの特性を考慮して、パワーデバイスを選定する必要があります。以下に各故障期の詳細について述べます。

図 7-1 半導体製品の故障率の時間経過(バスタブカーブ)

#### 初期故障期間

初期故障は、半導体チップ内の微細な欠陥などに起因して発生します。当社では過去の品質トラブル事例を蓄積し、パワーチップ、組立工程などの設計にこれら不具合事例をフィードバックすることによる絶え間ない品質向上活動を実施することで、初期不良品の低減に努めております。しかしながら設計段階での初期不良排除は非常に困難であり、この点を補うべく出荷試験を当社では実施しております。出荷試験ではスクリーニング・エージング試験を実施することによって、初期故障率の低減に努めております。

#### 偶発故障期間

故障率カーブの偶発故障期は初期故障品が除去されることで、パワーデバイス単体の故障率はほぼ一定となります。つまり、この期間ではアプリケーションの動作条件によりパワーデバイスの故障率は変化します。具体的にはパワーデバイスや他の部品などで構成されるシステム全体の使用条件や環境によって変わり、そのシステム固有の信頼度に相当します。つまり、この期間での故障率低減のためには、システムの最悪運転条件で各種特性(過電圧、過電流、過熱など)がパワーデバイスの絶対最大定格を超えないようにする必要があり、これら運転条件が仕様書に記載されている絶対最大定格に対し、ディレーティング(一般には電圧は絶対最大定格の50~60%以下、接合温度は絶対最大定格の70~80%以下)して使用することおよび、パワーデバイス適用回路、搭載環境条件などと十分にマッチングしている事が肝要となります。

#### 磨耗故障期間

故障率カーブの磨耗故障期はパワーデバイスの寿命による故障期です。この期間に到達前に寿命となるシステム設計が必要です。当社では以下に示す長期信頼性試験を設計段階で検証し品質確認を行っています。特に IEGT(PPI)の 熱疲労破壊モデルについては、第 4.4.7 節に示すように TFT(Thermal Fatigue Test)の破壊モードについて寿命確認を行っています。寿命設計に関しては、熱疲労破壊モデルを適用の上、適用システムの動作モードに適した熱疲労破壊耐量内での設計をしてください。

## 7.3. 宇宙線耐量について

## 宇宙線によるデバイス破壊

パワーデバイスはブロッキング電圧印加時、自然界に存在する宇宙線(Cosmic Ray)の影響である確率で破壊することが知られています。宇宙線は宇宙から飛来する高エネルギーの粒子(プロトンなど)で、地球の大気、磁場と反応して上層大気で2次的な高エネルギー粒子(中性子など)が生成され地上に降りそそぎます。この中性子線によって発生した電子・正孔対がアバランシェ降伏を誘発して最終的にデバイスは破壊に至ります。宇宙線破壊の特徴として下記があります。

- (1) 単発的な予期しない破壊。

- (2) パワーデバイスのブロッキング時に発生。

- (3) ブロッキング電圧に比例して発生頻度が増加。

- (4) パワーデバイスの使用環境により発生頻度が影響を受ける。 (パワーデバイスが稼働している標高が高いと発生頻度が増加、コンクリート造建屋内では頻度低減、他)

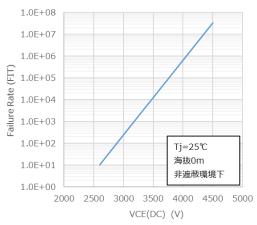

## IEGT(PPI)の宇宙線に対する故障率

図 7-2 に IEGT(PPI):ST3000GXH35A の宇宙線耐量(Fit 率)を示します。宇宙線に対する故障率を低減させるためにはブロッキング電圧(DC 電圧)を低く設定して使用することが有効です。また、標高が高い場所での使用は宇宙線による故障が増加しますので対策(コンクリートの遮蔽など)が必要です。

図 7-2 IEGT(PPI)の宇宙線に対する故障率(参考値)

## 7.4. SCFM (Short Circuit Failure Mode)

IEGT(PPI)はデバイスが破壊してもショートモードを維持することが可能です。これは SCFM(Short Circuit Failure Mode)と呼び、IEGT(PPI)の優位点の 1 つです。SCFM を考慮した応用システム例(多数直列接続で使用、他)では、何らかの原因でデバイス破壊が生じても、破壊デバイスはショートモードを維持するため、応用システムの稼働は他のデバイスで維持され停止することはありません。

図 7-3 は MMC(Modular Multilevel Converter)方式の VSC-HVDC の応用例です。 SCFM を実現するためには、IEGT(PPI)の直列接続数に余裕を持たせ、一部のデバイスが破壊しても他のデバイスで定格運転ができるようにシステムの冗長設計(N+1 redundancy)を行います。 MMC では通常 10%程度のデバイスを冗長として使用します。

図 7-3 IEGT(PPI)を直列接続した応用例(MMC 方式 VSC-HVDC)

#### SCFM の安定性

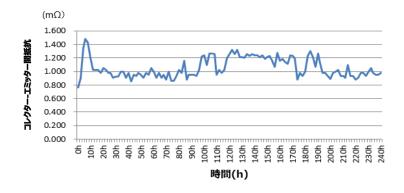

前項の破壊デバイスは SCFM を維持しますが、システムメンテナンスの時期に合わせて交換する必要があります。また、デバイスは交換時期までに安定した SCFM を保つ必要があります。当社の IEGT(PPI)は図 7-4 に示すとおりデバイス 破壊時からコレクター-エミッター間抵抗は 1.6mΩ以下でほぼショートモードを維持し、240 時間まで継続することが確認されています。 この結果から適切な圧接状態を維持すれば 240 時間以降も安定した SCFM を実現できます。

図 7-4 IEGT(PPI)のデバイス破壊時からのショートモードの維持状態

## 7.5. 代表的な信頼性試験

図 7-5 に代表的な信頼性試験内容を示します。

| 分類     | 試験項目                                                       | 内容及び試験条件                                                                                                                                  | 準拠規格        |             |           |         |  |

|--------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-----------|---------|--|

| 刀块     | 武凞項日                                                       | 内谷及び武殿栄任                                                                                                                                  | EIAJED-4701 | MIL-STD-883 | IEC 60749 | JESD 22 |  |

| 熱的破壊試験 | 温度サイクル試験                                                   | デバイスが低温と高温の繰り返し環境にさらされた場合の耐性を評価する。<br>試験条件例:Ta = -40℃/125℃                                                                                | 105         | 1010.7      | Part 25   | A104-B  |  |

|        | 衝撃試験                                                       | 使用中に受ける衝撃に対する耐性を評価する。<br>試験条件例:衝撃加速度 588m/s²パルス:1ms、波形:正弦半波方向:X1、Y1、Y2、Z1方向、回数:3回                                                         | 404         | 2002.3      | Part 10   | B104-C  |  |

| 機械的試験  | 振動試験                                                       | 使用中に受ける振動に対する耐性を評価する。試験は可変周波数振動と一定周波数振動があり、通常可変周波数振動を行う。<br>試験条件例:<br>周波数範囲:100~1500(Hz)、加速度:200(m/s²)、掃引の割合:約4(分)掃引周波数変化の方法:対数、総試験時間:48分 | 403         | 2007.2      | Part 12   | B103-B  |  |

|        | 端子強度引張り試験                                                  | 端子部分(PPIではゲートリード部分)の強度が、その取り付け配線または使用に加えられる力に対して耐えられるかどうかを評価する。試験条件例:リードの先端を規定過重で引っ張り、一定時間(30s)要する。試験後、外観に切断、折損、ゆるみがある場合不良判定とする。          | 401         | 2004.5      | Part 14   | B105-C  |  |

|        | 高温保存試験                                                     | 長時間、デバイスが高温下に放置された<br>場合の耐性を評価する。<br>試験条件例:Ta = Tstg.Max                                                                                  | 201         | 1008.2      | Part 6    | A103-C  |  |

|        | TFT試験<br>(Thermal Fatigue Test)<br>または、長周期サーマル<br>サイクリング試験 | デバイスに大電力印可のオンとオフを繰り返し、チップの自己発熱と冷却を繰り返す。<br>PPIの場合、圧接素子を構成している各部材と半導体チップの熱膨張差により発生する応力が半導体チップに損傷を与える度合いを評価する。                              | -           | -           | -         | -       |  |

| 寿命試験   | 低温保存試験                                                     | 長時間、デバイスが低温下に放置された<br>場合の耐性を評価する。<br>試験条件例:Ta = Tstg.Min                                                                                  | 202         | -           | -         | -       |  |

|        | 高温バイアス試験(ゲート)                                              | 長時間、デバイスが電気的ストレス、熱的<br>ストレスを加え、その耐性を評価する。<br>試験条件例:Tc = Tj max -5℃                                                                        | 102         | -           | Part 5    | A101-B  |  |

|        | 高温バイアス試験(コレクター)                                            | 電源電圧 = 最大電圧定格の80%                                                                                                                         |             |             |           |         |  |

|        | 室温バイアス試験                                                   | 長時間、デバイスが電気的ストレス、熱的<br>ストレスを加え、その耐性を評価する。<br>試験条件例:Tc = 25℃<br>電源電圧 = 最大電圧定格                                                              | 102         | -           | Part 5    | A101-B  |  |

図 7-5 代表的な信頼性試験

## 7.6. IEGT(PPI)の信頼性要件

IEGT(PPI)の信頼性は実装方法および動作上のストレス、使用環境上のストレスを加味して取り扱う必要があります。これらは、相互に密接な関係により、高信頼度で使用いただくため、主要なものについて説明します。

#### ● IEGT(PPI)の実装方法

IEGT(PPI)は主電極間に荷重を加えることにより、電気的、熱的なコンタクトを得る構造です。スタック実装する際は次の要件に留意してください。

- (1) IEGT(PPI)の主電極面は規定荷重値を均一な圧力で圧接する。圧力バラつき無く圧接するには、スタック荷 重部における構成部材(放熱フィンなど)の材質や平面度に注意が必要です。通電時では印加負荷により IEGT(PPI)自身が膨張し圧力が上昇するため、圧接力が均一に保てるようスタックには皿ばねなどを併用してく ださい。

- (2) 良好な熱伝導を確保し、適切な放熱設計を行う。十分な放熱効果を得るために、IEGT(PPI)の主電極と放 熱フィンをじかに接触させ、IEGT(PPI)の主電極と放熱フィンとの間には導電性のサーマルコンパウンドを塗布し てください。また、IEGT(PPI)の主電極は必ず両面とも冷却する必要があります。

#### ● IEGT(PPI)の動作条件

IEGT(PPI)に加味する電圧、電流や機器としての使用環境条件は、信頼度を左右する大きな要因です。目的とする回路に応じて適正な IEGT(PPI)の選択と回路設計により、動作点を設定しなければなりません。

IEGT(PPI)の故障率は、動作時における温度および最大温度と最小温度の差に著しく影響を受け、高温度および最大温度と最小温度の差が大きくなるにつれて故障率も増加します。IEGT(PPI)では比較的大きな電流、電圧を扱う用途が多く、電力消費も大きくなります。この電力消費は、IEGT(PPI)に発熱をもたらし、特性面および信頼性面で好ましくなく、効率良く放熱する必要があります。

また、回路設計にあたっては、外来のサージ電圧やノイズの重畳が考えられますので IEGT(PPI)特性の偏差を考慮して十分な回路マージンと保護回路で、余裕をもたすことができれば、IEGT(PPI)の寿命、ひいては機器としての寿命を大幅に延ばすことが可能になります。

IEGT(PPI)を高い信頼度で使用いただくため、絶対最大定格で規定の電圧、電流、電力、温度に対して、ディレーティングして使用することを推奨します。しかし、ディレーティングは信頼性と経済性を考慮して決める必要があります。

#### ● IEGT(PPI)の特性バラツキ

製造工程の自動化や製造技術の進歩向上は目覚ましいものがあり、これらの発展と積極的な導入により、品質、信頼性は年々向上の一途をたどっております。しかし、IEGT(PPI)に限らず半導体製品は、形状、構造、寸法が多種多様であり、物理化学的な技術を基に、高精度に制御管理する精密技術の上に成り立っております。このため、わずかな偏差でも特性におよぼす影響は大きく、最新技術を駆使しても、諸特性を均一に保つことは難しいと言えます。動作条件や回路構成によっては、各半導体の諸特性に応じて回路配置を考慮する必要もあります。また、IEGT(PPI)では、パッケージ内部に複数の半導体チップが並列に組み込まれていますが、それらの半導体チップの諸特性は同一パッケージ内で合わせ込むことにより、IEGT(PPI)の信頼性を向上させております。

#### ● IEGT(PPI)の耐環境性

IEGT(PPI)は気密封止構造による高信頼性を実現しておりますが、有害ガス、塩気、放射線などの雰囲気に直接さらされますと特性変動や劣化、シールやリード部分のサビなどの誘起原因になりますので、注意する必要があります。また、高電圧下で使用される場合には、IEGT(PPI)のパッケージへの結露や沿面汚れに注意が必要です。結露や汚れがひどい場合にはパッケージ沿面で放電し、装置を破壊する場合があります。絶縁を考えて、IEGT(PPI)を油など冷却用媒体の中に浸けて使用することがあります。この場合、IEGT(PPI)の現品表示、ゲート-エミッターリードに影響をおよぼすことがありますので、あらかじめ当社窓口までご相談願います。

## 7.7. IEGT(PPI)の熱疲労モード

IEGT(PPI)の熱疲労寿命は、使用される動作条件に応じた温度変化(ΔΤ)に強く依存しています。IEGT(PPI)では電気的接続および放熱を圧接構造により実現しているため、熱疲労的に高い信頼性が期待できます。この構造上の特徴により、ワイヤボンディングタイプのパワー半導体素子でいう短周期パワーサイクル耐量による熱疲労寿命の束縛はありませんが、ΔΤ に強く依存した TFT(Thermal Fatigue Test) 耐量(または長周期パワーサイクル耐量)は存在します。TFT 耐量による劣化モードは、IEGT(PPI)を構成している銅電極、モリブデン板、半導体チップの熱膨張差による応力が繰り返し発生することより、半導体チップが損傷に至ります。

## 7.8. IEGT(PPI)の故障モード

IEGT(PPI)の故障の形態を大きく分けると、ショート、オープンおよび劣化に分類されます。ショート不良の要因の主なものは、(1) 過電圧、過電流などのオーバーストレスによるもの、(2) 劣化が高じてショートに至るもの、(3) 電気化学的反応によるものなどがあります。

オープン不良については、一般的なボンディングワイヤを備える半導体製品と異なり、IEGT(PPI)では構造上の特徴により、オープン不良が発生しにくいものとなっています。

劣化は電気的特性でみると、耐圧の規格値以下への低下、電流の異常増加、あるいは特性値のドリフトなどいろいろな場合があります。半導体は物理的、化学的な技術を基に作られていますので、電圧や電流、温度により素子表面、内部における熱化学的な変化によって変動を起こすものが考えられ、これらが順次増大し規格値を超えてしまうものといえます。その原因としては、(1) 製造上の欠陥、(2) 設計上の問題、(3) 使用上の問題があります。

また、IEGT(PPI)に過大な電流が流れた場合、気密封止構造により外囲器が破裂しにくい構造となっていますが、過電流の大きさによっては外囲器が破裂して周辺器材を損傷することがあります。

## 8. トラブル発生時の対応

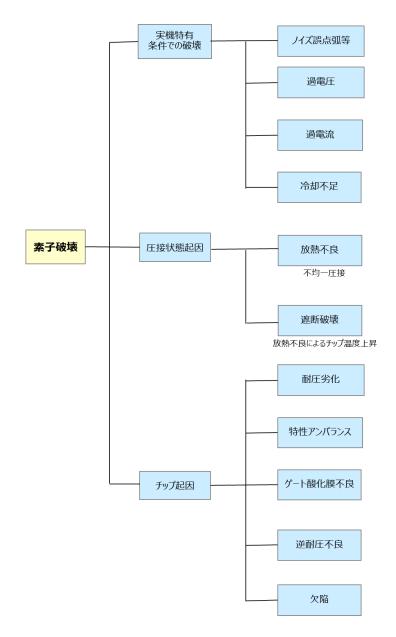

IEGT(PPI)を各種回路に適用、使用した場合、配線ミス、実装上のミス、制御信号不整合などの異常により異常動作、または破壊することがあります。異常動作または破壊が発生した場合、その発生原因を明確にし、対策する必要があります。 IEGT(PPI)が破壊した際の要因調査では図 8-1 のような FTA(Fault Tree Analysis)を元に進めると分かりやすいです。また、破壊した IGET(PPI)を分解、チップの破壊状態を確認することで破壊モードが推定できます。破壊モードの詳細は図 8-2 を参照ください。

図 8-1 FTA の一例

IEGT(PPI)が破壊しているかどうかを確認するには、カーブトレーサーなどの特性測定装置によって IEGT の場合は下記(1)、(2)を、FWD の場合は(3)を測定、確認することで判定できます。

- (1) G-E 間の漏れ電流

- (2) C-E 間の漏れ電流

- (3) A-K 間の漏れ電流

また、カーブトレーサーの代わりにテスター、バッテリーチェッカーなどの、電圧、抵抗が測定できる装置を使用しても簡易的な故障判定は可能です。

|   |                          |    |    |       | ペレット破壊            | 左記補足    | 考えられる    |                                                       |                                                                   |

|---|--------------------------|----|----|-------|-------------------|---------|----------|-------------------------------------------------------|-------------------------------------------------------------------|

|   |                          |    |    | パターン図 | (TR=IEGT、D=Diode) | 電気的要因、他 |          |                                                       |                                                                   |

|   |                          |    |    |       |                   | 他       |          |                                                       |                                                                   |

| 1 | ターンオフ破壊                  | オン | オン | オフ    | オフ                |         |          | <br>  TR1 枚 CE 短絡、GE 短絡<br> パターンのセル内で破壊               | <br>素子耐量を超えて Vcc、Vcp、Icp 印加<br>Ls が過大                             |

|   |                          | -  | -  | 0     | -                 | -       |          |                                                       | FWD 破壊後の SW による過電流                                                |

| 2 | GE 耐圧不良 1                | 0  | 0  | 0     | 0                 | 0       | ,        | TR1 枚以上<br>GE、または CE 短絡<br>溶融痕 微小の場合あり                | GE 間に定格を超えた電圧印加<br>(dv/dt による VGE の変動含む)<br>GE オープンで CE 間に電圧印加    |

| 3 | GE 耐圧不良 2                | -  | -  | -     | -                 | 0       | 面内で      | AI 電極はみ出し、別配線との                                       | 過度の繰り返し圧接による配線つぶれ<br>異物の挟み込み<br>片当たり含む過大圧接力による配線つぶれ、変形            |

| 4 | CE/AK への過電圧              | -  | -  | -     | -                 | -       | 1 4 41   |                                                       | IEGT 遮断時、FWD の逆回復時のサー                                             |

|   | IEGT<br>FWD              | -  | -  | 0     | 0                 | 0       |          | チップ終端付近が破壊<br>(チップコーナー部多い)                            | ジ電圧が素子耐量を超えて印加                                                    |

| 5 | 逆回復時破壊<br>(FWD)          | 0  | -  | -     | -                 | -       |          | D1 枚 or 複数で溶融<br>AK 短絡                                | 過大な V <sub>R</sub> 、I <sub>F</sub> 印加                             |

| 6 | 短時間通電後<br>逆回復破壊<br>(FWD) | -  | -  | 0     | -                 | -       |          | D1 枚バルクで溶融<br>AK 短絡                                   | 短時間通電後の逆回復パワーが印加<br>(IEGT ターンオフ破壊に伴い相手アーム<br>の FWD として動作している場合など) |

| 7 | 宇宙線破壊<br>(LTDS)          | -  | -  | 0     | 0                 | 0       |          | TR1 枚以上、または D1 枚以上<br>チップ終端付近、またはバルクの一<br>部がスポット的に溶融  | 標高が高いなど環境による影響                                                    |

| 8 | サージ電流破壊<br>(FWD)         | 0  | 0  | -     | -                 | 0       | <b>A</b> | D1 枚以上バルクで大きく溶融。<br>逆回復を伴う場合は周辺部分に<br>複数の溶融痕が発生する場合あり | 許容サージ電流を超えて通電                                                     |

図 8-2 IEGT/FWD チップ破壊パターンと推定破壊モード例

注1:上記主破壊チップの溶融面積が甚大な場合、隣接するチップも耐圧劣化、溶融することがあります。

注2:パターン例の図は一部 IEGT/FWD を兼ねています。(ダイオードにはチップ右上のゲート電極がありません。)

#### 製品取り扱い上のお願い

株式会社東芝およびその子会社ならびに関係会社を以下「当社」といいます。 本資料に掲載されているハードウエア、ソフトウエアおよびシステムを以下「本製品」といいます。

- 本製品に関する情報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を得て本資料 を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

- 当社は品質、信頼性の向上に努めていますが、半導体・ストレージ製品は一般に誤作動または故障する場合があります。 本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責 任において、お客様のハードウエア・ソフトウエア・システムに必要な安全設計を行うことをお願いします。なお、設計および使 用に際しては、本製品に関する最新の情報(本資料、仕様書、データシート、アプリケーションノート、半導体信頼性ハン ドブックなど)および本製品が使用される機器の取扱説明書、操作説明書などをご確認の上、これに従ってください。また、 上記資料などに記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの 情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判 断してください。

- 本製品は、特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な 財産損害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下"特定用途"という)に使用され ることは意図されていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇宙機器、医療機器 (ヘルスケア除く) 、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連機器、 昇降機器、発電関連機器などが含まれますが、本資料に個別に記載する用途は除きます。特定用途に使用された場合 には、当社は一切の責任を負いません。なお、詳細は当社営業窓口まで、または当社 Web サイトのお問い合わせフォー ムからお問い合わせください。

- 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

- 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用することはできません。

- 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及び第 三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に関して、明 示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保 証、第三者の権利の非侵害保証を含むがこれに限らない。) をしておりません。

- 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその 他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、「米国輸出管理規 則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず当社営業窓口までお問い合わせください。本製品のご 使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査の上、かか る法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は一切の責 任を負いかねます。

## 東芝デバイス&ストレージ株式会社

https://toshiba.semicon-storage.com/jp/