# Isolation Amplifier Application Circuits (Current Sensing) of the TLP7920 Reference Guide

RD004-RGUIDE-02

**TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

# **Table of Contents**

| 1. OVERVIEW                                                                               | 3  |

|-------------------------------------------------------------------------------------------|----|

| 1.1 Target applications                                                                   | 3  |

| 2. MAJOR FEATURES OF THE TLP7920                                                          | 4  |

| 3. APPLICATION CIRCUIT EXAMPLE AND BILL OF MATERIALS                                      | 9  |

| 3.1 Example of an application circuit for current sensing                                 | 9  |

| 3.2 Bill of materials                                                                     | 10 |

| 4. GUIDELINES FOR DESIGNING A CURRENT-SENSING CIRCUIT                                     | 10 |

| 4.1 Primary-side input line design                                                        | 10 |

| 4.2 Secondary-side input line design                                                      | 10 |

| 4.3 Current-sensing resistor (shunt resistor)                                             | 11 |

| 4.4 Test mode considerations                                                              | 12 |

| 5. SIMULATION                                                                             | 12 |

| 5.1 Basic operation                                                                       | 12 |

| 5.2 Noise superimposed on the input voltage                                               | 14 |

| 5.3 Circuit with filters                                                                  | 15 |

| 6. PRODUCT OVERVIEW                                                                       | 17 |

| 6.1. Overview                                                                             | 17 |

| 6.2. External view and pin assignment                                                     | 18 |

| 6.3. Internal block diagram                                                               | 18 |

| 6.4 Output voltages for different primary- and secondary-side power supply combinations . | 19 |

#### 1. Overview

Factory Automation (FA) market has AC servo, General Purpose Inverter, Solar Power Generation and Wind Power Generation areas and those application's key design point is to accurate current sense, voltage sense so that each application can realize high accuracy and stability of motions and controls and isolation performance between input and output signals. In order to realize such kind of high accuracy motions and controls, system has to monitor motor's current and voltage and feedback them to microcontroller (MCU) more properly.

The TLP7920 is an isolation amplifier which has optical coupled isolation feature in order to meet above requirement with 0.02% (typical) linearity accuracy. The TLP7920 also provides a common-mode transient immunity (CMTI) of 20 kV/µs (typical), therefore stable even in noisy motor control environments. In addition, the guaranteed isolation voltage of 5000 Vrms (minimum) makes the TLP7920 suit various industrial applications.

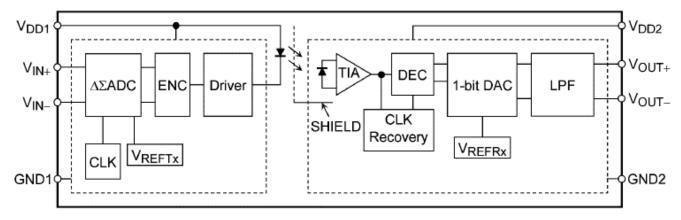

In order to achieve those characteristics, the TLP7920 has a high-precision delta-sigma AD converter at the primary side and DA converter at the secondary side. The primary and secondary sides of the TLP7920 isolation amplifier are optically coupled using an LED and a photodiode to provide electrical isolation and internal signal transfer of optical transfer with digital signal realizes high accuracy signal transfer.

The delta-sigma AD converter at the primary side encodes an input analog signal into digital data, then optically transmitted to the secondary side by an LED. At the secondary side, the optical signal is received by a photodiode, decoded by a decoder circuit, converted back to an analog signal by a DA converter, filtered internal conversion noise by a lowpass filter (LPF), then output analog signal properly.

This reference guide provides the unique features and characteristics of the TLP7920, focusing on common-mode transient immunity, nonlinearity characteristic, and power consumption, as well as design guidelines for typical current-sensing applications. For details of other features and functions of the TLP7920, see its datasheet.

To download the datasheet for the TLP7920  $\rightarrow$

Click Here

#### 1.1 Target applications

- Current sensing for industrial motor applications, including inverters, servo amplifiers, robots, machine tools, and high-capacity power supplies

- Current sensing for wind power and PV inverters, and industrial storage battery systems

- Current sensing for office and housing equipment, including uninterruptible power supplies (UPS), server power supplies, home storage battery systems, and air conditioners

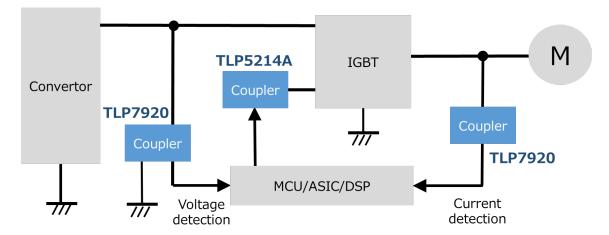

#### **Example of an application to an inverter**

Toshiba offers the TLP5214A photocoupler suitable for use as an IGBT gate driver.

For details of the TLP5214A  $\rightarrow$ Click Here

# 2. Major features of the TLP7920

#### Common-mode transient immunity (CMTI)

Common-mode noise is a type of electrical noise that overlaps on both signal and GND lines in the same direction. A photocoupler is used to optically transmit a signal between two isolated circuits with independent power supplies, however even in this case, a common-mode noise is generated by changes in the voltage of either one of the power supplies (for example, input a noise from outside). A common-mode noise generates a displacement current to flow through the internal coupling capacitance between the primary (input) and secondary (output) sides of a photocoupler and if a displacement current excees a given level into coupling capacitor, the photocoupler has malfunction, then resulting in faulty system operation.

A displacement current generated by transient common-mode noise could cause bit errors in an isolation amplifier, in the worst-case, it leads to a short-circuit failure of an IGBT. There fore it is important for stable system operations to tolerate common-mode noise. CMTI indicates the ability of an isolation amplifier to tolerate high-slew-rate transient voltage induced across GND lines. An isolation amplifier with a high CMTI provides high immunity to common-mode noise and is suit applications requiring electrical isolation.

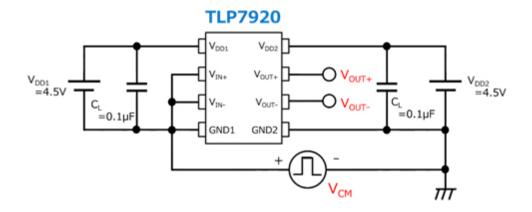

Figure 2.1 shows an example of a test circuit for measuring the output waveform with a common-mode voltage ( $V_{CM}$ ) applied.

Figure 2.1 Example of a test circuit for measuring the output waveform with a common-mode voltage ( $V_{CM}$ ) applied

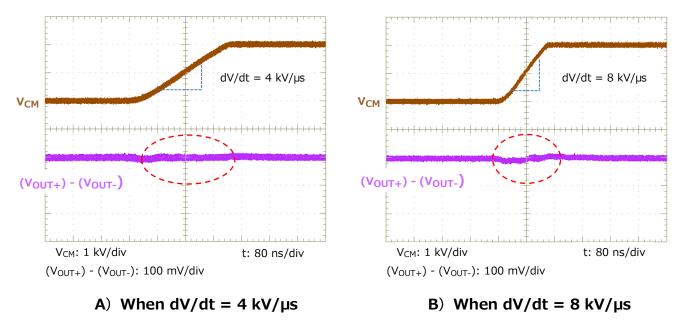

An inverter contains discrete IGBT (or IGBT module) with a collector-emitter voltage ( $V_{CE}$ ) of 600 to 650V or 1200V. The 600V to 650V IGBTs are generally used at a supply voltage of 400V, and 1200V IGBTs are commonly used at 800V. Typically, IGBTs have rise and fall times ( $t_r$  and  $t_f$ ) of roughly 100ns when switching. Under these conditions, the slew rate (dV/dt) of  $V_{CM}$  is calculated to be  $4kV/\mu s$  at a supply voltage of 400V and  $8kV/\mu s$  at 800V. Figure 2.2 shows examples of output waveforms of the TLP7920 when common-mode voltages ( $V_{CM}$ ) with  $4-kV/\mu s$  and  $8-kV/\mu s$  slew rates are applied. As shown in Figure 2.2,  $V_{OUT}$  does not have much noise, which proves that the TLP7920 has enough CMTI performance to apply actual applications.

Figure 2.2 Example of output waveforms of the TLP7920 with common-mode voltages  $(V_{CM})$  applied

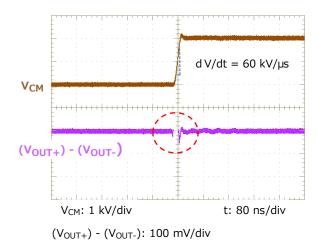

Just for reference, Figure 2.3 shows an example of an output waveform when the common-mode voltage  $V_{CM}$  has a very large dV/dt rate with  $60kV/\mu s$ . The  $V_{OUT}$  waveform has a noise spike caused by  $V_{CM}$  sudden change. This noise spike could cause a total system malfunction if it becomes larger.

Figure 2.3 Example of an output waveform of the TLP7920 when a common-mode voltage ( $V_{CM}$ ) with a very large slew rate is applied

#### About output linearity characteristics

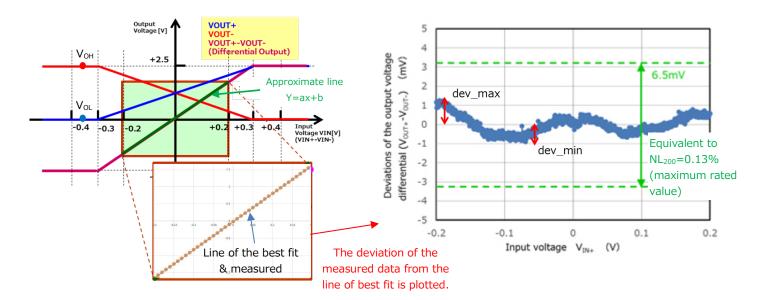

When system feedback needs using isolation amplifier detecting current fluctuations, it is important for input-output linearity characteristics to control system properly. The output of an isolation amplifier with bad linearity characteristics does not respond accurately with specific input so there are lacking of the stability and accuracy of a system. In the trend of increasing speed, accurate control is required for inverters and it is important for isolation amplifier to minimize the output errors. Although an electronic circuit or software can be used to correct output errors, both methods are impractically complicated and difficult, considering variations in device characteristics. Using an isolation amplifier with high precision linearity characteristics is more practical. Figure 2.4 shows a test circuit for measuring the linearity characteristics of an isolation amplifier.

Figure 2.4 Example of a nonlinearity test circuit

The  $NL_{200}$  or  $NL_{100}$  parameter represents the linearity of an isolation amplifier.  $NL_{200}$  is calculated as follows:

- 1. The least-squares method is used to find a line of the best fit that represents the relationship between the input voltage differential ( $V_{IN+}$ - $V_{IN-}$ ) and the output voltage differential ( $V_{OUT+}$ - $V_{OUT-}$ ).

- 2. The deviations of the output voltage differential  $(V_{OUT+}-V_{OUT-})$  from the line of the best fit are calculated.

- 3. The sum of the absolute values of the maximum and minimum deviations (|dev max|+|dev min|) is calculated.

- 4. The ratio of this sum to the full-scale differential output voltage (V<sub>OH</sub>-V<sub>OL</sub>) is calculated.

Figure 2.5 shows the relationship between the input voltage and the output voltage deviation from the line of the best fit.

Figure 2.5 Input voltage vs. output voltage deviation from the line of the best fit

NL<sub>200</sub> is calculated as follows:

$$NL_{200}(\%) = rac{rac{(|dev\_max| + |dev\_min|)}{2}}{V_{OH} - V_{OL}} imes 100$$

From Figure 2.5, dev\_max = 1.3 mV, dev\_min = -1 mV, and  $V_{OH}$ - $V_{OL}$  = 2.5 V, then:

$$NL_{200} = \frac{\frac{0.0013 + 0.001}{2}}{2.5} \times 100 = 0.046\%$$

7 / 20

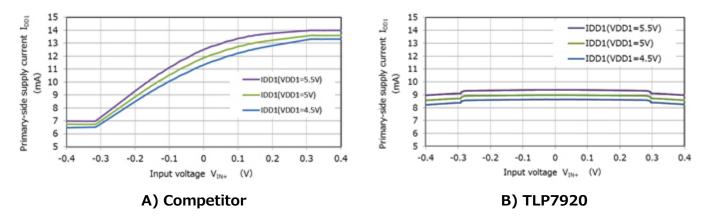

#### Primary-side supply current

Figure 2.6 shows the relationships between the input voltage and the primary-side supply current of the TLP7920 (B) side) and a competitor's isolation amplifier (A) side). The primary-side supply current of the competitor's isolation amplifier increases with input voltage while the TLP7920 has a unique digital encoder/decoder technology to maintain the primary-side supply current at almost a constant level around 9 mA (typical) over a range of input voltage (recommend operating range: -0.2 to +0.2 V). This contributes reduction of the maximum circuit current, simplifying the design of a primary-side power supply.

Figure 2.6 Relationships between the input voltage and the primary-side supply current of isolation amplifiers

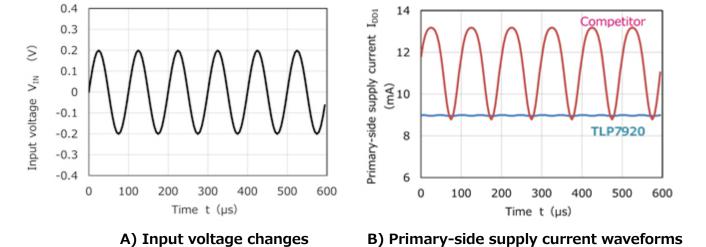

Figure 2.7 (B) shows the changes in the primary-side supply current in response to input voltage changes at a given frequency in Figure 2.7 (A).

Figure 2.7 Primary-side supply current waveforms in response to input voltage changes

The primary-side supply current of the competitor's isolation amplifier changes between 9 mA and 13 mA in response to changes in input voltage while the primary-side supply current of the TLP7920 remains around 9 mA regardless of input voltage change. For example, a

floating power supply such as a bootstrap is used as a primary-side power supply for an isolation amplifier since the floating power supply allows the use of small-value capacitors to reduce the circuit size. Obviously, the constant supply current of the TLP7920 contributes power supply consumption reduction and the circuit size reduction. In the trend of increasing system speed, this also contributes suppress electromagnetic interference (EMI) caused by large supply voltage fluctuations.

# 3. Application circuit example and bill of materials

#### 3.1 Example of an application circuit for current sensing

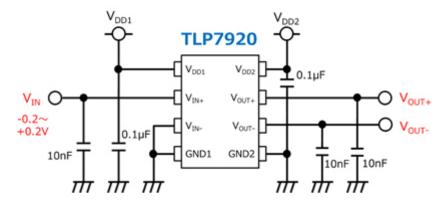

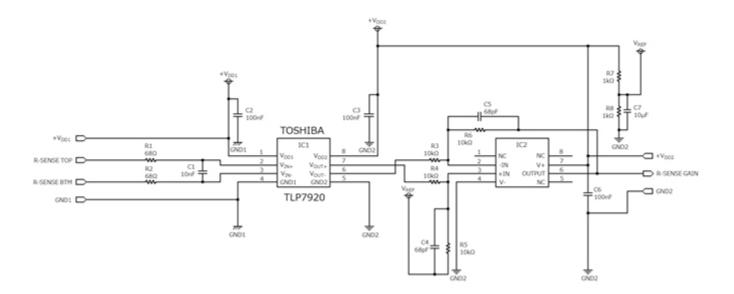

Figure 3.1 shows an example of a current-sensing circuit using the TLP7920.

Figure 3.1 Example of a current-sensing circuit using the TLP7920

In current-sensing applications, a current-sensing resistor (shunt resistor) is added between R-SENSE\_TOP and R-SENSE\_BTM in Figure 3.1. A voltage across the shunt resistor is measured to calculate the current flowing through it.

#### 3.2 Bill of materials

Table 3.1 shows a bill of materials for the current-sensing circuit using the TLP7920

Typical Ref. Qty Value Manufacturer Description Nο. Part Number Packaging Dimensions in mm (inches) 1 IC1 1 TLP7920 TOSHIBA DIP8 9.66 x 7.62 2 IC2 OPA237UA ΤI SOIC 6.0 x 4.9 1 2.0 x 1.25 3 R1, R2 2 68 O 0.25 W, ±5% 2012 (0805)2.0 x 1.25 4 R3, R4, R5, R6 4  $10\;k\Omega$ 0.25 W, ±0.5% 2012 (0805)2.0 x 1.25 5 R7, R8 2 1 kΩ 0.25 W, ±0.5% 2012 (0805) $1.0 \times 0.5$ 6 C1 10 nF Ceramic, 50 V, ±10% 1 1005 (0402)2.0 x 1.25 C2, C3, C6 100 nF Ceramic, 25 V, ±10% 2012 (0805) $1.6 \times 0.8$ 8 C4, C5 2 Ceramic, 100 V, ±5% 68 pF 1608 (0603)2.0 x 1.25 9 C7 1 10 µF Ceramic, 16 V, ±10% 2012 (0805)

Table 3.1 Bill of materials for the current-sensing circuit using the TLP7920

### 4. Guidelines for designing a current-sensing circuit

#### 4.1 Primary-side input line design

A clocked switched capacitor is used in the input section of the AD converter. In order to achieve continuous tracking and keep accurate characteristics, it is recommended to add a  $0.01\mu F$  bypass capacitor (C1 in Figure 3.1) to the input pin. To prevent the influence of aliasing noise from the AD converter, it is recommended to build an anti-aliasing lowpass filter at the input using two series resistors (R1 and R2 in Figure 3.1) and the bypass capacitor described above.

Calculation for the value of R1 and R2:

Design frequency of the anti-aliasing filter: 230kHz

Input bypass capacitor: 0.01µF

$$R1 = R2 = \frac{1}{2 \times \pi \times 230k \times 0.01\mu} \approx 68\Omega$$

#### 4.2 Secondary-side input line design

It is recommended to minimize the interconnect wires between the TLP7920 and the poststage ICs in order to reduce wire-to-wire coupling and board capacitances. Since the TLP7920 isolation amplifier provides an analog output, an external poststage amplifier circuit (IC2, R3, R4, R5, R6,

R7, R8, C4, and C5 in Figure 3.1) can be used to provide differential to single-ended conversion, amplitude adjustment, and noise filtering. When choosing poststage amplifier, it should have the spec which does not downgrade the performance of the TLP7920 (i.e., offset, gain, and response characteristics and their temperature dependence).

Calculation for the value of C4 and C5:

Design frequency of the noise filter: 230kHz

Amplitude adjustment gain: 0dB Input series resistors:  $10 \text{ k}\Omega$

$$C4 = C5 = \frac{1}{2 \times \pi \times 230k \times 10k} \approx 68pF$$

#### 4.3 Current-sensing resistor (shunt resistor)

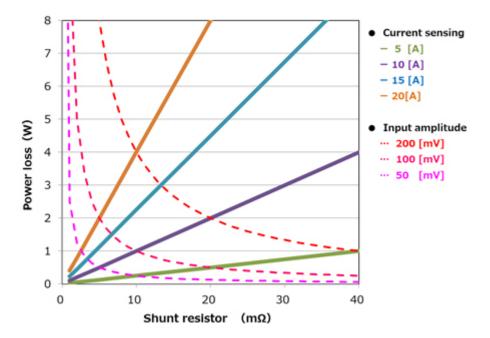

The value of the shunt resistor should be determined considering power loss and sensing accuracy. A small-value resistor is preferable in order to reduce power loss whereas a large-value resistor helps increase the signal-to-noise (SN) ratio and the sensing accuracy. Figure 4.1 shows the relationships between the shunt resistor value and the power loss. The intersection of the solid line (that represents the relationship between the shunt resistor value and the power loss) and the dashed line (that represents an auxiliary line for input amplitude) is a typical design value. An input voltage amplitude of  $\pm 200 \, \text{mV}$  is recommended for current sensing. It is recommended to determine whether the power loss requirement is satisfied based on this condition and the current level to be sensed.

Calculation example:

Design values for input amplitude: Vin

Shunt resistor: R<sub>shunt</sub>

Power loss: Pshunt

for 20A current sensing, if  $V_{IN} = 200 \text{ mV}$ :

$$R_{shunt} = \frac{V}{I} = \frac{200m}{20} = 10m\Omega$$

$$P_{shunt} = I^2 \times R = 20^2 \times 10m = 4W$$

© 2019

Toshiba Electronic Devices & Storage Corporation

Figure 4.1 Shunt resistor value vs. Power loss

#### 4.4 Test mode considerations

The TLP7920 enters test mode when either the  $V_{\text{IN+}}$  or  $V_{\text{IN-}}$  pin exceeds ( $V_{\text{DD1}}$ -2) volts (e.g., 5V -2V = 3V when  $V_{DD1} = 5V$ ). Don't use the TLP7920 in such a condition.

#### 5. Simulation

#### 5.1 Basic operation

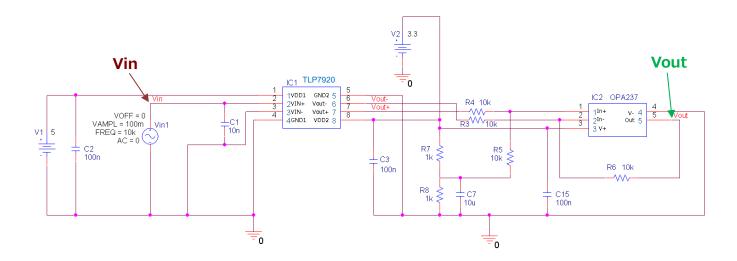

This section shows the simulation results for verifying the basic operation of the TLP7920. Figure 5.1 shows the simulation circuit under the following conditions:

- Simulation conditions

- · V<sub>DD1</sub> of IC1: 5V

- · V<sub>DD2</sub> of IC1 and V+ of IC2: 3.3V

- · Vin

Input voltage (10-kHz sine wave with 0.2Vp-p)

© 2019 12 / 20 2019-04-02 Toshiba Electronic Devices & Storage Corporation

Figure 5.1 Simulation circuit to verify basic operation

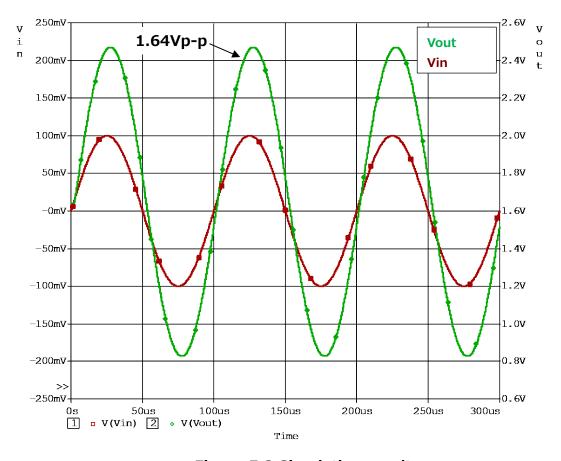

Figure 5.2 shows the simulation results. The output is a 10kHz sine wave with 1.64Vp-p, which has x8.2 as large an amplitude as the input signal (10kHz sine wave) with 0.2Vp-p. This is equal to the specified typical gain of x8.2 of the TLP7920, indicating that simulation ran properly.

Figure 5.2 Simulation results

#### **5.2 Noise superimposed on the input voltage**

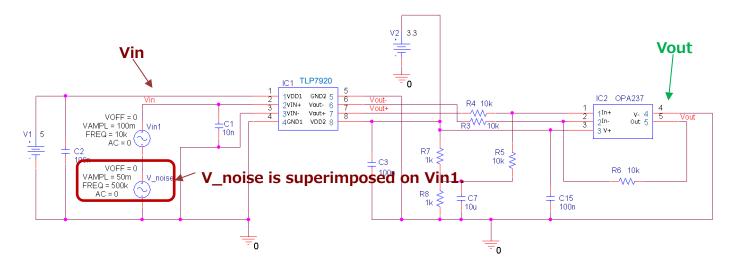

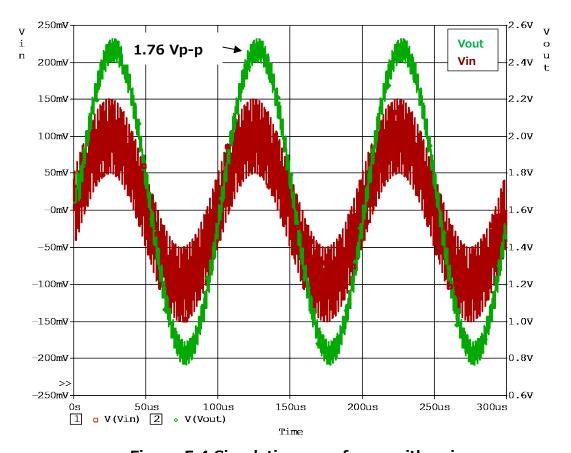

Running a simulation superimposing a noise signal (a 500-kHz sine wave with 100 mVp-p) on the input voltage, Vin1. The other conditions are the same as for the previous simulation. Figure 5.3 shows the circuit simulated.

Figure 5.3 Simulation circuit superimposing a noise

Figure 5.4 shows the simulation results, which indicate that the output waveform was not measured properly due to the influence of the noise.

Figure 5.4 Simulation waveforms with noise

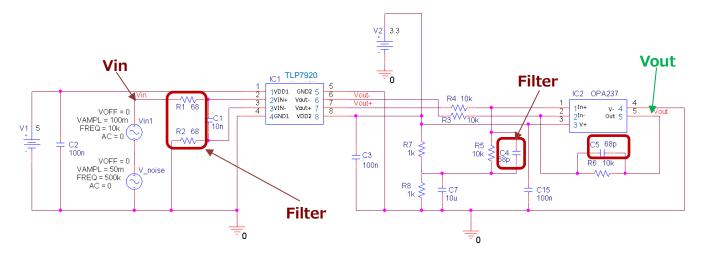

#### 5.3 Circuit with filters

Running a simulation with input filters. A 100mVp-p noise signal (1MHz sine wave) was superimposed onto Vin1. The added filters were as follows:

Primary-side input line:

Anti-aliasing LPF frequency: 230kHz

LPF resistor: R1 = R2 =  $68\Omega$

Input bypass capacitor  $C1 = 0.01 \mu F$

Secondary-side output line:

Noise filter frequency: 230kHz Amplitude adjustment gain: 0 dB Input series resistors: 10 k $\Omega$

Input bypass capacitors: C4 = C5 = 68 pF

Figure 5.5 shows the simulation circuit.

Figure 5.5 Circuit with filters simulated

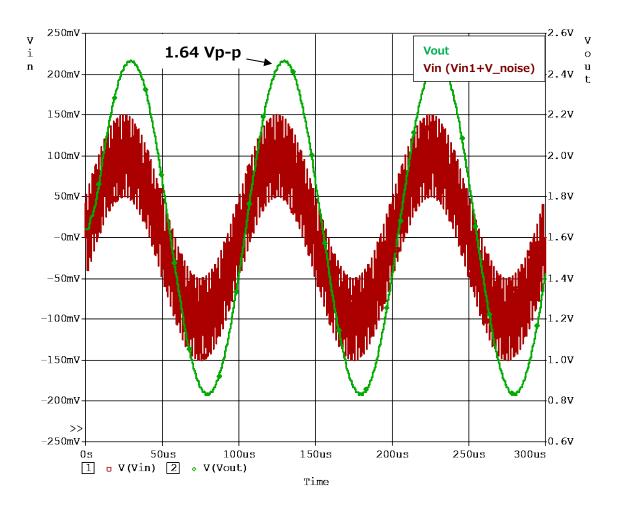

Figure 5.6 provides the simulation results, which show that the filters removed a noise from the output waveform. The output is a 10kHz sine wave with 1.64Vp-p, which has x8.2 as large an amplitude as the input signal (10kHz sine wave) with 0.2Vp-p. This is equal to the specified typical gain of x8.2 of the TLP7920, indicating that simulation ran properly.

© 2019

Toshiba Electronic Devices & Storage Corporation

15 / 20

Rev. 2

Figure 5.6 Results of simulation of a circuit with filters

#### 6. Product overview

#### 6.1. Overview

The TLP7920 is an optically coupled isolation amplifier that has a high-precision delta-sigma AD converter at the primary side and a DA converter at the secondary side.

Recommended supply voltage ranges:

```

Primary side = 4.5 to 5.5 V, Secondary side = 3.0 to 5.5 V

```

- Operating temperature range: -40 to +105°C

- Common-mode transient immunity (CMTI): 15kV/µs (minimum)

- Low power consumption:

Primary supply current = 8.6 mA (typical), Secondary supply current = 6.2 mA (typical)

Excellent output nonlinearity characteristics:

```

NL_{200}=0.02% (typical) at Vin+ = -200mV to +200mV NL_{100}=0.015% (typical) at Vin+ = -100mV to +100mV

```

Excellent temperature stability

Input offset drift:  $2\mu V/^{\circ}C$  (typical) Gain drift:  $0.00012V/V/^{\circ}C$  (typical)

V<sub>OUT</sub> nonlinearity drift: 0.00007%/°C (typical)

Safety standards

UL-approved: UL1577, File No. E67349

cUL-approved: CSA Component Acceptance Service No. 5A File No. E67349 VDE-approved: EN60747-5-5, EN60065, EN60950-1, EN 62368-1 (Note 1)

Note 1: When VDE-approved parts are needed, please designate the Option (D4).

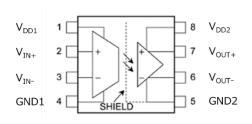

#### 6.2. External view and pin assignment

#### External view and marking

#### Pin assignment

| Pin No. | Symbol     | Description                |  |  |

|---------|------------|----------------------------|--|--|

| 1       | $V_{DD1}$  | Input side supply voltage  |  |  |

| 2       | $V_{IN+}$  | Positive input             |  |  |

| 3       | $V_{IN-}$  | Negative input             |  |  |

| 4       | GND1       | Input side ground          |  |  |

| 5       | GND2       | Output side ground         |  |  |

| 6       | $V_{OUT}$  | Negative output            |  |  |

| 7       | $V_{OUT+}$ | Positive output            |  |  |

| 8       | $V_{DD2}$  | Output side supply voltage |  |  |

Figure 6.1 External view, marking, and pin assignment of the TLP7920

#### 6.3. Internal block diagram

Note: Add 0.1-µF bypass capacitors between Pin 1 and Pin 4 and between Pin 5 and Pin 8.

Figure 6.2 Internal block diagram of the TLP7920

# 6.4 Output voltages for different primary- and secondary-side power supply combinations

Table 6.1 shows the output voltages obtained from different primary- and secondary-side power supply combinations.

Table 6.1 Output voltages for different power supply combinations

#### ■ V<sub>OUT+</sub> output

| I                                                      |     |                                       |     |

|--------------------------------------------------------|-----|---------------------------------------|-----|

|                                                        |     | Primary-Side Power                    |     |

|                                                        |     | Supply, V <sub>DD1</sub>              |     |

|                                                        |     | ON                                    | OFF |

| Secondary-<br>Side Power<br>Supply<br>V <sub>DD2</sub> | ON  | V <sub>IN</sub> x Gain/2<br>+1.25 (V) | GND |

|                                                        | OFF | GND                                   | GND |

#### ■ V<sub>OUT</sub>- output

|                                                        |     | Primary-Side Power                    |        |

|--------------------------------------------------------|-----|---------------------------------------|--------|

|                                                        |     | Supply, V <sub>DD1</sub>              |        |

|                                                        |     | ON                                    | OFF    |

| Secondary-<br>Side Power<br>Supply<br>V <sub>DD2</sub> | ON  | V <sub>IN</sub> x Gain/2<br>+1.25 (V) | +2.5 V |

|                                                        | OFF | GND                                   | GND    |

#### **Terms of Use**

This terms of use is made between Toshiba Electronic Devices and Storage Corporation ("We") and customers who use documents and data that are consulted to design electronics applications on which our semiconductor devices are mounted ("this Reference Design"). Customers shall comply with this terms of use. Please note that it is assumed that customers agree to any and all this terms of use if customers download this Reference Design. We may, at its sole and exclusive discretion, change, alter, modify, add, and/or remove any part of this terms of use at any time without any prior notice. We may terminate this terms of use at any time and for any reason. Upon termination of this terms of use, customers shall destroy this Reference Design. In the event of any breach thereof by customers, customers shall destroy this Reference Design, and furnish us a written confirmation to prove such destruction.

#### 1. Restrictions on usage

- 1. This Reference Design is provided solely as reference data for designing electronics applications. Customers shall not use this Reference Design for any other purpose, including without limitation, verification of reliability.

- 2. This Reference Design is for customer's own use and not for sale, lease or other transfer.

- 3. Customers shall not use this Reference Design for evaluation in high or low temperature, high humidity, or high electromagnetic environments.

- 4. This Reference Design shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

#### 2. Limitations

- 1. We reserve the right to make changes to this Reference Design without notice.

- 2. This Reference Design should be treated as a reference only. We are not responsible for any incorrect or incomplete data and information.

- 3. Semiconductor devices can malfunction or fail. When designing electronics applications by referring to this Reference Design, customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of semiconductor devices could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Customers must also refer to and comply with the latest versions of all relevant our information, including without limitation, specifications, data sheets and application notes for semiconductor devices, as well as the precautions and conditions set forth in the "Semiconductor Reliability Handbook".

- 4. When designing electronics applications by referring to this Reference Design, customers must evaluate the whole system adequately. Customers are solely responsible for all aspects of their own product design or applications. WE ASSUME NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- 5. No responsibility is assumed by us for any infringement of patents or any other intellectual property rights of third parties that may result from the use of this Reference Design. No license to any intellectual property right is granted by this terms of use, whether express or implied, by estoppel or otherwise.

- 6. THIS REFERENCE DESIGN IS PROVIDED "AS IS". WE (a) ASSUME NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (b) DISCLAIM ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO THIS REFERENCE DESIGN, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

#### 3. Export Control

Customers shall not use or otherwise make available this Reference Design for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). This Reference Design may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of this Reference Design are strictly prohibited except in compliance with all applicable export laws and regulations.

#### 4. Governing Laws

This terms of use shall be governed and construed by laws of Japan.

© 2019 20 / 20 Toshiba Electronic Devices & Storage Corporation