## Load Switch Application and Operation of the TCK321G, TCK322G and TCK323G

# **Reference Guide**

## RD008-RGUIDE-03

### **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

## TOSHIBA

### Table of Contents

| 1.    | OVERVIEW                                           | 3 |

|-------|----------------------------------------------------|---|

| 1.1.  | Target applications                                | 3 |

| 2.    | APPLICATION CIRCUIT EXAMPLE AND BILL OF MATERIALS4 | 1 |

| 2.1.  | Application circuit example                        | 1 |

| 2.2.  | Bill of materials                                  | 1 |

| 3.    | INPUT SELECTION FUNCTIONS                          | 5 |

| 3.1.  | Auto Selection mode                                | 5 |

| 3.2.  | Manual Selection mode                              | 5 |

| 4.    | DESIGN CONSIDERATIONS                              | 7 |

| 5.    | PRODUCT OVERVIEW                                   | 7 |

| 5.1.  | TCK321G, TCK322G and TCK323G                       | 7 |

| 5.1.1 | Overview                                           | 7 |

| 5.1.2 | . External view and pin assignment 8               | 3 |

| 5.1.3 | Product list                                       | • |

| 5.1.4 | Internal block diagram                             | ) |

| 5.1.5 | Operation logic table 10                           | ) |

| 5.1.6 | Pin description                                    | 2 |

### 1. Overview

Fabricated using a high-voltage CMOS process, the TCK321G, TCK322G and TCK323G 2-to-1 multiplexer load switches operate with an input voltage of up to 36 V. These load switches provide inrush current limiter, thermal shutdown, overvoltage lockout, undervoltage lockout, reverse-current blocking, and a flag output signal. The TCK321G and TCK322G provide manual selection mode in which an input is selected according to an external control signal. In addition, the TCK321G, TCK322G and TCK323G all have auto selection mode in which an input is selected in a predefined priority order. All these load switches also can operate on their own. The built-in multiplexer function suits the high-current, high-voltage power management of battery charging applications for smartphones, tablets, and other mobile devices having multiple charging options.

Among the many features of the TCK321G, TCK322G and TCK323G, this reference guide focuses on their operation and application of break-before-make switches designed for safe input selection.

For detail of the other protection features and other details of the TCK321G, TCK322G and TCK323G, see their datasheets.

To download the datasheets for the TCK321G, TCK322G and TCK323G  $\rightarrow$

#### Click Here

#### **1.1.** Target applications

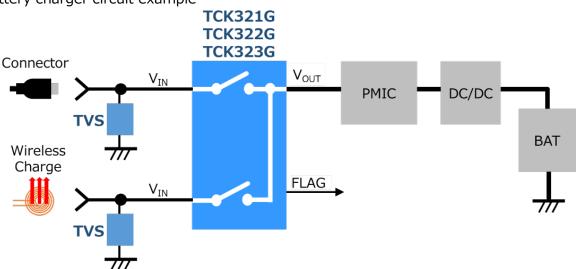

• Main switches in battery charging and other applications for smartphones, tablets, wearable devices, and other mobile devices having multiple charging options

Battery charger circuit example

\* Toshiba offers TVS diodes which suits charger and other high-current applications.

For details of TVS diodes  $\rightarrow$

Click Here

## TOSHIBA

### 2. Application circuit example and bill of materials

#### 2.1. Application circuit example

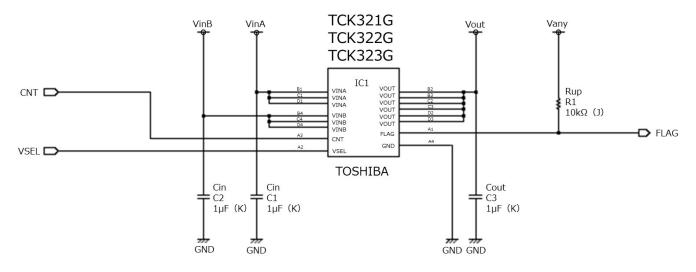

Figure 2.1.1 shows an example of an application circuit for the TCK321G, TCK322G and TCK323G.

#### 2.2. Bill of materials

Table 2.2.1 Bill of materials

| No. | Ref. | Qty | Value | Part Number                   | Manufacturer | Description                   | Packaging | Typical<br>Dimensions<br>mm (inches) |

|-----|------|-----|-------|-------------------------------|--------------|-------------------------------|-----------|--------------------------------------|

| 1   | IC1  | 1   | —     | ТСК321G<br>ТСК322G<br>ТСК323G | TOSHIBA      | Multiplexer<br>load switch IC | WCSP16C   | 1.9 x 1.9                            |

| 2   | R1   | 1   | 10kΩ  |                               |              | 63mW, ±5%                     | Ι         | 1.0 x 0.5<br>(0402)                  |

| 3   | C1   | 1   | 1µF   |                               |              | Ceramic, 50V, ±10%            | Ι         | 3.2 x 1.6<br>(1206)                  |

| 4   | C2   | 1   | 1µF   |                               |              | Ceramic, 50V, ±10%            | –         | 3.2 x 1.6<br>(1206)                  |

| 5   | C3   | 1   | 1µF   |                               |              | Ceramic, 50V, ±10%            | _         | 3.2 x 1.6<br>(1206)                  |

### **3. Input selection functions**

The TCK321G, TCK322G and TCK323G have break-before-make (BBM) switches for input selection, which open (break) one contact before closing (making) the other. The BBM switches prevent two power supply paths from being short-circuited momentarily. Both the Manual and Auto Selection modes take advantage of the characteristics of break-before-make switches. The Auto Selection mode is available with the TCK321G, TCK322G and TCK323G whereas the Manual Selection mode is available with the TCK321G and TCK322G. The following subsections describe the operation in each mode.

#### 3.1. Auto Selection mode

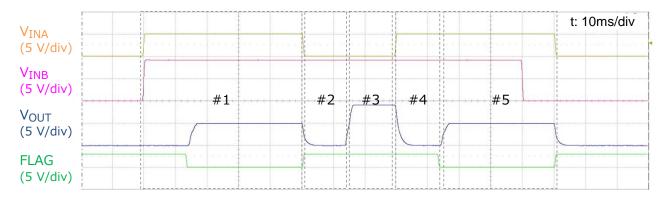

In Auto Selection mode, the TCK321G, TCK322G and TCK323G determine whether  $V_{INA}$  and  $V_{INB}$  are within the normal voltage range and automatically pass whichever is at a normal input voltage to the output. If both  $V_{INA}$  and  $V_{INB}$  are within the normal voltage range,  $V_{INA}$  takes precedence over  $V_{INB}$ . The function of the FLAG signal differs among these load switches. The FLAG signal is driven Low when either  $V_{INA}$  or  $V_{INB}$  is selected. Figure 3.1.1 and Figure 3.1.2 show typical waveforms.

- 1.  $V_{\text{INA}}$  is selected and passed to  $V_{\text{OUT}},$  and FLAG goes Low state.

- 2. When  $V_{INA}$  drops to 0 V, FLAG goes High state and  $V_{OUT}$  drops to 0 V.

- 3.  $V_{INB}$  is selected and passed to  $V_{OUT}$ .

- 4. When  $V_{\text{INA}}$  rises, FLAG goes Low state and  $V_{\text{OUT}}$  drops to 0 V.

- 5.  $V_{\text{INA}}$  is selected and passed to  $V_{\text{OUT}}.$

VINA (5 V/div)

t: 10ms/div

VINB (5 V/div)

#1

#2

#3

#4

#5

VOUT (5 V/div)

#1

#2

#3

#4

#5

FLAG (5 V/div)

[5 V/div]

[5 V/div]

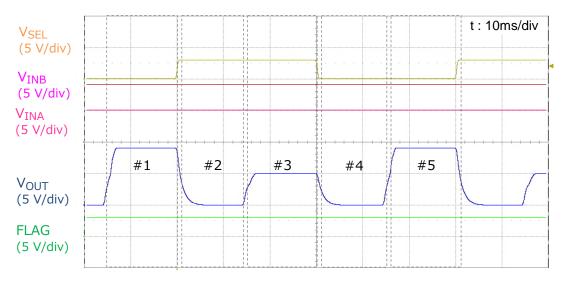

#### TCK323G: The FLAG output goes Low state when $V_{\text{INB}}$ is selected.

#### Figure 3.1.2 Typical waveforms of the TCK323G in Auto Selection mode

- 1. When  $V_{INA}$  is selected to  $V_{OUT}$ , FLAG goes High state.

- 2. When  $V_{\text{INA}}$  drops to 0 V,  $V_{\text{OUT}}$  drops to 0 V.

- 3.  $V_{INB}$  is selected and passed to  $V_{OUT}$ , and FLAG goes Low state.

- 4. When  $V_{INA}$  rises, FLAG goes High state and  $V_{OUT}$  drops to 0 V.

- 5.  $V_{INA}$  is selected and passed to  $V_{OUT}$ .

#### 3.2. Manual Selection mode

In Manual Selection mode, the TCK321G and TCK322G allow either one of the inputs to be selected via the  $V_{SEL}$  pin. Figure 3.2.1 shows typical waveforms.

## Figure 3.2.1 Typical waveforms of the TCK321G and TCK322G in Manual Selection mode

- 1.  $V_{\text{INB}}$  is selected and passed to  $V_{\text{OUT}}.$

- 2. When  $V_{SEL}$  is set High,  $V_{OUT}$  drops to 0 V.

- 3.  $V_{\text{INA}}$  is selected and passed to  $V_{\text{OUT}}.$

- 4. When  $V_{\text{SEL}}$  is set Low,  $V_{\text{OUT}}$  drops to 0 V.

- 5.  $V_{\text{INB}}$  is selected and passed to  $V_{\text{OUT}}$ .

### 4. Design considerations

#### External capacitors

Add external input and output capacitors at least  $1\mu$ F to achieve the guaranteed performance and improve the stability of a power supply.

#### Board assembly

Provide a GND plane as large as possible to reduce wire impedance. Voltage overshoot and undershoot may happen depending on transient responses of the input and output voltage and current, a PCB layout, and internal parasitic of an IC.

#### Reverse-current blocking

The TCK321G, TCK322G and TCK323G have a reverse-current blocking circuit. While the nchannel output MOSFET is off and the input voltage ( $V_{IN}$ ) is within the operating range, the reverse-current blocking circuit constantly monitors the output voltage ( $V_{OUT}$ ) and prevents a current from  $V_{OUT}$  to  $V_{IN}$  in the reverse direction. The purpose of the reverse-current blocking circuit is to protect a power supply and other circuits connected to the  $V_{IN}$  pin.

#### Protection circuits

The TCK321G, TCK322G and TCK323G have reverse-current blocking circuit, thermal shutdown, overvoltage lockout, and undervoltage lockout circuits which are not intended to guarantee that the ICs always remain below their absolute maximum ratings. You should apply the above design considerations and derate the absolute maximum rated values as described in the Toshiba Semiconductor Reliability Handbook to ensure that none of the absolute maximum ratings will be exceeded under any circumstances. It is recommended to add fail-safe and other safety features to an application system.

Power dissipation

Designing PCB, the IC temperature remains well below the maximum rated temperature during operation even at the maximum power dissipation point. For PCB design, ambient temperature, input voltage, and output current, and other environmental conditions should also be considered.

### 5. Product overview

## 5.1. TCK321G, TCK322G and TCK323G 5.1.1 Overview

The TCK321G, TCK322G and TCK323G 2-to-1 multiplexer load switches operate with an input voltage of up to 36V. These load switches feature a typical low on-resistance of  $98m\Omega$  (at  $V_{IN} = 4.5V$  and  $I_{OUT} = 1.0A$ ), a maximum output current of 2A, and a wide operating input voltage range from

## TOSHIBA

#### 2.3V to 36V.

• Small package: WCSP16C with a 0.5mm ball pitch (1.9mm x 1.9mm, t: 0.5mm typical),

PD = 1.65W

- High input voltage: V<sub>IN</sub> (max) = 36V

- High output current:  $I_{OUT}$  (DC) = 2.0A per channel

- Low on-resistance:  $R_{ON} = 98 \text{ m}\Omega$  (typical) at  $V_{IN} = 4.5 \text{V}$  and  $I_{OUT} = 1.0 \text{A}$

• Overvoltage lockout (OVLO) circuit: TCK321G = 12V, TCK322G and TCK323G = 15V (typical)

• Undervoltage lockout (UVLO): 2.9V (typical)

• Auto Selection mode in which either one of the two inputs is automatically selected (available with the TCK321G, TCK322G and TCK323G)

- Manual Selection mode in which either one of the two inputs is selected via an external signal (available with the TCK321G and TCK322G)

- FLAG output

• FLAG output in Auto Selection mode: Driven Low when the priority input ( $V_{INA}$  for the TCK321G and TCK322G and  $V_{INB}$  for the TCK323G) is within the normal voltage range

• FLAG output in Manual Selection mode: Driven Low when a voltage outside the normal range is applied to either one of the inputs

- Reverse-current blocking (switch-off state)

- Inrush current limiting circuit

- Thermal shutdown circuit

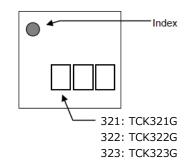

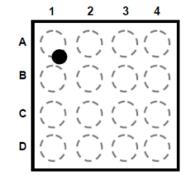

#### 5.1.2. External view and pin assignment

#### External view and marking

Pin assignment (Top view)

|   | 1    | 2                | 3    | 4    |

|---|------|------------------|------|------|

| Α | FLAG | V <sub>SEL</sub> | CNT  | GND  |

| в | VINA | Vout             | Vout | VINB |

| С | VINA | Vout             | Vout | VINB |

| D | VINA | Vout             | Vout | VINB |

Figure 5.1.1 External view, marking, and pin assignment of the TCK321G, TCK322G and TCK323G

#### 5.1.3 Product list

| Part<br>Number | Overvoltage<br>Lockout<br>V <sub>INA</sub> | Overvoltage<br>Lockout<br>V <sub>INB</sub> | FLAG Output<br>(in Auto Selection<br>mode) |

|----------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|

| TCK321G        | 12.0 V (typ.)                              | 12.0 V (typ.)                              | Q1                                         |

| TCK322G        | 15.0 V (typ.)                              | 15.0 V (typ.)                              | Q1                                         |

| TCK323G        | 15.0 V (typ.)                              | 15.0 V (typ.)                              | Q2                                         |

Table 5.1.1 Product list

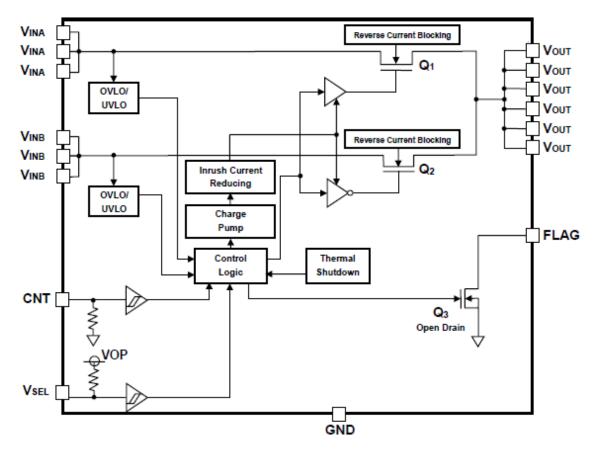

#### 5.1.4 Internal block diagram

Figure 5.1.2 Internal block diagram of the TCK321G, TCK322G and TCK323G

#### 5.1.5 Operation logic table

### Table 5.1.2 Operation logic table of the TCK321G, TCK322G and TCK323G

|             |                           | Manual S                         | Selection mode                                                        |                                                                                     |                                                                                     |                                                                                                                                                                 |  |  |  |

|-------------|---------------------------|----------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|             |                           |                                  | $V_{UVL} < V_{INA} < V_{OVL}$<br>and<br>$V_{UVL} < V_{INB} < V_{OVL}$ | $V_{UVL} < V_{INA} < V_{OVL}$ and $V_{INB} > V_{OVL} \text{ or } V_{UVL} > V_{INB}$ | $V_{UVL} > V_{INA} \text{ or } V_{INA} > V_{OVL}$ and $V_{UVL} < V_{INB} < V_{OVL}$ | $\label{eq:V_UVL} \begin{array}{c} V_{UVL} > V_{INA} \text{ or } V_{INA} > V_{OVL} \\ \\ and \\ \\ V_{INB} > V_{OVL} \text{ or } V_{UVL} > V_{INB} \end{array}$ |  |  |  |

|             | V <sub>SEL</sub> : "LOW"  | Q1 (V <sub>INA</sub> )           | OFF (V <sub>INA</sub> output disabled)                                |                                                                                     |                                                                                     |                                                                                                                                                                 |  |  |  |

| CNT: "HIGH" |                           | Q2 (V <sub>INB</sub> )           | $ON~(V_{INB}=V_{OUT})$                                                | OFF ( $V_{INB}$ output disabled)                                                    | $ON~(V_{INB}=V_{OUT})$                                                              | OFF (V <sub>INB</sub> output<br>disabled)                                                                                                                       |  |  |  |

|             |                           | Q3 (FLAG)<br>Note 2              | OFF (High-Z)                                                          | ON (LOW)                                                                            |                                                                                     |                                                                                                                                                                 |  |  |  |

|             |                           | Reverse-<br>Current<br>Blocking  | $V_{INA}$ : Enabled, $V_{INB}$ :<br>Disabled                          | $V_{INA}$ : Enabled, $V_{INB}$ :<br>Enabled                                         | $V_{INA}$ : Enabled, $V_{INB}$ :<br>Disabled                                        | $V_{INA}$ : Enabled, $V_{INB}$ :<br>Enabled                                                                                                                     |  |  |  |

|             |                           | Q1 (V <sub>INA</sub> )           | ON (V <sub>INA</sub> = V <sub>OUT</sub> )                             |                                                                                     | OFF (V <sub>INA</sub> output disabled)                                              |                                                                                                                                                                 |  |  |  |

|             | IGH"                      | Q2 (V <sub>INB</sub> )           |                                                                       | OFF (V <sub>INB</sub> output disabled)                                              |                                                                                     |                                                                                                                                                                 |  |  |  |

|             | V <sub>SEL</sub> : "HIGH" | Q3 (FLAG)<br>Note 2              | OFF (High-Z)                                                          |                                                                                     | ON (LOW)                                                                            |                                                                                                                                                                 |  |  |  |

|             |                           | Reverse-Current<br>Blocking      | $V_{INA}$ : Disabled,                                                 | $V_{INB}$ : Enabled                                                                 | $V_{INA}$ : Enabled, $V_{INB}$ : Enabled                                            |                                                                                                                                                                 |  |  |  |

|             |                           | Q1 (V <sub>INA</sub> )           | OFF (V <sub>INA</sub> output disabled)                                |                                                                                     |                                                                                     |                                                                                                                                                                 |  |  |  |

|             | "LOW"                     | Q2 (V <sub>INB</sub> )           |                                                                       | OFF ( $V_{INB}$ out                                                                 | tput disabled)                                                                      |                                                                                                                                                                 |  |  |  |

|             | N <sup>ser</sup> : "LC    | Q3 (FLAG)                        |                                                                       | OFF (H                                                                              | High-Z)                                                                             |                                                                                                                                                                 |  |  |  |

| CNT: "LOW"  |                           | Reverse-<br>Current<br>Blocking  |                                                                       | $V_{INA}$ : Enabled,                                                                | $V_{INB}$ : Enabled                                                                 |                                                                                                                                                                 |  |  |  |

|             | V <sub>seL</sub> : "HIGH" | Q1 (V <sub>INA</sub> )<br>Note1  | $ON (V_{INA} = V_{OUT})$                                              |                                                                                     | OFF ( $V_{INA}$ output disabled)                                                    |                                                                                                                                                                 |  |  |  |

|             |                           | Q2 (V <sub>INB</sub> )<br>Note 2 | OFF (V_{INB} output disabled)                                         |                                                                                     | $ON \; (V_{INB} = V_{OUT})$                                                         | OFF (V <sub>INB</sub> output<br>disabled)                                                                                                                       |  |  |  |

|             |                           | Q3 (FLAG)<br>Note3               | 321G/322G: ON (LOW) 323G: OFF (High-Z)                                |                                                                                     | 321G/322G: OFF (High-Z)<br>323G: ON (LOW)                                           | 321G/322G: OFF (High-Z)<br>323G: OFF (High-Z)                                                                                                                   |  |  |  |

|             |                           | Reverse-Current<br>Blocking      | V <sub>INA</sub> : Disabled,                                          | V <sub>INB</sub> : Enabled                                                          | $V_{INA}$ : Enabled, $V_{INB}$ :<br>Disabled                                        | $V_{INA}$ : Enabled, $V_{INB}$ : Enabled                                                                                                                        |  |  |  |

|             |                           |                                  |                                                                       |                                                                                     | Auto Selection m                                                                    | ode                                                                                                                                                             |  |  |  |

© 2020 Toshiba Electronic Devices & Storage Corporation Note 1: In Auto Selection mode,  $V_{INA}$  is always given precedence over  $V_{INB}$ .

The V<sub>INB</sub> input is never passed to V<sub>OUT</sub> as long as V<sub>INA</sub> is within the normal voltage range  $(V_{UVL} < V_{INA} < V_{OVL})$ . When V<sub>INA</sub> is outside the normal range  $(V_{UVL} > V_{INA} \text{ or } V_{INA} > V_{OVL})$ , it is determined whether V<sub>INB</sub> is within the normal voltage range.

This specification is common to the TCK321G, TCK322G and TCK323G.

Note 2: The functionality and operation of the FLAG pin differs between Manual and Auto Selection modes.

In Manual Selection mode, the FLAG pin is driven Low when either V<sub>INA</sub> or V<sub>INB</sub> is outside the normal voltage range (V<sub>UVL</sub> > V<sub>INX</sub> or V<sub>INX</sub> > V<sub>OVL</sub>). A Low on the FLAG output indicates that either V<sub>INA</sub> or V<sub>INB</sub> is outside the normal voltage range, regardless of which one is selected.

This specification is common to the TCK321G and TCK322G.

Note 3: The functionality and operation of the FLAG pin differs between Manual and Auto Selection modes.

The functionality and operation of the FLAG pin in Auto Selection mode also differ among the TCK321G, TCK322G, and TCK323G.

The TCK321G and TCK322G determine whether  $V_{INA}$  is within the normal voltage range.

When  $V_{INA}$  is within the normal voltage range ( $V_{UVL} < V_{INA} < V_{OVL}$ ), the FLAG pin is driven Low. (A Low on the FLAG pin indicates that  $V_{INA}$  is within the normal voltage range.)

The TCK323G determines whether  $V_{INB}$  is within the normal range.

When  $V_{INB}$  is within the normal voltage range ( $V_{UVL} < V_{INB} < V_{OVL}$ ), the FLAG pin is driven Low. (A Low on the FLAG pin indicates that  $V_{INB}$  is within the normal voltage range.)

#### 5.1.6 Pin description

|                              | Table 5          | 1.3 Pins of the TCK321G, TCK322G and TCK323G                                                                                                                                                               |  |

|------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin                          | Name             | Description                                                                                                                                                                                                |  |

| A1                           | FLAG             | Open-drain output.<br>The functionality of the FLAG pin differs between Auto and<br>Manual Selection modes. For details, see Table 5.1.2, "Operation<br>logic table of the TCK321G, TCK322G, and TCK323G." |  |

| A2                           | $V_{SEL}$        | Input select. The $V_{SEL}$ input is internally connected to VOP via a pullup resistor                                                                                                                     |  |

| A3                           | CNT              | Mode control.<br>The CNT pin is internally connected to GND via a pulldown<br>resistor.                                                                                                                    |  |

| A4                           | GND              | Ground                                                                                                                                                                                                     |  |

| B1, C1,<br>D1                | $V_{\text{INA}}$ | Power input. The $V_{\rm INA}$ input incorporates overvoltage lockout (OVLO) and undervoltage lockout (UVLO) circuits.                                                                                     |  |

| B4, C4<br>and D4             | $V_{\text{INB}}$ | Power input. The $V_{\rm INB}$ input incorporates overvoltage lockout (OVLO) and undervoltage lockout (UVLO) circuits.                                                                                     |  |

| B2, C2,<br>D2, B3,<br>C3, D3 | V <sub>OUT</sub> | Output.<br>V <sub>INA</sub> is given precedence over V <sub>INB</sub> in Auto Selection mode. For details, see Table 5.1.2, "Operation logic table of the TCK321G, TCK322G and TCK323G."                   |  |

#### Terms of Use

This terms of use is made between Toshiba Electronic Devices and Storage Corporation ("We") and customers who use documents and data that are consulted to design electronics applications on which our semiconductor devices are mounted ("this Reference Design"). Customers shall comply with this terms of use. Please note that it is assumed that customers agree to any and all this terms of use if customers download this Reference Design. We may, at its sole and exclusive discretion, change, alter, modify, add, and/or remove any part of this terms of use at any time without any prior notice. We may terminate this terms of use at any time and for any reason. Upon termination of this terms of use, customers shall destroy this Reference Design. In the event of any breach thereof by customers, customers shall destroy this Reference Design, and furnish us a written confirmation to prove such destruction.

#### 1. Restrictions on usage

1. This Reference Design is provided solely as reference data for designing electronics applications. Customers shall not use this Reference Design for any other purpose, including without limitation, verification of reliability.

2. This Reference Design is for customer's own use and not for sale, lease or other transfer.

3. Customers shall not use this Reference Design for evaluation in high or low temperature, high humidity, or high electromagnetic environments.

4. This Reference Design shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

#### 2. Limitations

1. We reserve the right to make changes to this Reference Design without notice.

2. This Reference Design should be treated as a reference only. We are not responsible for any incorrect or incomplete data and information.

3. Semiconductor devices can malfunction or fail. When designing electronics applications by referring to this Reference Design, customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of semiconductor devices could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Customers must also refer to and comply with the latest versions of all relevant our information, including without limitation, specifications, data sheets and application notes for semiconductor devices, as well as the precautions and conditions set forth in the "Semiconductor Reliability Handbook".

4. When designing electronics applications by referring to this Reference Design, customers must evaluate the whole system adequately. Customers are solely responsible for all aspects of their own product design or applications. WE ASSUME NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

5. No responsibility is assumed by us for any infringement of patents or any other intellectual property rights of third parties that may result from the use of this Reference Design. No license to any intellectual property right is granted by this terms of use, whether express or implied, by estoppel or otherwise.

6. THIS REFERENCE DESIGN IS PROVIDED "AS IS". WE (a) ASSUME NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (b) DISCLAIM ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO THIS REFERENCE DESIGN, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

#### 3. Export Control

Customers shall not use or otherwise make available this Reference Design for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). This Reference Design may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of this Reference Design are strictly prohibited except in compliance with all applicable export laws and regulations.

#### 4. Governing Laws

This terms of use shall be governed and construed by laws of Japan.