# MOSFET Parallel Operation (TK62N60X) Reference Guide

RD010-RGUIDE-02

**TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

1/17

2019-05-08

# Table of Contents

| 1.   | INTRODUCTION                                               | 3  |

|------|------------------------------------------------------------|----|

|      |                                                            |    |

| 2.   | VERIFICATION OF MOSFET OPERATION BY SIMULATION             | 4  |

| 2.1. | Simulation model                                           | 4  |

| 2.2. | PCB trace inductance                                       | 5  |

| 2.3. | Simulation circuit                                         | 7  |

| 2.4. | Waveforms under ideal conditions (with symmetrical traces) | 8  |

| 2.5. | Asymmetrically layout MOSFETs                              | 10 |

| 2.6. | Adding resistors to the gates of each MOSFETs              | 13 |

| 3.   | CONCLUSION                                                 | 16 |

# 1. Introduction

For power supply and other applications that MOSFETs are used as switching devices, in order to develop a new design with a higher output power based on an existing design, it is necessary to:

- 1. design a new topology or circuit configuration, or

- 2. replace MOSFETs with higher current rating (i.e., low on-resistance) without modification of the topology or circuit configuration.

The latter approach helps save a lot of development time. However, there is a limitation in increasing the current rating of a MOSFET without changing the package. To increase the output power of a design, it might be necessary to use MOSFETs in larger packages or use multiple MOSFETs in parallel. Paralleling MOSFETs has several advantages over replacing existing MOSFETs with those in larger packages. For example, since MOSFETs are common heat sources, paralleling MOSFETs makes it possible to spread heat sources apart from one another. In addition, using the same MOSFETs as in an existing system means that the same heat spreaders in the existing systems can be used.

When you choose to develop a new circuit design, you can create a printed circuit board in such a manner as to allow paralleling of multiple MOSFETs. Then, you can use the same board for different system models just by adjusting the number of parallel MOSFETs according to the output power requirement. This helps save design time and makes it possible to use the same parts across multiple system models.

As described above, paralleling MOSFETs provides various benefits for system designers. However, parallel MOSFETs might cause oscillation and other problems unless their placement and routing are symmetrical and a gate drive circuit is properly designed.

This reference guide describes the operation of parallel MOSFETs, referring to the results of simulation. As an example, the following descriptions use the TK62N60X, Toshiba's 600V MOSFET of the DTMOSIV series in the TO-247 package, which is ideal for use in the power factor correction (PFC) circuits and primary-side main switches for AC-DC power supplies. The focus of this reference guide is on providing design considerations for parallel MOSFETs to increase the output of a power supply unit.

To download the datasheets for the MOSFETs of the DTMOSIV series→

Click Here

# 2. Verification of MOSFET operation by simulation

#### 2.1. Simulation model

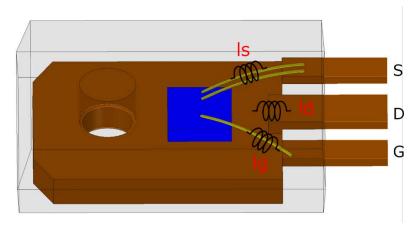

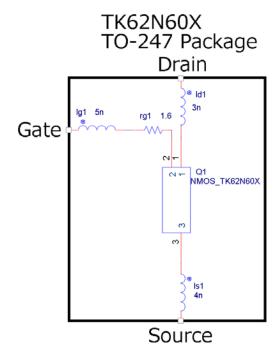

This section describes the simulation model of the TK62N60X used for verification. The PSpice model of the TK62N60X available on Toshiba's website characterizes only the chip design. In order to simulate the operation of the TK62N60X including the effect of its package, it is necessary to externally add the parasitic inductances of the TO-247 package to the PSpice model. Figure 2.1.1 illustrates the internal structure of the TO-247 package and its parasitic inductances. The bonding wires between the MOSFET chip and each of the package terminals have inductances, which are labeled lg, ls and ld in Figure 2.1.1. Figure 2.1.2 shows a simulation model including the internal parasitic inductances of the TO-247 package for TK62N60X.

Figure 2.1.1 Bonding wires in the TO-247 package

Figure 2.1.2 Simulation model

#### 2.2. PCB trace inductance

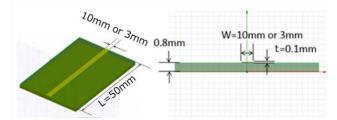

The PCB trace inductance can be calculated through an electromagnetic field analysis. Figure 2.2.1 shows the analysis conditions, and Table 2.2.1 shows the analysis results.

1. Copper trace thickness: 100 µm

2. Trace widths: Drain and source lines = 10 nm, gate line = 3 mm

3. Trace length: 50 mm4. Frequency: 1 MHz

Figure 2.2.1 Conditions for the electromagnetic field analysis

Table 2.2.1 Results of the electromagnetic field analysis

| Analysis Results  | with W = 3 mm     | Analysis Results with W = 10 mm |                   |  |

|-------------------|-------------------|---------------------------------|-------------------|--|

| Inductance per mm | Inductance when L | Inductance per mm               | Inductance when L |  |

| of trace          | = 50 mm           | of trace                        | = 50 mm           |  |

| 0.207 nH/mm       | 10.4 nH           | 0.0844 nH/mm                    | 4.22 nH           |  |

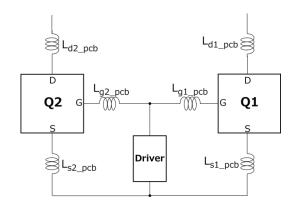

Since the inductance increases in proportion to the trace length, it is necessary to assume the length of each trace. Figure 2.2.2 shows the relationships between devices and trace inductances as well as the inductance labels. Table 2.2.2 lists the lengths and inductances of these traces.

Figure 2.2.2 Relationships between devices and trace inductances

Table 2.2.2 PCB trace inductance

| FET | Trace                                | Description                   | Trace | Trace      | Trace  |

|-----|--------------------------------------|-------------------------------|-------|------------|--------|

|     |                                      | Length                        | Width | Inductance |        |

| Q1  | Q1 Lg1_pcb Driver output to FET gate |                               | 20 mm | 3 mm       | 4.2 nH |

|     | terminal                             |                               |       |            |        |

|     | Ls1_pcb                              | FET gate terminal to driver   | 30 mm | 10 mm      | 2.6 nH |

|     |                                      | GND                           |       |            |        |

|     | Ld1_pcb                              | Inductor L to FET drain       | 50 mm | 10 mm      | 4.3 nH |

|     |                                      | terminal                      |       |            |        |

| Q2  | Lg2_pcb                              | Driver output to FET gate     | 20 mm | 3 mm       | 4.2 nH |

|     | terminal                             |                               |       |            |        |

|     | Ls2_pcb                              | FET source terminal to driver | 30 mm | 10 mm      | 2.6 nH |

|     |                                      | GND                           |       |            |        |

|     | Ld2_pcb                              | Inductor L to FET drain       | 50 mm | 10 mm      | 4.3 nH |

|     |                                      | terminal                      |       |            |        |

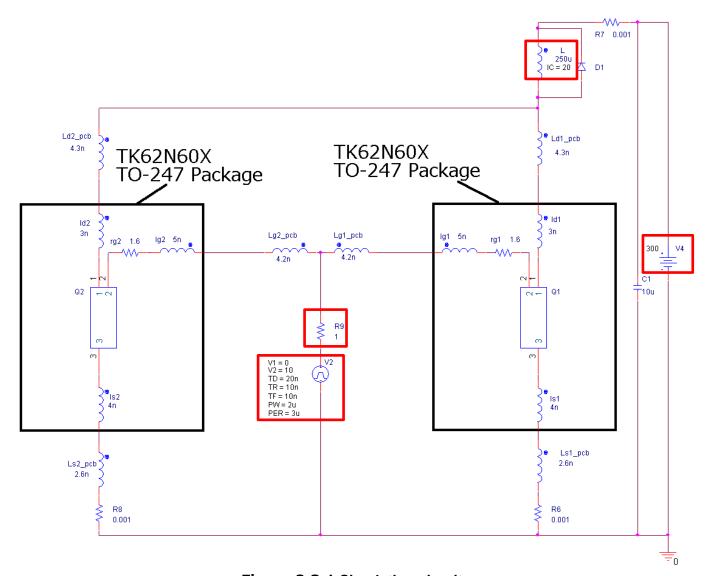

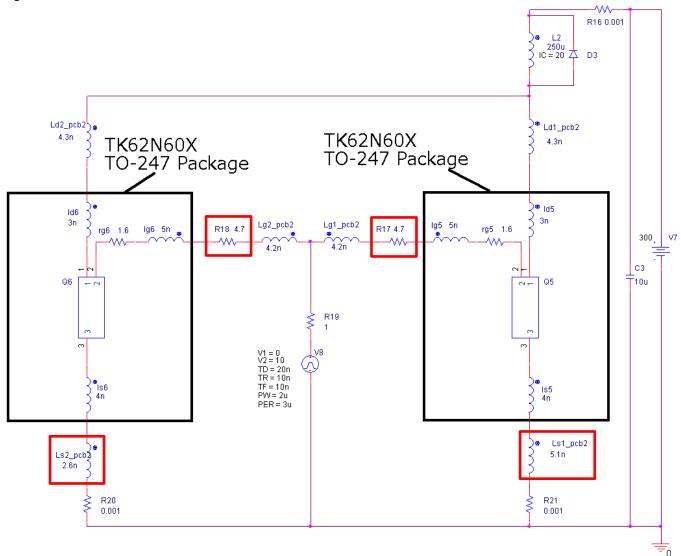

#### 2.3. Simulation circuit

Figure 2.3.1 shows the simulation circuit for verification. We performed a simulation under the following conditions:

(The PSpice circuit that can be simulated with OrCAD is available for download under the name of RD010-SPICE01.)

- 1. Supply voltage: V4 = 300 V

- 2. Inductance:  $L = 250 \mu H$ , initial current (IC) = 20 A

- 3. MOSFET driver: Supply voltage (V2) = 10 V

Output resistor (R9) =  $1 \Omega$  (common push-pull output)

Trise(TR) = Tfall(TF) = 10 ns

\* The assumption is that the device temperature remains constant at 25°C without self-heating.

Figure 2.3.1 Simulation circuit

## 2.4. Waveforms under ideal conditions (with symmetrical traces)

Figure 2.3.1 shows a simulation model in which the board traces connected to each MOSFET terminal have an equal inductance and the two parallel MOSFETs are routed completely symmetrically. First, we performed a simulation under these ideal conditions. Table 2.4.1 shows the parameters used for this simulation.

Table 2.4.1 Simulation parameters (ideal conditions)

| FET | Source Trace | Parasitic Inductance of | External Gate  |

|-----|--------------|-------------------------|----------------|

|     | Length       | Source Trace            | Resistor       |

| Q1  | 30 mm        | Ls1_pcb = 2.6 nH        | None (directly |

|     |              |                         | connected to   |

|     |              |                         | Q2)            |

| Q2  | 30 mm        | $Ls2\_pcb = 2.6 nH$     | None (directly |

|     |              |                         | connected to   |

|     |              |                         | Q1)            |

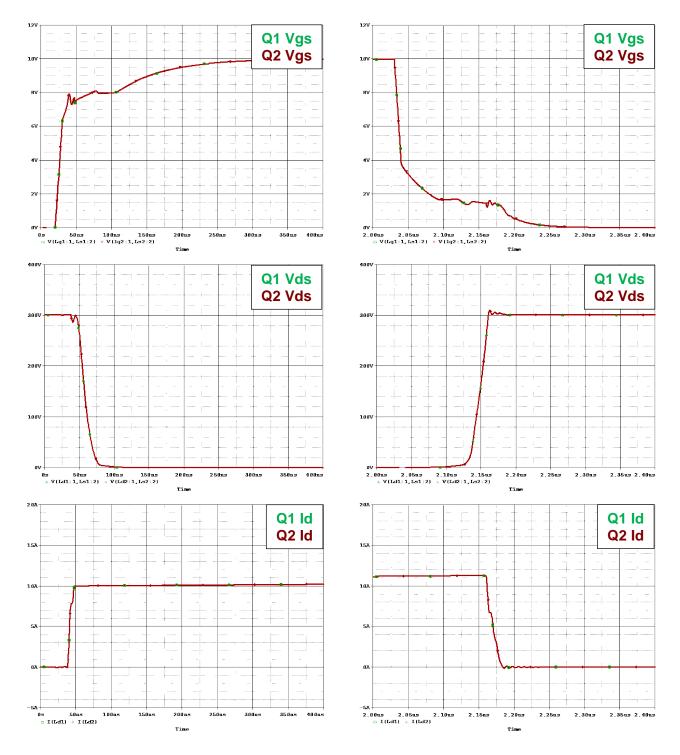

Figure 2.4.1 and Figure 2.4.2 show the simulation results. When Q1 and Q2 have an ideally symmetrical layout, their operations are perfectly balanced and have identical waveforms.

9/17

Figure 2.4.1 Turn-on waveforms under ideal conditions

Figure 2.4.2 Turn-off waveforms under ideal conditions

2019-05-08

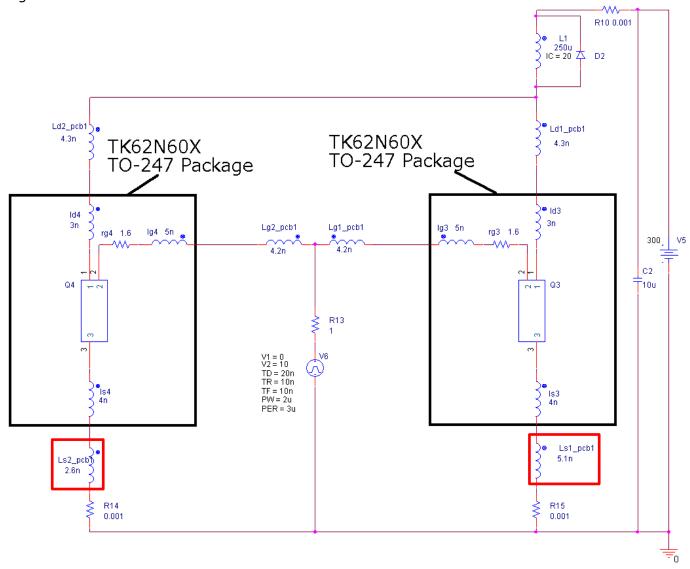

### 2.5. Asymmetrically layout MOSFETs

Next, we performed a simulation on parallel MOSFETs with an asymmetrical trace layout. The source trace of Q3 in Figure 2.5.1 is 60 mm long—30 mm longer than that of Figure 2.3.1. The 60-mm source trace of Q3 has an inductance of 5.1 nH. Table 2.5.1 shows the parameters used for this simulation.

| FET | Source Trace Length | Parasitic Inductance of | External Gate    |

|-----|---------------------|-------------------------|------------------|

|     |                     | Source Trace            | Resistor         |

| Q3  | 60 mm (30 mm + 30   | Ls1_pcb = 5.1 nH        | None (directly   |

|     | mm)                 |                         | connected to Q3) |

| Q4  | 30 mm               | Ls2_pcb = 2.6 nH        | None (directly   |

|     |                     |                         | connected to Q4) |

Table 2.5.1 Simulation parameters (asymmetrical layout)

Figure 2.5.1 shows the simulation circuit.

Figure 2.5.1 Simulation circuit

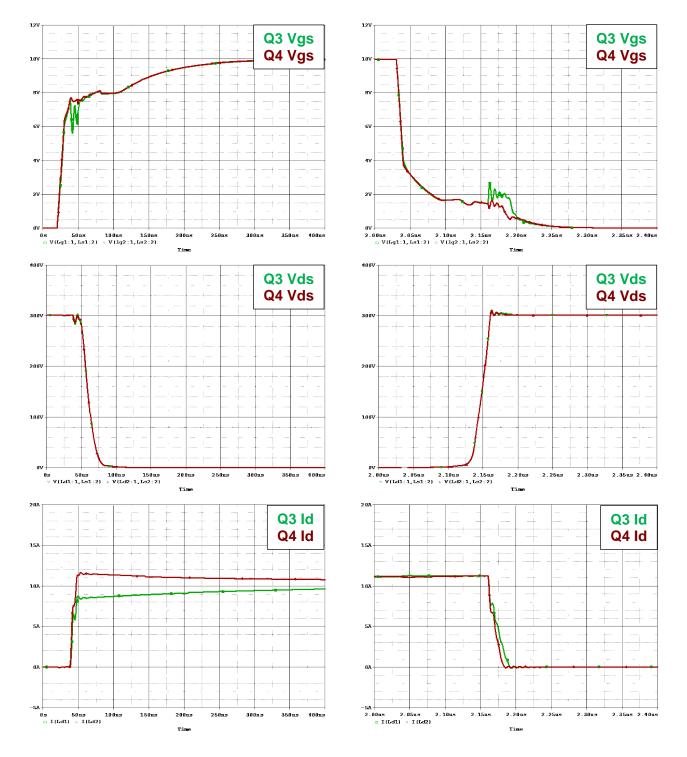

Figure 2.5.2 and Figure 2.5.3 show the simulation results. In Figure 2.5.3, Vgs oscillation is observed, and it indicates that an asymmetrical layout causes an oscillation. Figure 2.5.2 also indicates that MOSFET Q3 with larger source trace inductance turns on later than the other MOSFET Q4, and it is observed current concentration on Q4. An asymmetrical layout is undesirable in terms of both oscillation and current imbalance. It is important to create a layout as symmetrical as possible for parallel MOSFETs.

(Note: In actual operation, a MOSFET with larger current concentration dissipates much heat. This causes its on-resistance to increase, limiting a current. As a result, a current flowing to the other MOSFET increases. Therefore, the currents flowing to the parallel MOSFETs become balanced immediately after turn-on. Since this simulation is not considered heat generation, it took a longer for the currents to the parallel MOSFETs to be balanced.)

© 2019

Toshiba Electronic Devices & Storage Corporation

11 / 17

Rev. 2

Figure 2.5.2 Turn-on waveforms of asymmetrically layout parallel MOSFETs

Figure 2.5.3 Turn-off waveforms of asymmetrically layout parallel MOSFETs

## 2.6. Adding resistors to the gates of each MOSFETs

Next, to the circuit shown in Section 2.5 that occurred oscillation, we added 4.7  $\Omega$  resistors between the gates of the parallel MOSFETs and their drivers. Table 2.6.1 shows the parameters used for the simulation of this circuit.

Table 2.6.1 Simulation parameters (with gate resistors added)

| FET | Source Trace | Parasitic Inductance of | External Gate Resistor      |

|-----|--------------|-------------------------|-----------------------------|

|     | Length       | Source Trace            |                             |

| Q5  | 60 mm        | Ls1_pcb = 5.1 nH        | R17 = $4.7 \Omega$ (for Q5) |

| Q6  | 30 mm        | $Ls2_pcb = 2.6 nH$      | R18 = $4.7 \Omega$ (for Q6) |

Figure 2.6.1 shows the simulation circuit.

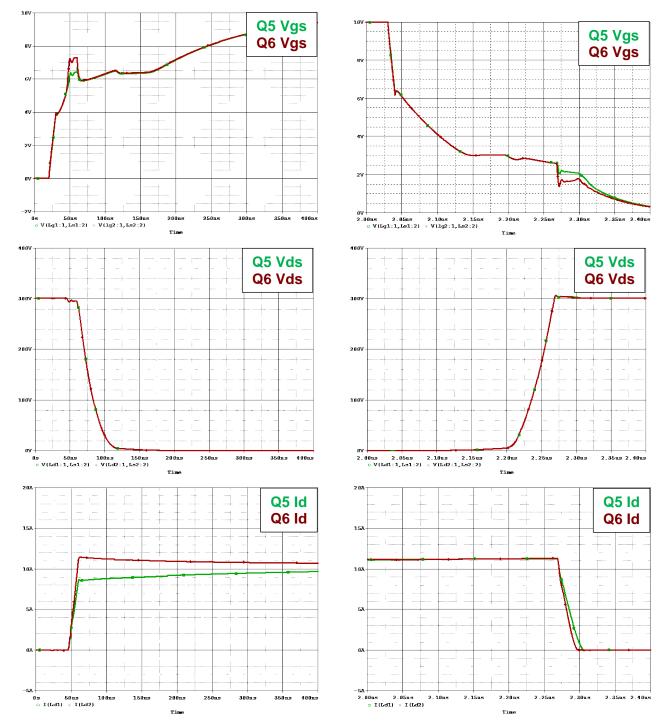

Figure 2.6.1 Simulation circuit

Figure 2.6.2 and Figure 2.6.3 show the simulation results, which is not observed oscillation. Since it is difficult to create a completely symmetrical layout for parallel MOSFETs, appropriate resistors should be added to the gate of each -MOSFETs. A slight difference in the value of gate resistors does not affect the MOSFET operation and it is acceptable to use general resistors with ±10% tolerance for this purpose. Oscillation was not observed, but unbalanced currents is still occurred during a switching transition.

(Note: In actual operation, a MOSFET with larger current concentration dissipates much heat. This causes its on-resistance to increase, limiting a current. As a result, a current flowing to the other MOSFET increases. Therefore, the currents flowing to the parallel MOSFETs become balanced immediately after turn-on. Since this simulation is not considered heat generation, it took a longer for the currents to the parallel MOSFETs to be balanced.)

© 2019 14 / 17 2019-05-08 Toshiba Electronic Devices & Storage Corporation Rev. 2

Figure 2.6.2 Turn-on waveforms of parallel MOSFETs with external gate resistors

Figure 2.6.3 Turn-off waveforms of parallel MOSFETs with external gate resistors

# 3. Conclusion

We verified the operation of parallel MOSFETs using the TK62N60X of the DTMOSIV series. As a result, we confirmed that it is important to create a board layout as symmetrical as possible for parallel MOSFETs and add gate resistors between driver IC and MOSFET.

When their layout is asymmetrical, the parallel MOSFETs do not turn on simultaneously due to a difference in the source trace inductance, causing a current imbalance during a switching transition. It is necessary to select MOSFETs with appropriate current ratings considering this current imbalance and verify their operation using an actual board.

© 2019 16 / 17 2019-05-08 Toshiba Electronic Devices & Storage Corporation Rev. 2

#### Terms of Use

This terms of use is made between Toshiba Electronic Devices and Storage Corporation ("We") and customers who use documents and data that are consulted to design electronics applications on which our semiconductor devices are mounted ("this Reference Design"). Customers shall comply with this terms of use. Please note that it is assumed that customers agree to any and all this terms of use if customers download this Reference Design. We may, at its sole and exclusive discretion, change, alter, modify, add, and/or remove any part of this terms of use at any time without any prior notice. We may terminate this terms of use at any time and for any reason. Upon termination of this terms of use, customers shall destroy this Reference Design. In the event of any breach thereof by customers, customers shall destroy this Reference Design, and furnish us a written confirmation to prove such destruction.

#### 1. Restrictions on usage

- 1. This Reference Design is provided solely as reference data for designing electronics applications. Customers shall not use this Reference Design for any other purpose, including without limitation, verification of reliability.

- 2. This Reference Design is for customer's own use and not for sale, lease or other transfer.

- 3. Customers shall not use this Reference Design for evaluation in high or low temperature, high humidity, or high electromagnetic environments.

- 4. This Reference Design shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

#### 2. Limitations

- 1. We reserve the right to make changes to this Reference Design without notice.

- 2. This Reference Design should be treated as a reference only. We are not responsible for any incorrect or incomplete data and information.

- 3. Semiconductor devices can malfunction or fail. When designing electronics applications by referring to this Reference Design, customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of semiconductor devices could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Customers must also refer to and comply with the latest versions of all relevant our information, including without limitation, specifications, data sheets and application notes for semiconductor devices, as well as the precautions and conditions set forth in the "Semiconductor Reliability Handbook".

- 4. When designing electronics applications by referring to this Reference Design, customers must evaluate the whole system adequately. Customers are solely responsible for all aspects of their own product design or applications. WE ASSUME NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- 5. No responsibility is assumed by us for any infringement of patents or any other intellectual property rights of third parties that may result from the use of this Reference Design. No license to any intellectual property right is granted by this terms of use, whether express or implied, by estoppel or otherwise.

- 6. THIS REFERENCE DESIGN IS PROVIDED "AS IS". WE (a) ASSUME NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (b) DISCLAIM ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO THIS REFERENCE DESIGN, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

#### 3. Export Control

Customers shall not use or otherwise make available this Reference Design for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). This Reference Design may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of this Reference Design are strictly prohibited except in compliance with all applicable export laws and regulations.

#### 4. Governing Laws

This terms of use shall be governed and construed by laws of Japan.

© 2019 17 / 17 Toshiba Electronic Devices & Storage Corporation