# Single-Phase PFC Power Supply Basic Simulation Circuit Reference Guide

RD031-RGUIDE-02

**TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

# Table of Contents

| 1.   | INTRODUCTION                     | 3  |

|------|----------------------------------|----|

| 2.   | OVERVIEW OF THE PFC POWER SUPPLY | 5  |

| 2.1. | Specifications                   | 5  |

| 2.2. | Circuit configuration            | 5  |

| 3.   | SIMULATION RESULTS               | 7  |

| 4.   | PRODUCT OVERVIEW                 | 10 |

| 4.1. | . TK16N60W                       | 10 |

| 4.2. | . TRS4E65F                       | 10 |

| 5.   | SIMULATION CIRCUIT               | 11 |

# 1. Introduction

Ideally, the voltage and current waveforms of alternating power are completely sinusoidal and in phase with each other. However, when an AC power supply is connected to a system, its voltage and current waveforms may go out of phase or become non-sinusoidal. A power factor represents the offset in time between the voltage and the current and is defined by following equations:

Power factor = Active power ÷ Apparent power

Active power is the actual power consumed by the load and can be calculated as an integral of instantaneous power (i.e., instantaneous voltage times instantaneous current) over an AC cycle. Apparent power is the product of the rms values of the input voltage and current.

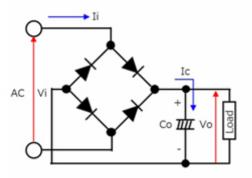

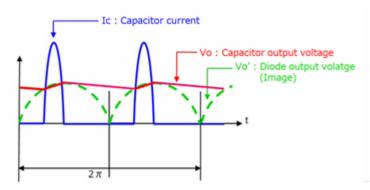

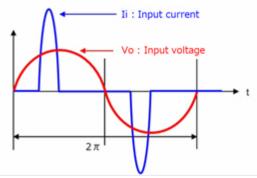

The power factor takes a value between 0 and 1. A power factor of 1 represents the ideal situation where apparent power is equal to active power. A power factor of 0 indicates that apparent power is equal to reactive power. A load with a low power factor draws more apparent power than a load with a high power factor for the same amount of active power transferred. A load with a low power factor is undesirable because it affects other systems and transmission and distribution equipment. Conventional AC-DC power supplies use a diode bridge and a capacitor. In these power supplies, an AC input is rectified to a varying DC voltage, which in turn is converted to a desired voltage. AC-DC power supplies have a pulsed input current since the capacitor is charged only when the capacitor output voltage falls below the output voltage of the diode bridge. Therefore, AC-DC power supplies have a low power factor. Figure 1.1 shows an example of a diode bridge rectifier with a capacitor filter. Figure 1.2 and Figure 1.3 show its waveforms.

Figure 1.1 Diode bridge rectifier with a capacitor filter

Figure 1.2 Waveforms at different nodes in the circuit

Figure 1.3 Input current and voltage waveforms

Rev. 2

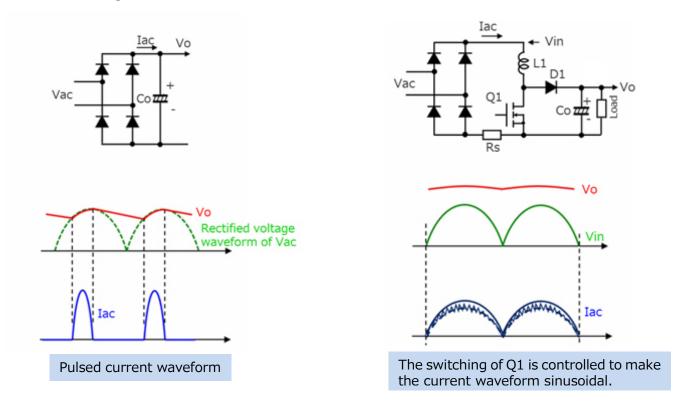

The aim of a power factor correction (PFC) circuit is to improve the power factor for AC-DC converters. At present, commonly used AC-DC power supplies incorporate a PFC circuit to improve their power factor. Typically, the PFC circuit in an AC-DC power supply is a boost converter in which an AC input is placed after a diode bridge. Figure 1.4 shows a diode bridge rectifier with a capacitor filter whereas Figure 1.5 shows a boost PFC converter.

Figure 1.4 Diode bridge rectifier with a capacitor filter

Figure 1.5 Boost PFC converter

A <u>video</u> describing the power factor of an AC-DC power supply and a PFC circuit is on Toshiba's website.

A single-phase PFC power supply, which consists of an inductor, a diode, and a MOSFET, is widely used for AC-DC power supplies with relatively small output power because it is simple and easy to control. A basic simulation circuit of a single-phase PFC power supply (RD031-SPICE-01) is available on Toshiba's website, which will help you understand its operation.

This Reference Guide provides an overview of this simulation circuit and describes its usage. OrCAD® Capture and PSpice® A/D from Cadence are necessary to simulate this circuit. Both the simulation circuit and the Reference Guide are based on OrCAD® 17.2.

# 2. Overview of the PFC power supply

RD031-SPICE-01 is a single-phase PFC power supply with a 500W output.

#### 2.1. Specifications

The specifications of the single-phase PFC power supply are as follows:

Input voltage: 90 to 264 V<sub>rms</sub>

Output voltage: 400 V

Output current: 0 to 1.25 AOperating frequency: 65 kHz

• Allowable peak-to-peak ripple current: 40 % of the peak input current

Inductance setting: 400 µH

# 2.2. Circuit configuration

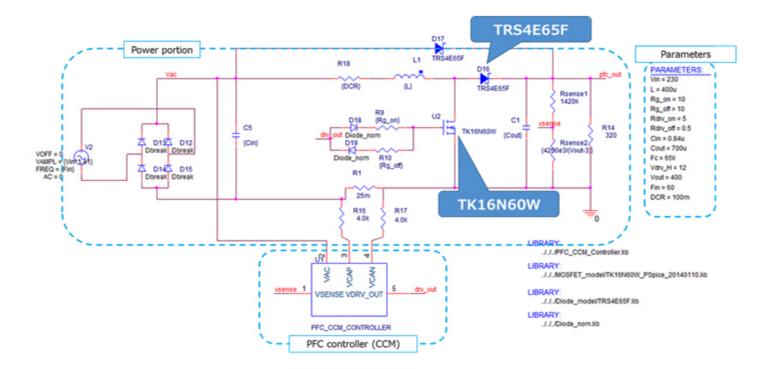

Figure 2.1 shows the simulation circuit for OrCAD<sup>®</sup>. It is a continuous-current-mode (CCM) PFC power supply, which mainly consists of three sections: a power supply section at the upper portion, a PFC controller at the lower portion, and the PARAMETERS section on the right-hand side. The PFC controller is a general-purpose controller with a MOSFET gate driver, which was prepared to create this CCM PFC power supply. The simulation circuit uses the TK16N60W and TRS4E65F as example of switching MOSFET and diode.

Figure 2.1 Simulation circuit of a 500W single-phase PFC power supply

#### Selection of the MOSFET and diode

The MOSFET and diode were selected, taking the following into consideration:

(1) Withstand voltage

In the steady state, the MOSFET and diode conduct the same voltage as the output voltage (400V) of the PFC power supply. Therefore, a MOSFET and diode with a withstand voltage of 600V or higher were selected for the simulation circuit.

(2) Current rating

The PFC power supply has the maximum input current when the output power has the maximum value and the input voltage has the minimum value. Suppose that PFC power supply has a conversion efficiency of 94% and a power factor of 1 at the maximum output power of 500W. Then, the maximum input current is calculated to be roughly  $5.9A_{rms}$  at the minimum input voltage of  $90V_{rms}$ .

Assuming a 50% duty cycle, a current of roughly  $3A_{rms}$  is applied to each device. Therefore, a MOSFET and diode with a current rating of 4A or higher were selected for the simulation circuit.

MOSFET: TK16N60W ( $V_{DS}$ =600V /  $I_{D}$ =15.9A /  $R_{DS(ON)}$ =190m $\Omega$ (Max)

Diode: TRS4E65F (650V/4A)

#### Selection of the inductor

The following paragraphs describe how to select an inductor. The value of the inductor to be used in the simulation circuit can be calculated from the following power supply parameters:

- Maximum output power: P<sub>out</sub> (W)

- Minimum AC line input voltage: V<sub>in\_min</sub> (V<sub>rms</sub>)

- PFC power conversion efficiency: η (%)

- PFC output voltage: V<sub>out</sub> (V)

- Switching frequency: F<sub>c</sub> (Hz)

- Allowable peak-to-peak ripple current: ΔI<sub>ripple</sub> (%)

Inductance is calculated by following an equation:

$$L = \frac{\left(V_{out} - \sqrt{2} \times V_{in\_min}\right) \times \eta \times 0.01 \times V_{in\_min}^{2}}{F_{c} \times 0.01 \times \Delta I_{ripple} \times P_{out} \times V_{out}}$$

where, the maximum output power ( $P_{out}$ ) is 500W, the minimum AC line input voltage ( $V_{in\_min}$ ) is 90V, the PFC output voltage is 400V, and the switching frequency ( $F_c$ ) is 65kHz. Suppose that the PFC power conversion efficiency ( $\eta$ ) is 94%. Then, inductance (L) is calculated to be 399 $\mu$ H. Therefore, inductance is set to 400 $\mu$ H in the simulation circuit.

In practice, the value of the inductor varies because of DC bias characteristics. Select an inductor that exhibits an inductance greater than the result of the above equation even when the inductance decreases because of DC bias characteristics.

6 / 16

# 3. Simulation results

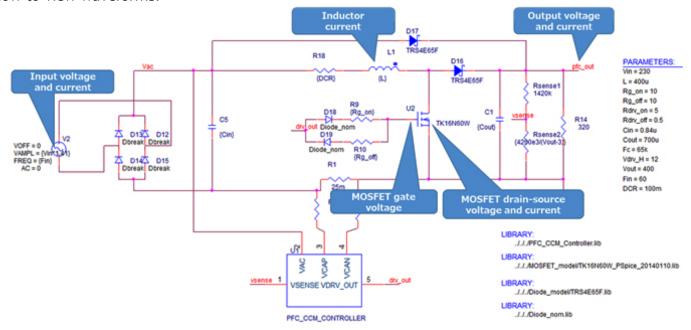

This section describes the results of the operation of each section of the simulation circuit. The following shows the waveforms of "input voltage and current", "inductor current", "output voltage and current", "MOSFET gate voltage", and "MOSFET drain-source voltage and current" highlighted in Figure 3.1 The simulation circuit model also allows you to view other waveforms. See Section 5 for how to view waveforms.

Figure 3.1 Waveforms observed

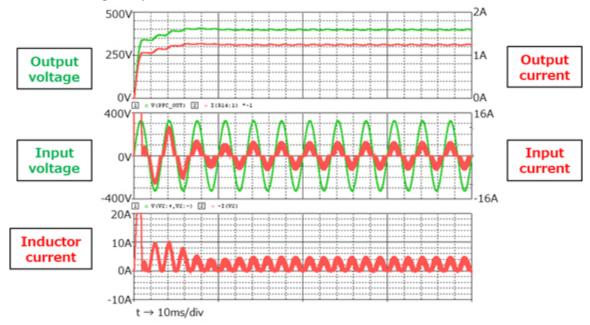

#### Input voltage and current, output voltage and current, and inductor current waveforms

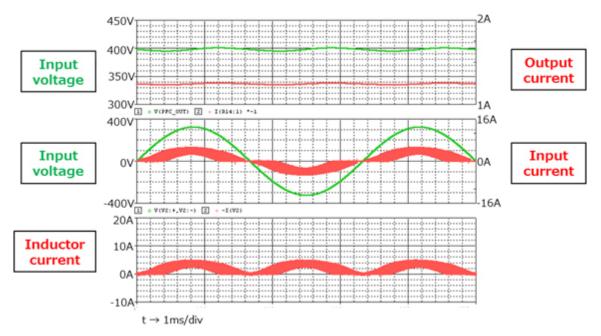

Figure 3.2 and Figure 3.3 show the waveforms of the AC input voltage and current, the PFC output voltage and current, and the inductor current. The output voltage waveform (at the top of Figure 3.2 and Figure 3.3) shows that the PFC output is regulated at 400V as required by the power supply specification. The inductor current waveform is half-sinusoidal (as shown at the bottom of Figure 3.2 and Figure 3.3), and the AC input current waveform (at the middle of Figure 3.2 and Figure 3.3) is sinusoidal, increasing the power factor.

Figure 3.2 Input voltage and current, output voltage and current, and inductor current waveforms

Figure 3.3 Input voltage and current, output voltage and current, and inductor current waveforms (enlarged view)

#### MOSFET gate voltage and MOSFET drain-source voltage and current waveforms

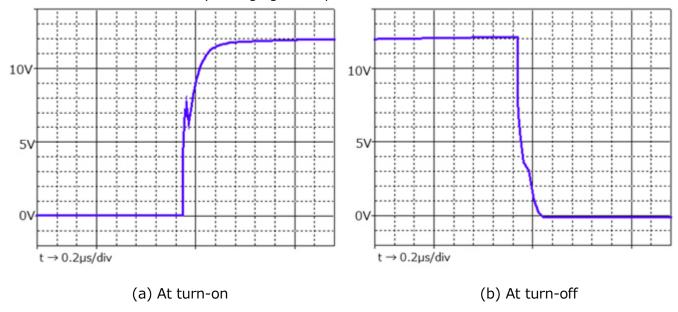

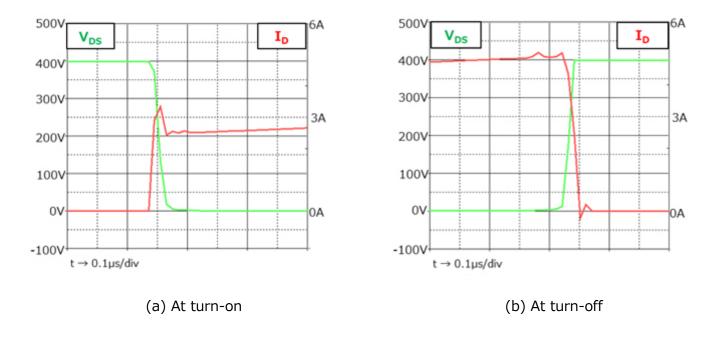

Figure 3.4 shows the waveforms of the gate voltage of the TK16N60W, which is used as a switching MOSFET in the simulation circuit. Figure 3.5 shows the waveforms of the drain-source voltage ( $V_{DS}$ ) and current ( $I_D$ ). The MOSFET is PWM-controlled to generate a half-sinusoidal inductor current. Figure 3.4 and Figure 3.5 show the MOSFET waveforms at the point in time when the inductor current has reached the peak value.

In the simulation circuit, parameters Rg\_on and Rg\_off are used to specify the parameters of an external resistor connected to the MOSFET gate. You can verify the effect of the gate resistance on the behavior of the MOSFET by changing these parameters.

Figure 3.4 MOSFET gate voltage waveforms

Figure 3.5 MOSFET drain-source voltage and current waveforms

# 4. Product overview

This section provides an overview of Toshiba's devices used as PSpice<sup>®</sup> models in the simulation circuit.

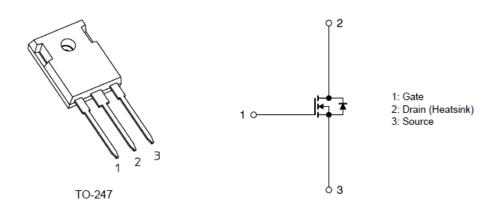

#### 4.1. TK16N60W

#### **Features**

- Low drain-source on-resistance due to a super-junction DTMOS process:  $R_{DS(ON)} = 160 m\Omega$  (Typ.)

- Optimized gate switching speed

- Easy-to-use enhanced-mode MOSFET:  $V_{th} = 2.7$  to 3.7V ( $V_{DS} = 10V$ ,  $I_D = 0.79$ mA)

#### Package and Pin assignment

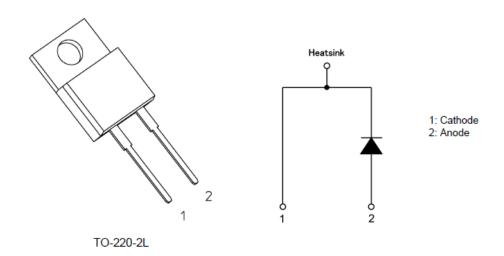

#### 4.2. TRS4E65F

#### **Features**

- High surge current capability: I<sub>FSM</sub> = 39A (Max)

- Low junction capacitance:  $C_j = 16pF$  (Typ.)

- Low leakage current:  $I_R = 0.2\mu A$  (Typ.)

## Package and Pin assignment

© 2019

# 5. Simulation circuit

You can freely change various parameters with OrCAD<sup>®</sup> Capture to verify the circuit operation according to the actual power supply specifications and evaluate how these parameters affect the circuit operation. This section describes how to set parameters and verify the circuit operation. This simulation circuit appears, when the OPJ file (.opj) inside the folder of RD031-SPICE-01 is opened.

#### **Parameter Settings**

Table 5.1 lists the adjustable parameters which is possible to you can set for the simulation circuit. Double-click a parameter name in the PARAMETERS section. Then, the Display Properties dialog box appears as shown in Figure 5.1. Change the value in the Value field.

| table 3.1 Adjustable Farameters List on the Farameters section |                  |                                            |  |  |

|----------------------------------------------------------------|------------------|--------------------------------------------|--|--|

| Parameter                                                      | Unit             | Description                                |  |  |

| Vin                                                            | V <sub>rms</sub> | AC input voltage                           |  |  |

| Fin                                                            | Hz               | AC input frequency                         |  |  |

| Vout                                                           | V                | PFC output voltage                         |  |  |

| L                                                              | Н                | Boost inductor parameter                   |  |  |

| DCR                                                            | Ω                | Inductor parasitic resistance              |  |  |

| Cin                                                            | F                | Input capacitor parameter                  |  |  |

| Cout                                                           | F                | Output capacitor parameter                 |  |  |

| Fc                                                             | Hz               | Switching frequency                        |  |  |

| Rg_on                                                          | Ω                | External gate resistor value for turn-on   |  |  |

| Rg_off                                                         | Ω                | External gate resistor value for turn-off  |  |  |

| Rdrv_on                                                        | Ω                | Gate driver internal resistor for turn-on  |  |  |

| Rdrv_off                                                       | Ω                | Gate driver internal resistor for turn-off |  |  |

| Vdrv_H                                                         | V                | Supply voltage of the gate driver          |  |  |

Table 5.1 Adjustable Parameters List on the Parameters section

Figure 5.1 Display Properties dialog box

Rev. 2

#### **Analysis Setting**

The following describes how to run a simulation on the simulation circuit.

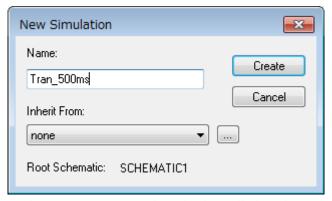

1. From the menu bar of OrCAD<sup>®</sup> Capture, select **PSpice** - **New Simulation Profile**. Then, the New Simulation dialog box shown in Figure 5.2 appears. Enter an arbitrary profile name and click **Create**.

Figure 5.2 New Simulation dialog box

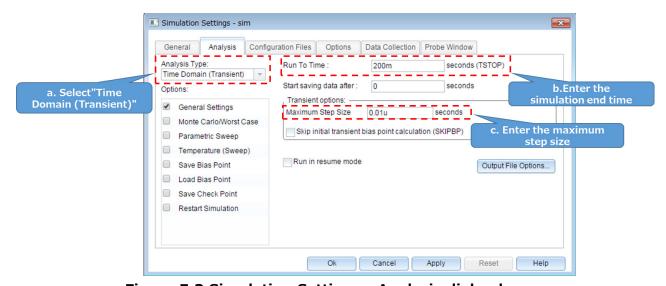

2. Then, the Simulation Settings dialog box shown in Figure 5.3 appears. In this dialog box, you can set parameters for various types of analysis. First, click the **Analysis** tab. Select **Time Domain (Transient)** from the **Analysis Type** drop-down list. Enter the simulation end time in the **Run To Time** field and the maximum step size in the **Maximum Step Size** field.

Figure 5.3 Simulation Settings - Analysis dialog box

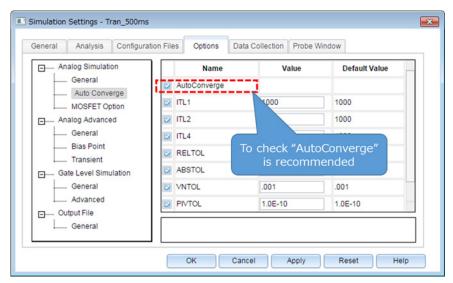

3. Click the **Options** tab to choose analysis options. For the simulation of our model, it is recommended to check **Analog Simulation** - **Auto Converge** - **AutoConverge** as shown in Figure 5.4 to enable the automatic convergence feature.

Figure 5.4 Simulation Settings - Options dialog box

- 4. Click **OK** to close the Simulation Settings dialog box.

- 5. To run a simulation, select **PSpice Run** from the menu bar of OrCAD Capture. Then, PSpice A/D starts automatically and runs a simulation.

#### **Viewing simulation results**

The following describes how to view the simulation results. You can display the waveforms of the simulation results in two ways.

## **Method 1: Selecting traces**

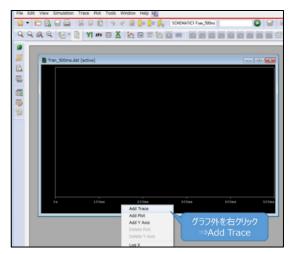

- 1. Right-click outside the graph area and select **Add Trace** as shown in Figure 5.5.

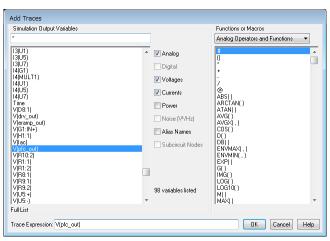

- 2. Then, the Add Traces dialog box shown in Figure 5.6 appears. Select traces to be added to a selected plot. To view a voltage waveform, select V(*trace\_name*). To view a current waveform, select I(*device\_name*).

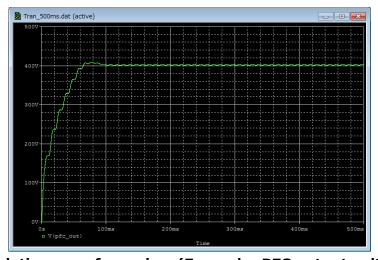

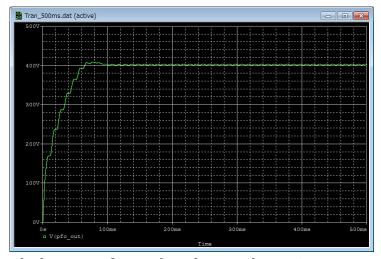

- 3. Click **OK**. Then, the selected waveform appears as shown in Figure 5.7.

Figure 5.5 Graph window Figure 5.6 Add Traces dialog box

Figure 5.7 Simulation waveform view (Example: PFC output voltage waveform)

#### Method 2 Adding markers

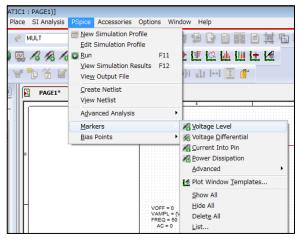

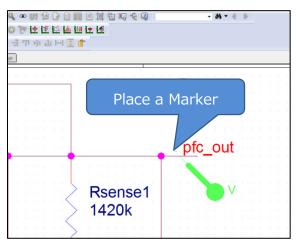

- 1. From the menu bar of OrCAD<sup>®</sup> Capture, select **PSpice Markers** and then a type of marker as shown in Figure 5.8.

- 2. Place the selected marker on the desired node in the simulation circuit as shown in Figure 5.9.

- 3. Then, its waveform appears in the graph window of PSpice® A/D as shown in Figure 5.10.

Figure 5.8 Selecting a marker type Figure 5.9 Placing a marker in the circuit

Figure 5.10 Simulation waveform view (Example: PFC output voltage waveform)

\*\*Cadence, Cadence logo, OrCAD, PSpice and OrCAD logo are trademarks or registered trademarks of Cadence Design Systems, Inc. in the U.S. and other countries.

© 2019

# **Terms of Use**

This terms of use is made between Toshiba Electronic Devices and Storage Corporation ("We") and customers who use documents and data that are consulted to design electronics applications on which our semiconductor devices are mounted ("this Reference Design"). Customers shall comply with this terms of use. Please note that it is assumed that customers agree to any and all this terms of use if customers download this Reference Design. We may, at its sole and exclusive discretion, change, alter, modify, add, and/or remove any part of this terms of use at any time without any prior notice. We may terminate this terms of use at any time and for any reason. Upon termination of this terms of use, customers shall destroy this Reference Design. In the event of any breach thereof by customers, customers shall destroy this Reference Design, and furnish us a written confirmation to prove such destruction.

#### 1. Restrictions on usage

- 1. This Reference Design is provided solely as reference data for designing electronics applications. Customers shall not use this Reference Design for any other purpose, including without limitation, verification of reliability.

- 2. This Reference Design is for customer's own use and not for sale, lease or other transfer.

- 3. Customers shall not use this Reference Design for evaluation in high or low temperature, high humidity, or high electromagnetic environments.

- 4. This Reference Design shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

#### 2. Limitations

- 1. We reserve the right to make changes to this Reference Design without notice.

- 2. This Reference Design should be treated as a reference only. We are not responsible for any incorrect or incomplete data and information.

- 3. Semiconductor devices can malfunction or fail. When designing electronics applications by referring to this Reference Design, customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of semiconductor devices could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Customers must also refer to and comply with the latest versions of all relevant our information, including without limitation, specifications, data sheets and application notes for semiconductor devices, as well as the precautions and conditions set forth in the "Semiconductor Reliability Handbook".

- 4. When designing electronics applications by referring to this Reference Design, customers must evaluate the whole system adequately. Customers are solely responsible for all aspects of their own product design or applications. WE ASSUME NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- 5. No responsibility is assumed by us for any infringement of patents or any other intellectual property rights of third parties that may result from the use of this Reference Design. No license to any intellectual property right is granted by this terms of use, whether express or implied, by estoppel or otherwise.

- 6. THIS REFERENCE DESIGN IS PROVIDED "AS IS". WE (a) ASSUME NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (b) DISCLAIM ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO THIS REFERENCE DESIGN, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

#### 3. Export Control

Customers shall not use or otherwise make available this Reference Design for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). This Reference Design may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of this Reference Design are strictly prohibited except in compliance with all applicable export laws and regulations.

#### 4. Governing Laws

This terms of use shall be governed and construed by laws of Japan.

© 2019

Toshiba Electronic Devices & Storage Corporation

16 / 16

2019-04-02