# フルブリッジ方式 DC-DC 電源 基本シミュレーション回路 リファレンスガイド

RD154-RGUIDE-01

東芝デバイス&ストレージ株式会社

# 目次

| 1.   | はじめに                | 3  |

|------|---------------------|----|

| 2.   | フルブリッジ方式 DC-DC 電源概要 | 6  |

| 2.1. | 電源仕様                | 6  |

| 2.2. | 回路構成                | 7  |

| 3.   | シミュレーション動作検証結果      | 9  |

| 4.   | 製品概要                | 16 |

| 4.1. | TPN11006PL          | 16 |

| 4.2. | TPH1R204PL          | 16 |

| 5.   | シミュレーション回路使用方法      | 17 |

# 1. はじめに

情報通信機器や家電をはじめ、ほとんどの電気機器は直流 (DC) 電圧で動作しています。そのため、交流 (AC) 電圧で供給される商用電力で直接動作させることができず、AC 電圧から DC 電圧に変換し供給する必要があります。

AC 電圧から DC 電圧への変換は AC-DC 電源で行われますが、機器内の各負荷の電源仕様によっては、AC-DC 電源より供給される DC 電圧をその仕様に応じた DC 電圧にさらに変換する必要があります。

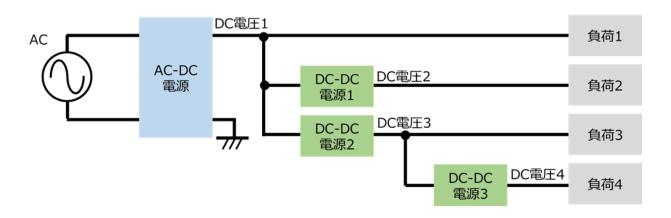

図 1.1 に、機器における電源ラインの構成例を示します。負荷に応じて複数の電源ラインがあり、AC-DC 電源より供給される出力電圧にそのまま負荷を接続する場合や、その出力電圧を更に DC-DC 電源を介して異なる DC 電圧へ変換して接続する場合があります。 このように DC 電圧を異なる DC 電圧へ変換を行うものが DC-DC 電源です。

図 1.1 機器における電源ライン構成例

DC電圧からDC電圧へ変換する方式には、大きく分けてシリーズレギュレート方式とスイッチングレギュレート方式 (以下、シリーズ方式とスイッチング方式) の2種類があります。本ドキュメントは、DC-DC電源で主流であるスイッチング方式を取り扱います。スイッチング方式は、スイッチング素子のオン/オフを調整し所望の電圧を生成するもので、シリーズ方式に比べ制御回路が複雑になりますが、一般にシリーズ方式よりも損失を少なくできます。

スイッチング方式には、トランスを介し入力側と出力側が絶縁された絶縁型DC-DC電源と、入力側と出力側が絶縁されていない非絶縁型DC-DC電源があります。本ドキュメントは絶縁型DC-DC電源を取り扱います。

絶縁型DC-DC電源は入力DC電圧をスイッチング素子で数十〜数百 kHz程度の周波数でスイッチングさせ、トランスを介し二次側に電力を伝達した後に整流、平滑してDC電圧を出力します。最終段のDC電圧の制御は、スイッチング素子のオン/オフの期間の調整で行います。

Rev.1

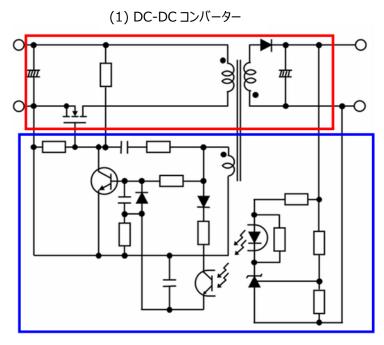

図 1.2 に絶縁型スイッチング方式 DC-DC 電源の回路ブロック例を示します。図に示すように (1) DC-DC コンバーター、 (2) 帰還回路の 2 ブロックで構成されています。各ブロックの機能を以下に示します。

(2) 帰還回路

図 1.2 絶縁型スイッチング方式 DC-DC 電源の回路ブロック例

- (1) DC-DC コンバーター入力された DC 電圧を、任意の DC 電圧に変換します。

- (2) 帰還回路 出力電圧が所望の値になるように、スイッチング素子のオン/オフを制御します。

トランスを使用した絶縁型スイッチング方式 DC-DC コンバーターには、さまざまな回路方式(トポロジー)が存在します。 表 1.1 に DC-DC コンバーターの代表的なトポロジーとその特徴を示します。

| DC-DC コンバーター部分の回路方式   |  | 電力レベル      | 長所                                   | 短所                   |

|-----------------------|--|------------|--------------------------------------|----------------------|

| フライバック                |  | < 200 W    | ・部品点数最小                              | ・大電力での効率低下・トランスが大きい  |

| フォワード                 |  | 50 W∼500 W | ・フライバックより高効率                         | ・トランスのリセット回路が必要      |

| アクティブクランプ<br>フォワード    |  | 50 W∼500 W | ・ソフトスイッチングにより<br>フォワードより高効率          | ・部品点数が多い・制御が難しい      |

| ハーフブリッジ               |  | 100 W∼1 kW | <ul><li>・高効率</li><li>・低ノイズ</li></ul> | ・専用設計のトランスが必要・制御が難しい |

| 共振ハーフブリッジ<br>(LLC 共振) |  | 100 W∼1 kW | ・ハーフブリッジより<br>高効率、低ノイズ               | ・専用設計のトランスが必要・制御が難しい |

| フルブリッジ                |  | > 200 W    | ・高効率<br>・大容量化が可能                     | ・部品点数が多い・制御が難しい      |

表 1.1 DC-DC コンバーターの代表的なトポロジーとその特徴

フルブリッジ方式 DC-DC コンバーターの動画はこちら →

Click Here

本ドキュメントで扱うフルブリッジ方式は、一次側に配置された 4 個のスイッチング素子をたすきがけに切り替えることにより、トランスの 1 次側に電源電圧がそのまま印加されることから大電力化が可能であるという長所を持ち、高効率、高電力密度が要求される電源に広く採用されています。スイッチング方式 DC-DC 電源におけるフルブリッジ方式 DC-DC コンバーター回路動作を理解いただくために、基本シミュレーション回路 (RD154-SPICE-01) を当社 Web 上で提供します。

本ドキュメントでは、この基本シミュレーション回路の概要、使用方法などを解説していきます。シミュレーション回路を動作させるためには、Cadence 社の OrCAD<sup>®</sup> Capture および PSpice<sup>®</sup> A/D ツールが必要となります。また、本シミュレーション 回路およびドキュメントは OrCAD<sup>®</sup> 17.2 に基づき作成されています。

# 2. フルブリッジ方式 DC-DC 電源概要

基本シミュレーション回路(RD154-SPICE-01)は、200 W 出力のフルブリッジ方式 DC-DC 電源です。

# 2.1. 電源仕様

本ドキュメントで説明するフルブリッジ方式 DC-DC 電源の仕様は以下の通りです。

・入力電圧 (V<sub>in</sub>): 24 V

·出力電圧 (Vout): 5 V

·出力電流 (Iout): 0~40 A

・二次側 MOSFET の動作周波数: 65 kHz (一次側動作周波数の2倍)

·巻線比: n1:n2:n3=5:2:2

・二次側許容リップル電流幅 (ΔI<sub>ripple</sub>): 20 %

## 2.2. 回路構成

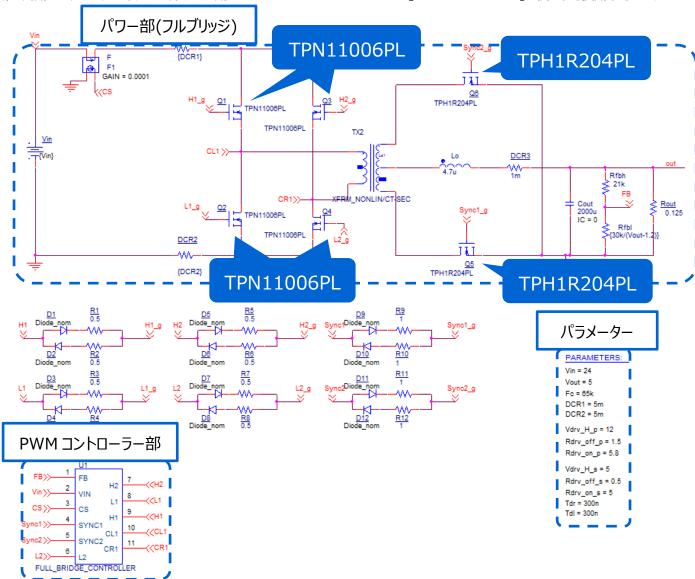

図 2.1 に OrCAD<sup>®</sup>上で動作するシミュレーション回路を示します。これは、フルブリッジ方式の DC-DC 電源であり、主にパワー部(フルブリッジ)、PWM コントローラー部で構成されています。パワー部のトランス二次側は MOSFET を用いた同期整流方式の回路となっています。PWM コントローラー部は本基本回路を実現するために用意した MOSFET ゲートドライバー内蔵の汎用コントローラーです。スイッチング用 MOSFET は、「TPN11006PL」と「TPH1R204PL」を例として使用しています。

図 2.1 200 W フルブリッジ方式 (DC-DC コンバーター部) 電源シミュレーション回路

# 一次側 MOSFET の選定

一次側 MOSFET (TPN11006PL: V<sub>DSS</sub>=60 V, I<sub>D</sub>=26 A) は以下の観点で選定しています。

(1) 素子耐圧

定常時の素子印加電圧は入力電圧 (=24 V) であり、スイッチング時のサージ電圧などを考慮し、耐圧 60 V 以上の素子を選定します。

(2) 電流定格

入力電流が最大となるのは、最大出力電力時です。最大出力電力=200W 時の変換効率を 90%とすると最大平均入力電流は 9.3 A となるので、電流定格が 19 A 以上の素子を選定します。

ここでは、当社製品ラインアップより電流 26 A の素子を選定しました。

#### 二次側 MOSFET の選定

二次側 MOSFET(TPH1R204PL: V<sub>DSS</sub>=40 V, I<sub>D</sub>=150 A)は以下の観点で選定しています。

(1) 素子耐圧

定常時の二次側巻線の中点と両端間の電圧は、巻線比が 5:2 なので入力電圧の 2/5 の 9.6 V となり、二次側の各 MOSFET にはその 2 倍の 19.2 V が印加されます。トランス電流切り替わり時にサージ電圧が発生するため耐圧 40 V 以上の素子を選定します。

(2) 電流定格

出力電流が最大となるのは、最大出力電力時です。最大出力電力=200 W 時の最大出力電流 40 A を二次側の 2 つの電流経路の MOSFET で分担するので、1 経路あたり 20 A の電流が流れるため、電流定格 40 A 以上の素子が必要です。また、導通損失抑制を重視して、出来るだけオン抵抗が低い素子を選定します。

# 出力インダクターの選定

二次側の出力インダクターの選定方法について説明します。本シミュレーション回路における出力インダクターのインダクタンス値は、電源仕様である下記項目を用いて計算により求めることができます。

・入力電圧: V<sub>in</sub> (V)

トランス巻線比: n<sub>2</sub>/n<sub>1</sub>=n<sub>3</sub>/n<sub>1</sub>

・ 出力電圧: Vout (V)

・スイッチング周波数: Fc (Hz)

・最大出力電流: Iout max (A)

・許容リップル電流幅: △I<sub>ripple</sub> (%)

出力インダクターのインダクタンス値(L。)は、以下の式で算出します。

$$L_{o} = \frac{\left(\frac{n_{2}}{n_{1}} \times V_{in} - V_{out}\right) \times V_{out}}{\frac{n_{2}}{n_{1}} \times V_{in} \times F_{c} \times I_{out\_max} \times \Delta I_{ripple} \times 0.01}$$

ここで、本モデルの電源仕様より、入力電圧( $V_{in}$ )=24 V、トランス巻線比( $n_2/n_1$ )=2/5、出力電圧( $V_{out}$ )=5 V、スイッチング周波数( $F_c$ )=65 kHz、最大出力電流( $I_{out\_max}$ )=40 A、許容リップル電流幅( $\Delta I_{ripple}$ )=20 %とすると、上記式より出力インダクターのインダクタンス値(Lo)は 4.61  $\mu H$  と算出されるため、設定値として 4.7  $\mu H$  を選定します。 実際の設計においては、インダクターは直流重畳特性によりインダクタンス値が変動します。 直流重畳特性によりインダクタンス値が低下した状態で、上記計算値の値を確保できる部品を選定してください。

# 3. シミュレーション動作検証結果

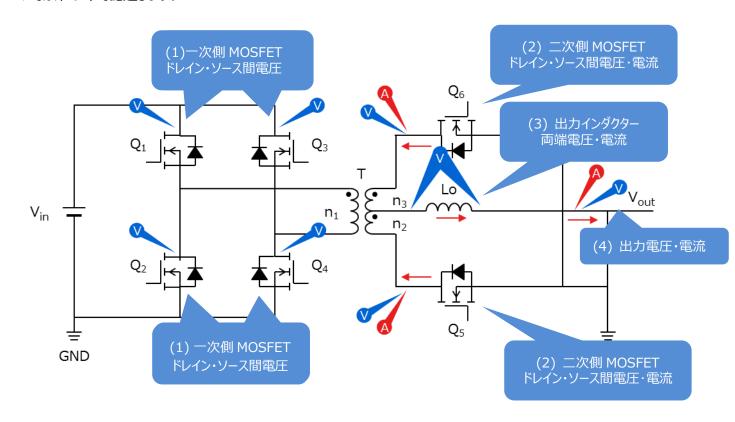

ここではシミュレーション回路における各部の動作シミュレーション波形を図 3.1 ((1) ~ (4)) のそれぞれのポイントで示します。

- (1) フルブリッジ方式基本動作(「一次側 MOSFET ドレイン・ソース間電圧」)

- (2) 二次側同期整流動作(「二次側 MOSFET ドレイン・ソース間電圧・電流」)

- (3) 出力インダクター両端電圧・電流

- (4) 電源としての「出力電圧・電流」

実際に回路モデルを使用する際には、図 3.1 以外の部分についても波形を表示させることが可能です。 波形の表示方法 については第5章で記述します。

図 3.1 シミュレーション波形測定ポイント一覧

# (1) フルブリッジ方式基本動作

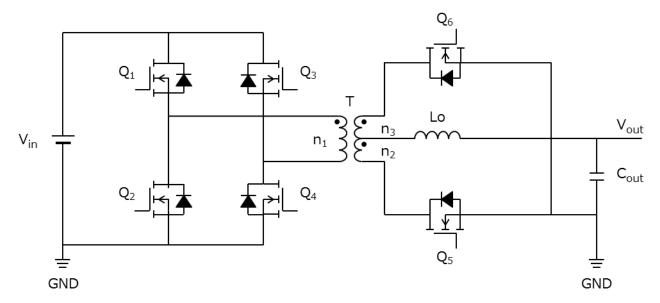

フルブリッジ回路を示した図 3.2 を使用して、フルブリッジ方式の基本動作を説明します。

Q<sub>1</sub>~Q<sub>4</sub>: 一次側 MOSFET

Q<sub>5</sub>, Q<sub>6</sub>: 二次側 MOSFET

Lo: 出力インダクター

図 3.2 フルブリッジ回路

フルブリッジ方式では、 $Q_1$  と  $Q_4$ 、 $Q_3$  と  $Q_2$  がそれぞれ対となり交互にオン/オフし、PWM(Pulse Width Modulation:パルス幅変調)制御を用いて出力電圧を制御します。

出力電圧 Vout は

$$V_{out} = 2 \times \frac{n_2}{n_1} \times V_{in} \times \frac{T_{on}}{T}$$

T: 一次側の周期

Ton: オン時間

で求まります。

## A. Q<sub>1</sub>,Q<sub>4</sub>オン、Q<sub>3</sub>,Q<sub>2</sub>オフ

一次側から二次側に電力が伝達する期間です。このときの一次側巻線電圧は入力電圧  $(V_{in})$  となります。二次側巻線には、 $n_2$ の極性記号側をプラスとして巻線比に応じた電圧

$$\frac{n_2}{n_1} \times V_{in}$$

が印加され、Q5を経由してLoには、

$$\Delta i_{Lo(Q1,Q4\_on)} = \frac{1}{L_O} \left( \frac{n_2}{n_1} \times V_{in} - V_{out} \right) \times T_{on}$$

で決定される電流が直線的に増加して流れ、C<sub>out</sub>を充電し出力電流 I<sub>out</sub>を供給します。このとき、L<sub>o</sub> には磁気エネルギーが蓄えられます。

#### B. $Q_1, Q_4 \dagger J$ , $Q_3, Q_2 \dagger J$

$Q_1 \sim Q_4$  のすべての MOSFET がオフとなり、 $L_0$  に蓄えられたエネルギーが  $Q_5$  と  $Q_6$  を経由して環流します。このとき、 $L_0$  には

$$\Delta i_{Lo(all_{off})} = \frac{-V_{out}}{L_o} \times \left(\frac{T}{2} - T_{on}\right)$$

の電流が直線的に減少して流れます。

#### C. Q<sub>1</sub>,Q<sub>4</sub>オフ、Q<sub>3</sub>,Q<sub>2</sub>オン

一次側から二次側に電力が伝達する期間です。この期間の一次側巻線電圧は - V<sub>in</sub>となり、二次側巻線には、n<sub>3</sub>の極性記号側をマイナスとして巻線比に応じた電圧

$$\frac{n_3}{n_1} \times V_{in}$$

が印加され、aと同様にQ6を経由してLoに

$$\Delta i_{Lo(Q3,Q2\_on)} = \frac{1}{L_o} \times \left(\frac{n_3}{n_1} \times V_{in} - V_{out}\right) \times T_{on}$$

の電流が流れます。

## D. Q<sub>1</sub>,Q<sub>4</sub>オフ、Q<sub>3</sub>,Q<sub>2</sub>オフ

bと同様にLoに蓄えられたエネルギーがQ5とQ6を経由して、

$$\Delta i_{Lo(all_{off})} = \frac{-V_{out}}{L_o} \times \left(\frac{T}{2} - T_{on}\right)$$

の電流が流れます。

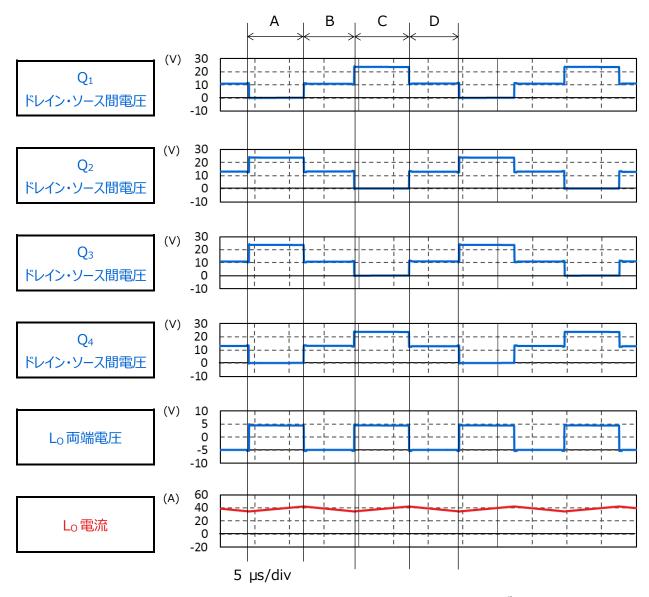

図 3.3 に一次側 MOSFET ドレイン・ソース間電圧、出力インダクター電圧・電流波形を示します。

図 3.3 一次側 MOSFET ドレイン・ソース間電圧、出力インダクター電圧・電流

# (2) 二次側同期整流動作

本シミュレーション回路は、二次側整流素子にダイオードではなく MOSFET を使用した同期整流回路を採用しています。 一般に MOSFET のオン抵抗による導通損失は、ダイオードの順方向電圧による導通損失より小さいため、同期整流回路は 導通損失を低減することが可能です。出力電流が大きいほど、同期整流回路の損失低減効果は大きく、高効率・大容量が 要求される用途ではよく採用されています。

各期間における二次側 MOSFET の動作は以下のとおりです。

- a.Q5オフ、Q6オン

- 二次側巻線 n2の極性記号側をプラスとして巻線比に応じた電圧

$$\frac{n_2}{n_1} \times V_{in}$$

が印加され、Q5を経由してLOに電流が流れます。

- b.  $Q_5$  オン、 $Q_6$  オン  $L_0$  に蓄えられた電力が  $Q_5$  と  $Q_6$  を経由して環流されます。

- c. Q5オン、Q6オフ 二次側巻線 n3の極性記号側をマイナスとして巻線比に応じた電圧

$$\frac{n_3}{n_1} \times V_{in}$$

が印加され、Q6を経由してLOに電流が流れます。

d. Q<sub>5</sub>オン、Q<sub>6</sub>オン

$L_O$ に蓄えられた電力が  $Q_5$ と  $Q_6$ を経由して環流されます。

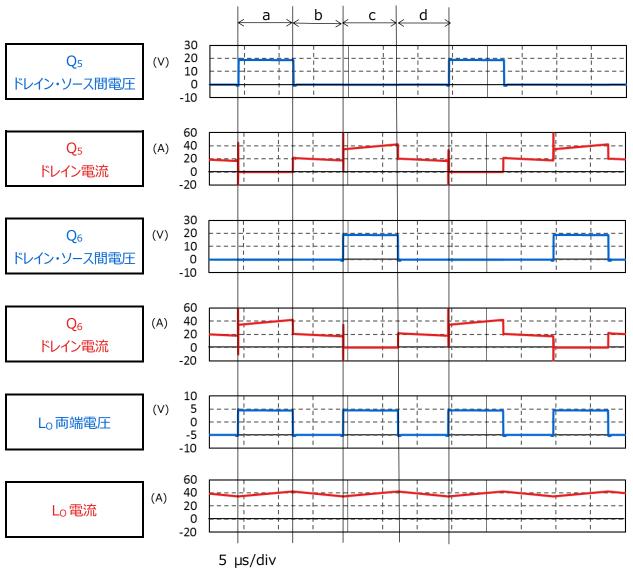

## (3) 出力インダクター両端電圧・電流

図 3.4 に、(2) で解説した二次側同期整流動作(二次側 MOSFET ドレイン・ソース間電圧・電流)と合わせて、出力インダクター電圧・電流波形を示します。

\*:ドレイン電流は、MOSFETからトランス二次側巻線に流れる向きを正としています。

図 3.4 二次側 MOSFET ドレイン・ソース間電圧・電流、出力インダクター電圧・電流波形

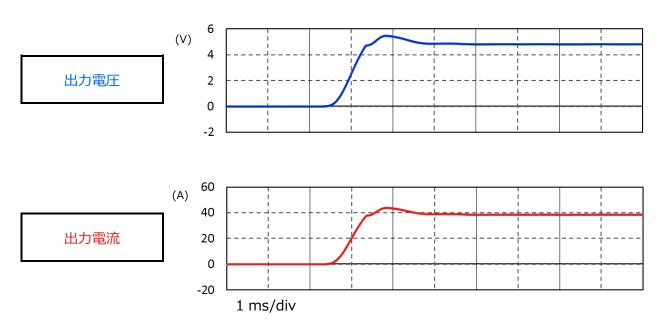

# (4) 電源としての「出力電圧・電流」

図 3.5 に本電源回路の出力電圧・電流波形を示します。設定電圧・電流で安定していることが分かります。

図 3.5 出力電圧・電流波形

Rev.1

# 4. 製品概要

本回路に PSpice®モデルを組み込んで検証している当社製品の概要を紹介します。

#### 4.1. TPN11006PL

#### 特長

- V<sub>DSS</sub>=60 V, I<sub>D</sub>=26 A

- 小さいゲート入力電荷量: Q<sub>SW</sub>=5.8 nC (標準)

- 小さい出力電荷量: Qoss=14.4 nC (標準)

- 低いオン抵抗 : R<sub>DS(ON)</sub>=8.8 mΩ(標準) (V<sub>GS</sub>=10 V)

- 低い漏れ電流: I<sub>DSS</sub>=10 µA(最大)(V<sub>DS</sub>=60 V)

- 取り扱いが簡単なエンハンスメントタイプ: V<sub>th</sub>=1.5~2.5 V(V<sub>DS</sub>=10 V、I<sub>D</sub>=0.2 mA)

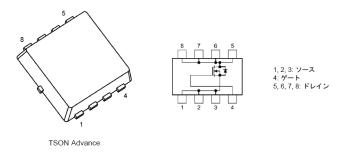

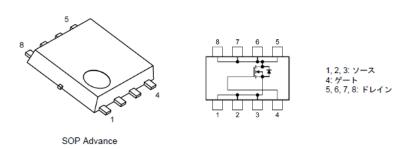

#### 外観と端子配置

幅 3.3 × 長さ 3.3 × 高さ 0.85 (mm)

# 4.2. TPH1R204PL

#### 特長

- V<sub>DSS</sub>=40 V, I<sub>D</sub>=150 A

- 小さいゲート入力電荷量: Q<sub>SW</sub>=17 nC (標準)

- 小さい出力電荷量: Qoss=56 nC(標準)

- 低いオン抵抗: R<sub>DS(ON)</sub>=1.0 mΩ(標準) (V<sub>GS</sub>=10 V)

- 低い漏れ電流: I<sub>DSS</sub>=10 µA (最大) (V<sub>DS</sub>=40 V)

- 取り扱いが簡単なエンハンスメントタイプ: V<sub>th</sub>=1.4~2.4 V (V<sub>DS</sub>=10 V, I<sub>D</sub>=0.5 mA)

#### 外観と端子配置

幅 5.0 × 長さ 6.0 × 高さ 0.95 (mm)

# 5. シミュレーション回路使用方法

本シミュレーション回路では、実際の仕様に沿った動作や、回路定数に応じた変化を検証するために、OrCAD® Capture 上で各種パラメーターを自由に変更し、動作解析をすることが可能です。以下では実際にシミュレーションを行う際のパラメーター設定方法、動作解析方法について説明します。

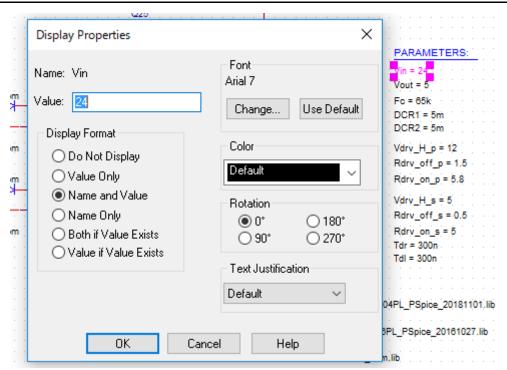

#### パラメーター設定の方法

シミュレーション回路で設定可能なパラメーターの一覧を表 5.1 に示します。パラメーター設定部の変数をダブルクリックすると、図 5.1 に示す「Display Properties」ウインドウが表示されますので、その中の「Value」値を変更してください。

単位 変数名 説明 Vin ٧ 入力電圧 出力電圧 Vout V Fc Hz 二次側 MOSFET のスイッチング周波数 一次側の電源プレーン寄生抵抗値 DCR1 Ω Ω 一次側の GND プレーン寄生抵抗値 DCR2 一次側ゲートドライバーの電源電圧 Vdrv\_H\_p ٧ 一次側 MOSFET Ω Rdrv off p ゲートドライバー内部抵抗 (オフ側) 一次側 MOSFET Rdrv\_on\_p Ω ゲートドライバー内部抵抗 (オン側) ٧ 二次側ゲートドライバーの電源電圧 Vdrv\_H\_s 二次側 MOSFET Rdrv\_off\_s Ω ゲートドライバー内部抵抗 (オフ側) 二次側 MOSFET Rdrv\_on\_s Ω ゲートドライバー内部抵抗 (オン側) Tdr Q3 と Q4 のレグのデッドタイム sec Tdl Q1 と Q2 のレグのデッドタイム sec

表 5.1 パラメーター設定部で設定可能な変数一覧

Rev.1

図 5.1 パラメーター設定画面

#### 解析設定の方法

本シミュレーション回路のシミュレーション実行手順を下記に説明します。

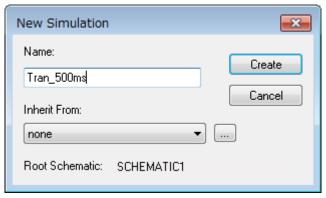

(1) OrCAD<sup>®</sup> Capture メニューバー上の「PSpice」-「New Simulation Profile」をクリックすると、図 5.2 に示す「New Simulation」ウインドウが表示されます。任意のプロファイル名を指定し、「Create」をクリックしてください。

図 5.2 「New Simulation」画面

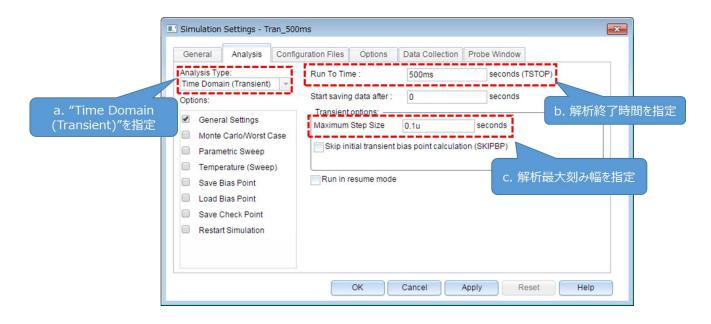

(2) 1.の手順後、図 5.3 に示す「Simulation Settings」ウインドウが表示され、各種解析設定が可能になります。まずは「Analysis」タブで解析方法の設定を行います。「Analysis Type」は「Time Domain(Transient)」を指定してください。「Run To Time」で解析終了時間を指定し、「Maximum Step Size」で解析における最大刻み幅を指定してください。

図 5.3 「Simulation Settings」-「Analysis」画面

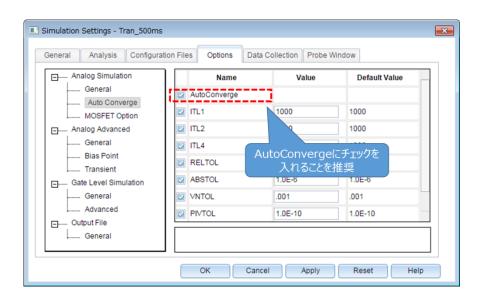

(3) 「Options」タブで解析オプションの設定を行います。本モデルでのシミュレーションにおいては、図 5.4 に示すように「Analog Simulation」-「Auto Converge」-「AutoConverge」にチェックを入れ、自動収束機能を有効にすることを推奨します。

図 5.4 「Simulation Settings」-「Options」画面

- (4) 上記設定が完了したら、「OK」をクリックし、「Simulation Settings」ウインドウを閉じてください。

- (5) OrCAD<sup>®</sup> Capture メニューバーの「PSpice」-「Run」でシミュレーションを実行します。PSpice<sup>®</sup> A/D が自動で起動し、シミュレーションが実行されます。

© 2020

## 結果確認方法

シミュレーション完了後の結果確認方法について説明します。PSpice® A/D 画面上に結果波形を表示する方法として、2 通りの方法があります。下記に各方法の手順について説明します。

# 方法1. ネット名を指定した結果表示

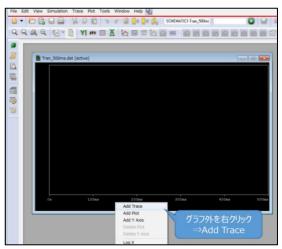

- (1) グラフウインドウのグラフ枠外を右クリック後、「Add Trace」を選択してください。(図 5.5)

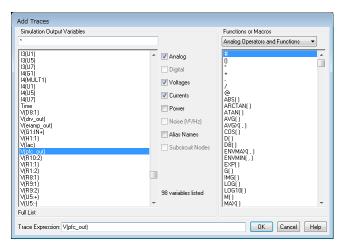

- (2) 「Add Traces」画面から表示する波形を選択します。電圧波形の場合には V(ネット名)、電流波形の場合には I(素子名)を選択してください。(図 5.6)

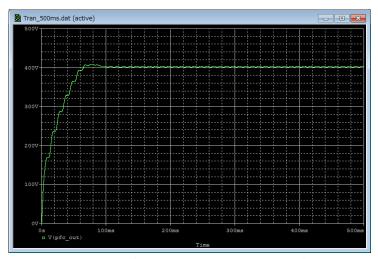

- (3) 選択後、「OK」をクリックすることで結果波形が表示されます。(図 5.7)

図 5.5 グラフウインドウ

図 5.6 「Add Traces」画面

図 5.7 結果波形表示 (例:出力電圧波形)

## 方法 2. Marker 機能を使用した結果表示

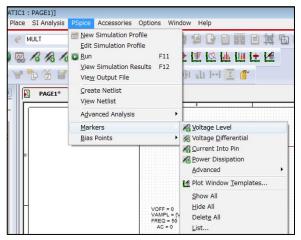

- (1) OrCAD® Capture メニューバーの「PSpice」-「Markers」から、表示させる波形に応じて Marker 種類を選択します。(図 5.8)

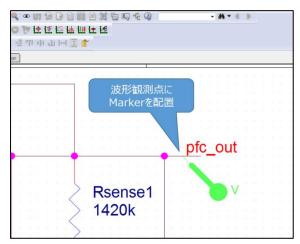

- (2) シミュレーション回路上の波形測定ポイントに Marker を配置します。(図 5.9)

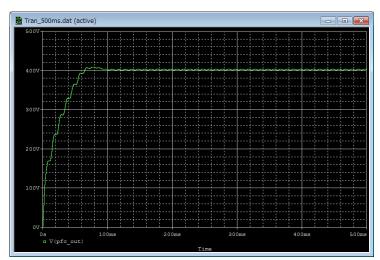

- (3)  $PSpice^{®}$  A/D のグラフウインドウに結果波形が表示されます。 (図 5.10)

図 5.8 Marker 種類選択画面

図 5.9 回路上への Marker 配置

図 5.10 結果波形表示(例:出力電圧波形)

※Cadence、Cadence ロゴ、OrCAD、PSpice および OrCAD ロゴは Cadence Design Systems, Inc.の米国 またはその他の国における商標または登録商標です。

© 2020

# ご利用規約

本規約は、お客様と東芝デバイス&ストレージ株式会社(以下「当社」といいます)との間で、当社半導体製品を搭載した機器を設計する際に参考となるドキュメント及びデータ(以下「本リファレンスデザイン」といいます)の使用に関する条件を定めるものです。お客様は本規約を遵守しなければなりません。本リファレンスデザインをダウンロードすることをもって、お客様は本規約に同意したものとみなされます。なお、本規約は変更される場合があります。当社は、理由の如何を問わずいつでも本規約を解除することができます。本規約が解除された場合は、お客様は、本リファレンスデザインを破棄しなければなりません。またお客様が本規約に違反した場合は、お客様は、本リファレンスデザインを破棄したことを証する書面を当社に提出しなければなりません。

#### 第1条 禁止事項

お客様の禁止事項は、以下の通りです。

- 1. 本リファレンスデザインは、機器設計の参考データとして使用されることを意図しています。信頼性検証など、それ以外の目的には使用しないでください。

- 2. 本リファレンスデザインを販売、譲渡、貸与等しないでください。

- 3. 本リファレンスデザインは、高低温・多湿・強電磁界などの対環境評価には使用できません。

- 4. 本リファレンスデザインを、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用しないでください。

#### 第2条 保証制限等

- 1. 本リファレンスデザインは、技術の進歩などにより予告なしに変更されることがあります。

- 2. 本リファレンスデザインは参考用のデータです。当社は、データおよび情報の正確性、完全性に関して一切の保証をいたしません。

- 3. 半導体素子は誤作動したり故障したりすることがあります。本リファレンスデザインを参考に機器設計を行う場合は、誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウェア・ソフトウェア・システムに必要な安全設計を行うことをお願いします。また、使用されている半導体素子に関する最新の情報(半導体信頼性ハンドブック、仕様書、データシート、アプリケーションノートなど)をご確認の上、これに従ってください。

- 4. 本リファレンスデザインを参考に機器設計を行う場合は、システム全体で十分に評価し、お客様の責任において適用可否を判断して下さい。当社は、適用可否に対する責任は負いません。

- 5. 本リファレンスデザインは、その使用に際して当社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 6. 当社は、本リファレンスデザインに関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をせず、また当社は、本リファレンスデザインに関する一切の損害(間接損害、結果的損害、特別損害、付随的損害、逸失利益、機会損失、休業損、データ喪失等を含むがこれに限らない。)につき一切の責任を負いません。

#### 第3条 輸出管理

お客様は本リファレンスデザインを、大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用してはなりません。また、お客様は「外国為替及び外国貿易法」、「米国輸出管理規則」等、適用ある輸出関連法令を遵守しなければなりません。

#### 第4条 準拠法

本規約の準拠法は日本法とします。

© 2020