# <u>TPD7106F</u> アプリケーションノート

# 概要

TPD7106F は、12 V 電源対応の N チャネル MOSFET 用ハイサイドゲートドライバーIC です。使用する MOSFET は内部のチャージポンプ回路(コンデンサー外付け)より駆動され、使用条件に最適なMOSFET を選択することにより、小電流から大電流までシステムに最適な仕様のハイサイドスイッチを構成することが可能です。 本 IC は、チャージポンプ電圧低下検出の機能と診断出力機能に加えて、電源逆接続保護機能を内蔵しており、システムの安全性向上に貢献します。 また、急速オフ指令を受け取り、外付け MOSFET をオフすることが可能です。

これは参考資料です。本資料での最終機器設計はしないでください。

# 目次

| 概要                                                          | 1  |

|-------------------------------------------------------------|----|

| 目次                                                          | 2  |

| 1. 製品概要                                                     | 5  |

| 1.1. TPD7106F の入出力端子                                        | 6  |

| 1.2. 製品比較 (TPD7104AF, TPD7106F, TPD7107F)                   | 6  |

| 2. 製品の機能                                                    | 7  |

| 2.1. 外付け MOSFET の制御                                         | 7  |

| 2.2. 外付け MOSFET を急速オフする機能                                   | 8  |

| 2.3. チャージポンプ回路                                              | 9  |

| 2.4. チャージポンプ電圧の低電圧検出機能                                      | 9  |

| 2.5. 電源逆接続保護機能                                              | 11 |

| 3. 電気的特性測定回路図                                               | 12 |

| 3.1. スイッチングタイム測定回路 1 (t <sub>ON</sub> , t <sub>OFF1</sub> ) | 12 |

| 3.2. スイッチングタイム測定回路 2 (t <sub>OFF2</sub> )                   | 13 |

| 3.3. 電源逆接続時出力電流測定回路                                         | 13 |

| 4. 端子等価回路図                                                  | 14 |

| 5. 応用回路例 (MOSFET 2 個並列の場合)                                  | 15 |

| 6. 用語の説明                                                    | 16 |

| 6.1. 絶対最大定格                                                 | 16 |

| 6.2. 電気的特性                                                  | 17 |

| 7. 評価ボード                                                    | 19 |

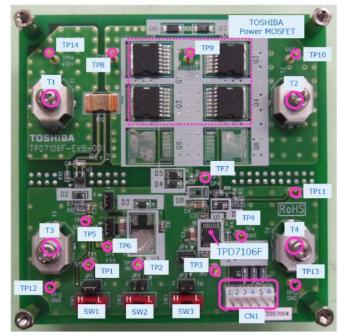

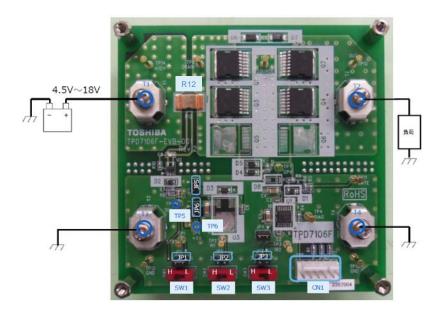

| 7.1. 評価ボード外観                                                | 19 |

| 7.2. 評価ボードの使用方法                                             | 20 |

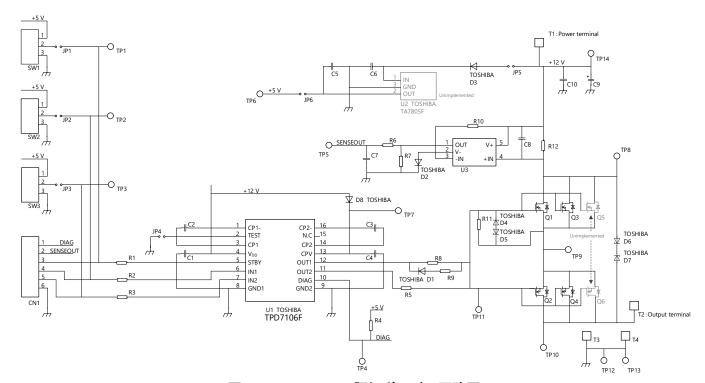

| 7.3. 評価ボード回路図                                               | 20 |

| 7.4. 部品表                                                    | 21 |

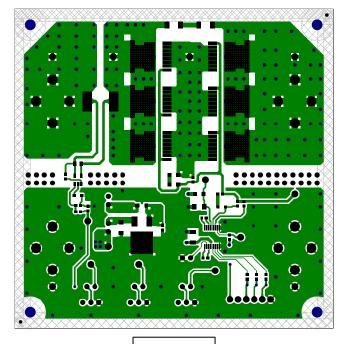

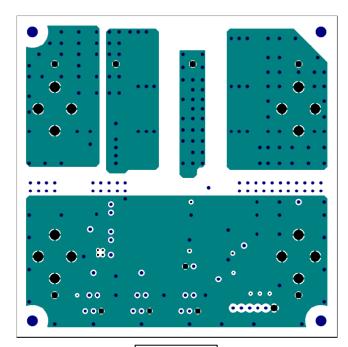

| 7.5. 評価ボード基板レイアウト                                           | 22 |

| 記載内容の留意点                                                    | 23 |

| 使用上のご注意およびお願い事項                                             | 23 |

| 使用上の注意事項                                                    | 23 |

| 製品取り扱い上のお願い                                                 | 24 |

# 図目次

| 义 | 1.1 | TPD7106F と駆動する MOSFET 群                     | 5  |

|---|-----|---------------------------------------------|----|

| 义 | 2.1 | 外付け MOSFET の制御                              | 7  |

| 义 | 2.2 | 入出力波形                                       | 7  |

| 义 | 2.3 | 急速オフ制御波形                                    | 8  |

| 义 | 2.4 | チャージポンプ電圧(V <sub>CPV</sub> )のスタンバイ解除時の立ち上がり | 9  |

| 义 | 2.5 | チャージポンプ電圧の低電圧検出機能                           | 9  |

| 义 | 2.6 | 低電圧検出波形                                     | 10 |

| 义 | 2.7 | 電源逆接続時の振る舞い                                 | 11 |

| 义 | 2.8 | 電源逆接続時の振る舞い (simulation)                    | 11 |

| 义 | 3.1 | スイッチングタイム測定回路 1                             | 12 |

| 义 | 3.2 | スイッチングタイムと負荷容量 (simulation)                 | 12 |

| 义 | 3.3 | スイッチングタイム測定回路 2                             | 13 |

| 义 | 3.4 | 電源逆接時出力電流測定回路                               | 13 |

| 义 | 4.1 | STBY 端子等価回路                                 | 14 |

| 义 | 4.2 | IN1,IN2 端子等価回路                              | 14 |

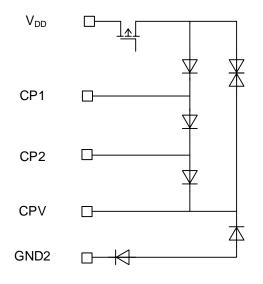

| 义 | 4.3 | CP1, CP2, CPV 端子等価回路                        | 14 |

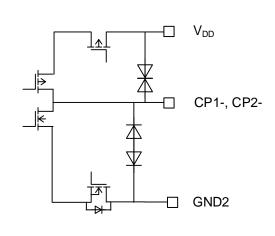

| 义 | 4.4 | CP1-, CP2- 端子等価回路                           | 14 |

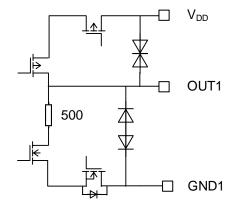

| 义 | 4.5 | OUT1 端子等価回路                                 | 14 |

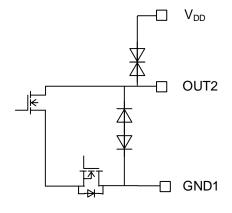

| 义 | 4.6 | OUT2 端子等価回路                                 | 14 |

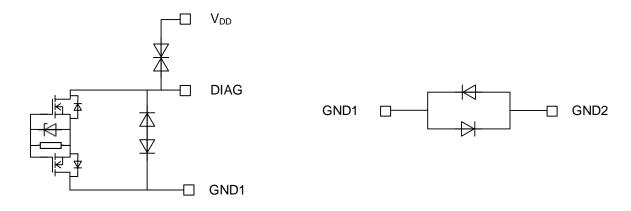

| 义 | 4.7 | DIAG 端子等価回路                                 | 15 |

| 义 | 4.8 | GND1, GND2 等価回路                             | 15 |

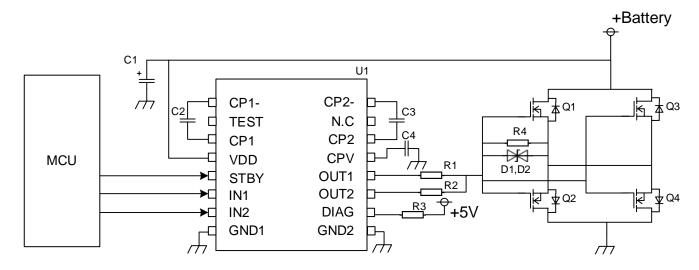

| 义 | 5.1 | 応用回路例                                       | 15 |

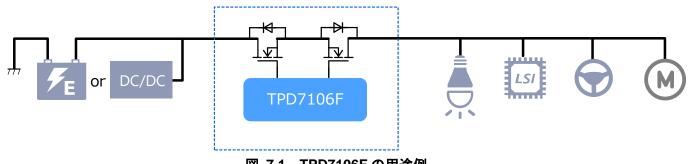

| 义 | 7.1 | TPD7106F の用途例                               | 19 |

| 义 | 7.2 | TPD7106F 評価ボードの外観と端子説明                      | 19 |

| 义 | 7.3 | TPD7106F 評価ボードの使用方法                         | 20 |

| 义 | 7.4 | TPD7106F 評価ボードの回路図                          | 20 |

| 図 | 75  | TPD7106F 評価ボードの其板レイアウト                      | 22 |

# 表目次

| 1.1 | 端子説明                            | . 6                                                                                                                    |

|-----|---------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 1.2 | 製品比較表                           | . 6                                                                                                                    |

|     |                                 |                                                                                                                        |

| 6.1 | 絶対最大定格                          | 16                                                                                                                     |

| 6.2 | 電気的特性 1                         | 17                                                                                                                     |

| 6.3 | 電気的特性 2                         | 18                                                                                                                     |

| 7.1 | 部品表                             | 21                                                                                                                     |

|     | 1.2<br>2.1<br>6.1<br>6.2<br>6.3 | 1.1 端子説明         1.2 製品比較表         2.1 真理値表         6.1 絶対最大定格         6.2 電気的特性 1         6.3 電気的特性 2         7.1 部品表 |

# 1. 製品概要

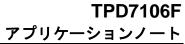

バッテリーなどの電源から負荷への電力供給ラインを遮断・接続するスイッチとしては、従来、メカニカルリレーが広く知られています。しかしながら、メカニカルリレーは機械的に接点を開放・接続を繰り返すため、耐久性に課題があり、長期信頼性が要求される用途では、半導体素子を使用した半導体リレーの普及が進んでいます。さらにシステムの増加に伴い、半導体リレーに要求される電流能力は年々大きくなっており、オン抵抗の低いディスクリート N チャネル MOSFET を使用したロードスイッチ回路を使用することで、低損失、低発熱の大電流半導体リレーを実現することが望まれます。

TPD7106F は、チャージポンプ回路を内蔵した 1 出力のハイサイドスイッチ用 N チャネル MOSFET ゲートドライバーであり、外付けディスクリート N チャネル MOSFET と組み合わせることで、大電流アプリケーションに対応したハイサイドスイッチを構成できます。また、この半導体リレーの構成は、メカニカルリレーと異なり接点摩耗がないため、メンテナンスフリー化を実現できます。そして、異常が発生した場合には MOSFET を保護するための急速にターンオフを制御する入出力端子により、マイコンから独立制御し、安全な動作を実現します。

図 1.1 TPD7106F と駆動する MOSFET 群

### 1.1. TPD7106F の入出力端子

表 1.1 端子説明

| 端子番号 | 記 <del>号</del> | 端子説明                                   |

|------|----------------|----------------------------------------|

| 1    | CP1-           | チャージポンプコンデンサー接続端子                      |

| 2    | TEST           | 内部回路テスト用端子、通常使用時=GND に接続               |

| 3    | CP1            | チャージポンプコンデンサー接続端子                      |

| 4    | $V_{DD}$       | 電源端子                                   |

| 5    | STBY           | スタンバイ制御端子                              |

| 6    | IN1            | 入力端子(通常オンオフ制御用)                        |

| 7    | IN2            | 入力端子(急速オフ用)                            |

| 8    | GND1           | GND 端子                                 |

| 9    | GND2           | GND 端子                                 |

| 10   | DIAG           | 診断出力端子(open drain)                     |

| 11   | OUT2           | N チャネルパワーMOSFET ゲート接続端子(急速オフ用出力端子)     |

| 12   | OUT1           | N チャネルパワーMOSFET ゲート接続端子(通常スイッチング用出力端子) |

| 13   | CPV            | チャージポンプ電圧出力端子                          |

| 14   | CP2            | チャージポンプコンデンサー接続端子                      |

| 15   | N.C            | 未接続端子                                  |

| 16   | CP2-           | チャージポンプコンデンサー接続端子                      |

### 1.2. 製品比較 (TPD7104AF, TPD7106F, TPD7107F)

当社の 1ch 出力ハイサイド用 N チャネル MOSFET ゲートドライバーIC の各製品の主な違いを以下の表に示します。電源逆接続保護や GND 断線保護など、製品によって安全性の高い保護機能を内蔵しています。TPD7106F の特長としては、10 mA の出力ソース電流と、0.4 A の出力シンク電流となっており、並列接続の MOSFET をオン/オフする能力をもっています。また、保護動作時の外付け MOSFET の制御方法は、製品によっても異なりますので、それらの点を考慮して適切な製品を選定してください。

表 1.2 製品比較表

| Item                            | TPD7104AF       | TPD7106F        | TPD7107F            |

|---------------------------------|-----------------|-----------------|---------------------|

| ウエハープロセス                        | BiCD0.13 µm     | BiCD0.13 μm     | BiCD0.13 μm         |

| Power Supply Voltage (DC)       | 24 V            | 27 V            | 26 V                |

| Power Supply Voltage (Pulse)    | 40 V (t≤300 ms) | 40 V (t≤500 ms) | 36 V (t≤400 ms)     |

| 出力ソース電流                         | 100 μΑ          | 10 mA           | 100 μΑ              |

| 出力シンク電流                         | 5 mA            | 0.4 A           | 5 mA / 230 mA (注 2) |

| 電源逆接続保護時の外付け<br>MOSFET の動作(注 1) | MOSFET OFF      | MOSFET OFF      | MOSFET ON           |

| GND 断線保護                        | -               | -               | 0                   |

| パッケージ                           | PS-8            | SSOP16          | WSON10A             |

注 1: 電源逆接続保護時の外付け MOSFET 動作の差異。

MOSFET ON: 損失低減を目的として、MOSFET をオン状態にして電流を流す。

MOSFET OFF: MOSFET をオフ状態にして、MOSFET のボディーダイオードに電流を流す。

電流を遮断するためには、ドレインとドレインが接続されるよう、追加のドライバーIC+MOSFET を接続。

注 2: 異常検知時に急速オフ動作に切り替わる。

# 2. 製品の機能

TPD7106F の機能には、入力信号による外付け MOSFET のオン/オフ制御、急速オフ制御があります。また、チャージポンプ回路を内蔵(コンデンサーは外付け)しており、そのチャージポンプ電圧の低電圧検出機能と診断出力、そして、電源逆接続に対する保護機能を内蔵しています。

#### 2.1. 外付け MOSFET の制御

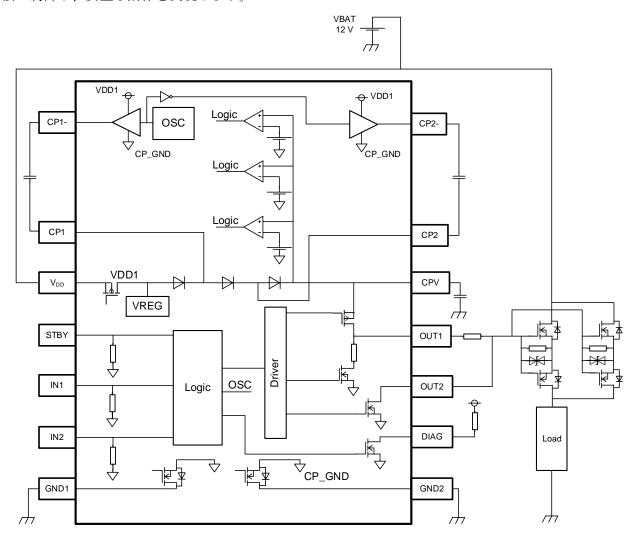

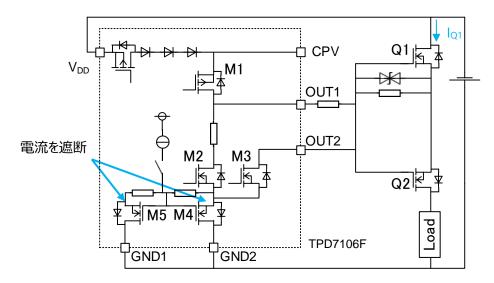

入力端子 IN1 から外付け N チャネル MOSFET を制御する信号を受けて、チャージポンプ (CP) とドライブ回路が動作します。図 2.1 で示しているトランジスターM1 を駆動する (M2 はオフ) ことで、十分なゲート電圧 (Vouti=Vdd+12 V (typ.)) で、MOSFET (Q1,Q2) をオンします (@Vini=Vih)。M2 を駆動する (M1 はオフ) ことで、MOSFET をオフ (ドライバーオン抵抗=630  $\Omega$  (typ.)) します (@Vini=Vii)。

VINI: IN1 端子入力電圧

VIH: ハイレベル入力電圧

VIL: ローレベル入力電圧

VOUTI: OUT1 端子出力電圧

図 2.1 外付け MOSFET の制御

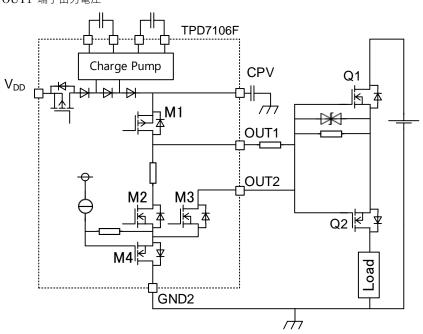

ton, toff1 スイッチングタイム

図 2.2 入出力波形

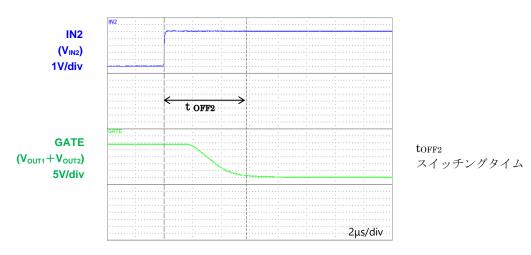

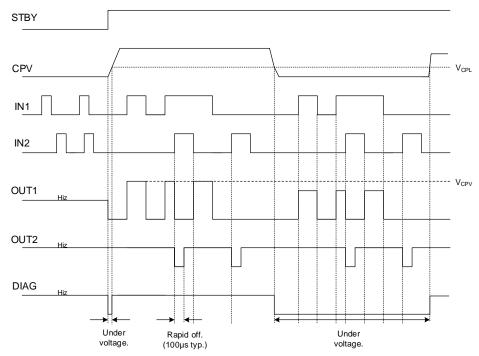

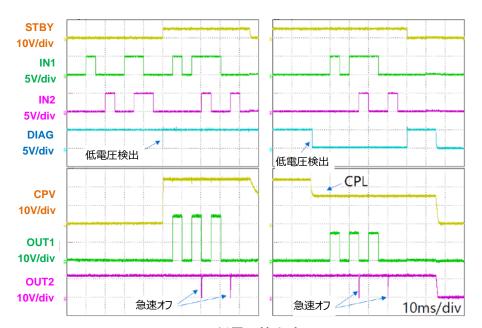

## 2.2. 外付け MOSFET を急速オフする機能

外付け MOSFET をすぐにオフさせたい場合は、入力端子 IN2 を使います。OUT1 の出力経路に OUT2 を接続します (図 2.1 参照)。M3 を駆動させる (M1 はオフ) ことで、急速にゲート電圧を下げ、外付け MOSFET (Q1,Q2) をオフします ( $@V_{IN2}=V_{IH}$ )。

V<sub>IN2</sub>: IN2 端子入力電圧V<sub>OUT2</sub>: OUT2 端子出力電圧

図 2.3 急速オフ制御波形

表 2.1 真理値表

| IN1     | IN2 | STBY | OUT1            | OUT2    | 状態           |

|---------|-----|------|-----------------|---------|--------------|

| X (注 1) | X   | L    | L Hiz (注 2) Hiz |         | スタンバイモード     |

| L       | L   | H    | L               | Hiz     | 通常動作         |

| Н       | L   | H    | H               | Hiz     | <b>迪希</b> 動作 |

| L       | H   | H    | L               | ${f L}$ | 急速オフモード      |

| Н       | Н   | Н    | L               | L       | 心胚々ノモート      |

注 1: Don't care

注 2: ハイインピーダンス

### 2.3. チャージポンプ回路

チャージポンプ回路は、外付けの N チャネル MOSFET のゲート駆動用電圧を生成するための昇圧電源回路です。ハイサイドスイッチの場合、N チャネル MOSFET がオンするとソースの電位は、電源電圧にほぼ等しくなり、オン状態を維持させるため、ゲートには電源電圧  $+10 \sim 15$  V と電源電圧以上の電圧を印加しなければなりません。 この電源電圧以上の電圧を IC 内部に生成する回路がチャージポンプ回路です。

図 2.4 チャージポンプ電圧(V<sub>CPV</sub>)のスタンバイ解除時の立ち上がり

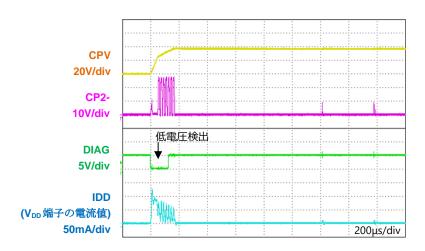

# 2.4. チャージポンプ電圧の低電圧検出機能

TPD7106F は、CPV 端子電圧を監視し、チャージポンプ電圧低下を検出します。チャージポンプ低下判定電圧  $V_{CPL}$  以下 ( $V_{DD}$ +4.7V 標準) になると、DIAG 端子は L ステートとなります。出力端子 OUT1, OUT2 は動作を維持します。なお、STBY 端子を L ステートとした場合、スタンバイモードとなるため、チャージポンプ回路は停止します。

図 2.5 チャージポンプ電圧の低電圧検出機能

図 2.6 低電圧検出波形

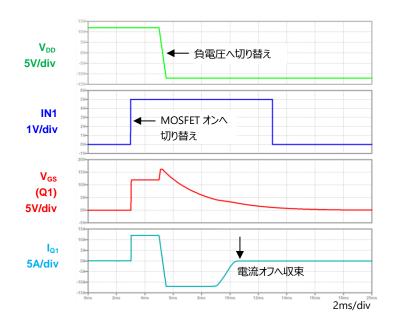

## 2.5. 電源逆接続保護機能

電源が逆極性で接続された場合、M1, M2 はオフし、GND 端子からの電流は、M4, M5 で遮断、外付け MOSFET をオフします。

図 2.7 電源逆接続時の振る舞い

図 2.8 電源逆接続時の振る舞い (simulation)

# 3. 電気的特性測定回路図

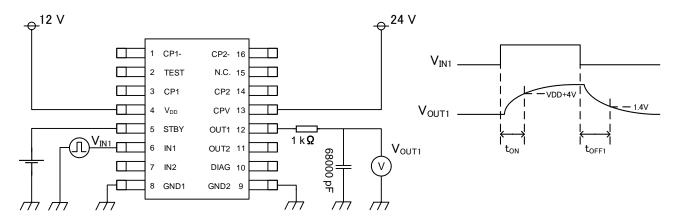

# 3.1. スイッチングタイム測定回路 1 (ton, toff1)

図 3.1 スイッチングタイム測定回路 1

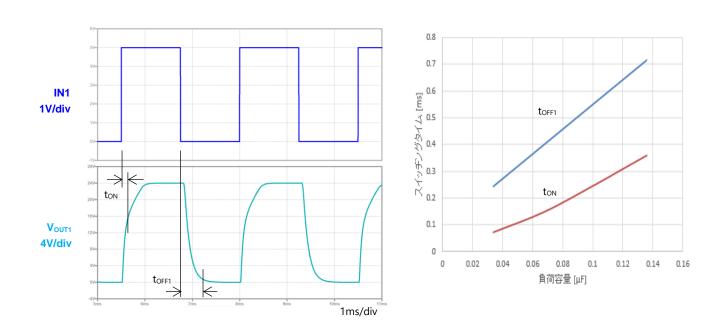

TPD7106F のスイッチングタイムは、駆動する負荷に影響されます。本製品を用いて電源供給経路を切り替える(一方の電源供給経路をカットし、その後、他方の電源供給経路を接続する)場合、それらの考慮をしてください。参考として、図 3.1 の負荷条件( $C_L$ =68000 pF)の回路を簡易 SPICE モデル(typ. 条件)でシミュレーションすると、スイッチングタイム:立ち上がり ton は、0.15 ms、立ち下がり toff1 は、0.4 ms になります。切り替え時に異なる電源経路が短絡しないようにこれらのスイッチングタイムを考慮して、設計してください。

図 3.2 スイッチングタイムと負荷容量 (simulation)

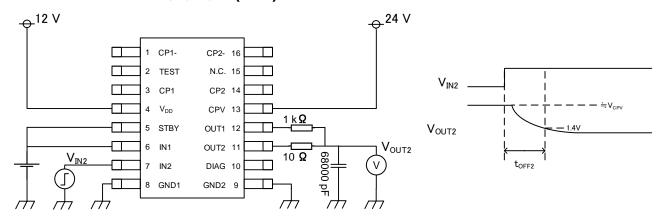

# 3.2. スイッチングタイム測定回路 2 (toff2)

図 3.3 スイッチングタイム測定回路 2

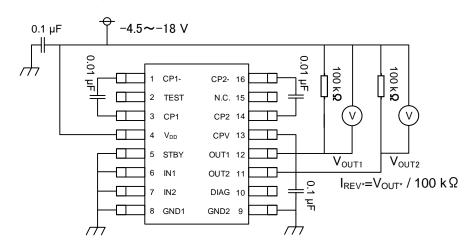

## 3.3. 電源逆接続時出力電流測定回路

図 3.4 電源逆接時出力電流測定回路

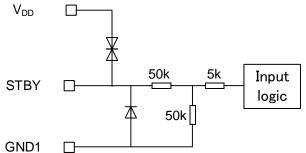

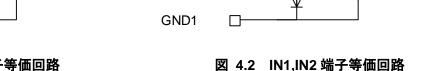

# 4. 端子等価回路図

IN1, IN2

The state of the sta

図 4.1 STBY 端子等価回路

図 4.3 CP1, CP2, CPV 端子等価回路

図 4.4 CP1-, CP2- 端子等価回路

図 4.5 OUT1 端子等価回路

図 4.6 OUT2 端子等価回路

\*) Resistance unit: [Ω]

図 4.7 DIAG 端子等価回路

図 4.8 GND1, GND2 等価回路

# 5. 応用回路例 (MOSFET 2 個並列の場合)

U1: TPD7106F

Q1, Q2, Q3, Q4 : Nch MOSFET / 40 V

D1, D2: CRZ16  $R1:1~k\Omega$

C4:  $1 \mu F / 50 V$

R2:10 Ω  $R3:10 k\Omega$  $R4:200\ k\Omega$ C1:  $10 \mu F / 50 V$ C2, C3:  $0.1 \mu F / 50 V$

注: 電源用コンデンサーは、できるだけIC の近くに接続してください。

図 5.1 応用回路例

# 6. 用語の説明

# 6.1. 絶対最大定格

表 6.1 絶対最大定格

| 用語          | 記号                                 | 説明                                                           |

|-------------|------------------------------------|--------------------------------------------------------------|

| 電源電圧 (DC)   | V <sub>DD (1)</sub>                | V <sub>DD</sub> 端子に印加しても IC が破壊、特性劣化および信頼性低下をひき起こさない直流電圧定格。  |

| 電源電圧 (パルス)  | V <sub>DD (2)</sub>                | V <sub>DD</sub> 端子に印加しても IC が破壊、特性劣化および信頼性低下をひき起こさないパルス電圧定格。 |

| 入力電圧 (1)    | $V_{STBY}$                         | STBY 端子に印加しても IC が破壊、特性劣化および信頼性低下をひき起こさない電圧定格。               |

| 入力電圧 (2)    | V <sub>IN1</sub> ,V <sub>IN2</sub> | IN1,IN2 端子に印加しても IC が破壊、特性劣化および信頼性低下をひき起こさない電圧定格。            |

| C P V 電 圧   | $V_{CPV}$                          | CPV 端子に印加しても IC が破壊、特性劣化および信頼性低下をひき起こさない電圧定格。                |

| TEST 端子電圧   | $V_{TEST}$                         | TEST 端子に印加しても IC が破壊、特性劣化および信頼性低下をひき起こさない電圧定格。               |

| 出力電流 (ソース)  | I <sub>OUT1 (1)</sub>              | IC が破壊、特性劣化および信頼性低下をひき起こさない出力端子から流し出し得る電流定格。                 |

| 出力電流 (シンク)  | I <sub>OUT1 (2)</sub>              | ICが破壊、特性劣化および信頼性低下をひき起こさない出力端子から吸い込み得る電流定格。                  |

| 出力電流 (シンク)  | ${ m I}_{{ m OUT2}}$               | ICが破壊、特性劣化および信頼性低下をひき起こさない出力端子から吸い込み得る電流定格。                  |

| 診断出力電圧      | $V_{DIAG}$                         | DIAG 端子に印加しても IC が破壊、特性劣化および信頼性低下をひき起こさない電圧定格。               |

| 診断出力電流      | I <sub>DIAG</sub>                  | IC が破壊、特性劣化および信頼性低下をひき起こさない DIAG 端子に流し得る電流定格。                |

| 許容損失        | $P_{D}$                            | 全動作範囲で、ICの破壊などが生じない消費電力の最大許容値。                               |

| 動作温度        | T <sub>opr</sub>                   | IC を正常に動作させるための周囲温度範囲。                                       |

| ジャンクション 温 度 | Tj                                 | IC の動作が許容される接合部温度の最大値。                                       |

| 保存温度        | T <sub>stg</sub>                   | 電圧を印加しない状態で、保存または輸送できる周囲温度範囲。                                |

# 6.2. 電気的特性

表 6.2 電気的特性 1

| 用語            | 記号                                                       | 説明                                                                                                                                                                                                      |

|---------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 動作電源電圧        | $V_{DD}$                                                 | 既定のジャンクション温度範囲で、IC の正常な動作および電気的特性が保証されるための電源電圧範囲。                                                                                                                                                       |

| 消 費 電 流       | I <sub>DD (1)</sub>                                      | 25°C のジャンクション温度で、入力電圧 $V_{STBY}$ を $V_{IL}$ よりも低い電圧に保ち、IC の動作をオフ 状態としたときに $V_{DD}$ 端子 (12 V) に流れる電流値。                                                                                                   |

| 消費電流          | I <sub>DD (2)</sub>                                      | 既定のジャンクション温度範囲で、入力電圧 $V_{STBY}$ を $V_{IH}$ よりも高い電圧に保ち、 $V_{IN1}$ , $V_{IN2}$ を $V_{IL}$ より低い電圧に保ち、 $IC$ の動作をオフ状態としたときに $V_{DD}$ 端子に流れる電流値。端子 $CP1/CP1$ -間、 $CP2/CP2$ -間に付ける容量素子は、それぞれ $0.01~\mu F$ とする。 |

| 消費電流          | I <sub>DD (3)</sub>                                      | 既定のジャンクション温度範囲で、入力電圧 $V_{IN}$ を $V_{IH}$ よりも高い電圧に保ち、IC の動作をオン状態としたときに $V_{DD}$ 端子に流れる電流値。端子 CP1/CP1-間、CP2/CP2-間に付ける容量素子は、それぞれ $0.01~\mu F$ 、端子 OUT1, OUT2 はオープンとする。                                     |

| ハイレベル 入 カ 電 圧 | $V_{\mathrm{IH}}$                                        | 既定のジャンクション温度範囲で、内部の制御回路が正常に動作して、外付けの N チャネル MOSFET がオンとなることを保証する入力端子 IN1, IN2, STBY の最小電圧。                                                                                                              |

| ローレベル入力電圧     | $V_{\mathrm{IL}}$                                        | 既定のジャンクション温度範囲で、内部の制御回路が正常に動作して、外付けの N チャネル MOSFET をオフとなることを保証する入力端子 IN1, IN2 の最大電圧。または、内部回路が、スタンバイ状態になることを保証する入力端子 STBY の最大電圧。                                                                         |

| 入 力 電 流       | $I_{\mathrm{IH}}$                                        | 既定のジャンクション温度範囲で、測定条件で規定される電圧を入力端子 IN1, IN2, STBY に印加したときにそれぞれの端子に流れ込む電流値。                                                                                                                               |

| 入 力 電 流       | $\mathrm{I}_{\mathrm{IL}}$                               | 既定のジャンクション温度範囲で、測定条件で規定される電圧を入力端子 IN1, IN2, STBY に印加したときにそれぞれの端子から流れ出す電流値。                                                                                                                              |

| ハイレベル 出 カ 電 圧 | V <sub>OH1</sub><br>V <sub>OH2</sub><br>V <sub>OH3</sub> | 既定のジャンクション温度範囲で、測定条件で規定される電圧、電流を印加したときに、出力端子 OUT1 に出力される電圧値。                                                                                                                                            |

| 出 カ クランプ 電 圧  | V <sub>OCL</sub>                                         | 既定のジャンクション温度範囲で、測定条件で規定される電圧を印加したときの、出力端子<br>OUT1 の電圧クランプ値。                                                                                                                                             |

| ローレベル出力電圧     | $V_{OL1}$                                                | 既定のジャンクション温度範囲で、測定条件で規定される電圧、電流を印加したときの、出力端子 OUT1 と OUT2 の出力電圧値。                                                                                                                                        |

| 診断出カリーク電流     | I <sub>DIAGH</sub>                                       | 既定のジャンクション温度範囲で、測定条件で規定される電圧を印加したときに、診断出力端子<br>DIAG に流れるリーク電流値。                                                                                                                                         |

| 診断出力電圧        | $V_{DIAGL}$                                              | 既定のジャンクション温度範囲で、測定条件で規定される電圧、電流を印加したときの診断出力端子 DIAG のオン電圧値。                                                                                                                                              |

# 表 6.3 電気的特性 2

| 用語                    | 記号                                                         | 説明                                                                                                                                                         |  |  |  |

|-----------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| チャージポンプ発振周波数          | fosc                                                       | 既定のジャンクション温度範囲で、測定条件で規定される電圧を印加したときに、チャージポンプを<br>駆動する発振器の発振周波数値。                                                                                           |  |  |  |

| チャージポンプ<br>低下判定電圧(検出) | $V_{\text{CPL}}$                                           | 既定のジャンクション温度範囲で、測定条件で規定される電圧を印加したときに、チャージポンプ電圧 V <sub>CPV</sub> の電圧低下を判定する検出電圧値。                                                                           |  |  |  |

| チャージポンプ低 下 判 定 電 圧    | $\Delta V_{	ext{CPL}}$                                     | 既定のジャンクション温度範囲で、測定条件で規定される電圧を印加したときに、チャージポンプ電圧 V <sub>CPV</sub> の電圧低下を判定する検出電圧値と、電圧低下の判定を解除するための検出電圧値の差分。                                                  |  |  |  |

| 出力ドライバーオン抵抗           | R <sub>ONH</sub><br>R <sub>ONL1</sub><br>R <sub>ONL2</sub> | 既定のジャンクション温度範囲で、測定条件で規定される電圧、電流を印加したときの診断出力端子 OUT1, OUT2 のオン抵抗値。                                                                                           |  |  |  |

| スイッチングタイム             | t <sub>ON</sub><br>t <sub>OFF1</sub>                       | 入力電圧の立ち上がり (50 %) から出力電圧の立ち上がり VDD + 4 V および、入力電圧の立ち下がり 50 % から出力電圧の立ち下がり 1.4 V までの遅延時間。         VIN1         VOUT1                                        |  |  |  |

| スイッチングタイム             | t <sub>OFF2</sub>                                          | 入力電圧の立ち上がり (50 %) から、出力電圧の立ち下がり 1.4 V までの遅延時間。  V <sub>IN2</sub>                                                                                           |  |  |  |

| 急速オフドライブ動作時間          | t <sub>O2ON</sub>                                          | OUT2 出力端子をチャージポンプ電圧(V <sub>CPV</sub> )相当の電位(24 V)に pull-up(100 kΩ)した状態で、IN2 端子を立ち上げ、出力電圧 V <sub>OUT2</sub> が、24 V の 50%を下回った時刻から、再び、24 V の 50%を上回るまでの経過時間。 |  |  |  |

| 電源逆接続時出力電流            | I <sub>REV1</sub><br>I <sub>REV2</sub>                     | 既定のジャンクション温度範囲で、測定条件で規定される電圧を印加したときに、出力端子<br>OUT1, OUT2 に流れる電流値。                                                                                           |  |  |  |

# 7. 評価ボード

本製品は、バッテリーなどのさまざまな電源系と、駆動するデバイスとの間を制御する半導体リレーの 用途に使われます。その機能を確認できるように周辺デバイスを実装した評価ボードを準備しています。 実負荷でのスイッチング動作、ファンクションを確認することができます。

図 7.1 TPD7106F の用途例

## 7.1. 評価ボード外観

| pin name        | Location | purpose                                   | Absolute maximum ratings                                  |

|-----------------|----------|-------------------------------------------|-----------------------------------------------------------|

| DIAG            | CN1-1    | Diagnosis output for U1                   | -0.3 to 27V                                               |

| SENSE OUT       | CN1-2    | Current sense output for U3               | -0.3 to 6V                                                |

| STBY            | CN1-3    | Standby mode control input for U1         | -0.3 to 27V                                               |

| IN1             | CN1-4    | Input for U1                              | -0.3 to 6V                                                |

| IN2             | CN1-5    | Input for U1                              | -0.3 to 6V                                                |

| GND             | CN1-6    | GND terminal                              |                                                           |

| +12V            | T1       | Power supply pin                          | -18 to 27V                                                |

| VOUT            | T2       | Output pin                                | -18 to 27V                                                |

| PGND            | T3       | GND terminal                              |                                                           |

| PGND            | T4       | GND terminal                              |                                                           |

| STBY            | TP1      | Monitor pin for U1                        | -0.3 to 27V                                               |

| IN1             | TP2      | Monitor pin for U1                        | -0.3 to 6V                                                |

| IN2             | TP3      | Monitor pin for U1                        | -0.3 to 6V                                                |

| DIAG            | TP4      | Monitor pin for Diagnosis output for IC1  | -0.3 to 27V                                               |

| SENSE OUT       | TP5      | Monitor pin for U3                        | -0.3 to 6V                                                |

| +5V             | TP6      | Monitor pin for U2                        | 4.25 to 5.25V                                             |

| CPV             | TP7      | Monitor pin for U1                        | 40V max                                                   |

| DRAIN(Q1,Q3,Q5) | TP8      | Monitor pin for drain of Q1,Q3,and Q5.    | 40V max                                                   |

| SOURCE          | TP9      | Monitor pin for source of FETs.           | -0.3V to VDD                                              |

| DRAIN(Q2,Q4,Q6) | TP10     | Monitor pin for drain of Q2,Q4,and Q6.    | 40V max                                                   |

| GATE            | TP11     | Monitor pin for gate of FETs.             | ±16V                                                      |

| PGND            | TP12     | GND pin.                                  |                                                           |

| PGND            | TP13     | GND pin.                                  |                                                           |

| +12V            | TP14     | Power supply pin                          | -0.3V to 27V                                              |

| STBY            | SW1      | 5V(H-state)/0V (L-state) Selection switch | I                                                         |

| IN1             | SW2      | 5V(H-state)/0V (L-state) Selection switch |                                                           |

| IN2             | SW3      | 5V(H-state)/0V (L-state) Selection switch | P34715790057079987900340000000000000000000000000000000000 |

図 7.2 TPD7106F 評価ボードの外観と端子説明

### 7.2. 評価ボードの使用方法

#### 【使用方法】

- 1. SW1,2,3 を"L"にします。 (STBY=IN1=IN2=0 V)

- 2. T1 に電源印加します。(必ず1.の後に行って下さい)

- 3. TP6 に 5 V を印加します。

- 4. SW1 の接続を"H"にします。 (スタンバイモード解除)

- 5. SW2 の接続を"H"にします。 (IN1=5 V)

- 6. 4.の状態で SW3 の接続を"H"にすることで、駆動 する MOSFET が、急速オフします。

- 7. SENSEOUT(TP5)は、R12 で検出した電流を差 動アンプで出力します。

#### 【使用上の注意】

- 1. CN1 で制御信号を入力する際には JP1,JP2,JP3 をオープンとしてください。

- 2. 負荷電流は最大 70A です。 (ヒートシンク無しの

- 3. JP5,JP6 はオープンとしてください。

図 7.3 TPD7106F 評価ボードの使用方法

### 7.3. 評価ボード回路図

図 7.4 TPD7106F 評価ボードの回路図

# 7.4. 部品表

表 7.1 部品表

| 部品番号           | 数量 | 部品名         | 定数/定格      | メーカー            | 説明             | パッケージ名称 | 標準寸法 (mm)        | I |

|----------------|----|-------------|------------|-----------------|----------------|---------|------------------|---|

| IC1            | 1  | TPD7106F    | -          | TOSHIBA         | MOSFET ゲートドライバ | SSOP-16 | 6.4 x 5.5        | I |

| IC2            | 1  | TA7805F     | -          | TOSHIBA         | レギュレータ         | HSOP-3  | 6.5 x 9.5        | I |

| IC3            | 1  | LTC6101BCS5 | -          | Analog Devices  | 電流センスアンプ       | TSOT-23 | 2.9 x 2.8        | I |

| Q1,Q2,Q3,Q4    | 4  | XPQR3004PB  | -          | TOSHIBA         | パワーMOSFET      | L-TOGL  | 8.45 x 9.9       | 1 |

| D1,D2          | 2  | 1SS352      | _          | TOSHIBA         | スイッチングダイオード    | USC     | 2.5 x 1.25       | l |

| D3,D8          | 2  | CRG09A      | -          | TOSHIBA         | 整流ダイオード        | S-FLAT  | 3.5 x 1.6        | I |

| D4,D5          | 2  | CRZ16       | -          | TOSHIBA         | ツェナーダイオード      | S-FLAT  | 3.5 x 1.6        | 1 |

| D6,D7          | 2  | CMZ27       | _          | TOSHIBA         | ツェナーダイオード      | M-FLAT  | 4.7 x 2.4        | I |

| R1,R2,R3,R4,R7 | 5  | -           | 10k        | -               | チップ抵抗          | -       | 1.6 x 0.8 (1608) | I |

| R5             | 1  | -           | 10         | -               | チップ抵抗          | -       | 1.6 x 0.8 (1608) | Ι |

| R6             | 1  | -           | 47k        | -               | チップ抵抗          | -       | 1.6 x 0.8 (1608) | I |

| R8             | 1  | -           | 1k         | -               | チップ抵抗          | -       | 1.6 x 0.8 (1608) | I |

| R9             | 1  | -           | 100        | -               | チップ抵抗          | -       | 1.6 x 0.8 (1608) | Ι |

| R10            | 1  | -           | 200        | -               | チップ抵抗          | -       | 1.6 x 0.8 (1608) | I |

| R11            | 1  | -           | 200k       | -               | チップ抵抗          | -       | 1.6 x 0.8 (1608) | I |

| R12            | 1  | BVS-M-R0005 | 0.5m Ω /5W | Isabellenhuette | シャント抵抗         | -       | 10 x 5.2         | I |

| C1,C4          | 1  | -           | 1.0uF/50V  | -               | チップセラミックコンデンサ  | -       | 3.2 x 1.6 (3216) | Ι |

| C2,C3,C6       | 2  | -           | 0.1uF/50V  | -               | チップセラミックコンデンサ  | -       | 1.6 x 0.8 (1608) | 1 |

| C5             | 1  | -           | 10uF/50V   | -               | チップセラミックコンデンサ  | -       | 3.2 x 1.6 (3216) | I |

| C7             | 1  | -           | 1000pF/50V | -               | チップセラミックコンデンサ  | -       | 1.6 x 0.8 (1608) | I |

| C8             | 1  | -           | 15pF/50V   | -               | チップセラミックコンデンサ  | -       | 2.0 x 1.2 (2012) | 1 |

| C9             | 1  | -           | 2.2uF/25V  | -               | セラミックコンデンサ     | -       | -                | I |

| C10            | 1  | -           | 100uF/25V  | -               | アルミ電解コンデンサ     | -       | -                | I |

未実装

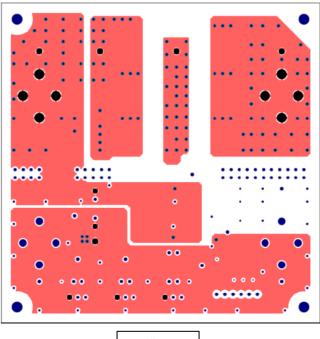

# 7.5. 評価ボード基板レイアウト

1st Layer

2nd Layer

3rd Layer

4th Layer

図 7.5 TPD7106F 評価ボードの基板レイアウト

### 記載内容の留意点

#### 1. ブロック図

ブロック図内の機能ブロック/回路/定数などは、機能を説明するため、一部省略・簡略化している場合があります。

#### 2. 等価回路

等価回路は、回路を説明するため、一部省略・簡略化している場合があります。

# 使用上のご注意およびお願い事項

#### 使用上の注意事項

絶対最大定格は複数の定格の、どの1つの値も瞬時たりとも超えてはならない規格です。 複数の定格のいずれに対しても超えることができません。絶対最大定格を超えると破壊、損傷お よび劣化の原因となり、破裂・燃焼による傷害を負うことがあります。

#### 製品取り扱い上のお願い

株式会社東芝およびその子会社ならびに関係会社を以下「当社」といいます。 本資料に掲載されているハードウエア、ソフトウエアおよびシステムを以下「本製品」といいます。

- 本製品に関する情報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を得て本 資料を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

- 当社は品質、信頼性の向上に努めていますが、半導体・ストレージ製品は一般に誤作動または故障する場合があります。本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウエア・ソフトウエア・システムに必要な安全設計を行うことをお願いします。なお、設計および使用に際しては、本製品に関する最新の情報(本資料、仕様書、データシート、アプリケーションノート、半導体信頼性ハンドブックなど)および本製品が使用される機器の取扱説明書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

- 本製品は、特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な財産損害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下"特定用途"という)に使用されることは意図されていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇宙機器、医療機器(ヘルスケア除く)、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連機器、昇降機器、発電関連機器などが含まれますが、本資料に個別に記載する用途は除きます。特定用途に使用された場合には、当社は一切の責任を負いません。なお、詳細は当社営業窓口まで、または当社 Web サイトのお問い合わせフォームからお問い合わせください。

- ◆ 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

- ◆ 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用することはできません。

- 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及 び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をしておりません。

- 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、「米国輸出管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず当社営業窓口までお問い合わせください。本製品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査の上、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は一切の責任を負いかねます。

# 東芝デバイス&ストレージ株式会社

https://toshiba.semicon-storage.com/jp/