TOSHIBA CDMOS Integrated Circuit Silicon Monolithic

# TC7735FTG

System power management IC for TFT / low-temperature polysilicon liquid crystal display

### 1. Summary

The TC7735FTG is a system power management IC for liquid crystal module of TFT and low-temperature polysilicon. It can generate each voltage level, which the liquid crystal display (LCD) driver requires. In addition, the TC7735FTG can generate the high-voltage power supply for source driver and gate driver and incorporates VCOM amplifier circuit. So, it can drive the LCD of TFT and low-temperature polysilicon easily by itself.

The TC7735FTG can also output the required voltage to connect various LCD drivers by incorporating the function of adjusting voltage. This optimizes the characteristics of whole LCD system. And the protection functions like the over current protection circuit and the under voltage lockout circuit are incorporated to improve safety in driving the IC.

### 2. Applications

TFT LCD module, low-temperature polysilicon LCD module, and so on

### 3. Features

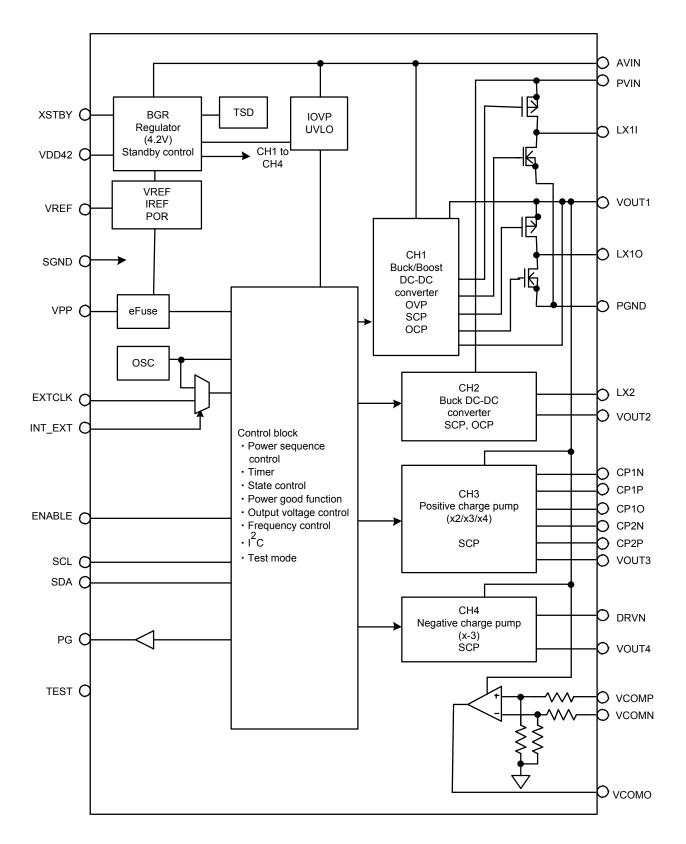

- System power management IC for compound LCD module CH1: Buck/Boost DC-DC convertor CH2: Buck DC-DC convertor CH3: Positive regulated charge pump CH4: Negative regulated charge pump Op-Amp for VCOM

- Supporting input voltage in wide range: 4.5V to 16V

- Built-in power supply sequence generating circuit

- Built-in OSC circuit: 1MHz

- Capable of supplying external clocks of switching frequency

- Built-in monitor of internal state by Power Good (PG terminal.)

- Built-in input under voltage lockout circuit, input over voltage protection circuit, thermal shutdown, and output over voltage protection circuit.

- Serial communication for debug (I<sup>2</sup>C bus)

- Power on reset function

- Operating temperature :-40 to 85°C

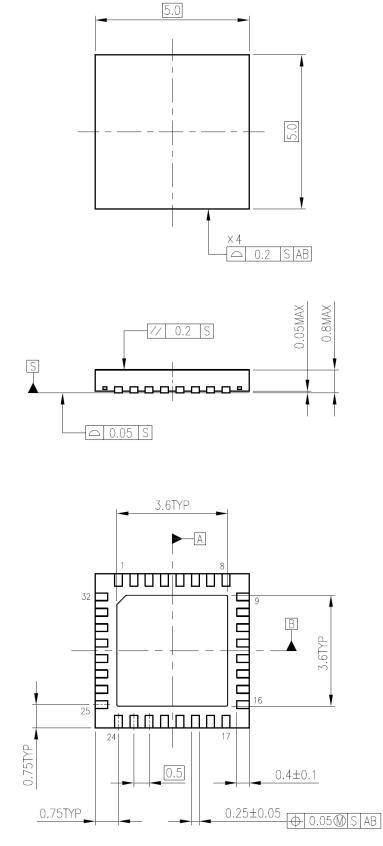

- Package : QFN32pin

This product has a MOS structure and is sensitive to electrostatic discharge. When handling this product, ensure that the environment is protected against electrostatic discharge by using an earth strap, a conductive mat and an ionizer. Ensure also that the ambient temperature and relative humidity are maintained at reasonable levels.

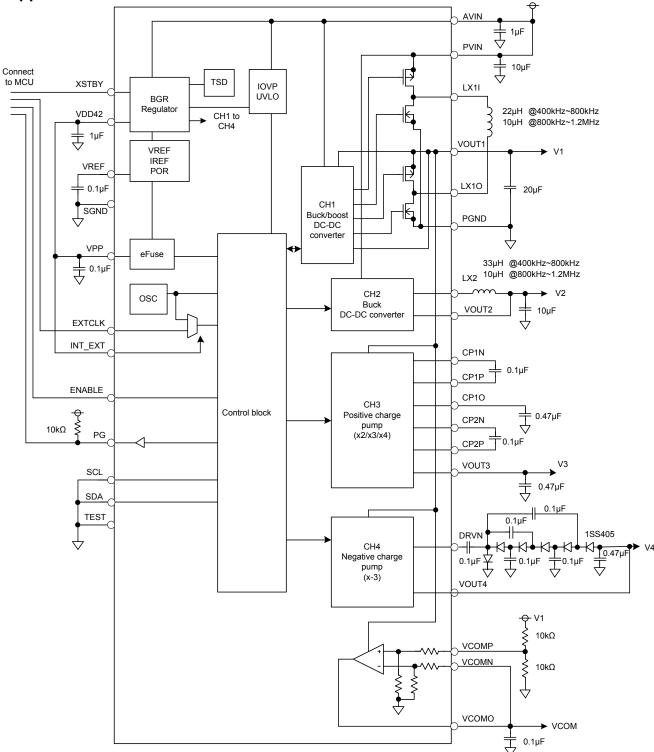

### 4. Block diagram

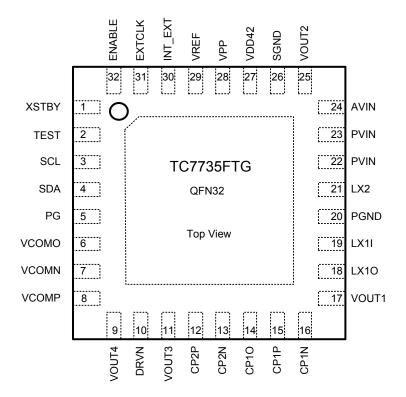

### 5. Pin assignment

Figure 5.1 Pin assignment

Note: Package of QFN32 adopted to the TC7735FTG has a thermal pad for heat radiation on the back side of the package. Contact the back side of the package to the board by reflow and so on.

### 6. Pin description

### Table 6.1 Pin description

| Pin name | I/O                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pin description                                                                                                                                                              |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PVIN     | -                                                                                                                    | Power supply terminal (1)<br>Power supply terminal. Supply the same power supply as AVIN terminal. It is short circuited internally to<br>AVIN terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                              |  |  |  |  |

| AVIN     | -                                                                                                                    | Power supply termin<br>Analog power sup<br>internally to PVIN te                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ply terminal. Supply the same power supply as PVIN terminal. It is short circuited                                                                                           |  |  |  |  |

| PGND     | -                                                                                                                    | Power GND termina<br>Connect to the co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | l<br>mmon ground (GND). It is short circuited internally to SGND terminal.                                                                                                   |  |  |  |  |

| SGND     | -                                                                                                                    | Analog GND termina<br>Connect to the co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | al<br>mmon ground (GND). It is short circuited internally to PGND terminal.                                                                                                  |  |  |  |  |

| VDD42    | ο                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tput terminal oltage of 4.2V for internal circuit. Connect the capacitor between VDD42 terminal and stabilize the voltage. It cannot supply power to the external device.    |  |  |  |  |

| VREF     | 0                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tput terminal<br>oltage of 1.5V for internal circuit. Connect the capacitor between VREF terminal and<br>abilize the voltage. It cannot supply power to the external device. |  |  |  |  |

| XSTBY    | I                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ol terminal (with pull-down)<br>ninal for the TC7735FTG. XSTBY="L": Operations of all circuits stop.                                                                         |  |  |  |  |

|          |                                                                                                                      | Enable control terminal<br>Enable terminal to control output voltage. Time of output voltage pattern, which is managed by control<br>logic, can be controlled by ENABLE terminal.<br>Input should not be in floating state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                              |  |  |  |  |

| ENABLE   | I                                                                                                                    | ENABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ENABLE Functions                                                                                                                                                             |  |  |  |  |

|          |                                                                                                                      | L Po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ower supplies for LCD modules (CH1 to CH4) and Op-amp for VCOM: All off                                                                                                      |  |  |  |  |

|          |                                                                                                                      | H Power supplies for LCD modules (CH1 to CH4) and Op-amp for VCOM: All on Each power supply starts up according to the sequence configured by the registered |                                                                                                                                                                              |  |  |  |  |

| EXTCLK   | 1                                                                                                                    | Input terminal of external clock signal (with pull-down)<br>To control switching frequency of each power supply by inputting external clocks, input clocks by<br>EXTCLK terminal. In supplying external clocks, set INT_EXT terminal high level. When external clocks are<br>not used, configure the EXTCLK terminal open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                              |  |  |  |  |

|          |                                                                                                                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ck select signal for each power supply.                                                                                                                                      |  |  |  |  |

|          |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OSC clocks or external clocks for each power supply.                                                                                                                         |  |  |  |  |

| INT_EXT  | .                                                                                                                    | INT_EXT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Functions                                                                                                                                                                    |  |  |  |  |

|          |                                                                                                                      | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Internal clock mode: Clocks for each power supply use internal OSC circuit.                                                                                                  |  |  |  |  |

|          | External clock mode: Clocks for each power supply are supplied externally.<br>Input clock signal by EXTCLK terminal. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                              |  |  |  |  |

|          |                                                                                                                      | When INT_EXT is high level, short circuit to VDD42 terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                              |  |  |  |  |

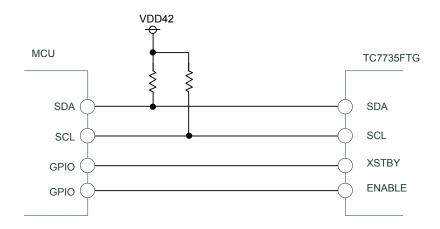

| SCL      | I                                                                                                                    | I <sup>2</sup> C clock input terminal<br>In using I <sup>2</sup> C communication, connect pull-up resistance. (Note 1)<br>When it is not used, connect it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                              |  |  |  |  |

| SDA      | I/O                                                                                                                  | I <sup>2</sup> C data input/outpu<br>In using I <sup>2</sup> C comn<br>When it is not used,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nunication, connect pull-up resistance. (Note 1)                                                                                                                             |  |  |  |  |

Note 1:ESD protection diode is connected to SDA and SCL terminals (VDD42 side). Pay attention that I<sup>2</sup>C bus cannot be shared with the external IC.

### Table 6.2 Pin description

| Pin name                     | I/O | Pin description                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PG                           | ο   | Power Good output terminal<br>PG signal outputs low level when channels of CH1 to CH4 operate normally. Connect pull-up resistance<br>because this terminal is an open drain output terminal.                                                                                                                                                                                     |  |  |  |

| LX1I<br>LX1O                 | 0   | Inductor connection terminal for CH1 (voltage buck/boost DC-DC convertor)<br>Driver output terminal of voltage buck/boost DC-DC convertor. Voltage boost DC-DC convertor or buck<br>DC-DC convertor can be constructed by connecting the inductor between LX1I terminal and LX10<br>terminal. Input voltage is switched to the boosting voltage or bucking voltage automatically. |  |  |  |

| VOUT1                        | 0   | Output terminal for CH1 (voltage buck/boost DC-DC convertor)<br>Output terminal of voltage buck/boost DC-DC convertor. The voltage of LDO circuit and charge pump<br>circuit is generated referring to the configured voltage which is outputted from VOUT1 terminal. Connect<br>the capacitor between VOUT1 terminal and PGND terminal to stabilize the voltage.                 |  |  |  |

| LX2                          | 0   | Inductor connection terminal for CH2 (voltage buck DC-DC convertor)<br>It generates the system power supply for LCD module. Available voltage range is 3V to 5V. Connect the<br>inductor to LX2 terminal.                                                                                                                                                                         |  |  |  |

| VOUT2                        | I   | Feedback terminal for CH2 (voltage buck DC-DC convertor)<br>It is a feedback input terminal to stabilize the output voltage of the voltage buck DC-DC convertor.<br>Connect the capacitor between VOUT2 terminal and PGND terminal to stabilize the voltage.                                                                                                                      |  |  |  |

| CP1P<br>CP1N<br>CP2P<br>CP2N | I/O | Capacitor connection terminal for CH3 (positive charge pump)<br>Positive charge pump circuit can be used by connecting capacitors between CP1P terminal and CF<br>terminal, and between CP2P terminal and CP2N terminal. When double charge pumps are used,<br>terminals of CP1P and CP1N should be open.                                                                         |  |  |  |

| CP10                         | 0   | Output terminal of middle point for CH3 (positive regulated charge pump)<br>It outputs the middle voltage of the voltage boost generated by the charge pump. Connect the<br>between CP1O terminal and PGND terminal to stabilize the voltage. When double charge pump<br>used, terminals of CP1O should be open.                                                                  |  |  |  |

| VOUT3                        | 0   | Output terminal for CH3 (positive regulated charge pump)<br>It outputs high voltage required by gate driver of LCD module. Connect the capacitor between VOUT3<br>terminal and PGND terminal to stabilize the voltage.                                                                                                                                                            |  |  |  |

| DRVN                         | ο   | Drive output terminal for CH4 (negative regulated charge pump)<br>It outputs high voltage of negative-side required by gate driver of LCD module. Charge pump circuit is<br>constructed by connecting the capacitor and the diode. And inverted voltage of VOUT1 is outputted.                                                                                                    |  |  |  |

| VOUT4                        | I   | Feedback terminal for CH4 (negative regulated charge pump)<br>Feedback input terminal stabilizes the output voltage of the negative charge pump. Feedback the<br>output voltage of the constructed charge-pump circuit externally.                                                                                                                                                |  |  |  |

| VCOMP                        | I   | Non-inverted input terminal of Op-amp for VCOM                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| VCOMN                        | I   | Inverted input terminal of Op-amp for VCOM                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| VCOMO                        | 0   | Output terminal of Op-amp for VCOM                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| VPP                          | I   | Voltage input terminal for eFuse<br>Short circuit to VDD42 terminal.                                                                                                                                                                                                                                                                                                              |  |  |  |

| TEST                         | I   | Test terminal (with pull-down)<br>Toshiba test terminal for shipping investigation. Connect it to the common ground (GND).                                                                                                                                                                                                                                                        |  |  |  |

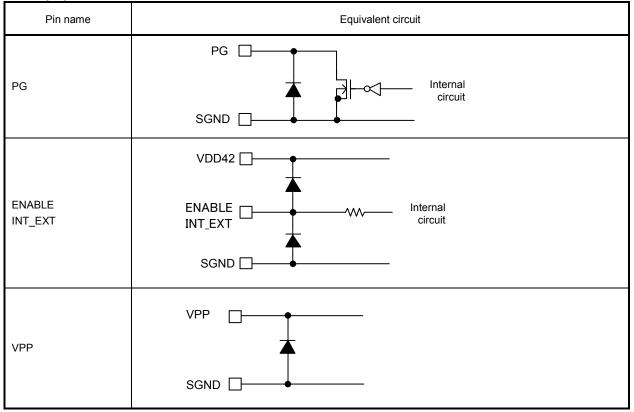

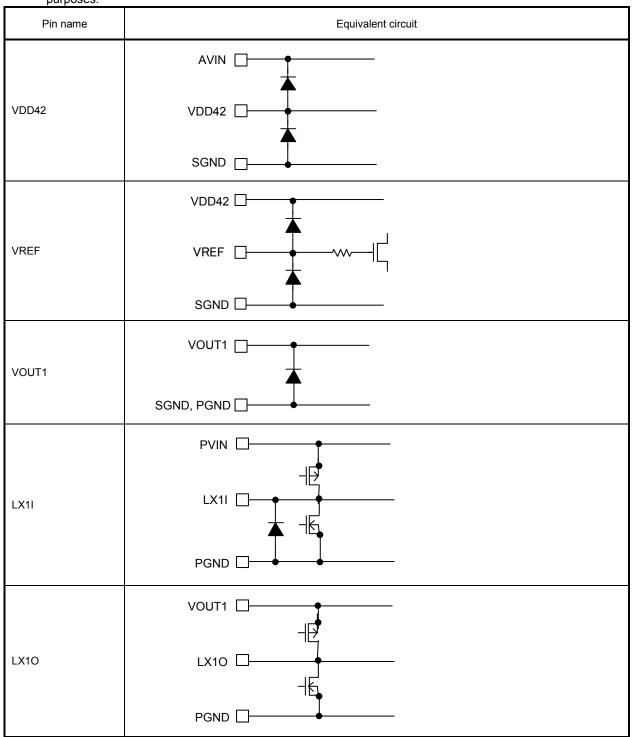

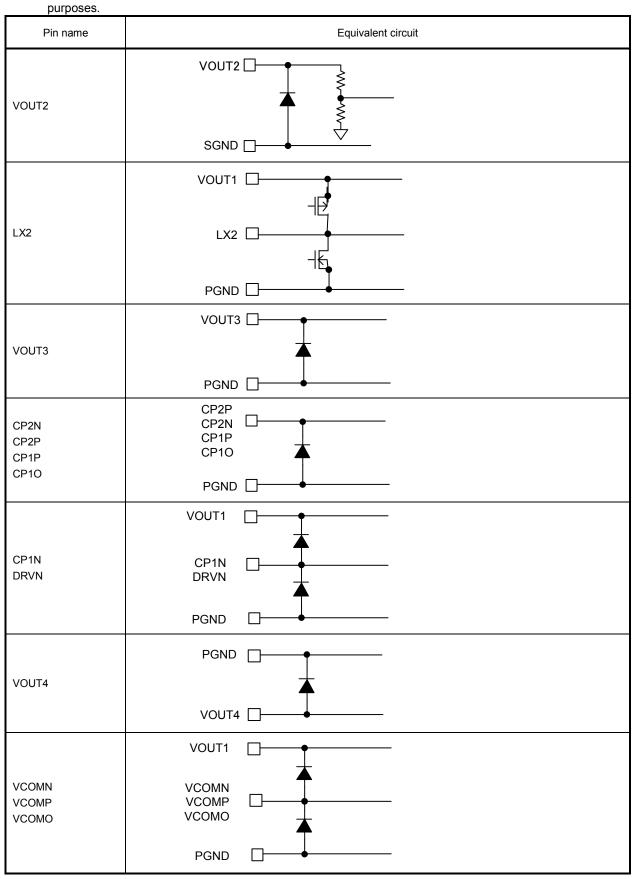

### 7. Equivalent circuit of input/output terminal

### 7.1 Power supply terminal

### Table 7.1 Equivalent circuit of power supply terminal

Note: The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory

| purposes.               |                    |

|-------------------------|--------------------|

| Pin name                | Equivalent circuit |

| AVIN,PVIN<br>PGND, SGND | AVIN, PVIN         |

### 7.2 Logic input/output terminal

### Table 7.2 Equivalent circuit of logic input/output terminal

Note: The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

| Pin name       | Equivalent circuit                                          |

|----------------|-------------------------------------------------------------|

| XSTBY          | XSTBY Internal<br>circuit<br>\$ 100kΩ                       |

|                |                                                             |

|                | VDD42                                                       |

| TEST<br>EXTCLK | TEST<br>EXTCLK                                              |

|                | SGND SGND                                                   |

|                | VDD42                                                       |

| SCL            | SCL                                                         |

|                |                                                             |

|                | VDD42                                                       |

| SDA            | SDA Internal<br>Internal<br>Internal<br>Internal<br>Circuit |

|                |                                                             |

### Table 7.3 Equivalent circuit of logic input/output terminal

Note: The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

### 7.3 Analog input/output terminal

### Table 7.4 Equivalent circuit of analog input/output terminal

Note: The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

### Table 7.5 Equivalent circuit of analog input/output terminal

Note: The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory

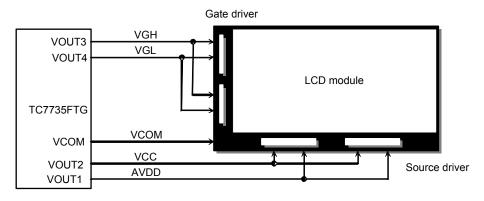

### 8. Function / Operation description

The TC7735FTG can generate high voltage that LCD driver requires. It can generate the power supply for system logic (VCC) and following four kinds of power supplies. High-voltage power supply (AVDD) for source driver, high-voltage power supply (VGH) and low-voltage power supply (VGL) for gate driver, and power supply for VCOM.

Figure 8.1 System diagram

The TC7735FTG can adjust the output voltage level of each power supply and the timing of ON/OFF sequence because it incorporates serial communication function for debug. The voltage environment can be optimized by writing these data to the internal eFuse.

| _      |                             |                        |

|--------|-----------------------------|------------------------|

| Output | Standard setting<br>product | Setting range (Note)   |

| VOUT1  | 9.2V                        | 5 to 15V (0.2V step)   |

| VOUT2  | 3.3V                        | 3 to 5V (0.1V step)    |

| VOUT3  | 18.0V                       | 14 to 22V (0.2V step)  |

| VOUT4  | -6.0V                       | -5 to -15V (0.2V step) |

Table 8.1 Setting output

Note: Standard setting product cannot be used to change the voltage setting. Product sample for debug is required in order to change the output settings using the serial communication function.

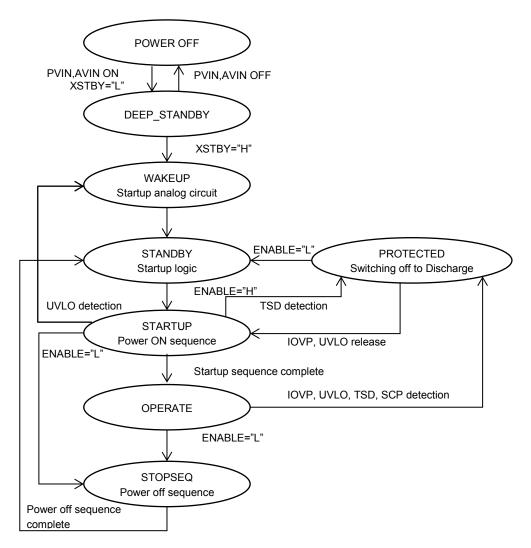

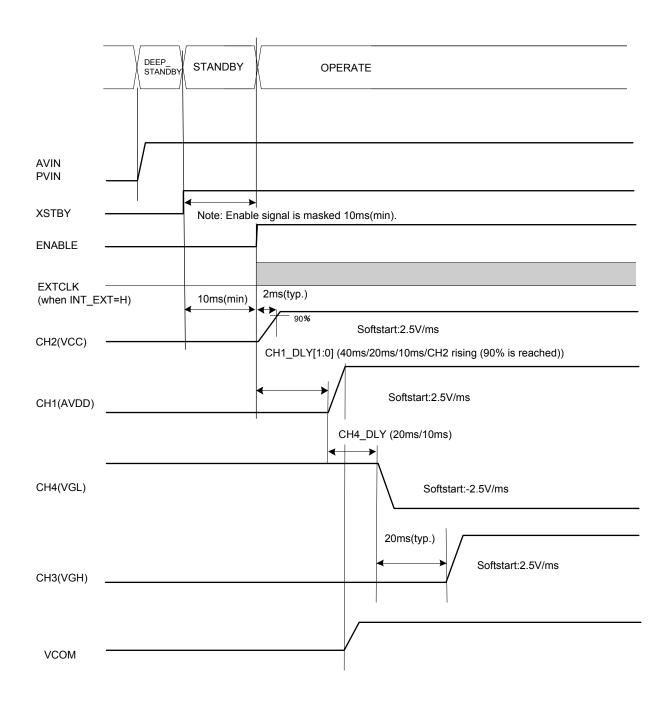

### 8.1 Operation description

Operation mode of the TC7735FTG transits by the setting of XSTBY and ENABLE terminals shown in the Figure 8.2.

Figure 8.2 Mode transition diagram

### 8.1.1 DEEP STANDBY

DEEP STANDBY supplies the power supply to PVIN and AVIN. XSTBY="L" input. All of OSC circuit, internal regulator, and each power supply circuit are turned off. Low-current consumption drive can be kept even in applying voltage to the power supply of PVIN and AVIN.

### 8.1.2 WAKEUP

It indicates the starting up of OSC circuit and the internal regulator after inputting high level to XSTBY. Register setting value is read out from eFuse.

### 8.1.3 STANDBY

In STANDBY mode, all internal regulators are operating under the condition that XSTBY is "H" and ENABLE is "L".  $I^2C$  can be controlled and register setting value is kept. Each power supply circuit for driving LCD is turned off.

### 8.1.4 STARTUP

Channel of each power supply and Op-Amp for VCOM start soft start according to the power ON sequence by inputting high level to ENABLE from STANDBY. Power ON sequence depends on the register setting value. When soft start of all power channels and of Op-Amp for VCOM have been completed, the operation moves to the OPERATE mode. In STARTUP, all protection circuits except SCP and OVP are valid.

### 8.1.5 OPERATE

All power channels and Op-Amp for VCOM operate and all protection functions are enabled. PG terminal outputs low level. The operation moves to PROTECTED mode after abnormality is detected by protection functions except OCP under the following conditions; abnormality is detected continuously during delay time counted by each function.

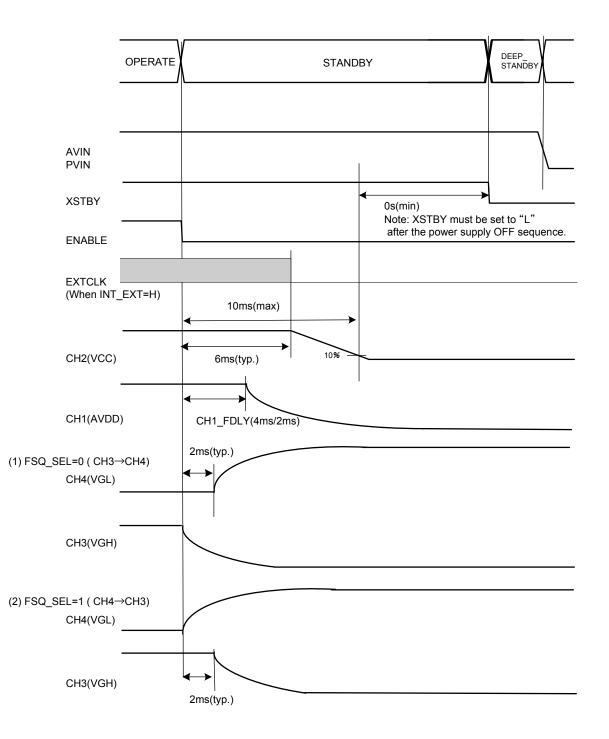

### 8.1.6 STOPSEQ

After OPERATE mode, each power supply is turned off according to the power OFF sequence by inputting low level to ENABLE. Power OFF sequence depends on the register setting value. When all power supplies are turned off, the operation moves to STANDBY mode.

### 8.1.7 PROTECTED

PROTECTED mode is moved from STARTUP or OPERATE mode when the outputs of power channels are turned off by the protection function of IOVP, SCP, TSD, or UVLO. PG terminal is Hi-Z. When IOVP or UVLO is released, the operation moves to STARTUP mode.

When low level is inputted to ENABLE, the operation moves to STANDBY mode.

### 8.2 Description of register (for debug)

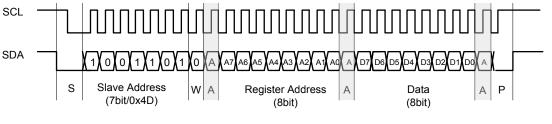

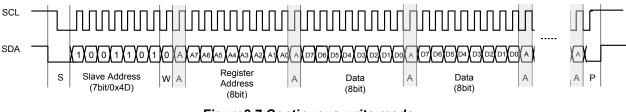

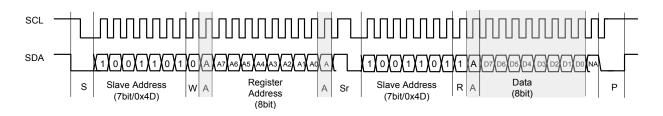

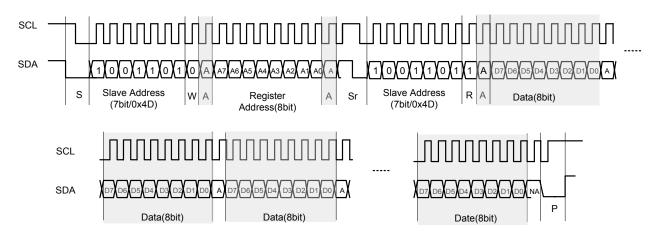

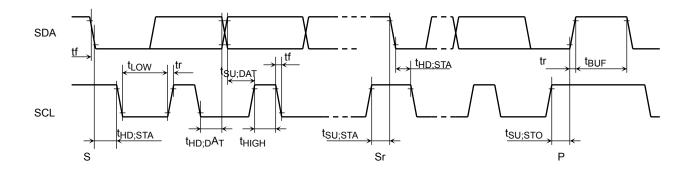

The TC7735FTG incorporates  $\mathrm{I}^2\mathrm{C}$  bus for debug to control the registers.

As shown in the Figure 8.3, pull up SCL and SDA terminals and connect them to the external MCU.

Figure 8.3 Example of connecting to MCU

Note: Register should be changed in STANDBY mode (XSTBY="H", ENABLE="L").

### 8.3 Register map

Refer to the below table of the register map. Register No. 03h to 06h are enabled in product sample for debug.

Table 8.2 Register map

| Register<br>No. | D7       | D6        | D5               | D4              | D3      | D2                  | D1      | D0      | R/W |

|-----------------|----------|-----------|------------------|-----------------|---------|---------------------|---------|---------|-----|

| 00h             | Reserved | SEL_REGI  | SLP_S            | EL[1:0]         | -       | PWIDE_SEL[2:0]      |         |         | R/W |

| 01h             | CH3TIM   | _SEL[1:0] | CH3DIV_          | CH3DIV_SEL[1:0] |         | /_SEL[1:0] Reserved |         | R/W     |     |

| 02h             | CH1_D    | 0LY[1:0]  | CH4_DLY CH1_FDLY |                 | FSQ_SEL | -                   | -       | -       | R/W |

| 03h             | Reserved | Reserved  | CH1_VSET[5:0]    |                 |         |                     | R/W     |         |     |

| 04h             | -        | Reserved  | - CH2_VSET[4:0]  |                 |         |                     | R/W     |         |     |

| 05h             | -        | Reserved  | CH3_VSET[5:0]    |                 |         |                     | R/W     |         |     |

| 06h             | -        | Reserved  | CH4_VSET[5:0]    |                 |         |                     | R/W     |         |     |

| 07h             | -        | TSD       | UVLO             | OVP             | SCP_CH1 | SCP_CH2             | SCP_CH3 | SCP_CH4 | R   |

### 8.3.1 Setting (00h)

|               | bit 7    | bit 6    | bit 5  | bit 4   | bit 3 | bit 2 | bit 1          | bit 0 |

|---------------|----------|----------|--------|---------|-------|-------|----------------|-------|

| 00h           | Reserved | SEL_REGI | SLP_SI | EL[1:0] | -     |       | PWIDE_SEL[2:0] |       |

| Initial value | 0        | 0        | 0      | 1       | 0     | 0     | 0              | 1     |

SEL\_REGI

: Select eFuse or register.

To enable the register, set SEL\_REGI="1". Table 8.3 SEL\_REGI

| SEL_REGI | Function         |

|----------|------------------|

| 0        | eFuse: Enable    |

| 1        | Register: Enable |

SLP\_SEL [1:0] Adjustment register in inputting external clocks (Refer to Table 8.4)

PWIDE\_SEL [2:0] : Adjustment register in inputting external clocks (Refer to Table 8.4)

### Table 8.4 SLP\_SEL, PWIDE\_SEL

| External clock frequency | SLP_SEL[1:0] | PWIDE_SEL [2:0] |

|--------------------------|--------------|-----------------|

| 400kHz to 800kHz         | 11           | 100             |

| 800kHz to 1.2MHz         | 01           | 001             |

Note: bit7: Fix to "0".

| 8.3.2         | Setting | (01h)     |                 |       |        |           |       |       |

|---------------|---------|-----------|-----------------|-------|--------|-----------|-------|-------|

|               | bit 7   | bit 6     | bit 5           | bit 4 | bit 3  | bit 2     | bit 1 | bit 0 |

| 01h           | CH3TIM  | _SEL[1:0] | CH3DIV_SEL[1:0] |       | CH4DIV | _SEL[1:0] | Rese  | erved |

| Initial value | 0       | 0         | 1               | 0     | 1      | 0         | 1     | 0     |

CH3TIM\_SEL [1:0] : CH3: Setting the number of multiple steps of the positive charge pump.

### Table 8.5 CH3TIM\_SEL

| CH3TIM_SEL [1:0] | Number of multiple steps |

|------------------|--------------------------|

| 00               | ×4                       |

| 01               | ×3                       |

| 10               | ×2                       |

| 11               | Setting forbidden        |

CH3DIV\_SEL [1:0] : CH3: Setting the ratio of frequency dividing of the positive charge pump. Switching frequency recommended value is 125kHz.

### Table 8.6 CH3DIV\_SEL

| CH3DIV_SEL[1:0] | Ratio of dividing frequency |

|-----------------|-----------------------------|

| 00              | 1/2                         |

| 01              | 1/4                         |

| 10              | 1/8                         |

| 11              | Setting forbidden           |

CH4DIV\_SEL [1:0] : CH4: Setting the ratio of frequency dividing of the negative charge pump. Switching frequency recommended value is 125kHz.

### Table 8.7 CH4DIV\_SEL

| CH4DIV_SEL[1:0] | Ratio of dividing frequency |

|-----------------|-----------------------------|

| 00              | 1/2                         |

| 01              | 1/4                         |

| 10              | 1/8                         |

| 11              | Setting forbidden           |

Note: bit1-0: Fix to "10".

| 8.3.3         | Setting | (02h)   |         |          |         |       |       |       |

|---------------|---------|---------|---------|----------|---------|-------|-------|-------|

| _             | bit 7   | bit 6   | bit 5   | bit 4    | bit 3   | bit 2 | bit 1 | bit 0 |

| 02h           | CH1_D   | LY[1:0] | CH4_DLY | CH1_FDLY | FSQ_SEL | -     | -     | -     |

| Initial value | 0       | 0       | 0       | 0        | 0       | 0     | 0     | 0     |

CH1\_DLY [1:0] : Setting the rising delay time of CH1 output.

Table 8.8 CH1\_DLY

| CH1_DLY[1:0] | Delay time                  |

|--------------|-----------------------------|

| 00           | 40ms                        |

| 01           | 20ms                        |

| 10           | 10ms                        |

| 11           | CH2 rising (90% is reached) |

CH4\_DLY : Setting the rising delay time of CH4 output.

### Table 8.9 CH4\_DLY

| CH4_DLY | Delay time |

|---------|------------|

| 0       | 20ms       |

| 1       | 10ms       |

CH1\_FDLY : Setting the falling delay time of CH1 output.

### Table 8.10 CH1\_FDLY

| CH1_FDLY | Delay time |

|----------|------------|

| 0        | 4ms        |

| 1        | 2ms        |

FSQ\_SEL Setting the rising order of CH3 and CH4 output.

### Table 8.11 FSQ\_SEL

| FSQ_SEL | Falling order |

|---------|---------------|

| 0       | CH3⇒CH4       |

| 1       | CH4⇒CH3       |

## <u>TOSHIBA</u>

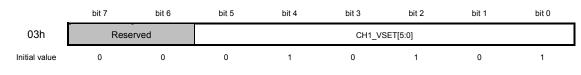

### 8.3.4 Setting VOUT1 (03h)

CH1\_VSET [5:0] : Setting VOUT1.

|                   |          |                   |          | _                 |          |                   |                      |

|-------------------|----------|-------------------|----------|-------------------|----------|-------------------|----------------------|

| CH1_VSET<br>[5:0] | VOUT1[V] | CH1_VSET<br>[5:0] | VOUT1[V] | CH1_VSET<br>[5:0] | VOUT1[V] | CH1_VSET<br>[5:0] | VOUT1[V]             |

| 000000            | 5.0      | 010000            | 8.2      | 100000            | 11.4     | 110000            | 14.6                 |

| 000001            | 5.2      | 010001            | 8.4      | 100001            | 11.6     | 110001            | 14.8                 |

| 000010            | 5.4      | 010010            | 8.6      | 100010            | 11.8     | 110010            | 15.0                 |

| 000011            | 5.6      | 010011            | 8.8      | 100011            | 12.0     | 110011            |                      |

| 000100            | 5.8      | 010100            | 9.0      | 100100            | 12.2     | 110100            |                      |

| 000101            | 6.0      | 010101            | 9.2      | 100101            | 12.4     | 110101            |                      |

| 000110            | 6.2      | 010110            | 9.4      | 100110            | 12.6     | 110110            |                      |

| 000111            | 6.4      | 010111            | 9.6      | 100111            | 12.8     | 110111            |                      |

| 001000            | 6.6      | 011000            | 9.8      | 101000            | 13.0     | 111000            |                      |

| 001001            | 6.8      | 011001            | 10.0     | 101001            | 13.2     | 111001            | Setting<br>forbidden |

| 001010            | 7.0      | 011010            | 10.2     | 101010            | 13.4     | 111010            |                      |

| 001011            | 7.2      | 011011            | 10.4     | 101011            | 13.6     | 111011            |                      |

| 001100            | 7.4      | 011100            | 10.6     | 101100            | 13.8     | 111100            |                      |

| 001101            | 7.6      | 011101            | 10.8     | 101101            | 14.0     | 111101            |                      |

| 001110            | 7.8      | 011110            | 11.0     | 101110            | 14.2     | 111110            |                      |

| 001111            | 8.0      | 011111            | 11.2     | 101111            | 14.4     | 111111            |                      |

### Table 8.12 CH1\_VSET

Note: bit7,bit6: Fix to "0".

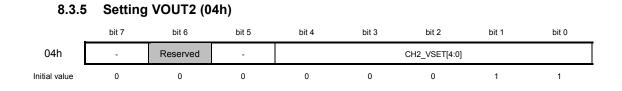

CH2\_VSET [4:0] : Setting VOUT2. (Note1)

### Table 8.13 CH2\_VSET

| CH2_VSET[4:0] | VOUT2[V] | CH2_VSET[4:0] | VOUT2[V]          |

|---------------|----------|---------------|-------------------|

| 00000         | 3.0      | 10000         | 4.6               |

| 00001         | 3.1      | 10001         | 4.7               |

| 00010         | 3.2      | 10010         | 4.8               |

| 00011         | 3.3      | 10011         | 4.9               |

| 00100         | 3.4      | 10100         | 5.0               |

| 00101         | 3.5      | 10101         |                   |

| 00110         | 3.6      | 10110         |                   |

| 00111         | 3.7      | 10111         |                   |

| 01000         | 3.8      | 11000         |                   |

| 01001         | 3.9      | 11001         |                   |

| 01010         | 4.0      | 11010         | Setting forbidden |

| 01011         | 4.1      | 11011         | -                 |

| 01100         | 4.2      | 11100         |                   |

| 01101         | 4.3      | 11101         | ]                 |

| 01110         | 4.4      | 11110         | ]                 |

| 01111         | 4.5      | 11111         | ]                 |

Note 1: Setting range of VOUT2: VOUT2 < V<sub>IN</sub> × 0.75

(It is the reference value because it depends on the conditions and external parts. Please confirm the operation in the actual operation conditions.)

Note: bit6: Fix to "0".

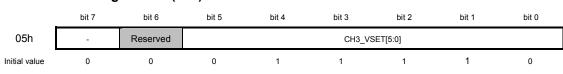

### 8.3.6 Setting VOUT3 (05h)

CH3\_VSET [5:0] : Setting VOUT3. (Note1)

### Table 8.14 CH3\_VSET

| CH3_VSET<br>[5:0] | VOUT3[V]  | CH3_VSET<br>[5:0] | VOUT3[V] | CH3_VSET<br>[5:0] | VOUT3[V] | CH3_VSET<br>[5:0] | VOUT3[V]             |

|-------------------|-----------|-------------------|----------|-------------------|----------|-------------------|----------------------|

| 000000            |           | 010000            | 15.2     | 100000            | 18.4     | 110000            | 21.6                 |

| 000001            |           | 010001            | 15.4     | 100001            | 18.6     | 110001            | 21.8                 |

| 000010            |           | 010010            | 15.6     | 100010            | 18.8     | 110010            | 22.0                 |

| 000011            |           | 010011            | 15.8     | 100011            | 19.0     | 110011            |                      |

| 000100            | Setting   | 010100            | 16.0     | 100100            | 19.2     | 110100            |                      |

| 000101            | forbidden | 010101            | 16.2     | 100101            | 19.4     | 110101            |                      |

| 000110            |           | 010110            | 16.4     | 100110            | 19.6     | 110110            |                      |

| 000111            |           | 010111            | 16.6     | 100111            | 19.8     | 110111            |                      |

| 001000            |           | 011000            | 16.8     | 101000            | 20.0     | 111000            |                      |

| 001001            |           | 011001            | 17.0     | 101001            | 20.2     | 111001            | Setting<br>forbidden |

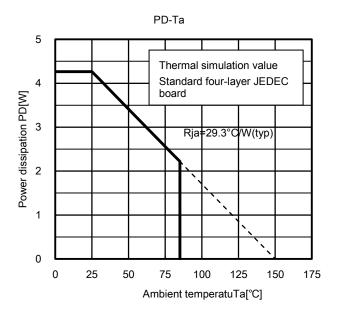

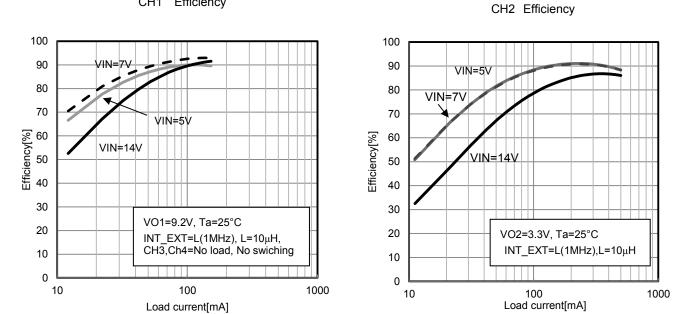

| 001010            | 14.0      | 011010            | 17.2     | 101010            | 20.4     | 111010            |                      |