32 ビット RISC マイクロコントローラ TX04 シリーズ

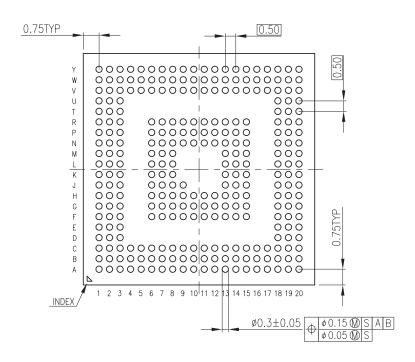

TMPM440FE/F10XBG

株式会社 **東芝** セミコンダクター & ストレージ社

#### お客様各位

2021-9-1

東芝デバイス&ストレージ株式会社 東芝デバイスソリューション株式会社

〒212-8520 神奈川県川崎市幸区堀川町 580-1

Tel: 044-548-2200

Fax: 044-548-8965

#### 非同期シリアル通信機能に関する誤記について

平素より東芝マイクロコントローラーをご使用頂き、誠にありがとうございます。

弊社マイコンに内蔵されております非同期シリアル通信機能(UART、または FUART)、50%デューティーモード付き非同期シリアル通信回路(UART)の送信割り込み発生タイミングで、データシート、リファレンスマニュアルの記載に誤記が発見されました。

大変ご迷惑をおかけ致しますが、本文章をご確認頂きますようお願い申し上げます。

本件のご不明な点につきましては、弊社営業担当までお問い合わせいただきますようお願い申し上げます。

一記一

### 1. 対象製品

| TMPM342FYXBG  | TMPM440FEXBG  | TMPA900CMXBG  |

|---------------|---------------|---------------|

| TMPM343F10XBG | TMPM440F10XBG | TMPA901CMXBG  |

| TMPM343FDXBG  | TMPM461F10FG  | TMPA910CRAXBG |

| TMPM366F20AFG | TMPM461F15FG  | TMPA910CRBXBG |

| TMPM366FWFG   | TMPM462F10FG  | TMPA911CRXBG  |

| TMPM366FYFG   | TMPM462F15FG  | TMPA912CMXBG  |

| TMPM366FDFG   | TMPM46BF10FG  | TMPA913CHXBG  |

| TMPM366FWXBG  | TMPM4G6FDFG   |               |

| TMPM366FYXBG  | TMPM4G6FEFG   |               |

| TMPM366FDXBG  | TMPM4G6F10FG  |               |

| TMPM367FDFG   | TMPM4G7FDFG   |               |

| TMPM367FDXBG  | TMPM4G7FEFG   |               |

| TMPM368FDFG   | TMPM4G7F10FG  |               |

| TMPM368FDXBG  | TMPM4G8FDFG   |               |

| TMPM369FDFG   | TMPM4G8FDXBG  |               |

| TMPM369FDXBG  | TMPM4G8FEFG   |               |

| TMPM36BF10FG  | TMPM4G8FEXBG  |               |

| TMPM36BFYFG   | TMPM4G8F10FG  |               |

| TMPM381FWDFG  | TMPM4G8F10XBG |               |

| TMPM381FWFG   | TMPM4G8F15FG  |               |

| TMPM383FSEFG  | TMPM4G8F15XBG |               |

| TMPM383FSUG   | TMPM4G9FDFG   |               |

| TMPM383FWEFG  | TMPM4G9FDXBG  |               |

| TMPM383FWUG   | TMPM4G9FEFG   |               |

| TMPM3V4FSEFG  | TMPM4G9FEXBG  |               |

| TMPM3V4FSUG   | TMPM4G9F10FG  |               |

| TMPM3V4FWEFG  | TMPM4G9F10XBG |               |

| TMPM3V4FWUG   | TMPM4G9F15FG  |               |

| TMPM3V6FWDFG  | TMPM4G9F15XBG |               |

| TMPM3V6FWFG   |               |               |

|               |               |               |

### 2. 詳細

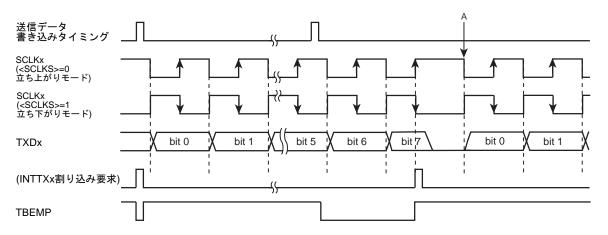

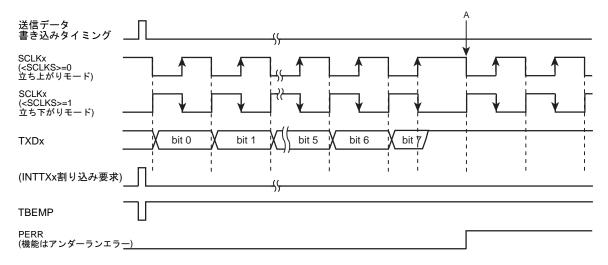

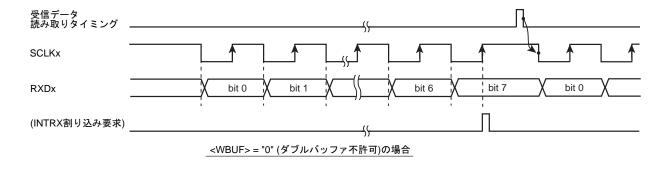

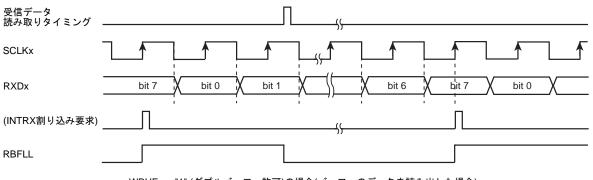

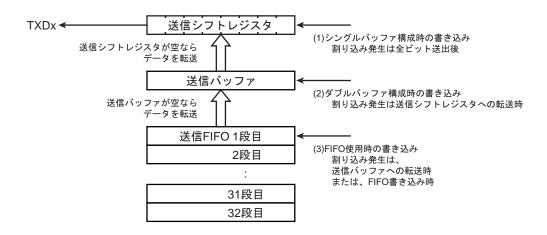

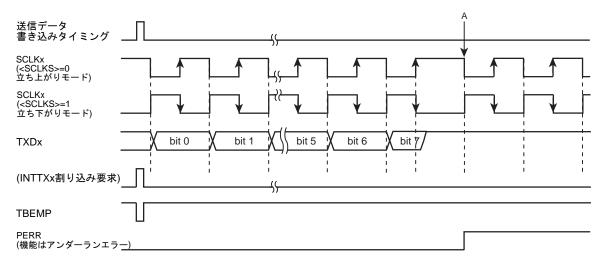

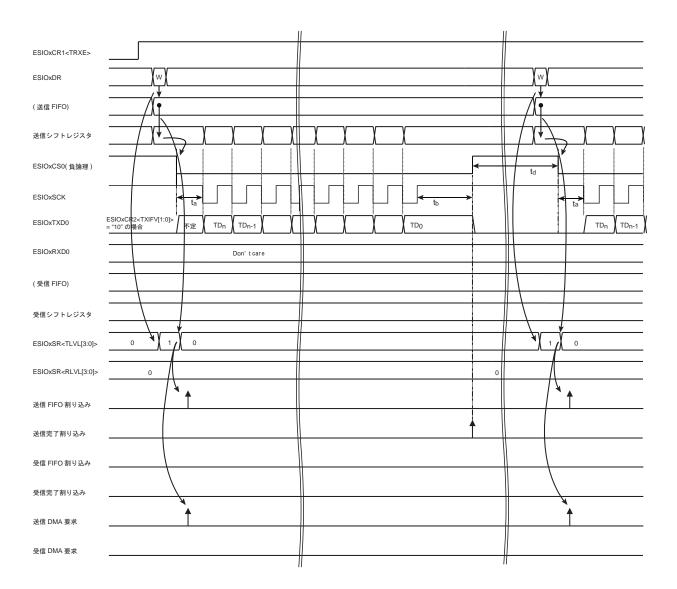

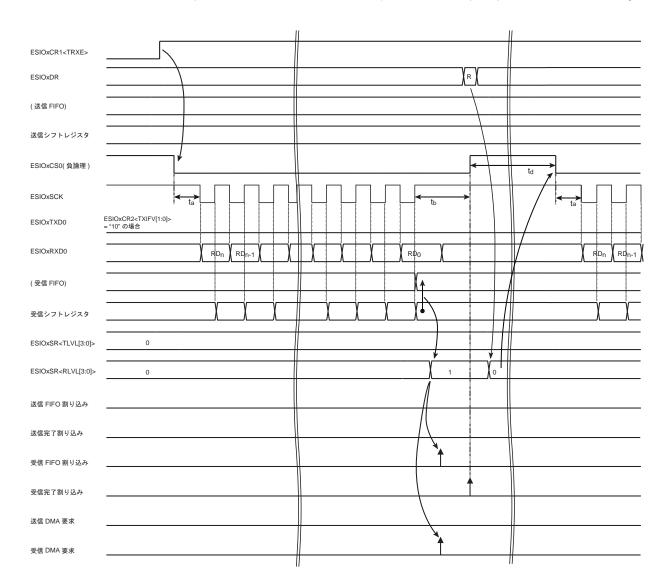

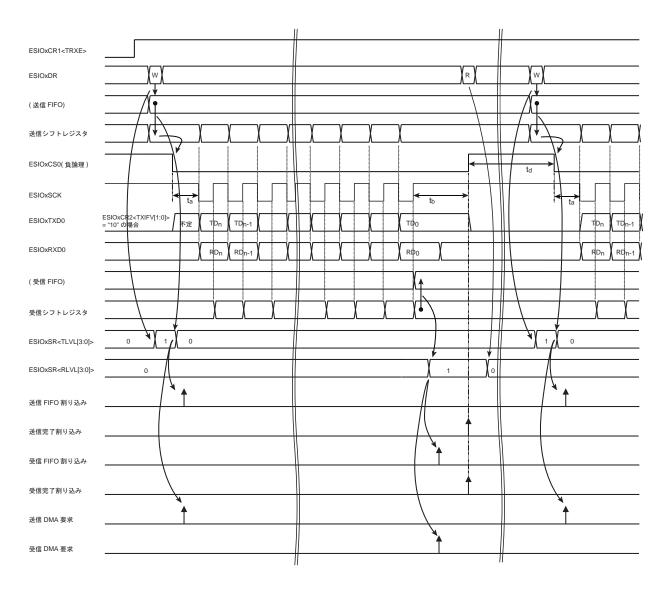

送信割り込みの発生タイミングは以下となります。

なお、送信割り込み発生タイミング誤記につきましては"送信 FIFO 未使用時"に限られ、"送信 FIFO 使用時"ではデータシートの記載のとおりとなります。

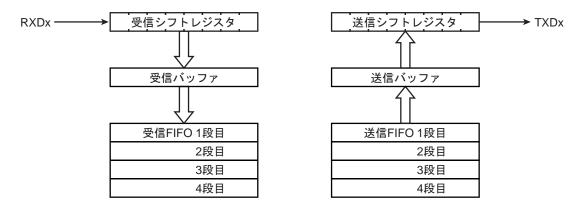

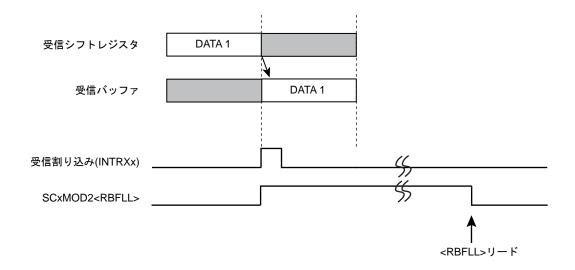

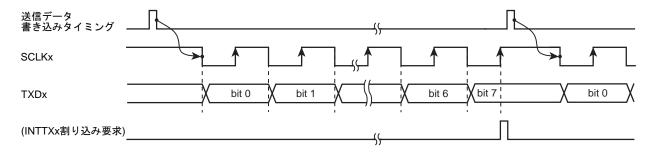

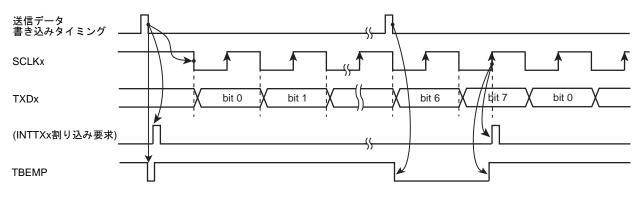

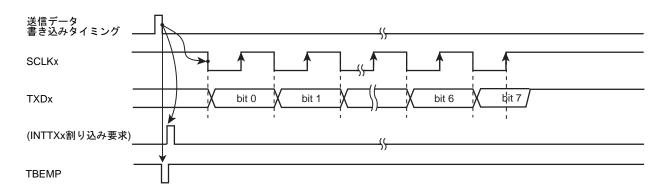

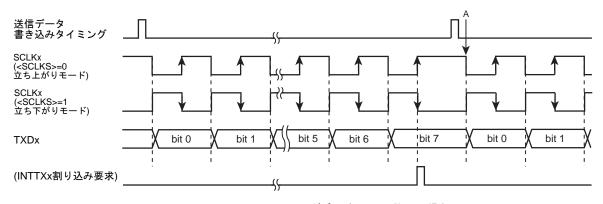

### 2.1. 送信 FIFO 未使用時

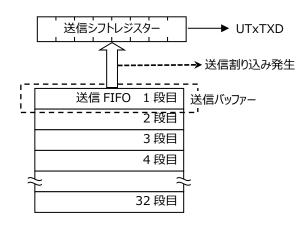

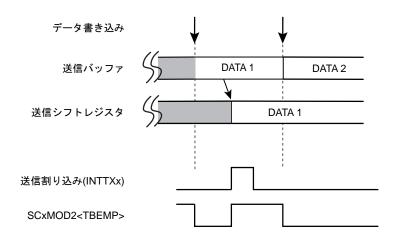

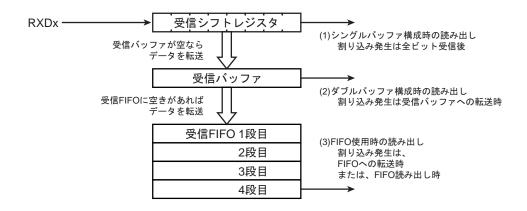

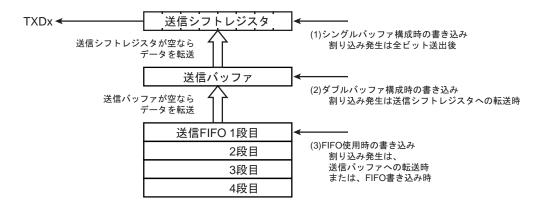

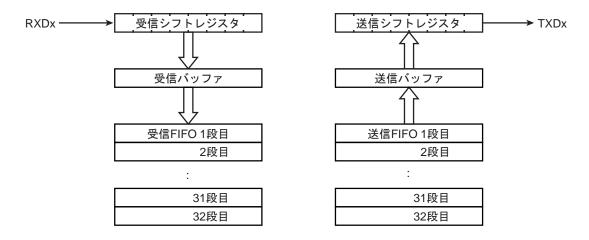

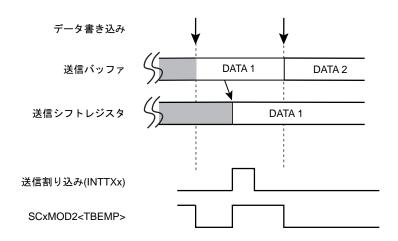

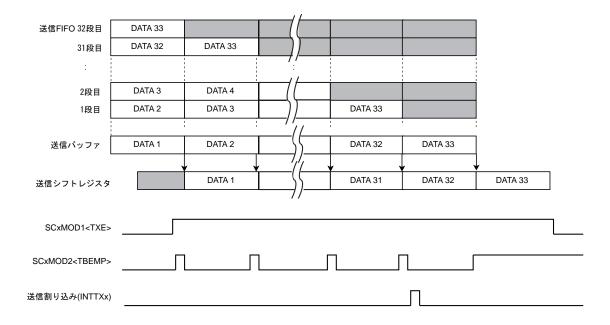

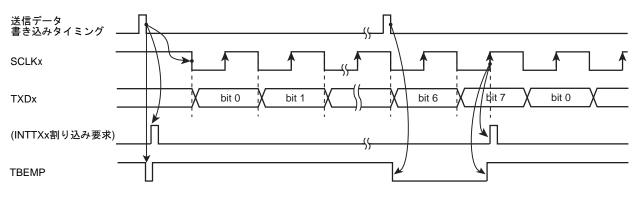

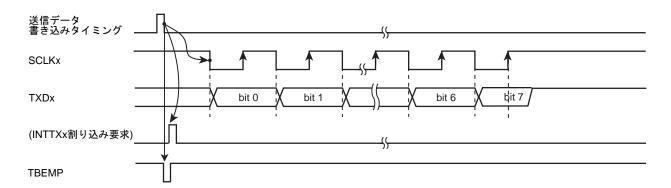

送信バッファー(送信 FIFO 1 段目)から送信シフトレジスターにデータが転送されたときに(送信バッファーに空きができたとき)送信割り込みが発生します。

### 2.1.1. 送信割り込み発生タイミング

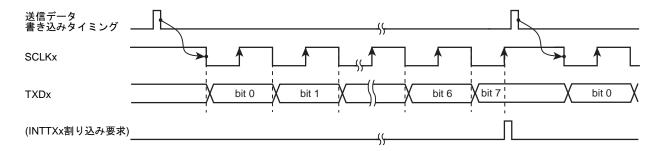

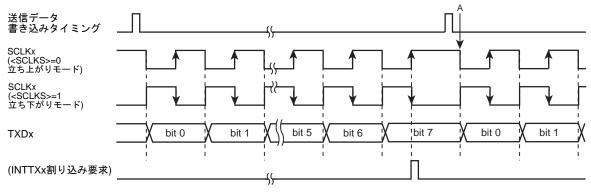

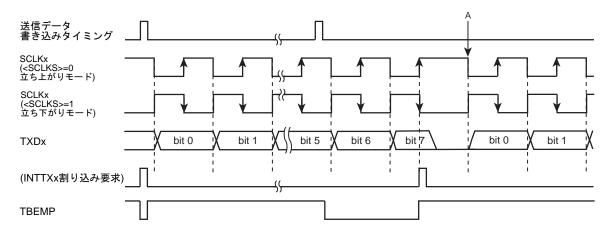

送信 FIFO 未使用時の送信割り込みは、次データに対する送信バッファーへの書き込みタイミングを通知するため、送信バッファーが空になったタイミングで発生します。送信割り込みは送信バッファーに次のデータが書き込まれると自動的にクリアされるため、連続的にデータを送信し続ける場合はソフトウェアによる送信割り込みのクリアは必要ありません(UARTxICR<TXIC>="1"設定)。

また、送信を終了する場合は、最終送信データがシフトレジスターに転送され、送信バッファーが空になった際に最後の送信割り込みが発生します。送信バッファーに次のデータを書き込まない場合は、割り込みハンドラー内でソフトウェアによる割り込みクリア(UARTxICR<TXIC> = "1"設定)を実行することで送信割り込みを意図的にクリアすることができます。

なお、データ送信中にソフトウェアで送信割り込みクリア(UARTxICR<TXIC> = "1"設定)を実行した場合、送信完了時の STOP ビット発生と同時のタイミングで送信バッファーにデータの書き込みを行うと、送信割り込みは発生しません。確実に送信割り込みを発生させる場合は、データ送信中にソフトウェアで送信割り込みをクリアしないで送信バッファーにデータを書き込むか、送信が停止している状態(UARTxFR<BUSY> = "0"のとき)で送信バッファーにデータを書き込んでください。

連続してデータを送信する場合は、次項の送信 FIFO を利用したデータ転送を推奨致します。

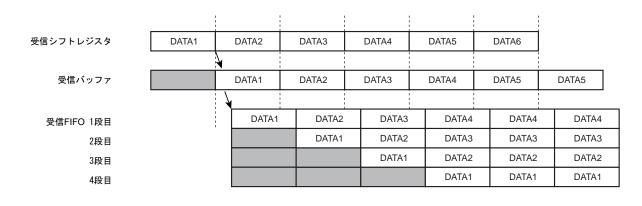

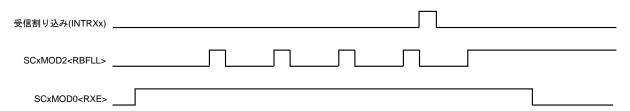

### 2.2. 送信 FIFO 使用時

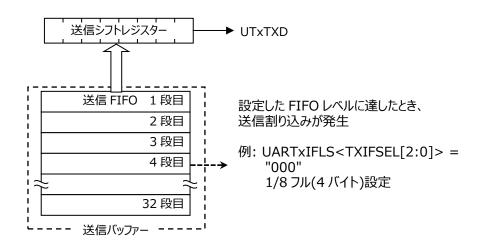

送信動作により送信 FIFO の格納段数が UARTxIFLS<TXIFSEL[2:0]>であらかじめ設定した FIFO レベルに達すると送信割り込みが発生します。

### 2.2.1. 送信割り込み発生タイミング

送信 FIFO 使用時は、設定した FIFO レベルに達したときに送信割り込み発生します。

例えば、UARTxIFLS<TXIFSEL[2:0]> = "000" (1/8 フル 4 バイト設定)の場合、送信 FIFO に格納されたデータが 4 段目に達したときに送信割り込みが発生します。

送信割り込みは設定した FIFO レベルを超えるデータが送信 FIFO に格納されるとクリアされ、設定した FIFO レベルに達すると再度発生します。

### 3. 誤記内容

製品により送信割り込み発生タイミングの記載内容が異なり、各製品に対する誤記掲載箇所の章番号を以下表に示します。なお、送信割り込み発生タイミング誤記につきましては"送信 FIFO 未使用時"に限られ、"送信 FIFO 使用時"ではデータシートの記載のとおりとなります。

誤記に対する修正、追記内容は、以降の「4. 誤記修正・追記内容」で説明し、全ての対象製品で共通の記載内容となります。

### 3.1. 記載タイプ A

### 3.1.1. 対象製品と対象箇所の章番号

| 製品名                                                                                          | 記載箇所章番号      |

|----------------------------------------------------------------------------------------------|--------------|

| TMPM342FYXBG                                                                                 | 16.4.7       |

| TMPM366F20AFG(注)                                                                             | 15.4.7       |

| TMPM366FWFG、TMPM366FYFG、TMPM366FDFG、TMPM366FWXBG、TMPM366FYXBG、TMPM366FDXBG                   | 16.4.7       |

| TMPM367FDFG、TMPM367FDXBG、TMPM368FDFG、TMPM368FDXBG、TMPM369FDFG、TMPM369FDXBG                   | 13.4.7       |

| TMPM36BFYFG、TMPM36BF10FG                                                                     | 13.4.7       |

| TMPA900CMXBG、TMPA901CMXBG、TMPA910CRAXBG、TMPA910CRBXBG、TMPA911CRXBG、TMPA912CMXBG、TMPA913CHXBG | 3.13.1.1 (7) |

注) 非同期シリアル通信機能(UART)章です。

#### タイプ A

修正が必要な記載箇所(赤枠)

| 割り込み種類       | 割り込み発生タイミング                             |

|--------------|-----------------------------------------|

| オーバーランエラー発生  | 過剰データの STOP ビット受信後                      |

| ブレークエラー 割り込み | STOP ビット受信後                             |

| パリティエラー 発生   | パリティデータ受信後                              |

| フレーミングエラー発生  | フレームオーバーとなる Bit データを受信した後               |

| 受信タイムアウト割り込み | 受信 FIFO にデータを取り込んでから、Baud16 の 511 クロック後 |

| 送信割り込み       | 最終 DATA (MSB データ)を送信した後                 |

| 受信割り込み       | STOP ビット受信後                             |

# 3.2. 記載タイプ B(1)

### 3.2.1. 対象製品と対象箇所の章番号

| 製品名                                                 | 記載箇所章番号  |

|-----------------------------------------------------|----------|

| TMPM461F10FG、TMPM461F15FG、TMPM462F10FG、TMPM462F15FG | 14.4.6.2 |

| イプ B(1)<br>正が必要な記載箇所( | (赤枠)        |                                                                                                             |  |  |

|-----------------------|-------------|-------------------------------------------------------------------------------------------------------------|--|--|

| 割り込み種類                | (93.11)     | 割り込み発生タイミング                                                                                                 |  |  |

| オーバランエラー割り込み          | FIFO がフルになっ | ったときの STOP ビット受信後                                                                                           |  |  |

| ブレークエラー割り込み           | STOP ビット受信  | 後                                                                                                           |  |  |

| パリティエラー割り込み           | パリティデータ受    | 信後                                                                                                          |  |  |

| フレーミングエラー割り込み         | フレームオーバと    | フレームオーバとなる Bit データを受信した後                                                                                    |  |  |

| 受信タイムアウト割り込み          | 受信 FIFO にデー | 受信 FIFO にデータを取り込んでから、Baud16 の 511 クロック後                                                                     |  |  |

| 送信割り込み                | FIFO 未使用時:  | 送信許可後、1パイト目はSTARTビット送信開始時とSTOPビット<br>送信開始時、2パイト目以降は、STOPビット送信開始時<br>(それぞれの割り込み発生でデータ書き込みを行い割り込みクリアした<br>場合) |  |  |

|                       | FIFO 使用時:   | STOP ビット送信開始時(MSB データ転送後)に FIFO 内が設定された FIFO レベルのデータ数となったとき                                                 |  |  |

|                       | FIFO 未使用時:  | STOP ビット受信後                                                                                                 |  |  |

| 受信割り込み                | FIFO 使用時:   | 設定した FIFO がフルとなるでーたの STOP ビット受信後                                                                            |  |  |

### 3.3. 記載タイプ B(2)

### 3.3.1. 対象製品と対象箇所の章番号

| 製品名                                                                                                                                                      | 記載箇所章番号  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| TMPM343FDXBG、TMPM343F10XBG、TMPM366F20AFG(注)                                                                                                              | 16.4.6.2 |

| TMPM381FWFG、TMPM381FWDFG、 TMPM383FSUG、TMPM383FSEFG、TMPM383FWUG、TMPM383FWEFG、 TMPM3V4FSUG、TMPM3V4FSEFG、TMPM3V4FWUG、TMPM3V4FWEFG、 TMPM3V6FWFG、TMPM3V6FWDFG | 11.4.6.2 |

| TMPM440FEXBG、TMPM440F10XBG                                                                                                                               | 26.4.6.2 |

注) 50%デューティーモード付き非同期シリアル通信回路(UART)章です。

#### タイプ B(2) 修正が必要な記載箇所(赤枠) 割り込み種類 割り込み発生タイミング オーバランエラー発生 FIFO がフルになった時の STOP ビット受信後 ブレークエラー 割り込み STOP ビット受信後 パリティデータ受信後 パリティエラー 発生 フレームオーバとなる Bit データを受信した後 フレーミングエラー発生 受信 FIFO にデータを取り込んでから、Baud16 の 511 クロック後 受信タイムアウト割り込み FIFO 未使用時: 送信許可設定後、1 バイト目は START ビット送信開始時と STOP ビット送信開始時と STOP ビット送信開始時 (それぞれの割り込み発生でデータ書き込みを行い割り込みクリアした 場合) 送信割り込み STOP ビット送信開始時(MSB データ転送後)に FIFO 内が設定された FIFO レベルのデータ数となった時 FIFO 使用時: FIFO 未使用時: STOP ビット受信後 受信割り込み FIFO 使用時: 設定した FIFO レベルがフルとなるデータの STOP ビット受信後

### 3.4. 記載タイプ B(3)

### 3.4.1. 対象製品と対象箇所の章番号

| 製品名                                                  | 記載箇所章番号        |

|------------------------------------------------------|----------------|

| TMPM4G6FDFG、TMPM4G6FEFG、TMPM4G6F10FG、TMPM4G7FDFG、    |                |

| TMPM4G7FEFG、TMPM4G7F10FG、TMPM4G8FDFG、TMPM4G8FDXBG、   | リファレンスマニュアル(注) |

| TMPM4G8FEFG、TMPM4G8FEXBG、TMPM4G8F10FG、TMPM4G8F10XBG、 | 高精度非同期シリアル通信   |

| TMPM4G8F15FG、TMPM4G8F15XBG、TMPM4G9FDFG、TMPM4G9FDXBG、 | 回路(FUART-B)    |

| TMPM4G9FEFG、TMPM4G9FEXBG、TMPM4G9F10FG、TMPM4G9F10XBG、 | 3.8.2          |

| TMPM4G9F15FG、TMPM4G9F15XB                            |                |

注)本文章の UARTxIFLS を*[FURTxIFLS]*に、UARTxICR を*[FURTxICR]*に、UARTxFR を *[FURTxFR]*に読み替えてください。

#### タイプ B(3) 修正が必要な記載箇所(赤枠) 割り込み種類 割り込み発生タイミング オーバランエラー発生 FIFO がフルになったときの STOP ビット受信後 ブレークエラー割り込み STOP ビット受信後 パリティエラー発生 パリティデータ受信後 フレーミングエラー発生 フレームオーバとなる Bit データを受信した後 受信タイムアウト割り込み 受信 FIFO にデータを取り込んでから、転送クロックの 511 クロック後 1 バイト保持レジスタ時(FIFO 未使用時) 送信許可設定後、1 バイト目は START ビット送信開始時と STOP ビット送 信開始時、2 バイト目以降は、STOP ビット送信開始時(それぞれの割り込み 発生でデータ書き込みを行い割り込みクリアした場合) 送信割り込み STOP ビット送信開始時(MSB データ転送後)に FIFO 内が設定された FIFO レベルのデータ数となったとき 1 バイト保持レジスタ時(FIFO 未使用時) STOP ビット受信後 受信割り込み FIFO 使用時 設定した FIFO レベルがフルとなるデータの STOP ビット受信後

# 3.5. 記載タイプ C

### 3.5.1. 対象製品と対象箇所の章番号

| 製品名          | TD 記載箇所章番号 |

|--------------|------------|

| TMPM46BF10FG | 19.4.6.2   |

| タイプ C          |                                         |

|----------------|-----------------------------------------|

| 修正が必要な記載箇所(赤枠) |                                         |

| 割り込み種類         | 割り込み発生タイミング                             |

| オーバーランエラー割り込み  | FIFO がフルになった時の STOP ビット受信後              |

| ブレークエラー割り込み    | STOP ビット受信後                             |

| パリティエラー割り込み    | パリティデータ受信後                              |

| フレーミングエラー割り込み  | フレームオーバーとなる Bit データを受信した後               |

| 受信タイムアウト割り込み   | 受信 FIFO にデータを取り込んでから、Baud16 の 511 クロック後 |

| 送信割り込み         | 最終 DATA の MSB データを送信した後                 |

| 受信割り込み         | STOP ビット受信後                             |

### 4. 誤記修正・追記内容

製品により送信割り込みの割り込み発生タイミングの記載が異なりますが、共通して正しい記載内容 は以下となります。

### 4.1. 送信割り込み発生タイミング

送信 FIFO 未使用時の送信割り込みは、次データに対する送信バッファーへの書き込みタイミングを 通知するため、送信バッファーが空になったタイミングで発生します。送信割り込みは送信バッファー に次のデータが書き込まれると自動的にクリアされるため、連続的にデータを送信し続ける場合はソフトウェアによる送信割り込みのクリアは必要ありません(UARTxICR<TXIC>="1"設定)。

また、送信を終了する場合は、最終送信データがシフトレジスターに転送され、送信バッファーが空になった際に最後の送信割り込みが発生します。送信バッファーに次のデータを書き込まない場合は、割り込みハンドラー内でソフトウェアによる割り込みクリア(UARTxICR<TXIC> = "1"設定)を実行することで送信割り込みを意図的にクリアすることができます。

なお、データ送信中にソフトウェアで送信割り込みクリア(UARTxICR<TXIC> = "1"設定)を実行した場合、送信完了時の STOP ビット発生と同時のタイミングで送信バッファーにデータの書き込みを行うと、送信割り込みは発生しません。確実に送信割り込みを発生させる場合は、データ送信中にソフトウェアで送信割り込みをクリアしないで送信バッファーにデータを書き込むか、送信が停止している状態(UARTxFR<BUSY> = "0"のとき)で送信バッファーにデータを書き込んでください。

以上

ARM, ARM Powered, AMBA, ADK, ARM9TDMI, TDMI, PrimeCell, RealView, Thumb, Cortex, Coresight, ARM9, ARM926EJ-S, Embedded Trace Macrocell, ETM, AHB, APB, and KEIL はARM LimitedのEUおよびその他の国における登録商標または商標です。

### はじめに(本仕様書での SFR 表記に関する注意点)

各周辺機能回路(IP)には、SFR(Special Function Register)と呼ばれる制御レジスタが準備されています。

メモリマップの章に各 IP の SFR アドレス一覧を記載しており、各 IP の章では SFR の詳細を説明しています。

本仕様書では、SFR に関して以下のルールに従って表現しています。

- a. IP 別 SFR の一覧表(一例)

- ・ 各 IP の章における SFR の一覧表では、レジスタ名称、アドレス、簡単な説明が表現されています。

- すべてのレジスタには、32bit で表現されるユニークなアドレスが割り振られており、各レジスタのアドレスは「Base Address + (固有)アドレス」で表現されています。(一部例外有)

Base Address = 0x0000\_0000

| レジスタ名      | Address(Base+) |        |

|------------|----------------|--------|

| コントロールレジスタ | SAMCR          | 0x0004 |

|            |                | 0x000C |

- 注) SAMCR レジスタのアドレスは 0x0000\_0004 番地「Base Address(0x000000000 番地)+固有アドレス(0x0004 番地)」 から 32 ビット分となります。

- 注) 本レジスタは記述説明用のサンプルです。本マイコンには存在しません。

- b. 各 SFR(レジスタ)の説明

- ・ 各レジスタは、基本的にすべて 32bit のレジスタで構成されています(一部例外有)。

- ・ 各レジスタの説明では、対象ビット、ビットシンボル、タイプ、リセット後の初期値、機能 説明が表現されています。

#### 1.2.2 SAMCR(コントロールレジスタ)

|            | 31   | 30    | 29 | 28 | 27 | 26 | 25  | 24  |

|------------|------|-------|----|----|----|----|-----|-----|

| bit symbol | -    | -     | -  | -  | -  | -  |     |     |

| リセット後      | 0    | 0     | 0  | 0  | 0  | 0  | 0 0 |     |

|            | 23   | 22    | 21 | 20 | 19 | 18 | 17  | 16  |

| bit symbol | -    | -     | -  | -  | -  | -  | -   | -   |

| リセット後      | 0    | 0     | 0  | 0  | 0  | 0  | 0   | 0   |

|            | 15   | 14    | 13 | 12 | 11 | 10 | 9   | 8   |

| bit symbol | -    | -     | -  | -  | -  | -  | МС  | DDE |

| リセット後      | 0    | 0     | 0  | 0  | 0  | 0  | 0   | 0   |

|            | 7    | 6     | 5  | 4  | 3  | 2  | 1   | 0   |

| bit symbol | MODE | TDATA |    |    |    |    |     |     |

| リセット後      | 0    | 0     | 0  | 1  | 0  | 0  | 0   | 0   |

| Bit   | Bit Symbol | Туре | 機能                                                                                               |

|-------|------------|------|--------------------------------------------------------------------------------------------------|

| 31-10 | -          | R    | リードすると"0"が読めます。                                                                                  |

| 9-7   | MODE[2:0]  | R/W  | 動作モード設定 000: サンプルモード 0 に設定 001: サンプルモード 1 に設定 010:サンプルモード 2 に設定 011:サンプルモード 3 に設定 上記以外: Reserved |

| 6-0   | TDATA[6:0] | W    | 送信データ                                                                                            |

#### 注) Type は基本的に下記3種類となります。

R / W: READ WRITE 読み出し/書き込み可能 R: READ 読み出しのみ可能 W: WRITE 書き込みのみ可能

c. データ表記について

SFR の説明において使用しているシンボルには以下のようなものがあります。

- · x:チャネル番号/ポート

- · n,m:ビット番号

- d. レジスタの表現

説明文においてレジスタを以下のように表現しています。

・ レジスタ名<Bit Symbol>

例: SAMCR<MODE>="000"または SAMCR<MODE[2:0]>="000" <MODE[2:0]>はビットシンボル MODE(3 ビット幅)の 2~0 ビット目を意味します。

・ レジスタ名[Bit]

例: SAMCR[9:7]="000"

レジスタ SAMCR(32 ビット幅)の 9~7 ビット目を意味します。

| TMPM440FE/F10XBG |

|------------------|

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

# 改訂履歴

| 日付         | 版 | 改訂理由             |  |

|------------|---|------------------|--|

| 2014/08/28 | 1 | First Release    |  |

| 2014/09/09 | 2 | Contents Revised |  |

| 2022/09/30 | 3 | Contents Revised |  |

| 2023/07/14 | 4 | Contents Revised |  |

| 2023/07/31 | 5 | Contents Revised |  |

# 目 次

# はじめに(本仕様書での SFR 表記に関する注意点)

| TMPM440FE/F10XBG                                                                                     |                                         |

|------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1.1 機能概要                                                                                             |                                         |

|                                                                                                      |                                         |

| 1.2 ピン配置図(Top view)                                                                                  |                                         |

| 1.3 ピン名称と機能                                                                                          | 7                                       |

| 1.3.1 ポート順                                                                                           | 7                                       |

| 1.4 電源の種類と供給端子                                                                                       | 23                                      |

|                                                                                                      |                                         |

| 第2章 製品情報                                                                                             |                                         |

| 2.1 各周辺機能の情報                                                                                         | 26                                      |

| 2.1.1 Programmable Servo/Sequence Controller (PSC ver.B)                                             |                                         |

| 2.1.1.1 PSC 起動要因一覧                                                                                   |                                         |

| 2.1.1.2 ダイレクトポート制御機能対応ポート                                                                            |                                         |

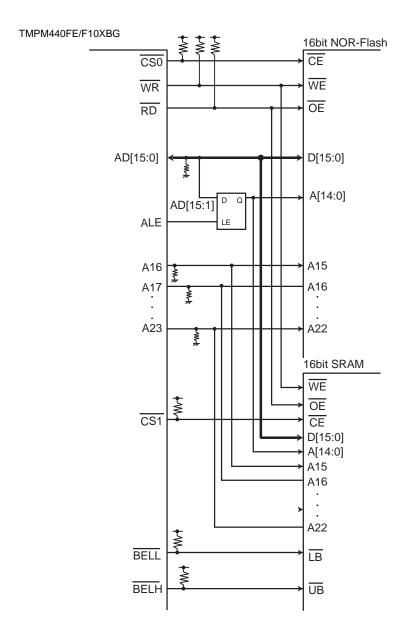

| 2.1.2 外部バスインタフェース(EBIF)                                                                              | 27                                      |

| 2.1.2.1 アドレス、データ端子の設定<br>2.1.3 DMA コントローラ(DMAC)                                                      | 20                                      |

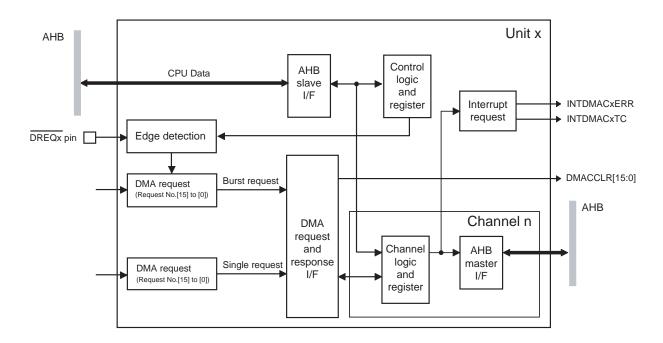

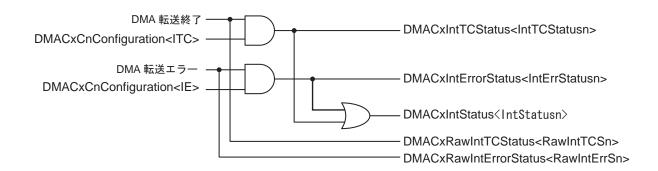

| 2.1.3 DMA コントローフ(DMAC)                                                                               | 28                                      |

| 2.1.3.1 円成ユーット 2.1.3.2 要因一覧表                                                                         |                                         |

| 2.1.3.3 レジスター覧                                                                                       |                                         |

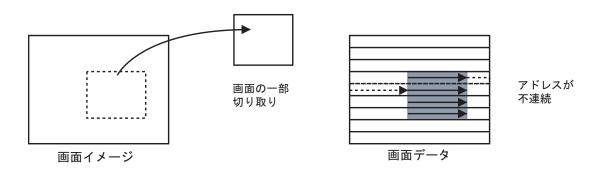

| 2.1.3.4 使用上の注意                                                                                       |                                         |

| 2.1.4 16 ビットタイマ/イベントカウンタ(TMRB)                                                                       | 34                                      |

| 2.1.4.1 内蔵チャネル                                                                                       |                                         |

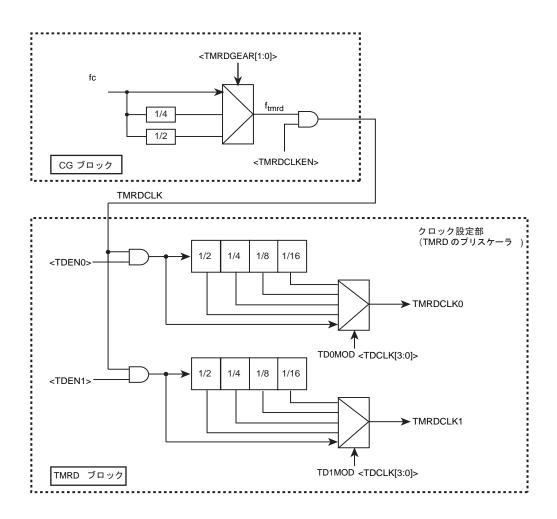

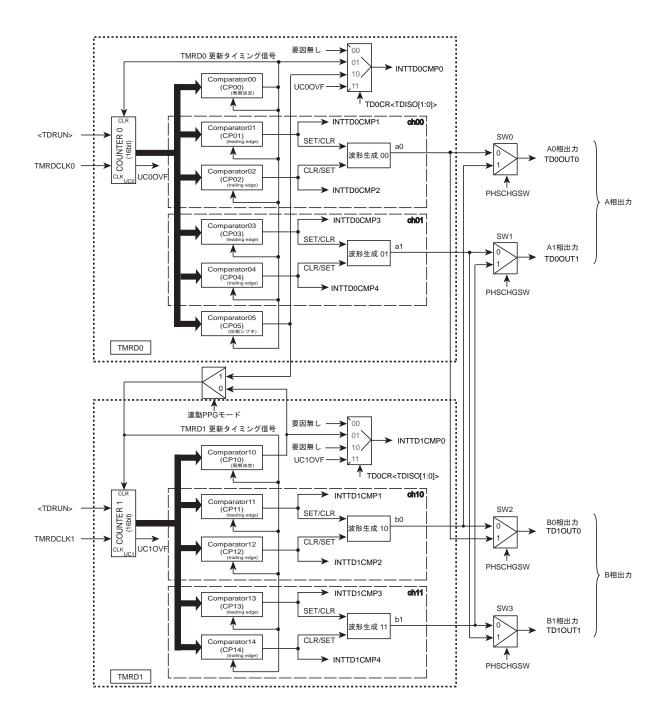

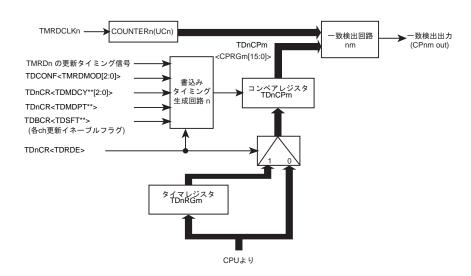

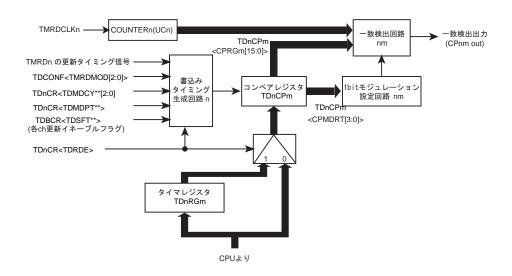

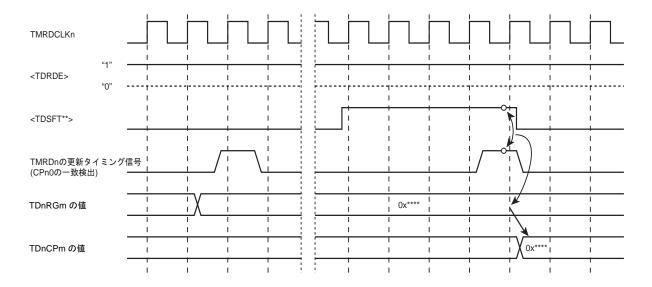

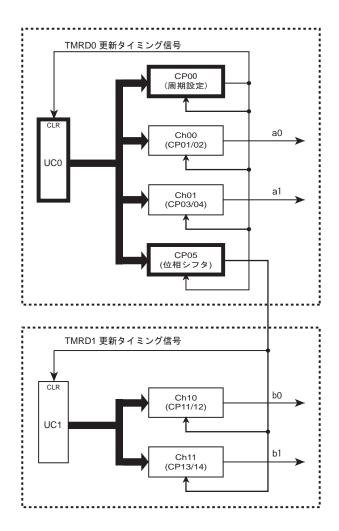

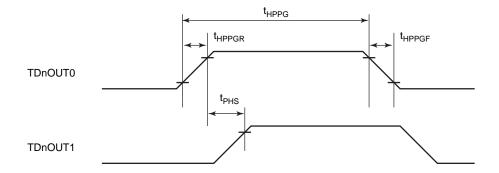

| 2.1.5 高分解能 16 ビットタイマ出力 (TMRD ver.B)                                                                  | 35                                      |

| 2.1.5.1 内蔵ブロック<br>2.1.5.2 コンペアレジスタの設定範囲                                                              |                                         |

| 2.1.5.2 コンペアレンスタの設定範囲 2.1.5.3 レジスタ一覧                                                                 |                                         |

| 2.1.6 32 ビットタイマ (TMRC)                                                                               | 37                                      |

| 2.1.6.1 内蔵ユニット                                                                                       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

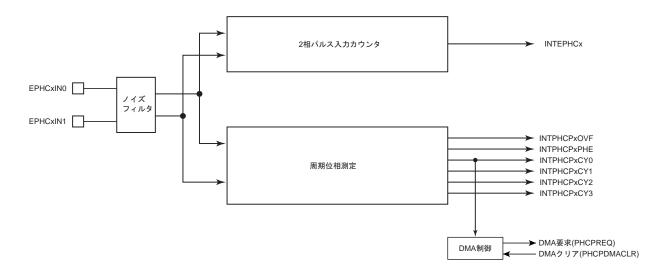

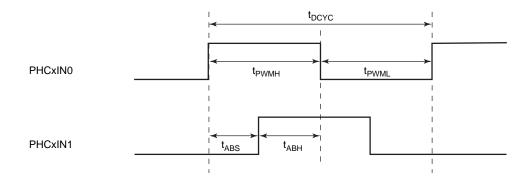

| 2.1.7 2 相パルス入力カウンタ (PHCNT)                                                                           | 37                                      |

| 2.1.7.1 内蔵チャネル                                                                                       |                                         |

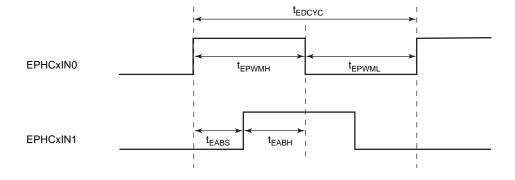

| 2.1.8 高機能 2 相パルス入力カウンタ(EPHC)                                                                         | 38                                      |

| 2.1.8.1 PSC がアクセスするレジスタ                                                                              |                                         |

| 2.1.8.2 EPHCx_PSCADAT(EPHCx16 ビットカウンタリードレジスタ) 2.1.8.3 EPHCx_PSCBUC(EPHCx 24 ビットカウンタリードレジスタ)          |                                         |

| 2.1.8.4 EPHCx PSCBCAP00(EPHCx キャプチャ 00 レジスタ)                                                         |                                         |

| 2.1.8.5 EPHCx PSCBCAP10(EPHCx キャプチャ 10 レジスタ)                                                         |                                         |

| 2.1.8.6 EPHCx_PSCBCAP20(EPHCx キャプチャ 20 レジスタ)                                                         |                                         |

| 2.1.8.7 EPHCx_PSCBCAP30(EPHCx キャプチャ 30 レジスタ)                                                         |                                         |

| 2.1.8.8 EPHCx_PSCB0DAT(EPHCx 周期カウンタ 0 レジスタ)                                                          |                                         |

| 2.1.8.9 EPHCx_PSCB1DAT(EPHCx 周期カウンタ 1 レジスタ)<br>2.1.8.10 EPHCx PSCB2DAT(EPHCx 周期カウンタ 2 レジスタ)          |                                         |

| 2.1.8.11 EPHCx PSCB3DAT(EPHCx 周期カウンタ 3 レジスタ)                                                         |                                         |

| 2.1.8.12 EPHCx_PSCBCDAT(EPHCx 周期カウンタ共通レジスタ)                                                          |                                         |

| 2.1.8.13 EPHCx_PSCB0PDT(EPHCx 位相差 0 レジスタ)                                                            |                                         |

| 2.1.8.14 EPHCx_PSCB1PDT(EPHCx 位相差 1 レジスタ)                                                            |                                         |

| 2.1.8.15 EPHCx_PSCB2PDT(EPHCx 位相差 2 レジスタ)<br>2.1.8.16 EPHCx PSCB3PDT(EPHCx 位相差 3 レジスタ)               |                                         |

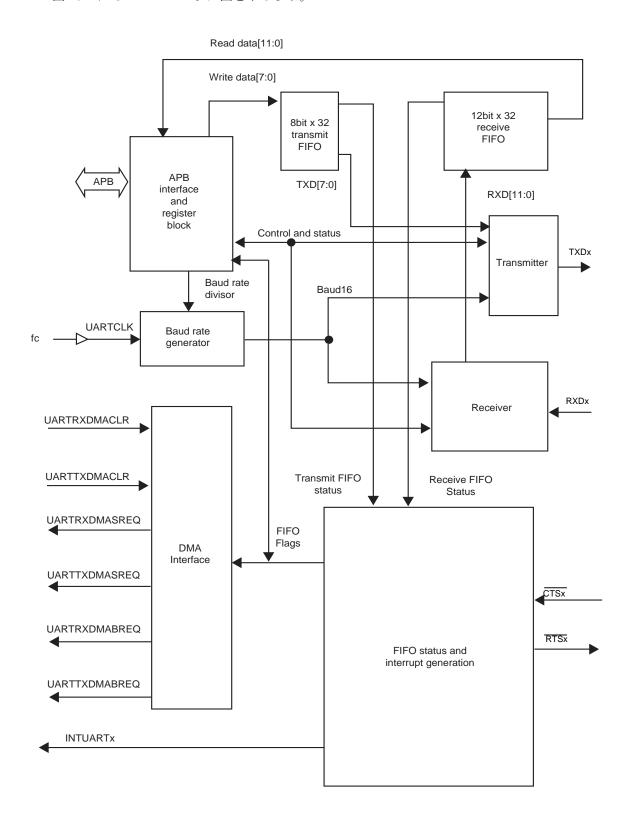

| 2.1.8.16 EPHCx_PSCB3PDT(EPHCx 位相差 3 レジスタ)<br>2.1.9 4 バイト FIFO 付きシリアルチャネル(SIO/UART with 4 bytes FIFO) | 17                                      |

| 2.1.9 4 / ハイド Fire in さ ン ケ ノ ル ケ キ ホル (Sio/OART with 4 bytes Fire)                                  | 4/                                      |

| 2.1.10 32 バイト FIFO 付きシリアルチャネル(SIO/UART with 32 bytes FIFO)                                           | 47                                      |

| 2.1.10.1 内蔵チャネル                                                                                      |                                         |

|                             | アル I/O (ESIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48 |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                             | チャネル<br>/ リアル通信回路(UART)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19 |

|                             | ・ リ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46 |

| 2.1.12.2 使用で                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|                             | バスインタフェース(I2C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49 |

| 2.1.13.1 内蔵チ                | チャネル<br>⁄ ウエイクアップ(KWUP)とキーマトリクススキャン(KSCAN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50 |

| 2.1.14 キーオン<br>2.1.14.1 内蔵コ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50 |

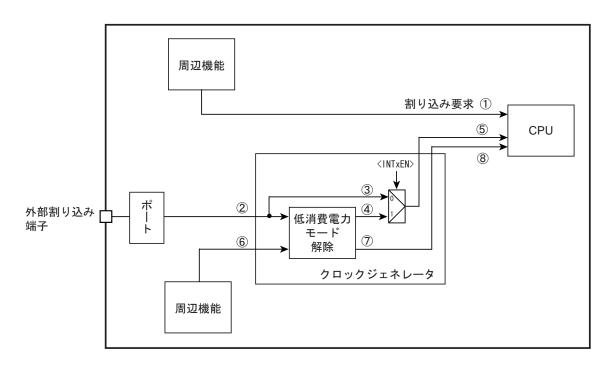

|                             | サ電力モードからの解除                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

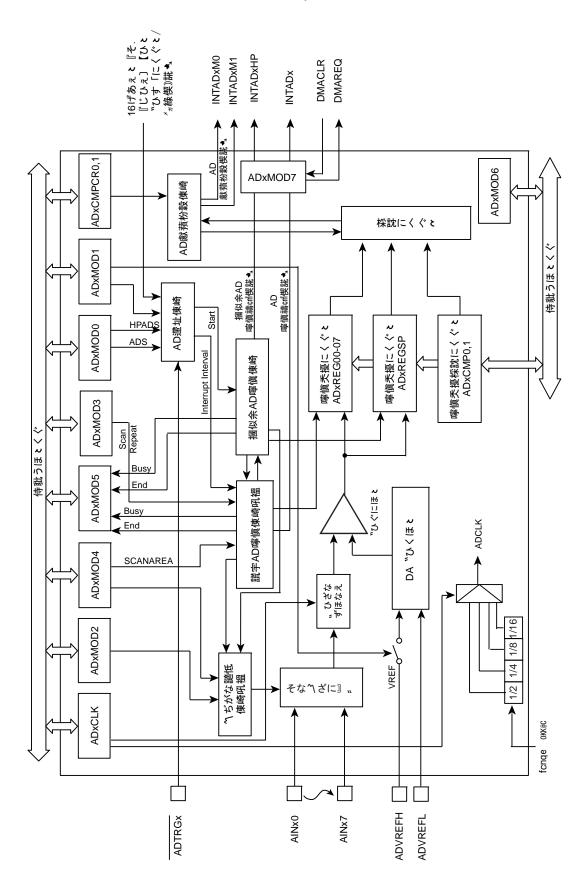

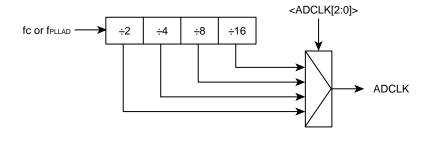

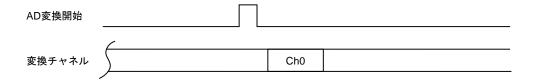

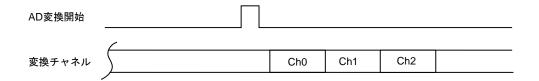

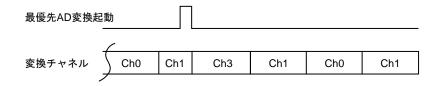

| 2.1.15 アナログ                 | 「デジタルコンバータ(ADC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54 |

|                             | できない機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|                             | ユニット<br>ドアクセスするレジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|                             | PSCREGn(変換結果格納レジスタ、n=00~07)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 2.1.15.5 ADx_F              | PSCREGSP (最優先 AD 変換結果格納レジスタ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

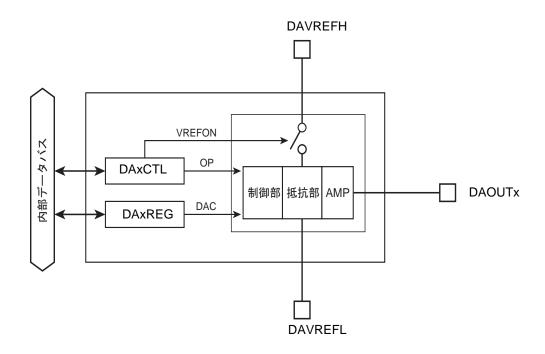

|                             | ンアナログコンバータ(DAC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58 |

|                             | チャネル<br>「インタフェース                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59 |

|                             | ヿックァニ へ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 2.2 户门227效形门                | 町の1女形1目刊                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9  |

| ****                        | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 第3章 プロセッ                    | <u>サコア</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 3.1 コアに関っ                   | する情報                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61 |

|                             | ,<br>なオプション                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|                             | 込み                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|                             | 本数<br>憂先度ビット数                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|                             | 変儿/久 ログ 下数                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |