Bi-CMOS Linear Integrated Circuit Silicon Monolithic

# TB9M003FG

IC for automotive three-phase brushless DC motor

### 1. Description

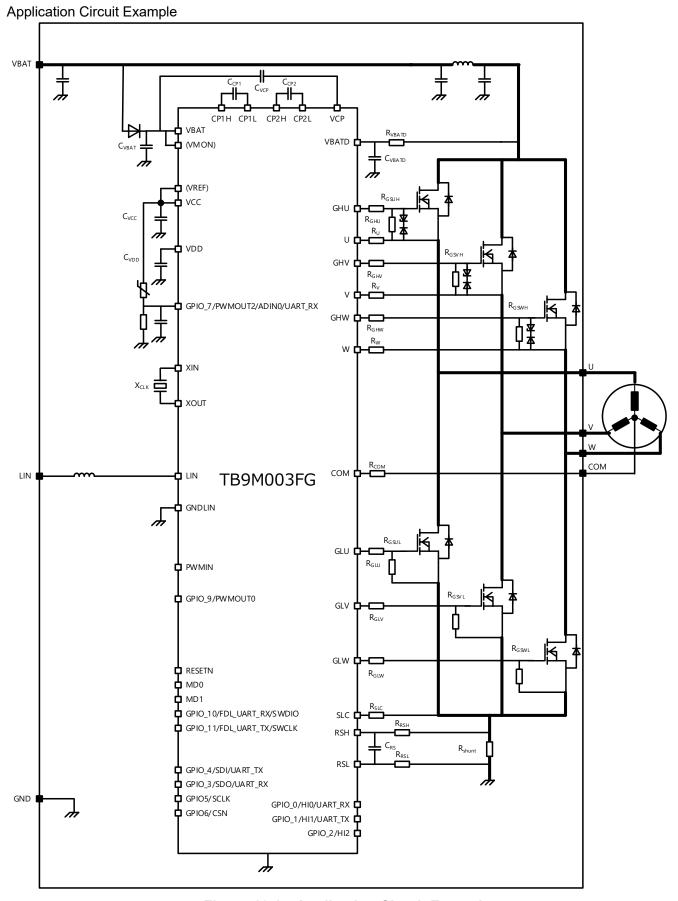

The TB9M003FG is a gate driver IC with a microcontroller unit (MCU) for automotive brushless DC (BLDC) motor applications, which incorporates Toshiba's unique Vector Engine (VE) to simplify motor vector control and offload the CPU.

The TB9M003FG is designed to be used with external N-channel FET pairs, making it suitable for BLDC motors with a wide range of output. The TB9M003FG also incorporates a CPU and a flash ROM, making it possible to program a control method and parameters according to the motor and application requirements. The TB9M003FG can be configured to transition to Standby mode in the idle state in order to reduce power consumption.

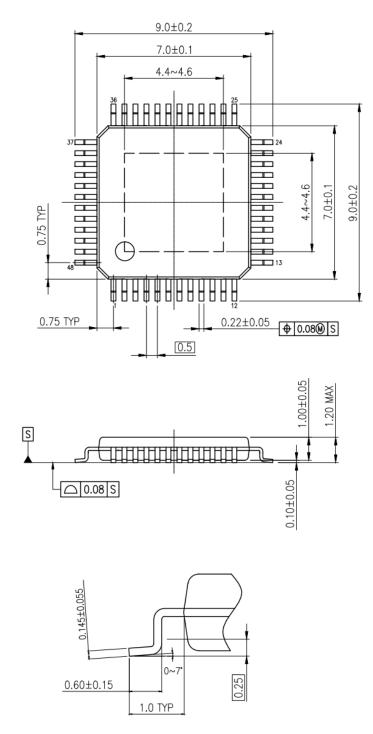

weight: 0.14 g (typ.)

### 2. Applications

For automotive (electric pumps and fans), three-phase brushless motor control and drive.

#### 3. Features

- Integrated MCU and gate drivers enable downsizing of the system

- Built-in vector engine for our original sensorless control

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

\* Arm and Cortex are registered trademarks of Arm Limited (or its subsidiary) in the US and/or elsewhere.

arm

Start of commercial production 2024-01

#### 4. Functions

- 32 bit Arm® Cortex®-M0 core

- Serial Wire Debug Support

- 32ch Interrupt Controller1 cycle multiplier

- Up to 40 MHz clock frequency

- Single Bus Master System

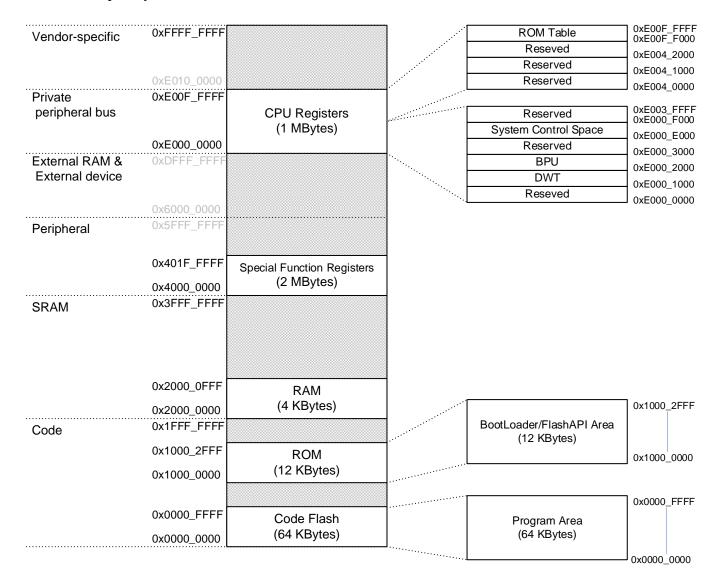

- 12 KBytes ROM(BootLoader, Flash API) (incECC SEC/DED)

- 64 KBytes Code Flash(incl. ECC SEC/DED)

- 4 KBytes SRAM (incl. ECC SEC/DED)

- 32-bit Compare Timers (DTIMER)

- 28-bit Capture Timer (8 inputs, 6 measurement)

- Watchdog Timer(WATCHDOG)

- Power saving modes (CPU Sleep, Standby)

- 4ch Pulse Width Modulator Generator(PWMGEN)

- 12 General-purpose I/O Ports (GPIO)

- 10-bit A/D Converter (GADC) with 2 analog inputs + internal temperature, VMON

- 12-bit A/D Converter (MADC)

- Vector Engine(VE)

- Programmable Motor Driver(PMD)

- Encoder(ENC)

- LDOs (LDO5V, LDO15V)

- Power On Reset (POR5V, PORL)

- 2 on-chip OSCs (IOSCH, IOSCL)

- External X'tal OSC

- PLL

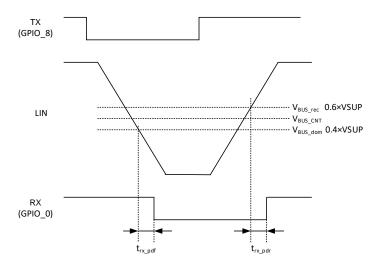

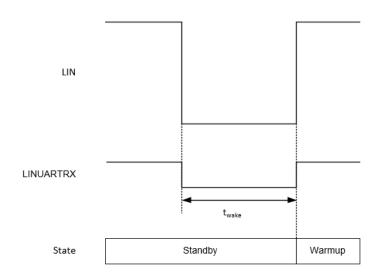

- LIN ISO17987/SAEJ2602 transceiver + controller

- 2 full duplex serial interfaces (UART1, UART2), UART1 with LIN support

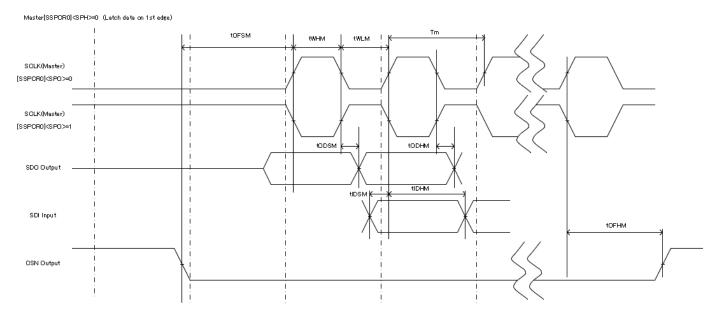

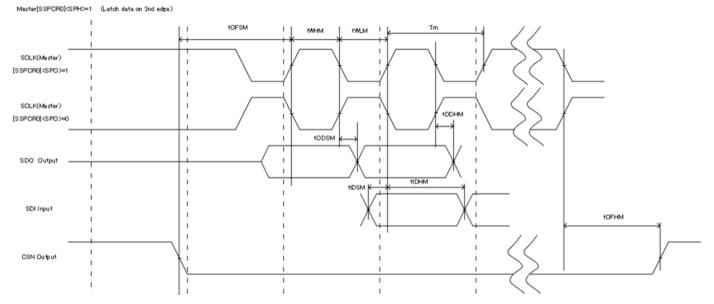

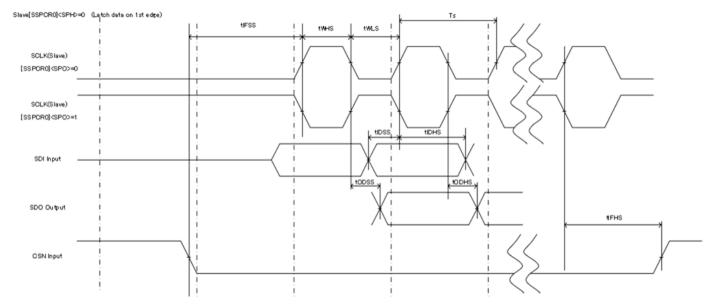

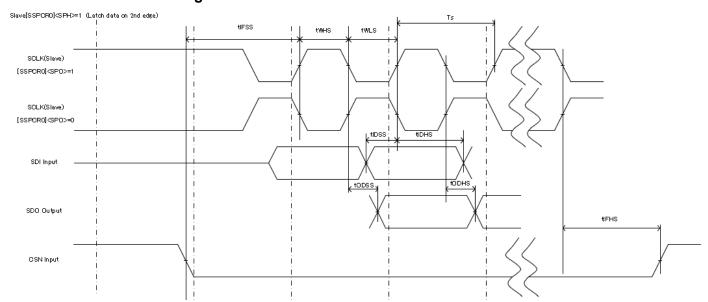

- SPI-I/F

- MOSFET driver including charge pump

- High-speed operational amplifier for motor current sensing via shunt

- Over current protection (LDO, MOSFET driver)

- Over temperature protection

- Package HTQFP48-0707-0.50

- Single power supply from 6.0V to 18V

- Temperature Range  $T_i = -40$ °C to +175°C

- Green package (RoHS compliant)

- AEC-Q100 grade 0 qualified

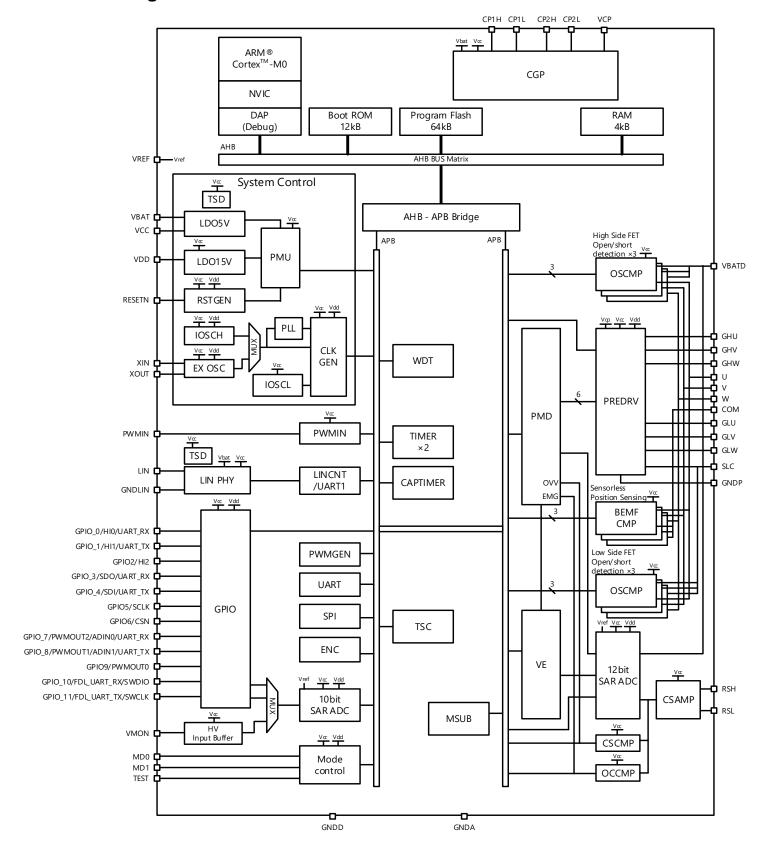

# 5. Block Diagram

Figure 5.1 Block Diagram

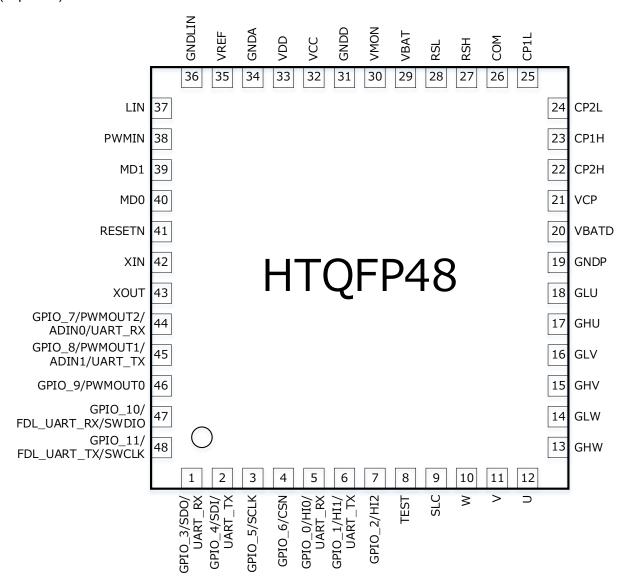

### 6. Pin Assignments

(Top view)

Figure 6.1 Pin Assignment Diagram

# 7. Pin Description

**Table 7.1 Pin Description**

| Pin | Cumbal             | I/O | Decembries                                          |

|-----|--------------------|-----|-----------------------------------------------------|

|     | Symbol             |     | Description                                         |

| 1   | GPIO_3/SDO/UART_RX | I/O | General-purpose I/O port / SPI data output/UART_RX  |

| 2   | GPIO_4/SDI/UART_TX | I/O | General-purpose I/O port / SPI data input/UART_TX   |

| 3   | GPIO_5/SCLK        | I/O | General-purpose I/O port / SPI data clock           |

| 4   | GPIO_6/CSN         | I/O | General-purpose I/O port / SPI chip select          |

| 5   | GPIO_0/HI0/UART_RX | I/O | General-purpose I/O port/ Hall sensor input/UART_RX |

| 6   | GPIO_1/HI1/UART_TX | I/O | General-purpose I/O port/ Hall sensor input/UART_TX |

| 7   | GPIO_2/HI2         | I/O | General-purpose I/O port/ Hall sensor input         |

| 8   | TEST               | I   | Test mode select                                    |

| 9   | SLC                | I   | Low-side FET source input                           |

| 10  | W                  | I   | Phase-W motor connection pin                        |

| 11  | V                  | I   | Phase-V motor connection pin                        |

| 12  | U                  | I   | Phase-U motor connection pin                        |

| 13  | GHW                | 0   | Phase-W high-side FET gate output                   |

| 14  | GLW                | 0   | Phase-W low-side FET gate output                    |

| 15  | GHV                | 0   | Phase-V high-side FET gate output                   |

| 16  | GLV                | 0   | Phase-V low-side FET gate output                    |

| 17  | GHU                | 0   | Phase-U high-side FET gate output                   |

| 18  | GLU                | 0   | Phase-U low-side FET gate output                    |

| 19  | GNDP               | -   | Power ground                                        |

| 20  | VBATD              | I   | Battery voltage regulator input for driver circuit  |

| 21  | VCP                | 0   | Voltage regulator output for charge pump            |

| 22  | CP2H               | 0   | Boost capacitor connection pin for charge pump      |

| 23  | CP1H               | 0   | Boost capacitor connection pin for charge pump      |

| 24  | CP2L               | 0   | Boost capacitor connection pin for charge pump      |

| 25  | CP1L               | 0   | Boost capacitor connection pin for charge pump      |

| 26  | СОМ                | ı   | Motor pseudo-neutral point input                    |

| 27  | RSH                | I   | VCC side of current-sense resistor                  |

| 28  | RSL                | I   | Ground side of current-sense resistor               |

| 29  | VBAT               | ı   | Battery voltage regulator input                     |

| 30  | VMON               | ı   | Battery voltage regulator input (for ADC input)     |

| 31  | GNDD               | -   | Logic ground                                        |

| 32  | VCC                | 0   | 5-volt regulator output                             |

| 33  | VDD                | 0   | 1.5-volt regulator output                           |

| 34  | GNDA               | -   | Analog ground                                       |

| 35  | VREF               | ı   | ADC reference voltage input                         |

| 36  | GNDLIN             | -   | Ground for LIN Phy                                  |

| 37  | LIN                | I/O | LIN bus line                                        |

| 38  | PWMIN              | ı   | PWM speed input                                     |

| 39  | MD1                | ı   | Mode select                                         |

| 40 | MD0                         | I   | Mode select                                                         |

|----|-----------------------------|-----|---------------------------------------------------------------------|

| 41 | RESETN                      | I/O | Reset I/O                                                           |

| 42 | XIN                         | ı   | Crystal or ceramic oscillator connection pin                        |

| 43 | XOUT                        | 0   | Crystal or ceramic oscillator connection pin                        |

| 44 | GPIO_7/PWMOUT2/ADIN0/UART_R | I/O | General-purpose I/O port / ADC input/UART_RX                        |

| 45 | GPIO_8/PWMOUT1/ADIN1/UART_T | I/O | General-purpose I/O port / ADC input/UART_TX                        |

| 46 | GPIO_9/PWMOUT0              | I/O | General-purpose I/O port / PWM output                               |

| 47 | GPIO_10/FDL_UART_RX/SWDIO   | I/O | General-purpose I/O port / UART RX for FDL_UART/<br>SWDIO for Debug |

| 48 | GPIO_11/FDL_UART_TX/SWCLK   | I/O | General-purpose I/O port / UART TX for FDL_UART/<br>SWCLK for Debug |

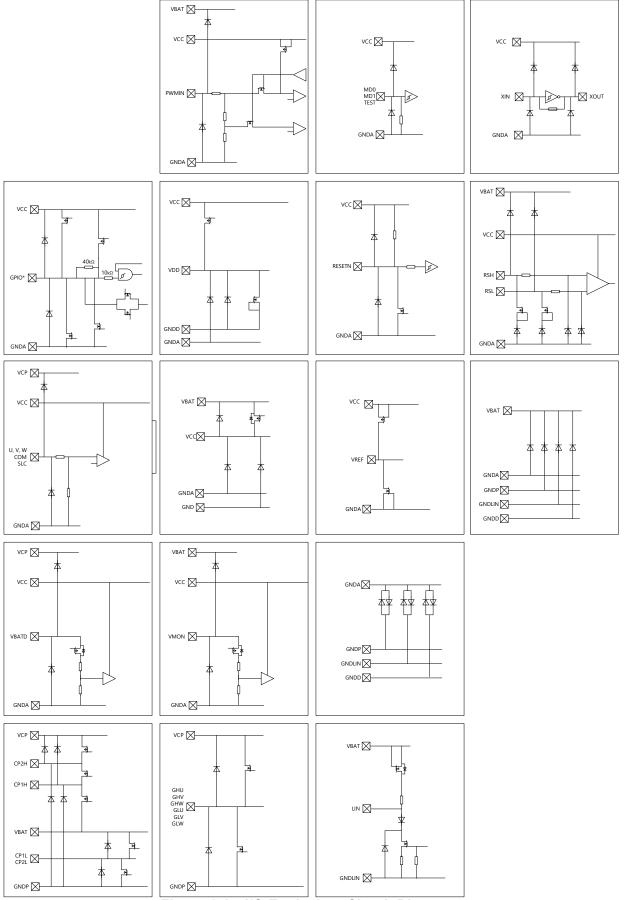

# 8. I/O Equivalent Circuits

Figure 8.1 I/O Equivalent Circuit Diagrams

# 9. Functional Description

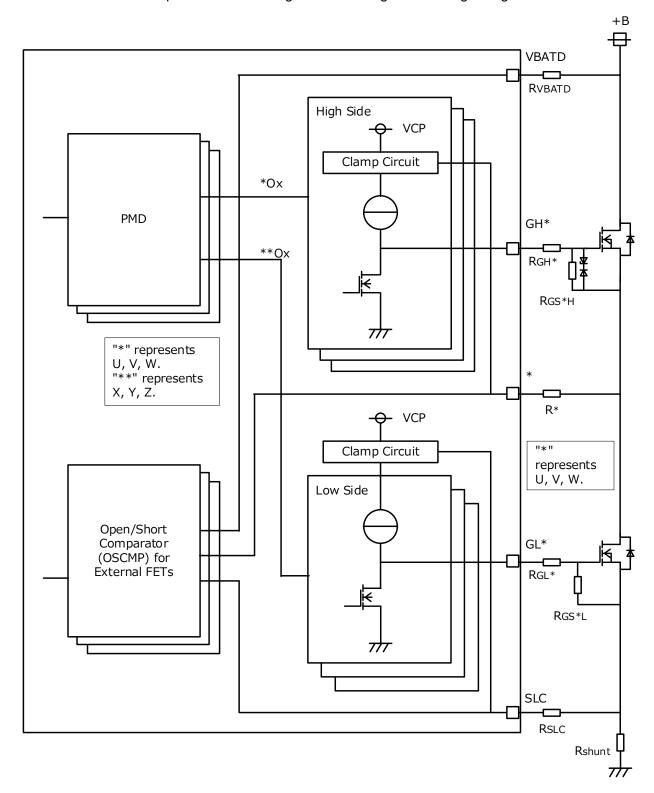

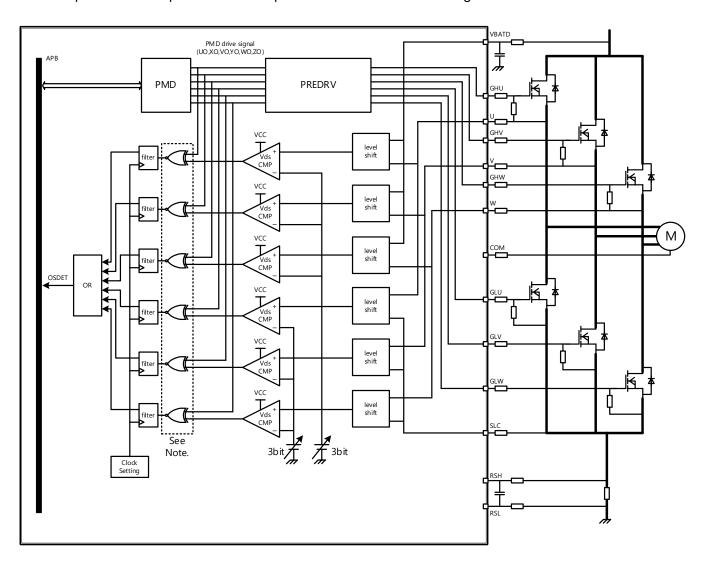

#### 9.1. Predriver Circuit

- Six-channel predriver circuit for driving a three-phase inverter (consisting of high-side and low-side Nchannel MOSFETs) for a BLDC motor

- Turns on and off the predrivers according to the drive signals from digital logic

Figure 9.1.1 Predriver Circuit Diagram

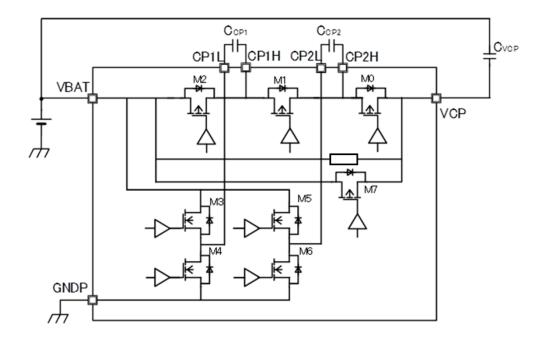

# 9.2. Charge Pump Circuit

The CGP generates a voltage for the PREDRV to drive external high-side N-channel FETs.

Figure 9.2.1 Charge Pump Circuit Diagram

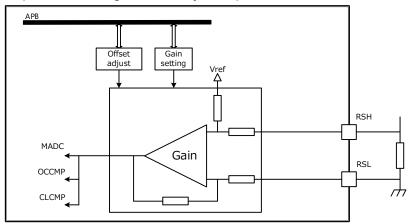

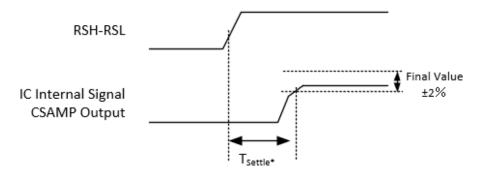

#### 9.3. Current-Sense Amplifier (CSAMP)

- The Current-Sense Amplifier (CSAMP) amplifies the voltage across an external shunt resistor by the gain programmed via a 3-bit register field.

- The amplified voltage is applied to the MADC, Overcurrent Detection Comparator (OCCMP), and Current Clamp Comparator (CLCMP).

- The output offset voltage can be adjusted prior.

**Current-Sense Amplifier Circuit Diagram Figure 9.3.1**

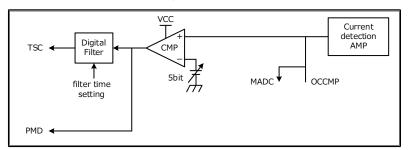

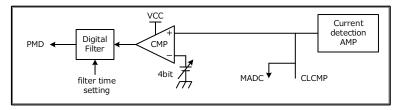

#### 9.4. Current Clamp Comparator (CLCMP)

- The CLCMP limits current if the output from the Current-Sense Amplifier (CSAMP) exceeds the programmed voltage threshold.

- The output voltage of the CSAMP is applied to the CLCMP.

- This threshold is programmable in 32 steps (i.e., with a 5-bit value)

- The CLCMP incorporates a digital filter to prevent malfunction caused by noise.

**Figure 9.4.1 Current Clamp Comparator Circuit Diagram**

#### 9.5. Overcurrent Detection Comparator (OCCMP)

- The OCCMP reports an error when the output from the Current-Sense Amplifier (CSAMP) exceeds the programmed threshold.

- The OCCMP can be enabled and disabled via the ANASTBY register.

- The overcurrent threshold is programmable with a four-bit value via a special function register.

- The OCCMP incorporates a digital filter to prevent malfunction caused by noise.

**Overcurrent Detection Comparator Circuit Diagram** Figure 9.5.1

# 9.6. Open/Short Comparator (OSCMP) for External FETs

The Open/Short Comparator detects open- and short-circuits involving external FETs.

Figure 9.6.1 OSCMP Block Diagram

# 9.7. Vector Engine(VE)

**Table 9.7.1 VE Function List**

| Category               | Function                                 | Description                                                                                                                                                                                                                           |

|------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Basic functions                          | Fixed-point calculation  Vector control tasks  Tasks for interfacing with the PMD and MADC                                                                                                                                            |

|                        | Current control tasks                    | PI control of d-axis and q-axis currents  Non-interference control  Output limiting based on scalar voltage values                                                                                                                    |

|                        | SIN/COS<br>Calculation 1 task            | Calculates the sine and cosine values of phase θ  · Allows phase interpolation and clipping                                                                                                                                           |

|                        | SIN/COS<br>Calculation 2 task            | Calculates the sine and cosine values of phase $\boldsymbol{\theta}$                                                                                                                                                                  |

|                        | SIN/COS<br>Calculation 3 task            | Calculates the sine and cosine values of phase θ • Allows phase interpolation and clipping                                                                                                                                            |

|                        | Output Voltage<br>Transformation<br>task | Coordinate axis transformation (inverse Park transformation)  Two types of phase transformation (space vector modulation and inverse Clark transformation)                                                                            |

| Calculation            | Output Control task                      | Converts three-phase voltage into PWM output settings for the PMD (two types)  · Allows output limiting  · Allows dead-time compensation                                                                                              |

|                        | Trigger Generation task                  | Calculates the PMD's AD conversion sampling timing from three-phase duty cycles                                                                                                                                                       |

|                        | Current Correction<br>Preparation task   | Corrects detected current values for low inductance motor. Used in combination with Input Process 3 and Input Process 6 tasks.                                                                                                        |

|                        | Input Process tasks                      | Reads conversion results from the MADC and converts them into fixed-point values (six types)  Supports current polarity determination (hysteresis/reverse hysteresis)                                                                 |

|                        | Input current transformation             | Phase transformation (Clark transformation)     Coordinate axis transformation                                                                                                                                                        |

|                        | Individual functions                     | Arctangent (ATAN) calculation     Square-root calculation     No Operation(NOP)                                                                                                                                                       |

|                        | Position Estimation task                 | $\boldsymbol{\cdot}$ Calculates electrical angle speed and phase $\theta$ from motor parameters, voltage, and current                                                                                                                 |

|                        | Position Sensor<br>Input Process task    | Calculates phase $\theta$ and electric angular velocity from the inputs from a position sensor such as an encoder that generates multiple pulses per revolution                                                                       |

|                        | Program<br>Schedule control              | <ul> <li>Program schedule capable of defining the order in which to execute tasks and their start-up control</li> <li>Supports up to 32 tasks</li> </ul>                                                                              |

| Schedule<br>management | Start-up control                         | Repetition start  Starts the input schedule upon completion of an AD conversion Starts executing an Input Process task upon ADC-complete interrupt when the VE is in the Standby state following the completion of an output schedule |

| Interrupt control      | Schedule-complete interrupt              | Generates an interrupt when a task with the END flag set to "1" is executed repeatedly for the specified number of times ([REPTIME]).                                                                                                 |

|       | Error interrupt       | Interrupt generated when the VE receives a PWM interrupt from the PMD during the execution of an output schedule, judging it as an error.                                                                                                                                                                                     |

|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Other | Outputs for debugging | Outputs a signal that indicates that the task is running by toggling the debug output when the task starts and stops. For example, depending on the timing of the PMD debug output, the period indicating the operation may appear to be inverted (L output).  This can be monitored by the debug output function of the PMD. |

# 9.8. Programmable Motor Driver(PMD)

**Table 9.8.1 PMD Function List**

| Category                 | Function                           | Description                                                                                                                                                                                                                                                                                                                                   |

|--------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Resolution                         | The count resolution for PWM carriers is 1/VECLK.                                                                                                                                                                                                                                                                                             |

|                          | Resolution                         | The PWM frequency and duty cycle are programmed with 15-bit values.                                                                                                                                                                                                                                                                           |

|                          |                                    | Capable of generating PWM carriers with a frequency between 0.06 kHz and 117.18 kHz (when VECLK=60 MHz) and with a 15-bit amplitude                                                                                                                                                                                                           |

|                          | PWM carrier                        | <ul> <li>Four types of carrier waveform (triangular, sawtooth, inverted triangular, and<br/>inverted sawtooth)</li> </ul>                                                                                                                                                                                                                     |

|                          | generation                         | Selectable carrier waveforms for each phase                                                                                                                                                                                                                                                                                                   |

| PWM output               |                                    | Capable of producing phase differences between the base carrier and each of<br>the U, V, and W phases independently.                                                                                                                                                                                                                          |

|                          | Thurs a least D\A/A                | Three-phase PWM waveforms are generated by comparing the PWM carriers and                                                                                                                                                                                                                                                                     |

|                          | Three-phase PWM generation         | the programmed duty cycles.  The duty cycles of the three phases can be the same or independently                                                                                                                                                                                                                                             |

|                          | generation                         | programmed.                                                                                                                                                                                                                                                                                                                                   |

|                          | O                                  | Each of the six output ports can be programmed to be driven to the PWM output level, logic High, or logic Low.                                                                                                                                                                                                                                |

|                          | Commutation control                | PWM waveforms can be generated independently for each of the three phases with a common PWM carrier (three-phase complementary PWM).                                                                                                                                                                                                          |

| AD conversion triggering | Synchronous ADC trigger generation | Generates MADC synchronous trigger signals to start AD conversion at any timing synchronous to the PWM carrier                                                                                                                                                                                                                                |

|                          | Protection control                 | Turns off the PWM outputs in response to a protection input signal                                                                                                                                                                                                                                                                            |

| Protection               | 1 Totection control                | Provides two types of protection control (EMG and OVV)                                                                                                                                                                                                                                                                                        |

| functions                | Dead-time control                  | Inserts a dead-time period to prevent a short-circuit between high-side and low-side switches (U/X, V/Y, W/Z) during their switching when generating three-phase complementary PWM signals                                                                                                                                                    |

|                          |                                    | Double- and triple-buffered registers allow the PWM period, duty cycles, ADC trigger timing, and the commutation control settings for the six output ports to be changed dynamically.                                                                                                                                                         |

| Register<br>buffering    | -                                  | <ul> <li>The update timing of execute buffers is selectable from: 1) asynchronous, 2) the center of the PWM period, 3) the end of the PWM period, and 4) the center and end of the PWM period.</li> </ul>                                                                                                                                     |

|                          |                                    | <ul> <li>The update timing of intermediate buffers is selectable from: 1) asynchronous,</li> <li>2) the center of the PWM period, 3) the end of the PWM period, 4) the 1/4 point of the PWM period, 5) the 3/4 point of the PWM period, 6) center and end point of the PWM period, and 7) the 1/4 and 3/4 point of the PWM period.</li> </ul> |

|                          |                                    | Capable of generating interrupt requests synchronous to a PWM waveform                                                                                                                                                                                                                                                                        |

|                          | DIA/AA in to mount                 | • The interrupt timing is selectable from the center and end of the base carrier.                                                                                                                                                                                                                                                             |

|                          | PWM interrupt (INTPWM)             | <ul> <li>The interval between PWM interrupts is selectable from one-half, one, two,<br/>and four PWM periods.</li> </ul>                                                                                                                                                                                                                      |

| Interrupt requests       |                                    | Capable of enabling and disabling the decimation of synchronous MADC triggers and buffer updates when interrupts are decimated                                                                                                                                                                                                                |

|                          | EMG interrupt (INTEMC)             | Interrupt request generated in the event of a protection event via an EMGx input                                                                                                                                                                                                                                                              |

|                          | OVV interrupt (INTOVV)             | Interrupt request generated in the event of a protection event via an OVVx input                                                                                                                                                                                                                                                              |

|                          |                                    | Capable of monitoring the operating timing of the motor-related peripherals via an output port                                                                                                                                                                                                                                                |

|                          |                                    | Monitor timing of the synchronous MADC trigger output from the PMD                                                                                                                                                                                                                                                                            |

| Debug output             | _                                  | Monitor timing of interrupt requests from motor-related peripherals                                                                                                                                                                                                                                                                           |

|                          |                                    | Monitor MADC conversion                                                                                                                                                                                                                                                                                                                       |

|                          |                                    | Monitor timing of VE task transitions                                                                                                                                                                                                                                                                                                         |

|                          |                                    | Monitor ENC internal signal.                                                                                                                                                                                                                                                                                                                  |

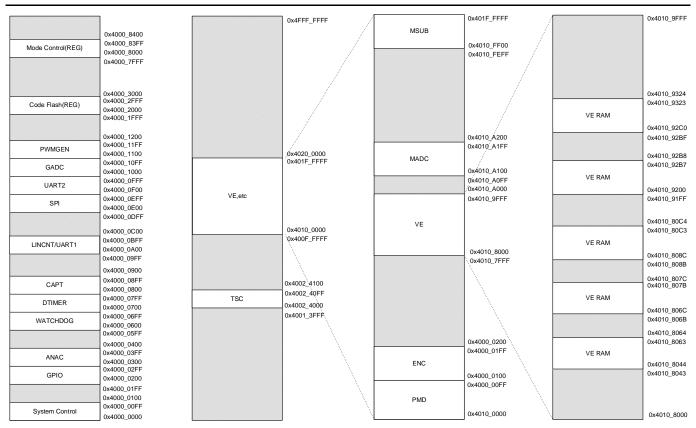

#### 9.9. Memory Map

Figure 9.9.1 Memory Map

Figure 9.9.2 Memory Map

### 10. Absolute Maximum Ratings

**Table 10.1 Absolute Maximum Ratings**

| Characteristic                              | Symbol | Pin(s)                                | Rating                                         | Unit                                  |  |

|---------------------------------------------|--------|---------------------------------------|------------------------------------------------|---------------------------------------|--|

|                                             | Vbat   | VBAT                                  | -0.3 to +40                                    |                                       |  |

| Supply voltage                              | Vcp    | VCP                                   | -0.3 to +40                                    |                                       |  |

| Supply voltage                              | Vcc    | VCC, VREF -0.3 to +6                  |                                                | V                                     |  |

|                                             | Vdd    | VDD                                   | -0.3 to +2.1                                   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |  |

| Ground-to-ground<br>voltage<br>differential | Vgnd   | GNDA, GNDD, GNDP, GNDLIN              | -0.3 to +0.3                                   |                                       |  |

|                                             | Vin1   | LIN                                   | -27 to +40 (Note1)                             |                                       |  |

|                                             | Vin2   | VBATD,                                | -0.3 to Vcp+0.3 (40 V max)                     |                                       |  |

|                                             | Vin3   | PWMIN                                 | -4 to Vbat+0.3 (40 V max)<br>(Note2), (Note5)  |                                       |  |

| la action like as                           | Vin4   | VMON                                  | -0.3 to Vbat+0.3 (40 V max)                    |                                       |  |

| Input voltage                               | Vin5   | U, V, W, COM, SLC                     | -2.5 to Vcp+0.3 (40 V max)<br>(Note3), (Note6) | V                                     |  |

|                                             | Vin6   | RSH, RSL                              | -2 to Vbat+0.3 (40 V max)<br>(Note5)           |                                       |  |

| Input voltage                               | Vin7   | TEST, MD0, MD1, RESETN<br>GPIO_x, XIN | -0.3 to Vcc+0.3<br>(6 V max)                   | <b>-</b>                              |  |

|                                             | Vout1  | LIN                                   | -27 to +40 (Note1)                             |                                       |  |

|                                             | Vout2  | GHU, GHV, GHW<br>GLU, GLV, GLW        | -0.3 to Vcp+0.3 (40 V max)<br>(Note4)          |                                       |  |

| Output voltage                              | Vout3  | CP1H, CP2H                            | -0.3 to Vcp+0.3 (40 V max)                     | V                                     |  |

|                                             | Vout4  | CP1L, CP2L                            | -0.3 to Vbat+0.3 (40 V max)                    |                                       |  |

|                                             | Vout5  | XOUT, RESETN<br>GPIO_X                | -0.3 to Vcc+0.3<br>(6 V max)                   |                                       |  |

| Operating temperature                       | Та     | -                                     | -40 to +150                                    | °C                                    |  |

| Storage<br>temperature                      | Tstg   | -                                     | -55 to +150                                    | °C                                    |  |

#### Note:

None of the absolute maximum ratings must be exceeded even instantaneously. Exposure to stress

exceeding absolute maximum ratings might cause permanent destruction or degradation of an IC and

adversely affect other components.

Ensure that none of the absolute maximum ratings is exceeded under any operating conditions. Use the IC within the specified operating ranges.

- At outside the ±18-V range, there is a limit to the period during which the TB9M003FG may be exposed to such conditions: ≤ 90 minutes at 18 to 28 V and ≤ 400 ms at 28 to 40 V

Note1: VBAT = 6.0 to 18 V

Note2: Vin3 is the voltage applied by connecting  $10k\Omega$  minimum in series. Note3: Vin5 is the voltage applied by connecting  $47\Omega$  minimum in series.

Note4: Vout2 is the voltage applied by connecting  $47\Omega$  minimum in series.

Note5: The voltage between VBAT and RSH, RSL should not exceed -0.3V to +40V.

Note6: The voltage between VCP and U, V, W, COM, SLC should not exceed -0.3V to +40V.

# 11. Operating Ranges

**Table 11.1 Operating Ranges**

| Characteristic        | Symbol | Rating     | Unit | Remarks                                                        |

|-----------------------|--------|------------|------|----------------------------------------------------------------|

|                       |        | 18 to 27   |      | Electrical characteristics are not guaranteed. (Note)          |

| Supply voltage        | Vbat   | 6 to 18    | V    | Vbat range in which electrical characteristics are guaranteed. |

|                       |        | 4.8 to 6   |      | Electrical characteristics are not guaranteed.(Note)           |

| Operating temperature | Tonr   | -40 to 150 | °C   | Ambient temperature, Ta                                        |

| Operating temperature | Topr   | -40 to 175 |      | Junction temperature, Tj (Note)                                |

Note: Not tested in a pre-shipment test

#### 12. Electrical Characteristics

#### 12.1. Overall Electrical Characteristics

VBAT=6 to 18 V, VCC=4.8 to 5.2 V, VDD=1.45 to 1.55 V, and Tj=-40 to 175°C unless otherwise noted

| Characteristic       | Symbol | Pin           | Test Condition                                                                | Min | Тур. | Max | Unit |

|----------------------|--------|---------------|-------------------------------------------------------------------------------|-----|------|-----|------|

| Standby current<br>1 | Istby1 | VBAT          | Standby mode<br>LFCLK OFF<br>VBAT=VBATD=12 V, Ta=25°C                         | -   | -    | 20  | μΑ   |

| Standby current 2    | lstby2 | VBATD<br>VMON | Standby mode<br>LFCLK OFF<br>VBAT=VBATD=12 V, Ta=70°C<br>Guaranteed by design | -   | -    | 90  | μА   |

#### Reference information:

The current consumption at the VBAT pin is approximately 33mA under the following conditions:

- VBAT=12V, room temperature, HFCLK used, SYSCLK=40MHz, VECLK=60MHz (reset state), LIN is disabled, CGP is enable, PREDRV is disabled (no external FET gate drive), No other IC external load Current consumption varies depending on usage conditions such as CPU load and operating frequency.

# 12.2. Reset Generator and Standby Time

Vbat=6 to 18 V, VCC=4.8 to 5.2 V, VDD=1.45 to 1.55 V, and Tj=-40 to 175°C unless otherwise noted

| Characteristic                     | Symbol   | Pin    | Test Condition                                                                                                                                                       | Min          | Тур. | Max          | Unit |

|------------------------------------|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|--------------|------|

| Low-level reset output voltage     | Voutlrst |        | lout=+5 mA                                                                                                                                                           | 0            | -    | 0.4          | ٧    |

| High-level input threshold voltage | Vihrst   |        | -                                                                                                                                                                    | VCC<br>×0.75 | -    | -            | ٧    |

| Low-level input threshold voltage  | Vilrst   | RESETN | -                                                                                                                                                                    | -            | -    | VCC<br>×0.25 | V    |

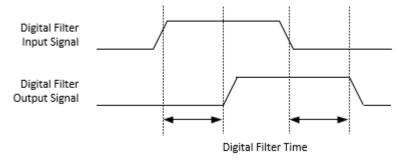

| Input noise filter<br>(analog)     | Tfilrst  |        | (See Figure 12.2.1)                                                                                                                                                  | 10           | 20   | 40           | μs   |

| Input pull-up<br>resistor          | Rpullup  |        | Between the VCC and RESETN pins                                                                                                                                      | 30           | 50   | 100          | kΩ   |

| WATCHDOG reset time                | Twdt     | -      | Time from a WATCHDOG reset request to an internal reset release (except when the flash memory is busy)                                                               | -            | 70   | -            | μs   |

| Power-on reset settling time       | Trst1    | -      | Time from recovery from a VCC undervolage condition to a CPU reset release                                                                                           | -            | -    | 8            | ms   |

| Recovery settling time             | Trst2    | -      | Time from when a wake-up request is detected to when a CPU reset is released after the LDO15V stabilizes                                                             | -            | -    | 2            | ms   |

| External oscillator settling time  | Trst3    | -      | Time from when the oscillator is started<br>by software to when it settles to a<br>steady state (when a 16-MHz<br>CERALOCK ceramic resonator from<br>Murata is used) | -            | -    | 1            | ms   |

| PLL settling time                  | Tpll     | -      | -                                                                                                                                                                    | -            | -    | 140          | μs   |

Figure 12.2.1 Measurement of Digital Filter Time

#### 12.3. 5-V Regulator (LDO5V)

VBAT=6 to 18 V, VCC=4.8 to 5.2 V, VDD=1.45 to 1.55 V, and Tj=-40 to 175°C unless otherwise noted

| Characteristic                         | Symbol  | Pin | Test Condition                                                                                                                                                           | Min  | Тур. | Max  | Unit |

|----------------------------------------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VCC output<br>voltage 1                | Vcc1    | _   | lload = -10 μA to -135 mA (Total VCC/VDD current consumption of maximum self consumption current inside the IC and external load current (max. 60mA))  Tj = -40 to 150°C | 4.9  | 5.0  | 5.1  | V    |

| VCC output<br>voltage 3                | Vcc3    |     | lload = -10 µA to -135 mA (Total VCC/VDD current consumption of maximum self consumption current inside the IC and external load current (max. 60mA))  Tj = 150 to 175°C | 4.8  | 5.0  | 5.2  | V    |

| Current limit 1                        | llimit1 |     | VCC ≥ 4.0 V                                                                                                                                                              | -850 | -475 | -250 | mA   |

| Current limit 2                        | Ilimit2 | VCC | VCC ≤ 3.0 V                                                                                                                                                              | -250 | -112 | -10  | mA   |

| Dropout voltage                        | Vdrop   |     | Vbat = 4.8 V,lload = -120 mA < (-5mA + current consumed by LDO5V)                                                                                                        | -    | 0.2  | 0.45 | V    |

| Undervoltage<br>detection voltage<br>1 | Vrst1   |     | VCC falling (UV_VCC)                                                                                                                                                     | 4.0  | -    | 4.35 | V    |

| Undervoltage<br>release voltage 1      | Vrstr1  |     | VCC rising (UV_VCC)                                                                                                                                                      | 4.2  | -    | 4.75 | V    |

| Undervoltage<br>detection voltage<br>3 | Vrst3   |     | VCC falling (POR5V)                                                                                                                                                      | 3.07 | 3.45 | 3.83 | ٧    |

| Undervoltage<br>release voltage 3      | Vrstr3  |     | VCC rising (POR5V)                                                                                                                                                       | 3.22 | 3.60 | 3.98 | V    |

#### Note:

- Connect a capacitor of 1.0 µF or more as close as possible to the VCC pin.

- The current limit at VCC in Standby mode is Current Ilimit2.

# 12.4. 1.5-Voltage Regulator (LDO15V)

VBAT=6 to 18 V, VCC=4.8 to 5.2 V, VDD=1.45 to 1.55 V, and Tj=-40 to 175°C unless otherwise noted

| Characteristic                              | Symbol  | Pin | Test Condition                                                                                                                                    | Min  | Тур. | Max  | Unit |

|---------------------------------------------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VDD output<br>voltage                       | Vdd     |     | lload = -10 μA to -60 mA + (Total VDD current consumption of maximum self consumption current inside the IC and external load current (max. 1mA)) | 1.45 | 1.5  | 1.55 | ٧    |

| Current limit 3                             | Ilimit3 |     | -                                                                                                                                                 | -250 | -150 | -70  | mA   |

| Undervoltage<br>detection voltage<br>2      | Vrst2   | VDD | VDD falling                                                                                                                                       | 1.3  | -    | 1.4  | ٧    |

| Undervoltage release voltage 2              | Vrstr2  |     | VDD rising                                                                                                                                        | 1.35 | -    | 1.45 | ٧    |

| Overvoltage<br>detection/release<br>voltage | Vddov   |     | -                                                                                                                                                 | 1.55 | -    | 1.65 | ٧    |

Note: Connect a capacitor of 2.2 µF or more as close as possible to the VDD pin.

# 12.5. Charge Pump

VBAT=6 to 18 V, VCC=4.8 to 5.2 V, VDD=1.45 to 1.55 V, and Tj=-40 to 175°C unless otherwise noted

| Characteristic                                            | Symbol     | Pin  | Test Condition                                                                                  | Min          | Тур.         | Max         | Unit |

|-----------------------------------------------------------|------------|------|-------------------------------------------------------------------------------------------------|--------------|--------------|-------------|------|

| Output voltage<br>1                                       | Vcp1       |      | VBAT = 6 V, Iload = -10 μA to -31.8mA,<br>Cload=15,000 pF                                       | VBAT<br>+6.5 | -            | -           | V    |

| Output voltage<br>2                                       | Vcp2       |      | VBAT = 8 to 18V, Iload = -10 μA to -<br>31.8mA, Cload=15,000 pF                                 | VBAT<br>+10  | VBAT<br>+12  | VBAT<br>+14 | V    |

| Output voltage<br>3                                       | Vcp3       |      | VBAT=5 V, Iload = -10 μA to -13.8mA,<br>Cload=5,500 pF                                          | VBAT<br>+6.5 | VBAT<br>+8.7 | -           | V    |

| Boost<br>overvoltage<br>detection<br>threshold<br>voltage | Vcplim1    | VCP  | -                                                                                               | 31           | 33           | 35          | ٧    |

| Boost<br>overvoltage<br>recovery<br>threshold<br>voltage  | Vcplim_r1  |      | -                                                                                               | 29.5         | 31.5         | 33.5        | ٧    |

| Boost disable<br>threshold<br>voltage 1                   | Vcpstop1   | VBAT | -                                                                                               | 27           | 28.5         | 30          | ٧    |

| Boost enable<br>threshold<br>voltage 1                    | Vcpstop_r1 | VDAI | -                                                                                               | 26           | 27.5         | 29          | ٧    |

| Boost disable<br>threshold<br>voltage 2                   | Vcpstop2   | VCD  | -                                                                                               | 34           | 36           | 38          | ٧    |

| Boost enable<br>threshold<br>voltage 2                    | Vcpstop_r2 | VCP  | -                                                                                               | 32           | 34           | 36          | ٧    |

| Boost frequency                                           | Fcp        | -    | -                                                                                               | 237.5        | 250          | 262.5       | kHz  |

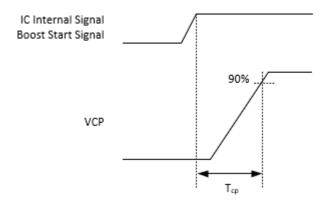

| Rise time                                                 | Тср        | VCP  | Time from when the boost start signal is asserted to when the output voltage reaches 90% of Vcp | -            | -            | 1           | ms   |

Note: Enable the charge pump when VBAT ≥ 5 V.

Figure 12.5.1 Measurement of Rise Time

#### 12.6. Oscillator

VBAT=6 to 18 V, VCC=4.8 to 5.2 V, VDD=1.45 to 1.55 V, and Tj=-40 to 175°C unless otherwise noted

| Characteristic                        | Symbol | Pin         | Test Condition                                                          | Min          | Тур. | Max          | Unit |

|---------------------------------------|--------|-------------|-------------------------------------------------------------------------|--------------|------|--------------|------|

| Oscillation<br>frequency 1<br>(HFCLK) | Fosc1  | -           | -                                                                       | 19           | 20   | 21           | MHz  |

| Oscillation frequency 2 (LFCLK)       | Fosc2  | -           | -                                                                       | 24           | 32   | 40           | kHz  |

| Oscillation frequency 3 (XCLK)        | Fosc3  | XIN<br>XOUT | Values of a usable external<br>CERALOCK ceramic resonator or<br>crystal | 16<br>(Note) | -    | 20<br>(Note) | MHz  |

Note: Typical value of an external oscillator.

Contact the manufacturer of external components for the matching with XCLK.

Toshiba has tested the CSTNE16M0VH3C000R0 and CSTNE20M0VH3C000R0 and confirmed that they operate with the XCLK properly.

#### 12.7. 12-Bit ADC

VBAT=6 to 18 V, VCC=4.8 to 5.2 V, VDD=1.45 to 1.55 V, and Tj=-40 to 175°C unless otherwise noted

| Characteristic                  | Symbol     | Pin   | Test Condition                                                        | Min   | Тур. | Max   | Unit  |

|---------------------------------|------------|-------|-----------------------------------------------------------------------|-------|------|-------|-------|

| Conversion time 1               | Tconv1     | -     | Settling time + Conversion time<br>MADCCLK=30MHz                      | -     | 1.33 | -     | μs    |

| INL1                            | Inl1       | -     | Guaranteed by design                                                  | -2    | -    | 2     | LSB   |

| DNL1                            | Dnl1       | -     | Guaranteed by design                                                  | -1    | -    | 2     | LSB   |

| Total error 1                   | Err_total1 | -     | Guaranteed by design                                                  | -6    | -    | 6     | LSB   |

| Input voltage<br>division ratio | Ratio_r1   | VBATD | Buffer input voltage division ratio<br>Input voltage range: 6 to 27 V | 0.095 | 0.1  | 0.105 | Times |

Note: When the MADC is enabled, the pull-down resistors for reducing the input voltage have a value of 250 kΩ typical.

#### 12.8. 10-Bit ADC

VBAT=6 to 18 V, VCC=4.8 to 5.2 V, VDD=1.45 to 1.55 V, and Tj=-40 to 175°C unless otherwise noted

| Characteristic                  | Symbol     | Pin  | Test Condition                                                                                        | Min   | Тур. | Max   | Unit  |

|---------------------------------|------------|------|-------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Conversion time 2               | Tconv2     | -    | Settling time + Conversion time<br>GADCCLK=10MHz                                                      | -     | 16.4 | -     | μs    |

| INL2                            | Inl2       | -    | -                                                                                                     | -2.5  | -    | 2.5   | LSB   |

| DNL2                            | Dnl2       | -    | -                                                                                                     | -1.5  | -    | 1.5   | LSB   |

| Total error 2                   | Err_total2 | -    | -                                                                                                     | -3    | -    | 3     | LSB   |

| Input voltage<br>division ratio | Ratio_r2   | VMON | Buffer input voltage division ratio<br>Input voltage range: 6 to 27 V                                 | 0.095 | 0.1  | 0.105 | Times |

| Amplifier error                 | Err_amp2   | -    | Buffer amplifier input-output differential<br>Input voltage range between 0.2 V and<br>supply voltage | -10   | -    | 10    | mV    |

#### 12.9. Predriver Circuit (PREDRV)

VBAT=6 to 18 V, VCC=4.8 to 5.2 V, VDD=1.45 to 1.55 V, and Tj=-40 to 175°C unless otherwise noted

| Characteristic        | Symbol | Pin               | Test Condition                                                                                                                                                                                                          | Min  | Тур. | Max | Unit     |

|-----------------------|--------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|----------|

| Output voltage<br>HH1 | Vohh1  |                   | High-side high-level output Referenced to the source of FETs VBAT ≥ 8 V, Icp=31.8 mA Cload=15,000 pF (Note1)                                                                                                            | 8    | 10   | 14  | V        |

| Output voltage<br>HH2 | Vohh2  |                   | High-side high-level output Referenced to the source of FETs VBAT ≥ 6V, lcp=31.8 mA Cload=15,000 pF (Note1)                                                                                                             | 4.5  | -    | 14  | V        |

| Output voltage<br>HH3 | Vohh3  | GHU<br>GHV<br>GHW | High-side high-level output Referenced to the source of FETs VBAT ≥ 4.8V, Icp=31.8 mA Cload=15,000 pF (Note1) Process variations are not considered. (Only temperature variations are considered.) Guaranteed by design | 3.8  | -    | 14  | V        |

| Output voltage<br>HH4 | Vohh4  |                   | High-side high-level output Referenced to the source of FETs VBAT ≥ 5V, Icp=13.8mA Cload=5,500 pF (Note2)                                                                                                               | 4.5  | 1    | 14  | ٧        |

| Output voltage<br>LH  | Volh   |                   | High-side low-level output<br>Igx=100 μA<br>* The VB values of 4.8 to 6 V and 18<br>to 27 V are guaranteed by design.                                                                                                   | -0.1 | ı    | 0.1 | V        |

| Output voltage<br>HL1 | Vohl1  |                   | Low-side high-level output Referenced to the source of FETs VBAT ≥ 8 V, Icp=31.8 mA Cload=15,000 pF (Note1)                                                                                                             | 8    | 10   | 14  | V        |

| Output voltage<br>HL2 | Vohl2  |                   | Low-side high-level output Referenced to the source of FETs VBAT ≥ 6V, lcp=31.8 mA Cload=15,000 pF (Note1)                                                                                                              | 4.5  | 1    | 14  | <b>V</b> |

| Output voltage<br>HL3 | Vohl3  | GLU<br>GLV<br>GLW | Low-side high-level output Referenced to the source of FETs VBAT ≥ 4.8 V, Icp=31.8 mA Cload=15,000 pF (Note1) Process variations are not considered. (Only temperature variations are considered.) Guaranteed by design | 3.8  | -    | 14  | V        |

| Output voltage<br>HL4 | Vohl4  |                   | Low-side high-level output Referenced to the source of FETs Guaranteed by design: VBAT ≥ 5 V                                                                                                                            | 4.5  | -    | 14  | V        |

| Output voltage<br>LL  | Voll   |                   | Low-side low-level output<br>Igx=100 μA<br>* The VBAT values of 4.8 to 6 V and<br>18 to 27 V are guaranteed by design.                                                                                                  | -0.1 | -    | 0.1 | >        |

Note1: Although the PREDRV specifications are prescribed at an lcp of 31.8 mA (i.e., a load current of the charge pump assuming that six FETs with a total Cloud of 15,000 pF are driven at a PWM frequency of 20 kHz), these output voltage characteristics are tested with a load current (Igx) of -100 μA.

Note2: Although the PREDRV specifications are prescribed at an Icp of 13.8 mA (i.e., a load current of the charge pump if six FETs with a total Cloud of 5,500 pF are driven at a PWM frequency of 20 kHz), this output voltage characteristic is tested with a load current (lgx) of -100 µA.

| Characteristic              | Symbol    | Pin                      | Test Condition                                                                                                                  | Min   | Тур. | Max   | Unit |

|-----------------------------|-----------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| Phase-1 charge<br>current 1 | lphase1c1 |                          | Minimum setting for Phase 1:  [PREDRVSRCR] <iphase1> = 0000  (0mA)  * Common to the high-side and low-side predrivers</iphase1> | -0.1  | 0    | 0.1   | mA   |

| Phase-1 charge<br>current 2 | lphase1c2 | GHU                      | [PREDRVSRCR] <iphase1> = 1000 (15mA)  * Common to the high-side and low-side predrivers</iphase1>                               | -19.5 | -15  | -10.5 | mA   |

| Phase-1 charge<br>current 3 | lphase1c3 | GHV<br>GHW<br>GLU<br>GLV | [PREDRVSRCR] <iphase1> = 1001 (30mA) * Common to the high-side and low-side predrivers</iphase1>                                | -39   | -30  | -21   | mA   |

| Phase-1 charge<br>current 4 | lphase1c4 | GLW                      | [PREDRVSRCR] <iphase1> = 1011 (60mA)  * Common to the high-side and low-side predrivers</iphase1>                               | -78   | -60  | -42   | mA   |

| Phase-1 charge<br>current 5 | lphase1c5 |                          | Maximum setting Phase 1: [PREDRVSRCR] <iphase1> = 1111 (120mA)  * Common to the high-side and low-side predrivers</iphase1>     | -156  | -120 | -84   | mA   |

| Characteristic                   | Symbol     | Pin        | Test Condition                                                                                 | Min   | Тур. | Max   | Unit |

|----------------------------------|------------|------------|------------------------------------------------------------------------------------------------|-------|------|-------|------|

| Phase-2 high-<br>side current 1  | lphase2h1  |            | Minimum high-side setting for Phase<br>2: [PREDRVSRCR] <iphase2h> =<br/>00000 (1mA)</iphase2h> | -1.4  | -1   | -0.6  | mA   |

| Phase-2 high-<br>side current 2  | lphase2h2  |            | [PREDRVSRCR] <iphase2h> = 00001 (2mA)</iphase2h>                                               | -2.6  | -2   | -1.4  | mA   |

| Phase-2 high-<br>side current 3  | lphase2h3  |            | [PREDRVSRCR] <iphase2h> = 00011 (4mA)</iphase2h>                                               | -5.2  | -4   | -2.8  | mA   |

| Phase-2 high-<br>side current 4  | lphase2h4  | GHU        | [PREDRVSRCR] <iphase2h> = 00111 (8mA)</iphase2h>                                               | -10.4 | -8   | -5.6  | mA   |

| Phase-2 high-<br>side current 5  | lphase2h5  | GHV<br>GHW | [PREDRVSRCR] <iphase2h> = 01111 (16mA)</iphase2h>                                              | -20.8 | -16  | -11.2 | mA   |

| Phase-2 high-<br>side current 6  | lphase2h6  | GLU<br>GLV | [PREDRVSRCR] <iphase2h> = 10000 (18mA)</iphase2h>                                              | -23.4 | -18  | -12.6 | mA   |

| Phase-2 high-<br>side current 7  | lphase2h7  | GLW        | [PREDRVSRCR] <iphase2h> = 10001 (20mA)</iphase2h>                                              | -26   | -20  | -14   | mA   |

| Phase-2 high-<br>side current 8  | lphase2h8  |            | [PREDRVSRCR] <iphase2h> = 10011 (24mA)</iphase2h>                                              | -31.2 | -24  | -16.8 | mA   |

| Phase-2 high-<br>side current 9  | lphase2h9  |            | [PREDRVSRCR] <iphase2h> = 10111 (32mA)</iphase2h>                                              | -41.6 | -32  | -22.4 | mA   |

| Phase-2 high-<br>side current 10 | lphase2h10 |            | Maximum high-side setting for Phase 2: [PREDRVSRCR] <iphase2h> = 11111 (48mA)</iphase2h>       | -62.4 | -48  | -33.6 | mA   |

| Characteristic              | Symbol     | Pin        | Test Condition                                                                                                                                                                                                                        | Min    | Тур. | Max    | Unit |

|-----------------------------|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--------|------|

| Phase-2 low-side current 1  | lphase2l1  |            | Minimum low-side setting for Phase 2:<br>[PREDRVSRCR] <iphase2l> =<br/>00000 (1mA)</iphase2l>                                                                                                                                         | -1.4   | -1   | -0.6   | mA   |

| Phase-2 low-side current 2  | lphase2l2  |            | [PREDRVSRCR] <iphase2l> = 00001 (2mA)</iphase2l>                                                                                                                                                                                      | -2.6   | -2   | -1.4   | mA   |

| Phase-2 low-side current 3  | lphase2l3  |            | [PREDRVSRCR] <iphase2l> = 00011 (4mA)</iphase2l>                                                                                                                                                                                      | -5.2   | -4   | -2.8   | mA   |

| Phase-2 low-side current 4  | lphase2l4  |            | [PREDRVSRCR] <iphase2l> = 00111 (8mA)</iphase2l>                                                                                                                                                                                      | -10.4  | -8   | -5.6   | mA   |

| Phase-2 low-side current 5  | lphase2l5  |            | [PREDRVSRCR] <iphase2l> = 01111 (16mA)</iphase2l>                                                                                                                                                                                     | -20.8  | -16  | -11.2  | mA   |

| Phase-2 low-side current 6  | lphase2l6  | GHU<br>GHV | [PREDRVSRCR] <iphase2l> = 10000 (18mA)</iphase2l>                                                                                                                                                                                     | -23.4  | -18  | -12.6  | mA   |

| Phase-2 low-side current 7  | lphase2l7  | GHW<br>GLU | [PREDRVSRCR] <iphase2l> = 10001 (20mA)</iphase2l>                                                                                                                                                                                     | -26    | -20  | -14    | mA   |

| Phase-2 low-side current 8  | lphase2l8  | GLV<br>GLW | [PREDRVSRCR] <iphase2l> = 10011 (24mA)</iphase2l>                                                                                                                                                                                     | -31.2  | -24  | -16.8  | mA   |

| Phase-2 low-side current 9  | lphase2l9  | OLVV       | [PREDRVSRCR] <iphase2l> = 10111 (32mA)</iphase2l>                                                                                                                                                                                     | -41.6  | -32  | -22.4  | mA   |

| Phase-2 low-side current 10 | lphase2l10 |            | Maximum low-side setting for Phase 2: [PREDRVSRCR] <iphase2l> = 11111 (48mA)</iphase2l>                                                                                                                                               | -62.4  | -48  | -33.6  | mA   |

| Phase-3 current             | lphase3    |            | Maximum high-side setting for Phase 2: [PREDRVSRCR] <iphase2h> = 11111 (48mA)  Maximum low-side setting for Phase 2: [PREDRVSRCR]<iphase2h> = 11111 (48mA)  * Separate to the high-side and low-side predrivers</iphase2h></iphase2h> | -218.4 | -168 | -117.6 | mA   |

| Characteristic                    | Symbol     | Pin               | Test Condition                                                                                                                                                                                                                                                                                      | Min | Тур. | Max | Unit |

|-----------------------------------|------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Output resistor 1                 | Routh      | GHU<br>GHV<br>GHW | High-side discharge side<br>Iol=-20 mA                                                                                                                                                                                                                                                              | 2   | 5.4  | 12  | Ω    |

| Output resistor 2                 | Routl      | GLU<br>GLV<br>GLW | Low-side discharge side<br>lol=-20 mA                                                                                                                                                                                                                                                               | 2   | 5.4  | 12  | Ω    |

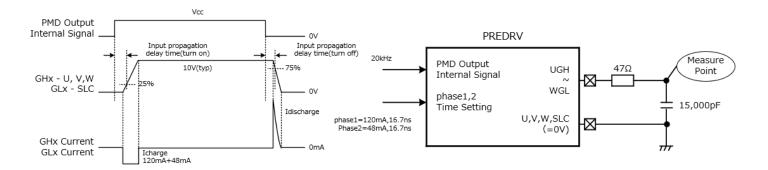

| Input propagation<br>delay time 1 | Thondelay  |                   | High-side turn-on Cload=15,000 pF, 25% of VGHx Phase-1 charge current setting register [PREDRVSRCR]< PHASE1> = 111 (120 mA max) Phase -2 charge current setting register [PREDRVSRCR]< PHASE2H> = 11111 (48 mA max) Total: 168 mA U, V, W, SLC= 0 V (See Figure 12.9.1.)                            | -   | 0.4  | 1.0 | με   |

| Input propagation<br>delay time 2 | Thoffdelay | GHU<br>GHV<br>GHW | High-side turn-off Cload=15,000 pF, 75% of VGHx U, V, W, SLC= 0 V (External parts: R=47 Ω, C=15,000 pF) Observed outside the 47-Ω resistor (See Figure 12.9.1.)                                                                                                                                     | 1   | 0.3  | 1.0 | μs   |

| Input propagation<br>delay time 3 | Tlondelay  | GLU<br>GLV<br>GLW | Low-side turn-on Cload=15,000 pF, 25% of VGLx Phase-1 charge current setting register [PREDRVSRCR] <iphase1>= 111 (120 mA max) Phase -2 charge current setting register [PREDRVSRCR]<iphase2l>= 11111 (48 mA max) Total: 168 mA 10%-90% U, V, W, SLC= 0 V (See Figure 12.9.1.)</iphase2l></iphase1> | -   | 0.4  | 1.0 | μs   |

| Input propagation delay time 4    | Tloffdelay |                   | Low-side turn-off Cload=15,000 pF, 75% of VGLx U, V, W, SLC= 0 V (External parts: R=47 Ω, C=15,000 pF) Observed outside the 47-Ω resistor (See Figure 12.9.1.)                                                                                                                                      | -   | 0.3  | 1.0 | μs   |

Figure 12.9.1 Measurement of Input Propagation Delay Times and Measurement circuit diagram

| Characteristic              | Symbol    | Pin | Test Condition                                                                                                | Min   | Тур.  | Max    | Unit |

|-----------------------------|-----------|-----|---------------------------------------------------------------------------------------------------------------|-------|-------|--------|------|

| Initial Phase-1<br>period 1 | Tphase1i1 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase1>:<br/>000000 (0 ns, minimum setting)<br/>Guaranteed by design</tphase1> | -     | 0     | -      | ns   |

| Initial Phase-1<br>period 2 | Tphase1i2 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase1>:<br/>000001 (16.7 ns)</tphase1>                                        | 15.8  | 16.7  | 17.5   | ns   |

| Initial Phase-1<br>period 3 | Tphase1i3 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase1>:<br/>000011 (50 ns)</tphase1>                                          | 47.5  | 50    | 52.5   | ns   |

| Initial Phase-1<br>period 4 | Tphase1i4 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase1>:<br/>000111 (116.7 ns)</tphase1>                                       | 110.9 | 116.7 | 122.5  | ns   |

| Initial Phase-1<br>period 5 | Tphase1i5 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase1>:<br/>001111 (250 ns)</tphase1>                                         | 237.5 | 250   | 262.5  | ns   |

| Initial Phase-1<br>period 6 | Tphase1i6 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase1>:<br/>011111 (516.7 ns)</tphase1>                                       | 490.9 | 516.7 | 542.5  | ns   |

| Initial Phase-1<br>period 7 | Tphase1i7 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase1>:<br/>111111 (1050 ns, maximum setting)</tphase1>                       | 997.5 | 1050  | 1102.5 | ns   |

| Characteristic             | Symbol    | Pin | Test Condition                                                                                                           | Min    | Тур.   | Max    | Unit |

|----------------------------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|------|

| Phase-2 target period 1    | Tphase2t1 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase2>:<br/>0000000 (0 ns, minimum setting)<br/>Guaranteed by design</tphase2>           | -      | 0      | -      | ns   |

| Phase-2 target<br>period 2 | Tphase2t2 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase2>:<br/>0000001 (16.7 ns)</tphase2>                                                  | 15.8   | 16.7   | 17.5   | ns   |

| Phase-2 target period 3    | Tphase2t3 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase2>:<br/>0000011 (50 ns)</tphase2>                                                    | 47.5   | 50     | 52.5   | ns   |

| Phase-2 target period 4    | Tphase2t4 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase2>:<br/>0000111 (116.7 ns)</tphase2>                                                 | 110.9  | 116.7  | 122.5  | ns   |

| Phase-2 target period 5    | Tphase2t5 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase2>:<br/>0001111 (250 ns)</tphase2>                                                   | 237.5  | 250    | 262.5  | ns   |

| Phase-2 target period 6    | Tphase2t6 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase2>:<br/>0011111 (516.7 ns)</tphase2>                                                 | 490.9  | 516.7  | 542.5  | ns   |

| Phase-2 target<br>period 7 | Tphase2t7 | ı   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase2>:<br/>0111111 (1050 ns)</tphase2>                                                  | 997.5  | 1050   | 1102.5 | ns   |

| Phase-2 target<br>period 8 | Tphase2t8 | -   | VECLK=60MHz<br>[MCSSDRVPTSR] <tphase2>:<br/>1111111 (2116.7 ns)</tphase2>                                                | 2010.9 | 2116.7 | 2222.5 | ns   |

| Dead time                  | Tdead     | -   | Dead-Time register:<br>[DTR] <dtr[9:0]> = 0x02D<br/>When dead time is programmed to be<br/>3 µs. VECLK=60 MHz</dtr[9:0]> | 2.85   | 3      | 3.15   | μs   |

# 12.10. Current-Sense Amplifier (CSAMP)

VBAT=6 to 18 V, VCC=4.8 to 5.2 V, VDD=1.45 to 1.55 V, and Tj=-40 to 175°C unless otherwise noted

| Characteristic                  | Symbol    | Pin | Test Condition                                                                                                                                                                             | Min               | Тур.  | Max               | Unit  |

|---------------------------------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------------------|-------|

| Input common-mode voltage range | Vcomin    |     | -                                                                                                                                                                                          | -0.2              | -     | 2.0               | V     |

| Gain 1                          | Gain1     |     | Programmed to be ×5                                                                                                                                                                        | 4.95              | 5     | 5.05              | Times |

| Gain 2                          | Gain2     | RSH | Programmed to be ×10                                                                                                                                                                       | 9.9               | 10    | 10.1              | Times |

| Gain 3                          | Gain3     | RSL | Programmed to be ×15                                                                                                                                                                       | 14.85             | 15    | 15.15             | Times |

| Gain 4                          | Gain4     |     | Programmed to be ×20                                                                                                                                                                       | 19.8              | 20    | 20.2              | Times |

| Gain 5                          | Gain5     |     | Programmed to be ×40                                                                                                                                                                       | 39.6              | 40    | 40.4              | Times |

| Gain 6                          | Gain6     |     | Programmed to be ×60                                                                                                                                                                       | 59.25             | 59.85 | 60.45             | Times |

| Output offset voltage<br>1      | Vooffset1 | -   | Programmed to be Vcc/ 2 * Gain60 after calibration, including input offset                                                                                                                 | VCC/2<br>-0.0606  | 2.5   | VCC/2<br>+0.0606  | V     |

| Output offset voltage 2         | Vooffset2 | -   | Programmed to be Vcc/ 5 * Gain60 after calibration, including input offset                                                                                                                 | VCC/5<br>-0.0606  | 1.0   | VCC/5<br>+0.0606  | V     |

| Output offset voltage 3         | Vooffset3 | -   | Programmed to be Vcc/ 8 * Gain60 after calibration, including input offset                                                                                                                 | VCC/8<br>-0.0606  | 0.625 | VCC/8<br>+0.0606  | V     |

| Output offset voltage<br>4      | Vooffset4 | -   | Programmed to be Vcc/ 10 * Gain60 after calibration, including input offset                                                                                                                | VCC/10<br>-0.0606 | 0.5   | VCC/10<br>+0.0606 | V     |

| Settling time 1                 | Tsettle1  | -   | Gain = 5, output voltage: 2.5V ↔ 3.5 V No external input filter Time required for the output voltage to settle to within ±2% of its final value Guaranteed by design (See Figure 12.10.1)  | -                 | -     | 0.5               | μs    |

| Settling time 2                 | Tsettle2  | -   | Gain = 20, output voltage: 2.5V ↔ 3.5 V No external input filter Time required for the output voltage to settle to within ±2% of its final value Guaranteed by design (See Figure 12.10.1) | -                 | -     | 0.8               | μs    |

| Settling time 3                 | Tsettle3  | -   | Gain = 60, output voltage: 2.5V ↔ 3.5 V No external input filter Time required for the output voltage to settle to within ±2% of its final value Guaranteed by design (See Figure 12.10.1) | -                 | -     | 1.7               | μs    |