# eFuse Application Circuit (with Thermal Shutdown)

# **Reference Guide**

## RD241A-RGUIDE-01

### **Toshiba Electronic Devices & Storage Corporation**

### **Table of Contents**

| 1.    | In | troduction                                   | 3  |

|-------|----|----------------------------------------------|----|

| 2.    | Sp | ecifications and Appearance                  | 4  |

| 2.1.  |    | Specifications                               | .4 |

| 2.2.  |    | Block Diagrams                               | .5 |

| 2.2.1 | 1. | Module Board Block Diagram                   | 5  |

| 2.2.2 | 2. | Base Board Block Diagram                     | 6  |

| 2.3.  |    | Appearance and Component Layout              | 7  |

| 2.3.1 | 1. | Module Board                                 | 7  |

| 2.3.2 | 2. | Base Board                                   | .9 |

| 3.    | Sc | hematic, Bill of Materials, and PCB Pattern1 | 1  |

| 3.1.  |    | Schematic                                    | 11 |

| 3.2.  |    | Bill of Materials                            | 11 |

| 3.3.  |    | PCB Pattern                                  | 11 |

| 4.    | Op | peration1                                    | 5  |

| 4.1.  |    | Operation Procedure                          | 15 |

| 4.2.  |    | Base Board External Connector Specifications | 17 |

| 4.3.  |    | Module Board Operation Summary               | 19 |

| 4.4.  |    | Over Temperature Detection                   | 19 |

| 4.5.  |    | Output Overcurrent Detection                 | 19 |

| 5.    | Pr | ecautions1                                   | 9  |

### 1. Introduction

This reference guide document describes the specifications and operation procedure of the eFuse Application Circuit (with Thermal Shutdown).

In recent years, various protective functions have become important in various consumer devices such as notebook PCs, game machines, storage devices, servers, etc. This document describes the Protection Circuit (hereafter referred to as "this design"), which is ideal for these applications, it is built using the eFuse IC (electronic fuse) and the over temperature detection IC Thermoflagger<sup>™</sup>.

eFuse IC (electronic fuse) operates when excessive current flows and has a fast current interruption function compared to the conventional fuse. In addition, it can be used repeatedly because it doesn't get destroyed by a single event of overcurrent. Various other protection functions, such as overvoltage protection, are also built in.

Thermoflagger<sup>™</sup> (Over temperature detection IC) detects abnormally high temperature in the electronic devices in conjunction with a PTC thermistor. By arranging several PTC thermistors and connecting them to the Thermoflagger<sup>™</sup>, a wide range of abnormal temperatures can be detected at a low-cost. Featuring low current consumption operation, this product contributes to power saving.

This Design consists of a module board and a base board.

The module board consists of an eFuse IC (TCKE905ANA) with overcurrent protection and an over temperature detection IC Thermoflagger<sup>TM</sup> (TCTH021BE). In case of overcurrent detection, the eFuse IC cuts off the current. If the temperature of the PTC thermistor connected to the over temperature detection IC Thermoflagger<sup>TM</sup> rises due to abnormal heating, the Thermoflagger<sup>TM</sup> will output an over temperature detection signal and then this signal is sent to the eFuse IC which cuts off the current. In addition to eFuse IC functions, this design can be used to create a compact circuit that cuts off the output current when over temperature is detected at several points on the BOARD.

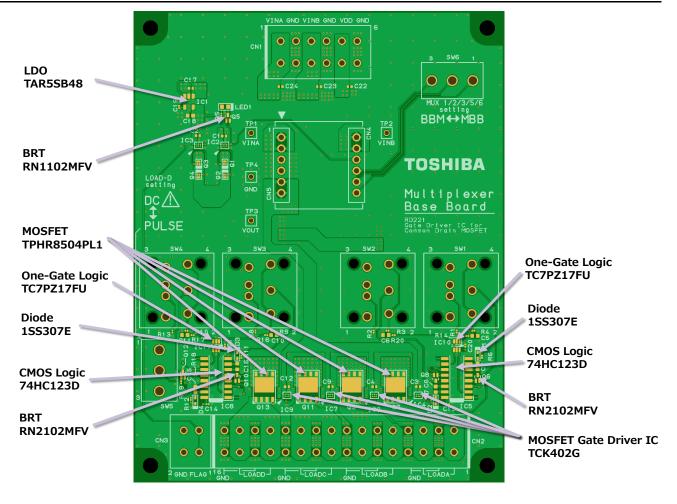

The base board is used for evaluating the module board. It is equipped with the N-ch power MOSFETs <u>TPHR8504PL1</u>, the MOSFET gate driver ICs <u>TCK402G</u>, the <u>transistors with bias resistors</u> for signal-control, the <u>one-gate logic ICs</u> <u>TC7PZ17FU</u>, and the <u>CMOS logic ICs</u> <u>74HC123D</u>.

The base board is also used in the reference design of the <u>Power Multiplexer Circuit</u>.

### 2. Specifications and Appearance

### 2.1. Specifications

Table 2.1 and Table 2.2 show the specifications of the module board and the base board.

| Board Name                | Input Voltage        | Rated<br>Output Current                   |

|---------------------------|----------------------|-------------------------------------------|

| eFuse Application Circuit | Min. 2.7V<br>Typ. 5V | 1.1A (Typ.),<br>up to 4A with appropriate |

| (with Thermal Shutdown)   | Max. 6V              | resistor setting                          |

### Table 2.1 Module Board Specifications

### Table 2.2 Base Board Specifications

| Input/Output | Description                                                                                                                                                                                                                             |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input        | VINA input (VINA 2.7V to 6V)<br>VINB input (not used)<br>Drive power supply (VDD 5V to 12V)                                                                                                                                             |

| Output       | Output load A to D (LOAD-A to LOAD-D, each Load can have both resistive<br>load and capacitive load, Max current is 4A for the module board of this<br>design)<br>FLAG output (H-level (approximately 5V) is output when VINA is input) |

### 2.2. Block Diagrams

### 2.2.1. Module Board Block Diagram

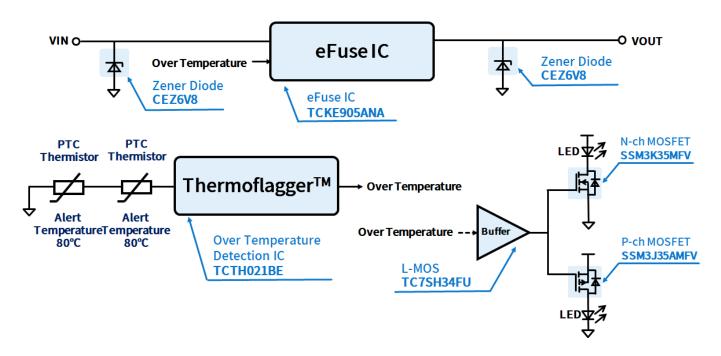

Fig. 2.1 shows the block diagram of the module board (eFuse Application Circuit (with Thermal Shutdown)).

Fig. 2.1 Module Board Block Diagram

### 2.2.2. Base Board Block Diagram

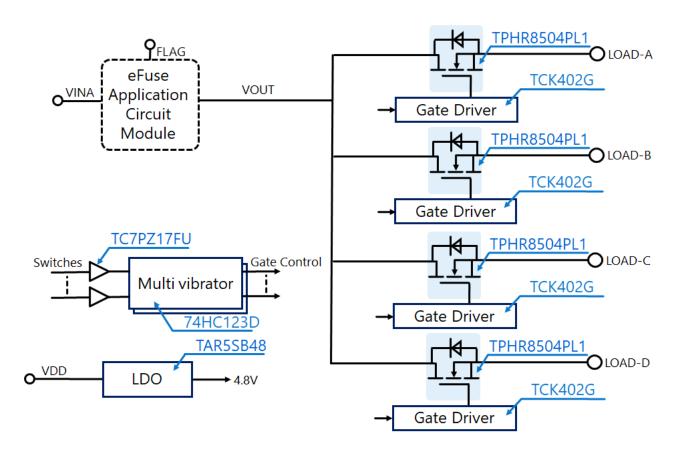

Fig. 2.2 shows the block diagram of the base board.

Fig. 2.2 Base Board Block Diagram

### 2.3. Appearance and Component Layout

The appearance and the component layout of the module board and the base board are shown below.

### 2.3.1. Module Board

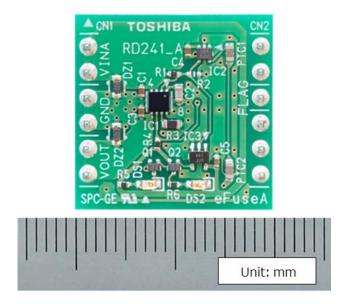

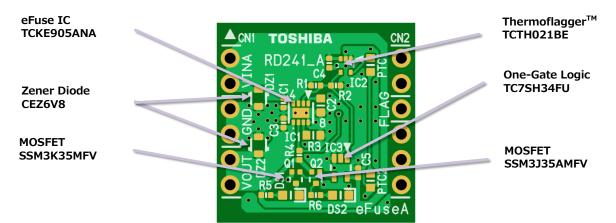

Fig. 2.3 shows the appearance and Fig. 2.4 and 2.5 show the component layout of the module board.

Fig. 2.3 Module Board (Top View)

Fig. 2.4 Module Board Component Layout (Top View)

Fig. 2.5 Module Board Component Layout (Bottom View)

### 2.3.2. Base Board

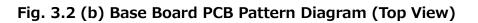

Fig. 2.6 shows the appearance and Fig. 2.7 shows the component layout of the base board.

Fig. 2.6 Base Board (Top View)

### RD241A-RGUIDE-01

Fig. 2.7 Base Board Component Layout (Top View)

### 3. Schematic, Bill of Materials, and PCB Pattern

### 3.1. Schematic

Refer to the following files: Module board RD241-SCHEMATIC1-xx.pdf Base board RD221-SCHEMATIC7-xx.pdf (xx is the revision number.)

### 3.2. Bill of Materials

Refer to the following files: Module board RD241A-BOM1-xx.pdf Base board RD221-BOM7-xx.pdf (xx is the revision number.)

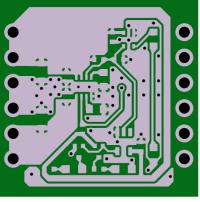

### 3.3. PCB Pattern

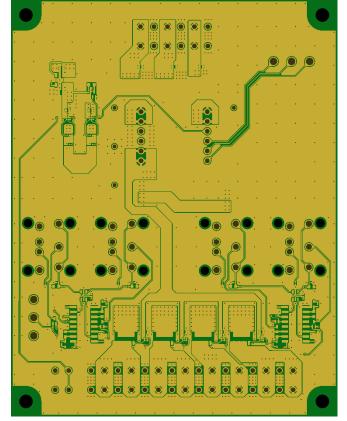

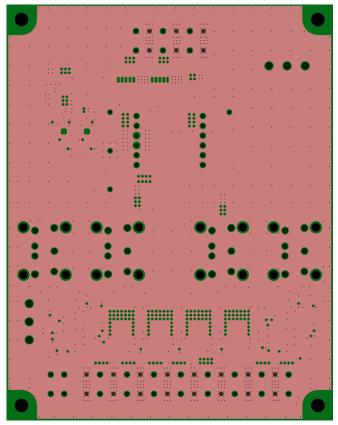

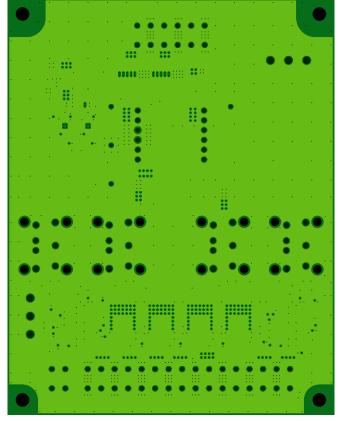

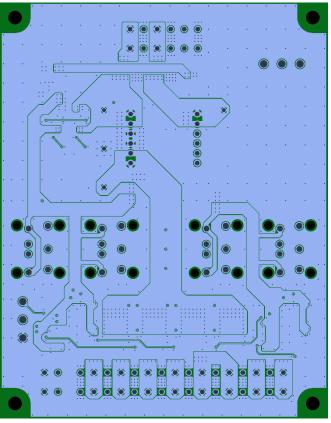

Fig. 3.1 shows the PCB pattern diagram of the module board, and Fig. 3.2 shows the pattern diagram of the base board.

For more details, refer to the following files: Module board RD241-LAYER1-xx.pdf Base board RD221-LAYER7-xx.pdf (xx is the revision number.)

<Layer 1 Top>

<Layer 2 Bottom>

Fig. 3.1 Module Board PCB Pattern Diagram (Top View)

### RD241A-RGUIDE-01

<LAYER1 Top>

<LAYER2>

### RD241A-RGUIDE-01

<LAYER3>

<LAYER4 Bottom>

### 4. Operation

### 4.1. Operation Procedure

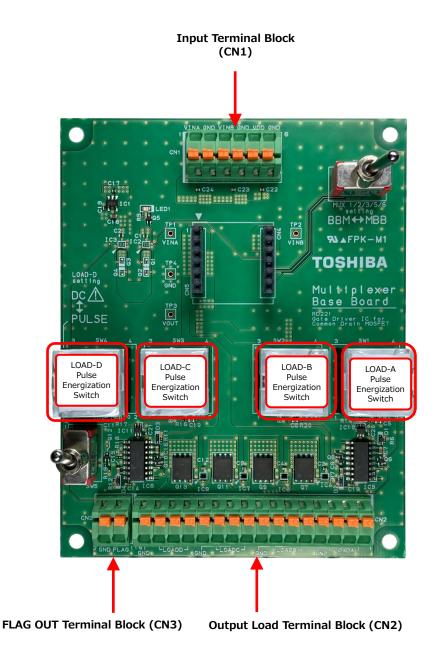

The standard procedure to start up this design is as follows:

- 1. Connect the module board to the module board connector (CN4, CN5) on the base board as shown in Fig. 4.2.

- 2. At CN1 terminal block of the baseboard, first apply VDD power supply (5V), and then apply VINA power supply (5V).

- To stop the operation, first turn off VINA power supply, and then turn off VDD power supply.

\*Be careful not to get burned from the overheated load resistance.

Fig. 4.1 Connectors and Switches on the Base Board

Fig. 4.2 Connection Between Base Board and Module Board

### 4.2. Base Board External Connector Specifications

The external connector specifications of the base board are as follows.

| Table 4.1 Input Terminal Block (CN1) Specifications |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Terminal<br>No. | Input<br>Terminal<br>Name | Description                                                                 | Voltage Range | Current Rating |

|-----------------|---------------------------|-----------------------------------------------------------------------------|---------------|----------------|

| 1               | VINA                      | eFuse Application Circuit (with<br>Thermal Shutdown)<br>VINA input terminal | Max. 6V       | Max. 4A*       |

| 2               | GND                       | (GND of the above terminal)                                                 |               |                |

| 3               | VINB                      | (not used)                                                                  |               |                |

| 4               | 4 GND (not used)          |                                                                             | _             | -              |

| 5               | VDD                       | Power supply terminal for driving the base board                            | 5V to 12V -   |                |

| 6               | GND                       | (GND of the above terminal)                                                 |               |                |

\* Individual component specifications allow a current flow greater than this value. However, the current on this board should not exceed this value because of the heat dissipation limitation.

| Terminal No. | Output Load<br>Name | Description                    |  |

|--------------|---------------------|--------------------------------|--|

| 1            |                     | For resistive load connection  |  |

| 2            | LOAD-A              | (GND of the above terminal)    |  |

| 3            | LUAD-A              | For capacitive load connection |  |

| 4            |                     | (GND of the above terminal)    |  |

| 5            | LOAD-B              | For resistive load connection  |  |

| 6            |                     | (GND of the above terminal)    |  |

| 7            |                     | For capacitive load connection |  |

| 8            |                     | (GND of the above terminal)    |  |

| 9            |                     | For resistive load connection  |  |

| 10           | LOAD-C              | (GND of the above terminal)    |  |

| 11           | LUAD-C              | For capacitive load connection |  |

| 12           |                     | (GND of the above terminal)    |  |

| 13           | LOAD-D              | For resistive load connection  |  |

| 14           |                     | (GND of the above terminal)    |  |

| 15           |                     | For capacitive load connection |  |

| 16           |                     | (GND of the above terminal)    |  |

### Table 4.2 Output Load Terminal Block (CN2) Specifications

### Table. 4.3 FLAG Out Terminal Block (CN3) Specifications

| Terminal No. | Output Terminal<br>Name | Description                                                       |

|--------------|-------------------------|-------------------------------------------------------------------|

| 1            | FLAG                    | FLAG output<br>H-level (approximately 3.3V) when<br>VINA is input |

| 2            | GND                     | (GND of the above terminal)                                       |

### 4.3. Module Board Operation Summary

### 4.4. Over Temperature Detection

In this design the temperature above 80°C is considered abnormal temperature. If the temperature of either of the two PTC thermistors (PTC1, PTC2) connected to PTCO terminal of TCTH021BE (IC2) exceeds approximately 80 °C (abnormal temperature), the PTCGOOD terminal changes from High level to Low level. This signal is connected to EN/UVLO terminal of TCKE905ANA (IC1) and the input terminal of TC7SH34FU (IC3), which cuts off the output VOUT of TCKE905ANA (IC1), turns off SSM3K35MFV (Q1) and turns on SSM3J35AMFV (Q2), this turns off the blue LED (DS1) and turns on the red LED (DS2).

### 4.5. Output Overcurrent Detection

TCKE905ANA (IC1) has an overcurrent protection function. If a current of approximately 1.1A or more flows from the terminal VOUT, the overcurrent protection function activates to cut off VOUT and FLAG terminal changes from High level to Low level.

### 5. Precautions

- •Be careful of the electric shock as the applied voltage is high.

- •Be careful not to get burned from the heat generated at the load.

### Terms of Use

This terms of use is made between Toshiba Electronic Devices and Storage Corporation ("We") and Customer who downloads or uses this Reference Design. Customer shall comply with this terms of use. This Reference Design means all documents and data in order to design electronics applications on which our semiconductor device is embedded.

#### Section 1. Restrictions on usage

This Reference Design is provided solely as reference data for designing electronics applications. Customer shall not use this Reference Design for any other purpose, including without limitation, verification of reliability.

Customer shall not use this Reference Design for sale, lease or other transfer.

3. Customer shall not use this Reference Design for evaluation in high or low temperature, high humidity, or high electromagnetic environments.

4. This Reference Design shall not be used for or incorporated into any product or system whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

#### Section 2. Limitations

1. We reserve the right to make changes to this Reference Design without notice.

2. This Reference Design should be treated as a reference only. WE ARE NOT RESPONSIBLE FOR ANY INCORRECT OR INCOMPLETE DATA AND INFORMATION.

Semiconductor devices can malfunction or fail. When designing electronics applications by referring to this Reference Design, Customer is responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of semiconductor devices could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Customer must also refer to and comply with the latest versions of all relevant our information, including without limitation, specifications, data sheets and application notes for semiconductor devices, as well as the precautions and conditions set forth in the "Semiconductor Reliability Handbook".

Designing electronics applications by referring to this Reference Design, Customer must evaluate the whole system sufficiently. Customer is solely responsible for applying this Reference Design to Customer's own product design or applications. WE ASSUME NO LIABILITY FOR CUSTOMER'S PRODUCT DESIGN OR APPLICATIONS.

WE SHALL NOT BE RESPONSIBLE FOR ANY INFRINGEMENT OF PATENTS OR ANY OTHER INTELLECTUAL PROPERTY RIGHTS OF THIRD PARTIES THAT MAY RESULT FROM THE USE OF THIS REFERENCE DESIGN. NO LICENSE TO ANY INTELLECTUAL PROPERTY RIGHT IS GRANTED BY THIS TERMS OF USE, WHETHER EXPRESS OR

IMPLIED, BY ESTOPPEL OR OTHERWISE. 6. THIS REFERENCE DESIGN IS PROVIDED "AS IS". WE (a) ASSUME NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (b) DISCLAIM ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO THIS REFERENCE DESIGN, INCLUDING WITHOUT LIMITATION, WARRANTIES OR CONDITIONS OF FUNCTION AND WORKING, WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

#### Section 3. Terms and Termination

It is assumed that Customer agrees to any and all this terms of use if Customer downloads or uses this Reference Design. We may, at its sole and exclusive discretion, change, alter, modify, add, and/or remove any part of this terms of use at any time without any prior notice. We may terminate this terms of use at any time and without any cause. Upon termination of this terms of use, Customer shall eliminate this Reference Design. Furthermore, upon our request, Customer shall submit to us a written confirmation to prove elimination of this Reference Design.

#### Section 4. Export Control

Customer shall not use or otherwise make available this Reference Design for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). This Reference Design may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Act and the U.S. Export Administration Regulations. Export and re-export of this Reference Design is strictly prohibited except in compliance with all applicable export laws and regulations.

#### Section 5. Governing Laws

This terms of use shall be governed and construed by laws of Japan, without reference to conflict of law principle.

#### Section 6. Jurisdiction

Unless otherwise specified, Tokyo District Court in Tokyo, Japan shall be exclusively the court of first jurisdiction for all disputes under this terms of use.