# Gate Drive Circuit for SiC MOSFET Module

# Design guide

RD237-DGUIDE-01

**Toshiba Electronic Devices & Storage Corporation**

# **Table of Contents**

| 1. Iı                                                               | ntroduction                                              | .4                               |

|---------------------------------------------------------------------|----------------------------------------------------------|----------------------------------|

| 2. M                                                                | ain Components Used                                      | .5                               |

| 2.1.                                                                | Pre-Driver Coupler TLP5231                               | . 5                              |

| 2.2.                                                                | LDO Regulator IC TCR1HF50B                               | . 6                              |

| 2.3.                                                                | High-Speed Comparator IC TC75S57FU                       | . 7                              |

| 2.4.                                                                | Small Package MOSFET TPC8132                             | . 7                              |

| 2.5.                                                                | Tiny Package MOSFET SSM6K804R                            | . 8                              |

| 2.6.                                                                | Small Signal MOSFET SSM3K318R                            | . 8                              |

| 2.7.                                                                | Small Signal MOSFET SSM3K15AFS                           | . 9                              |

| 2.8.                                                                | Small Signal NPN Bipolar Transistor 2SC6026MFV           | . 9                              |

|                                                                     |                                                          |                                  |

| 3. 0                                                                | utline of Gate Driver for SiC MOSFET Module1             | L <b>O</b>                       |

| 3. O<br><sub>3.1.</sub>                                             | utline of Gate Driver for SiC MOSFET Module1  Features   |                                  |

|                                                                     | Features                                                 | 10                               |

| 3.1.<br>3.2.                                                        | Features                                                 | 10<br>10                         |

| 3.1.<br>3.2.<br>3.3.                                                | Features  Pin Description                                | 10<br>10<br>11                   |

| 3.1.<br>3.2.<br>3.3.<br><b>4. C</b>                                 | Pin Description                                          | 10<br>10<br>11                   |

| 3.1.<br>3.2.<br>3.3.<br><b>4. C</b><br>4.1.<br>4.2.<br>4.2.<br>4.2. | Features  Pin Description  Specifications  ircuit Design | 10<br>11<br>13<br>13<br>14<br>14 |

# RD237-DGUIDE-01

| 4.4. G  | ate Drive Circuit (Secondary Side of TLP5231)    | 20 |

|---------|--------------------------------------------------|----|

| 4.4.1.  | Buffer MOSFET                                    | 20 |

| 4.4.2.  | External Gate Resistor Setting                   | 22 |

| 4.5. P  | rotection Circuit                                | 24 |

| 4.5.1.  | DESAT (Desaturation) Detection Circuit Operation | 24 |

| 4.5.2.  | UVLO Function (Under Voltage Lock Out)           | 28 |

| 4.5.3.  | Active Miller Clamp (AMC)                        | 29 |

| 4.6. Te | emperature Detection Output                      | 30 |

# 1. Introduction

This design guide (hereafter referred to as this guide) describes the design methodology of the Gate Drive Circuit for SiC MOSFET Module (hereafter referred to as this design).

SiC (Silicon Carbide) MOSFETs have been developed in recent years because they allow the reduction of on-resistance while maintaining a higher breakdown voltage compared to the conventional Si (Silicon) MOSFETs. Therefore, these are being evaluated and adopted more and more with the aim of improving inverter efficiency.

SiC MOSFET modules equipped with SiC MOSFET chips are used in power conversion in motor drives used in industrial applications and inverters for railroad cars contributing to a more efficient and compact industrial equipment.

This design uses the pre-driver <u>TLP5231</u> that is capable of high-current gate drive by using external buffer MOSFETs and has various protection functions to achieve isolated gate drive for high-current and high-voltage SiC MOSFET modules.

This design is optimized for driving the gates of Toshiba's Dual SiC MOSFET modules (MG400V2YMS3, MG600Q2YMS3, MG250YD2YMS3). By using this design, the application circuit of the SiC MOSFET module can be easily configured.

It is equipped with two gate drive circuits to match the above-mentioned SiC MOSFET modules, and in addition it is miniaturized to the same size as that of the module so that it can be mounted directly on top of the module, therefore creating an excellent solution for suppressing parasitic inductance in wiring.

This design features a variety of the protection circuits, including DESAT (desaturation) detection function, active miller clamp function, etc. In addition, each component can be adjusted according to the actual target specifications.

For more details about Toshiba's SiC MOSFET modules, kindly refer to their datasheets and other related documents.

When using a SiC MOSFET module other than the above-mentioned modules, each component needs to be adjusted. Refer to the datasheet and other related documents of TLP5231, the design guide of this reference design, etc. for adjusting each component.

Image of this design attached directly to Toshiba's Dual SiC MOSFET Module

# 2. Main Components Used

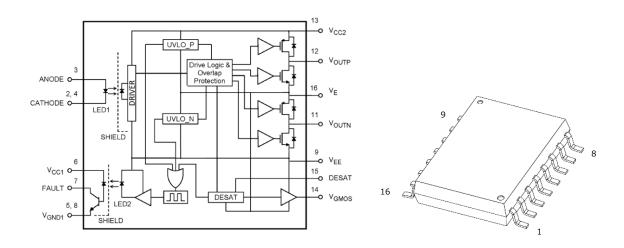

# 2.1. Pre-Driver Coupler TLP5231

This design uses TLP5231 pre-drive photocouplers that are capable of high-current gate-drive by using an external buffer MOSFET and incorporates various protection functions. The main features of TLP5231 are as follows.

• Output peak current: ±2.5A (Max.)

• Operating temperature: -40 to 110°C

• Threshold input current: 3.5mA (Max.)

• Propagation delay time: 300ns (Max.)

Common-mode transient immunity: ±25kV/µs (Min.)

Isolation voltage: 5000Vrms (Min.)

• Dual output for external complementary type MOS buffer

• Under Voltage Lock-Out (UVLO) protection for positive and negative gate power supply

Safety Standards

UL recognized: UL 1577, File No.E67349

cUL recognized: CSA Component Acceptance Service No.5A File No.E67349

VDE approved: EN 60747-5-5, EN 62368-1 (Note 2.1)

CQC approved: GB4943.1, GB8898 Japan Factory

Note: When a VDE approved type is needed, please designate the "Optional (D4)".

• Structural parameter: Minimum creepage and clearance 8mm

Fig. 2.1 TLP5231 Internal Circuit Configuration and Package (SO16L)

5/31

2024-07-23

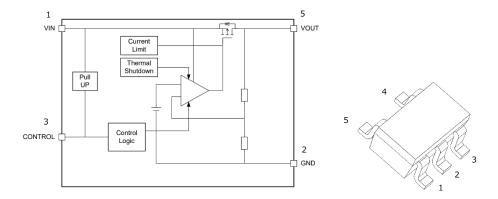

#### 2.2. LDO Regulator IC TCR1HF50B

This design uses TCR1HF50B LDO regulators for producing the internal 5V power supply. The main features of TCR1HF50B are as follows.

- High maximum input voltage: 40V (Max.), Operation input voltage range: 4V to 36V

- Low quiescent current  $I_{BON} = 1\mu A$  (Typ.) @  $I_{OUT} = 0mA$

- High response load transient

- -60mV/+50mV @ 3.3V output,  $I_{OUT} = 0mA \leftrightarrow 10mA$

- ◆ High accuracy output voltage: ±1% (Ta = 25°C)

- Built-in overcurrent protection circuit

- Built-in overheat protection circuit

- Built-in inrush current reduction circuit

- Pull up connection between CONTROL and VIN

- Ceramic capacitors can be used

- General package SMV (SOT-25) (2.9mm x 2.8mm x 1.1mm)

•

Fig. 2.2 TCR1HF50B Internal Circuit Configuration and Package (SOT-25)

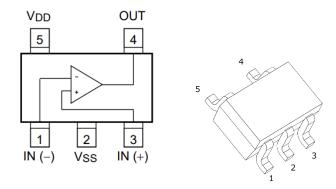

#### 2.3. High-Speed Comparator IC TC75S57FU

This design uses CMOS type general-purpose single comparators (TC75S57FU) in active miller clamp circuits. The main features of TC75S57FU are as follows.

- Low current consumption:  $I_{DD} = 100 \mu A$  (Typ.)

- Single power supply operation:  $V_{DD} = \pm 0.9$  to  $\pm 3.5 \text{V}$  or 1.8 to 7V

- Wide common mode input voltage range: V<sub>SS</sub> to V<sub>DD</sub> 0.9V

- Push-pull output circuit

- Low input bias current

- Small package

Fig. 2.3 TC75S57FU Internal Circuit Configuration and Package (SOT-353)

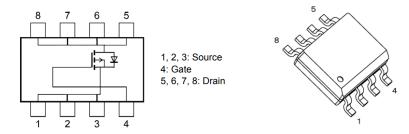

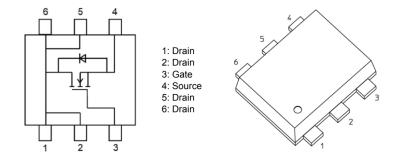

#### 2.4. Small Package MOSFET TPC8132

This design uses TPC8132 P-ch MOSFETs as buffer for gate-drive of TLP5231. The main features of TPC8132 are as follows.

- Small footprint due to small and thin package

- Low drain-source on-resistance:  $R_{DS(ON)} = 20 m\Omega$  (Typ.) (V<sub>GS</sub> =-10V)

- Low leakage current: I<sub>DSS</sub> =-10µA (Max.) (V<sub>DS</sub> =-40V)

- Enhancement mode:  $V_{th} = -0.8$  to -2.0V ( $V_{DS} = -10V$ ,  $I_D = -0.2mA$ )

Fig. 2.4 TCP8132 Internal Circuit Configuration and Package (SOP-8)

2024-07-23

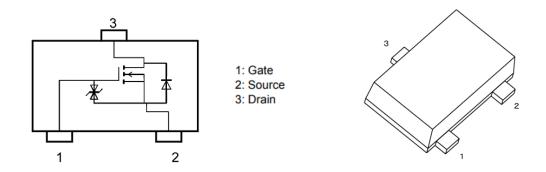

# 2.5. Tiny Package MOSFET SSM6K804R

This design uses SSM6K804R N-ch MOSFETs as buffer for gate-drive of TLP5231 and in the DESAT detection soft turn-off. The main features of SSM6K804R are as follows.

- 175°C MOSFET

- 4.5V drive

- Low drain-source on-resistance

```

R_{DS(ON)} = 12m\Omega \text{ (Typ.) (@V_{GS} = 4.5V)}

R_{DS(ON)} = 9m\Omega \text{ (Typ.) (@V_{GS} = 10V)}

```

Fig. 2.5 SSM6K804R Internal Circuit Configuration and Package (TSOP6F)

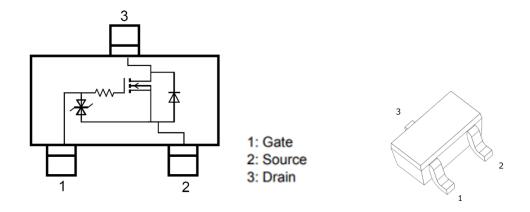

# 2.6. Small Signal MOSFET SSM3K318R

This design uses SSM3K318R N-ch MOSFET in the active miller clamp circuit. The main features of SSM3K318R are as follows.

- 4.5V gate drive voltage

- Low drain-source on-resistance

$$R_{DS(ON)} = 145 m\Omega \text{ (Max.) (@V_{GS} = 4.5V)}$$

$R_{DS(ON)} = 107 m\Omega \text{ (Max.) (@V_{GS} = 10V)}$

Fig. 2.6 SSM3K318R Internal Circuit Configuration and Package (SOT-23F)

#### 2.7. Small Signal MOSFET SSM3K15AFS

This design uses SSM3K15AFS N-ch MOSFETs in the input-drive (photocoupler) of TLP5231. The main features of SSM3K15AFS are as follows.

- 2.5V drive

- Low on-resistance

```

R_{DS(ON)} = 3.6\Omega \text{ (Max.) (@V_{GS} = 4V)}

R_{DS(ON)} = 6.0\Omega \text{ (Max.) (@V_{GS} = 2.5V)}

```

Fig. 2.7 SSM3K15AFS Internal Circuit Configuration and Package (SOT-416)

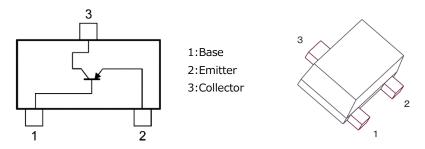

#### 2.8. Small Signal NPN Bipolar Transistor 2SC6026MFV

This design uses 2SC6026MFV NPN bipolar transistors in the fault detector circuit. The main features of 2SC6026MFV are as follows.

- High withstand voltage: V<sub>CEO</sub> = 50V

- High collector current: I<sub>C</sub> = 150mA (Max.)

- High current amplification factor: h<sub>FE</sub> = 120 to 400

- Excellent  $h_{FE}$  linearity:  $h_{FE}$  (IC = 0.1mA)/ $h_{FE}$  (IC = 2mA) = 0.95 (Typ.)

Fig. 2.8 2SC6026MFV Internal Circuit Configuration and Package (SOT-723)

# 3. Outline of Gate Driver for SiC MOSFET Module

This design is a gate drive circuit that can drive Toshiba's Dual SiC MOSFET Modules. This design is equipped with the gate-drive circuit using the pre-drive photocoupler TLP5231, an insulated power supply, and protection circuits.

#### 3.1. Features

- High-current gate-drive via external buffer MOSFETs

- Single power supply operation with isolated DC-DC circuit

- Short-circuit proof (using DESAT detection)

- Low gate-drive voltage detection (UVLO)

- Active Miller Clamp (AMC)

- Output on/off control

- Fault detection output

- Temperature monitor output

# 3.2. Pin Description

It features a controller connector (CN1) as the external interface and uses a XG4A-1431 (Omron connector.

Table 3.1 Controller Connector (CN1) Specifications

| Pin# | Signal<br>Name | I/O | Description                                                          | Pin# | Signal<br>Name | I/O | Description                                                           |

|------|----------------|-----|----------------------------------------------------------------------|------|----------------|-----|-----------------------------------------------------------------------|

| 1    | GND            | -   | GND                                                                  | 2    | VDD            | -   | Power supply voltage for control                                      |

| 3    | (N.C.)         | -   |                                                                      | 4    | B_INA          | I   | Low-side gate control<br>signal input                                 |

| 5    | B_FLT          | 0   | Low-side fault<br>detection output<br>(Resistor collector<br>output) | 6    | B_ENA          | I   | Low-side enable signal<br>input                                       |

| 7    | A_INA          | I   | High-side gate control signal input                                  | 8    | (N.C.)         | ı   |                                                                       |

| 9    | A_ENA          | I   | High-side enable<br>signal input                                     | 10   | (5V)           | -   | External 5V power<br>supply pin<br>(Optional)                         |

| 11   | GND            | -   | GND                                                                  | 12   | A_FLT          | 0   | High-side fault<br>detection output<br>(Resistor collector<br>output) |

| 13   | TH1            | 0   | Temperature detection output 1                                       | 14   | TH2            | 0   | Temperature detection output 2                                        |

# 3.3. Specifications

Table 3.2 lists the recommended operating ranges of the gate drivers for SiC MOSFET modules. Table 3.3 lists the electrical properties of the gate drive output-voltage and the protective functions.

**Table 3.2 Recommended Operation Range**

| Item                                                        | Min.            | Тур.       | Max. | Unit |      |     |

|-------------------------------------------------------------|-----------------|------------|------|------|------|-----|

| Power supply voltage for control                            |                 | $V_{DD}$   | 20.0 | 24   | 28.0 | ٧   |

| Input signal                                                | INPUT           | High Level | 4.0  | -    | 5.0  | V   |

| (gate control signal, enable signal)                        |                 | Low Level  | 0    | 1    | 1.8  |     |

| Switching Frequency Note 3.1 (SiC MOSFET module gate drive) | f <sub>sw</sub> |            | -    | -    | 50   | kHz |

Note 3.1: Set frequency such that each component remains within its rated temperature range in actual application.

2024-07-23

**Table 3.3 Electrical Characteristics**

| Item                                                          | Symbol                                                 | Conditions                                                                    | Min  | Тур. | Max  | Unit |

|---------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| Gate drive output<br>High voltage                             | V <sub>CC2</sub>                                       |                                                                               | 18.5 | 20   | 21.5 | ٧    |

| Gate drive output<br>Low voltage                              | V <sub>EE</sub>                                        |                                                                               | -7.2 | -6.7 | -6.2 | V    |

| UVLO_P threshold                                              | V <sub>UVLOP</sub> –                                   | Protection operation voltage @IF = 8mA V <sub>OUTP</sub> -V <sub>E</sub> > 5V | 11   | 12   | 13   | V    |

| (V <sub>CC2</sub> -V <sub>E</sub> )                           | V <sub>UVLOP+</sub>                                    | Protection release voltage $@IF = 8mA$ $V_{OUTP}$ - $V_E < 5V$                | 12   | 13   | 14   | V    |

| UVLO_N Threshold                                              | V <sub>UVLON</sub> -                                   | Protection operation voltage $ @IF = 8mA $ $V_{OUTN}$ - $V_E > 1V$            | -5.7 | -5.0 | -4.7 |      |

| (V <sub>E</sub> -V <sub>EE</sub> )                            | V <sub>UVLON+</sub>                                    | Protection release voltage                                                    | -6   | -5.3 | -5   | V    |

| Drain-source voltage<br>when DESAT is<br>detected<br>Note 3.2 | V <sub>DS</sub> (High side) V <sub>DS</sub> (Low side) | V <sub>CC2</sub> -V <sub>E</sub> = 20V<br>Ta = 25℃                            | 0.46 | -    | -    | V    |

| Thermistor rated                                              | rated                                                  | Tc = 25℃                                                                      | 3.5  | 5.0  | 6.5  | kΩ   |

| resistance                                                    | resistance                                             |                                                                               | 125  | 165  | 205  | Ω    |

| Thermistor B<br>constant                                      | В                                                      | TNTC = 25 to 150℃                                                             | -    | 3375 | -    | К    |

Note 3.2 When DESAT is detected, the drain-source voltage is equal to DESAT threshold voltage of TLP5231 minus the voltage drop across the diodes (D703, D704, D705, D706) and the resistor (R708).

# 4. Circuit Design

# 4.1. Overall Block Diagram

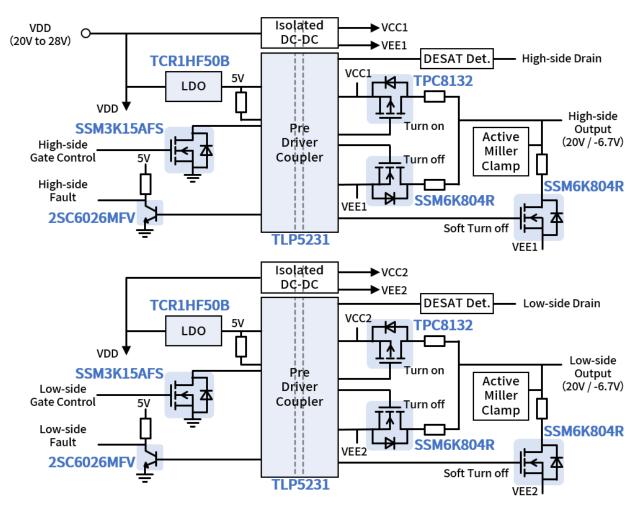

Fig. 4.1 shows the block diagram of the gate driver for SiC MOSFET module. It is equipped with TLP5231 pre-drive photocouplers, isolated DCDC converters, and active miller clamp circuits that enable high-current gate-drive via external buffer MOSFETs. It operates according to the control power supply voltage supplied from VDD.

Fig. 4.1 Gate Driver Block Diagram for SiC MOSFET Module

# 4.2. Gate Control Circuit (Primary Side of TLP5231)

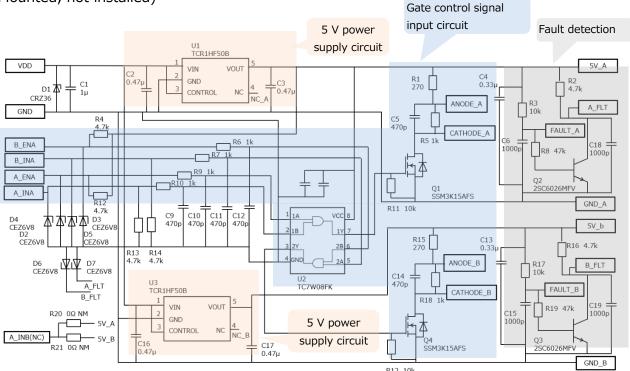

Fig. 4.2 shows the circuit of the primary side (input side) of TLP5231. (NM stands for Not Mounted, not installed)

Fig. 4.2 Primary Control Circuit

# 4.2.1. 5 V Power Supply Circuit

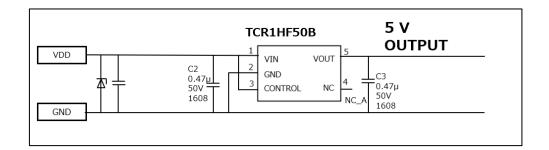

Fig. 4.3 shows 5V power supply circuit. It uses TCR1HF50B LDO regulators (U1, U3) to produce 5V from VDD.

The 5V output of TCR1HF50B is supplied to the primary-side power supply input  $V_{\text{CC1}}$  of TLP5231(U300, U400), the gate-control-signal input circuit, and the fault-detection output circuit . There is no problem if a common TCR1HF50B is used as a power supply for the high-side and low-side drives, but separate TCR1HF50B are used for each high-side and low-side to distribute the losses.

Fig. 4.3 TCR1HF50B (LDO Regulator) Circuit

#### 4.2.2. Gate Control Signal Input

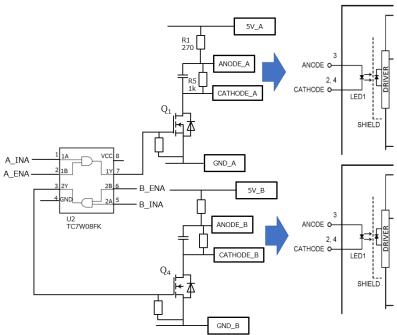

Fig. 4.4 shows the gate control signal input circuit.

A\_INA (input signal) and A\_ENA (enable) are the gate control signal inputs for the high side. A\_ENA can control enable/disable of gate drive output. When enabled, the A\_ENA signal is High and when disabled A\_ENA signal is Low. When A\_ENA is open, it is enabled because it is pulled up by the internal circuit. A\_INA and A\_ENA are input to TC7W08FK (AND circuit), and the output 1Y is input to the gate of MOSFET  $Q_1$ . When both A\_INA and A\_ENA are H (the output 1Y is H), the MOSFET  $Q_1$  turns on and an input on-current  $I_{F(ON)}$  flows between ANODE\_A and CATHODE\_A of TLP5231 for the high-side. This  $I_{F(ON)}$  activates the high-side SiC MOSFET module. When 1Y is Low, there is no  $I_F$  flow between ANODE\_A and CATHODE\_A, so SiC MOSFET module is disabled.

Fig. 4.4 Gate Control Signal Input Circuit

$I_{\text{F}}$  (LED input forward current) between the primary anode and TLP5231 is expressed by the following equation:

$$I_F = \frac{V_{DD} - V_F}{R1} - \frac{V_F}{R5} \tag{4-1}$$

To set  $I_F$  of TLP5231 equal to 11mA, the current flowing through R1 must be 12.6mA. R1 is connected to 5V power supply, and the current flowing to R5 becomes 1.6mA. The typical input forward voltage VF of TLP5231 between anode and cathode is 1.58V. Now, R1 and R5 are determined by the following equations.

© 2024

Toshiba Electronic Devices & Storage Corporation

$$R1 = \frac{V_{DD} - V_F}{12.6mA} = \frac{5V - 1.58V}{12.6mA} = 271\Omega$$

$$R5 = \frac{V_F}{1.6 \, mA} = \frac{1.58 \, V}{1.6 \, mA} = 988\Omega$$

In the actual circuit, R1 of  $270\Omega$  and R5 of  $1000\Omega$  are selected to be close to the values calculated above.

The  $I_F$  can be calculated using these resistance values as follows.

$$I_F = \frac{5V - 1.58V}{270\Omega} - \frac{1.58V}{1000\Omega} = 11.08mA$$

The gate control signal input B\_INA (input signal) and B\_ENA (enable) for the low side also perform the same operation as the high side.

Table 4.1 shows the truth values.

**Table 4.1 Truth Table**

| A_INA<br>(CN1:Pin7) | A_ENA<br>(CN1:Pin9) | I <sub>F(ON)</sub> _A | SiC MOSFET<br>Module _A |

|---------------------|---------------------|-----------------------|-------------------------|

| L                   | L                   | OFF                   | OFF                     |

| Н                   | L                   | OFF                   | OFF                     |

| Н                   | Н                   | ON                    | ON                      |

| L                   | Н                   | OFF                   | OFF                     |

Since a pull-up resistor is connected to the A\_ENA terminal in this design, if the A\_ENA signal is not input, it will be in the active state. A L-level input is required to set the A\_ENA signal to disable state.

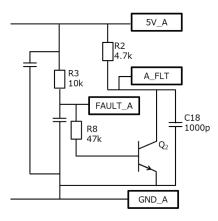

#### 4.2.3. Fault Detection Output Circuit

Fig. 4.5 shows the high side fault detection output circuit.

In this design, when a high side fault (Under-voltage protection and DESAT operation) is detected in the SiC MOSFET module, the FAULT\_A signal of TLP5231 is inverted and output as A\_FLT signal. When a fault is detected, the FAULT\_A goes to H level, the transistor Q2 turns on, and the A\_FLT goes to L level. The same applies to the low side. A\_FLT and B\_FLT are resistor pull-up collector outputs; therefore, they allow wired OR configuration. And, according to TLP5231 sequence, when Q702 gate ( $V_{GMOS}$ ) becomes L level, the normal operation is resumed, and the FLT pin goes from the L level to the H level.

Fig. 4.5 Fault Detection Output Circuit

| UVLO<br>(Under Voltage Lock Out) | DESAT Detected | FLT Output<br>(CN1:5pin,12pin) |

|----------------------------------|----------------|--------------------------------|

| Normal Operation                 | No             | H Level                        |

| Under Voltage Lock Out           | No             | L Level                        |

| Normal Operation                 | Yes            | L Level                        |

| Under Voltage Lock Out           | Yes            | L Level                        |

**Table 4.2 Fault Output Truth Table**

Rev.1

### 4.3. Gate Drive Power Supply Circuit

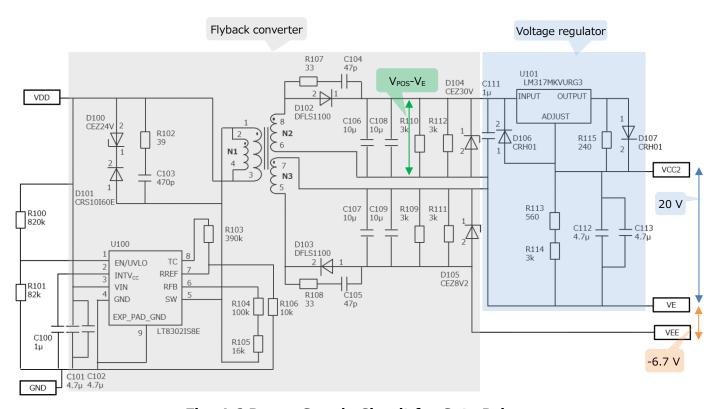

Fig. 4.6 shows the high-side gate drive power supply circuit. The gate-drive power supply consists of an isolated DC-DC converter and a voltage regulator. The isolated DC-DC converter is a flyback converter that converts the control power supply voltage VDD into a positive voltage 24 V (V<sub>POS</sub>-V<sub>E</sub>) and a negative voltage -6.7V (V<sub>EE</sub>-V<sub>E</sub>). The turn-on gate-drive output voltage (VCC2-VE) is regulated from a positive voltage of 24V to 20V by the voltage regulator (U101). The turn-off gate-drive output voltage (VEE-VE) is a negative voltage -6.7V.

These gate drive output voltages are set considering the rated gate voltages and the gate switching properties of the used SiC MOSFET Module and the under voltage detection (UVLO) levels of TLP5231. The same applies to the low-side gate drive power supply circuit.

To change the positive or negative voltage, UVLO operation (V<sub>UVLOP+</sub>, V<sub>UVLON+</sub>) of TLP5231 used in this design must be adjusted. Note that TLP5231 does not operate unless both positive and negative power supplies are aligned, during evaluation, always apply a negative power supply at less than  $V_{UVLON+}$ -6.0V (Min.) even if only the positive power supply is acceptable.

Fig. 4.6 Power Supply Circuit for Gate Drive

LT8302 is used for the control IC of the flyback converter. The output voltage can be set by the following equation using the external resistors (R104, R105, R106) and the transformer winding rate ( $N_{PS2}$ ,  $N_{PS3}$ ).

$$V_{POS} - V_E = V_{REF} \times \left(\frac{R104 + R105}{R106}\right) \times \left(\frac{1}{N_{PS2}}\right) - V_F$$

$$V_E - V_{EE} = V_{REF} \times \left(\frac{R104 + R105}{R106}\right) \times \left(\frac{1}{N_{PS3}}\right) - V_F$$

$V_{REF} = 1.00V$  (LT8302 internal reference voltage)

$N_{PS2}$ ,  $N_{PS3}$  of the transformer must be adjusted to match the actual requirements. The winding ratios of this design are shown in Table 4.3.

VoltageWinding RatioPositive voltage24V $N_{PS2} = 0.5 (N1:N2)$ Negative voltage-6.7V $N_{PS3} = 1.8 (N1:N3)$

**Table 4.3 Winding Ratios of Transformer**

If there is an error in the measured output voltage  $V_E$  - $V_{EE~(MEAS)}$  with respect to the target output voltage  $V_E$  - $V_{EE}$  of the mounted resistance value (R104, R105), readjust it to the final resistance value (R104<sub>(FINAL)</sub>, R105<sub>(FINAL)</sub>) by using the following equation.

$$R_{104(FINAL)} + R_{105(FINAL)} = \frac{V_E - V_{EE}}{V_E - V_{EE \text{ (MEAS)}}} \times R_{106}$$

In this design, R104 =  $100k\Omega$  and R105 =  $16k\Omega$  are the readjusted values.

A LM317MKVURG3 is used as the voltage regulator IC that regulates the turn-on gate-drive output voltage ( $V_{CC2}$ - $V_E$ ).  $V_{CC2}$ - $V_E$  can be set by the following formula using the external resistors R113, R114, and R115.

In this design,  $V_{CC2}$ - $V_E$  is set to 20V.

$$V_{CC2} - V_E = V_{REF} \times \left(1 + \frac{R113 + R114}{R115}\right) + I_{ADJ} \times (R113 + R114)$$

$$V_{CC2} - V_E = 1.25V \times \left(1 + \frac{560\Omega + 3k\Omega}{240\Omega}\right) + 50\mu A \times (560\Omega + 3k\Omega) = 20V$$

$V_{REF} = 1.25V$  (LM317MKVURG3 internal reference voltage)

$I_{ADJ} = 50\mu A$  (LM317MKVURG3 ADJUST terminal outflow current)

$R113 = 560\Omega$ ,  $R114 = 3k\Omega$ ,  $R115 = 240\Omega$

# 4.4. Gate Drive Circuit (Secondary Side of TLP5231)

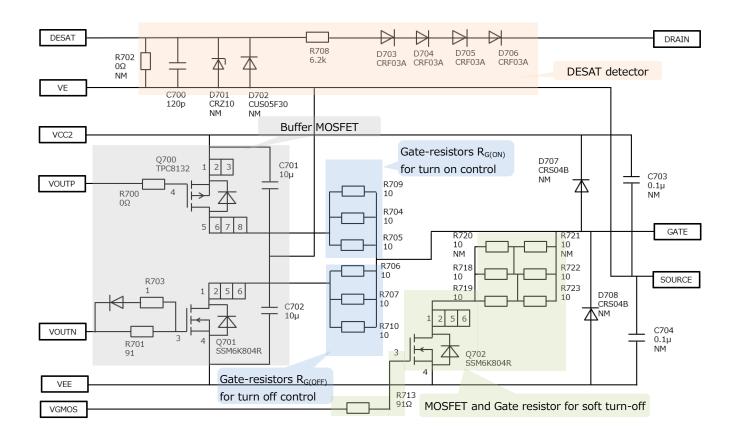

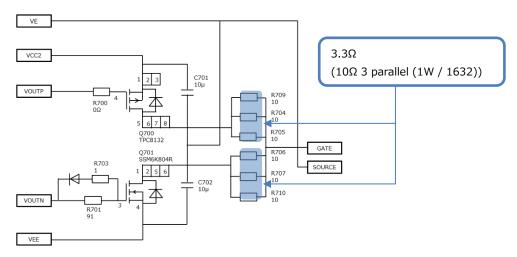

Fig. 4.7 shows the high-side gate drive circuit.

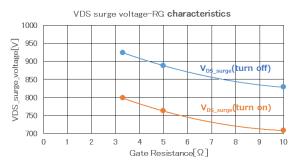

The gate drive circuit consists of buffer MOSFETs (Q700, Q701 for high-current gate drive), gate resistors for controlling turn-on/turn-off, a DESAT detection circuit, and a combination of resistors and a soft turn-off MOSFET for short-circuit protection.

Fig. 4.7 Gate Drive Circuit

When an input on-current  $I_{F(ON)}$  flows due to the gate control signal input, the  $V_{OUTP}$  output becomes Low ( $V_{OUTN}$  is Low) and the buffer P-ch MOSFET Q700 is turned on to charge the gate of the SiC MOSFET module and turn on the SiC MOSFET.

If the input on-current  $I_{F(ON)}$  does not flow, the  $V_{OUTN}$  output becomes High ( $V_{OUTP}$  is High) and the buffer N-ch MOSFET Q701 is turned on to discharge the gate of the SiC MOSFET module and turn off the SiC MOSFET.

#### 4.4.1. Buffer MOSFET

The MOSFETs used as the buffer MOSFETs are shown below.

P-ch MOSFET: TPC8132  $(V_{DSS} = 40V, I_D = -7A (DC), I_{DP} = -28A (Pulse))$ N-ch MOSFET: SSM6K804R  $(V_{DSS} = 40V, I_D = 12A (DC), I_{DP} = 50A (Pulse))$

The gate-drive average current  $I_{CHG\_SiC}$  in this design is 0.185A, and the gate drive peak current  $I_{CHG\_PEAK}$  is 9.9A. The current capability of the selected buffer MOSFET is sufficient to drive the gate.

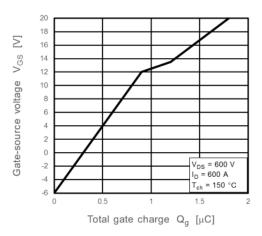

• Gate-drive average-current I<sub>CHG</sub> calculation

The gate charge ( $Q_g$ ) of our Dual SiC MOSFET module (MG600Q2YMS3) is estimated to be 1.85 $\mu$ C with  $V_{GS}$  change of -6.7 V to 20 V from Fig. 4.8.

Fig. 4.8 Total Gate Charge

From the following equation, the mean charge current required for gate-drive is 0.093A.

$$I_{CHG\ SiC} = Q_G \times f_{SW} = 1.85\mu C \times 50kHz = 0.093A$$

$f_{SW} = 50kHz$  (Gating control signal frequency)

If the SiC MOSFET module MG400V2YMS3 is used, I<sub>CHG SiC</sub> is 0.093A. (Same as MG600Q2YMS3)

● Calculation of gate-drive peak current I<sub>CHG\_PEAK\_MAX</sub>

To calculate the maximum peak current  $I_{CHG\_PEAK\_MAX}$  required for gate drive, the gate resistor  $R_{G(ON)}$  is considered  $0\Omega$ .

From equation (4-1) below, I<sub>CHG PEAK MAX</sub> becomes 9.9A.

The on-resistance of the gate-drive buffer MOSFET in this design is neglected because it is very small compared to  $r_{iq}$ .

$$I_{CHG\_PEAK\_MAX} = \frac{V_{GS}}{r_{ig} + R_{G(ON)}} = \frac{26.7V}{2.7\Omega + 0\Omega}$$

(4-1)

$V_{GS} = V_{CC2} - V_{EE} = 20V - (-6.7V) = 26.7V$

Inner-gate resistance of  $r_{ig} = 2.7\Omega$  (MG600Q2YMS3)

If the SiC MOSFET module MG400V2YMS3 is used, I<sub>CHG\_PEAK\_MAX</sub> is 7.6A.

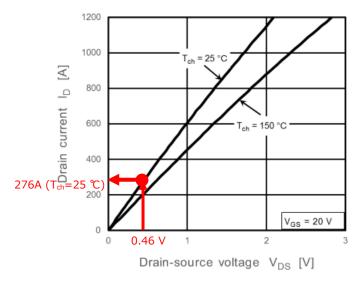

### 4.4.2. External Gate Resistor Setting

The gate drive circuit is shown in Fig. 4.9. The current path differs for turn-on and turn-off. Different gate resistor value settings are possible for turn-on and turn-off. The gate resistors are determined by considering the turn-on/turn-off times and resistance-loss based on Qg of SiC MOSFET module. In this design, the turn-on and turn-off gate resistors are set to  $3.3\Omega$  ( $10\Omega$  3 parallel, 1W, 1632 metric).

From Equation (4-1), the gate-drive peak current  $I_{CHG\_PEAK}$  with gate resistor  $R_{G(ON)}=3.3\Omega$  is 4.45A.

Fig. 4.9 Gate Drive Circuit

We evaluated MG600Q2YMS3 ( $V_{DS} \le 800V$ ,  $I_D \le 600A$ ), MG400V2YMS3( $V_{DS} \le 1200V$ ,  $I_D \le 400A$ ), MG250YD2YMS3( $V_{DS} \le 1200V$ ,  $I_D \le 250A$ ) in this design.

When designing an actual product, take the safety standard into consideration.

The following table shows the measured results using MG600Q2YMS3.

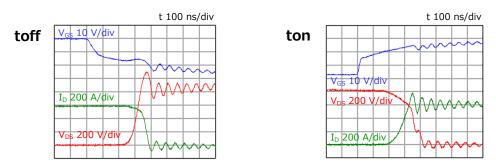

<Turn-on/Turn-off result>

Measuring conditions:  $V_{DS} = 800V$ ,  $I_D = 600A$ , lead-load  $100\mu H$ ,  $R_{G(ON)} = R_{G(OFF)} = 3.3\Omega$ ,  $T_{AB} = 25^{\circ}C$

Fig. 4.10 Turn-On/Turn-Off Waveform

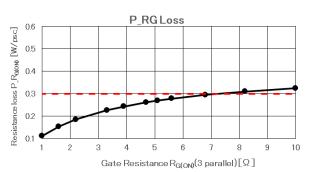

#### <Gate Resistance Loss Characteristics (Calculation)>

Fig. 4.11 Resistance Loss Characteristics

The calculation the loss  $P_R_{G(ON)}$  for each turn-on gate resistor  $R_{G(on)}$  is as shown below. The on-resistance of the gate-drive buffer MOSFET is ignored because it is very small compared to  $r_{ig}$ .

$$P_{\_}R_{G(ON)} = R_{G(ON)}/(R_{G(ON)} + r_{ig}) \times P_{GATE\_ON}/(Number of Parallel resistors)$$

=

$$R_{G(ON)}/(R_{G(ON)}+2.7\Omega) \times 2.47W / 3 = 0.23W$$

$P_{GATE\_ON} = 1/2 \times V_{GS} \times Q_g \times f_{SW}$  (turn-on charging energy)

$r_{ig}$ : 2.7 $\Omega$  MG600Q2YMS3 internal resistance

$V_{GS}$ :26.7V VCC2-VEE = 20V-(-6.7V) = 26.7V

Q<sub>q</sub>:1.85uC (from MG600Q2YMS3 datasheet)

f<sub>sw</sub>:50 kHz gate-drive frequency

The turn-off gate-resistor  $R_{G(\text{off})}$  is also calculated in the same way.

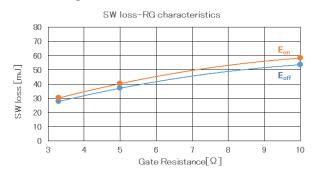

#### <Switching loss result>

#### Fig. 4.12 Switching Loss Characteristics

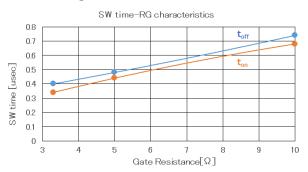

#### <Switching time result>

Fig. 4.13 Switching Time Characteristics

#### <V<sub>DS</sub> surge voltage result>

Fig. 4.14 V<sub>DS</sub> Surge Voltage Characteristics

If the gate resistance is derated 30% with respect to the rated 1W, the gate resistance must be adjusted to be less than or equal to 0.3W. However, if the gate resistance is reduced, the switching-time is shortened and  $V_{DS}$  surge voltage is increased. And if the gate resistance is increased, the resistance loss and switching loss increases, resulting in heat generation.

When adjusting the gate resistor according to the actual specifications, take into account the heat generation, switching loss,  $V_{DS}$  surge voltage, etc. of the respective components. Refer to the data sheet of the power device to be used (e.g. SiC MOSFET Module) and the related documentation to select the gate resistance value.

#### 4.5. Protection Circuit

#### 4.5.1. DESAT (Desaturation) Detection Circuit Operation

DESAT detect function is designed to protect SiC MOSFET module from being damaged by excessive current. It is done by using the DESAT terminal which monitors the drain-source voltage  $(V_{DS})$  of SiC MOSFET module.

If an abnormal high current flows into the drain current ( $I_D$ ) of SiC MOSFET module,  $V_{DS}$  increases along with  $I_D$  according to the static characteristic curve of Drain Current ( $I_D$ ) and Drain Source-to-Source Voltage ( $V_{DS}$ ).

If the  $V_{DS}$  monitored by the DESAT terminal exceeds the threshold voltage  $V_{DESAT}$  (TLP5231  $V_{DESAT}$  8.0 V default), the SiC MOSFET module operation is stopped, and the fault signal is output from FLT terminal of the connector CN1.

DESAT detection method does not allow direct monitoring of the drain current  $(I_D)$ , and therefore, accuracy cannot be increased. However, it is a relatively simple configuration and is used for an emergency-stop when a large current occurs.

Fig. 4.15 shows the current loop used for monitoring DESAT.

Fig. 4.15 DEDAT detecting operation

R713 91Ω

When SiC MOSFET is on, DESAT terminal acts as a constant current source and outputs a blanking capacitance charging current I<sub>CHG</sub> of approximately 0.5mA, and charges and the blanking

VEE

VGMOS

capacitance  $C_{BLANK}$  connected between DESAT pin and VE pin. The voltage generated by  $C_{BLANK}$  is equal to the sum of voltage drops when  $I_{CHG}$  flows through the resistor  $R_{DESAT}$  (R708) and the high voltage tolerant diode  $D_{DESAT}$  (D703, D704, D705, D706) and the drain-source voltage  $V_{DS}$  of SiC MOSFET module.

The voltage between DESAT and  $V_E$  ( $V_{DESAT(ON)}$ ) at that time is expressed by the following equation.

$$V_{DESAT(ON)} = V_{DS} + VF(D_{DESAT}) + I_{CHG} \times R_{DESAT}$$

$$V_{DESAT(ON)} = V_{DS} + VF(D703 + D704 + D705 + D706) + I_{CHG} \times R708$$

Since SiC MOSFET module is on,  $I_{CHG}$  is superimposed on the drain current  $I_D$  several 10A through the drain source. For this reason, the above  $V_{DS}$  is a voltage generated according to the  $I_D$ - $V_{DS}$  static characteristic curve of the SiC MOSFET module. The voltage drop of a small current  $I_{CHG}$  is included in the voltage drop of  $I_D$  and is not visible.

$V_{DS}$  of the normally-on SiC MOSFET module is voltage according to  $I_D$ , but  $V_{DS}$  increases when an overcurrent occurs. If  $V_{DS}$  increases and  $V_{DESAT(ON)}$  exceeds DESAT threshold voltage  $V_{DESAT}$  (TLP5231  $V_{DESAT}$  8.0V (Typ.)), the soft turn-off MOSFET (Q702) is turned on. This is judged to be an abnormal condition. The resistive Rs connected to the drains of Q702 gently pull out the gate charge. This suppresses the spike-voltage generated between the drain and the source, and soft shutdown occurs to prevent the destruction of the SiC MOSFET module.

DESAT is detected by the following equation.

$$V_{DESAT} = V_{DESAT(ON)} = V_{DS} + V_F (D703 + D704 + D705 + D706) + I_{CHG} \times R708$$

(4-2)

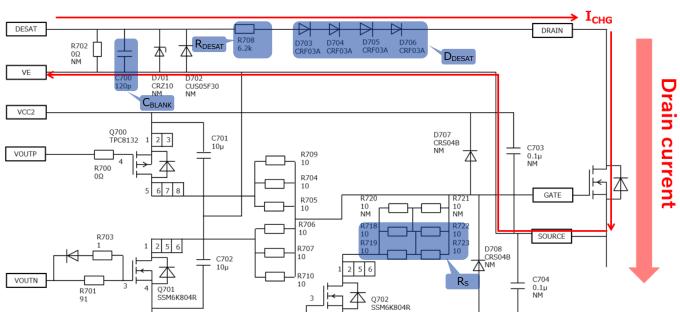

When DESAT is detected, the value of  $V_{DS}$  is determined from the drain-source voltage ( $V_{DS}$ ) and drain current ( $I_D$ ) characteristics of SiC MOSFET module to be used, after first determining the abnormal current.

In this design, based on MG600Q2YMS3 specifications, the minimum fault detection current  $I_{DESAT\_MIN}$  when a DESAT is detected is set to  $I_D$  = 276A at  $T_{CH}$  = 25°C, and for this the  $V_{DS}$  can be read as 0.46V from Fig. 4.16.

Adjust R708 so that  $V_{DESAT(ON)}$  is equal to DESAT threshold  $V_{DESAT}$ .

In this design, R708 is adjusted by setting 0.46V to the lowest  $V_{DS\_MIN}$  of the drain-to-source voltage  $V_{DS}$  when a DESAT is detected.

From equation (4-2), R708 at DESAT detection can be written as Equation (4-3).

$$R708 = \frac{\left(V_{DESAT\_MIN} - V_F(D703 + D704 + D705 + D706) - V_{DS\_MIN}\right)}{I_{CHG\_MAX}} \tag{4-3}$$

SiC MOSFET Module Drain-Source  $V_{DS\_MIN}$ : 0.46V (Min.) DESAT Threshold  $V_{DESAT\_MIN}$ : 7.5V (Min.)

Blanking Capacitance Charge Current  $I_{CHG\_MAX}$ : 0.82mA (Max.) High Voltage Diode  $D_{DESAT}$  (D703 $\sim$ D706) Forward Voltage  $V_F$ : 1.96V (Typ.)

$$R708 = \frac{(7.5V - 1.96V - 0.46V)}{0.82mA} = 6200\Omega$$

R708 is selected as  $6.2k\Omega$  and therefore the lowest DESAT detection  $V_{DS}$  is approximately 0.46V and  $I_D$  is 276A.

Kindly do appropriate design according to the actual specifications and then do enough evaluation of the real circuit.

Fig. 4.16 I<sub>D</sub>-V<sub>DS</sub> Characteristic

DESAT terminal is connected to the drain terminal of SiC MOSFET module through a high-voltage diode (D<sub>DESAT</sub>). If the drain voltage of SiC MOSFET module fluctuates due to external noises while SiC MOSFET module in ON, DESAT voltage may fluctuate. If DESAT voltage fluctuation exceeds DESAT threshold (8.0V Typ.), the protection operation will be initiated and the soft shutdown of the SiC MOSFET module will occur. Since the noise generated by the high-voltage inverter circuit is large, a blanking capacitor C<sub>BLANK</sub> (C700) is added to form a low-pass filter.

A trade-off due to the addition of this  $C_{BLANK}$  (C700) is the blanking time  $t_{BLANK}$  in which  $V_{DESAT(ON)}$  reaches  $V_{DESAT}$  when a short-circuit fault occurs.

The blanking-time  $t_{BLANK}$  is given by the following formula.

$$t_{BLANK} = \{C_{BLANK} \times (V_{DESAT} - V_{DESAT(ON)})\} / I_{CHG}$$

$$t_{BLANK} = \{C700 \times (V_{DESAT} - V_{DS} - VF(D703 + D704 + D705 + D704) - I_{CHG} \times R708)\} / I_{CHG}$$

$$(4-4)$$

After the blanking time t<sub>BLANK</sub>, the soft shutdown of SiC MOSFET module occurs.

The gate-voltage  $V_G$  at soft shutdown decreases exponentially over time, as shown by the following equation:

$$V_{G} = (V_{CC2} + |V_{EE}|) \times \exp\left(\frac{-t}{C_{in} \times R_{S}}\right) - |V_{EE}|$$

If the time to fall to  $V_{G(OFF)}$  is set to be the soft turn-off time  $t_{STO}$ , the following formula is used.

$$t_{STO} = -C_{in} \times R_S \times \ln \left( \frac{V_{G(OFF)} + |V_{EE}|}{V_{CC2} + |V_{EE}|} \right)$$

(4-5)

t<sub>STO</sub> can be adjusted with the resistance value of Rs (consisting of R718 to R723).

The tDESAT\_TOTAL from the time of fault to the time of soft shutdown is the sum of  $t_{BLANK}$ ,  $t_{STO}$ , and tDESAT(FILTER).

$$t_{DESAT\_TOTAL} = t_{BLANK} + t_{STO} + t_{DESAT(FILTER)}$$

In this design, the maximum blanking time  $t_{BLANK\_MAX}$  is used to calculate the maximum tDESAT\_TOTAL (Max.) to be 2.86µs from the following formula.  $V_{DS}$  is set to  $V_{DS}$ =0.46V during normal operation.

$$\begin{split} t_{DESAT\_TOTAL(MAX)} &= \left\{120 pF \times (9.0 V - 0.46 V - 1.96 V - 0.29 mA \times 6.2 k\Omega)\right\} / \ 0.29 mA - 53 nF \times 10 \Omega \times \\ &\ln \left(\frac{2 V + |-6.7 V|}{20 V + |-6.7 V|}\right) + 0.29 \mu s = 1.98 \mu s + 0.594 \mu s + 0.29 \mu s = 2.86 \mu s \end{split}$$

Blanking capacitance C<sub>BLANK</sub>: 120pF

DESAT threshold V<sub>DESAT</sub>: 9.0V (Max.)

Blanking capacitance Charge Current I<sub>CHG</sub>: 0.29mA (Min.)

Input capacitance C<sub>in</sub>: 53nF for SiC MOSFET Modules (MG600Q2YMS3) (Typ.)

Drain resistance  $R_S$  of MOSFET for soft turn-off:  $10\Omega$  (Typ.) (R718, R719, R722, R723: $10\Omega$ , 2 series in 2 parallel, R720, R721: not mounted)

Positive power supply voltage  $V_{CC2}$ : 20V (Typ.)

Negative power supply voltage V<sub>EE</sub>: -6.7V (Typ.)

SiC MOSFET Module (MG600Q2YMS3) Gate Threshold Voltage  $V_{G(OFF)}$ : 2V (Set to a value less than 3.6V)

Note that the capacitance of the pins of the protective diodes which are connected in parallel to the blanking capacitor  $C_{BLANK}$  (C700) will affect  $t_{BLANK}$ .

$C_{BLANK}$  (C700) and  $R_{DESAT}$  (R708) must be adjusted carefully because they also affect  $V_{DS}$  of SiC MOSFET module and the noise tolerance of DESAT terminal (CR filter parameter) when DESAT is detected.

Depending on actual use conditions, if the parasitic inductance (Ls) of the electric wiring generates a large surge voltage when the current is cut off and exceeds the component rated voltage, it may result in damage. To reduce the surge-voltage caused by Ls, the snubber circuit must be connected as close as possible to SiC MOSFET module. Verify DESAT detection operation sufficiently using an actual device.

#### 4.5.2. UVLO Function (Under Voltage Lock Out)

TLP5231 incorporated in this design has a built-in UVLO function. The voltages of the positive power supply (V<sub>CC2</sub>-V<sub>E</sub>) and the negative power supply (V<sub>E</sub>-V<sub>EE</sub>) on the secondary side are monitored. When the positive voltage is lower than the UVLO threshold voltage (VUVLOP-), or if the negative voltage is more than the UVLO threshold voltage (V<sub>UVLON-</sub>), the operation is stopped. When the positive power supply voltage exceeds V<sub>UVLOP+</sub> and the negative power supply voltage drops below V<sub>UVLON+</sub>, normal operation is resumed. This function prevents SiC MOSFET module from passing current between the drain/source at inadequate gate voltage. It is intended to prevent damage due to overheating. Note that TLP5231 does not operate unless both the positive and negative power supplies are aligned, so be sure to apply a negative power supply even if only the positive power supply is acceptable.

UVLO takes precedence over all functions because TLP5231 starts operation after UVLO is released.

#### Positive power supply voltage undervoltage protection (UVLO\_P)

When the positive power supply voltage ( $V_{CC2}-V_E$ ) on the secondary side of TLP5231 drops below the threshold voltage V<sub>ULVOP</sub>-, the gate drive output is stopped, and FLT pins (pins 5 and 12 of CN1) of this design go from H level to L level. When the positive power supply voltage  $(V_{CC2}-V_E)$ on the secondary side rises above the threshold voltage V<sub>ULVOP+</sub>, the gate drive output is enabled, and FLT pins go from L level to H level (only when the negative power supply voltage is below the UVLO threshold).

#### Negative power supply voltage undervoltage protection (UVLO\_N)

When the negative supply voltage (V<sub>E</sub>-V<sub>EE</sub>) on the secondary side of TLP5231 rises above the threshold voltage V<sub>ULYON</sub>-, the gate drive output is stopped, and FLT pins (pins 5 and 12 of CN1) of this design go from H level to L level. When the negative power supply voltage ( $V_E-V_{EE}$ ) on the secondary side drops below the threshold voltage V<sub>ULVON+</sub>, the gate-drive output is enabled, and FLT pins go from L level to H level (only when the positive power supply voltage is above the UVLO threshold).

Table4.4 shows UVLO threshold voltages.

© 2024 2024-07-23 28 / 31 Toshiba Electronic Devices & Storage Corporation

| Table 4 | 1.4 UV | LO Thr | eshold | Voltages |

|---------|--------|--------|--------|----------|

|---------|--------|--------|--------|----------|

| LIVI O. D. throshold | V <sub>UVLOP+</sub>  | 13 V (Typ.)   |

|----------------------|----------------------|---------------|

| UVLO_P threshold     | $V_{UVLOP-}$         | 12 V (Typ.)   |

| LIVI O. N. throchold | V <sub>UVLON+</sub>  | -5.3 V (Typ.) |

| UVLO_N threshold     | V <sub>UVLON</sub> _ | -5.0 V (Typ.) |

### 4.5.3. Active Miller Clamp (AMC)

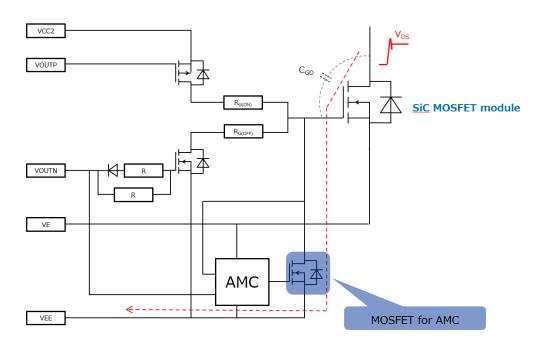

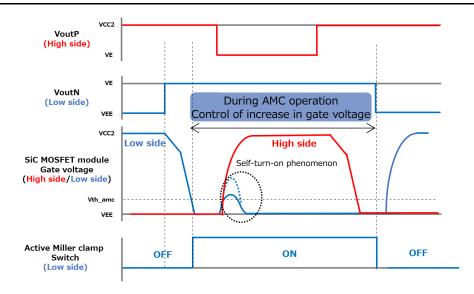

In a bridge configuration in which devices are connected in series at the top and bottom, when one of the devices turns on, then the voltage across its drain and source changes quickly (higher dV/dt). This will lead to current flow from drain to gate of another device via its drain to gate capacitance ( $C_{DG}$ ), which can cause the gate voltage to rise and turn on the MOSFET accidently. This is a malfunction called as self-turn on. Active miller clamp (AMC) is a function that prevents this malfunction.

Fig. 4.18 shows AMC operation of this design, and Fig. 4.19 shows the operation waveforms. When the gate control signal of this design goes to L level (VOUTN goes to H level), the gate voltage of SiC MOSFET module drops, the MOSFET for AMC turns on, and the gate voltage is clamped to negative voltage (VEE) without using the gate resistor  $R_{G(OFF)}$ . Through these measures, self-turning on can be prevented by controlling the rise of the gate voltage.

Fig. 4.18 Active Miller Clamp Operation

Fig. 4.19 Active Miller Clamp Operation Waveform Image

# 4.6. Temperature Detection Output

The connector (CN1) of this design provides a connection pin which is connected to the thermistor output built into SiC MOSFET module. It can be used to monitor the temperature of the SiC MOSFET module. This design is not equipped with a temperature detection circuit; therefore, the user can add an external detection circuit if necessary.

Refer to the Table 3.3 for the rated resistance and the B constant of the thermistor in SiC MOSFET module MG600Q2YMS3.

30 / 31

#### **Terms of Use**

This terms of use is made between Toshiba Electronic Devices and Storage Corporation ("We") and Customer who downloads or uses this Reference Design. Customer shall comply with this terms of use. This Reference Design means all documents and data in order to design electronics applications on which our semiconductor device is embedded.

#### Section 1. Restrictions on usage

- 1. This Reference Design is provided solely as reference data for designing electronics applications. Customer shall not use this Reference Design for any other purpose, including without limitation, verification of reliability.

- 2. Customer shall not use this Reference Design for sale, lease or other transfer.

- 3. Customer shall not use this Reference Design for evaluation in high or low temperature, high humidity, or high electromagnetic environments.

- 4. This Reference Design shall not be used for or incorporated into any product or system whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

#### Section 2. Limitations

- 1. We reserve the right to make changes to this Reference Design without notice.

- 2. This Reference Design should be treated as a reference only. WE ARE NOT RESPONSIBLE FOR ANY INCORRECT OR INCOMPLETE DATA AND INFORMATION.

- 3. Semiconductor devices can malfunction or fail. When designing electronics applications by referring to this Reference Design, Customer is responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of semiconductor devices could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Customer must also refer to and comply with the latest versions of all relevant our information, including without limitation, specifications, data sheets and application notes for semiconductor devices, as well as the precautions and conditions set forth in the "Semiconductor Reliability Handbook".

- 4. Designing electronics applications by referring to this Reference Design, Customer must evaluate the whole system sufficiently. Customer is solely responsible for applying this Reference Design to Customer's own product design or applications. WE ASSUME NO LIABILITY FOR CUSTOMER'S PRODUCT DESIGN OR APPLICATIONS.

5. WE SHALL NOT BE RESPONSIBLE FOR ANY INFRINGEMENT OF PATENTS OR ANY OTHER INTELLECTUAL PROPERTY RIGHTS OF THIRD PARTIES THAT MAY RESULT FROM THE USE OF THIS REFERENCE DESIGN. NO LICENSE TO ANY INTELLECTUAL PROPERTY RIGHT IS GRANTED BY THIS TERMS OF USE, WHETHER EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE.

- 6. THIS REFERENCE DESIGN IS PROVIDED "AS IS". WE (a) ASSUME NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (b) DISCLAIM ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO THIS REFERENCE DESIGN, INCLUDING WITHOUT LIMITATION, WARRANTIES OR CONDITIONS OF FUNCTION AND WORKING, WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

#### **Section 3. Terms and Termination**

It is assumed that Customer agrees to any and all this terms of use if Customer downloads or uses this Reference Design. We may, at its sole and exclusive discretion, change, alter, modify, add, and/or remove any part of this terms of use at any time without any prior notice. We may terminate this terms of use at any time and without any cause. Upon termination of this terms of use, Customer shall eliminate this Reference Design. Furthermore, upon our request, Customer shall submit to us a written confirmation to prove elimination of this Reference Design.

#### **Section 4. Export Control**

Customer shall not use or otherwise make available this Reference Design for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). This Reference Design may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Act and the U.S. Export Administration Regulations. Export and re-export of this Reference Design is strictly prohibited except in compliance with all applicable export laws and regulations.

#### **Section 5. Governing Laws**

This terms of use shall be governed and construed by laws of Japan, without reference to conflict of law principle.

#### Section 6. Jurisdiction

Unless otherwise specified, Tokyo District Court in Tokyo, Japan shall be exclusively the court of first jurisdiction for all disputes under this terms of use.

2024-07-23