32 ビット RISC マイクロコントローラー

**TXZ+ファミリー

TMPM4K グループ(1)**

リファレンスマニュアル

クロック制御と動作モード

**(CG-M4K(1)-E)**

**Revision 1.1**

**2025-09**

東芝デバイス&ストレージ株式会社

## 目次

|                                                |    |

|------------------------------------------------|----|

| 序章 .....                                       | 6  |

| 関連するドキュメント .....                               | 6  |

| 表記規約 .....                                     | 7  |

| 用語・略語 .....                                    | 9  |

| 1. クロック制御と動作モード .....                          | 10 |

| 1.1. 概要 .....                                  | 10 |

| 1.2. クロック制御 .....                              | 11 |

| 1.2.1. クロックの種類 .....                           | 11 |

| 1.2.2. リセット動作による初期値 .....                      | 11 |

| 1.2.3. クロック系統図 .....                           | 12 |

| 1.2.4. ウオーミングアップ機能 .....                       | 13 |

| 1.2.4.1. 高速発振用ウォーミングアップタイマー .....              | 13 |

| 1.2.4.2. ウオーミングアップタイマーの使用方法 .....              | 14 |

| 1.2.5. fsys 用クロック遅倍回路(PLL) .....               | 14 |

| 1.2.5.1. リセット解除後の PLL 設定 .....                 | 14 |

| 1.2.5.2. PLL 遅倍値の計算式と設定例 .....                 | 15 |

| 1.2.5.3. 動作中の PLL 遅倍値の変更 .....                 | 16 |

| 1.2.5.4. PLL 動作開始/停止切り替えシーケンス .....            | 17 |

| 1.2.6. システムクロック .....                          | 18 |

| 1.2.6.1. システムクロックの設定方法 .....                   | 19 |

| 1.2.7. クロック供給設定機能 .....                        | 21 |

| 1.2.8. クロックの端子出力機能 .....                       | 21 |

| 1.2.9. プリスケーラークロック .....                       | 21 |

| 1.3. 動作モード .....                               | 22 |

| 1.3.1. 動作モードの詳細 .....                          | 22 |

| 1.3.1.1. 各モードの特長 .....                         | 22 |

| 1.3.1.2. 低消費電力モードへの遷移と復帰 .....                 | 23 |

| 1.3.1.3. 低消費電力モードの選択 .....                     | 23 |

| 1.3.1.4. 低消費電力モードにおける周辺機能状態 .....              | 24 |

| 1.3.2. モード状態遷移 .....                           | 25 |

| 1.3.2.1. IDLE モード遷移フロー .....                   | 25 |

| 1.3.2.2. STOP1 モード遷移フロー .....                  | 26 |

| 1.3.3. 低消費電力モードからの復帰 .....                     | 27 |

| 1.3.3.1. 低消費電力モードの解除ソース .....                  | 27 |

| 1.3.3.2. 低消費電力モード解除時のウォーミングアップ .....           | 28 |

| 1.3.4. モード遷移によるクロック動作 .....                    | 29 |

| 1.3.4.1. NORMAL → IDLE → NORMAL 動作モード遷移 .....  | 29 |

| 1.3.4.2. NORMAL → STOP1 → NORMAL 動作モード遷移 ..... | 29 |

| 1.4. レジスターの説明 .....                            | 30 |

|                                                  |    |

|--------------------------------------------------|----|

| 1.4.1. レジスター一覧                                   | 30 |

| 1.4.2. レジスター詳細                                   | 31 |

| 1.4.2.1. [CGPROTECT] (CG ライトプロテクトレジスター)          | 31 |

| 1.4.2.2. [CGOSCCR] (発振制御レジスター)                   | 31 |

| 1.4.2.3. [CGSYSCR] (システムクロック制御レジスター)             | 32 |

| 1.4.2.4. [CGSTBYCR] (スタンバイ制御レジスター)               | 33 |

| 1.4.2.5. [CGSCOCR] (SCOUT 出力制御レジスター)             | 33 |

| 1.4.2.6. [CGPLL0SEL] (fsys 用 PLL セレクトレジスター)      | 34 |

| 1.4.2.7. [CGWUPHCR] (高速発振ウォーミングアップレジスター)         | 34 |

| 1.4.2.8. [CGFSYSENA] (fsys 供給停止レジスターA)           | 35 |

| 1.4.2.9. [CGFSYSENB] (fsys 供給停止レジスターB)           | 37 |

| 1.4.2.10. [CGFCEN] (fc 供給停止レジスター)                | 38 |

| 1.4.2.11. [CGSPCLKEN] (ADC、デバッグ回路用クロック供給停止レジスター) | 39 |

| 1.5. 製品別情報                                       | 40 |

| 1.5.1. [CGFSYSENA]                               | 40 |

| 1.5.2. [CGFSYSENB]                               | 41 |

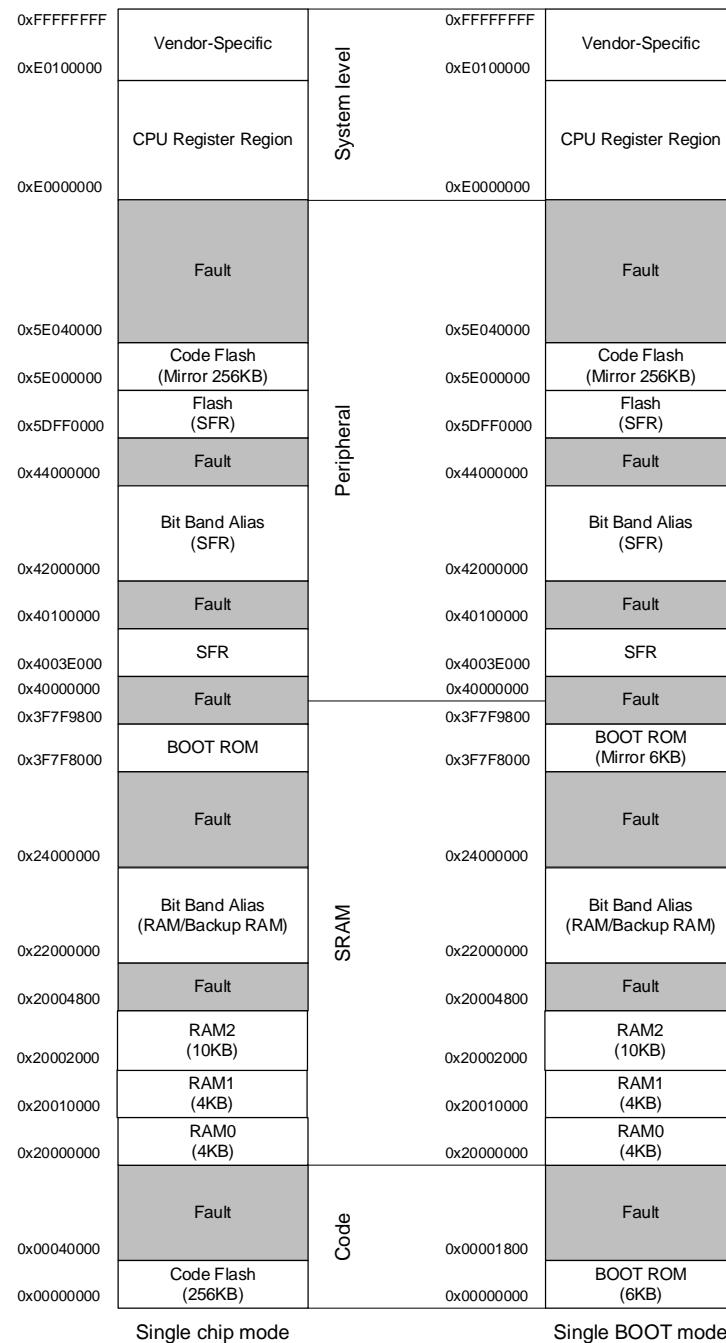

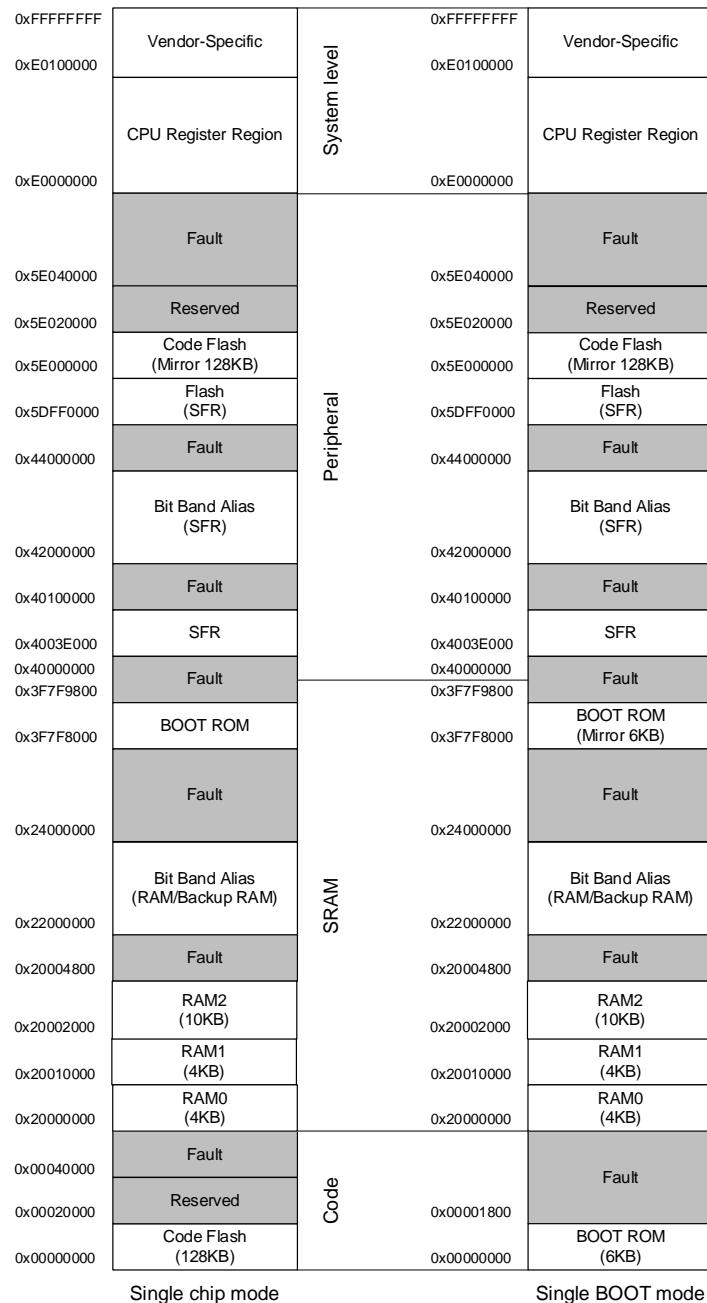

| 2. メモリーマップ                                       | 42 |

| 2.1. 概要                                          | 42 |

| 2.1.1. TMPM4KxFYB                                | 43 |

| 2.1.2. TMPM4KxFWB                                | 44 |

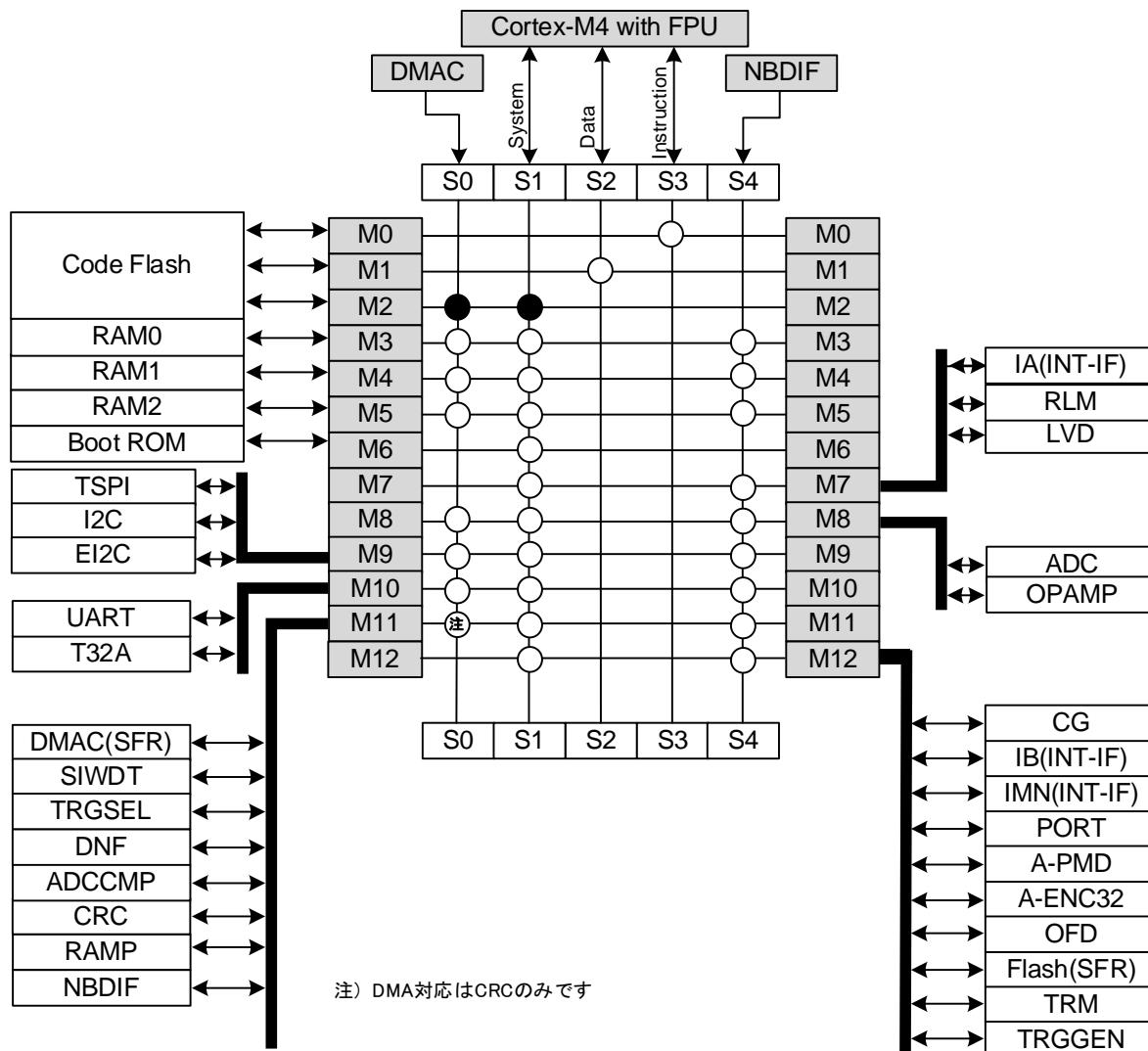

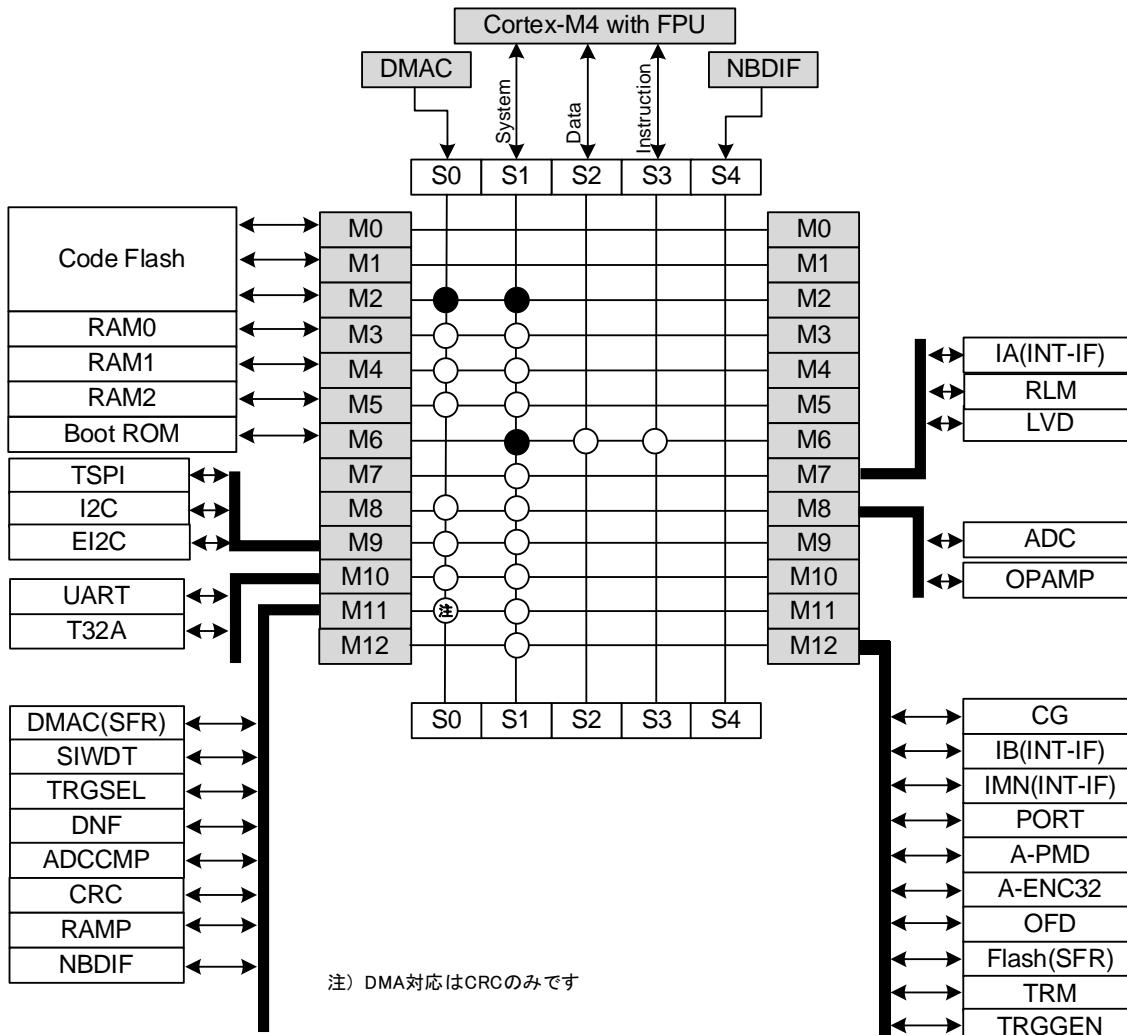

| 2.2. バスマトリックス                                    | 45 |

| 2.2.1. 構成                                        | 46 |

| 2.2.1.1. シングルチップモード                              | 46 |

| 2.2.1.2. シングルブートモード                              | 47 |

| 2.2.2. 接続表                                       | 48 |

| 2.2.2.1. メモリー関連の接続                               | 48 |

| 2.2.2.2. 周辺機能の接続                                 | 50 |

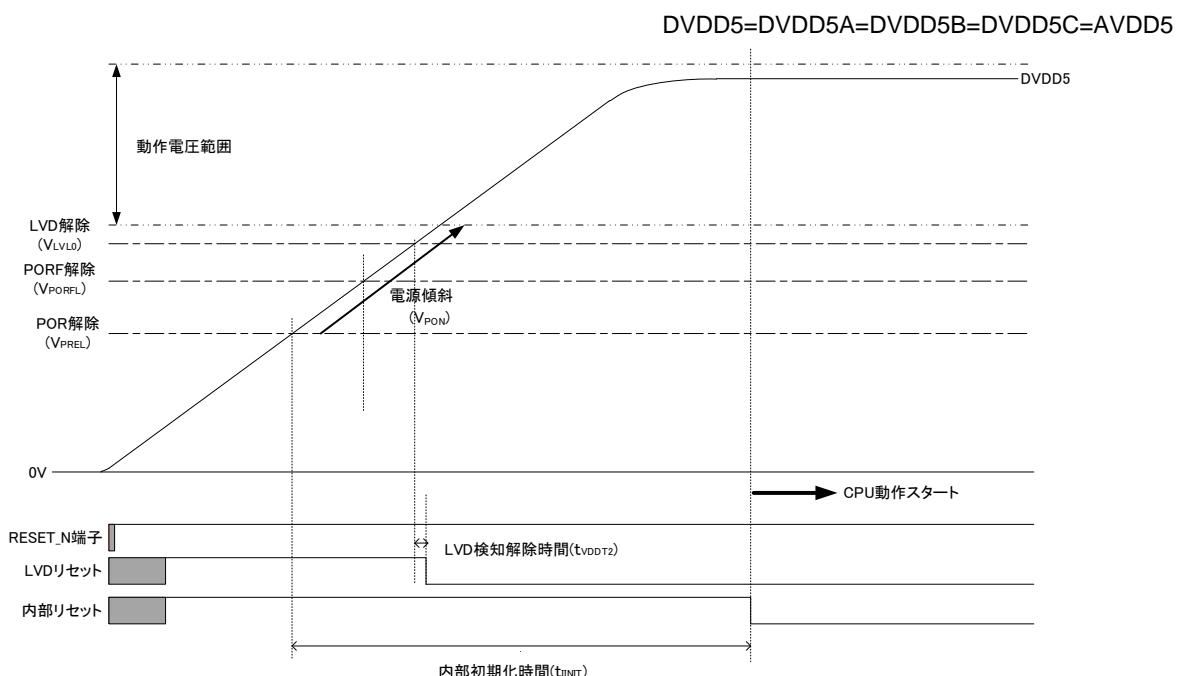

| 3. リセットと電源制御                                     | 51 |

| 3.1. 概要                                          | 51 |

| 3.2. 機能説明・動作説明                                   | 51 |

| 3.2.1. コールドリセット                                  | 51 |

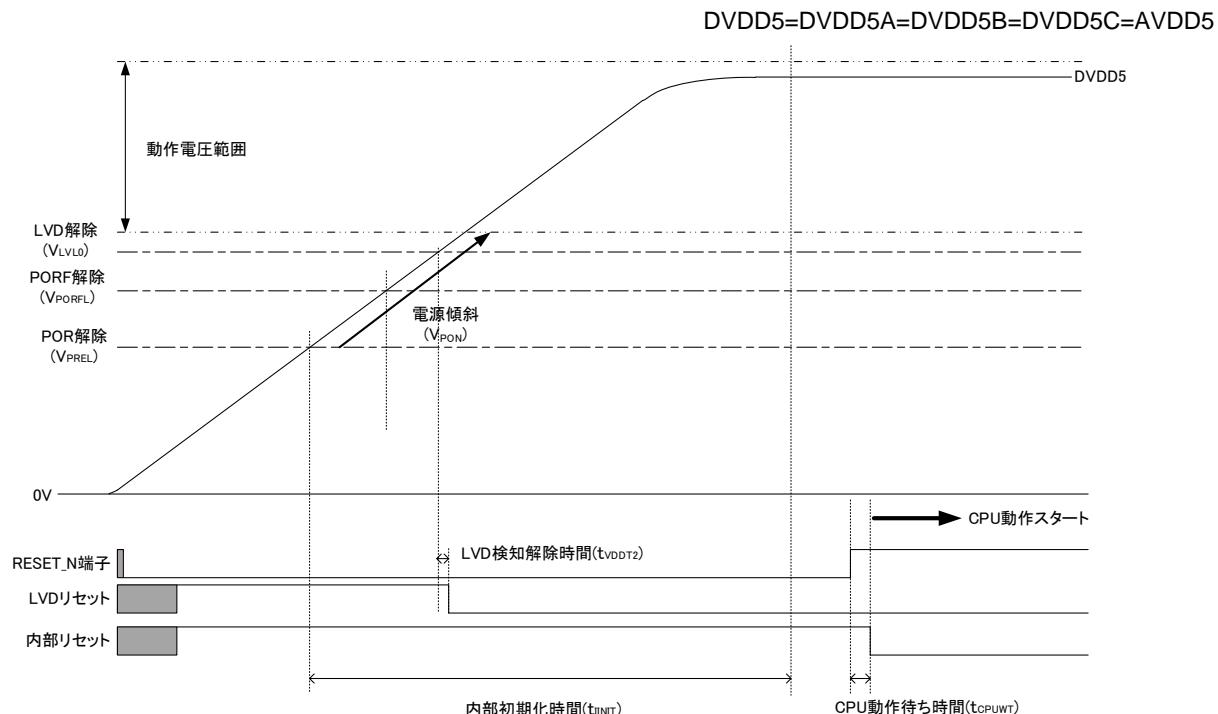

| 3.2.1.1. パワーオンリセット回路によるリセット(RESET_N 端子を使用しない場合)  | 52 |

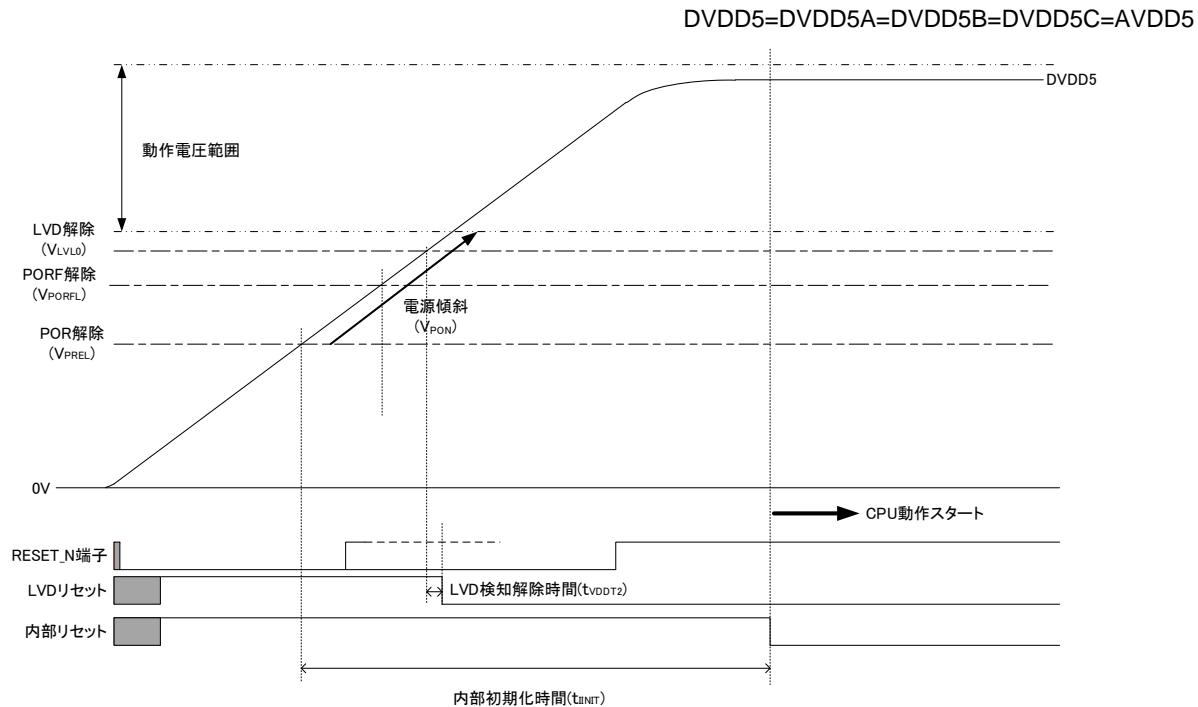

| 3.2.1.2. RESET_N 端子によるリセット                       | 53 |

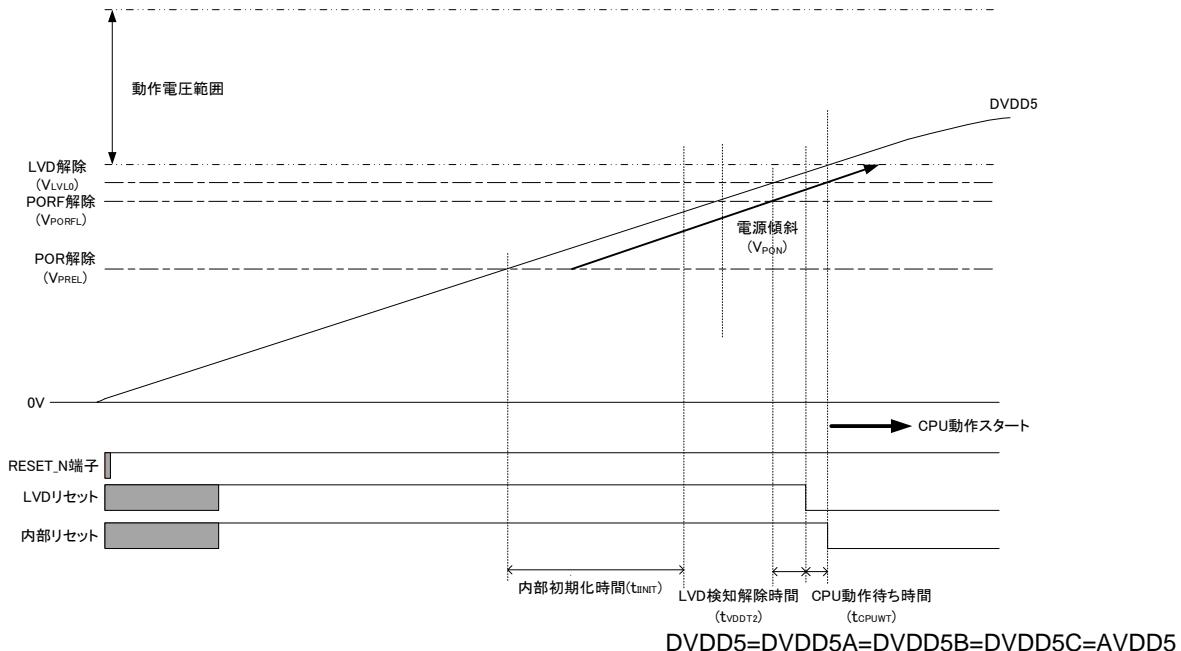

| 3.2.1.3. LVD によるリセットの継続                          | 55 |

| 3.2.2. ウオームリセット                                  | 56 |

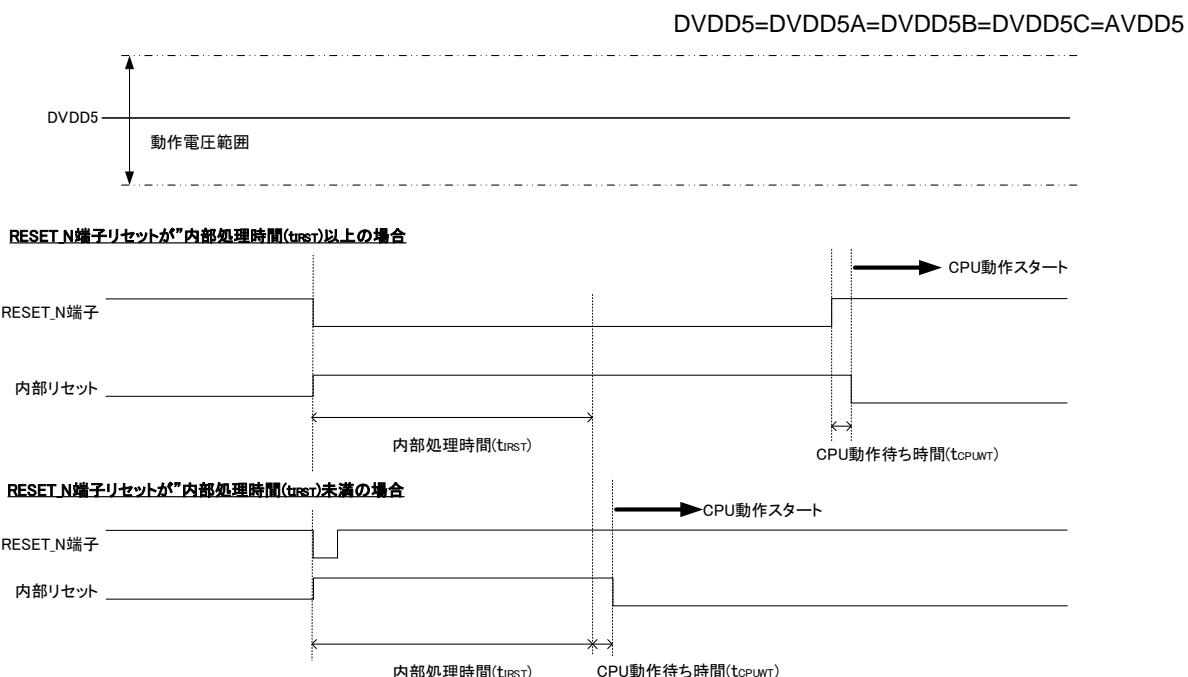

| 3.2.2.1. RESET_N 端子によるウオームリセット                   | 56 |

| 3.2.2.2. LVD によるウオームリセット                         | 56 |

| 3.2.2.3. その他の内部リセットによるウオームリセット                   | 56 |

| 3.2.3. シングルブートモードの起動                             | 57 |

| 3.2.3.1. RESET_N 端子を使った起動                        | 57 |

| 3.2.3.2. 電源安定時のシングルブートモードの起動                     | 58 |

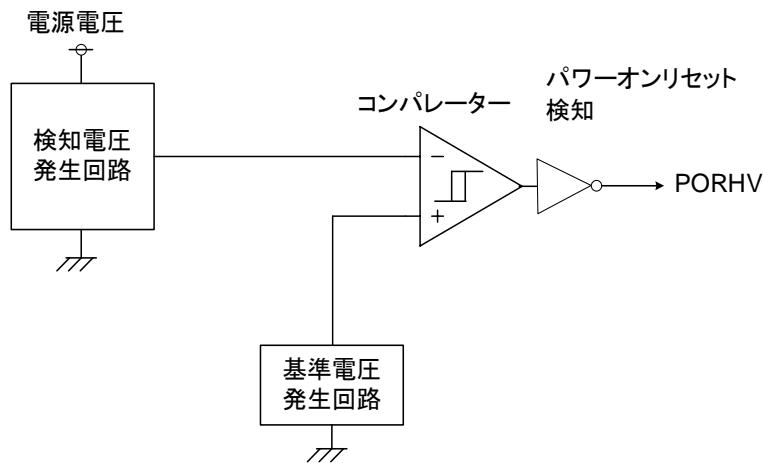

| 3.2.4. パワーオンリセット回路                               | 59 |

---

|                                                 |    |

|-------------------------------------------------|----|

| 3.2.4.1. 電源投入時の動作 .....                         | 59 |

| 3.2.4.2. 電源切断時の動作 .....                         | 59 |

| 3.2.5. 電源切断と再投入 .....                           | 60 |

| 3.2.5.1. 外部のリセット回路または内蔵 LVD リセットを使用している場合 ..... | 60 |

| 3.2.5.2. 外部のリセット回路/内蔵 LVD リセットを使用しない場合 .....    | 60 |

| 3.2.6. リセット解除後 .....                            | 60 |

| 3.2.6.1. リセット要因と初期化範囲 .....                     | 61 |

| 4. 改訂履歴 .....                                   | 62 |

| 製品取り扱い上のお願い .....                               | 63 |

## 図目次

|                                            |    |

|--------------------------------------------|----|

| 図 1.1 クロック系統図 .....                        | 12 |

| 図 1.2 モード状態遷移 .....                        | 25 |

| 図 1.3 NORMAL→STOP1→NORMAL 動作モード遷移 .....    | 29 |

| 図 2.1 TMPM4KxFYB .....                     | 43 |

| 図 2.2 TMPM4KxFWB .....                     | 44 |

| 図 2.3 シングルチップモード .....                     | 46 |

| 図 2.4 シングルブートモード .....                     | 47 |

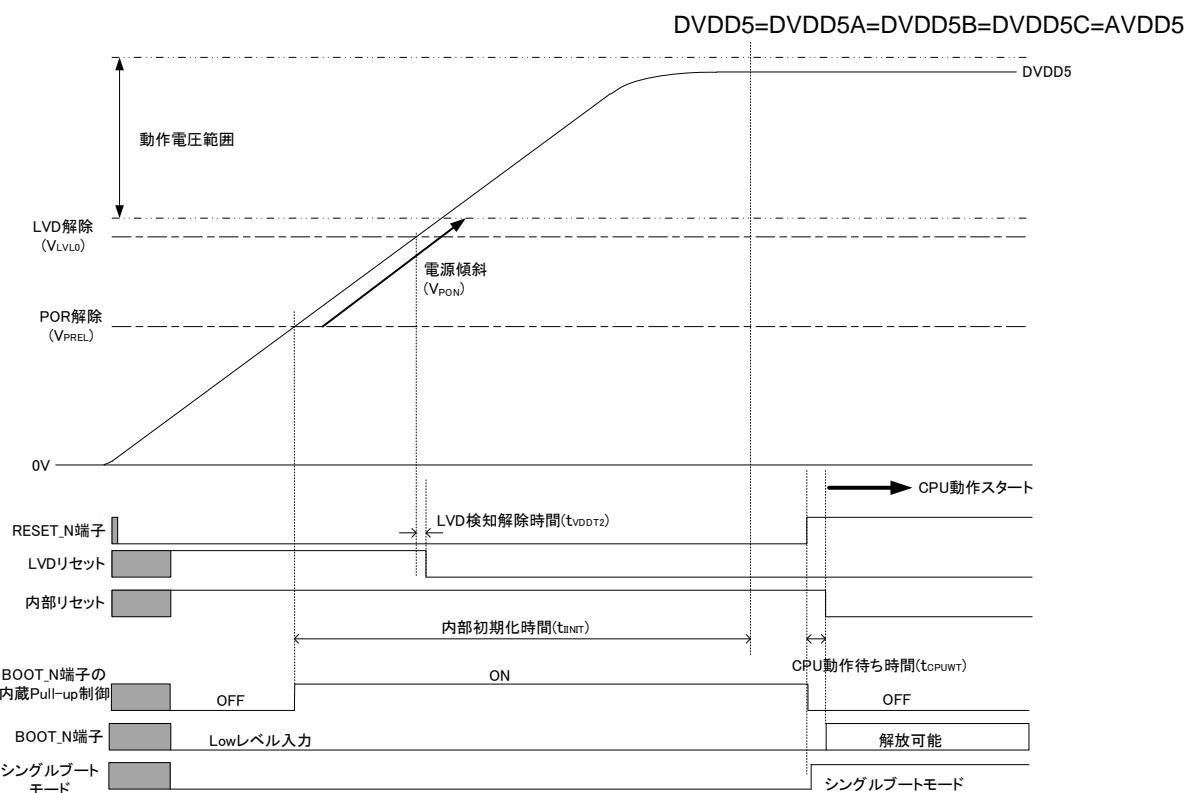

| 図 3.1 パワーオンリセット回路によるリセット動作 .....           | 52 |

| 図 3.2 RESET_N 端子によるリセット動作(1) .....         | 53 |

| 図 3.3 RESET_N 端子によるリセット動作(2) .....         | 54 |

| 図 3.4 LVD リセットによるリセット動作 .....              | 55 |

| 図 3.5 ウオームリセット動作 .....                     | 56 |

| 図 3.6 電源投入時にリセット端子を使用したシングルブートモードの起動 ..... | 57 |

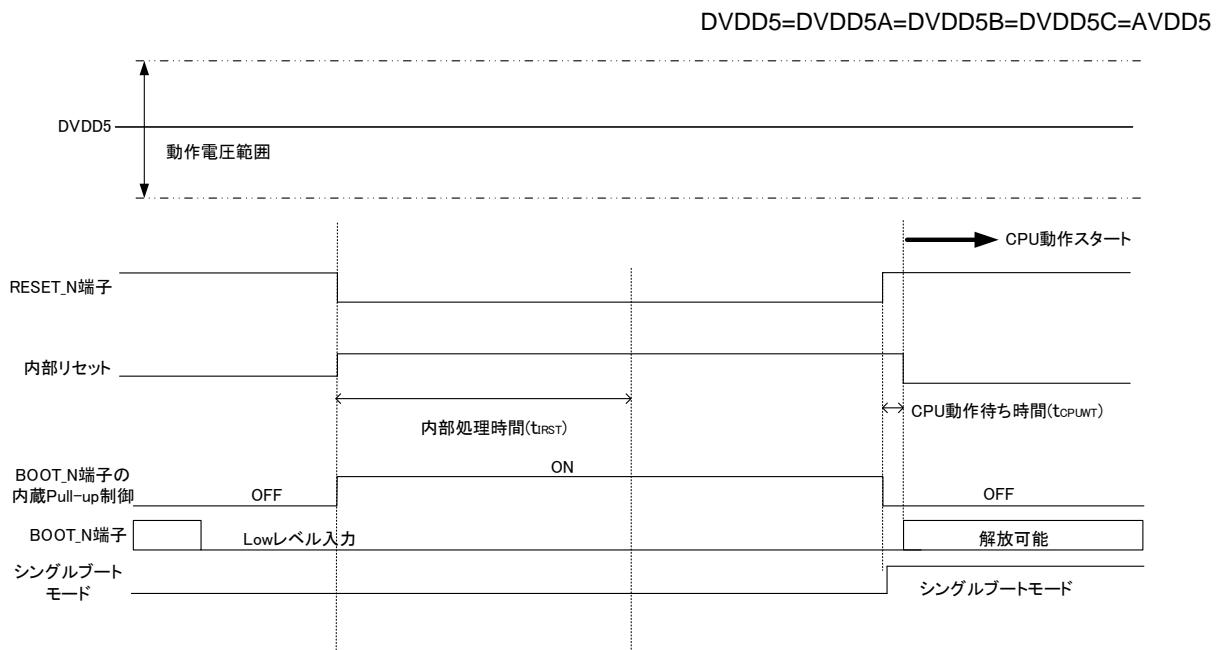

| 図 3.7 電源安定時のシングルブートモードの起動 .....            | 58 |

| 図 3.8 パワーオンリセット回路 .....                    | 59 |

## 表目次

|                                            |    |

|--------------------------------------------|----|

| 表 1.1 [CGPLL0SEL]<PLL0SET[23:0]>設定詳細 ..... | 15 |

| 表 1.2 PLL 補正值(例) .....                     | 16 |

| 表 1.3 PLL0SET 設定値(例) .....                 | 16 |

| 表 1.4 動作周波数(単位: MHz)例 .....                | 18 |

| 表 1.5 SCOUT 端子使用可否一覧 .....                 | 21 |

| 表 1.6 低消費電力モード選択 .....                     | 23 |

| 表 1.7 低消費電力モード別ブロック動作状態一覧 .....            | 24 |

| 表 1.8 解除ソース一覧 .....                        | 27 |

| 表 1.9 ウオーミングアップ .....                      | 28 |

| 表 1.10 [CGFSYSENA]の製品別割り当て .....           | 40 |

| 表 1.11 [CGFSYSENB]の製品別割り当て .....           | 41 |

| 表 2.1 シングルチップモード .....                     | 48 |

| 表 2.2 シングルブートモード .....                     | 48 |

| 表 2.3 シングルチップモード .....                     | 49 |

| 表 2.4 シングルブートモード .....                     | 49 |

| 表 2.5 周辺機能の接続 .....                        | 50 |

| 表 3.1 リセット要因と初期化される範囲 .....                | 61 |

| 表 4.1 改訂履歴 .....                           | 62 |

## 序章

### 関連するドキュメント

| 文書名                             |

|---------------------------------|

| Arm® ドキュメンテーションセット Cortex®-M4 編 |

| 例外                              |

| 周波数検知回路                         |

| 電圧検知回路                          |

| クロック選択式ウォッチドッグタイマー              |

| フラッシュメモリー                       |

| データシート                          |

## 表記規約

- 数値表記は以下の規則に従います。

- 16進数表記: 0xABCD

- 10進数表記: 123 または 0d123(10進表記であることを示す必要のある場合だけ使用)

- 2進数表記: 0b111(ビット数が本文中に明記されている場合は「0b」を省略可)

- ローアクティブの信号は信号名の末尾に「\_N」で表記します。

- 信号がアクティブレベルに移ることを「アサート(assert)」アクティブでないレベルに移ることを「デアサート(deassert)」と呼びます。

- 複数の信号名は[m:n]とまとめて表記する場合があります。

例: S[3:0]は S3、S2、S1、S0 の4つの信号名をまとめて表記しています。

- 本文中 [ ] で囲まれたものはレジスターを定義しています。

例: [ABCD]

- 同種で複数のレジスター、フィールド、ビット名は「n」で一括表記する場合があります。

例: [XYZ1], [XYZ2], [XYZ3] → [XYZn]

- 「レジスター一覧」中のレジスターナンバーでユニットまたはチャネルは「x」で一括表記しています。

ユニットの場合、「x」は A、B、C、...を表します。

例: [ADACR0], [ADBCR0], [ADCCR0] → [ADxCR0]

- チャネルの場合、「x」は 0、1、2、...を表します。

例: [T32A0RUNA], [T32A1RUNA], [T32A2RUNA] → [T32AxRUNA]

- レジスターのビット範囲は[m:n]と表記します。

例: [3:0]はビット 3 から 0 の範囲を表します。

- レジスターの設定値は 16進数または2進数のどちらかで表記されています。

例: [ABCD]<EFG> = 0x01 (16進数)、[XYZn]<VW> = 1 (2進数)

- ワード、バイトは以下のビット長を表します。

バイト: 8 ビット

ハーフワード: 16 ビット

ワード: 32 ビット

ダブルワード: 64 ビット

- レジスター内の各ビットの属性は以下の表記を使用しています。

R: リードオンリー

W: ライトオンリー

R/W: リード/ライト

- 断りのない限り、レジスターアクセスはワードアクセスだけをサポートします。

- 本文中の予約領域「Reserved」として定義されたレジスターは書き換えを行わないでください。

また、読み出した値を使用しないでください。

- Default 値が「-」となっているビットから読み出した値は不定です。

- 書き込み可能なビットフィールドと、リードオンリー「R」のビットフィールドが共存するレジスターに書き込みを行う場合、リードオンリー「R」のビットフィールドには Default 値を書き込んでください。

Default 値が「-」となっている場合は、個々のレジスターの定義に従ってください。

- ライトオンリーのレジスターの Reserved ビットフィールドには Default 値を書き込んでください。

Default 値が「-」となっている場合は、個々のレジスターの定義に従ってください。

- 書き込みと読み出しで異なる定義のレジスターへのリードモディファイライト処理は行わないでください。

\*\*\*\*\*

Arm、Cortex および Thumb は Arm Limited(またはその子会社)の US またはその他の国における

登録商標です。All rights reserved.

\*\*\*\*\*

arm

本資料に記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。

**用語・略語**

この仕様書で使用されている用語・略語の一部を記載します。

|           |                                                  |

|-----------|--------------------------------------------------|

| ADC       | Analog to Digital Converter                      |

| A-ENC32   | Advanced Encoder Input Circuit(32-bit)           |

| A-PMD     | Advanced Programmable Motor Control Circuit      |

| CG        | Clock Control and Operation Mode                 |

| CRC       | Cyclic Redundancy Check                          |

| D-Bus     | DCode Memory Interface                           |

| DMAC      | Direct Memory Access Controller                  |

| DNF       | Digital Noise Filter                             |

| EHOSC     | External High-speed Oscillator                   |

| EI2C      | I <sup>2</sup> C Interface Version A             |

| fsys      | Frequency of SYSTEM Clock                        |

| IA(INTIF) | Interrupt Control Register A                     |

| IB(INTIF) | Interrupt Control Register B                     |

| I-Bus     | ICode Memory Interface                           |

| IHOSC     | Internal High-speed Oscillator                   |

| IMN       | Interrupt Monitor                                |

| INT       | Interrupt                                        |

| I2C       | Inter-Integrated Circuit                         |

| LVD       | Voltage Detection Circuit                        |

| NBDIF     | Non Break Debug Interface                        |

| NMI       | Non-maskable Interrupt                           |

| OFD       | Oscillation Frequency Detector                   |

| OPAMP     | Operational Amplifier                            |

| POR       | Power-on Reset Circuit                           |

| PORF      | Power-on Reset Circuit for FLASH and Debug       |

| RAMP      | RAM Parity                                       |

| RLM       | Low-speed Oscillation/Power Supply Control/Reset |

| S-Bus     | System Interface                                 |

| SCOUT     | Source Clock Output                              |

| SIWDT     | Clock Selective Watchdog Timer                   |

| TRGSEL    | Trigger Selection Circuit                        |

| TRM       | Trimming Circuit                                 |

| TSPI      | Serial Peripheral Interface                      |

| T32A      | 32-bit Timer Event Counter                       |

| UART      | Asynchronous Serial Communication Circuit        |

## 1. クロック制御と動作モード

### 1.1. 概要

クロック/モード制御ブロックでは、クロックギアやプリスケーラークロックの選択、発振器のウォーミングアップなどを設定することができます。

また、動作モードとして **NORMAL** モードと低消費電力モードがあり、使用方法に応じモード遷移を行うことで消費電力を抑えることができます。

クロックに関連する機能としては以下のようないわがあります。

- システムクロックの制御

- プリスケーラークロックの制御

## 1.2. クロック制御

### 1.2.1. クロックの種類

クロックの一覧を以下に示します。

EHCLKIN: 外部から入力される高速クロック

fosc: 内部発振回路で生成されるクロックと X1、X2 端子より入力されるクロックの

[CGOSCCR]<OSCSEL>で選択後のクロック

f<sub>PLL</sub>: PLL0 により倍速されたクロック

fc: [CGPLL0SEL]<PLL0SEL>で選択されたクロック(高速クロック)

f<sub>sys</sub>: [CGSYSCR]<GEAR[2:0]>で選択されたシステムクロック

ΦT0: [CGSYSCR]<PRCK[3:0]>で選択されたクロック(プリスケーラークロック)

f<sub>IHOSC1</sub>: 内蔵高速発振器 1 で生成されるクロック

f<sub>IHOSC2</sub>: 内蔵高速発振器 2 で生成されるクロック

ADCLK: ADC 用変換クロック

TRCLKIN: デバッグ回路(トレースまたは SWV)のトレース機能用クロック

### 1.2.2. リセット動作による初期値

リセット動作により、クロック設定は下記のような状態に初期化されます。

外部高速発振器: 停止

内蔵高速発振器 1: 発振

内蔵高速発振器 2: 停止

PLL(倍速回路): 停止

ギアクロック: fc(分周なし)

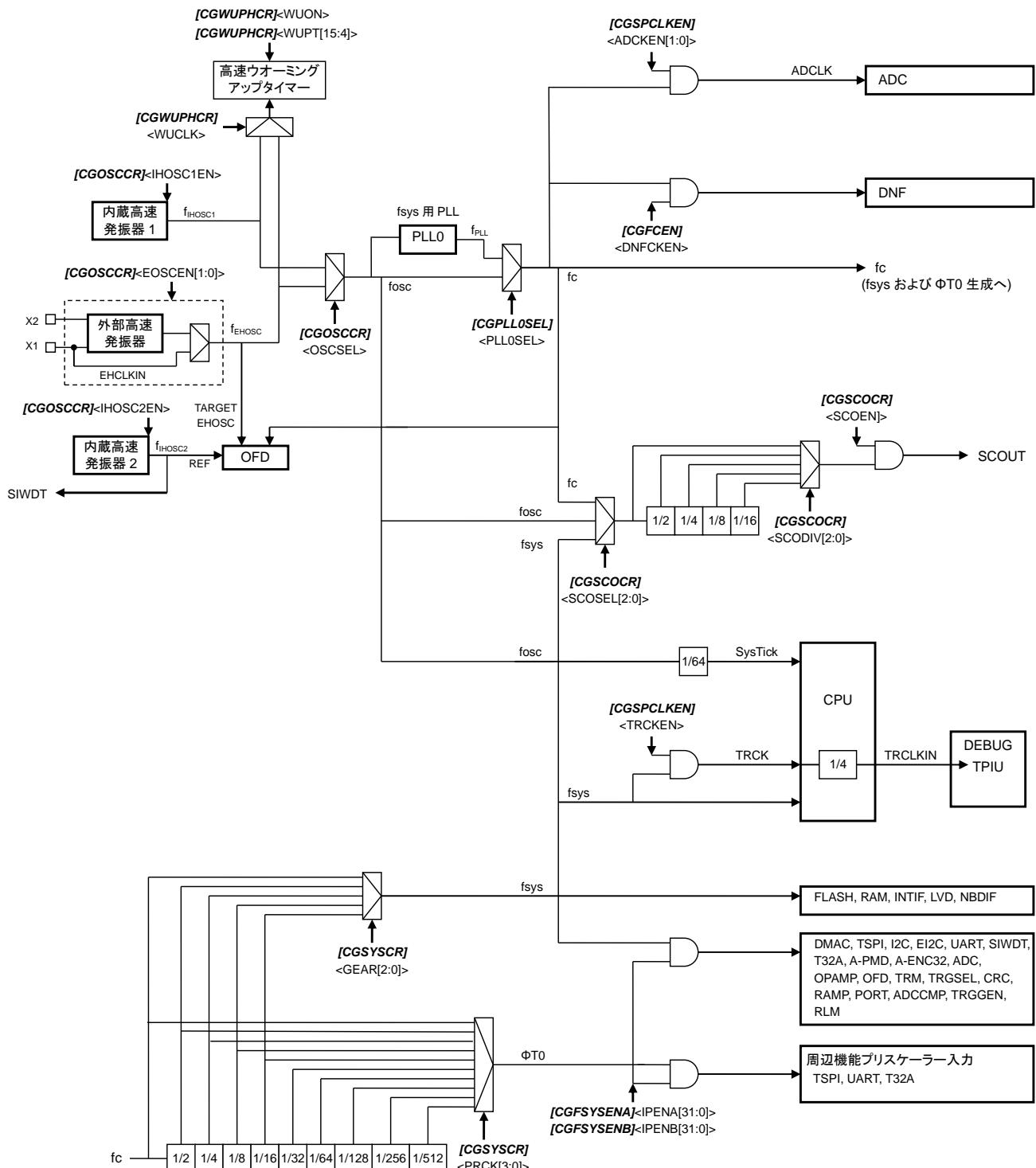

## 1.2.3. クロック系統図

クロック系統図を示します。

図 1.1 クロック系統図

## 1.2.4. ウオーミングアップ機能

ウォーミングアップ機能は、自動で高速発振用ウォーミングアップタイマーを起動して、STOP1 モード解除時の発振安定時間を確保するための機能の他、外部発振器や内蔵発振器の安定待ちのために高速発振用ウォーミングアップタイマーを使用したカウントアップタイマーとしても使用可能です。

この章では、ウォーミングアップタイマー用レジスターへの設定方法と、カウントアップタイマーとして使用する場合について説明しています。STOP1 モード解除時の詳細説明については、「1.3.3.2. 低消費電力モード解除時のウォーミングアップ」を参照してください。

### 1.2.4.1. 高速発振用ウォーミングアップタイマー

高速発振用ウォーミングアップタイマーとして、16 ビットのアップタイマーを内蔵しています。STOP1 モードへ遷移前に設定する場合も、下記の計算式で算出し、下位 4 ビットを切り捨てて、上位 12 ビットへ設定します。レジスターは、**[CGWUPHCR]<WUPT[15:4]>**に設定することになります。

<計算式>

(外部高速発振の場合)

$$\begin{aligned} \text{ウォーミングアップタイマー設定値(16 ビット)} \\ = (\text{ウォーミングアップ時間(s)} \div \text{クロック周期(s)}) - 16 \end{aligned}$$

(例) 発振器 10MHz(クロック周期 100ns)で、ウォーミングアップ時間 5ms を設定する場合

$$\begin{aligned} \text{ウォーミングアップタイマー設定値(16 ビット)} &= (5ms \div 100ns) - 16 \\ &= 50000 - 16 \\ &= 49984 \\ &= 0xC340 \end{aligned}$$

レジスターへは、上位 12 ビットを設定しますので、下記のように設定します。

**[CGWUPHCR]<WUPT[15:4]>** = 0xC34

(内蔵高速発振器 1 の場合)

$$\begin{aligned} \text{ウォーミングアップタイマー設定値(16 ビット)} \\ = ((\text{ウォーミングアップ時間(s)} - 63.3(\mu s)) \div \text{クロック周期(s)}) - 41 \end{aligned}$$

(例) 発振器 10MHz(クロック周期 100ns)で、ウォーミングアップ時間 163.4μs を設定する場合

$$\begin{aligned} \text{ウォーミングアップタイマー設定値(16 ビット)} &= ((163.4\mu s - 63.3\mu s) \div 100ns) - 41 \\ &= (100.1\mu s \div 100ns) - 41 \\ &= 960 \\ &= 0x03C0 \end{aligned}$$

レジスターへは、上位 12 ビットを設定しますので、下記のように設定します。

**[CGWUPHCR]<WUPT[15:4]>** = 0x03C

設定範囲は、 $0x03C \leq <WUPT[15:4]> \leq 0xFFFF$  で行い、ウォーミングアップ時間は、 $163.4\mu s \sim 6.6194$  ms となります。

### 1.2.4.2. ウオーミングアップタイマーの使用方法

ウォーミングアップ機能の使用方法を説明します。

(1) クロックの選択

高速発振の場合は、ウォーミングアップタイマーでカウントするクロック種別(内蔵発振/外部発振)を、**[CGWUPHCR]<WUCLK>**で選択します。

(2) ウォーミングアップタイマー設定値の算出

ウォーミングアップ時間は、高速発振用のタイマーへ任意の値が設定可能です。それぞれの計算式から算出し、設定してください。

(3) ウォーミングアップの開始および終了確認

ソフトウェア(命令)によりウォーミングアップの開始および終了確認を行う場合、開始は、**[CGWUPHCR]<WUON>**へ"1"を設定することでウォーミングアップタイマーがスタートします。終了は**[CGWUPHCR]<WUEF>**が"1"→"0"になることで判別します。"1"でウォーミングアップ中、"0"で終了を示します。カウント終了後、タイマーはリセットされて初期状態に戻ります。タイマー動作中に**[CGWUPHCR]<WUON>**へ"0"を書き込んでも、強制終了にはなりません。"0"書き込みは無視されます。

注) ウォーミングアップタイマーは発振クロックで動作しているため、発振周波数にゆらぎがある場合は誤差を含みます。従って概略時間としてとらえる必要があります。

### 1.2.5. fsys 用クロック遅倍回路(PLL)

fsys 用クロック遅倍回路は、高速発振器の出力クロック **fosc** の周波数(6MHz～24MHz)に最適な条件で遅倍した **f<sub>PLL</sub>** クロック(最大 120MHz)を出力する回路です。これにより、発振器への入力周波数は低く内部クロックは高速にすることが可能です。

#### 1.2.5.1. リセット解除後の PLL 設定

PLL はリセット解除後、ディセーブルです。

PLL を使用するためには、**[CGPLL0SEL]<PLL0ON>**が"0"の状態で、**[CGPLL0SELJ]<PLL0SET[23:0]>**の遅倍値の設定を行った後、PLL の初期化時間として約 100μs 経過後に、**<PLL0ON>**を"1"に設定して PLL の動作を開始します。その後、ロックアップ時間約 400μs 経過後に、**[CGPLL0SELJ]<PLL0SEL>**を"1"に設定することにより、**fosc** を遅倍した **f<sub>PLL</sub>** クロックを使用することができます。

なお、PLL 動作が安定するまでの時間は、ウォーミングアップ機能などを用いて確保する必要があります。

## 1.2.5.2. PLL 週波数の計算式と設定例

PLL 週波数を設定する  $[CGPLL0SEL]<PLL0SET[23:0]>$  の内訳詳細を下記に示します。

表 1.1  $[CGPLL0SEL]<PLL0SET[23:0]>$  設定詳細

| PLL0SET の内訳  | 機能           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| [23:17]      | 補正值設定        | fosc / 450000 の商(整数)。表 1.2 を参照してください。                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| [16:14]      | fosc 設定      | 000: 6 ≤ fosc ≤ 7<br>001: 7 < fosc ≤ 8<br>010: 8 < fosc ≤ 10<br>011: 10 < fosc ≤ 12<br>(単位: MHz)                                                                                                                                                                                                                                                                                                                                                                                    |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| [13:12]      | 分周設定         | 00: Reserved<br>01: 1 / 2 (2 分周)<br>10: 1 / 4 (4 分周)<br>11: 1 / 8 (8 分周)                                                                                                                                                                                                                                                                                                                                                                                                            |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| [11:8]       | 小数部<br>週波数設定 | <table border="0"> <tr> <td>0000: 0.0000</td> <td>1000: 0.5000</td> </tr> <tr> <td>0001: 0.0625</td> <td>1001: 0.5625</td> </tr> <tr> <td>0010: 0.1250</td> <td>1010: 0.6250</td> </tr> <tr> <td>0011: 0.1875</td> <td>1011: 0.6875</td> </tr> <tr> <td>0100: 0.2500</td> <td>1100: 0.7500</td> </tr> <tr> <td>0101: 0.3125</td> <td>1101: 0.8125</td> </tr> <tr> <td>0110: 0.3750</td> <td>1110: 0.8750</td> </tr> <tr> <td>0111: 0.4375</td> <td>1111: 0.9375</td> </tr> </table> | 0000: 0.0000 | 1000: 0.5000 | 0001: 0.0625 | 1001: 0.5625 | 0010: 0.1250 | 1010: 0.6250 | 0011: 0.1875 | 1011: 0.6875 | 0100: 0.2500 | 1100: 0.7500 | 0101: 0.3125 | 1101: 0.8125 | 0110: 0.3750 | 1110: 0.8750 | 0111: 0.4375 | 1111: 0.9375 |

| 0000: 0.0000 | 1000: 0.5000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| 0001: 0.0625 | 1001: 0.5625 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| 0010: 0.1250 | 1010: 0.6250 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| 0011: 0.1875 | 1011: 0.6875 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| 0100: 0.2500 | 1100: 0.7500 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| 0101: 0.3125 | 1101: 0.8125 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| 0110: 0.3750 | 1110: 0.8750 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| 0111: 0.4375 | 1111: 0.9375 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| [7:0]        | 整数部<br>週波数設定 | 0x00: 0<br>0x01: 1<br>0x02: 2<br>:<br>0xFD: 253<br>0xFE: 254<br>0xFF: 255                                                                                                                                                                                                                                                                                                                                                                                                           |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |

注) 週波数は、 $<PLL0SET[7:0]>$ (整数部)と $<PLL0SET[11:8]>$ (小数部)の合算です。

$f_{PLL}$  は、以下の計算式で表されます。

$$f_{PLL} = f_{osc} \times ([CGPLL0SEL]<PLL0SET[7:0]> + [CGPLL0SEL]<PLL0SET[11:8]>) \times [CGPLL0SEL]<PLL0SET[13:12]>$$

- 注 1) 周波数精度の絶対値は保証しません。

- 注 2) 小数部週波数設定にリニアリティーはありません。

- 注 3)  $f_{PLL} \leq$  最大動作周波数

表 1.2 PLL補正值(例)

| fosc(MHz) | <PLL0SET[23:17]>(10進、整数値) |

|-----------|---------------------------|

| 6.00      | 14                        |

| 8.00      | 18                        |

| 10.00     | 23                        |

| 12.00     | 27                        |

| 24.00     | 54                        |

PLL 補正值は、以下で求めることができます

$fosc = 6.0\text{MHz}$  時、 $6 / 0.45 = 13.33 \rightarrow 14$  ; 小数部は切り上げ

[CGPLL0SEL]<PLL0SET[23:0]>の主な設定例を、下記に示します。

入力周波数(fosc)を、PLL で遅倍、分周し、目的とするクロック周波数(f<sub>PLL</sub>)を生成します。

分周値は、1/2、1/4、1/8 から選択します。

また、遅倍後の周波数は次の範囲で設定してください。

$200\text{MHz} \leq (fosc \times \text{遅倍値}) \leq 400\text{MHz}$

表 1.3 PLL0SET設定値(例)

| fosc(MHz) | 遅倍値     | 分周値 | f <sub>PLL</sub> (MHz) | <PLL0SET[23:0]> |

|-----------|---------|-----|------------------------|-----------------|

| 6.00      | 40.0000 | 1/2 | 120.00                 | 0x1C1028        |

| 8.00      | 30.0000 | 1/2 | 120.00                 | 0x24501E        |

| 10.00     | 24.0000 | 1/2 | 120.00                 | 0x2E9018        |

| 12.00     | 20.0000 | 1/2 | 120.00                 | 0x36D014        |

| 24.00     | 10.0000 | 1/2 | 120.00                 | 0x6D900A        |

| 6.00      | 53.3125 | 1/4 | 79.97                  | 0x1C2535        |

| 8.00      | 40.0000 | 1/4 | 80.00                  | 0x246028        |

| 10.00     | 32.0000 | 1/4 | 80.00                  | 0x2EA020        |

| 12.00     | 26.6250 | 1/4 | 79.88                  | 0x36EA1A        |

| 24.00     | 13.3125 | 1/4 | 79.88                  | 0x6DA50D        |

### 1.2.5.3. 動作中の PLL 遅倍値の変更

PLL 遅倍クロック動作中に、遅倍値の変更を行う場合、まず[CGPLL0SEL]<PLL0SEL>に"0"を設定し、PLL 遅倍クロックを使用しない設定に切り替えます。そして、[CGPLL0SEL]<PLL0ST>=0 を読み出し、遅倍クロックを使用しない設定に切り替わったことを確認した後、[CGPLL0SEL]<PLL0ON>を"0"として PLL を停止します。

その後、[CGPLL0SEL]<PLL0SET[23:0]>の遅倍値を変更し、PLL の初期化時間として約 100μs 経過後に、[CGPLL0SEL]<PLL0ON>を"1"に設定して PLL の動作を開始します。

その後、ロックアップ時間約 400μs 経過後に、[CGPLL0SEL]<PLL0SEL>を"1"に設定します。

最後に、[CGPLL0SEL]<PLL0ST>をリードし、切り替わったことを確認します。

## 1.2.5.4. PLL 動作開始/停止切り替えシーケンス

## (1) fc 設定(PLL 停止 → PLL 動作)

fc 設定として、PLL 停止状態から PLL 動作状態への切り替え手順例は、下記のようになります。

| «切り替え前の状態»                                  |                                   |

|---------------------------------------------|-----------------------------------|

| <code>[CGPLL0SEL]&lt;PLL0ON&gt; = 0</code>  | fsys 用 PLL 動作が停止                  |

| <code>[CGPLL0SEL]&lt;PLL0SEL&gt; = 0</code> | fsys 用 PLL 選択が PLL 未使用(fosc)      |

| <code>[CGPLL0SEL]&lt;PLL0ST&gt; = 0</code>  | fsys 用 PLL 選択ステータスが PLL 未使用(fosc) |

| «切り替えシーケンス例»                                          |                                              |

|-------------------------------------------------------|----------------------------------------------|

| 1 <code>[CGPLL0SEL]&lt;PLL0SET[23:0]&gt; = 0xX</code> | PLL 適倍値設定(0xX)を選択する                          |

| 2 100μs 以上待つ                                          | 適倍設定後の待ち時間                                   |

| 3 <code>[CGPLL0SEL]&lt;PLL0ON&gt; = 1</code>          | fsys 用 PLL 動作を発振にする                          |

| 4 400μs 以上待つ                                          | PLL 出力クロック安定待ち時間(ロックアップ時間)                   |

| 5 <code>[CGPLL0SEL]&lt;PLL0SEL&gt; = 1</code>         | fsys 用 PLL 選択を PLL 使用(fPLL)にする               |

| 6 <code>[CGPLL0SEL]&lt;PLL0ST&gt;</code> をリード         | fsys 用 PLL 選択ステータスが PLL 使用(fPLL)(= 1)になるまで待つ |

注) 1 ~ 4 は、切り替え前の状態が`[CGPLL0SEL]<PLL0ON>=1` の場合は不要です。

PLL 出力クロックが安定した状態から切り替える場合は、5、6 のみの実行で PLL 動作状態へ切り替え可能です。

## (2) fc 設定(PLL 動作→PLL 停止)

fc 設定として、PLL 動作状態から PLL 停止状態への切り替え手順例は、下記のようになります。

| «切り替え前の状態»                                  |                                  |

|---------------------------------------------|----------------------------------|

| <code>[CGPLL0SEL]&lt;PLL0ON&gt; = 1</code>  | fsys 用 PLL 選択が発振                 |

| <code>[CGPLL0SEL]&lt;PLL0SEL&gt; = 1</code> | fsys 用 PLL 選択が PLL 使用(fPLL)      |

| <code>[CGPLL0SEL]&lt;PLL0ST&gt; = 1</code>  | fsys 用 PLL 選択ステータスが PLL 使用(fPLL) |

| «切り替えシーケンス例»                                  |                                               |

|-----------------------------------------------|-----------------------------------------------|

| 1 <code>[CGPLL0SEL]&lt;PLL0SEL&gt; = 0</code> | fsys 用 PLL 選択を PLL 未使用(fosc)にする               |

| 2 <code>[CGPLL0SEL]&lt;PLL0ST&gt;</code> をリード | fsys 用 PLL 選択ステータスが PLL 未使用(fosc)(= 0)になるまで待つ |

| 3 <code>[CGPLL0SEL]&lt;PLL0ON&gt; = 0</code>  | fsys 用 PLL 動作を停止にする                           |

## 1.2.6. システムクロック

システムクロックの源振として、内蔵高速発振クロック、外部高速発振クロック(発振子接続またはクロック入力)が使用可能です。

システムクロックは[CGSYSCR]<GEAR[2:0]>(クロックギア)で分周が可能です。設定は動作中に変更可能ですが、レジスター書き込み後、実際にクロックが切り替わるまでに  $f_c$  で最大 16 クロックの時間が必要です。クロック切り替えの完了は、[CGSYSCR]<GEARST[2:0]>で確認してください。

注) タイマーカウンターなどの周辺機能の動作中にクロックギアを切り替えないようにしてください。

発振周波数、PLL 適倍値などで設定した周波数  $f_c$  に対するクロックギア比(1/1 ~ 1/16)による動作周波数例を下記に示します。

表 1.4 動作周波数(単位: MHz)例

| 外部<br>発振<br>(MHz) | 外部<br>クロック<br>入力<br>(MHz) | 内蔵発振<br>IHOSC1<br>(MHz) | PLL<br>適倍値<br>(分周後) | 最大<br>周波数<br>( $f_c$ )(MHz) | クロックギア<br>PLL = ON 時 |       |       |      |      | クロックギア<br>PLL = OFF 時 |     |     |      |      |

|-------------------|---------------------------|-------------------------|---------------------|-----------------------------|----------------------|-------|-------|------|------|-----------------------|-----|-----|------|------|

|                   |                           |                         |                     |                             | 1/1                  | 1/2   | 1/4   | 1/8  | 1/16 | 1/1                   | 1/2 | 1/4 | 1/8  | 1/16 |

| 6                 | 6                         | -                       | 20                  | 120                         | 120                  | 60    | 30    | 15   | 7.5  | 6                     | 3   | 1.5 | -    | -    |

| 8                 | 8                         | -                       | 15                  | 120                         | 120                  | 60    | 30    | 15   | 7.5  | 8                     | 4   | 2   | 1    | -    |

| 10                | 10                        | 10                      | 12                  | 120                         | 120                  | 60    | 30    | 15   | 7.5  | 10                    | 5   | 2.5 | 1.25 | -    |

| 12                | 12                        | -                       | 10                  | 120                         | 120                  | 60    | 30    | 15   | 7.5  | 12                    | 6   | 3   | 1.5  | -    |

| 24                | 24                        | -                       | 5                   | 120                         | 120                  | 60    | 30    | 15   | 7.5  | 24                    | 12  | 6   | 3    | 1.5  |

| 6                 | 6                         | -                       | 13.329              | 79.97                       | 79.97                | 39.99 | 20    | 10   | 5    | 6                     | 3   | 1.5 | -    | -    |

| 8                 | 8                         | -                       | 10                  | 80                          | 80                   | 40    | 20    | 10   | 5    | 8                     | 4   | 2   | 1    | -    |

| 10                | 10                        | 10                      | 8                   | 80                          | 80                   | 40    | 20    | 10   | 5    | 10                    | 5   | 2.5 | 1.25 | -    |

| 12                | 12                        | -                       | 6.657               | 79.88                       | 79.88                | 39.95 | 19.98 | 9.99 | 4.99 | 12                    | 6   | 3   | 1.5  | -    |

| 24                | 24                        | -                       | 3.328               | 79.88                       | 79.88                | 39.95 | 19.98 | 9.99 | 4.99 | 24                    | 12  | 6   | 3    | 1.5  |

## 1.2.6.1. システムクロックの設定方法

## (1) fosc 設定(内蔵発振→外部発振)

fosc 設定として、内蔵高速発振器 1(IHOSC1)から外部高速発振器(EHOSC)への切り替え手順例を下記に示します。

| «切り替え前の状態»                           |                              |

|--------------------------------------|------------------------------|

| <i>[CGOSCCR]&lt;IHOSC1EN&gt; = 1</i> | 内蔵高速発振器 1 が発振                |

| <i>[CGOSCCR]&lt;OSCSEL&gt; = 0</i>   | fosc 用高速発振選択が内部(IHOSC1)      |

| <i>[CGOSCCR]&lt;OSCF&gt; = 0</i>     | fosc 用高速発振選択ステータスが内部(IHOSC1) |

| X1/X2 端子に発振子を接続(注)                   |                              |

注) 発振子以外は接続しないでください。

| «切り替えシーケンス例»                                                                      |                                                                   |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 1 <i>[PHPDN]&lt;bit[1:0]&gt; = 00</i><br><i>[PHIE]&lt;bit[1:0]&gt; = 00</i>       | X1/X2 端子のプルダウンをディセーブル<br>X1/X2 端子の入力制御をディセーブル                     |

| 2 <i>[CGOSCCR]&lt;EOSCEN[1:0]&gt; = 01</i>                                        | 外部発振器の動作選択を外部高速発振器(EHOSC)                                         |

| 3 <i>[CGWUPHCR]&lt;WUCLK&gt; = 1</i><br><i>[CGWUPHCR]&lt;WUPT[15:4]&gt; = 任意値</i> | 高速発振ウォーミングアップクロック選択を外部高速発振器(EHOSC)<br>ウォーミングアップタイマー設定値へ発振器安定時間を設定 |

| 4 <i>[CGWUPHCR]&lt;WUON&gt; = 1</i>                                               | 高速発振ウォーミングアップをスタートする                                              |

| 5 <i>[CGWUPHCR]&lt;WUEF&gt;をリード</i>                                               | 高速発振ウォーミングアップ終了(=0)になるまで待つ                                        |

| 6 <i>[CGOSCCR]&lt;OSCSEL&gt; = 1</i>                                              | fosc 用高速発振選択を外部高速発振器(EHOSC)へ                                      |

| 7 <i>[CGOSCCR]&lt;OSCF&gt;をリード</i>                                                | fosc 用高速発振選択ステータスが外部(EHOSC)になるまで待つ                                |

| 8 <i>[CGOSCCR]&lt;IHOSC1EN&gt; = 0</i>                                            | 内蔵高速発振器 1 を停止                                                     |

## (2) fosc 設定(内蔵発振→外部クロック入力)

fosc 設定として、内蔵高速発振器 1(IHOSC1)から外部クロック入力(EHCLKIN)への切り替え手順例を下記に示します。

| «切り替え前の状態»                           |                                     |

|--------------------------------------|-------------------------------------|

| <i>[CGOSCCR]&lt;IHOSC1EN&gt; = 1</i> | 内蔵高速発振器 1 が発振                       |

| <i>[CGOSCCR]&lt;OSCSEL&gt; = 0</i>   | fosc 用高速発振選択が内蔵高速発振器 1(IHOSC1)      |

| <i>[CGOSCCR]&lt;OSCF&gt; = 0</i>     | fosc 用高速発振選択ステータスが内蔵高速発振器 1(IHOSC1) |

| EHCLKIN へのクロック入力                     | 適正電圧範囲で入力してください。                    |

| «切り替えシーケンス例»                                                            |                                                     |

|-------------------------------------------------------------------------|-----------------------------------------------------|

| 1 <i>[PHPDN]&lt;bit[0]&gt; = 0</i><br><i>[PHIE]&lt;bit[0]&gt; = 0/1</i> | X1/EHCLKIN 端子のプルダウンをディセーブル<br>X1/EHCLKIN 端子の入力制御は任意 |

| 2 <i>[CGOSCCR]&lt;EOSCEN[1:0]&gt; = 10</i>                              | 外部高速発振器の動作選択を外部クロック入力(EHCLKIN)にする                   |

| 3 <i>[CGOSCCR]&lt;OSCSEL&gt; = 1</i>                                    | fosc 用高速発振選択を外部クロックへ                                |

| 4 <i>[CGOSCCR]&lt;OSCF&gt;をリード</i>                                      | fosc 用高速発振選択ステータスが外部(=1)になるまで待つ                     |

| 5 <i>[CGOSCCR]&lt;IHOSC1EN&gt; = 0</i>                                  | 内蔵高速発振器 1 を停止                                       |

## (3) fosc 設定(外部発振/外部クロック入力→内蔵発振)

fosc 設定として、外部高速発振器(EHOSC)動作状態または外部クロック入力(EHCLKIN)動作状態から、内蔵高速発振器 1(IHOSC1)への切り替え手順例を下記に示します。

| «切り替え前の状態»                                      |                                      |

|-------------------------------------------------|--------------------------------------|

| <i>[CGOSCCRJ]&lt;EOSCEN[1:0]&gt; = 01 or 10</i> | 外部高速発振器の動作選択が外部高速発振器(EHOSC)か外部クロック入力 |

| <i>[CGOSCCRJ]&lt;OSCSEL&gt; = 1</i>             | fosc 用高速発振選択が外部高速発振器(EHOSC)          |

| <i>[CGOSCCRJ]&lt;OSCF&gt; = 1</i>               | fosc 用高速発振選択ステータスが外部高速発振器(EHOSC)     |

| «切り替えシーケンス例»                                |                                          |

|---------------------------------------------|------------------------------------------|

| 1 <i>[CGWUPHCR]&lt;WUCLK&gt;=0</i>          | ウォーミングアップクロック選択を内蔵高速発振器 1(IHOSC1)にする     |

| 2 <i>[CGWUPHCR]&lt;WUPT[15:4]&gt;=0x03C</i> | 高速発振ウォーミングアップ設定値に 163.4μs(=0x03C)以上を設定する |

| 3 <i>[CGOSCCR]&lt;IHOSC1EN&gt; = 1</i>      | 内蔵高速発振器 1 を発振する                          |

| 4 <i>[CGWUPHCR]&lt;WUON&gt; = 1</i>         | 高速発振ウォーミングアップタイマーをスタートする                 |

| 5 <i>[CGWUPHCR]&lt;WUEF&gt;</i> をリード        | ウォーミングアップタイマーステータスが終了(=0)になるまで待つ         |

| 6 <i>[CGOSCCR]&lt;OSCSEL&gt; = 0</i>        | fosc 用高速発振選択を内蔵高速発振器 1(IHOSC1)にする        |

| 7 <i>[CGOSCCR]&lt;OSCF&gt;</i> をリード         | fosc 用高速発振選択ステータスが内蔵高速発振器 1(=0)になるまで待つ   |

| 8 <i>[CGOSCCR]&lt;EOSCEN[1:0]&gt; = 00</i>  | 外部高速発振器の動作選択を未使用にする                      |

### 1.2.7. クロック供給設定機能

本製品には、周辺機能に対してクロック供給 On/Off 機能があり、使用しない周辺機能に対して、クロック供給を停止することで消費電流を削減することができます。

リセット解除後は、一部の周辺機能を除き、クロックが供給されていない状態です。

使用する機能のクロックを供給するには **[CGFSYSENA]**、**[CGFSYSENB]**、**[CGFCEN]**、**[CGSPCLKEN]** の該当のビットを "1" に設定します。

レジスターの詳細は、「1.4. レジスターの説明」を参照してください。

### 1.2.8. クロックの端子出力機能

本製品には、クロックの端子出力機能があります。出力可能なクロックとして、高速発振「fosc」、高速クロック「fc」、システムクロック「fsys」を SCOUT 端子から出力できます。

詳細は、「1.4.2.5. **[CGSCOCR]** (SCOUT 出力制御レジスター)」を参照してください。

SCOUT 端子の動作モード別使用可否状態を示します。

表 1.5 SCOUT端子使用可否一覧

| SCOUT 選択 | 動作モード       |       |

|----------|-------------|-------|

|          | NORMAL/IDLE | STOP1 |

| fosc     | ○           | ×     |

| fc       | ○           | ×     |

| fsys     | ○           | ×     |

注) ○: 使用可能、×: 使用不可

### 1.2.9. プリスケーラークロック

周辺機能には、それぞれにクロック  $\Phi T0$  を分周するプリスケーラーがあります。これらのプリスケーラーへ入力するクロック  $\Phi T0$  は、**[CGSYSCR]<PRCK[3:0]>** で分周することができます。リセット後の  $\Phi T0$  は、fc が選択されます。

レジスター書き込み後、実際にクロックが切り替わるまでに fc で最大 512 クロックの時間が必要です。クロック切り替えの完了は、**[CGSYSCR]<PRCKST[3:0]>** で確認してください。

注) タイマーカウンターなどの周辺機能の動作中にプリスケーラークロックを切り替えないようにしてください。

## 1.3. 動作モード

本製品には、動作モードとして NORMAL モードと低消費電力モード(IDLE、STOP1)があり、使用方法に応じモード遷移を行うことで消費電力を抑えることができます。

### 1.3.1. 動作モードの詳細

#### 1.3.1.1. 各モードの特長

NORMAL、低消費電力モードの特長は次のとおりです。

- NORMAL モード

CPU コア、および周辺回路を動作させるモードです。リセット解除後は、NORMAL モードとなります。

- 低消費電力モード

低消費電力モードは以下のとおりです。

- IDLE モード

CPU が停止するモードです。

周辺機能は各周辺機能のレジスター、クロック供給設定機能などにより、動作/停止を行ってください。

注)IDLE モード中は CPU によるウォッチドッグタイマーのクリアができませんので注意してください。

- STOP1 モード

内蔵高速発振器も含めて全ての内部回路が停止するモードです。

STOP1 モードが解除されると内蔵高速発振器 1(IHOSC1)が発振を開始し、NORMAL モードへ復帰します。

STOP1 モードに遷移する前に、STOP1 解除に使用しない割り込みは禁止してください。

### 1.3.1.2. 低消費電力モードへの遷移と復帰

各低消費電力動作へ遷移するには、スタンバイ制御レジスター [*CGSTBYCR*]<STBY[1:0]>で IDLE/STOP1 モードを選択し、WFI (Wait For Interrupt)命令を実行します。WFI 命令によって低消費電力モードへ遷移した場合、低消費電力モードからの復帰はリセットまたは割り込み発生により行われます。割り込みで復帰する場合には、設定を行っておく必要があります。詳細はリファレンスマニュアル「例外」の「割り込み」章を参照してください。

注 1) 本製品ではイベントによる復帰はサポートしていないため、WFE (Wait For Event)による低消費電力モードへの遷移は行わないでください。

注 2) 本製品は、Arm Cortex-M4®(FPU 機能搭載)コアの SLEEPDEEP による低消費電力モードはサポートしていません。システム制御レジスターの<SLEEPDEEP>ビットは設定しないでください。

### 1.3.1.3. 低消費電力モードの選択

低消費電力モード選択は、[*CGSTBYCR*]<STBY[1:0]>の設定で選択されます。

下表に<STBY[1:0]>の設定より選択されるモードを示します。

表 1.6 低消費電力モード選択

| モード   | [ <i>CGSTBYCR</i> ]<STBY[1:0]> |

|-------|--------------------------------|

| IDLE  | 00                             |

| STOP1 | 01                             |

注) 上記の設定以外は行わないでください

## 1.3.1.4. 低消費電力モードにおける周辺機能状態

各モードにおける周辺機能(ブロック)の動作状態を表 1.7 に示します。

なお、リセット解除後は、一部のブロックを除きクロックが供給されない状態となります。

必要に応じて、[CGFSYSENA]、[CGFSYSENB]、[CGFCEN]、[CGSPCLKEN]を設定しクロック供給を許可してください。

表 1.7 低消費電力モード別ブロック動作状態一覧

| Block                     | NORMAL | IDLE    | STOP1 |

|---------------------------|--------|---------|-------|

| Processor core (Debug 含む) | ○      | —       | —     |

| DMAC                      | ○      | ○       | —     |

| I/O port                  | 端子状態   | ○       | ○     |

|                           | レジスター  | ○       | —     |

| ADC(OPAMP 含む)             | ○      | ○       | —     |

| UART                      | ○      | ○       | —     |

| I2C                       | ○      | ○       | —     |

| EI2C                      | ○      | ○       | —     |

| TSPI                      | ○      | ○       | —     |

| A-PMD                     | ○      | ○       | —     |

| A-ENC32                   | ○      | ○       | —     |

| T32A                      | ○      | ○       | —     |

| TRGSEL                    | ○      | ○       | —     |

| CRC                       | ○      | ○       | —     |

| SIWDT                     | ○      | ○ (注 1) | —     |

| LVD                       | ○      | ○       | ○     |

| OFD                       | ○      | ○       | —     |

| TRM                       | ○      | 使用不可    | —     |

| CG                        | ○      | ○       | ○     |

| PLL                       | ○      | ○       | —     |

| RAM パリティー(RAMP)           | ○      | ○       | —     |

| 外部高速発振器(EHOSC)            | ○      | ○       | —     |

| 内蔵高速発振器 1(IHOSC1)         | ○      | ○       | —     |

| 内蔵高速発振器 2(IHOSC2)         | ○      | ○       | —     |

| Code Flash                | アクセス可能 | アクセス可能  | データ保持 |

| RAM                       |        | (注 2)   |       |

○: 動作可能

—: 対象のモードに遷移すると自動的に周辺回路へのクロックが停止

注 1) プロテクト A モードのみ。それ以外の場合は、IDLE モードへ遷移する前に SIWDT を停止してください。

注 2) CPU 以外のデータアクセス(R/W)する周辺機能(DMA など)がバスマトリックス上で接続されていない場合は、データ保持となります。

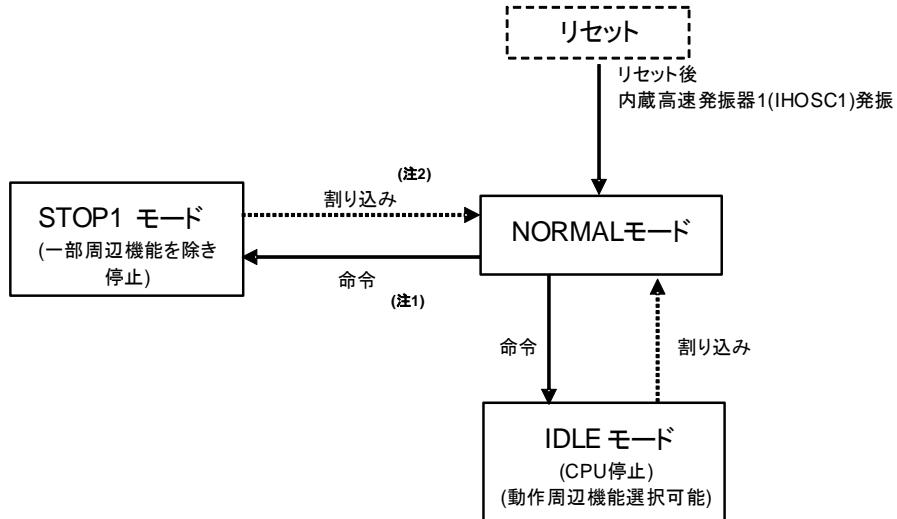

## 1.3.2. モード状態遷移

図 1.2 モード状態遷移

注 1) 復帰時にウォーミングアップが必要となります。ウォーミングアップ時間の設定は STOP1 モードに入る前のモード(NORMAL モード)で設定する必要があります。

注 2) STOP1 モードからの復帰時は割り込み起動要因の処理ルーチンに分岐します。

## 1.3.2.1. IDLE モード遷移フロー

IDLE へ遷移する場合は、以下の順番で設定してください。

IDLE モードは割り込みで解除されますので、IDLE モードへ遷移する前に割り込みの設定を行ってください。IDLE モード解除に使用可能な割り込みは「1.3.3.1. 低消費電力モードの解除ソース」を参照してください。解除に使用しない割り込み、および使用できない割り込みは禁止してください。

| 遷移フロー(NORMAL モードから) |                                          |                             |

|---------------------|------------------------------------------|-----------------------------|

| 1                   | <i>[SIWDxEN]&lt;WDTE&gt; = 0</i>         | SIWDT をディセーブルにする            |

| 2                   | <i>[SIWDxCR]&lt;WDCR[7:0]&gt; = 0xB1</i> | SIWDT をディセーブルにする            |

| 3                   | <i>[FCSR0]&lt;RDYBSY&gt;をリード</i>         | Flash が Ready 状態(=1)になるまで待つ |

| 4                   | <i>[CGSTBYCR]&lt;STBY[1:0]&gt; = 00</i>  | 低消費電力モード選択を IDLE にする        |

| 5                   | <i>[CGSTBYCR]&lt;STBY[1:0]&gt;をリード</i>   | 4 のレジスターライトを確認する(=00)       |

| 6                   | WFI 命令実行                                 | IDLE へ遷移する                  |

注) SIWDT のプロテクト A モードを使用する場合は、1、2 の処理は不要です。

## 1.3.2.2. STOP1 モード遷移フロー

STOP1 モードへ遷移する場合は、以下の順番で設定してください。

STOP1 モードは割り込みで解除されますので、STOP1 モードへ遷移する前に割り込みの設定を行ってください。STOP1 モード解除に使用可能な割り込みは「1.3.3.1. 低消費電力モードの解除ソース」を参照してください。解除に使用しない割り込み、および使用できない割り込みは禁止してください。

| 遷移フロー(NORMAL モードから) |                                        |                                              |

|---------------------|----------------------------------------|----------------------------------------------|

| 1                   | <i>[SIWDxEN]</i> <WDTE> = 0            | SIWDT をディセーブルにする                             |

| 2                   | <i>[SIWDxCR]</i> <WDCR[7:0]> = 0xB1    | SIWDT をディセーブルにする                             |

| 3                   | <i>[FCSR0]</i> <RDYBSY>をリード            | Flash が Ready 状態(=1)になるまで待つ                  |

| 4                   | <i>[CGWUPHCR]</i> <WUEF>をリード           | 高速発振ウォーミングアップ終了(=0)になるまで待つ                   |

| 5                   | <i>[CGWUPHCR]</i> <WUCLK> = 0          | 高速発振ウォーミングアップクロック選択を内蔵高速発振器 1(IHOSC1)にする     |

|                     | <i>[CGWUPHCR]</i> <WUPT[15:4]> = 0x03C | 高速発振ウォーミングアップタイマー設定値に 163.4μs(=0x03C)以上を設定する |

| 6                   | <i>[CGSTBYCR]</i> <STBY[1:0]> = 01     | 低消費電力モード選択を STOP1 にする                        |

| 7                   | <i>[CGPLL0SEL]</i> <PLL0SEL> = 0       | fsys 用 PLL 選択を PLL 未使用(fosc)にする              |

| 8                   | <i>[CGPLL0SEL]</i> <PLL0ST>をリード        | fsys 用 PLL 選択ステータスが PLL 未使用になるまで待つ(=0)       |

| 9                   | <i>[CGPLL0SEL]</i> <PLL0ON> = 0        | fsys 用 PLL 動作を停止する                           |

| 10                  | <i>[CGOSCCR]</i> <IHOSC1EN> = 1        | 内蔵高速発振器 1 を発振にする                             |

| 11                  | <i>[CGWUPHCR]</i> <WUON> = 1           | 高速発振ウォーミングアップタイマーをスタートする                     |

| 12                  | <i>[CGWUPHCR]</i> <WUEF>をリード           | ウォーミングアップタイマーステータスが終了(=0)になるまで待つ             |

| 13                  | <i>[CGOSCCR]</i> <OSCSEL> = 0          | fosc 用高速発振選択を内蔵高速発振器 1(IHOSC1)にする            |

| 14                  | <i>[CGOSCCR]</i> <OSCF>をリード            | fosc 用高速発振選択ステータスが内蔵高速発振器 1(=0)になるまで待つ       |

| 15                  | <i>[CGOSCCR]</i> <EOSCEN[1:0]> = 00    | 外部発振の動作選択を未使用にする                             |

| 16                  | <i>[CGOSCCR]</i> <IHOSC2EN> = 0        | 内蔵高速発振器 2(IHOSC2)を停止する                       |

| 17                  | <i>[CGOSCCR]</i> <EOSCEN[1:0]>をリード     | 15 のレジスターライトを確認する(=00)                       |

| 18                  | <i>[CGOSCCR]</i> <IHOSC2F>をリード         | IHOSC2 用内蔵発振安定フラグが"0"になるまで待つ                 |

| 19                  | WFI 命令実行                               | STOP1 へ遷移する                                  |

### 1.3.3. 低消費電力モードからの復帰

#### 1.3.3.1. 低消費電力モードの解除ソース

低消費電力モードからの復帰は、割り込み、マスク不能割り込み、リセットによって行うことができます。使用できるスタンバイ解除ソースは、低消費電力モードにより決まります。

詳細を下表に示します。

表 1.8 解除ソース一覧

| 低消費電力モード |      | IDLE                                                                              | STOP1   |   |

|----------|------|-----------------------------------------------------------------------------------|---------|---|

| 解除ソース    | 割り込み | INT00 ~ INT10 (注 1)                                                               | ○       | ○ |

|          |      | INTEMGx, INTOVVx, INTPWMx                                                         | ○       | × |

|          |      | INTENCx0, INTENCx1                                                                | ○       | × |

|          |      | INTADxPDA, INTADxPDB                                                              | ○       | × |

|          |      | INTADxCP0, INTADxCP1, INTADxTRG                                                   | ○       | × |

|          |      | INTADxSGL, INTADxCNT                                                              | ○       | × |

|          |      | INTADCCMP                                                                         | ○       | × |

|          |      | INTSCxRX, INTSCxTX, INTSCxERR                                                     | ○       | × |

|          |      | INTI2CxNST, INTI2CxATX, INTI2CxBRX, INTI2CxNA                                     | ○       | × |

|          |      | INTT32AxAC, INTT32AxACAP0, INTT32AxACAP1, INTT32AxB, INTT32AxBCAP0, INTT32BxBCAP1 | ○       | × |

|          |      | INTDMAATC, INTDMAAERR                                                             | ○       | × |

|          |      | INTPARI                                                                           | ○       | × |

|          |      | INTFLCRDY                                                                         | ○       | × |

|          |      | SysTick 割り込み                                                                      | ○       | × |

|          |      | マスク不能割り込み(INTWDT0)                                                                | ○ (注 2) | × |

|          |      | マスク不能割り込み(INTLVD)                                                                 | ○       | ○ |

|          |      | リセット(SIWDT)                                                                       | ○ (注 2) | × |

|          |      | リセット(LVD)                                                                         | ○       | ○ |

|          |      | リセット(OFD)                                                                         | ○       | × |

|          |      | リセット(RESET_N 端子)                                                                  | ○       | ○ |

○: 解除後、割り込み処理を開始します

×: 解除に使用できません

注 1) INT00 ~ INT10(外部割り込み 00 ~ 10)は、立ち上がり/立ち下がり/レベルのいずれかを選択することができます。設定の詳細はリファレンスマニュアル「例外」を参照してください。

注 2) プロテクト A モードのみ。それ以外の場合は、遷移する前に SIWDT を停止してください。

- 割り込み要求による解除

割り込みによって低消費電力モードを解除する場合、CPUで割り込みが検出されるよう準備しておく必要があります。STOP1モードの解除に使用する割り込みは、CPUの設定の他にINTIFで割り込み検出の設定を行う必要があります。

- マスク不能割り込み(NMI)による解除

NMIの要因にはSIWDT割り込み(INTWDT、プロテクトAモードのみ)とLVD割り込み(INTLVD)があります。

- リセットによる解除

リセットは全ての低消費電力モードからの解除を行うことができます。

リセットで解除した場合には、解除後NORMALモードでレジスターが初期化された状態になります。詳細は「3.2.6.1.リセット要因と初期化範囲」を参照してください。

- SysTick割り込みによる解除

SysTick割り込みはIDLEモードでのみ使用可能です。

割り込みの詳細に関しては、リファレンスマニュアル「例外」の「割り込み」章を参照してください。

### 1.3.3.2. 低消費電力モード解除時のウォーミングアップ

モード遷移時、内部回路の安定のためウォーミングアップが必要な場合があります。

STOP1モードからNORMALモードへの復帰では、自動的に内部発振が選択されウォーミングアップ用タイマーが起動されます。ウォーミングアップ時間経過後にシステムクロックの出力が開始されます。

このため、STOP1モードに遷移する命令を実行する前に、[CGWUPHCR]<WUPT[15:4]>でウォーミングアップ時間の設定を行ってください。設定方法については、「1.2.4.1.高速発振用ウォーミングアップタイマー」を参照してください。

各動作モード遷移におけるウォーミングアップ設定の有無を下表に示します。

表 1.9 ウォーミングアップ

| 動作モード遷移        | ウォーミングアップ設定 |

|----------------|-------------|

| NORMAL → IDLE  | 不要          |

| NORMAL → STOP1 | 不要          |

| IDLE → NORMAL  | 不要          |

| STOP1 → NORMAL | 必要          |

### 1.3.4. モード遷移によるクロック動作

モード遷移の際の、クロック動作について以下に示します。

#### 1.3.4.1. NORMAL → IDLE → NORMAL 動作モード遷移

IDLE モードは、CPU が停止するモードです。周辺機能へのクロック供給は、設定状態を保持します。必要に応じて、各周辺機能のレジスター、クロック供給設定機能などにより、動作/停止を行ってください。IDLE 状態から、NORMAL モードへの復帰時にウォーミングアップは行いません。

IDLE モードへ遷移する命令(WFI)実行後、プログラムカウンターは次の行を示して CPU 停止状態となります。解除ソースにより、CPU 再起動となり、割り込み許可状態の場合、先に解除ソースの割り込み処理を経て、遷移命令(WFI)の次の行を実行することになります。

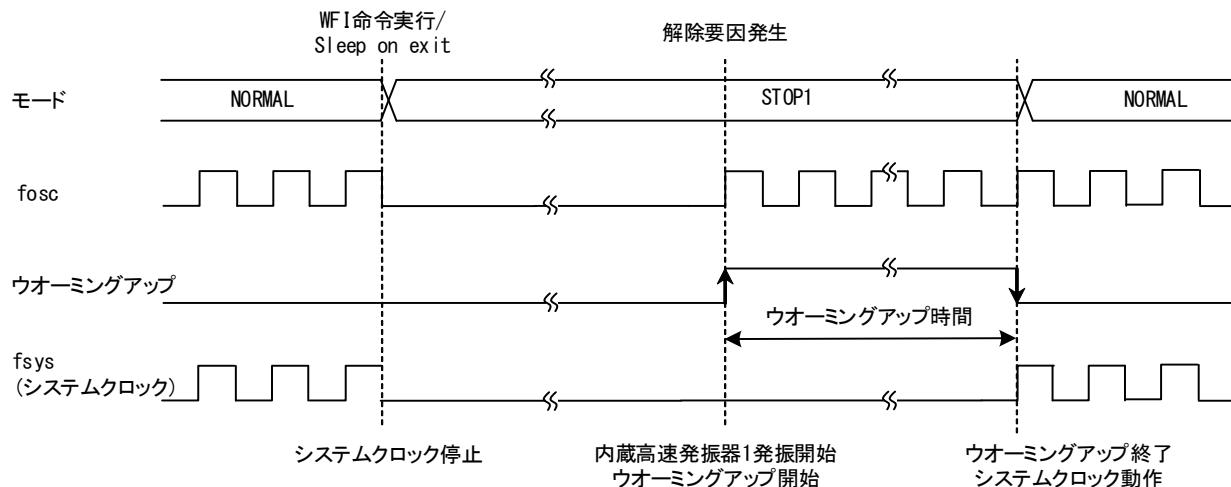

#### 1.3.4.2. NORMAL→STOP1→NORMAL 動作モード遷移

STOP1 モードから NORMAL モードへ復帰する場合、ウォーミングアップは自動的に起動します。

STOP1 モードへ遷移する前に[CGWUPHCR]<WUPT[15:4]>へウォーミングアップ時間(163.4μs 以上)の設定を行ってください。

注) RESET\_N 端子、LVD リセットが解除要因となった場合、ウォーミングアップ時間は、ウォームリセット時の動作と同じで"内部処理時間"と"CPU 動作待ち時間"に置き換わります。詳細は「3.2.2.1. RESET\_N 端子によるウォームリセット」、「3.2.2.2. LVD によるウォームリセット」を参照してください。

図 1.3 NORMAL→STOP1→NORMAL動作モード遷移

## 1.4. レジスターの説明

### 1.4.1. レジスター一覧

CG 関連のレジスターとアドレスを以下に示します。

| 周辺機能         | チャネル/ユニット | ベースアドレス |

|--------------|-----------|---------|

| クロック制御と動作モード | CG        | —       |

| レジスター名                   | アドレス(Base+) |

|--------------------------|-------------|

| CG ライトプロテクトレジスター         | [CGPROTECT] |

| 発振制御レジスター                | [CGOSCCR]   |

| システムクロック制御レジスター          | [CGSYSCR]   |

| スタンバイ制御レジスター             | [CGSTBYCR]  |

| SCOUT 出力制御レジスター          | [CGSCOCR]   |

| fsys 用 PLL セレクトレジスター     | [CGPLL0SEL] |

| 高速発振ウォーミングアップレジスター       | [CGWUPHCR]  |

| fsys 供給停止レジスターA          | [CGFSYSENA] |

| fsys 供給停止レジスターB          | [CGFSYSENB] |

| fc 供給停止レジスター             | [CGFCEN]    |

| ADC、デバッグ回路用クロック供給停止レジスター | [CGSPCLKEN] |

## 1.4.2. レジスター詳細

## 1.4.2.1. [CGPROTECT] (CG ライトプロテクトレジスター)

| Bit  | Bit symbol   | リセット後 | Type | 機能                                                                                                     |

|------|--------------|-------|------|--------------------------------------------------------------------------------------------------------|

| 31:8 | -            | 0     | R    | リードすると"0"が読めます。                                                                                        |

| 7:0  | PROTECT[7:0] | 0xC1  | R/W  | CG レジスターライトプロテクト(本レジスター以外の全て)制御<br>0xC1: CG レジスターへのライト許可(プロテクト解除)<br>0xC1 以外: CG レジスターへのライト禁止(プロテクト有効) |

## 1.4.2.2. [CGOSCCR] (発振制御レジスター)

| Bit   | Bit symbol  | リセット後 | Type | 機能                                                                                                         |

|-------|-------------|-------|------|------------------------------------------------------------------------------------------------------------|

| 31:20 | -           | 0     | R    | リードすると"0"が読めます。                                                                                            |

| 19    | IHOSC2F     | 0     | R    | IHOSC2 用内蔵発振安定フラグ<br>0: 停止またはウォーミングアップ中<br>1: 発振安定                                                         |

| 18:17 | -           | 0     | R    | リードすると"0"が読めます。                                                                                            |

| 16    | IHOSC1F     | 1     | R    | IHOSC1 用内蔵発振安定フラグ(注 4)<br>0: 停止またはウォーミングアップ中<br>1: 発振安定                                                    |

| 15:13 | -           | 0     | R    | リードすると"0"が読めます。                                                                                            |

| 12    | -           | 0     | R/W  | "0"を書いてください。                                                                                               |

| 11:10 | -           | 0     | R    | リードすると"0"が読めます。                                                                                            |

| 9     | OSCF        | 0     | R    | fosc 用高速発振器選択ステータス<br>0: 内蔵高速発振器 1 (IHOSC1)<br>1: 外部高速発振器 (EHOSC)                                          |

| 8     | OSCSEL      | 0     | R/W  | fosc 用高速発振器選択(注 1)<br>0: 内蔵高速発振器 1 (IHOSC1)<br>1: 外部高速発振器 (EHOSC)                                          |

| 7:4   | -           | 0     | R    | リードすると"0"が読めます。                                                                                            |

| 3     | IHOSC2EN    | 0     | R/W  | 内蔵高速発振器 2 (IHOSC2)(注 2)<br>0: 停止<br>1: 発振                                                                  |

| 2:1   | EOSCEN[1:0] | 00    | R/W  | 外部高速発振器の動作選択(EHOSC)(注 3)<br>00: 外部高速発振器未使用<br>01: 外部高速発振器 (EHOSC)<br>10: 外部クロック入力(EHCLKIN)<br>11: Reserved |

| 0     | IHOSC1EN    | 1     | R/W  | 内蔵高速発振器 1 (IHOSC1)<br>0: 停止<br>1: 発振                                                                       |

注 1) 設定変更した場合、書き込み値が[CGOSCCR]<OSCF>ビットに、反映されていることを確認後、次の操作を行うようにしてください。

注 2) [SIWDxOSCCR]<OSCPRO>=1 (SIWDT のライトプロテクトが有効)の場合は、設定しても変更されません。

注 3) 発振子接続で使用する場合は必ず"01" (外部高速発振器)に設定してください。

注 4) 内蔵高速発振器 1 (IHOSC1)の発振安定は、<IHOSC1F>を使わず、ウォーミングアップタイマーを設定し[CGWUPHCR]<WUEF>により確認してください。

## 1.4.2.3. [CGSYSCR] (システムクロック制御レジスター)

| Bit   | Bit symbol  | リセット後 | Type | 機能                                                                                                                                                                                                       |

|-------|-------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:28 | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                          |

| 27:24 | PRCKST[3:0] | 0000  | R    | プリスケーラークロック(ΦT0)選択ステータス<br>0000: fc 0100: fc/16 1000: fc/256<br>0001: fc/2 0101: fc/32 1001: fc/512<br>0010: fc/4 0110: fc/64 1010 ~ 1111: Reserved<br>0011: fc/8 0111: fc/128                           |

| 23:19 | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                          |

| 18:16 | GEARST[2:0] | 000   | R    | システムクロック(fsys)のギア選択ステータス<br>000: fc 100: fc/16<br>001: fc/2 101 ~ 111: Reserved<br>010: fc/4<br>011: fc/8                                                                                                |

| 15:12 | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                          |

| 11:8  | PRCK[3:0]   | 0000  | R/W  | プリスケーラークロック(ΦT0)選択<br>0000: fc 0100: fc/16 1000: fc/256<br>0001: fc/2 0101: fc/32 1001: fc/512<br>0010: fc/4 0110: fc/64 1010 ~ 1111: Reserved<br>0011: fc/8 0111: fc/128<br>周辺機能に供給するプリスケーラークロックを選択します。 |

| 7:3   | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                          |

| 2:0   | GEAR[2:0]   | 000   | R/W  | システムクロック(fsys)のギア選択<br>000: fc 100: fc/16<br>001: fc/2 101 ~ 111: Reserved<br>010: fc/4<br>011: fc/8                                                                                                     |

## 1.4.2.4. [CGSTBYCR] (スタンバイ制御レジスター)

| Bit  | Bit symbol | リセット後 | Type | 機能                                                                  |

|------|------------|-------|------|---------------------------------------------------------------------|

| 31:2 | -          | 0     | R    | リードすると"0"が読みます。                                                     |

| 1:0  | STBY[1:0]  | 00    | R/W  | 低消費電力モード選定<br>00: IDLE<br>01: STOP1<br>10: Reserved<br>11: Reserved |

## 1.4.2.5. [CGSCOCR] (SCOUT 出力制御レジスター)

| Bit  | Bit symbol  | リセット後 | Type | 機能                                                                                                     |

|------|-------------|-------|------|--------------------------------------------------------------------------------------------------------|

| 31:7 | -           | 0     | R    | リードすると"0"が読みます。                                                                                        |

| 6:4  | SCODIV[2:0] | 000   | R/W  | SCOUT 分周選択(注)<br>000: 分周なし<br>001: 2 分周<br>010: 4 分周<br>011: 8 分周<br>100: 16 分周<br>101 ~ 111: Reserved |

| 3:1  | SCOSEL[2:0] | 000   | R/W  | SCOUT ベースクロック選択(注)<br>000: fosc<br>001: fc<br>010: Reserved<br>011: fsys<br>100 ~ 111: Reserved        |

| 0    | SCOEN       | 0     | R/W  | SCOUT 出力許可<br>0: 禁止<br>1: 許可                                                                           |

注) <SCOSEL[2:0]>で「011:fsys」を選択時は、<SCODIV[2:0]>で「000:分周なし」は選択できません。

## 1.4.2.6. [CGPLL0SEL] (fsys 用 PLL セレクトレジスター)

| Bit  | Bit symbol    | リセット後    | Type | 機能                                                          |

|------|---------------|----------|------|-------------------------------------------------------------|

| 31:8 | PLL0SET[23:0] | 0x000000 | R/W  | PLL0 過倍設定<br>過倍設定については、「1.2.5.2. PLL 過倍値の計算式と設定例」を参照してください。 |

| 7:3  | -             | 0        | R    | リードすると"0"が読めます。                                             |

| 2    | PLL0ST        | 0        | R    | fsys 用 Clock 選択ステータス<br>0: fosc<br>1: f <sub>PLL</sub>      |

| 1    | PLL0SEL       | 0        | R/W  | fsys 用 Clock 選択<br>0: fosc<br>1: f <sub>PLL</sub>           |

| 0    | PLL0ON        | 0        | R/W  | fsys 用 PLL 動作<br>0: 停止<br>1: 発振                             |

## 1.4.2.7. [CGWUPHCR] (高速発振ウォーミングアップレジスター)

| Bit   | Bit symbol | リセット後 | Type | 機能                                                                                                           |

|-------|------------|-------|------|--------------------------------------------------------------------------------------------------------------|

| 31:20 | WUPT[15:4] | 0x800 | R/W  | ウォーミングアップタイマーの計算値 16 ビットの上位 12 ビットの値を設定します。<br>ウォーミングアップタイマーの設定については、「1.2.4.1. 高速発振用ウォーミングアップタイマー」を参照してください。 |

| 19:16 | WUPT[3:0]  | 0000  | R    | ウォーミングアップタイマーの計算値 16 ビットの下位 4 ビットの値で、"0000" 固定です。                                                            |

| 15:9  | -          | 0     | R    | リードすると"0"が読めます。                                                                                              |

| 8     | WUCLK      | 0     | R/W  | ウォーミングアップクロック選択(注 1)<br>0: 内蔵高速発振器 1(IHOSC1)<br>1: 外部高速発振器(EHOSC)                                            |

| 7:2   | -          | 0     | R    | リードすると"0"が読めます。                                                                                              |

| 1     | WUEF       | 0     | R    | ウォーミングアップタイマーステータス(注 2)<br>0: ウォーミングアップ終了<br>1: ウォーミングアップ中                                                   |

| 0     | WUON       | 0     | W    | ウォーミングアップタイマー制御<br>0: Don't care<br>1: ウォーミングアップスタート                                                         |

注 1) STOP1 復帰時のウォーミングアップは内蔵発振器で行ってください。外部発振器を選んで STOP1 へ遷移することは禁止です。

注 2) ウォーミングアップ中(<WUEF>=1)は、レジスターの書き換え禁止です。設定は、<WUEF>=0 のときに行ってください。

## 1.4.2.8. [CGFSYSENA] (fsys 供給停止レジスターA)

| Bit | Bit symbol | リセット後 | Type | 機能                                                 |

|-----|------------|-------|------|----------------------------------------------------|

| 31  | IPENA31    | 0     | R    | リードすると"0"が読みます。                                    |

| 30  | IPENA30    | 0     | R/W  | T32A ch5 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 29  | IPENA29    | 0     | R/W  | T32A ch4 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 28  | IPENA28    | 0     | R/W  | T32A ch3 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 27  | IPENA27    | 0     | R/W  | T32A ch2 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 26  | IPENA26    | 0     | R/W  | T32A ch1 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 25  | IPENA25    | 0     | R/W  | T32A ch0 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 24  | IPENA24    | 0     | R/W  | I2C ch0 のクロックイネーブル (注 3)<br>0: クロック停止<br>1: クロック供給 |

| 23  | IPENA23    | 0     | R/W  | UART ch3 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 22  | IPENA22    | 0     | R/W  | UART ch2 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 21  | IPENA21    | 0     | R/W  | UART ch1 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 20  | IPENA20    | 0     | R/W  | UART ch0 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 19  | IPENA19    | 0     | R/W  | TSPI ch3 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 18  | IPENA18    | 0     | R/W  | TSPI ch2 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 17  | IPENA17    | 0     | R/W  | TSPI ch1 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 16  | IPENA16    | 0     | R/W  | TSPI ch0 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 15  | IPENA15    | 0     | R    | リードすると"0"が読みます。                                    |

| 14  | IPENA14    | 0     | R    |                                                    |

| 13  | IPENA13    | 0     | R    |                                                    |

| 12  | IPENA12    | 0     | R    |                                                    |

| 11  | IPENA11    | 0     | R    |                                                    |

| 10  | IPENA10    | 0     | R/W  | PORT L のクロックイネーブル<br>0: クロック停止<br>1: クロック供給        |

| Bit | Bit symbol | リセット後 | Type | 機能                                          |

|-----|------------|-------|------|---------------------------------------------|

| 9   | IPENA09    | 0     | R/W  | PORT K のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

| 8   | IPENA08    | 0     | R/W  | PORT J のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

| 7   | IPENA07    | 0     | R/W  | PORT H のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

| 6   | IPENA06    | 0     | R/W  | PORT G のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

| 5   | IPENA05    | 0     | R/W  | PORT F のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

| 4   | IPENA04    | 0     | R/W  | PORT E のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

| 3   | IPENA03    | 0     | R/W  | PORT D のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

| 2   | IPENA02    | 0     | R/W  | PORT C のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

| 1   | IPENA01    | 0     | R/W  | PORT B のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

| 0   | IPENA00    | 0     | R/W  | PORT A のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

注 1) レジスターの初期値がクロック停止でも、リセット期間中は全てクロック供給されています。

注 2) TMPM4K2、TMPM4K1 で存在しない機能のビットは"0"をライトしてください。詳細は「1.5. 製品別情報」を参照してください。

注 3) I2C と EI2C は排他的に使ってください。

## 1.4.2.9. [CGFSYSENB] (fsys 供給停止レジスターB)

| Bit | Bit symbol | リセット後 | Type | 機能                                                  |

|-----|------------|-------|------|-----------------------------------------------------|

| 31  | IPENB31    | 1     | R/W  | SIWDT ch0 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 30  | IPENB30    | 1     | R/W  | NBDIF のクロックイネーブル<br>0: クロック停止<br>1: クロック供給          |

| 29  | IPENB29    | 0     | R    | リードすると"0"が読めます。                                     |

| 28  | IPENB28    | 1     | R/W  | "1"を書いてください。                                        |

| 27  | IPENB27    | 0     | R    | リードすると"0"が読めます。                                     |

| 26  | IPENB26    | 0     | R    |                                                     |

| 25  | IPENB25    | 0     | R    |                                                     |

| 24  | IPENB24    | 0     | R/W  | EI2C ch0 のクロックイネーブル (注 3)<br>0: クロック停止<br>1: クロック供給 |

| 23  | IPENB23    | 0     | R    | リードすると"0"が読めます。                                     |

| 22  | IPENB22    | 0     | R    |                                                     |

| 21  | IPENB21    | 0     | R    |                                                     |

| 20  | IPENB20    | 0     | R    |                                                     |

| 19  | IPENB19    | 0     | R    |                                                     |

| 18  | IPENB18    | 0     | R    |                                                     |

| 17  | IPENB17    | 0     | R    |                                                     |

| 16  | IPENB16    | 0     | R/W  | DMAC のクロックイネーブル<br>0: クロック停止<br>1: クロック供給           |

| 15  | IPENB15    | 0     | R/W  | TRGSEL のクロックイネーブル<br>0: クロック停止<br>1: クロック供給         |

| 14  | IPENB14    | 0     | R/W  | TRM のクロックイネーブル<br>0: クロック停止<br>1: クロック供給            |

| 13  | IPENB13    | 0     | R/W  | OFD のクロックイネーブル<br>0: クロック停止<br>1: クロック供給            |

| 12  | IPENB12    | 0     | R/W  | CRC のクロックイネーブル<br>0: クロック停止<br>1: クロック供給            |

| 11  | IPENB11    | 0     | R/W  | RAM Parity のクロックイネーブル<br>0: クロック停止<br>1: クロック供給     |

| 10  | IPENB10    | 0     | R    | リードすると"0"が読めます。                                     |

| 9   | IPENB09    | 0     | R/W  | A-PMD ch1 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 8   | IPENB08    | 0     | R/W  | A-PMD ch0 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 7   | IPENB07    | 0     | R/W  | A-ENC32 ch0 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給    |

| 6   | IPENB06    | 0     | R/W  | A-ENC32 ch1 のクロックイネーブル<br>0: クロック停止<br>1: クロック供給    |

| 5   | IPENB05    | 0     | R    | リードすると"0"が読めます。                                     |

| Bit | Bit symbol | リセット後 | Type | 機能                                              |

|-----|------------|-------|------|-------------------------------------------------|

| 4   | IPENB04    | 0     | R    |                                                 |

| 3   | IPENB03    | 0     | R/W  | ADCCMP のクロックイネーブル<br>0: クロック停止<br>1: クロック供給     |

| 2   | IPENB02    | 0     | R/W  | OPAMP のクロックイネーブル<br>0: クロック停止<br>1: クロック供給      |

| 1   | IPENB01    | 0     | R/W  | ADC unit B のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

| 0   | IPENB00    | 0     | R/W  | ADC unit A のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

注 1) レジスターの初期値がクロック停止でも、リセット期間中は全てクロック供給されています。

注 2) TMPM4K2、TMPM4K1 で存在しない機能のビットは"0"をライトしてください。詳細は「1.5. 製品別情報」を参照してください。

注 3) I2C と EI2C は排他的に使ってください。

#### 1.4.2.10. [CGFCEN] (fc 供給停止レジスター)

| Bit  | Bit symbol | リセット後 | Type | 機能                                       |

|------|------------|-------|------|------------------------------------------|

| 31:8 | -          | 0     | R    | リードすると"0"が読めます。                          |

| 7    | DNFCKEN    | 0     | R/W  | DNF のクロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

| 6:0  | -          | 0     | R    | リードすると"0"が読めます。                          |

注) レジスターの初期値がクロック停止でも、リセット期間中は全てクロック供給されています。

## 1.4.2.11. [CGSPCLKEN] (ADC、デバッグ回路用クロック供給停止レジスター)

| Bit   | Bit symbol | リセット後 | Type | 機能                                                             |

|-------|------------|-------|------|----------------------------------------------------------------|

| 31:18 | -          | 0     | R    | リードすると"0"が読めます。                                                |

| 17    | ADCKEN1    | 0     | R/W  | ADC unit B 用変換クロックイネーブル(注 2)<br>0: クロック停止<br>1: クロック供給         |

| 16    | ADCKEN0    | 0     | R/W  | ADC unit A 用変換クロックイネーブル(注 2)<br>0: クロック停止<br>1: クロック供給         |

| 15:1  | -          | 0     | R    | リードすると"0"が読めます。                                                |

| 0     | TRCKEN     | 0     | R/W  | デバッグ回路(トレースまたは SWV)のトレース機能用クロックイネーブル<br>0: クロック停止<br>1: クロック供給 |

注 1) レジスターの初期値がクロック停止でも、リセット期間中は全てクロック供給されています。

注 2) "0"(クロック停止)に設定する場合は、必ず AD 変換が停止または終了していることを確認してください。

注 3) AD 変換結果比較回路(ADCCMP)を使用する場合、変換クロックイネーブル

([CGSPCLKEN]<ADCKEN0><ADCKEN1>)を同時に"1"に設定してください。

## 1.5. 製品別情報

各製品別で異なる[CGFSYSENA]および[CGFSYSENB]に関する情報を以下に示します。

### 1.5.1. [CGFSYSENA]

表 1.10 [CGFSYSENA]の製品別割り当て

| Bit | Bit symbol | 接続先  | チャネル番号<br>/ユニット名<br>入出力ポート名 | M4K4 | M4K2 | M4K1 |

|-----|------------|------|-----------------------------|------|------|------|

| 31  | IPENA31    | -    | -                           | -    | -    | -    |

| 30  | IPENA30    | T32A | 5                           | ○    | ○    | ○    |

| 29  | IPENA29    |      | 4                           | ○    | ○    | ○    |

| 28  | IPENA28    |      | 3                           | ○    | ○    | ○    |

| 27  | IPENA27    |      | 2                           | ○    | ○    | ○    |

| 26  | IPENA26    |      | 1                           | ○    | ○    | ○    |

| 25  | IPENA25    |      | 0                           | ○    | ○    | ○    |

| 24  | IPENA24    | I2C  | 0                           | ○    | ○    | ○    |

| 23  | IPENA23    | UART | 3                           | ○    | -    | -    |

| 22  | IPENA22    |      | 2                           | ○    | ○    | ○    |

| 21  | IPENA21    |      | 1                           | ○    | ○    | ○    |

| 20  | IPENA20    |      | 0                           | ○    | ○    | ○    |

| 19  | IPENA19    | TSPI | 3                           | ○    | -    | -    |

| 18  | IPENA18    |      | 2                           | ○    | ○    | ○    |

| 17  | IPENA17    |      | 1                           | ○    | -    | -    |

| 16  | IPENA16    |      | 0                           | ○    | ○    | ○    |

| 15  | IPENA15    | -    | -                           | -    | -    | -    |

| 14  | IPENA14    | -    | -                           | -    | -    | -    |

| 13  | IPENA13    | -    | -                           | -    | -    | -    |

| 12  | IPENA12    | -    | -                           | -    | -    | -    |

| 11  | IPENA11    | -    | -                           | -    | -    | -    |

| 10  | IPENA10    | PORT | L                           | ○    | ○    | -    |

| 9   | IPENA09    |      | K                           | ○    | ○    | ○    |

| 8   | IPENA08    |      | J                           | ○    | ○    | ○    |

| 7   | IPENA07    |      | H                           | ○    | ○    | ○    |

| 6   | IPENA06    |      | G                           | ○    | ○    | ○    |

| 5   | IPENA05    |      | F                           | ○    | ○    | ○    |

| 4   | IPENA04    |      | E                           | ○    | ○    | ○    |

| 3   | IPENA03    |      | D                           | ○    | ○    | ○    |

| 2   | IPENA02    |      | C                           | ○    | ○    | ○    |

| 1   | IPENA01    |      | B                           | ○    | ○    | ○    |

| 0   | IPENA00    |      | A                           | ○    | ○    | ○    |

注) ○: 対応、-: 非対応

## 1.5.2. [CGFSYSENB]

表 1.11 [CGFSYSENB]の製品別割り当て

| Bit | Bit symbol | 接続先     | チャネル番号<br>/ユニット名<br>入出力ポート名 | M4K4 | M4K2 | M4K1 |

|-----|------------|---------|-----------------------------|------|------|------|

| 31  | IPENB31    | SIWDT   | 0                           | ○    | ○    | ○    |

| 30  | IPENB30    | NBDIF   | -                           | ○    | -    | -    |

| 29  | IPENB29    | - (注 2) | -                           | -    | -    | -    |

| 28  | IPENB28    | - (注 2) | -                           | -    | -    | -    |

| 27  | IPENB27    | -       | -                           | -    | -    | -    |

| 26  | IPENB26    | -       | -                           | -    | -    | -    |

| 25  | IPENB25    | -       | -                           | -    | -    | -    |

| 24  | IPENB24    | EI2C    | 0                           | ○    | ○    | ○    |