32 ビット RISC マイクロコントローラー<sup>TM</sup>

**TXZ+ファミリー**

**TMPM4K グループ(1)**

リファレンスマニュアル

入出力ポート

**(PORT-M4K(1))**

**Revision 1.1**

**2025-09**

東芝デバイス&ストレージ株式会社

## 目次

|                                            |    |

|--------------------------------------------|----|

| 序章 .....                                   | 4  |

| 関連するドキュメント .....                           | 4  |

| 表記規約 .....                                 | 5  |

| 用語・略語 .....                                | 7  |

| 1. 概要 .....                                | 8  |

| 2. 動作説明 .....                              | 8  |

| 2.1. クロック供給 .....                          | 8  |

| 3. 信号接続一覧 .....                            | 9  |

| 4. レジスター説明 .....                           | 14 |

| 4.1. レジスター一覧 .....                         | 15 |

| 4.2. ポート機能レジスター設定一覧 .....                  | 17 |

| 4.2.1. 機能端子を使用する際の設定について .....             | 17 |

| 4.2.2. PORT A .....                        | 18 |

| 4.2.3. PORT B .....                        | 19 |

| 4.2.4. PORT C .....                        | 20 |

| 4.2.5. PORT D .....                        | 21 |

| 4.2.6. PORT E .....                        | 22 |

| 4.2.7. PORT F .....                        | 23 |

| 4.2.8. PORT G .....                        | 24 |

| 4.2.9. PORT H .....                        | 25 |

| 4.2.10. PORT J .....                       | 26 |

| 4.2.11. PORT K .....                       | 27 |

| 4.2.12. PORT L .....                       | 28 |

| 5. ポート回路図 .....                            | 29 |

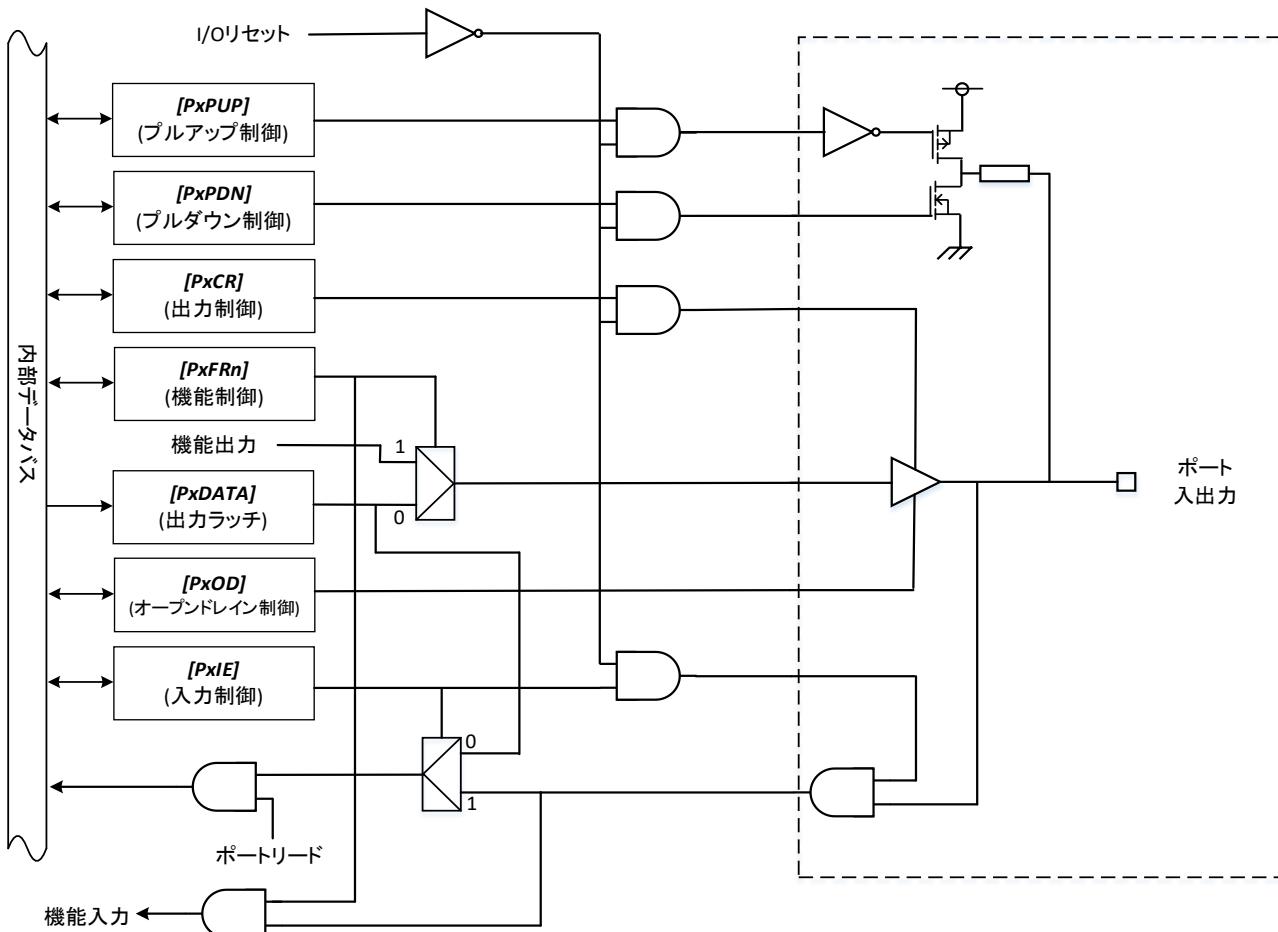

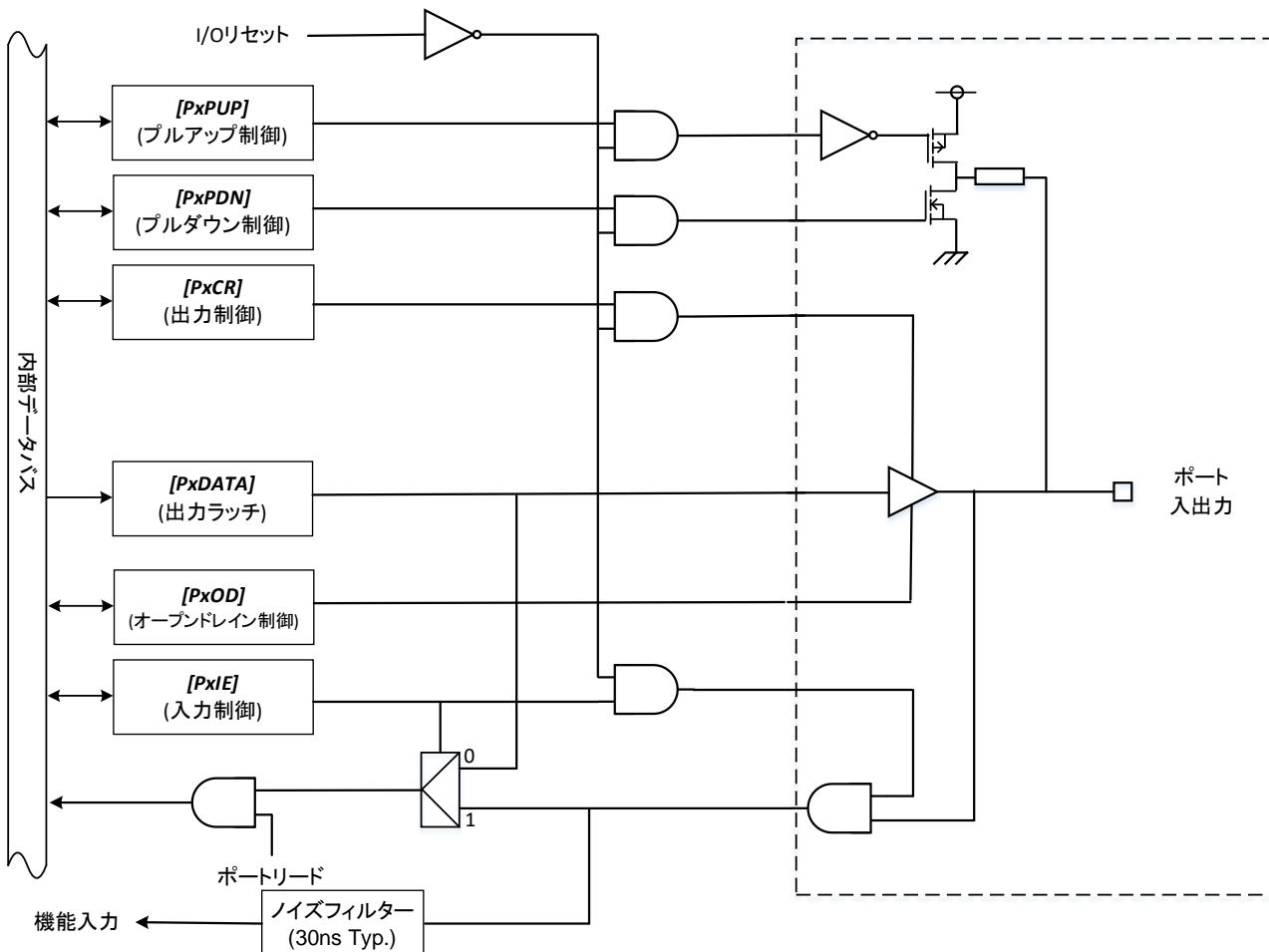

| 5.1. タイプ FTU1a .....                       | 30 |

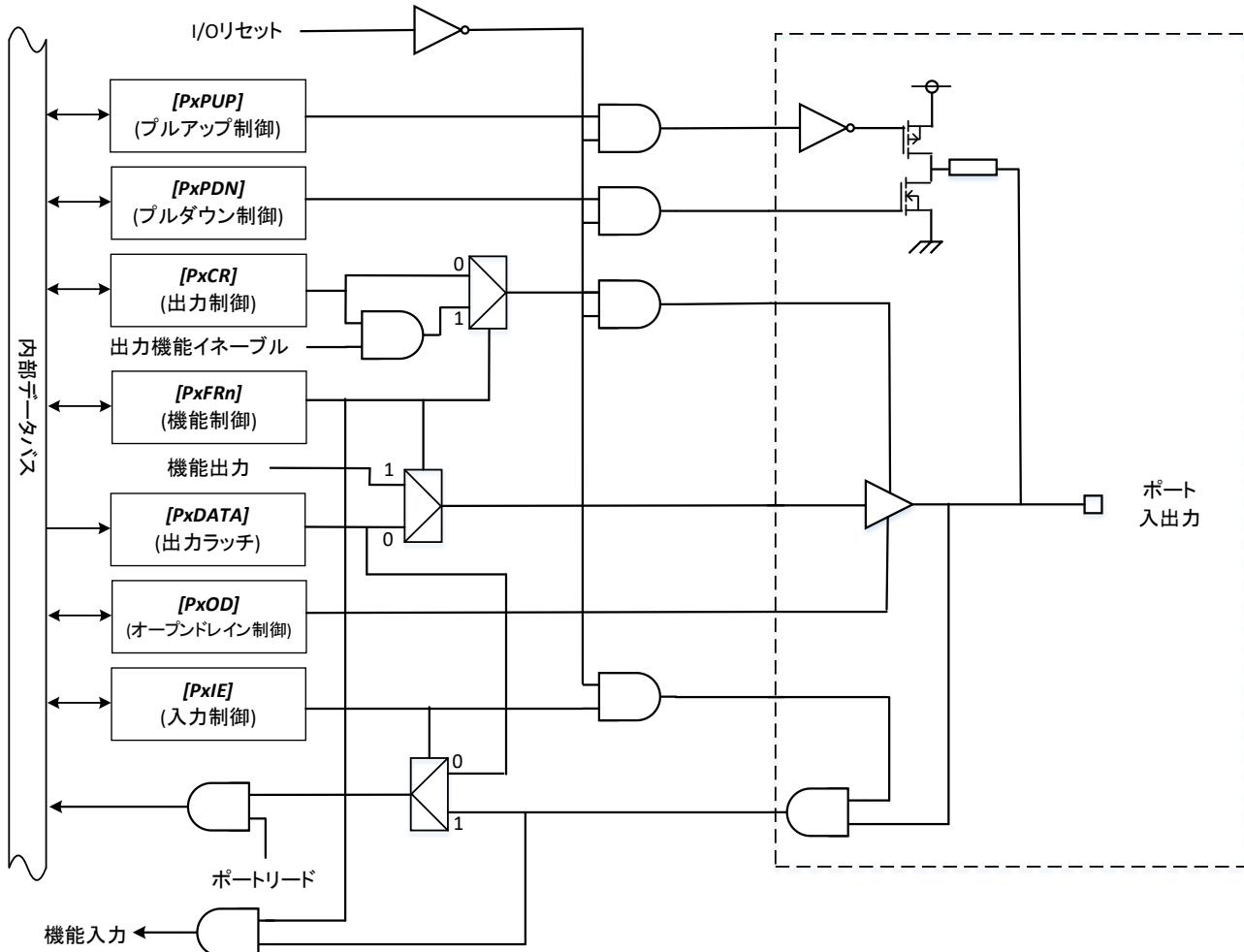

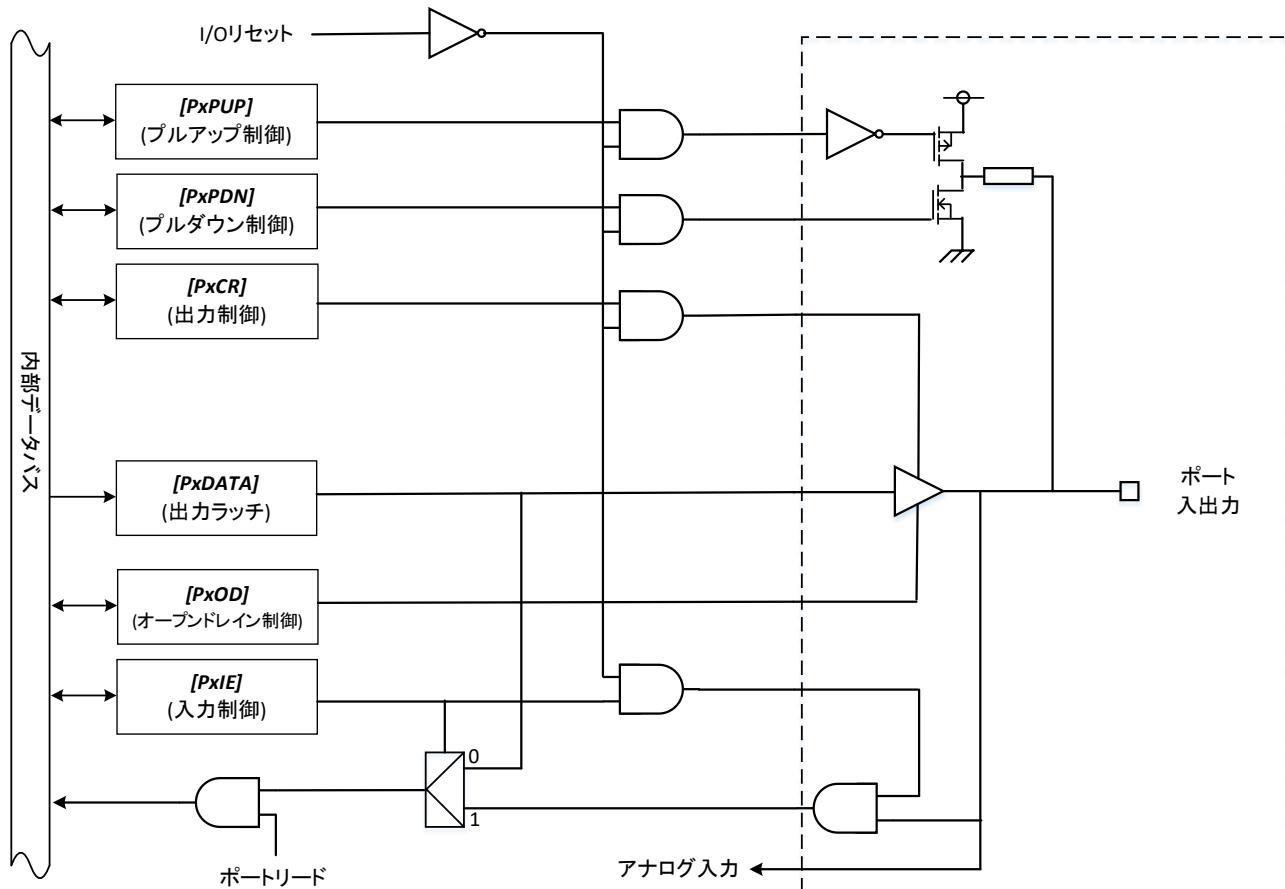

| 5.2. タイプ FTU2a .....                       | 31 |

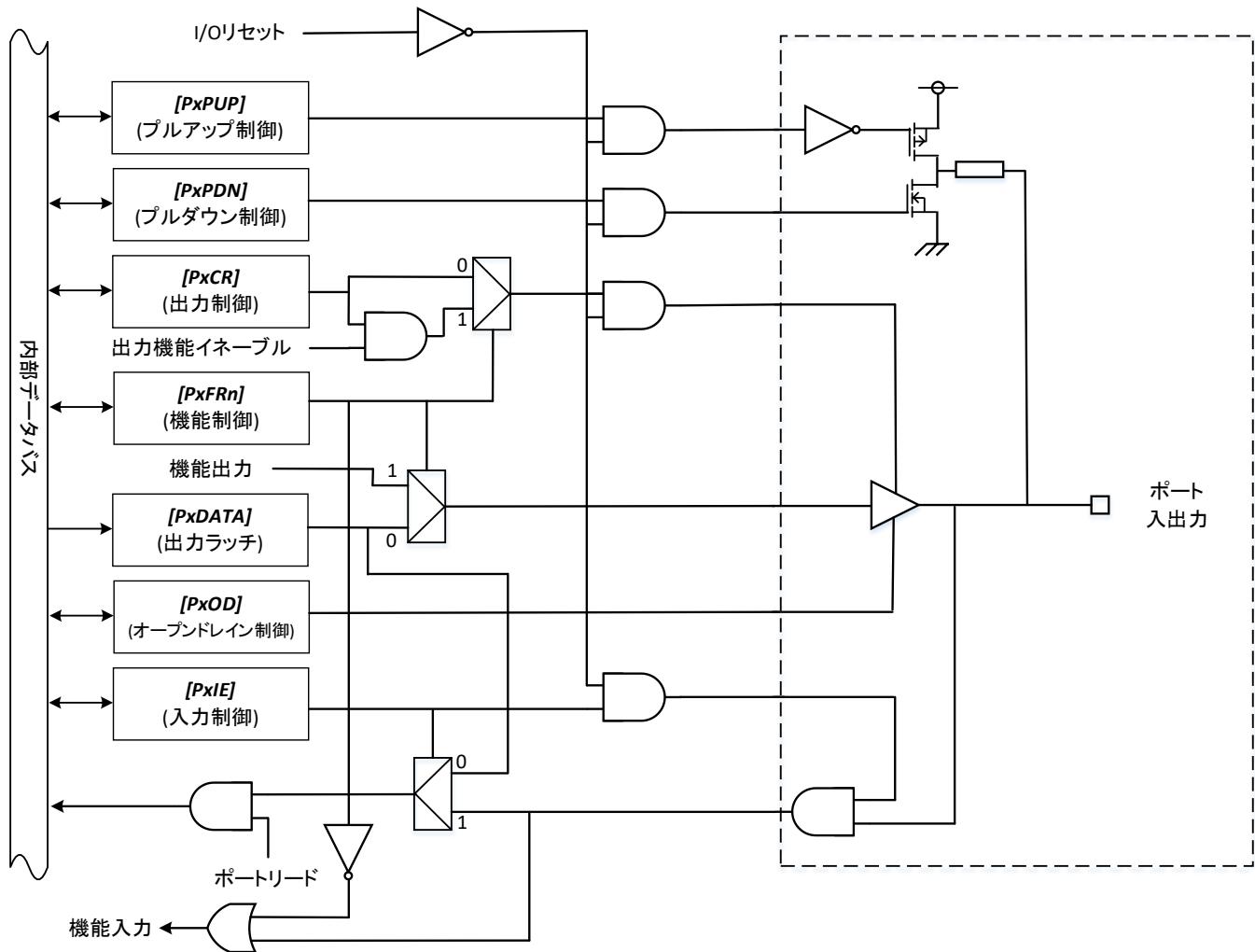

| 5.3. タイプ FTU2c .....                       | 32 |

| 5.4. タイプ FTU3a .....                       | 33 |

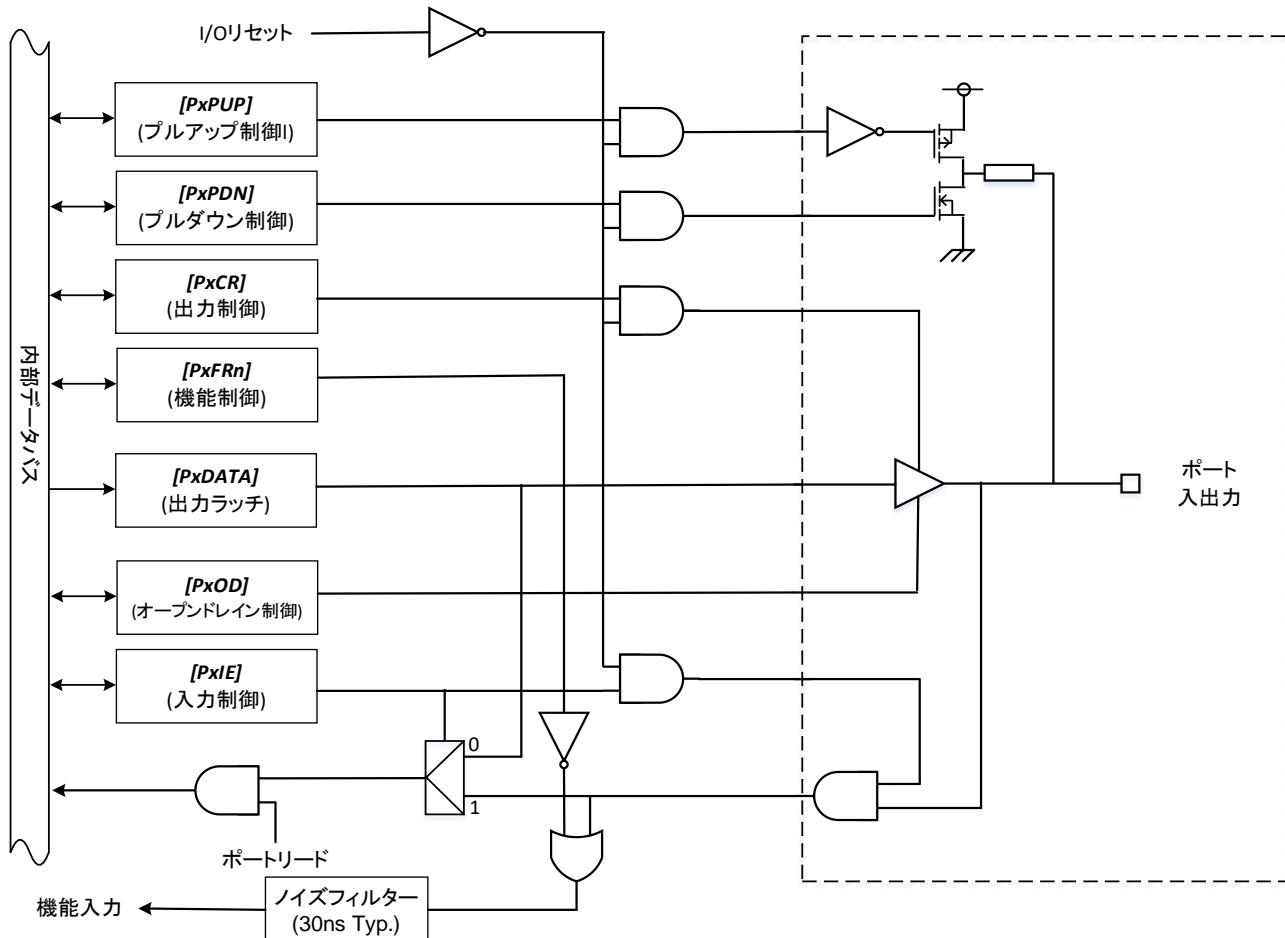

| 5.5. タイプ FTU4a .....                       | 34 |

| 5.6. タイプ FTU5a .....                       | 35 |

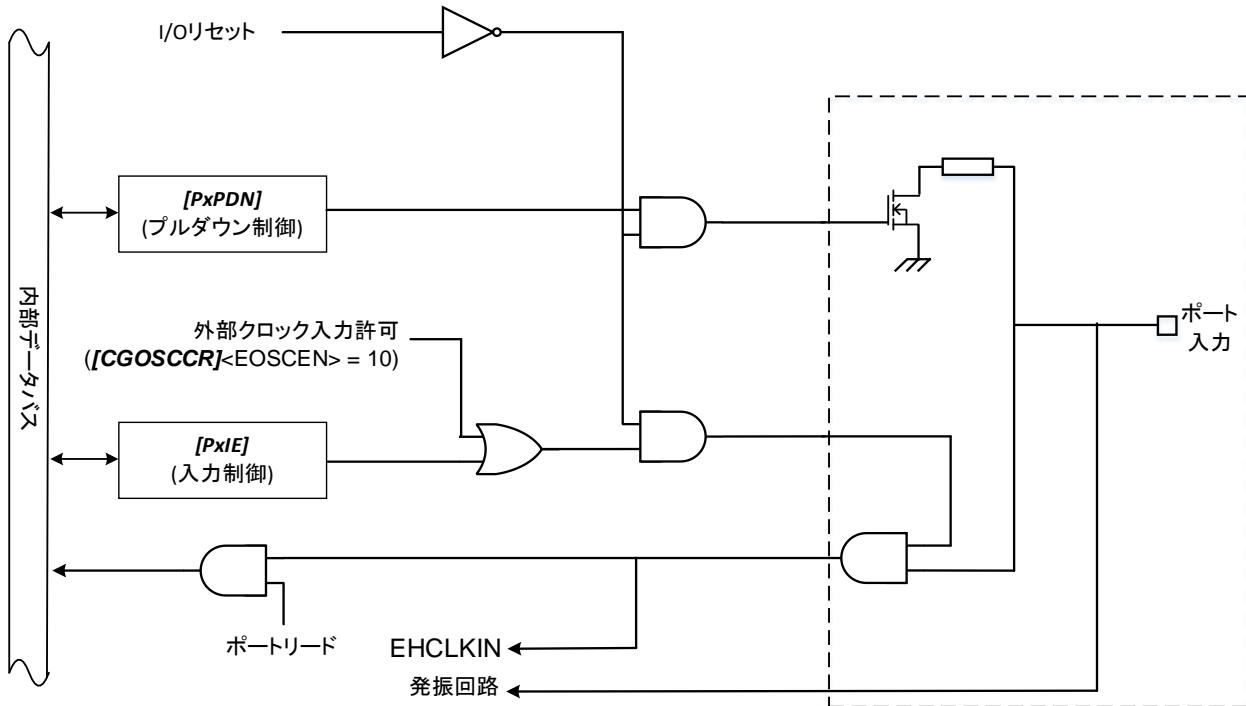

| 5.7. タイプ FTU11a .....                      | 36 |

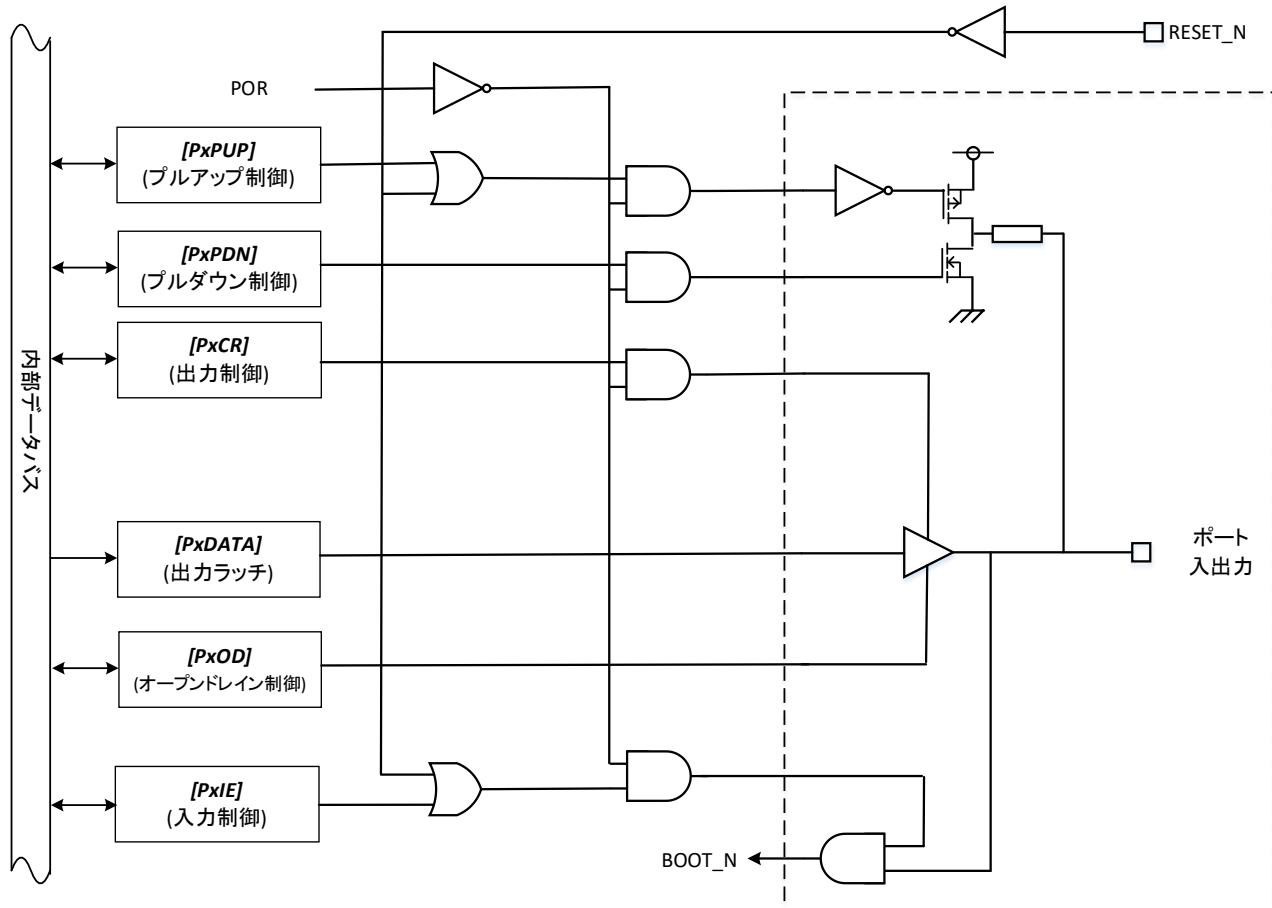

| 5.8. タイプ FTU16a .....                      | 37 |

| 6. 使用上のご注意およびお願い事項 .....                   | 38 |

| 6.1. リセット期間中の端子状態について .....                | 38 |

| 6.2. 未使用端子の処理について .....                    | 38 |

| 6.3. デバッグインターフェース端子を汎用ポートとして使用する際の注意 ..... | 38 |

| 7. 改訂履歴 .....                              | 39 |

---

|                  |    |

|------------------|----|

| 製品取り扱い上のお願い..... | 40 |

|------------------|----|

## 図目次

|                           |    |

|---------------------------|----|

| 図 5.1 ポートタイプ FTU1a .....  | 30 |

| 図 5.2 ポートタイプ FTU2a .....  | 31 |

| 図 5.3 ポートタイプ FTU2c .....  | 32 |

| 図 5.4 ポートタイプ FTU3a .....  | 33 |

| 図 5.5 ポートタイプ FTU4a .....  | 34 |

| 図 5.6 ポートタイプ FTU5a .....  | 35 |

| 図 5.7 ポートタイプ FTU11a ..... | 36 |

| 図 5.8 ポートタイプ FTU16a ..... | 37 |

## 表目次

|                              |    |

|------------------------------|----|

| 表 3.1 信号接続一覧(1/5) .....      | 9  |

| 表 3.2 信号接続一覧(2/5) .....      | 10 |

| 表 3.3 信号接続一覧(3/5) .....      | 11 |

| 表 3.4 信号接続一覧(4/5) .....      | 12 |

| 表 3.5 信号接続一覧(5/5) .....      | 13 |

| 表 4.1 ポートレジスターのベースアドレス ..... | 15 |

| 表 4.2 レジスター一覧 .....          | 16 |

| 表 4.3 ポート A レジスター設定 .....    | 18 |

| 表 4.4 ポート B レジスター設定 .....    | 19 |

| 表 4.5 ポート C レジスター設定 .....    | 20 |

| 表 4.6 ポート D レジスター設定 .....    | 21 |

| 表 4.7 ポート E レジスター設定 .....    | 22 |

| 表 4.8 ポート F レジスター設定 .....    | 23 |

| 表 4.9 ポート G レジスター設定 .....    | 24 |

| 表 4.10 ポート H レジスター設定 .....   | 25 |

| 表 4.11 ポート J レジスター設定 .....   | 26 |

| 表 4.12 ポート K レジスター設定 .....   | 27 |

| 表 4.13 ポート L レジスター設定 .....   | 28 |

| 表 7.1 改訂履歴 .....             | 39 |

## 序章

### 関連するドキュメント

| 文書名                              |

|----------------------------------|

| 製品個別情報                           |

| クロック制御と動作モード                     |

| 例外                               |

| フラッシュメモリー                        |

| I <sup>2</sup> C インターフェース        |

| I <sup>2</sup> C インターフェースバージョン A |

| シリアルペリフェラルインターフェース               |

| 12 ビットアナログデジタルコンバーター             |

| 32 ビットタイマーイベントカウンター              |

| 非同期シリアル通信回路                      |

| アドバンストプログラマブルモーター制御回路            |

| アドバンストエンコーダー入力回路(32-bit)         |

| デバッグインターフェース                     |

| ノンブレークデバッグインターフェース               |

## 表記規約

- 数値表記は以下の規則に従います。

- 16進数表記: 0xABCD

- 10進数表記: 123 または 0d123 (10進表記であることを示す必要のある場合だけ使用)

- 2進数表記: 0b111 (ビット数が本文中に明記されている場合は「0b」を省略可)

- ローアクティブの信号は信号名の末尾に「\_N」で表記します。

- 信号がアクティブレベルに移ることを「アサート (assert)」アクティブでないレベルに移ることを「デアサート (deassert)」と呼びます。

- 複数の信号名は[m:n]とまとめて表記する場合があります。

例: S[3: 0]はS3、S2、S1、S0の4つの信号名をまとめて表記しています。

- 本文中[]で囲まれたものはレジスターを定義しています。

例: [ABCD]

- 同種で複数のレジスター、フィールド、ビット名は「n」で一括表記する場合があります。

例: [XYZ1], [XYZ2], [XYZ3] → [XYZn]

- 「レジスター一覧」中のレジスターナンバーでユニットまたはチャネルは「x」で一括表記しています。

ユニットの場合、「x」はA、B、C、...を表します。

例: [ADACR0], [ADBCR0], [ADCCR0] → [ADxCR0]

チャネルの場合、「x」は0、1、2、..を表します。

例: [T32A0RUNA], [T32A1RUNA], [T32A2RUNA] → [T32AxRUNA]

- レジスターのビット範囲は [m:n] と表記します。

例: [3: 0]はビット3から0の範囲を表します。

- レジスターの設定値は16進数または2進数のどちらかで表記されています。

例: [ABCD]<EFG> = 0x01 (16進数), [XYZn]<VW> = 1 (2進数)

- ワード、バイトは以下のビット長を表します。

- バイト: 8ビット

- ハーフワード: 16ビット

- ワード: 32ビット

- ダブルワード: 64ビット

- レジスター内の各ビットの属性は以下の表記を使用しています。

- R: リードオンリー

- W: ライトオンリー

- R/W: リード/ライト

- 断りのない限り、レジスターアクセスはワードアクセスだけをサポートします。

- 本文中の予約領域「Reserved」として定義されたレジスターは書き換えを行わないでください。

また、読み出した値を使用しないでください。

- Default 値が「-」となっているビットから読み出した値は不定です。

- 書き込み可能なビットフィールドと、リードオンリー「R」のビットフィールドが共存するレジスターに書き込みを行う場合、リードオンリー「R」のビットフィールドにはDefault 値を書き込んでください。

Default 値が「-」となっている場合は、個々のレジスターの定義に従ってください。

- ライトオンリーのレジスターの Reserved ビットフィールドには Default 値を書き込んでください。

Default 値が「-」となっている場合は、個々のレジスターの定義に従ってください。

- 書き込みと読み出しで異なる定義のレジスターへのリードモディファイライト処理は行わないでください

---

資料に記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。

**用語・略語**

この仕様書で使用されている用語・略語の一部を記載します。

|       |                                      |

|-------|--------------------------------------|

| EI2C  | I <sup>2</sup> C Interface Version A |

| I2C   | Inter-Integrated Circuit             |

| JTAG  | Joint Test Action Group              |

| NBDIF | Non-break Debug Interface            |

| SW    | Serial Wire                          |

## 1. 概要

ポート関連のレジスターとその設定について説明します。以下に機能の一覧を示します。

| 機能分類   | 機能                        | 説明                                                            |

|--------|---------------------------|---------------------------------------------------------------|

| ポート    | -                         | 内蔵プログラマブルアップ/ダウンの選択、オープンドレイン出力選択が可能                           |

| 周辺機能端子 | クロック出力                    | システムクロックの出力が可能                                                |

|        | 外部割り込み                    | ノイズフィルター(フィルターフレーム typ. 30ns)付き割り込み入力端子                       |

|        | 32ビットタイマーイベントカウンター        | インプットキャプチャ入力端子、タイマー出力端子                                       |

|        | シリアルペリフェラルインターフェース        | データ入力端子、データ出力端子、クロック入出力端子                                     |

|        | 非同期シリアル通信回路               | データ入力端子、データ出力端子、ハンドシェーク機能端子                                   |

|        | I <sup>2</sup> C インターフェース | データ入出力端子、クロック入出力端子                                            |

|        | アナログデジタルコンバーター            | アナログ入力端子                                                      |

|        | アドバンストプログラマブルモーター制御回路     | X/Y/Z 相出力端子、U/V/W 相出力端子、異常検出入力端子、過電圧検出入力端子                    |

|        | アドバンストエンコーダー入力回路(32-bit)  | エンコーダー入力端子                                                    |

|        | トリガーセレクター                 | 外部トリガー入力端子                                                    |

| デバッグ端子 | JTAG                      | テストモード選択入力端子、シリアルクロック入力端子、シリアルデータ出力端子、シリアルデータ入力端子、テストリセット入力端子 |

|        | SW                        | シリアルワイヤデータ入出力端子、シリアルワイヤクロック入力端子、シリアルワイヤビューワ出力端子               |

|        | トレース                      | トレースクロック出力端子、トレースデータ出力端子 4 本                                  |

|        | NBDIF                     | NBD 同期入力端子、NBD クロック入力端子、NBD データ入出力端子 4 本                      |

| 制御端子   | 高速発振回路                    | 高速発振子接続端子/外部クロック入力端子                                          |

|        | BOOT モード制御                | BOOT モード制御用端子                                                 |

## 2. 動作説明

### 2.1. クロック供給

ポートを使用する場合は、fsys 供給停止レジスター A または B (*[CGFSYSENA]*, *[CGFSYSENB]*)、fc 供給停止レジスター (*[CGFCEN]*) で該当するクロックイネーブルビットを "1"(クロック供給)に設定してください。該当レジスター、ビット位置は製品によって異なります。そのため製品によって、レジスターが存在しない場合があります。詳細はリファレンスマニュアルの「クロック制御と動作モード」を参照してください。

### 3. 信号接続一覧

各リファレンスマニュアルのブロック図(信号一覧表)に記載された信号名を機能端子順に変換した表です。周辺機能のレジスター設定はポート順に説明していますので、ポート名の逆引きにご使用ください。

数値は端子番号を表します。

表 3.1 信号接続一覧(1/5)

| 参照リファレンスマニュアル                                                  | 兼用機能端子名                           | ポート名 | M4K4<br>(LQFP64) | M4K2<br>(LQFP48) | M4K1<br>(LQFP44) |

|----------------------------------------------------------------|-----------------------------------|------|------------------|------------------|------------------|

| 非同期シリアル通信回路                                                    | UT0RXD                            | PK0  | 63               | 48               | 43               |

|                                                                |                                   | PK1  | 64               | 1                | 44               |

|                                                                |                                   | PK2  | 1                | 2                | 1                |

|                                                                |                                   | PK3  | 2                | 3                | 2                |

|                                                                | UT0TXDA                           | PK1  | 64               | 1                | 44               |

|                                                                |                                   | PK0  | 63               | 48               | 43               |

|                                                                |                                   | PK3  | 2                | 3                | 2                |

|                                                                |                                   | PK2  | 1                | 2                | 1                |

|                                                                | UT1RXD                            | PA1  | 18               | 13               | -                |

|                                                                |                                   | PA0  | 19               | 14               | -                |

|                                                                |                                   | PB0  | 31               | 23               | 22               |

|                                                                |                                   | PB1  | 32               | 24               | 23               |

|                                                                | UT1TXDA                           | PA0  | 19               | 14               | -                |

|                                                                |                                   | PA1  | 18               | 13               | -                |

|                                                                |                                   | PB1  | 32               | 24               | 23               |

|                                                                |                                   | PB0  | 31               | 23               | 22               |

| I <sup>2</sup> C インターフェース/<br>I <sup>2</sup> C インターフェースバージョン A | UT2RXD                            | PG1  | 57               | 42               | 40               |

|                                                                | UT2TXDA                           | PG0  | 56               | 41               | 39               |

|                                                                | UT3RXD                            | PC1  | 34               | -                | -                |

|                                                                |                                   | PC0  | 35               |                  |                  |

|                                                                | UT3TXDA                           | PC0  | 35               | -                | -                |

|                                                                |                                   | PC1  | 34               |                  |                  |

|                                                                | I <sup>2</sup> C0SDA/<br>EI2C0SDA | PB0  | 31               | 23               | 22               |

|                                                                | I <sup>2</sup> C0SCL/<br>EI2C0SCL | PB1  | 32               | 24               | 23               |

| シリアルペリフェラル<br>インターフェース                                         | TSPI0RXD                          | PK2  | 1                | 2                | 1                |

|                                                                | TSPI0TXD                          | PK3  | 2                | 3                | 2                |

|                                                                | TSPI0SCK                          | PK4  | 3                | 4                | 3                |

|                                                                | TSPI1RXD                          | PA1  | 18               | -                | -                |

|                                                                | TSPI1TXD                          | PA0  | 19               |                  |                  |

|                                                                | TSPI1SCK                          | PA2  | 20               |                  |                  |

|                                                                | TSPI2RXD                          | PG1  | 57               | 42               | 40               |

|                                                                | TSPI2TXD                          | PG0  | 56               | 41               | 39               |

|                                                                | TSPI2SCK                          | PG2  | 58               | 43               | 41               |

|                                                                | TSPI3RXD                          | PC1  | 34               | -                | -                |

|                                                                | TSPI3TXD                          | PC0  | 35               |                  |                  |

|                                                                | TSPI3SCK                          | PC2  | 33               |                  |                  |

表 3.2 信号接続一覧(2/5)

| 参照リファレンスマニュアル       | 兼用機能端子名    | ポート名 | M4K4<br>(LQFP64) | M4K2<br>(LQFP48) | M4K1<br>(LQFP44) |

|---------------------|------------|------|------------------|------------------|------------------|

| 32 ビットタイマーイベントカウンター | T32A00INA0 | PK1  | 64               | 1                | 44               |

|                     | T32A00OUTA | PK0  | 63               | 48               | 43               |

|                     | T32A00INC0 | PK1  | 64               | 1                | 44               |

|                     | T32A00UTC  | PK0  | 63               | 48               | 43               |

|                     | T32A01INA0 | PA1  | 18               | 13               | -                |

|                     | T32A01INA1 | PA2  | 20               | -                | -                |

|                     | T32A01OUTA | PA2  | 20               | -                | -                |

|                     | T32A01INB0 | PA0  | 19               | 14               | 13               |

|                     | T32A01OUTB | PA0  | 19               | 14               | 13               |

|                     | T32A01INC0 | PA1  | 18               | 13               | -                |

|                     | T32A01INC1 | PA2  | 20               | -                | -                |

|                     | T32A01UTC  | PA2  | 20               | -                | -                |

|                     | T32A02INA0 | PG1  | 57               | 42               | 40               |

|                     | T32A02INA1 | PG2  | 58               | 43               | 41               |

|                     | T32A02OUTA | PG0  | 56               | 41               | 39               |

|                     | T32A02INC0 | PG1  | 57               | 42               | 40               |

|                     | T32A02INC1 | PG2  | 58               | 43               | 41               |

|                     | T32A02UTC  | PG0  | 56               | 41               | 39               |

|                     | T32A03INA0 | PC1  | 34               | -                | -                |

|                     | T32A03INA1 | PC2  | 33               | -                | -                |

|                     | T32A03OUTA | PC0  | 35               | 25               | 24               |

|                     | T32A03INC0 | PC1  | 34               | -                | -                |

|                     | T32A03INC1 | PC2  | 33               | -                | -                |

|                     | T32A03UTC  | PC0  | 35               | 25               | 24               |

|                     | T32A04INA0 | PF1  | 52               | -                | -                |

|                     | T32A04INA1 | PF2  | 51               | -                | -                |

|                     | T32A04OUTA | PF0  | 55               | 40               | 38               |

|                     | T32A04INC0 | PF1  | 52               | -                | -                |

|                     | T32A04INC1 | PF2  | 51               | -                | -                |

|                     | T32A04UTC  | PF0  | 55               | 40               | 38               |

|                     | T32A05INA0 | PB1  | 32               | 24               | 23               |

|                     | T32A05OUTA | PB0  | 31               | 23               | 22               |

|                     | T32A05OUTB | PB1  | 32               | 24               | 23               |

|                     | T32A05INC0 | PB1  | 32               | 24               | 23               |

|                     | T32A05UTC  | PB0  | 31               | 23               | 22               |

表 3.3 信号接続一覧(3/5)

| 参照リファレンスマニュアル       | 兼用機能端子名           | ポート名 | M4K4<br>(LQFP64) | M4K2<br>(LQFP48) | M4K1<br>(LQFP44) |

|---------------------|-------------------|------|------------------|------------------|------------------|

| 12ビットアナログデジタルコンバーター | AINA11/<br>AINB11 | PD0  | 37               | 27               | 26               |

|                     | AINA12/<br>AINB12 | PD1  | 38               | 28               | 27               |

|                     | AINA10/<br>AINB10 | PD2  | 39               | 29               | 28               |

|                     | AINA09/<br>AINB09 | PD3  | 40               | 30               | 29               |

|                     | AINA08/<br>AINB08 | PD4  | 41               | 31               | 30               |

|                     | AINA07/<br>AINB07 | PD5  | 42               | 32               | 31               |

|                     | AINA06/<br>AINB06 | PD6  | 43               | 33               | 32               |

|                     | AINA05/<br>AINB05 | PE0  | 44               | 34               | 33               |

|                     | AINA04/<br>AINB04 | PE1  | 45               | 35               | 34               |

|                     | AINA03/<br>AINB03 | PE2  | 46               | 36               | -                |

| 例外                  | AINA02/<br>AINB02 | PE3  | 47               | -                | -                |

|                     | AINA01/<br>AINB01 | PE4  | 48               | -                | -                |

|                     | INT00a            | PK0  | 63               | 48               | 43               |

|                     | INT00b            | PF1  | 52               | -                | -                |

|                     | INT01a            | PK1  | 64               | 1                | 44               |

|                     | INT01b            | PF2  | 51               | -                | -                |

|                     | INT02a            | PK2  | 1                | 2                | 1                |

|                     | INT02b            | PB0  | 31               | 23               | 22               |

|                     | INT03a            | PK3  | 2                | 3                | 2                |

|                     | INT03b            | PB1  | 32               | 24               | 23               |

|                     | INT04             | PG0  | 56               | 41               | 39               |

表 3.4 信号接続一覧(4/5)

| 参照リファレンスマニュアル                | 兼用機能端子名 | ポート名 | M4K4<br>(LQFP64) | M4K2<br>(LQFP48) | M4K1<br>(LQFP44) |

|------------------------------|---------|------|------------------|------------------|------------------|

| アドバンストプログラマブル<br>モーター制御回路    | EMG0    | PJ6  | 22               | 15               | 14               |

|                              |         | PD6  | 43               | 33               | 32               |

|                              |         | PH2  | 13               | 8                | 8                |

|                              | OVV0    | PJ7  | 21               | -                | -                |

|                              | UO0     | PJ0  | 28               | 21               | 20               |

|                              | VO0     | PJ2  | 26               | 19               | 18               |

|                              | WO0     | PJ4  | 24               | 17               | 16               |

|                              | XO0     | PJ1  | 27               | 20               | 19               |

|                              | YO0     | PJ3  | 25               | 18               | 17               |

|                              | ZO0     | PJ5  | 23               | 16               | 15               |

|                              | PMD0DBG | PB0  | 31               | 23               | 22               |

|                              |         | PG0  | 56               | 41               | 39               |

|                              |         | PJ0  | 28               | 21               | 20               |

|                              | EMG1    | PF0  | 55               | 40               | -                |

|                              | UO1     | PG0  | 56               | 41               | -                |

|                              | VO1     | PG1  | 57               | 42               | -                |

|                              | WO1     | PG2  | 58               | 43               | -                |

|                              | XO1     | PG3  | 59               | 44               | -                |

|                              | YO1     | PG4  | 60               | 45               | -                |

|                              | ZO1     | PG5  | 61               | 46               | -                |

| アドバンストエンコーダー<br>入力回路(32-bit) | PMD1DBG | PB1  | 32               | 24               | -                |

|                              |         | PJ1  | 27               | 20               | -                |

|                              |         | PG1  | 57               | 42               | -                |

|                              | ENC0A   | PG0  | 56               | 41               | 39               |

|                              | ENC0B   | PG1  | 57               | 42               | 40               |

|                              | ENC0Z   | PG2  | 58               | 43               | 41               |

|                              | ENC1A   | PJ5  | 23               | 16               | 15               |

|                              | ENC1B   | PJ4  | 24               | 17               | 16               |

|                              | ENC1Z   | PJ3  | 25               | 18               | 17               |

表 3.5 信号接続一覧(5/5)

| 参照リファレンスマニュアル             | 兼用機能端子名    | ポート名 | M4K4<br>(LQFP64) | M4K22<br>(LQFP48) | M4K1<br>(LQFP44) |

|---------------------------|------------|------|------------------|-------------------|------------------|

| 製品個別情報<br>(トリガーセレクター)     | TRGIN0     | PF0  | 55               | 40                | 38               |

|                           | TRGIN1     | PB1  | 32               | 24                | 23               |

|                           | TRGIN2     | PF2  | 51               | -                 | -                |

| デバッグインターフェース<br>(JTAG/SW) | TMS        | PK2  | 1                | 2                 | 1                |

|                           | TCK        | PK3  | 2                | 3                 | 2                |

|                           | TDO        | PK1  | 64               | 1                 | 44               |

|                           | TDI        | PK0  | 63               | 48                | 43               |

|                           | TRST_N     | PK4  | 3                | 4                 | 3                |

|                           | SWDIO      | PK2  | 1                | 2                 | 1                |

|                           | SWCLK      | PK3  | 2                | 3                 | 2                |

|                           | SWV        | PK1  | 64               | 1                 | 44               |

| デバッグインターフェース<br>(トレース)    | TRACECLK   | PL4  | 8                | -                 | -                |

|                           | TRACEDATA0 | PL0  | 7                |                   |                  |

|                           | TRACEDATA1 | PL1  | 6                |                   |                  |

|                           | TRACEDATA2 | PL2  | 5                |                   |                  |

|                           | TRACEDATA3 | PL3  | 4                |                   |                  |

| デバッグインターフェース<br>(NBDIF)   | NBDSYNC    | PK4  | 3                | -                 | -                |

|                           | NBDCLK     | PL4  | 8                |                   |                  |

|                           | NBDDATA0   | PL0  | 7                |                   |                  |

|                           | NBDDATA1   | PL1  | 6                |                   |                  |

|                           | NBDDATA2   | PL2  | 5                |                   |                  |

|                           | NBDDATA3   | PL3  | 4                |                   |                  |

| クロック制御と動作モード              | X1         | PH0  | 15               | 10                | 10               |

|                           | EHCLKIN    | PH0  | 15               | 10                | 10               |

|                           | X2         | PH1  | 16               | 11                | 11               |

|                           | SCOUT      | PJ0  | 28               | 21                | 20               |

| フラッシュメモリー                 | BOOT_N     | PJ6  | 22               | 15                | 14               |

## 4. レジスター説明

ポートを使用する際には以下のレジスターを設定する必要があります。

レジスターは全て 32 ビットですが、ポートのビット数、機能の割り当てにより構成が異なります。

以下の説明では"x"はポート名、"n"はファンクション番号を示します。

| レジスターナンバー |                     | Type | 設定値                      | 説明                                                                                                                                   |

|-----------|---------------------|------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| [PxDATA]  | データレジスター            | R/W  | 0 または 1                  | ポートの状態あるいは出力データの読み込み、出力データの書き込みを行います。                                                                                                |

| [PxCR]    | 出力コントロールレジスター       | R/W  | 0: 出力禁止<br>1: 出力許可       | 出力の制御を行います。                                                                                                                          |

| [PxFRn]   | ファンクションレジスター n      | R/W  | 0: PORT<br>1: 機能         | 機能設定を行ないます。<br>"1"を設定することにより割り当てられている機能を使用できるようになります。ファンクションレジスターはポートに割り当てられている機能ごとに存在します。複数の機能が割り当てられている場合、1つの機能のみ有効になるように設定してください。 |

| [PxOD]    | オープンドレインコントロールレジスター | R/W  | 0: CMOS<br>1: オープンドレイン   | プログラマブルオープンドレインの制御を行います。<br>プログラマブルオープンドレインは、[PxOD]に"1"を設定することにより、出力データが"1"の場合に出力バッファをディセーブルにし、擬似的にオープンドレインを実現する機能です。                |

| [PxPUP]   | プルアップコントロールレジスター    | R/W  | 0: プルアップ禁止<br>1: プルアップ許可 | プログラマブルプルアップ抵抗を制御します。                                                                                                                |

| [PxPDN]   | プルダウンコントロールレジスター    | R/W  | 0: プルダウン禁止<br>1: プルダウン許可 | プログラマブルプルダウン抵抗を制御します。                                                                                                                |

| [PxIE]    | 入力コントロールレジスター       | R/W  | 0: 入力禁止<br>1: 入力許可       | 入力の制御を行ないます。<br>[PxIE]を"1"に設定してからポートの状態が[PxDATA]に反映されるまで 100ns(最大)の時間が必要です。                                                          |

## 4.1. レジスター一覧

存在しないビットをリードすると"0"が読みます。ライトは意味を持ちません。

表 4.1 ポートレジスターのベースアドレス

| 周辺機能   | チャネル/ユニット | ベースアドレス |

|--------|-----------|---------|

| 入出力ポート | PA        | -       |

|        | PB        | -       |

|        | PC        | -       |

|        | PD        | -       |

|        | PE        | -       |

|        | PF        | -       |

|        | PG        | -       |

|        | PH        | -       |

|        | PJ        | -       |

|        | PK        | -       |

|        | PL        | -       |

表 4.2 レジスター一覧

| レジスター名              | アドレス<br>(Base+) | ポート A    | ポート B    | ポート C    | ポート D    | ポート E    | ポート F    |

|---------------------|-----------------|----------|----------|----------|----------|----------|----------|

| データレジスター            | 0x0000          | [PADATA] | [PBDATA] | [PCDATA] | [PDDATA] | [PEDATA] | [PFDATA] |

| 出力コントロールレジスター       | 0x0004          | [PACR]   | [PBCR]   | [PCCR]   | [PDCR]   | [PECR]   | [PFCR]   |

| ファンクションレジスター1       | 0x0008          | [PAFR1]  | [PBFR1]  | [PCFR1]  | -        | -        | -        |

| ファンクションレジスター2       | 0x000C          | [PAFR2]  | [PBFR2]  | [PCFR2]  | -        | -        | -        |

| ファンクションレジスター3       | 0x0010          | [PAFR3]  | [PBFR3]  | [PCFR3]  | -        | -        | -        |

| ファンクションレジスター4       | 0x0014          | [PAFR4]  | [PBFR4]  | [PCFR4]  | -        | -        | [PFFR4]  |

| ファンクションレジスター5       | 0x0018          | [PAFR5]  | [PBFR5]  | [PCFR5]  | [PDR5]   | -        | [PFFR5]  |

| ファンクションレジスター6       | 0x001C          | [PAFR6]  | [PBFR6]  | -        | -        | -        | [PFFR6]  |

| ファンクションレジスター7       | 0x0020          | [PAFR7]  | [PBFR7]  | -        | -        | -        | [PFFR7]  |

| ファンクションレジスター8       | 0x0024          | -        | [PBFR8]  | -        | -        | -        | -        |

| オープンドレインコントロールレジスター | 0x0028          | [PAOD]   | [PBOD]   | [PCOD]   | [PDOD]   | [PEOD]   | [PFOD]   |

| ブルアップコントロールレジスター    | 0x002C          | [PAPUP]  | [PBPUP]  | [PCPUP]  | [PDPUP]  | [PEPUP]  | [PFPUP]  |

| ブルダウンコントロールレジスター    | 0x0030          | [PAPDN]  | [PBPDN]  | [PCPDN]  | [PDPDN]  | [PEPDN]  | [PFPDN]  |

| 入力コントロールレジスター       | 0x0038          | [PAIE]   | [PBIE]   | [PCIE]   | [PDIE]   | [PEIE]   | [PFIE]   |

| レジスター名              | アドレス<br>(Base+) | ポート G    | ポート H    |          | ポート J    | ポート K    | ポート L    |

|---------------------|-----------------|----------|----------|----------|----------|----------|----------|

|                     |                 |          | PH0/1    | PH2/3    |          |          |          |

| データ レジスター           | 0x0000          | [PGDATA] | [PHDATA] | [PHDATA] | [PJDATA] | [PKDATA] | [PLDATA] |

| 出力コントロールレジスター       | 0x0004          | [PGCR]   | -        | [PHCR]   | [PJCR]   | [PKCR]   | [PLCR]   |

| ファンクションレジスター1       | 0x0008          | [PGFR1]  | -        | -        | -        | [PKFR1]  | -        |

| ファンクションレジスター2       | 0x000C          | [PGFR2]  | -        | -        | -        | [PKFR2]  | -        |

| ファンクションレジスター3       | 0x0010          | [PGFR3]  | -        | -        | -        | [PKFR3]  | -        |

| ファンクションレジスター4       | 0x0014          | [PGFR4]  | -        | -        | [PJFR4]  | [PKFR4]  | -        |

| ファンクションレジスター5       | 0x0018          | [PGFR5]  | -        | [PHFR5]  | [PJFR5]  | [PKFR5]  | -        |

| ファンクションレジスター6       | 0x001C          | [PGFR6]  | -        | -        | [PJFR6]  | [PKFR6]  | [PLFR6]  |

| ファンクションレジスター7       | 0x0020          | [PGFR7]  | -        | -        | [PJFR7]  | [PKFR7]  | [PLFR7]  |

| オープンドレインコントロールレジスター | 0x0028          | [PGOD]   | -        | [PHOD]   | [PJOD]   | [PKOD]   | [PLOD]   |

| ブルアップコントロールレジスター    | 0x002C          | [PGPUP]  | -        | [PHPUP]  | [PPUP]   | [PKPUP]  | [PLPUP]  |

| ブルダウンコントロールレジスター    | 0x0030          | [PGPDN]  | [PHPDN]  | [PHPDN]  | [PJPDN]  | [PKPDN]  | [PLPDN]  |

| 入力コントロールレジスター       | 0x0038          | [PGIE]   | [PHIE]   | [PHIE]   | [PJIE]   | [PKIE]   | [PLIE]   |

注) “-” 表記のアドレスにはアクセスしないでください。

## 4.2. ポート機能レジスター設定一覧

ポート機能レジスター設定一覧の表の見方を説明します。

[PxFRn]の欄は、設定の必要なファンクションレジスターを示します。このレジスターを"1"に設定するとその機能が有効となります。(x はポート名、n はファンクション番号)

表中の"N/A"のビットはリードすると"0"が読め、ライトは意味を持ちません。

表中の"0"、"1"は設定値を示し、"0/1"は任意に設定可能であることを示します。

| PORT          | リセット状態      | Input/Output | Port type | 制御レジスター    |            |                           |        |         |         |        |

|---------------|-------------|--------------|-----------|------------|------------|---------------------------|--------|---------|---------|--------|

|               |             |              |           | [PADATA]   | [PACR]     | [PAFRn]                   | [PAOD] | [PAPUP] | [PAPDN] | [PAIE] |

| PA0           | リセット後       |              |           | 0          | 0          | 0                         | 0      | 0       | 0       | 0      |

|               | Input Port  | Input        |           | 0/1        | 0          | 0                         | 0/1    | 0/1     | 0/1     | 1      |

|               | Output Port | Output       |           | 0/1        | 1          | 0                         | 0/1    | 0/1     | 0/1     | 0      |

|               | INT07a      | Input        | FTU4a     | 0/1        | 0          | 0                         | 0/1    | 0/1     | 0/1     | 1      |

|               | UT1TXDA     | Output       | FTU1a     | 0/1        | 1          | [PAFR1]                   | 0/1    | 0/1     | 0/1     | 0      |

|               | UT1RXD      | Input        | FTU1a     | 0/1        | 0          | [PAFR2]                   | 0/1    | 0/1     | 0/1     | 1      |

|               | TSPI1TXD    | Output       | FTU2a     | 0/1        | 1          | [PAFR3]                   | 0/1    | 0/1     | 0/1     | 0      |

|               | T32A01INB0  | Input        | FTU1a     | 0/1        | 0          | [PAFR4]                   | 0/1    | 0/1     | 0/1     | 1      |

|               | T32A01OUTB  | Output       | FTU1a     | 0/1        | 1          | [PAFR5]                   | 0/1    | 0/1     | 0/1     | 0      |

| PA2           | リセット後       |              |           | 0          | 0          | 0                         | 0      | 0       | 0       | 0      |

|               | Input Port  | Input        |           | 0/1        | 0          | 0                         | 0/1    | 0/1     | 0/1     | 1      |

|               | Output Port | Output       |           | 0/1        | 1          | 0                         | 0/1    | 0/1     | 0/1     | 0      |

|               | TSPI1SCK    | Input        |           | 0          |            | [PAFR3]                   | 0/1    | 0/1     | 0/1     | 1      |

|               |             | Output       | FTU1a     | 0/1        | 1          |                           |        |         |         | 0      |

|               | T32A01INA1  | Input        | FTU1a     | 0/1        | 0          | [PAFR4]                   | 0/1    | 0/1     | 0/1     | 1      |

|               | T32A01INC1  | Input        | FTU1a     | 0/1        | 0          | [PAFR5]                   | 0/1    | 0/1     | 0/1     | 1      |

|               | T32A01OUTA  | Output       | FTU1a     | 0/1        | 1          | [PAFR6]                   | 0/1    | 0/1     | 0/1     | 0      |

|               | T32A01OUTC  | Output       | FTU1a     | 0/1        | 1          | [PAFR7]                   | 0/1    | 0/1     | 0/1     | 0      |

| 端子            |             |              |           |            |            |                           |        |         |         |        |

| [PxFRn]       |             |              |           |            |            |                           |        |         |         |        |

|               | UT1TXDA     | UT1RXD       | TSPI1TXD  | T32A01INB0 | T32A01OUTB | Input Port<br>Output Port |        |         |         |        |

| [PAFR1]<bit0> | 1           | 0            | 0         | 0          | 0          | 0                         |        |         |         |        |

| [PAFR2]<bit0> | 0           | 1            | 0         | 0          | 0          | 0                         |        |         |         |        |

| [PAFR3]<bit0> | 0           | 0            | 1         | 0          | 0          | 0                         |        |         |         |        |

| [PAFR4]<bit0> | 0           | 0            | 0         | 1          | 0          | 0                         |        |         |         |        |

| [PAFR5]<bit0> | 0           | 0            | 0         | 0          | 1          | 0                         |        |         |         |        |

### 4.2.1. 機能端子を使用する際の設定について

機能端子を周辺機能の出力端子として使用する際には、ファンクションレジスターを使用する周辺機能([PxFRn]<bit m>=1)に設定し、出力コントロールレジスターを出力許可([PxCR]<bit m>=1)に設定した後、周辺機能の設定をしてください。ファンクションレジスターの設定よりも先に出力許可すると、ファンクションレジスターが設定されるまで、ポートのデータレジスター値が出力されます。

機能端子を周辺機能の入力端子として使用する際には、入力コントロールレジスターを入力([PxIE]<bit m>=1)に設定し、ファンクションレジスターを使用する周辺機能([PxFRn]<bit m>=1)に設定した後、周辺機能の設定をしてください。

また、I<sup>2</sup>Cなどの入出力端子となる周辺機能を使用する場合は、入力コントロールレジスターを入力([PxIE]<bit m>=1)に設定、ファンクションレジスターを使用する周辺機能([PxFRn]<bit m>=1)に設定、出力コントロールレジスターを出力許可([PxCR]<bit m>=1)に設定した後、周辺機能の設定をしてください。

- 複数の機能が割り当てられているポートは、使用する機能を一つだけ選択してください。

- 同一機能が複数ポートに割り当てられている端子は、排他的に使用してください。

## 4.2.2. PORT A

表 4.3 ポートAレジスター設定

| PORT | リセット状態<br>機能 | Input/Output | Port type | 制御レジスター  |        |         |        |         |         |        |

|------|--------------|--------------|-----------|----------|--------|---------|--------|---------|---------|--------|

|      |              |              |           | [PADATA] | [PACR] | [PAFRn] | [PAOD] | [PAPUP] | [PAPDN] | [PAIE] |

| PA0  | リセット後        | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port   | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port  | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT07a       | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | UT1TXDA      | Output       | FTU1a     | 0/1      | 1      | [PAFR1] | 0/1    | 0/1     | 0/1     | 0      |

|      | UT1RXD       | Input        | FTU1a     | 0/1      | 0      | [PAFR2] | 0/1    | 0/1     | 0/1     | 1      |

|      | TSPI1TXD     | Output       | FTU2a     | 0/1      | 1      | [PAFR3] | 0/1    | 0/1     | 0/1     | 0      |

|      | T32A01INB0   | Input        | FTU1a     | 0/1      | 0      | [PAFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A01OUTB   | Output       | FTU1a     | 0/1      | 1      | [PAFR5] | 0/1    | 0/1     | 0/1     | 0      |

| PA1  | リセット後        | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port   | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port  | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT09        | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | UT1RXD       | Input        | FTU1a     | 0/1      | 0      | [PAFR1] | 0/1    | 0/1     | 0/1     | 1      |

|      | UT1TXDA      | Output       | FTU1a     | 0/1      | 1      | [PAFR2] | 0/1    | 0/1     | 0/1     | 0      |

|      | TSPI1RXD     | Input        | FTU1a     | 0/1      | 0      | [PAFR3] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A01INA0   | Input        | FTU1a     | 0/1      | 0      | [PAFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A01INC0   | Input        | FTU1a     | 0/1      | 0      | [PAFR5] | 0/1    | 0/1     | 0/1     | 1      |

| PA2  | リセット後        | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port   | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port  | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | TSPI1SCK     | Input        | FTU1a     | 0/1      | 0      | [PAFR3] | 0/1    | 0/1     | 0/1     | 1      |

|      |              | Output       |           |          | 1      |         |        |         |         | 0      |

|      | T32A01INA1   | Input        | FTU1a     | 0/1      | 0      | [PAFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A01INC1   | Input        | FTU1a     | 0/1      | 0      | [PAFR5] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A01OUTA   | Output       | FTU1a     | 0/1      | 1      | [PAFR6] | 0/1    | 0/1     | 0/1     | 0      |

|      | T32A01UTC    | Output       | FTU1a     | 0/1      | 1      | [PAFR7] | 0/1    | 0/1     | 0/1     | 0      |

## 4.2.3. PORT B

表 4.4 ポートBレジスター設定

| PORT | リセット状態                   | Input/Output | Port type | 制御レジスター   |        |         |        |        |         |        |

|------|--------------------------|--------------|-----------|-----------|--------|---------|--------|--------|---------|--------|

|      | 機能                       |              |           | [PB DATA] | [PBCR] | [PBFRn] | [PBOD] | [PBPU] | [PBPDN] | [PBIE] |

| PB0  | リセット後                    | -            | -         | 0         | 0      | 0       | 0      | 0      | 0       | 0      |

|      | Input Port               | Input        | -         | 0/1       | 0      | 0       | 0/1    | 0/1    | 0/1     | 1      |

|      | Output Port              | Output       | -         | 0/1       | 1      | 0       | 0/1    | 0/1    | 0/1     | 0      |

|      | INT02b                   | Input        | FTU4a     | 0/1       | 0      | 0       | 0/1    | 0/1    | 0/1     | 1      |

|      | UT1TXDA                  | Output       | FTU1a     | 0/1       | 1      | [PBFR2] | 0/1    | 0/1    | 0/1     | 0      |

|      | I2C0SDA/<br>EI2C0SDA (注) | I/O          | FTU1a     | 0/1       | 1      | [PBFR3] | 1      | 0/1    | 0/1     | 1      |

|      | T32A05OUTA               | Output       | FTU1a     | 0/1       | 1      | [PBFR4] | 0/1    | 0/1    | 0/1     | 0      |

|      | T32A05UTC                | Output       | FTU1a     | 0/1       | 1      | [PBFR5] | 0/1    | 0/1    | 0/1     | 0      |

|      | PMD0DBG                  | Output       | FTU1a     | 0/1       | 1      | [PBFR7] | 0/1    | 0/1    | 0/1     | 0      |

|      | UT1RXD                   | Input        | FTU1a     | 0/1       | 0      | [PBFR8] | 0/1    | 0/1    | 0/1     | 1      |

| PB1  | リセット後                    | -            | -         | 0         | 0      | 0       | 0      | 0      | 0       | 0      |

|      | Input Port               | Input        | -         | 0/1       | 0      | 0       | 0/1    | 0/1    | 0/1     | 1      |

|      | Output Port              | Output       | -         | 0/1       | 1      | 0       | 0/1    | 0/1    | 0/1     | 0      |

|      | INT03b                   | Input        | FTU4a     | 0/1       | 0      | 0       | 0/1    | 0/1    | 0/1     | 1      |

|      | T32A05OUTB               | Output       | FTU1a     | 0/1       | 1      | [PBFR1] | 0/1    | 0/1    | 0/1     | 0      |

|      | UT1RXD                   | Input        | FTU1a     | 0/1       | 0      | [PBFR2] | 0/1    | 0/1    | 0/1     | 1      |

|      | I2C0SCL/<br>EI2C0SCL (注) | I/O          | FTU1a     | 0/1       | 1      | [PBFR3] | 1      | 0/1    | 0/1     | 1      |

|      | T32A05INA0               | Input        | FTU1a     | 0/1       | 0      | [PBFR4] | 0/1    | 0/1    | 0/1     | 1      |

|      | T32A05INC0               | Input        | FTU1a     | 0/1       | 0      | [PBFR5] | 0/1    | 0/1    | 0/1     | 1      |

|      | TRGIN1                   | Input        | FTU1a     | 0/1       | 0      | [PBFR6] | 0/1    | 0/1    | 0/1     | 1      |

|      | PMD1DBG                  | Output       | FTU1a     | 0/1       | 1      | [PBFR7] | 0/1    | 0/1    | 0/1     | 0      |

|      | UT1TXDA                  | Output       | FTU1a     | 0/1       | 1      | [PBFR8] | 0/1    | 0/1    | 0/1     | 0      |

注) I2C と EI2C は排他的に使用してください。

## 4.2.4. PORT C

表 4.5 ポートCレジスター設定

| PORT | リセット状態      | Input/Output | Port type | 制御レジスター  |        |         |        |         |         |        |

|------|-------------|--------------|-----------|----------|--------|---------|--------|---------|---------|--------|

|      |             |              |           | [PCDATA] | [PCCR] | [PCFRn] | [PCOD] | [PCPUP] | [PCPDN] | [PCIE] |

| PC0  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT08       | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | UT3TXDA     | Output       | FTU1a     | 0/1      | 1      | [PCFR1] | 0/1    | 0/1     | 0/1     | 0      |

|      | UT3RXD      | Input        | FTU1a     | 0/1      | 0      | [PCFR2] | 0/1    | 0/1     | 0/1     | 1      |

|      | TSPI3TXD    | Output       | FTU2a     | 0/1      | 1      | [PCFR3] | 0/1    | 0/1     | 0/1     | 0      |

|      | T32A03OUTA  | Output       | FTU1a     | 0/1      | 1      | [PCFR4] | 0/1    | 0/1     | 0/1     | 0      |

|      | T32A03OUTC  | Output       | FTU1a     | 0/1      | 1      | [PCFR5] | 0/1    | 0/1     | 0/1     | 0      |

| PC1  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT10       | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | UT3RXD      | Input        | FTU1a     | 0/1      | 0      | [PCFR1] | 0/1    | 0/1     | 0/1     | 1      |

|      | UT3TXDA     | Output       | FTU1a     | 0/1      | 1      | [PCFR2] | 0/1    | 0/1     | 0/1     | 0      |

|      | TSPI3RXD    | Input        | FTU1a     | 0/1      | 0      | [PCFR3] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A03INA0  | Input        | FTU1a     | 0/1      | 0      | [PCFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A03INC0  | Input        | FTU1a     | 0/1      | 0      | [PCFR5] | 0/1    | 0/1     | 0/1     | 1      |

| PC2  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT07b      | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | TSPI3SCK    | Input        | FTU1a     | 0/1      | 0      | [PCFR3] | 0/1    | 0/1     | 0/1     | 1      |

|      |             | Output       |           |          | 1      |         |        |         |         | 0      |

|      | T32A03INA1  | Input        | FTU1a     | 0/1      | 0      | [PCFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A03INC1  | Input        | FTU1a     | 0/1      | 0      | [PCFR5] | 0/1    | 0/1     | 0/1     | 1      |

## 4.2.5. PORT D

表 4.6 ポートD レジスター設定

| PORT | リセット状態                | Input/Output | Port type | 制御レジスター  |        |         |        |         |         |        |

|------|-----------------------|--------------|-----------|----------|--------|---------|--------|---------|---------|--------|

|      |                       |              |           | [PDDATA] | [PDCR] | [PDFRn] | [PDOD] | [PDPUP] | [PDPDN] | [PDIE] |

| PD0  | リセット後                 | -            | -         | 0        | 0      | N/A     | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | N/A     | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | N/A     | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA11/<br>AINB11 (注) | Input        | FTU5a     | 0/1      | 0      | N/A     | 0/1    | 0       | 0       | 0      |

| PD1  | リセット後                 | -            | -         | 0        | 0      | N/A     | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | N/A     | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | N/A     | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA12/<br>AINB12 (注) | Input        | FTU5a     | 0/1      | 0      | N/A     | 0/1    | 0       | 0       | 0      |

| PD2  | リセット後                 | -            | -         | 0        | 0      | N/A     | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | N/A     | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | N/A     | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA10/<br>AINB10 (注) | Input        | FTU5a     | 0/1      | 0      | N/A     | 0/1    | 0       | 0       | 0      |

| PD3  | リセット後                 | -            | -         | 0        | 0      | N/A     | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | N/A     | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | N/A     | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA09/<br>AINB09 (注) | Input        | FTU5a     | 0/1      | 0      | N/A     | 0/1    | 0       | 0       | 0      |

| PD4  | リセット後                 | -            | -         | 0        | 0      | N/A     | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | N/A     | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | N/A     | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA08/<br>AINB08 (注) | Input        | FTU5a     | 0/1      | 0      | N/A     | 0/1    | 0       | 0       | 0      |

| PD5  | リセット後                 | -            | -         | 0        | 0      | N/A     | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | N/A     | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | N/A     | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA07/<br>AINB07 (注) | Input        | FTU5a     | 0/1      | 0      | N/A     | 0/1    | 0       | 0       | 0      |

| PD6  | リセット後                 | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA06/<br>AINB06 (注) | Input        | FTU5a     | 0/1      | 0      | 0       | 0/1    | 0       | 0       | 0      |

|      | EMG0                  | Input        | FTU1a     | 0/1      | 0      | [PDFR5] | 0/1    | 0/1     | 0/1     | 1      |

注) アナログ入力端子(AINAx/AINBx)として使用する場合、[PDIE]は入力禁止"0"、[PDCR]は出力禁止"0"、[PDPUP]はプルアップ禁止"0"、[PDPDN]はプルダウン禁止"0"にしてください。

## 4.2.6. PORT E

表 4.7 ポートEレジスター設定

| PORT | リセット状態                | Input/Output | Port type | 制御レジスター  |        |         |        |         |         |        |

|------|-----------------------|--------------|-----------|----------|--------|---------|--------|---------|---------|--------|

|      |                       |              |           | [PEDATA] | [PECR] | [PEFRn] | [PEOD] | [PEPUP] | [PEPDN] | [PEIE] |

| PE0  | リセット後                 | -            | -         | 0        | 0      | N/A     | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | N/A     | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | N/A     | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA05/<br>AINB05 (注) | Input        | FTU5a     | 0/1      | 0      | N/A     | 0/1    | 0       | 0       | 0      |

| PE1  | リセット後                 | -            | -         | 0        | 0      | N/A     | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | N/A     | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | N/A     | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA04/<br>AINB04 (注) | Input        | FTU5a     | 0/1      | 0      | N/A     | 0/1    | 0       | 0       | 0      |

| PE2  | リセット後                 | -            | -         | 0        | 0      | N/A     | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | N/A     | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | N/A     | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA03/<br>AINB03 (注) | Input        | FTU5a     | 0/1      | 0      | N/A     | 0/1    | 0       | 0       | 0      |

| PE3  | リセット後                 | -            | -         | 0        | 0      | N/A     | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | N/A     | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | N/A     | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA02/<br>AINB02 (注) | Input        | FTU5a     | 0/1      | 0      | N/A     | 0/1    | 0       | 0       | 0      |

| PE4  | リセット後                 | -            | -         | 0        | 0      | N/A     | 0      | 0       | 0       | 0      |

|      | Input Port            | Input        | -         | 0/1      | 0      | N/A     | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port           | Output       | -         | 0/1      | 1      | N/A     | 0/1    | 0/1     | 0/1     | 0      |

|      | AINA01/<br>AINB01 (注) | Input        | FTU5a     | 0/1      | 0      | N/A     | 0/1    | 0       | 0       | 0      |

注) アナログ入力端子(AINAx/AINBx)として使用する場合、[PEIE]は入力禁止"0"、[PECR]は出力禁止"0"、[PEPUP]はプルアップ禁止"0"、[PEPDN]はプルダウン禁止"0"にしてください。

## 4.2.7. PORT F

表 4.8 ポートFレジスター設定

| PORT | リセット状態      | Input/Output | Port type | 制御レジスター  |        |         |        |         |         |        |

|------|-------------|--------------|-----------|----------|--------|---------|--------|---------|---------|--------|

|      |             |              |           | [PFDATA] | [PFCR] | [PFFRn] | [PFOD] | [PFPUP] | [PFPDN] | [PFIE] |

| PF0  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | T32A04OUTA  | Output       | FTU1a     | 0/1      | 1      | [PFFR4] | 0/1    | 0/1     | 0/1     | 0      |

|      | T32A04OUTC  | Output       | FTU1a     | 0/1      | 1      | [PFFR5] | 0/1    | 0/1     | 0/1     | 0      |

|      | TRGIN0      | Input        | FTU1a     | 0/1      | 0      | [PFFR6] | 0/1    | 0/1     | 0/1     | 1      |

|      | EMG1        | Input        | FTU1a     | 0/1      | 0      | [PFFR7] | 0/1    | 0/1     | 0/1     | 1      |

| PF1  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT00b      | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A04INA0  | Input        | FTU1a     | 0/1      | 0      | [PFFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A04INC0  | Input        | FTU1a     | 0/1      | 0      | [PFFR5] | 0/1    | 0/1     | 0/1     | 1      |

| PF2  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT01b      | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A04INA1  | Input        | FTU1a     | 0/1      | 0      | [PFFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A04INC1  | Input        | FTU1a     | 0/1      | 0      | [PFFR5] | 0/1    | 0/1     | 0/1     | 1      |

|      | TRGIN2      | Input        | FTU1a     | 0/1      | 0      | [PFFR6] | 0/1    | 0/1     | 0/1     | 1      |

## 4.2.8. PORT G

表 4.9 ポートGレジスター設定

| PORT | リセット状態      | Input/Output | Port type | 制御レジスター  |        |         |        |         |         |        |

|------|-------------|--------------|-----------|----------|--------|---------|--------|---------|---------|--------|

|      |             |              |           | [PGDATA] | [PGCR] | [PGFRn] | [PGOD] | [PGPUP] | [PGPDN] | [PGIE] |

| PG0  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT04       | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | UT2TXDA     | Output       | FTU1a     | 0/1      | 1      | [PGFR1] | 0/1    | 0/1     | 0/1     | 0      |

|      | TSPI2TXD    | Output       | FTU2a     | 0/1      | 1      | [PGFR2] | 0/1    | 0/1     | 0/1     | 0      |

|      | T32A02OUTA  | Output       | FTU1a     | 0/1      | 1      | [PGFR3] | 0/1    | 0/1     | 0/1     | 0      |

|      | T32A02OUTC  | Output       | FTU1a     | 0/1      | 1      | [PGFR4] | 0/1    | 0/1     | 0/1     | 0      |

|      | ENC0A       | Input        | FTU1a     | 0/1      | 0      | [PGFR5] | 0/1    | 0/1     | 0/1     | 1      |

|      | VO1         | Output       | FTU2a     | 0/1      | 1      | [PGFR6] | 0/1    | 0/1     | 0/1     | 0      |

| PG1  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT05       | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | UT2RXD      | Input        | FTU1a     | 0/1      | 0      | [PGFR1] | 0/1    | 0/1     | 0/1     | 1      |

|      | TSPI2RXD    | Input        | FTU1a     | 0/1      | 0      | [PGFR2] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A02INA0  | Input        | FTU1a     | 0/1      | 0      | [PGFR3] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A02INC0  | Input        | FTU1a     | 0/1      | 0      | [PGFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | ENC0B       | Input        | FTU1a     | 0/1      | 0      | [PGFR5] | 0/1    | 0/1     | 0/1     | 1      |

|      | VO1         | Output       | FTU2a     | 0/1      | 1      | [PGFR6] | 0/1    | 0/1     | 0/1     | 0      |

| PG2  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | TSPI2SCK    | Input        |           |          | 0      |         |        |         |         | 1      |

|      |             | Output       | FTU1a     | 0/1      | 1      | [PGFR2] | 0/1    | 0/1     | 0/1     | 0      |

|      | T32A02INA1  | Input        | FTU1a     | 0/1      | 0      | [PGFR3] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A02INC1  | Input        | FTU1a     | 0/1      | 0      | [PGFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | ENC0Z       | Input        | FTU1a     | 0/1      | 0      | [PGFR5] | 0/1    | 0/1     | 0/1     | 1      |

| PG3  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | XO1         | Output       | FTU2a     | 0/1      | 1      | [PGFR6] | 0/1    | 0/1     | 0/1     | 0      |

| PG4  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | YO1         | Output       | FTU2a     | 0/1      | 1      | [PGFR6] | 0/1    | 0/1     | 0/1     | 0      |

| PG5  | リセット後       | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port  | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | ZO1         | Output       | FTU2a     | 0/1      | 1      | [PGFR6] | 0/1    | 0/1     | 0/1     | 0      |

## 4.2.9. PORT H

表 4.10 ポートH レジスター設定

| PORT | リセット状態<br>機能 | Input/Output | PORT type | 制御レジスター  |        |         |        |         |         |        |

|------|--------------|--------------|-----------|----------|--------|---------|--------|---------|---------|--------|

|      |              |              |           | [PHDATA] | [PHCR] | [PHFRn] | [PHOD] | [PHPUP] | [PHPDN] | [PHIE] |

| PH0  | リセット後        | -            | -         | 0        | N/A    | N/A     | N/A    | N/A     | 0       | 0      |

|      | Input Port   | Input        | -         | 0/1      | N/A    | N/A     | N/A    | N/A     | 0/1     | 1      |

|      | X1           | Input        | FTU11a    | 0/1      | N/A    | N/A     | N/A    | N/A     | 0       | 0      |

|      | EHCLKIN      | Input        | FTU11a    | 0/1      | N/A    | N/A     | N/A    | N/A     | 0       | 0/1    |

| PH1  | リセット後        | -            | -         | 0        | N/A    | N/A     | N/A    | N/A     | 0       | 0      |

|      | Input Port   | Input        | -         | 0/1      | N/A    | N/A     | N/A    | N/A     | 0/1     | 1      |

|      | X2           | Output       | FTU11a    | 0/1      | N/A    | N/A     | N/A    | N/A     | 0       | 0      |

| PH2  | リセット後        | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port   | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port  | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | EMG0         | Input        | FTU1a     | 0/1      | 0      | [PHFR5] | 0/1    | 0/1     | 0/1     | 1      |

| PH3  | リセット後        | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port   | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port  | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

## 4.2.10. PORT J

表 4.11 ポートJ レジスター設定

| PORT | リセット状態            | Input/Output | PORT type | 制御レジスター  |        |         |        |         |         |        |

|------|-------------------|--------------|-----------|----------|--------|---------|--------|---------|---------|--------|

|      |                   |              |           | [PJDATA] | [PJCR] | [PJFRn] | [PJOD] | [PJPUP] | [PJPDN] | [PJIE] |

| PJ0  | リセット後             | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port        | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port       | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | UO0               | Output       | FTU2a     | 0/1      | 1      | [PJFR5] | 0/1    | 0/1     | 0/1     | 0      |

|      | SCOUT             | Output       | FTU1a     | 0/1      | 1      | [PJFR6] | 0/1    | 0/1     | 0/1     | 0      |

|      | PMD0DBG           | Output       | FTU1a     | 0/1      | 1      | [PJFR7] | 0/1    | 0/1     | 0/1     | 0      |

| PJ1  | リセット後             | -            | -         | 0        | 0      | 0       | 0      | 0       |         | 0      |

|      | Input Port        | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port       | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | XO0               | Output       | FTU2a     | 0/1      | 1      | [PJFR5] | 0/1    | 0/1     | 0/1     | 0      |

|      | PMD1DBG           | Output       | FTU1a     | 0/1      | 1      | [PJFR7] | 0/1    | 0/1     | 0/1     | 0      |

| PJ2  | リセット後             | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port        | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port       | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | VO0               | Output       | FTU2a     | 0/1      | 1      | [PJFR5] | 0/1    | 0/1     | 0/1     | 0      |

| PJ3  | リセット後             | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port        | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port       | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | ENC1Z             | Input        | FTU1a     | 0/1      | 0      | [PJFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | YO0               | Output       | FTU2a     | 0/1      | 1      | [PJFR5] | 0/1    | 0/1     | 0/1     | 0      |

| PJ4  | リセット後             | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port        | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port       | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | ENC1B             | Input        | FTU1a     | 0/1      | 0      | [PJFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | WO0               | Output       | FTU2a     | 0/1      | 1      | [PJFR5] | 0/1    | 0/1     | 0/1     | 0      |

| PJ5  | リセット後             | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port        | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port       | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | ENC1A             | Input        | FTU1a     | 0/1      | 0      | [PJFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | ZO0               | Output       | FTU2a     | 0/1      | 1      | [PJFR5] | 0/1    | 0/1     | 0/1     | 0      |

| PJ6  | リセット中<br>(BOOT_N) | Input        | FTU16a    | 0        | 0      | 0       | 0      | 0 (注)   | 0       | 0 (注)  |

|      | リセット後             | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port        | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port       | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | EMG0              | Input        | FTU1a     | 0/1      | 0      | [PJFR5] | 0/1    | 0/1     | 0/1     | 1      |

| PJ7  | リセット後             | -            | -         | 0        | 0      | 0       | 0      | 0       | 0       | 0      |

|      | Input Port        | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port       | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | OVV0              | Input        | FTU1a     | 0/1      | 0      | [PJFR5] | 0/1    | 0/1     | 0/1     | 1      |

注) PJ6 は、リセット端子(RESET\_N)によるリセット期間中は、プルアップ許可、入力許可で、

BOOT\_N 端子の状態を入力できます。

## 4.2.11. PORT K

表 4.12 ポートK レジスター設定

| PORT | リセット状態               | Input/Output | PORT type | 制御レジスター  |        |         |        |         |         |        |

|------|----------------------|--------------|-----------|----------|--------|---------|--------|---------|---------|--------|

|      |                      |              |           | [PKDATA] | [PKCR] | [PKFRn] | [PKOD] | [PKPUP] | [PKPDN] | [PKIE] |

| PK0  | リセット後<br>(TDI)       | Input        | FTU2a     | 0        | 0      | [PKFR7] | 0      | 1       | 0       | 1      |

|      | Input Port           | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port          | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT00a               | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | UT0RXD               | Input        | FTU1a     | 0/1      | 0      | [PKFR1] | 0/1    | 0/1     | 0/1     | 1      |

|      | UT0TXDA              | Output       | FTU1a     | 0/1      | 1      | [PKFR2] | 0/1    | 0/1     | 0/1     | 0      |

|      | T32A00OUTA           | Output       | FTU1a     | 0/1      | 1      | [PKFR4] | 0/1    | 0/1     | 0/1     | 0      |

|      | T32A00OUTC           | Output       | FTU1a     | 0/1      | 1      | [PKFR5] | 0/1    | 0/1     | 0/1     | 0      |

| PK1  | リセット後<br>(TDO/SWV)   | Output       | FTU2a     | 0        | 1(注)   | [PKFR7] | 0      | 0       | 0       | 0      |

|      | Input Port           | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port          | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT01a               | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | UT0TXDA              | Output       | FTU1a     | 0/1      | 1      | [PKFR1] | 0/1    | 0/1     | 0/1     | 0      |

|      | UT0RXD               | Input        | FTU1a     | 0/1      | 0      | [PKFR2] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A00INA0           | Input        | FTU1a     | 0/1      | 0      | [PKFR4] | 0/1    | 0/1     | 0/1     | 1      |

|      | T32A00INC0           | Input        | FTU1a     | 0/1      | 0      | [PKFR5] | 0/1    | 0/1     | 0/1     | 1      |

| PK2  | リセット後<br>(TMS/SWDIO) | Input/Output | FTU2a     | 0        | 1(注)   | [PKFR7] | 0      | 1       | 0       | 1      |

|      | Input Port           | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port          | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT02a               | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | UT0RXD               | Input        | FTU1a     | 0/1      | 0      | [PKFR1] | 0/1    | 0/1     | 0/1     | 1      |

|      | UT0TXDA              | Output       | FTU1a     | 0/1      | 1      | [PKFR2] | 0/1    | 0/1     | 0/1     | 0      |

|      | TSPI0RXD             | Input        | FTU1a     | 0/1      | 0      | [PKFR3] | 0/1    | 0/1     | 0/1     | 1      |

| PK3  | リセット後<br>(TCK/SWCLK) | Input        | FTU2a     | 0        | 0      | [PKFR7] | 0      | 0       | 1       | 1      |

|      | Input Port           | Input        | -         | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |

|      | Output Port          | Output       | -         | 0/1      | 1      | 0       | 0/1    | 0/1     | 0/1     | 0      |

|      | INT03a               | Input        | FTU4a     | 0/1      | 0      | 0       | 0/1    | 0/1     | 0/1     | 1      |