# Isolated Gate Drive Circuit for 3-Phase Inverter

# **Reference Guide**

## RD238-RGUIDE-01

## **Toshiba Electronic Devices & Storage Corporation**

### **Table of Contents**

| 1.   | Introduction4                                                         |

|------|-----------------------------------------------------------------------|

| 2.   | Specifications5                                                       |

| 2.1. | Circuit Block Diagram5                                                |

| 2.2. | Appearance and Component Arrangement6                                 |

| 3.   | Schematic, Bill of Materials, and PCB Pattern Diagram .9              |

| 3.1. | Schematic9                                                            |

| 3.2. | Bill of Materials9                                                    |

| 3.3. | PCB Pattern Diagram9                                                  |

| 4.   | Names and Functions of Components12                                   |

| 4.1. | Input/Output Signal Connector (CN11)12                                |

| 4.2. | Control Power Supply Connector (CN10)13                               |

| 4.3. | Power Module Connectors14                                             |

| 4.4. | Jumper Resistors for External 5V (R10, R11)15                         |

| 5.   | Operation16                                                           |

| 5.1. | Operation Check                                                       |

| 5.   | 1.1. Operation Check of the Board Alone16                             |

| 5.   | 1.2. Power Module Connection Operation Check                          |

| 5.   | 1.3. Each Protection Function                                         |

| 5.2. | Adjusting Circuits                                                    |

| 5.   | 2.1. Adjusting the Gate Resistance                                    |

|      | 2.2. Adjusting DESAT Detection Voltage (R34x, R35x, D32x, D33x, D34x, |

| D:   | 35x, D37x)                                                            |

| 1x) 22 | 3. Adjusting DESAT Detection Duration (C38x, R3  | 5    |

|--------|--------------------------------------------------|------|

| 1x)23  | 4. Adjusting the Input-Signal RC Filter (C20x/R2 | 5    |

|        | ecautions                                        | 5.3. |

### 1. Introduction

This Reference Guide (hereafter, this guide) describes the specifications and operation procedures of the Isolated Gate Drive Circuit for 3-Phase Inverter (hereafter, this design).

3-phase inverters which is capable of converting power are indispensable for not only industrial inverters but also for renewable energy such as photovoltaic power generation and will become increasingly important in the future.

This design allows isolated gate drive of power modules used in 3-phase inverter circuits.

It incorporates various protective functions and uses the smart gate driver coupler <u>TLP5222</u> that does not require complicated external circuit, realizing a 7-channel (U-, V-, and W-phase high-side low-side and braking circuit) gate drive circuit on a small board. UVLO monitors and protects against the drop in gate-drive-voltage, overcurrent protection by detecting DESAT (non-saturation) and self-turn-on prevention by active miller clamp can be equipped to safely drive the power semiconductor module.

It is also possible to adjust each component according to the actual circuit designs. Refer to TLP5222 datasheet, related documentation, RD238 Design Guide, etc. for adjusting each component.

When this design is considered to use actual application, refer to the TLP5222 datasheet and design circuits to make operation conditions and environments meet applied safety standard.

Fig. 1 Photograph of This Design

## 2. Specifications

Table 2.1 lists the main specifications of this design.

#### Table 2.1 Board Specifications of Isolated Gate Drive Circuit for 3-Phase Inverter

| Item                             | Specifications                                            |  |  |

|----------------------------------|-----------------------------------------------------------|--|--|

| Power supply voltage for control | DC 24V                                                    |  |  |

|                                  | 7 ch: U-phase (low-side, high-side)                       |  |  |

| Number of driving channels       | V-phase (low-side, high-side)                             |  |  |

| Number of unving channels        | W-phase (low-side, high-side)                             |  |  |

|                                  | Brake circuit                                             |  |  |

| Gate control signal input        | 5V CMOS                                                   |  |  |

| Enable signal input              | 37 CMOS                                                   |  |  |

| Gate drive frequency             | 20kHz                                                     |  |  |

| Gate drive output                | +16V / -8V                                                |  |  |

| Maximum gate drive peak current  | ±2.5A                                                     |  |  |

| Error detection output           | Open collector output (with pull-up resistor)             |  |  |

| Temperature detection terminal   | NTC with built-in external power module                   |  |  |

|                                  | Overcurrent protection and soft shutdown by detecting     |  |  |

| Power module protection function | DESAT                                                     |  |  |

|                                  | Active miller clamp (AMC)                                 |  |  |

|                                  | Gate-drive under voltage lock out (UVLO)                  |  |  |

| Board size                       | 100mm x 100mm                                             |  |  |

|                                  | FR-4 1.6mm thickness 4 layers                             |  |  |

| Board layer configuration        | Copper foil thickness: Outer layer 18µm, Inner layer 35µm |  |  |

|                                  | Double-sided silk, double-sided mounting                  |  |  |

#### 2.1. Circuit Block Diagram

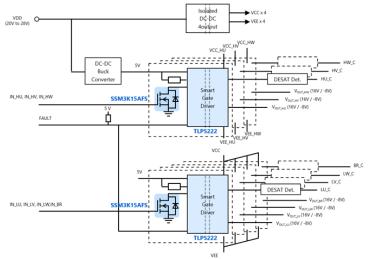

Fig. 2.1 shows the block diagram of this design.

#### Fig. 2.1 Block Diagram of Isolated Gate Drive Circuit for 3-Phase Inverter

#### 2.2. Appearance and Component Arrangement

TOSHIBA

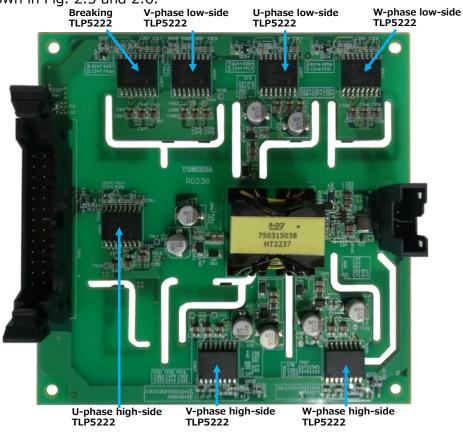

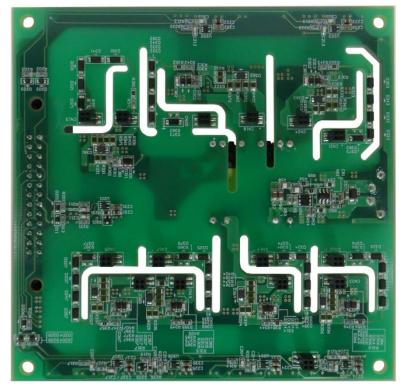

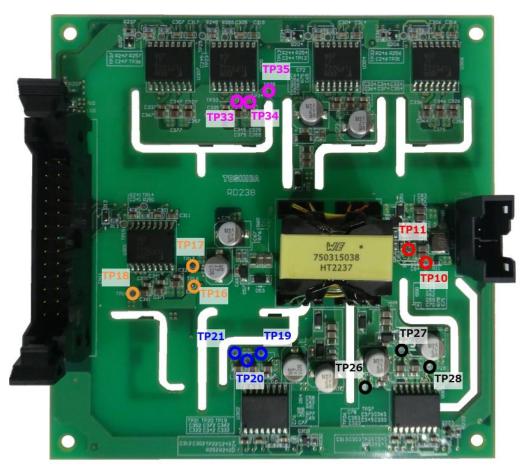

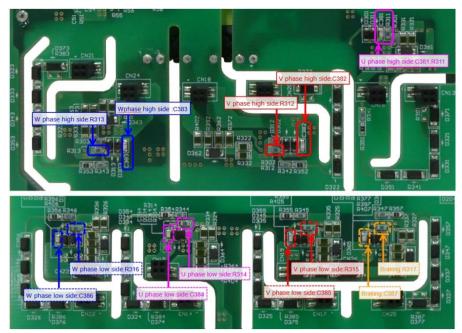

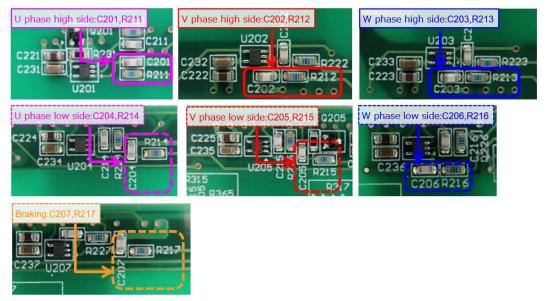

The appearance of this design is shown in Fig. 2.2 through 2.4, and the layout of major components is shown in Fig. 2.5 and 2.6.

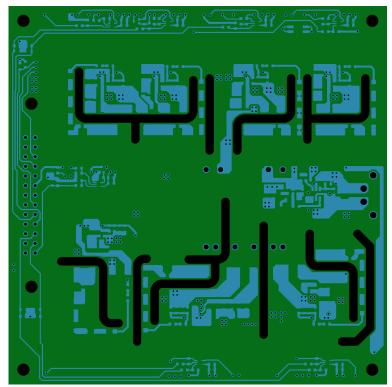

Fig. 2.2 Board (Top View)

Fig. 2.3 Board (Bottom View)

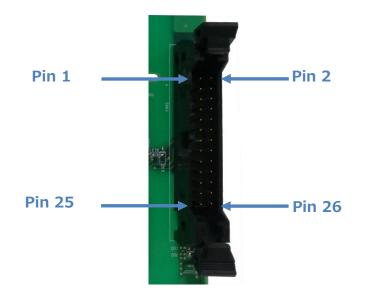

Fig. 2.4 Board (Side View)

### RD238-RGUIDE-01

Fig. 2.5 Layout of Main Components (Top View)

Fig. 2.6 Layout of Main Components (Bottom View)

### 3. Schematic, Bill of Materials, and PCB Pattern Diagram

#### 3.1. Schematic

Refer to the file below. RD238-SCHEMATIC-xx.pdf (xx is the revision number.)

#### 3.2. Bill of Materials

Refer to the file below. RD238-BOM-xx.pdf (xx is the revision number.)

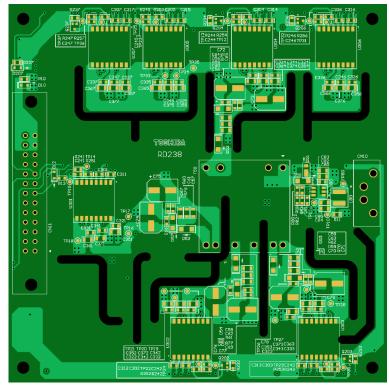

#### 3.3. PCB Pattern Diagram

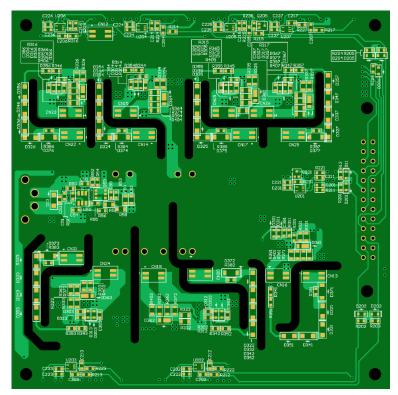

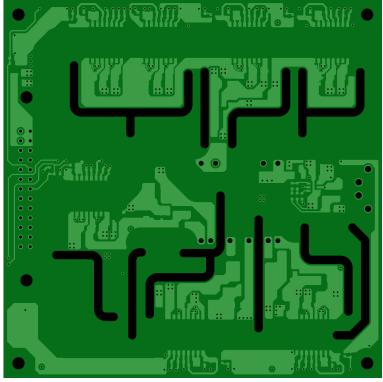

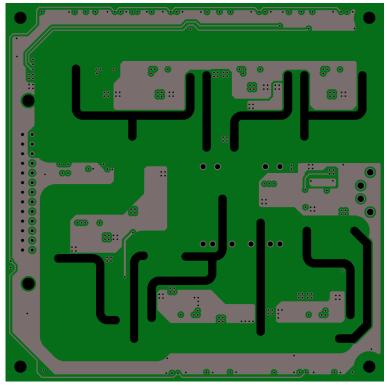

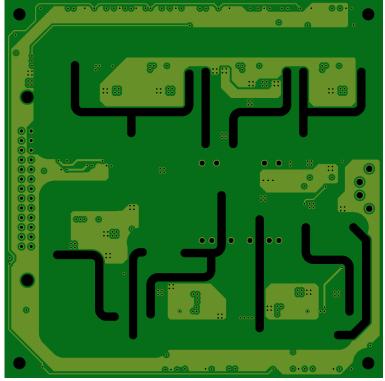

Fig. 3.1 shows the pattern diagram of this design. Also refer to the following file: RD238-LAYER-xx.pdf (xx is the revision number.)

<Layer 1 Front>

< Layer 2>

< Layer 3>

< Layer 4 > Fig. 3.1 PCB Pattern Diagram (Front View)

### 4. Names and Functions of Components

### 4.1. Input/Output Signal Connector (CN11)

This connector is used for Input/output signals. XG4A-2632 (made by OMRON, with 2.54mm pitch) is used.

Fig. 4.1 Input/Output Signal Connector (CN11)

| Pin# | Signal<br>name | I/O | Description                                                   | Pin#                             | Signal<br>name | I/O | Description |

|------|----------------|-----|---------------------------------------------------------------|----------------------------------|----------------|-----|-------------|

| 1    | IN_HU          | Ι   | U-phase high-side signal input                                | 2                                |                |     |             |

| 3    | IN_HV          | Ι   | V-phase high-side signal input                                | 4                                |                |     |             |

| 5    | IN_HW          | Ι   | W-phase high-side signal input                                | 6                                |                |     |             |

| 7    | IN_LU          | Ι   | U-phase low-side signal input                                 | 8                                |                |     |             |

| 9    | IN_LV          | Ι   | V-phase low-side signal input                                 | 10                               |                |     |             |

| 11   | IN_LW          | Ι   | W-phase low-side signal input                                 | W-phase low-side signal input 12 |                |     |             |

| 13   | EN             | Ι   | Enable signal input                                           | 14                               |                |     |             |

| 15   | FAULT          | 0   | Fault Detection Output<br>(pull-up resistor collector output) | 16                               | GND            | -   | GND         |

| 17   | IN_BR          | Ι   | Gate signal input for brake                                   | 18                               |                |     |             |

| 19   | TH1            | 0   | Temperature detection terminal 1                              | 20                               |                |     |             |

| 21   | TH2            | 0   | Temperature detection terminal 2                              | 22                               |                |     |             |

| 23   |                |     | Terminal for applying external                                | 24                               |                |     |             |

| 25   | (5V)           | -   | power 5V<br>(Optional)                                        | 26                               |                |     |             |

Table4.1 Specifications of Input/Output Signal Connector (CN11)

### 4.2. Control Power Supply Connector (CN10)

TOSHIBA

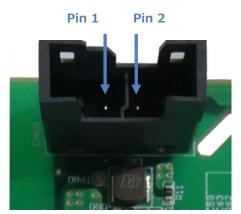

This connector is used for applying control power supply voltage. XW4M-02D1-V1DS (made by OMRON, with 3.5mm pitch) is used.

Fig. 4.2 Control Power Supply Connector (CN10)

#### Table 4.2 Specifications of Control Power Connector (CN10)

| Pin# | Signal name | Description                         | Pin# | Signal name | Description |

|------|-------------|-------------------------------------|------|-------------|-------------|

| 1    | VDD         | Power supply<br>voltage for control | 2    | GND         | GND         |

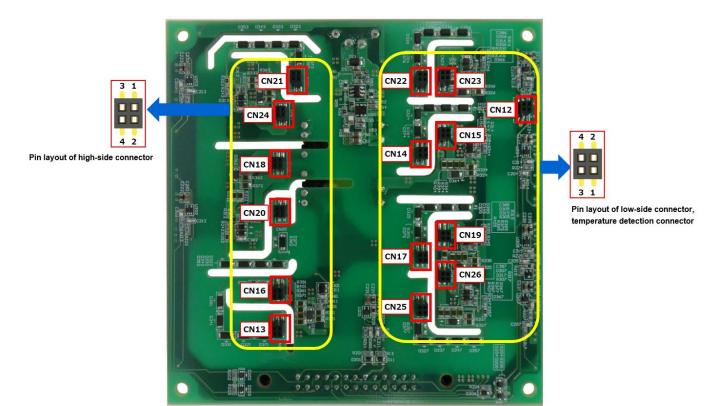

#### 4.3. Power Module Connectors

These are the high-side, low-side and brake-circuit gate-drive output connectors for each phase (phase U, V, and W), and DESAT detection connectors. 62300421021 (made by Würth Elektronik) is used.

Fig. 4.3 Layout of Power Module Connectors (on Back Side of the Board)

|      | Pin#    | Description                 |      | Pin#    | Description                |

|------|---------|-----------------------------|------|---------|----------------------------|

| CN21 | 1,2,3,4 | W-phase high-side collector | CN22 | 1,2,3,4 | W-phase low-side collector |

| CN24 | 1,3     | W-phase high-side gate      | CN23 | 1,3     | W-phase low-side gate      |

|      | 2,4     | W-phase high-side emitter   |      | 2,4     | W-phase low-side emitter   |

| CN18 | 1,3     | V-phase high-side gate      | CN12 | 1,3     | Temperature detection 1    |

|      | 2,4     | V-phase high-side emitter   |      | 2,4     | Temperature detection 2    |

| CN20 | 1,2,3,4 | V-phase high-side collector | CN15 | 1,3     | U-phase low-side gate      |

| CN16 | 1,3     | U-phase high-side gate      |      | 2,4     | U-phase low-side emitter   |

|      | 2,4     | U-phase high-side emitter   | CN14 | 1,2,3,4 | U-phase low-side collector |

| CN13 | 1,2,3,4 | U-phase high-side collector | CN19 | 1,3     | V-phase low-side gate      |

|      |         |                             |      | 2,4     | V-phase low-side emitter   |

|      |         |                             | CN17 | 1,2,3,4 | V-phase low-side collector |

|      |         |                             | CN26 | 1,3     | Brake gate                 |

|      |         |                             |      | 2,4     | Brake emitter              |

|      |         |                             | CN25 | 1,2,3,4 | Brake collector            |

#### Table 4.3 Specifications of Power Module Connectors

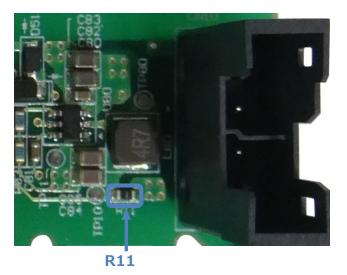

### 4.4. Jumper Resistors for External 5V (R10, R11)

An external 5V is applied to Pin23 and Pin25 of CN11, which can be used instead of the internal voltage. The jumper resistors (R10, R11) are then implemented as shown in Table4.4.

**R10**

#### Fig. 4.4 Jumper Resistor for External 5V

#### Table 4.4 Mounting Specifications for Jumper Resistors

|           |                               | -                             |

|-----------|-------------------------------|-------------------------------|

| Component | Internal 5V power use         | External 5V application       |

| R10       | Not Mount                     | Mount ( $0\Omega$ resistance) |

| R11       | Mount ( $0\Omega$ resistance) | Not Mount                     |

### 5. Operation

#### 5.1. Operation Check

This section explains the operation of the circuit board alone and the power module connection status.

#### 5.1.1. Operation Check of the Board Alone

Power module is not connected in this operation check. The operation checking details are as follows.

- (1) Internal 5V output and isolated power supply output

- (2) Gate-drive output and error detection signal output when DESAT detection is enabled

- (3) Gate-drive output and error detection signal output when DESAT detection is disabled

(1)Check 5V output and isolated power output.

Insert the socket with lead into CN10 and the socket with flat cable into CN11 to turn on the 24V power supply for control of CN10.

Check that 5V regulator output and isolated DC-DC power output are as shown in Table 5.1.

| Item                          | Item                          |         |                                     |                                     |

|-------------------------------|-------------------------------|---------|-------------------------------------|-------------------------------------|

| Internal 5V power             | Internal 5V power             |         |                                     |                                     |

| For U-phase gate drive        |                               |         | TP16 (+)-TP17 (-):<br>Orange circle |                                     |

| For V-phase gate drive        | Positive<br>supply<br>voltage | 16V±5%  | TP19 (+)-TP20 (-):<br>Blue circle   |                                     |

| For W-phase gate drive        |                               | 1001370 | TP26 (+)-TP27 (-):<br>Black circle  |                                     |

| For driving the low-side gate |                               |         | TP33 (+)-TP34 (-):<br>Purple round  |                                     |

| For U-phase gate drive        |                               |         |                                     | TP18 (+)-TP17 (-):<br>Orange circle |

| For V-phase gate drive        | Negative                      | -8V±5%  | TP21 (+)-TP20 (-):<br>Blue circle   |                                     |

| For W-phase gate drive        | supply<br>voltage             | -0113%  | TP28 (+)-TP27 (-):<br>Black circle  |                                     |

| For driving the low-side gate |                               |         | TP35 (+)-TP34 (-):<br>Purple round  |                                     |

#### Table 5.1 Operation Check

Fig. 5.1 Measurement Positions for Checking Operation

(2)Check of gate-drive output and error detection signal output when DESAT is detected Apply voltage to the gate control signal pin and enable signal pin according to Table 5.2, and check the gate drive output and error detection output.

| Iab                 | Table 5.2 Checking High-Side and Low-Side Operation |                           |                 |  |  |  |  |

|---------------------|-----------------------------------------------------|---------------------------|-----------------|--|--|--|--|

| Gate control signal |                                                     | Gate drive output voltage | Error detection |  |  |  |  |

| Input voltage       | Input voltage                                       | Cate anve output voltage  | output voltage  |  |  |  |  |

| No-input or 0V      | No-input or 5V                                      |                           | 5V              |  |  |  |  |

| 5V                  | No-input of 5V                                      | -8.0V±5%                  | 0V              |  |  |  |  |

| No-input or 0V      | 0V                                                  | -0.07±3%                  | 5V              |  |  |  |  |

| 5V                  | 0 v                                                 |                           | 20              |  |  |  |  |

Table 5.2 Checking High-Side and Low-Side Operation

Since a pull-down resistor is mounted on the gate control signal input pin, the gate drive output is turned-8.0V even if the gate control signal is not input.

The enable signal input pin has a pull-up resistor inside, when no signal input, it is a high level. To set it to a low level, input a 0V signal.

Refer to Table 4.1 for the input voltage application terminals.

<Gate drive output measurement location>

•Voltage between Pin1 (3) and Pin2 (4) on the connectors below

CN16 (U-phase high-side), CN18 (V-phase high-side), CN24 (W-phase high-side),

CN15 (U-phase low-side), CN19 (V-phase low-side), CN23 (W-phase low-side),

CN26 (braking)

<Error detection output measurement location>

- •Error detection output pin: Voltage between Pin15(FAULT) and Pin2 of CN11

- (3) Checking gate-drive output and error-detection-signal output when no DESAT is detected After turning OFF the control power supply, short-circuit the gate-drive-output and DESAT detection connectors with lead clips, etc. as shown in Table 5.3. Turn on the control power supply voltage 24V again, apply a voltage to the gate control signal input pin and enable signal input pin according to Table 5.4, and check the gate drive output and error detected output.

| Phase             | Connectors to be shorted |           |  |

|-------------------|--------------------------|-----------|--|

| U-phase high-side | CN16/2pin                | CN13/1pin |  |

| U-phase low-side  | CN15/2pin                | CN14/1pin |  |

| V-phase high-side | CN18/2pin                | CN20/1pin |  |

| V-phase low-side  | CN19/2pin                | CN17/1pin |  |

| W-phase high-side | CN24/2pin                | CN21/1pin |  |

| W-phase low-side  | CN23/2pin                | CN22/1pin |  |

| Brake             | CN26/2pin                | CN25/1pin |  |

**Table 5.3 Short Positions**

Refer to Fig. 4.3 for the connector position and terminal arrangement to be shorted.

| Table of Feldening high blac and Loth blac operation |                                |                           |                                   |  |  |  |

|------------------------------------------------------|--------------------------------|---------------------------|-----------------------------------|--|--|--|

| Gate control signal<br>Input voltage                 | Enable signal<br>Input voltage | Gate drive output voltage | Error detection<br>output voltage |  |  |  |

| No-input or OV                                       | Non-input or 5V                | -8.0V±5%                  |                                   |  |  |  |

| 5V                                                   | Non input of 5V                | 16V±5%                    | 5V                                |  |  |  |

| No-input or 0V                                       | 0V                             | -8.0V±5%                  | 24                                |  |  |  |

| 5V                                                   |                                |                           |                                   |  |  |  |

Table 5.4 Checking High-Side and Low-Side Operation

Terminals input to the gate control signal and enable signal in Table 5.4 and measurement locations of gate drive output and error detection output are the same as those described in Table 5.2.

When the board is confirmed as normal, proceed with "Power Module Connection Operation Check".

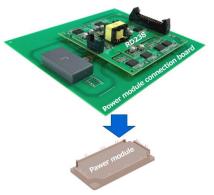

#### 5.1.2. Power Module Connection Operation Check

Connect this design, the converter board for connecting the power module, and the power module, and apply 24V to CN10. Then, apply high voltage to the power module.

When a gate control signal (low-side or high-side) is input from an external controller to CN11 of this design, the connected power module will switch based on the gate control signal.

When operating the power module complementarily, the gate control signals on the high-side and low-side must have a dead-time. Never operate the power module on the high-side and low-side simultaneously (arm short-circuit).

This design does not have a dead-time generation function.

<Reference>

Fig. 5.2 shows the connection example of this design, the Power module connection board, and the power module.

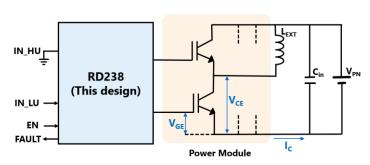

Fig. 5.3 shows the measurement block diagram.

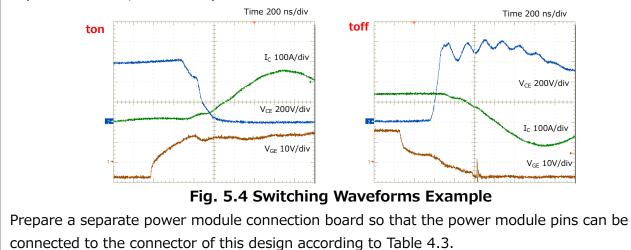

Fig. 5.4 shows the switching waveform example (U-phase low-side) when a power module is connected.

Fig. 5.3 Measurement Block Diagram

#### Fig. 5.2 Connection Example of a Power Module Connection Board

Measuring conditions:  $V_{PN}$  = 600 V,  $I_D$  =150 A, Inductive-load  $L_{EXT}$  = 200µH,  $T_a$  = 25°C, U-phase low-side, Cin = 0.22µF

#### 5.1.3. Each Protection Function

The protection functions include DESAT detection for overcurrent protection/short-circuit protection, under voltage lock out (UVLO) of gate-voltage for overheat protection of the power module, and active miller clamp for self-turn-on protection. Only when DESAT detector operates, the gate-drive voltage is soft-shut down, and FAULT signal of Pin15 of CN11 becomes L-level. Then, FAULT is returned to H-level automatically by function of TLP5222. Each protection operation is as follows.

(1) UVLO (Under Voltage Lock Out)

Prerequisites: For gated input signal (5V applied) and enable input signal (open or 5V applied), the same operation is performed on 7 channels.

- V<sub>UVLO-</sub> (Gated Positive Power UVLO Detect) If VCC2 - VE is reduced from normal operation (VCC2 - VE = 16V), UVLO runs in VCC2 - VE < 10V (Typ.) and the gate-drive-voltage is turned VE - VEE = -8.0V to turn off the power module.

- ②  $V_{UVLO+}$  (Gated Positive Power UVLO Cancel) If VCC2-VE is increased, UVLO is released at VCC2 - VE > 11.4V (Typ.), the gate-drive-voltage is turned VCC2 - VE = 16V, and the power module is turned on.

- (2) Overcurrent protection by detecting DESAT (UVLO is inactive)

- 5V is applied to Pin1 of CN11 and the gate-drive-voltage is normally turned on. (normal operation)

- ② DESAT detection operates in comparing the DESAT pin voltage, which changes based on collector-emitter voltage, and DESAT threshold voltage (6.6V (Typ.)).

- ③ When the DESAT pin voltage exceeds the DESAT threshold voltage of 6.6V (Typ.), it detects the overcurrent and initiates the protection operation.

- ④ Soft shutdown (gradual OFF transition) of the gate-drive voltage to turn off the power module.

- ⑤ Error detection signal (FAULT signal) changes from 5V to 0V to notify the error.

- (3) Prevention of malfunction by active miller clamp

If noise is applied externally to the capacitive component that exists between the collector and gate of the power module, an unintended current is generated, causing malfunction. The active miller clamp prevents this malfunction.

### 5.2. Adjusting Circuits

#### 5.2.1. Adjusting the Gate Resistance

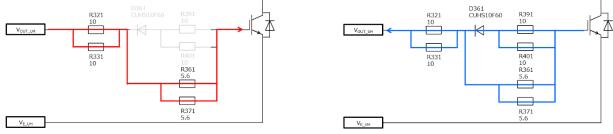

This design implements a forward diode in the turn-off current path. You can adjust the turn-on and turn-off times to match the actual specifications. Adjust while paying attention to the operation and heat generation of each component. Table 5.5 shows the resistor specifications implemented in this design.

Fig. 5.5 Gate Resistance Configuration Diagram of Turn-on / Turn-off

| Component<br>Number | Configuration | Resistance<br>at turn-on | Resistance<br>at turn-off | Resistance Specifications |  |  |

|---------------------|---------------|--------------------------|---------------------------|---------------------------|--|--|

| R32x                | Parallel      | $\checkmark$             | $\checkmark$              | Rectangular chip resistor |  |  |

| R33x                | Faraller      | $\checkmark$             | $\checkmark$              | (0.5Ŵ,10Ω,2012mm)         |  |  |

| R36x                | Parallel      | $\checkmark$             | $\checkmark$              | Rectangular chip resistor |  |  |

| R37x                | Parallel      | $\checkmark$             | $\checkmark$              | (0.5W,5.6Ω,2012mm)        |  |  |

| R39x                | Parallel      | _                        | $\checkmark$              | Rectangular chip resistor |  |  |

| R40x                | Parallel      | _                        | ~                         | (0.5Ŵ,10Ω,2012mm)         |  |  |

#### Table 5.5 Gate Resistance Specifications

Component number suffix indicates the number of each phase as shown below.

U-phase high-side : 1, V-phase high-side : 2, W-phase high-side : 3

U-phase low-side: 4, V-phase low-side: 5, W-phase low-side: 6, Braking: 7

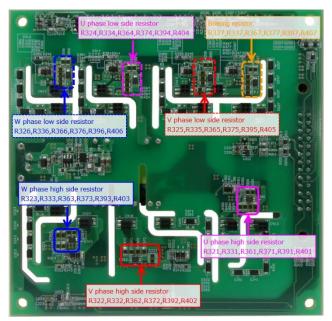

Fig. 5.6 Gate Resistor Layout

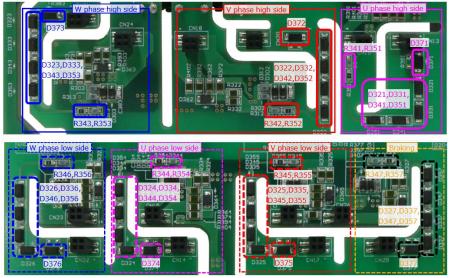

# 5.2.2. Adjusting DESAT Detection Voltage (R34x, R35x, D32x, D33x, D34x, D35x, D37x)

This design has  $R34x = 820\Omega / R35x = 0\Omega$ , high withstand voltage diodes at D32x/D33x/D34x/D35x, and a zener diode at D37x. DESAT detection voltage can be changed by adjusting the resistor value, number of high withstanding voltage diodes in series, and zener voltage according to the actual specifications.

Fig. 5.7 DESAT Detection Resistor Layout

### 5.2.3. Adjusting DESAT Detection Duration (C38x, R31x)

This design includes a 100pF blanking capacitor (C38x) and a  $30k\Omega V_{OUT}$ -DESAT resistor (R31x). Set the protective function in C38x and R31x within the short-circuit withstand time of the power module.

Fig. 5.8 Blanking Capacitor Layout

#### 5.2.4. Adjusting the Input-Signal RC Filter (C20x/R21x)

This design has a RC filter (C20x = 470pF, R21x =  $1k\Omega$ ) mounted on the gate-control input to prevent malfunction due to external noises.

Adjust the filter constant to increase the noise suppression effect according to the actual environment.

Fig. 5.9 RC Filter Layout

#### 5.3. Precautions

Pay special attention to the following when operating.

- $\boldsymbol{\cdot}$  Make sure that the polarities of the connectors and terminals are correct before supplying power.

- High voltage is applied to the smoothing capacitor, and it takes time to fully discharge the capacitor even after the power is turned off. Make sure that the capacitor is sufficiently discharged before touching the BOARD.

- When checking the operation, cover the BOARD with an acrylic case for safety.

- MOSFETs and other components generate heat during operation. Be careful not to get burned when handling them.

#### Terms of Use

This terms of use is made between Toshiba Electronic Devices and Storage Corporation ("We") and Customer who downloads or uses this Reference Design. Customer shall comply with this terms of use. This Reference Design means all documents and data in order to design electronics applications on which our semiconductor device is embedded.

#### Section 1. Restrictions on usage

1. This Reference Design is provided solely as reference data for designing electronics applications. Customer shall not use this Reference Design for any other purpose, including without limitation, verification of reliability.

2. Customer shall not use this Reference Design for sale, lease or other transfer.

3. Customer shall not use this Reference Design for evaluation in high or low temperature, high humidity, or high electromagnetic environments.

4. This Reference Design shall not be used for or incorporated into any product or system whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

#### Section 2. Limitations

1. We reserve the right to make changes to this Reference Design without notice.

2. This Reference Design should be treated as a reference only. WE ARE NOT RESPONSIBLE FOR ANY INCORRECT OR INCOMPLETE DATA AND INFORMATION.

3. Semiconductor devices can malfunction or fail. When designing electronics applications by referring to this Reference Design, Customer is responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of semiconductor devices could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Customer must also refer to and comply with the latest versions of all relevant our information, including without limitation, specifications, data sheets and application notes for semiconductor devices, as well as the precautions and conditions set forth in the "Semiconductor Reliability Handbook".

4. Designing electronics applications by referring to this Reference Design, Customer must evaluate the whole system sufficiently. Customer is solely responsible for applying this Reference Design to Customer's own product design or applications. WE ASSUME NO LIABILITY FOR CUSTOMER'S PRODUCT DESIGN OR APPLICATIONS.

5. WE SHALL NOT BE RESPONSIBLE FOR ANY INFRINGEMENT OF PATENTS OR ANY OTHER INTELLECTUAL PROPERTY RIGHTS OF THIRD PARTIES THAT MAY RESULT FROM THE USE OF THIS REFERENCE DESIGN. NO LICENSE TO ANY INTELLECTUAL PROPERTY RIGHT IS GRANTED BY THIS TERMS OF USE, WHETHER EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE.

6. THIS REFERENCE DESIGN IS PROVIDED "AS IS". WE (a) ASSUME NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (b) DISCLAIM ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO THIS REFERENCE DESIGN, INCLUDING WITHOUT LIMITATION, WARRANTIES OR CONDITIONS OF FUNCTION AND WORKING, WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

#### Section 3. Terms and Termination

It is assumed that Customer agrees to any and all this terms of use if Customer downloads or uses this Reference Design. We may, at its sole and exclusive discretion, change, alter, modify, add, and/or remove any part of this terms of use at any time without any prior notice. We may terminate this terms of use at any time and without any cause. Upon termination of this terms of use, Customer shall eliminate this Reference Design. Furthermore, upon our request, Customer shall submit to us a written confirmation to prove elimination of this Reference Design.

#### Section 4. Export Control

Customer shall not use or otherwise make available this Reference Design for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). This Reference Design may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Act and the U.S. Export Administration Regulations. Export and re-export of this Reference Design is strictly prohibited except in compliance with all applicable export laws and regulations.

#### Section 5. Governing Laws

This terms of use shall be governed and construed by laws of Japan, without reference to conflict of law principle.

#### Section 6. Jurisdiction

Unless otherwise specified, Tokyo District Court in Tokyo, Japan shall be exclusively the court of first jurisdiction for all disputes under this terms of use.