# 車載用ブラシ付き DC モーター制御回路 (TB9103FTG 使用)デザインガイド

RD245-DGUIDE-01

東芝デバイス&ストレージ株式会社

# 目次

| 1.   | はじめに                                     | 3 |

|------|------------------------------------------|---|

| 2.   | 仕様とブロック図                                 | 4 |

| 3.   | 主な使用部品!                                  | 5 |

| 3.1. | 車載用 2ch Half-bridge ゲートドライバーIC TB9103FTG | 5 |

| 3.2. | パワーMOSFET XPN7R104NC                     | 6 |

| 3.3. | パワーMOSFET XPH3R304PS                     | 7 |

| 3.4. | パワーMOSFET XPH1R104PS                     | 8 |

| 3.5. | MOSFET SSM3J66MFV                        | 8 |

| 3.6. | ボルテージレギュレーター TB9005FNG                   | 9 |

| 4.   | 回路設計                                     | 0 |

| 4.1. | 電源回路 1                                   | 0 |

| 4.2. | モーター駆動ブリッジ回路1                            | 2 |

| 4.3. | 制御入力信号回路1                                | 3 |

| 4.4. | 出力信号回路                                   | 4 |

| 4.5. | 逆接続保護回路                                  | 5 |

# 1. はじめに

本デザインガイド (以下、本ガイド) では、TB9103FTGを使用した車載用ブラシ付きDCモーター制御回路のリファレンス デザイン (以下、本デザイン) について説明します。

現在、ブラシ付きDCモーターは自動車のドア、窓、シートなどの駆動回路に広く用いられています。東芝の自動車用2ch Half-bridgeゲートドライバーIC TB9103FTGはより良いモーター制御のための多くの機能を備えています。Half-bridge modeで2台のモーターを、またはH-bridge modeで1台のモーターを制御するために使用でき、デッドタイム制御機能、さまざまな異常検出機能および異常検出信号出力機能はモーター動作のより安全な実装に役立ちます。さらに、入力電圧範囲が広いためさまざまな用途に適しています。また、小型のQFN24パッケージ(4 × 4mm)を採用しコンパクトな実装が可能です。

本デザインはTB9103FTGのさまざまな機能を簡単にテストおよび評価するのに役立ちます。 モーター制御には基板上のスイッチによるマニュアル制御と、外付けMCU(マイクロコントローラーユニット)を用いたMCU制御の2通りが可能です。また、本デザインは2種のモーター駆動用パワーMOSFETをテストするためのオプションを用意しています。パワーMOSFET XPN7R104NCおよびXPH3R304PSはそれぞれ10Aと20Aの大電流制御に使用します。 加えて、本デザインに電源を逆方向で接続してしまった際に機能する逆方向接続保護回路にパワーMOSFET XPH1R104PSを使用します。また、本デザイン中の5V電源としてTB9005FNGを使用します。この5V電源は外付けMCUの電源に用いることができ、TB9005FNGの低電圧リセット、パワーオンリセット、ウオッチドッグタイマー機能はMCU制御に役立ちます。

2024-10-23

# 2. 仕様とブロック図

本デザインの主な仕様を表 2.1 に示します。

表 2.1 本デザインの仕様

| 項目          | 仕様                               |  |  |

|-------------|----------------------------------|--|--|

| 入力電源電圧      | DC 8∼18V                         |  |  |

| 制御信号電圧      | DC 5V                            |  |  |

| 出力電流        | 10A (Max.) XPN7R104NC MOSFET 使用時 |  |  |

| 山刀电机        | 20A (Max.) XPH3R304PS MOSFET 使用時 |  |  |

| 制御モータータイプ   | ブラシ付き DC モーター                    |  |  |

| モーター制御モード   | Half-bridge mode および             |  |  |

| C—2—шлт С—1 | H-bridge mode                    |  |  |

| 基板サイズ       | 75mm x 75mm                      |  |  |

| 基板レイヤ−構成    | 4 層基板 (1 層あたり 35µm)              |  |  |

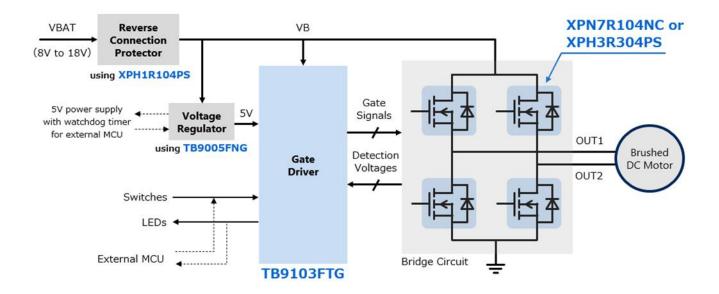

本デザインのブロック図を図 2.1 に示します。

図 2.1 本デザインのブロック図

# 3. 主な使用部品

この章では本デザインに使用している主な部品について説明します。東芝は本デザインに使用しているものを含めて幅広い パワー半導体、ドライバーカプラー、レギュレーターのラインアップを取りそろえています。

# 3.1. 車載用 2ch Half-bridge ゲートドライバーIC TB9103FTG

本デザインは MOSFET を介したブラシ付き DC モーター制御のために TB9103FTG を使用しています。

# 特長

- 制御モードを2モード搭載: Half-bridge mode、H-bridge mode

- 2chの独立したHalf-bridgeとして使用可能

- chごとにデッドタイム制御、シャットダウン制御

- 低電力スリープモード

- 各種異常検出搭載:

- > VB低電圧検出、VCC低電圧検出、VCP高電圧検出

- ▶ ゲート-ソース間電圧検出、ゲート電圧異常時シャットダウン

- ▶ ドレイン-ソース間電圧検出、過電流シャットダウン

- 過熱検出、シャットダウン

- ▶ 異常検出時オープンドレイン出力から通知

- 動作電圧範囲: 7~18V

- AEC-Q100 Rev-J: グレード1

- 小型パッケージ QFN24 (4mm x 4mm)

#### 外観と端子配置図

18 17 16 15 14 13 nSLEEP 19 12 SL1 GND 20 11 GL1 10 SH1 IN1 21 E-PAD IN2 22 9 GH1 IN3 23 8 DH IN4 24 GH2 1 2 3 4 5 6 DIAG1 DIAG2 SL2 GL2 SH2

© 2024

# 3.2. パワーMOSFET XPN7R104NC

本デザインはモーター制御に使用するパワーMOSFET に XPN7R104NC または XPH3R304PS のどちらかを選択できます。 この節では XPN7R104NC について説明します。

## 特長

- AEC-Q101適合

- 小型、薄型で実装面積が小さい。: TSON Advance(WF)

- オン抵抗が低い。: R<sub>DS(ON)</sub> = 5.6mΩ (Typ.) (V<sub>GS</sub> = 10V)

- ドレイン電流: I<sub>D</sub> = 20A (Max.)

- 漏れ電流が低い。: I<sub>DSS</sub> = 10µA (Max.) (V<sub>DS</sub> = 40V)

- 取り扱いが簡単な、エンハンスメントタイプです。:  $V_{th} = 1.5 \sim 2.5 \text{V}$  ( $V_{DS} = 10 \text{V}$ ,  $I_{D} = 0.2 \text{mA}$ )

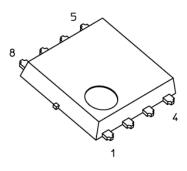

# 外観と内部回路構成図

TSON Advance(WF)

1, 2, 3: Source

4: Gate

5, 6, 7, 8: Drain

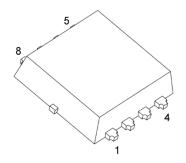

# 3.3. パワーMOSFET XPH3R304PS

本デザインはモーター制御に使用するパワーMOSFET に XPN7R104NC または XPH3R304PS のどちらかを選択できます。 この節では XPH3R304PS について説明します。

# 特長

- AEC-Q101適合

- 小型、薄型で実装面積が小さい。: SOP Advance(WF)

- オン抵抗が低い。: R<sub>DS(ON)</sub> = 2.5mΩ (Typ.) (V<sub>GS</sub> = 10V)

- ドレイン電流: I<sub>D</sub> = 60A (Max.)

- 漏れ電流が低い。: I<sub>DSS</sub> = 10µA (Max.) (V<sub>DS</sub> = 40V)

- 取り扱いが簡単な、エンハンスメントタイプです。:  $V_{th} = 2.0 \sim 3.0 \text{V}$  ( $V_{DS} = 10 \text{V}$ ,  $I_{D} = 0.2 \text{mA}$ )

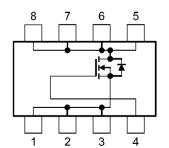

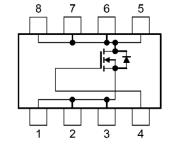

## 外観と内部回路構成図

SOP Advance(WF)

1, 2, 3: Source

4: Gate

5, 6, 7, 8: Drain

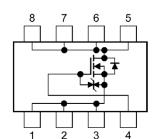

# 3.4. パワーMOSFET XPH1R104PS

本デザインは逆方向接続保護回路に大電流向けパワーMOSFET XPH1R104PS を使用しています。

# 特長

- AEC-Q101適合

- 小型、薄型で実装面積が小さい。: SOP Advance(WF)

- オン抵抗が低い。: R<sub>DS(ON)</sub> = 0.95mΩ (Typ.) (V<sub>GS</sub> = 10V)

- ドレイン電流: I<sub>D</sub> = 120A (Max.)

- 漏れ電流が低い。: I<sub>DSS</sub> = 10µA (Max.) (V<sub>DS</sub> = 40V)

- 取り扱いが簡単な、エンハンスメントタイプです。:  $V_{th} = 2.0 \sim 3.0 \text{V}$  ( $V_{DS} = 10 \text{V}$ ,  $I_{D} = 0.5 \text{mA}$ )

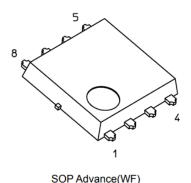

#### 外観と内部回路構成図

1, 2, 3: Source

4: Gate

5, 6, 7, 8: Drain

3.5. MOSFET SSM3J66MFV

本デザインは LED の点灯制御に P チャネル MOSFET SSM3J66MFV を使用しています。

#### 特長

- AEC-Q101適合

- 1.2V駆動

- オン抵抗が低い。: R<sub>DS(ON)</sub> = 390mΩ (Typ.) (V<sub>GS</sub> = -4.5V)

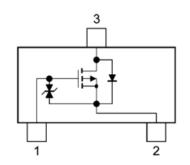

## 外観と端子配置図

- 1. Gate

- 2. Source

- 3. Drain

© 2024

2024-10-23

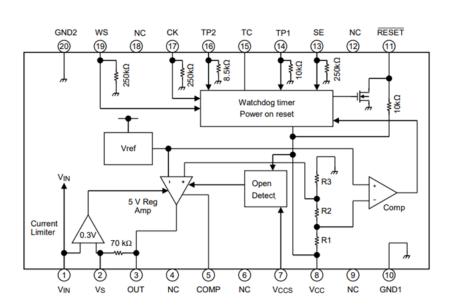

# 3.6. ボルテージレギュレーター TB9005FNG

本デザインは 5V 電源にボルテージレギュレーターTB9005FNG を使用しています。また、本デザインはオプションとして CN4 を介して外付けマイクロコントローラーに 5V 給電することが可能です。

#### 特長

● 出力電圧:5.0V±0.1V(-40~125℃)

● 低消費電流: 90µA (V<sub>IN</sub> = 12V, T<sub>a</sub> = 25℃) @ 5V定電圧出力 + リセットタイマー

リセットファンクション:低電圧監視/パワーオンリセット/ウオッチドッグタイマー

● 電流リミッター内蔵:外部抵抗調整可

● 動作温度範囲:-40~125℃

● Vcc断線 (オープン) 検出機能付き

● 小型フラットパッケージ: SSOP-20pin (0.65mmピッチ)

### 外観と端子配置図

車載対応品の認証についての詳細は当社の営業担当までお問い合わせください。

# 4. 回路設計

この章では本デザインの回路の要点について解説します。回路図は RD245-SCHEMATIC-xx.pdf を、部品表は RD245-BOM-xx.pdf を参照ください。 本デザインのブロック図は図 2.1 に示しています。

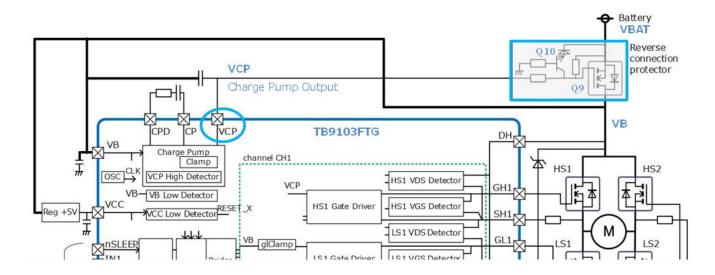

# 4.1. 電源回路

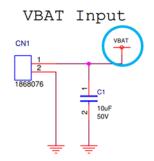

VBAT 電源回路の回路図を図 4.1 に示します。バッテリー電源 (VBAT) は本デザインの主電源であり、電源入力端子 CN1 から入力されます。図 2.1 および図 4.2 に示すように VBAT 電源は逆接続保護回路を介して VB 電源を生成します。 この VB 電源は TB9103FTG に供給され、パワーMOSFET で構成されるブリッジ回路を介してモーター駆動に用いられます。 VBAT に入力可能な電圧範囲は 8~18V です。

図 4.1 VBAT 電源回路

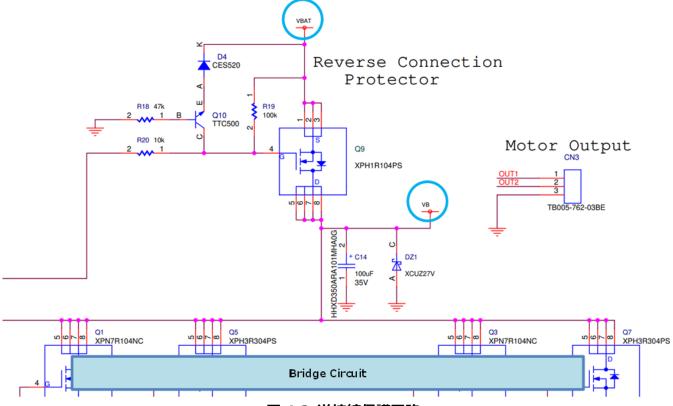

図 4.2 逆接続保護回路

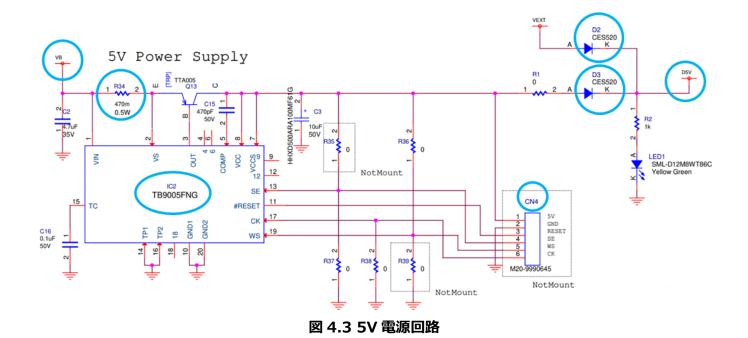

5V 電源回路の回路図を図 4.3 に示します。5V 電源 (D5V) は VB から TB9005FNG を介して生成され TB9103FTG に供給されます。D5V は LED の動作や nSLEEP, IN1, MODE, DIAG1 などの本デザインにおける各種信号のプルアップに用いられます。LED1 (黄緑) は D5V が供給されると点灯します。

本デザインはオプションとして外付け MCU 接続端子 (CN2) からも 5V 電源 (VEXT) を供給できます。VEXT はダイオード D2 および D3 を介して 5V 出力に接続されており、両電源が同時に印加された場合に大電流が流れるのを防ぎます。本デザインは抵抗 R1 を取り外すことで 5V 電源回路を使用しないオプションも用意しています。

TB9005FNG は過電流保護機能を備えており、電流検出抵抗 (R34) を使用して電流を制限します。図 4.3 に示すように、R34 は VIN 端子と VS 端子の間に接続されています。R34 の最大降下電圧は 0.3V です。 本デザインでは R34 が 470m $\Omega$ であるため、制限電流値は 0.3V/470m $\Omega$  = 0.638A となります。

TB9005FNG の 5V 出力は CN4 を介して外付け MCU へ供給することもできます。また、TB9005FNG は低電圧リセット、パワーオンリセット、ウオッチドッグタイマーなどのリセット機能を備えており、外付け MCU にリセット信号を出力できます。詳細は本デザインのリファレンスガイドおよび TB9005FNG のデータシートを参照ください。

注:対象アプリケーションに必要な電力に応じて、5V電圧レギュレーター回路の適切な熱設計を行う必要があります。

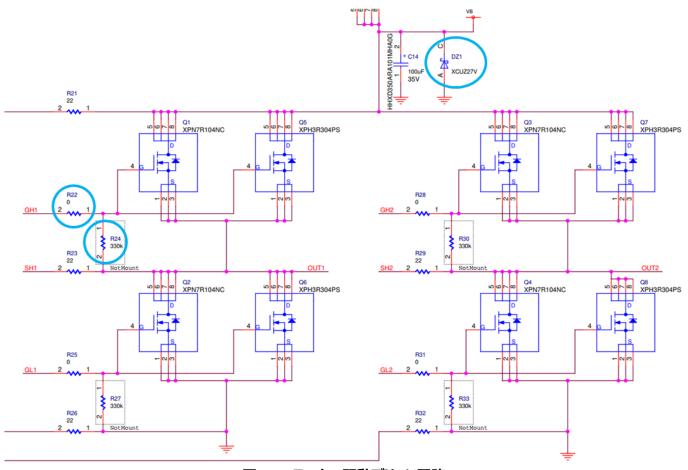

# 4.2. モーター駆動ブリッジ回路

モーター駆動ブリッジ回路の回路図を図 4.4 に示します。本デザインはパワーMOSFET で構成した H-bridge 回路をゲートドライバーIC TB9103FTG によって制御することでブラシ付き DC モーターの駆動を行います。モーター駆動ブリッジ回路に使用するパワーMOSFET は XPN7R104NC または XPH3R304PS の定格電流が異なる 2 種類から選択できます。 XPN7R104NC は TSON Advance(WF) パッケージ、XPH3R304PS は SOP Advance(WF) パッケージの製品です。

TB9103FTG の各ゲート駆動出力端子には 150kΩのプルダウン抵抗が内蔵されています。これに加えて本デザインでは R24 (標準では未実装) のような外部プルダウン抵抗を追加することができます。TB9103FTG と各 MOSFET のゲートとの 間には R22 のような直列抵抗が接続されてあり、MOSFET のターンオンおよびターンオフの時間に影響するゲートの充放電速 度を決定します。したがって、これらの直列抵抗を変更することでターンオンおよびターンオフの時間をアプリケーションの要件に応じたものに調整できます。各 MOSFET の VDS および VGS は TB9103FTG に監視され、異常があれば検出されます。

図 4.4 モーター駆動ブリッジ回路

ツェナーダイオード XCUZ27V (DZ1) はモーターの駆動による電圧変動を制限するために使用します。また、コンデンサー C14 は VB 電源電圧を安定させるために使用します。

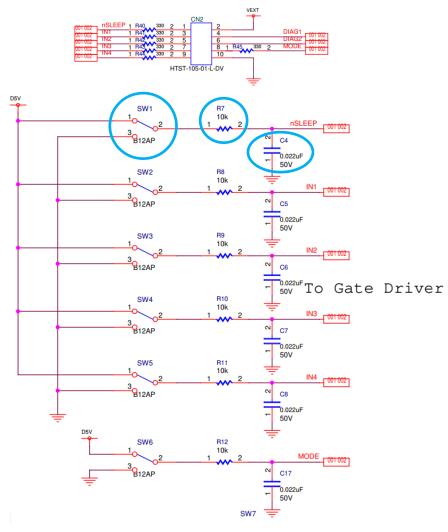

#### 4.3. 制御入力信号回路

入力信号 nSLEEP, IN1, IN2, IN3, IN4, MODE はモーター制御に使用します。本デザインではこれらの信号を制御するのにトグルスイッチ SW1~6 を使用する、または CN2 に接続した外付け MCU を使用する 2 通りの方法があります。本デザインの操作方法についての詳細はリファレンスガイド (RD245-RGUIDE-xx.pdf) の操作説明を参照ください。

制御入力信号回路の回路図を図 4.5 に示します。本デザインの回路では CN2 を介した外付け MCU からの入力信号がスイッチ SW1~6 からのものよりも優先されます。 nSLEEP 信号を例にすると、外付け MCU 未接続時には nSLEEP 信号はSW1 によって制御され、接続時には SW1 の状態にかかわらず nSLEEP は外付け MCU によって制御されます。 この仕様は $10k\Omega$ の直列抵抗 R7~12 によって外付け MCU の出力インピーダンスが SW1~6 のものよりも低くすることで設計しています。 コンデンサーC4~8 および C17 は SW1~6 のチャタリングによって生じる意図しない信号変化を除去するのに使用します。 他の入力信号も同様にして制御されます。

図 4.5 制御入力信号回路

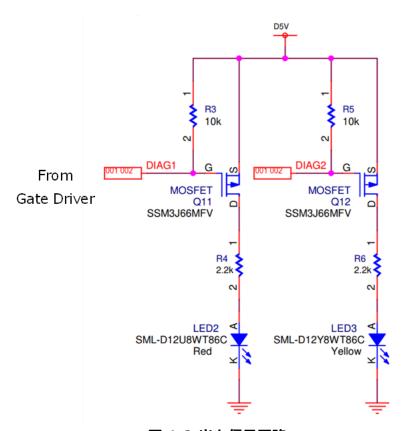

# 4.4. 出力信号回路

出力信号回路の回路図を図 4.6 に示します。TB9103FTG の出力信号 DIAG1 および DIAG2 の状態が LED2 (赤) および LED3 (黄) の点灯・消灯によって示されます。各出力信号は CN2 を介して外付け MCU で監視することも可能です。

各出力信号はアクティブ Low であり、それぞれが Low になると P チャネル MOSFET を使用したハイサイドスイッチ Q11 および Q12 がオンされて対応する LED が点灯します。異常検出の概要を表 4.1 に示します。異常検出についての詳細は TB9103FTG のデータシートを参照ください。

図 4.6 出力信号回路

表 4.1 異常検出の概要

| LED2<br>(DIAG1) | LED3<br>(DIAG2) | DIAG1<br>状態 | DIAG2<br>状態 | 検出された異常    |

|-----------------|-----------------|-------------|-------------|------------|

| オン              | オフ              | Low         | High        | CH1 での異常   |

| オフ              | オン              | High        | Low         | CH2 での異常   |

| オン              | オン              | Low         | Low         | 両チャンネルでの異常 |

| オフ              | オフ              | High        | High        | -          |

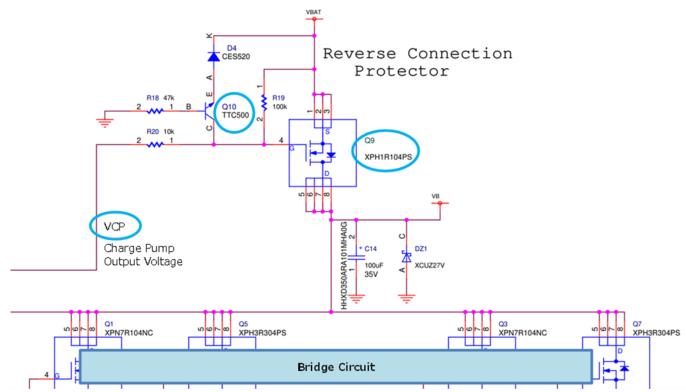

### 4.5. 逆接続保護回路

逆接続保護回路は CN1 に VBAT 電源を誤って逆方向に接続した際に本デザインを保護する回路です。逆接続保護回路の概観を図 4.7 に、回路図を図 4.8 にそれぞれ示します。この回路では 120A 大電流パワーMOSFET XPH1R104PSを保護機能のスイッチとして使用します。

図 4.7 逆接続保護回路の概観

CN1 に電源が正しい方向で接続された場合、MOSFET Q9 がオンするまで、Q9 のボディーダイオードに電流が流れます。 ゲートドライバーIC TB9103FTG の VCP 端子にはチャージポンプによって高電圧が生成されます。 この VCP 電圧が VBAT 電源電圧に対して Q9 の VGS 電圧のしきい値以上に上回るため Q9 がオンします。 この間、トランジスターQ10 はベース電圧がエミッター電圧を下回るためオフしています。 このようにして、正しい接続がなされた場合、Q9 は常にオン状態であり本デザインは通常動作します。

CN1 に電源が逆方向で接続された場合、電源の高電圧側が本デザインの GND に接続され、低電圧側が VBAT に接続されるため、GND が VBAT よりも高電圧になります。この場合、MOSFET Q9 のボディーダイオードが逆バイアスされ電流を遮断し、トランジスターQ10 はベース-エミッター間が順方向バイアスとなるためオンします。この間、Q9 は VGS 電圧が非常に低くなるためオフします。このようにして、逆方向接続がなされた場合、Q9 は常にオフ状態であり本デザインを保護します。

図 4.8 逆接続保護回路

# ご利用規約

本規約は、お客様と東芝デバイス&ストレージ株式会社(以下「当社」といいます)との間で、当社半導体製品を搭載した機器を設計する際に参考となるドキュメント及びデータ(以下「本リファレンスデザイン」といいます)の使用に関する条件を定めるものです。お客様は本規約を遵守しなければなりません。

#### 第1条 禁止事項

お客様の禁止事項は、以下の通りです。

- 1. 本リファレンスデザインは、機器設計の参考データとして使用されることを意図しています。信頼性検証など、それ以外の目的には使用しないでください。

- 2. 本リファレンスデザインを販売、譲渡、貸与等しないでください。

- 3. 本リファレンスデザインは、高低温・多湿・強電磁界などの対環境評価には使用できません。

- 4. 本リファレンスデザインを、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用しないでください。

### 第2条 保証制限等

- 1. 本リファレンスデザインは、技術の進歩などにより予告なしに変更されることがあります。

- 2. 本リファレンスデザインは参考用のデータです。当社は、データ及び情報の正確性、完全性に関して一切の保証をいたしません。

- 3. 半導体素子は誤作動したり故障したりすることがあります。本リファレンスデザインを参考に機器設計を行う場合は、誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウェア・ソフトウェア・システムに必要な安全設計を行うことをお願いします。また、使用されている半導体素子に関する最新の情報(半導体信頼性ハンドブック、仕様書、データシート、アプリケーションノートなど)をご確認の上、これに従ってください。

- 4. 本リファレンスデザインを参考に機器設計を行う場合は、システム全体で十分に評価し、お客様の責任において適用可否を判断して下さい。当社は、適用可否に対する責任は負いません。

- 5. 本リファレンスデザインは、その使用に際して当社及び第三者の知的財産権その他の権利に対する保証又は実施権の許諾を行うものではありません。

- 6. 当社は、本リファレンスデザインに関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をせず、また当社は、本リファレンスデザインに関する一切の損害(間接損害、結果的損害、特別損害、付随的損害、逸失利益、機会損失、休業損害、データ喪失等を含むがこれに限らない。)につき一切の責任を負いません。

#### 第3条 契約期間

本リファレンスデザインをダウンロード又は使用することをもって、お客様は本規約に同意したものとみなされます。本規約は予告なしに変更される場合があります。当社は、理由の如何を問わずいつでも本規約を解除することができます。本規約が解除された場合は、お客様は本リファレンスデザインを破棄しなければなりません。さらに当社が要求した場合には、お客様は破棄したことを証する書面を当社に提出しなければなりません。

## 第4条 輸出管理

お客様は本リファレンスデザインを、大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用してはなりません。また、お客様は「外国為替及び外国貿易法」、「米国輸出管理規則」等、適用ある輸出関連法令を遵守しなければなりません。

#### 第5条 準拠法

本規約の準拠法は日本法とします。

#### 第6条 管轄裁判所

本リファレンスデザインに関する全ての紛争については、別段の定めがない限り東京地方裁判所を第一審の専属管轄裁判所とします。