**TOSHIBA CDMOS Integrated Circuit Silicon Monolithic**

## TC78B043FTG/FNG

Sine Wave PWM Drive Controller for Three-phase Brushless Motor

#### 1. Outline

The TC78B043FTG/FNG are Sine Wave PWM drive controllers for 3-phase brushless motors.

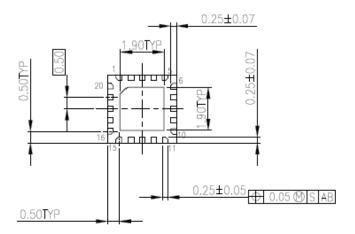

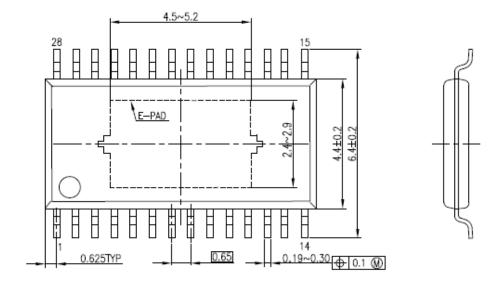

The TC78B043FTG is encapsulated in a WQFN20 package, and the TC78B043FNG is encapsulated in a HTSSOP28 package. And, they have built-in non-volatile memory (NVM), allowing various settings according to the characteristics and usage of the motor to be written to the NVM via SPI communication. Additionally, the NVM in the TC78B043FNG has initial settings suitable for common motors, allowing driving a motor without writing via SPI communication. Furthermore, it is equipped with four pins: FGC pin, LATYPE pin, LAOFS pin, and LA pin. The voltage settings of these pins also allow adjustments of some parameters, such as motor lead angle control.

TC78B043FTG has no four pins: FGC pin, LATYPE pin, LAOFS pin, and LA pin. The NVM has no initial settings for motor control. Therefore, to control the motor, it is necessary to write settings to the NVM via SPI communication.

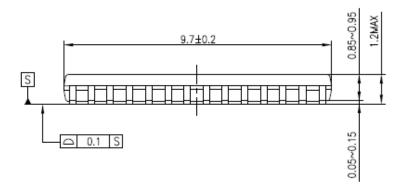

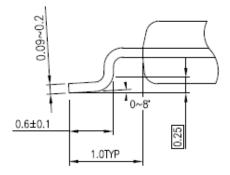

TC78B043FNG

Weight: 0.10 g (typ.)

### 2. Applications

Air conditioner fan motors Air cleaner fan motors

#### 3. Features

- Sine Wave PWM Drive

- The Operational Supply Voltage Range: VCC=6~ 23V (Absolute Maximum Rating is 25 V)

- Various settings are available owing to NVM (Nonvolatile Memory) and SPI communication

- Automatic Lead Angle Control or Fixed Lead Angle Control is selectable.

- Hall element Input or Hall IC Input is selectable.

- Forward Rotation and Reverse Rotation can be switched.

- Speed Control Input with Analog Voltage, PWM Duty, or SPI is selectable.

- Number of pulses for Rotation Pulse Signal Output is selectable.

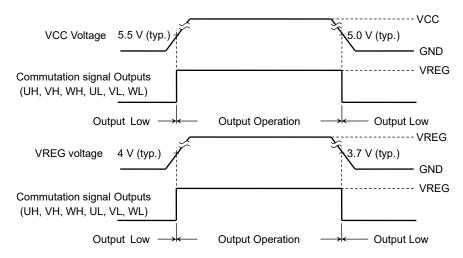

- Built-in Regulator Circuit (VREG= 5 V (typ.), 35 mA (max.))

- Thermal Shut Down Function (TSD)

- Power Supply Low Voltage Detection (UVLO)

- Current Limiting Function

- Output Over-current Detection (ISD)

- Lock Protection Function

Start of mass production 2025-09

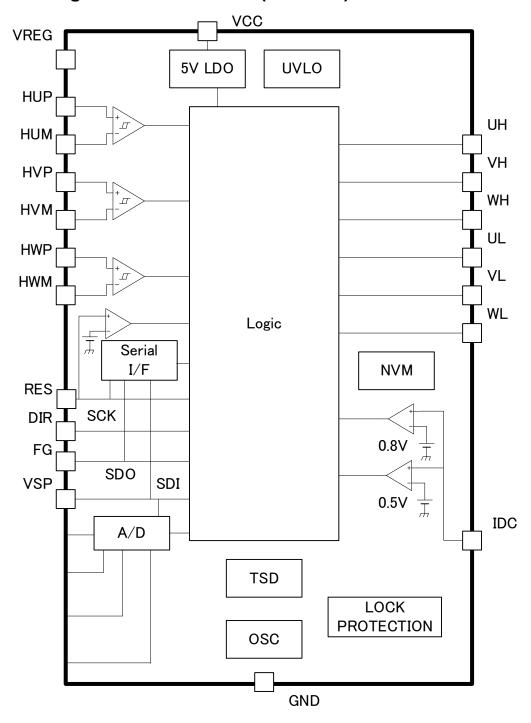

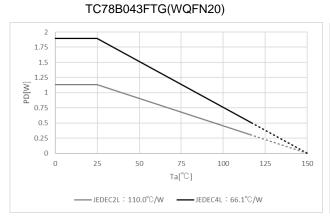

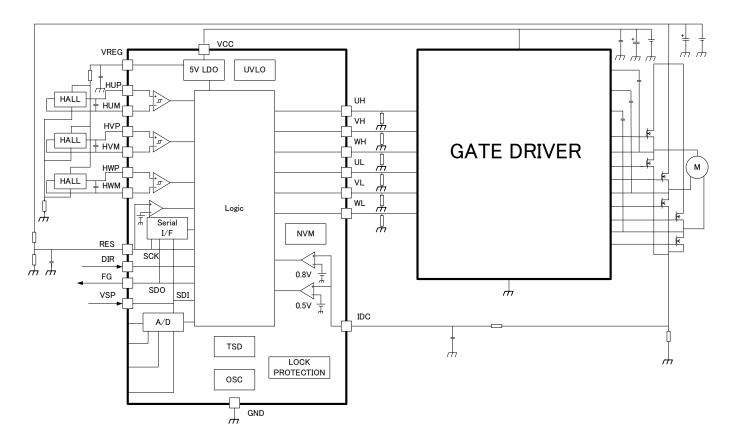

## 4. Block Diagram: TC78B043FTG (WQFN20)

Note: Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.

Fig.4 Block Diagram

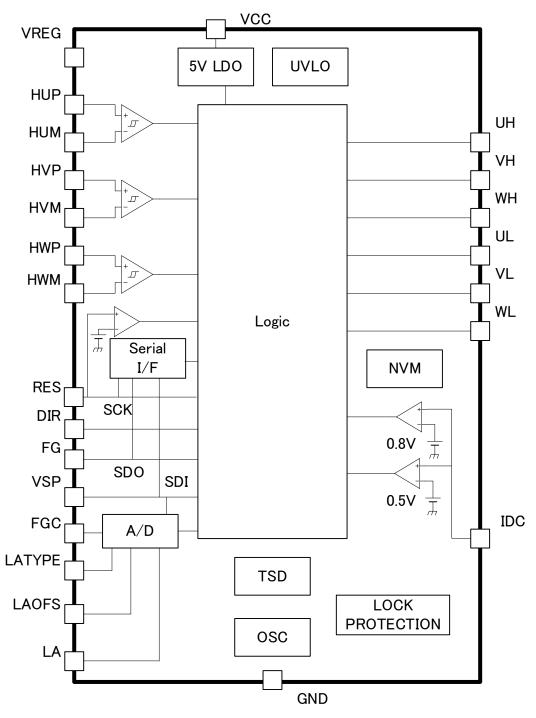

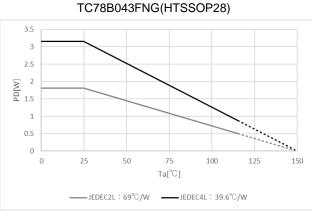

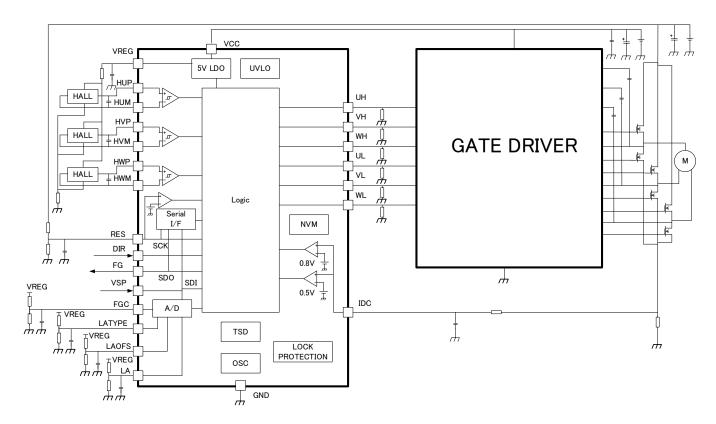

### 5. Block Diagram: TC78B043FNG (HTSSOP28)

Note: Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.

Fig.5 Block Diagram

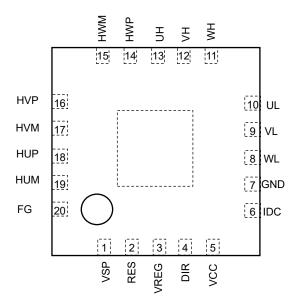

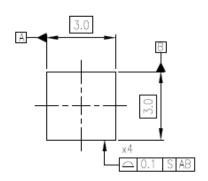

### 6. Pin Assignment: TC78B043FTG (WQFN20)

<Top view>

Fig.6 Pin Assignment

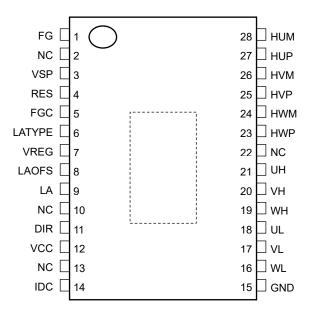

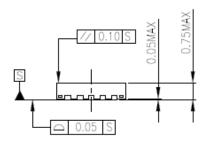

### 7. Pin Assignment: TC78B043FNG (HTSSOP28)

<Top view>

Fig.7 Pin Assignment

### 8. Pin Description

#### **Table 8 Pin Description**

| TC78B043FTG<br>(WQFN20)<br>Pin number | TC78B043FNG<br>(HTSSOP28)<br>Pin number | Name   | Input<br>Output | Pin Description                                                                                     |

|---------------------------------------|-----------------------------------------|--------|-----------------|-----------------------------------------------------------------------------------------------------|

| 1                                     | 3                                       | VSP    | Input           | Dual use of Speed Control Input and Data-in for SPI Communication                                   |

| 2                                     | 4                                       | RES    | Input           | Dual use of Failure Detection (Over-voltage Detection) Input and Clock signal for SPI Communication |

| 3                                     | 7                                       | VREG   | Output          | 5 V Reference Voltage Output                                                                        |

| 4                                     | 11                                      | DIR    | Input           | Forward/Reverse switching Input / Short Brake Input / Failure Detection Input                       |

| 5                                     | 12                                      | VCC    | Power           | Power Supply Voltage                                                                                |

| 6                                     | 14                                      | IDC    | Input           | Current Limiting Input / Over-current Detection Input                                               |

| 7                                     | 15                                      | GND    | Ground          | Ground                                                                                              |

| 8                                     | 16                                      | WL     | Output          | W-phase Low-side Commutation Signal Output                                                          |

| 9                                     | 17                                      | VL     | Output          | V-phase Low-side Commutation Signal Output                                                          |

| 10                                    | 18                                      | UL     | Output          | U-phase Low-side Commutation Signal Output                                                          |

| 11                                    | 19                                      | WH     | Output          | W-phase High-side Commutation Signal Output                                                         |

| 12                                    | 20                                      | VH     | Output          | V-phase High-side Commutation Signal Output                                                         |

| 13                                    | 21                                      | UH     | Output          | U-phase High-side Commutation Signal Output                                                         |

| 14                                    | 23                                      | HWP    | Input           | W-phase Hall Signal (+) Input                                                                       |

| 15                                    | 24                                      | HWM    | Input           | W-phase Hall Signal (-) Input                                                                       |

| 16                                    | 25                                      | HVP    | Input           | V-phase Hall Signal (+) Input                                                                       |

| 17                                    | 26                                      | HVM    | Input           | V-phase Hall Signal (-) Input                                                                       |

| 18                                    | 27                                      | HUP    | Input           | U-phase Hall Signal (+) Input                                                                       |

| 19                                    | 28                                      | HUM    | Input           | U-phase Hall Signa (-) Input                                                                        |

| 20                                    | 1                                       | FG     | Output          | Dual use of Rotation Pulse Output and Data out for SPI Communication                                |

| _                                     | 5                                       | FGC    | Input           | Input for setting Rotation pulse / Sine Wave Reset method                                           |

| _                                     | 6                                       | LATYPE | Input           | Input for setting Lead Angle Control type / with or without Stop Sequence                           |

| _                                     | 8                                       | LAOFS  | Input           | Input for setting Lead Angle value / SPD value offset                                               |

| _                                     | 9                                       | LA     | Input           | Input for setting Maximum Lead Angle value / Fixed Lead Angle value                                 |

|                                       | 2                                       | NC     | -               | Non Connection                                                                                      |

| _                                     | 10                                      | NC     | -               | Non Connection                                                                                      |

|                                       | 13                                      | NC     | -               | Non Connection                                                                                      |

|                                       | 22                                      | NC     | -               | Non Connection                                                                                      |

Note: The absolute maximum rating of the RES pin is 6 V, however, the RES pin is designed not to be destroyed by the VSP voltage even though the RES pin is shorted to the adjacent VSP pin.

Note: The absolute maximum rating of the DIR pin is 6 V, however, the DIR pin is designed not to be destroyed by the VCC voltage even though the DIR pin is shorted to the adjacent VCC pin.

## 9. I/O Equivalent Circuit

The equivalent circuit diagram may be omitted or simplified for explanatory purposes.

Table 9 I/O Equivalent Circuit

| Pin name                     | Remarks                                                                                                             | I/O Internal Circuit   |

|------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------|

| DIR                          | Digital Filter for Input Signals:18/fosc                                                                            |                        |

| FG                           |                                                                                                                     | VREG                   |

| UH<br>VH<br>WH<br>UL<br>VL   |                                                                                                                     | VREG  A  A  A  A  A  A |

| RES                          | Digital Filter for Input Signals:18/fosc                                                                            |                        |

| LA<br>FGC<br>LATYPE<br>LAOFS | Pins for TC78B043FNG (HTSSOP28)  Be sure to input voltage to each pin before use, otherwise the input is undefined. | VREG                   |

| Pin name                               | Remarks                                  | I/O Internal Circuit            |

|----------------------------------------|------------------------------------------|---------------------------------|

| VSP                                    |                                          | VREG VREG                       |

| HUP<br>HUM<br>HVP<br>HVM<br>HWP<br>HWM | Digital Filter for Input Signals:18/fosc | VREG                            |

| IDC                                    | Digital Filter for Input Signals:18/fosc | VREG 200 kΩ  VREG 5 pF  7 0.5 V |

#### 10. Functional Description

#### 10.1. Settings of Driving Waveform

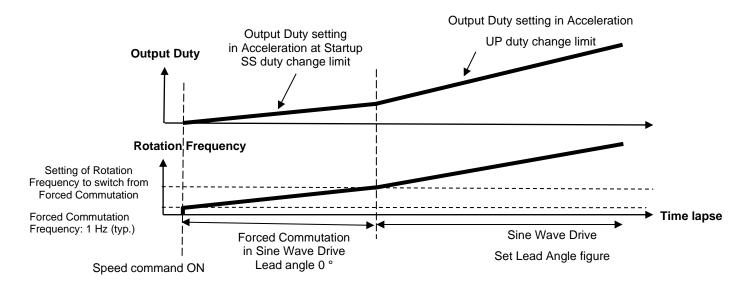

For the startup of this device, either from the Forced Commutation of the Sin Wave Drive (180°Commutation) or from the Square Wave Drive (120°Commutation) can be selected. In case of the Sine Wave Drive Startup, the motor is started to rotate by the Forced Commutation 1 Hz of the Sine Wave Drive, and when the rotation frequency exceeds the set value for switching, the driving waveform is switched to the Sine Wave Drive for Normal Rotation.

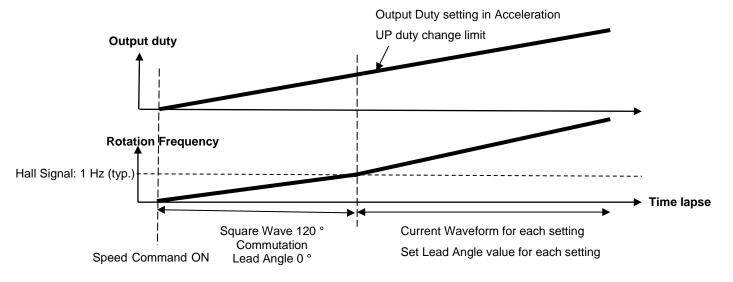

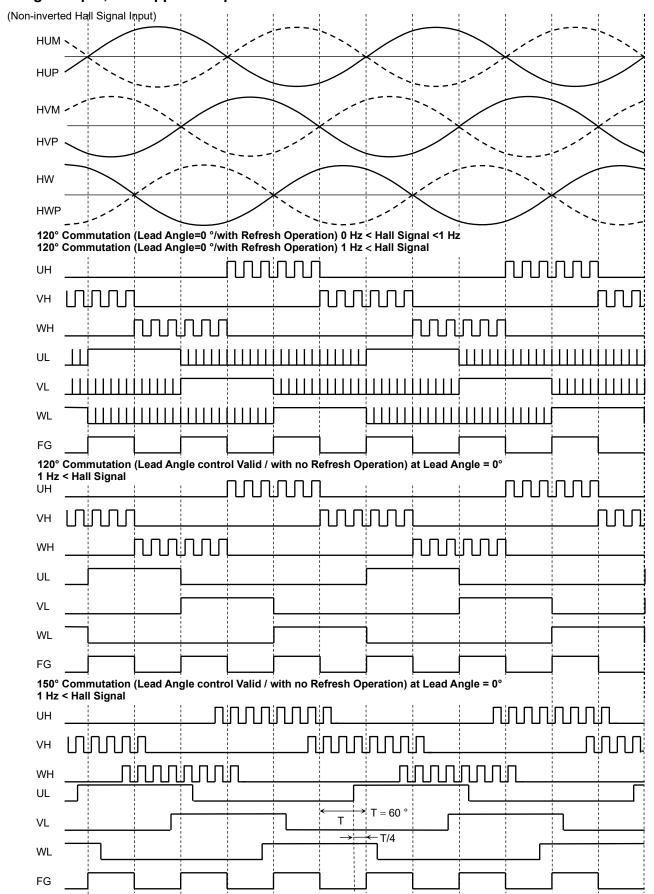

For the Square Wave Drive Startup, the driving waveform is switched to the Squire Wave Drive for Normal Rotation when the Hall Signal exceeds the Rotation Frequency of f = 1Hz. The Lead Angle value below the Rotation Frequency 1Hz is 0°. And when the frequency exceeds 1Hz and the driving waveform is shifted to Normal Rotation, the Lead Angle value is shifted to the value set by the Lead Angle Function.

Also in Normal Rotation, either the Sine Wave Drive or the Square Wave Drive can be selected. For the Sine Wave Drive during Normal Rotation, the Reset Method of the Hall Signal which generates the Sine Wave can be selected from 60 ° Reset, 360 ° Reset, 180 ° Reset, and 60 °/120 ° Reset. The reset method is starts from the 60 ° Reset Method and shifted to the selected method when the Rotation Speed Fluctuation is settled within the set value.

When the Rotation Frequency Fluctuation exceeds the set value or falls below 1 Hz, the method is returned to the 60 ° Reset method.

For the Sine Wave Drive during Normal Rotation, by setting the number of averaging times, the Rotation Frequency Fluctuation is reduced, because the period of Hall Signal Input is averaged by that number of times with the set width.

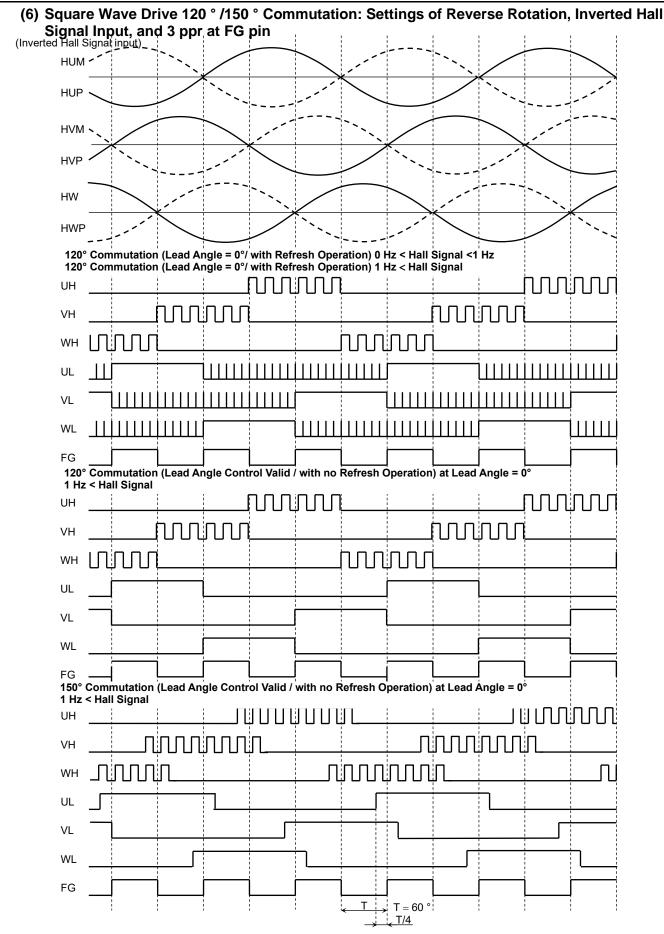

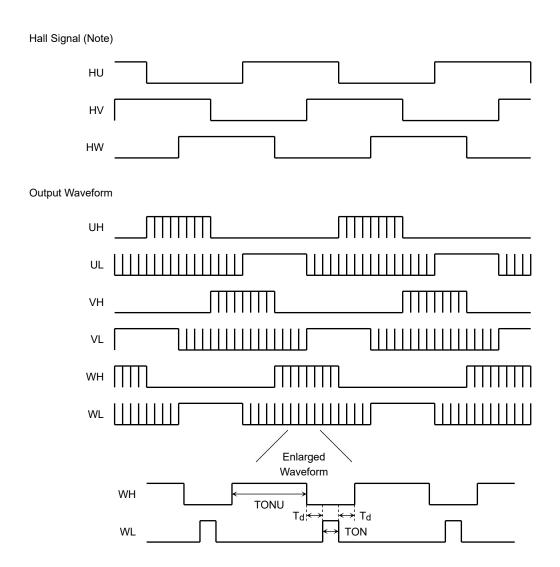

For the Square Wave Drive, either 120 ° Commutation or 150 ° Commutation can be selected. And in 120 ° Commutation, the Lead Angle Control Valid/Invalid can be selected.

**Table10.1.1 Settings of Driving Waveform**

| Register settings<br>2[15:12]<br>PWM_MODE<br>[3:0] | Inverted Hall Signal Input<br>(Note)                                           | At Rotation Startup                                                 | In Normal Rotation<br>Non-inverted Hall Signal<br>Input (Note)                                           | Reset Method of Sine<br>Wave Generation                                  |

|----------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 0000<br>0001<br>0010<br>0011                       | Square Wave Drive  120°Commutation  (Lead Angle = 0°  /with Refresh Operation) | Forced Commutation<br>Sine Wave Drive: 60°<br>Reset (Lead Angle=0°) | Sine Wave Drive<br>(Lead Angle: Lead Angle<br>setting)                                                   | 60° Reset<br>60°⇔360° Reset<br>60°⇔180° Reset<br>60°⇔60° / 120° Reset    |

| 0100<br>0101<br>0110<br>0111                       | /with Reflesh Operation)                                                       |                                                                     |                                                                                                          | 60 ° Reset<br>60 °⇔360° Reset<br>60 °⇔180° Reset<br>60°⇔60° / 120° Reset |

| 1000                                               |                                                                                | Square Wave Drive                                                   | Square Wave Drive150° Commutation (Lead Angle: Lead Angle setting / with no Refresh Operation)           | -                                                                        |

| 1001                                               |                                                                                | 120° Commutation<br>(Lead Angle = 0°<br>/with Refresh Operation     | Square Wave Drive 120° Commutation (Lead Angle: Lead Angle setting / with no Refresh Operation)          | -                                                                        |

| 1010<br>1011<br>1100<br>1101<br>1110               |                                                                                |                                                                     | Square Wave Drive 120° Commutation (Lead Angle control Invalid, Lead Angle = 0°/ with Refresh Operation) | -<br>-<br>-<br>-                                                         |

Note: When the rotation direction is set to Forward Rotation and Hall Signals are input in the correct order, it is defined as the Non-inverted Hall Signal Input, and the motor is driven in Normal Rotation according to the setting. On the other hand, when the Hall Signals are input in the opposite order due to reverse wind, etc., this is defined as the Inverted Hall Signal Input, and in this case, the motor is driven in the Square Wave Drive 120° Commutation.

And when the rotation direction is set to Reverse Rotation, the motor is driven in Normal Rotation when Hall Signals are input in the reverse order, and the motor is driven in the Square Wave Drive 120° Commutation when Hall Signals are input in the positive order.

The Refresh Operation is to turn ON the Low-side Commutation Signals at a fixed cycle (carrier cycle). The ON duty is approximately 8%.

Table 10.1.2 Settings of Rotation Frequency to switch from Forced Commutation

| Resister settings<br>6[1:0]<br>START_FREQ [1:0] | Rotation Frequency to switch from Forced Commutation [Hz] |

|-------------------------------------------------|-----------------------------------------------------------|

| 00                                              | 2                                                         |

| 01                                              | 4                                                         |

| 10                                              | 5                                                         |

| 11                                              | 8                                                         |

Table10.1.3 Settings of Rotation Frequency Fluctuation Figure to switch Sine Wave Reset Method

| Resister settings<br>6[3:2]<br>SIN_SW_RATIO[1:0] | Rotation Frequency Fluctuation Figure to switch Sine Wave Reset method [%] |

|--------------------------------------------------|----------------------------------------------------------------------------|

| 00                                               | 6.25                                                                       |

| 01                                               | 12.5                                                                       |

| 10                                               | 25                                                                         |

| 11                                               | 37.5                                                                       |

Table10.1.4 Settings of Averaging Times Number in Sine Wave Drive

| Resister settings<br>6[5:4]<br>AVE_SEL[1:0] | Averaging Times Number [times] |

|---------------------------------------------|--------------------------------|

| 00                                          | 2                              |

| 01                                          | 4                              |

| 10                                          | 8                              |

| 11                                          | Invalid                        |

Fig.10.1.1 Settings of Forced Commutation in Sine Wave Drive at Startup

Fig.10.1.2 Settings of Square Wave 120 ° Commutation at Startup

#### 10.2. Operating Waveforms

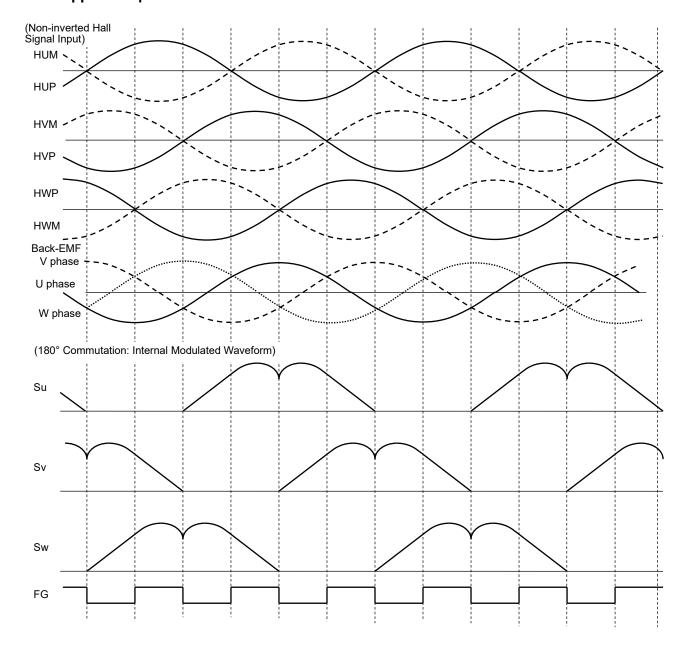

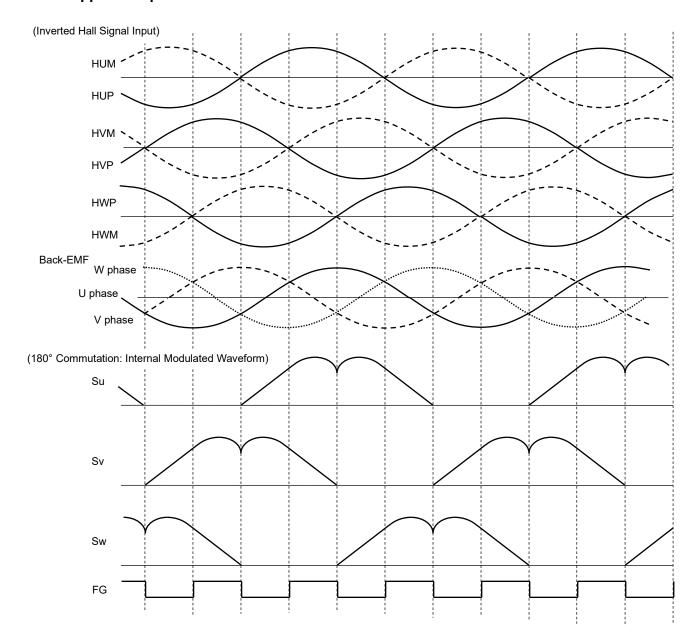

(1) Sine Wave Drive: Settings of Forward Rotation, Non-inverted Hall Signal Input, Lead Angle 0°, and 3 ppr at FG pin

Fig.10.2.1 Sine Wave Drive: Settings of Forward Rotation, Non-inverted Hall Signal Input, Lead Angle 0°, and 3 ppr at FG pin

Note: The Timing Chart is simplified for explanatory purposes.

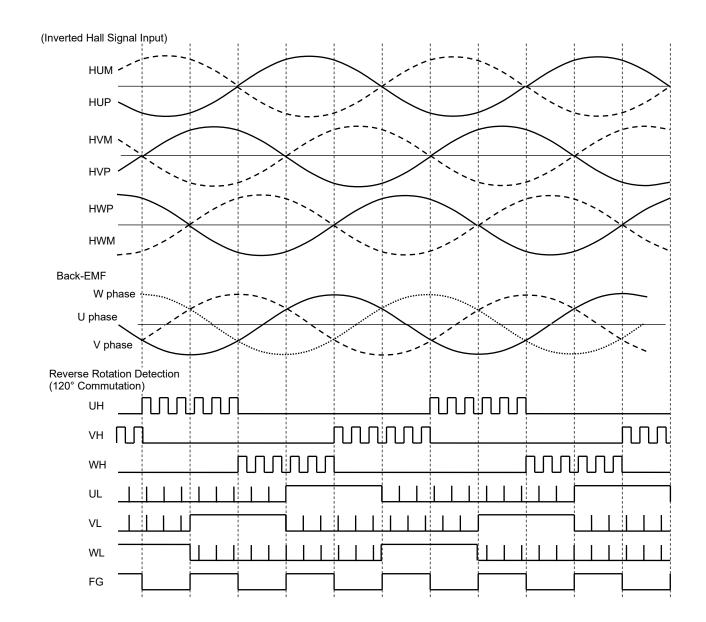

#### (2) Square Wave Drive in 120° Commutation: Settings of Forward Rotation, Inverted Hall Signal Input, and 3 ppr at FG pin

Fig.10.2.2 Square Wave Drive in 120° Commutation: Settings of Forward Rotation, Inverted Hall Signal Input, and 3 ppr at FG pin

Note: In case of the Inverted Hall Signal Input, the motor is driven in 120 ° Commutation with 0° Lead Angle. (Reverse Rotation Operation)

# (3) Sine Wave Drive: Settings of Reverse Rotation, Inverted Hall Signal Input, Lead Angle 0°, and 3 ppr at FG pin

Fig.10.2.3 Sine Wave Drive: Settings of Reverse Rotation, Inverted Hall Signal Input, Lead Angle 0°, and 3 ppr at FG pin

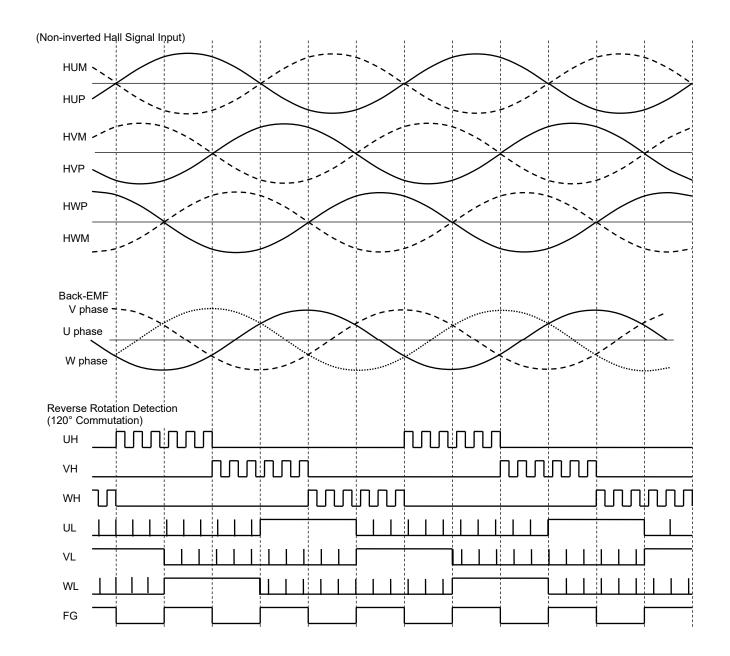

# (4) Square Wave Drive in 120° Commutation: Settings of Reverse Rotation, Non-inverted Hall Signal Input, and 3 ppr at FG pin

Fig.10.2.4 Square Wave Drive in 120° Commutation: Settings of Reverse Rotation, Non-inverted Hall Signal Input, and 3 ppr at FG pin

Note: In case of the Non-inverted Hall Signal Input, the motor is driven in 120 ° Commutation with 0° Lead Angle. (Reverse Rotation Operation)

## **TOSHIBA**

# (5) Square Wave Drive 120 ° /150 ° Commutation: Settings of Forward Rotation, Non-inverted Hall Signal Input, and 3 ppr at FG pin

Fig.10.2.5 Square Wave Drive 120 ° /150 ° Commutation: Settings of Forward Rotation, Non-inverted Hall Signal Input, and 3 ppr at FG pin

Fig.10.2.6 Square Wave Drive 120 ° /150 ° Commutation: Settings of Reverse Rotation, Inverted Hall Signal Input, and 3 ppr at FG pin

# 10.2.1. Operating Waveforms of Square Wave PWM Drive in 120° Commutation (with Refresh Operation)

Fig.10.2.1.1. Operating Waveforms of Square Wave PWM Drive in 120° Commutation (with Refresh Operation)

Note: As for the Hall Signal, Square Wave is used to simplify the chart.

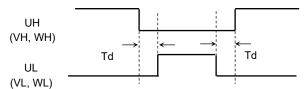

To ensure the bootstrap voltage, the Low-side UL, VL, and WL Outputs are always ON in the carrier cycle even during the OFF period. At this time, the High-side UH, VH, and WH Outputs are turned off with a dead time at the timing when the Low-side of each phase is turned on, as shown in the enlarged waveform in the chart above.

TONL = carrier period x 8 % (s) (constant regardless of VSP Input)

Speed change during Square Wave Drive is determined by the Speed Command, and Acceleration/Deceleration is performed by ON duty of TONU.

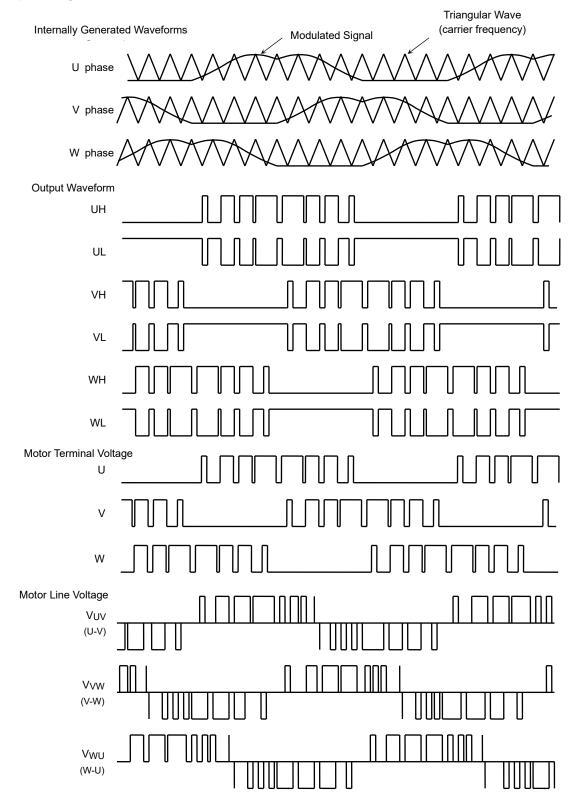

#### 10.2.2 Operating Waveforms of Sine Wave PWM Drive

Fig.10.2.2.1 Operating Waveforms of Sine Wave PWM Drive

Note: As for speed change in Sine Wave Drive, the amplitude of the modulation signal changes with the Speed Command, and Acceleration/Deceleration is performed by the ON duty of the Output Waveform.

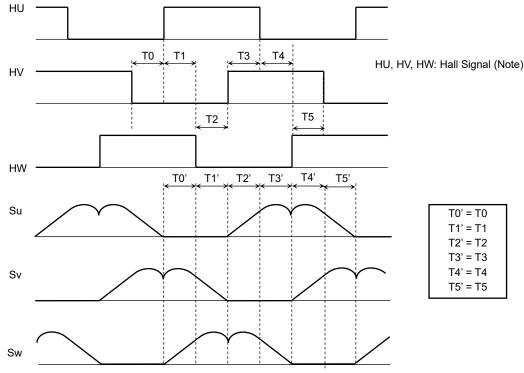

#### 10.3. Sine Wave PWM Generation Method

#### (1) Settings of Sine Wave 60° Reset Method

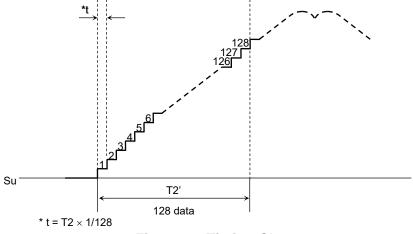

The Sine Wave PWM Signal is generated by creating a modulated waveform from a Hall Signal and comparing this modulated waveform with a Triangular Waveform. The period of time (Electrical Angle: 60°) between the up edge (down edge) of the three Hall Signals and the next down edge (up edge) is counted, and this period is used as the data for the next 60° phase portion in the modulation waveform. The 60° phase portion in the modulation waveform consists of 128 data, and the time width of one data is 1/128 of the time width of the previous 60° phase, and the modulation waveform advances in this width.

Fig.10.3.1 Settings of Sine Wave 60° Reset

In the above Figure, the T1' data of the modulation waveform advances within a time width of 1/128 of the period T1 from the HU (up edge) to the HW (down edge), and likewise, the T2' data advances within a time width of 1/128 of the period T2 from the HW (down edge) to the HV (up edge). When the next edge does not come even after 128 data arrives, the 128th data is retained as it is. (In the case of Forced Commutation in Sin Wave Drive, when the next edge does not come even after 128 data arrives, the next 128 data advances in the same time width until the next edge arrives.) Every 60° Electrical Angle, the modulation waveform is reset in synchronization with the up/down edges of the Hall Signals. Therefore, the modulation waveform is made discontinuous at each resetting when the Hall Signal is out of position or during Acceleration/Deceleration.

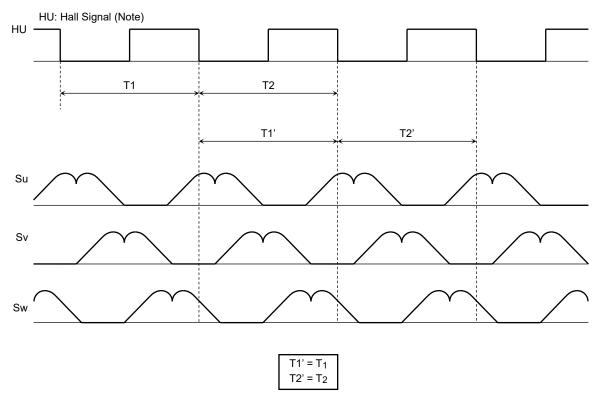

Fig.10.3.2 Timing Chart

Note: As for the Hall Signal, Square Wave is used to simplify the figure.

#### (2) Settings of Sine Wave 360° Reset Method

The Sine Wave PWM signal is generated by creating a modulated waveform from a Hall Signal and comparing this modulated waveform with a triangular waveform.

The period of time (electrical angle: 360°) between the down edge of the HU signal and the next down edge is counted, and this period is used as the data for the 360° phase portion in the next modulation waveform. The 360° phase portion in the modulation waveform consists of 128 x 6 data, and the time width of one data is 1/(128 x 6) of the time width of the previous 360° phase, and the modulation waveform is generated in this width.

Fig.10.3.3 Timing Chart

In the above chart, the T1' data of the modulation waveform advances within a time width of the period T1 from the HU (down edge) to the next HU (down edge). When the next HU edge does not come even after T1' data ends, the data is retained as it is.

The modulation waveform is reset synchronously with the down-edge of each 360° electric angle of the HU Hall Signal.

During motor Acceleration/Deceleration, the modulation waveform is made discontinuous at each reset.

Note: As for the Hall Signal, Square Wave is used to simplify the chart.

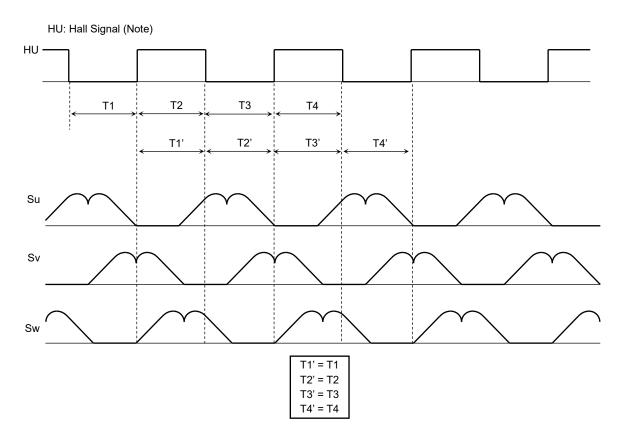

#### (3) Settings of Sine Wave 180° Reset Method

The Sine Wave PWM signal is generated by creating a modulated waveform from a Hall Signal and comparing this modulated waveform with a triangular waveform.

The period of time (electrical angle: 180°) between the down edge of the HU signal and the next down edge is counted, and this period is used as the data for the 180° phase portion in the next modulation waveform. The 180° phase portion in the modulation waveform consists of 128 x 3 data, and the time width of one data is 1/(128 x 3) of the time width of the previous 180° phase, and the modulation waveform is generated in this width.

Fig.10.3.4 Timing Chart

In the above figure, the T1' data of the modulation waveform advances within a time width of the period T1 from the HU (down edge) to the next HU (up edge). When the next HU down edge does not come even after T1' data ends, the data is retained as it is.

The modulation waveform is reset synchronously with the down edge of each 360° electric angle of the HU Hall Signal.

During motor acceleration/deceleration, the modulation waveform is made discontinuous at each reset.

Note: As for the Hall Signal, Square Wave is used to simplify the chart.

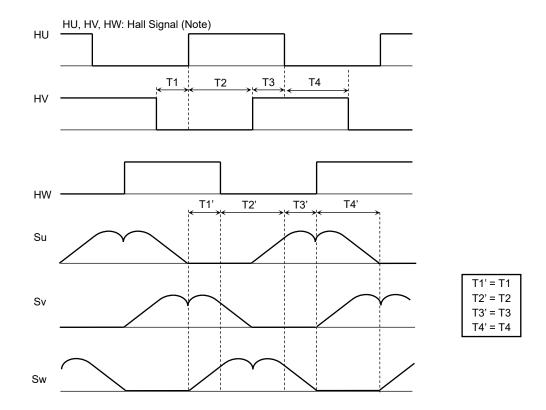

#### (4) Settings of Sine Wave 60°/120° Reset Method

The Sine Wave PWM signal is generated by creating a modulated waveform from a Hall Signal and comparing this modulated waveform with a triangular waveform.

The period of time (electrical angle: 60°/120°) between the edge of the HU/HV signals and the next edge is counted, and this period is used as the data for the 60°/120° phase of the next modulation waveform.

The 60° phase portion in the modulation waveform consists of 128 data, and the time width of one data is 1/128 of the time width of the previous 60° phase, and the modulation waveform is generated in this width. The 120° phase portion in the modulation waveform consists of 128 x 2 data, and the time width of one data is 1/(128 x 2) of the time width of the previous 120° phase, and the modulation waveform is generated in this width.

Fig10.3.5 Timming Chart

In the above figure, the T1' data of the modulation waveform advances within a time width of the period T1 from the HV (down edge) to the HU (up edge). When the next HV down edge does not come even after T1' data ends, the data is retained as it is.

The modulation waveform is reset synchronously with the down-edge/up-edge of each 60°/120° electric angle of the HU/HV Hall Signals.

During motor acceleration/deceleration, the modulation waveform is made discontinuous at each reset.

Note: As for the Hall Signal, Square Wave is used to simplify the chart.

#### 10.4. Settings of Acceleration/Deceleration/Stopping Sequence

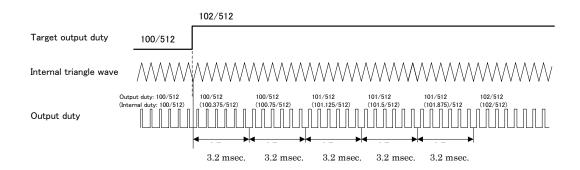

The Output Duty Change Ratio for Acceleration at startup, Acceleration/Deceleration in Steady State, and Stopping can be set, those are changed every 3.2 msec.

Fig.10.4.1 Example: In case of Setting Duty Change Limit = 3/8 during Acceleration

#### 10.4.1. Settings of Output Duty for Acceleration at Startup

The settings of Output Duty for Acceleration at Startup are shown below. The Output Duty is increased with the set ratio of "SS duty change limit".

| Table 10.4.1.1 Settings of Duty | for Acceleration at Startup |

|---------------------------------|-----------------------------|

|---------------------------------|-----------------------------|

| Resister settings 5[3:0] SS_DUTY_CHANGE_LIMIT[3:0] | SS Duty Change Limit                      |

|----------------------------------------------------|-------------------------------------------|

| 0000                                               | Immediate Input Figure<br>= Output Figure |

| 0001                                               | 1/8×1/8                                   |

| 0010                                               | 2/8×1/8                                   |

| 0011                                               | 3/8×1/8                                   |

| 0100                                               | 4/8×1/8                                   |

| 0101                                               | 6/8×1/8                                   |

| 0110                                               | 10/8×1/8                                  |

| 0111                                               | 20/8×1/8                                  |

| 1000                                               | 1/8                                       |

| 1001                                               | 2/8                                       |

| 1010                                               | 3/8                                       |

| 1011                                               | 4/8                                       |

| 1100                                               | 6/8                                       |

| 1101                                               | 10/8                                      |

| 1110                                               | 20/8                                      |

| 1111                                               | 56/8                                      |

#### 10.4.2. Settings of Output Duty for Acceleration in Steady State

The settings of Output Duty for Acceleration in Steady State are shown below. The Output Duty is increased with the set ratio of "UP duty change limit".

Table10.4.2.1 Settings of Duty for Acceleration in Steady state

| Register settings<br>5[7:4]<br>UP_DUTY_CHANGE_LIMIT[3:0] | UP Duty Change Limit                      |

|----------------------------------------------------------|-------------------------------------------|

| 0000                                                     | Immediate Input Figure<br>= Output Figure |

| 0001                                                     | 1/8×1/8                                   |

| 0010                                                     | 2/8×1/8                                   |

| 0011                                                     | 3/8×1/8                                   |

| 0100                                                     | 4/8×1/8                                   |

| 0101                                                     | 6/8×1/8                                   |

| 0110                                                     | 10/8×1/8                                  |

| 0111                                                     | 20/8×1/8                                  |

| 1000                                                     | 1/8                                       |

| 1001                                                     | 2/8                                       |

| 1010                                                     | 3/8                                       |

| 1011                                                     | 4/8                                       |

| 1100                                                     | 6/8                                       |

| 1101                                                     | 10/8                                      |

| 1110                                                     | 20/8                                      |

| 1111                                                     | 56/8                                      |

#### 10.4.3. Settings of Output Duty for Deceleration and Stopping Sequence

The settings of Output Duty for Deceleration and Stop Sequence are shown below. (The Output Duty is reduced with the set ratio of "DWN duty change limit".

Table 10.4.3.1 Settings of Duty for Deceleration and Stopping Sequence

| Register settings<br>5[11:8]<br>DWN_DUTY_CHANGE_LIMIT[3:0] | DWN Duty Change Limit                     |

|------------------------------------------------------------|-------------------------------------------|

| 0000                                                       | Immediate Input Figure<br>= Output Figure |

| 0001                                                       | 1/8×1/8                                   |

| 0010                                                       | 2/8×1/8                                   |

| 0011                                                       | 3/8×1/8                                   |

| 0100                                                       | 4/8×1/8                                   |

| 0101                                                       | 6/8×1/8                                   |

| 0110                                                       | 10/8×1/8                                  |

| 0111                                                       | 20/8×1/8                                  |

| 1000                                                       | 1/8                                       |

| 1001                                                       | 2/8                                       |

| 1010                                                       | 3/8                                       |

| 1011                                                       | 4/8                                       |

| 1100                                                       | 6/8                                       |

| 1101                                                       | 10/8                                      |

| 1110                                                       | 20/8                                      |

| 1111                                                       | 56/8                                      |

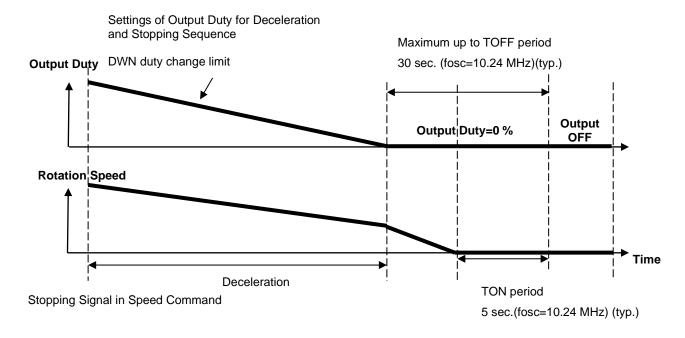

#### 10.4.4. Settings of Stopping Sequence

Stopping Sequence Valid or Invalid is selectable.

In case of Stop Sequence Invalid, the Motor Output is immediately turned off with a stopping signal (Commutation Signal Output = all Low).

And in case of Stop Sequence Valid, when a stopping signal in Speed Command is input, the Output Duty is lowered according to the setting of "DWN duty change limit", and the Output Duty is turned to 0 %. When the Hall Signal is no longer switched, the Motor Output is turned OFF (Commutation signal output = all Low) after the TON period. And after Output Duty = 0 %, when the TOFF period is past, the Motor Output is turned OFF (Commutation Signal Output = all Low), because TOFF is the maximum value.

Table10.4.4.1 Setting of Stop Sequence Valid/Invalid

| Register settings<br>5[15]<br>STOP_SEQ | Stopping Sequence |

|----------------------------------------|-------------------|

| 0                                      | Valid             |

| 1                                      | Invalid           |

Fig. 10.4.4.1 Stopping Sequence

#### 10.5. Settings of Initial Output Duty in returning from Idle Rotation

When the motor is returned from idle rotation, the Initial Output Duty Cycle is determined based on the set reference frequency, and the motor starts rotating. Thereafter, the Output Duty is increased or decreased according to the settings of Acceleration/Deceleration with the Speed Command Input Figure.

Example: 250 Hz setting, 125 Hz at idle rotation

The idle rotation starts with the Output Duty = 125 Hz/250 Hz = 50%, and the Output Duty is increased or decreased according to the settings of Acceleration/Deceleration with the Speed Command Input.

Table 10.5.1 Settings of Reference Frequency of Initial Output Duty in returning from Idle Rotation

| Register settings<br>6[7:6]<br>HZ_RANGE[1:0] | Reference frequency     | Example: Reference rpm in case of 8-pole motor | Example: Reference rpm in case of 10-pole motor |

|----------------------------------------------|-------------------------|------------------------------------------------|-------------------------------------------------|

| 00                                           | Invalid                 | Invalid                                        | Invalid                                         |

|                                              | (Immediate Input Figure | (Immediate Input Figure                        | (Immediate Input Figure                         |

|                                              | = Output Figure)        | = Output Figure)                               | = Output Figure)                                |

| 01                                           | 166.7 Hz                | 2500 rpm                                       | 2000 rpm                                        |

| 10                                           | 250 Hz                  | 3750 rpm                                       | 3000 rpm                                        |

| 11                                           | 416.7 Hz                | 6250 rpm                                       | 5000 rpm                                        |

#### 10.6. Settings of Speed Command

The setting of Speed Command is selected from the settings in the table below.

Table 10.6.1 10.6. Settings of Speed Command

| Register settings<br>6[15:13]<br>TRQ_SEL[2:0] | Settings of Speed Command                                    |

|-----------------------------------------------|--------------------------------------------------------------|

| 000                                           | Analog Voltage Input to VSP pin: A Mode                      |

| 001                                           | Analog Voltage Input to VSP pin: B Mode                      |

| 010                                           | Analog Voltage Input to VSP pin: Velocity Curve Mode         |

| 011                                           | PWM Duty Input VSP pin: Low active Velocity Curve Mode       |

| 100                                           | PWM Duty Input (High active) to VSP pin: Velocity Curve Mode |

| 101                                           | SPI Communication Input: Velocity Curve Mode                 |

| 110                                           | -                                                            |

| 111                                           | -                                                            |

#### 10.6.1. High-voltage Input to VSP pin Operation Mode

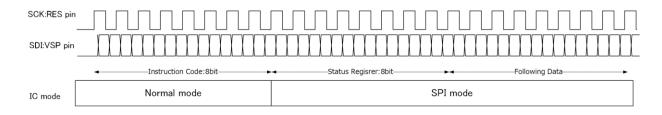

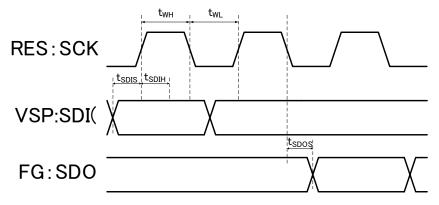

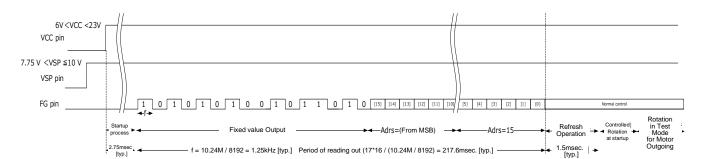

When the Input Voltage to the VSP pin is set to 7.75 V < VSP ≤ 10 V, "High-voltage Input to VSP pin Operation Mode" is selected, and the Motor Outgoing Test Mode or the Commutation Output Low can be selected with the register. (When the Input Voltage exceed 10 V, what is outside range of the VSP Operating Input Voltage, "High-voltage Input to VSP pin Operation Mode" is selected.)

In the Motor Outgoing Test Mode, the Sine Wave Drive operates with zero Lead Angle and the Output ON Duty is maintained at the maximum value. Even though the Sine Wave Generation Method is changed to another reset method, the Sine Wave 60° Reset remains set.

"High-voltage Input to VSP pin Operation Mode" Valid or Invalid can also be selected with the register. The register can also be used to select "High-voltage Input to VSP pin Operation Mode" Valid or Invalid. When the register is set to Invalid, the maximum value in the Speed Command is maintained. The settings of the Lead Angle and the Sine Wave Generation Method are kept unchanged.

Table 10.6.1.1 Settings of High-voltage Input to VSP pin Operation Mode

| Register settings<br>11[5]<br>SHIP_CHG | High-voltage Input to VSP pin<br>Operation Mode  |

|----------------------------------------|--------------------------------------------------|

| 0                                      | Motor Outgoing Test Mode • Sine Wave 60° Reset   |

|                                        | <ul> <li>Zero Lead Angle</li> </ul>              |

|                                        | <ul> <li>Output ON Duty maximum value</li> </ul> |

| 1                                      | Commutation Output all Low<br>(Motor Output OFF) |

Table 10.6.1.2 Settings of High-voltage Input to VSP pin Operation Mode Valid/Invalid

| Register settings<br>11[6]<br>SHIP_MASK | High-voltage Input to VSP pin<br>Operation Mode |

|-----------------------------------------|-------------------------------------------------|

| 0                                       | Valid                                           |

| 1                                       | Invalid                                         |

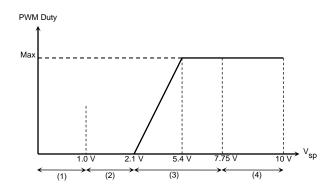

#### 10.6.2. Settings of Speed Command: A Mode of Analog Voltage Input to VSP pin

When the speed command is set to "A Mode of Analog Voltage Input to VSP pin", by inputting analog voltage to the VSP pin, the Output can be controlled and the Motor Speed is controlled as shown below.

- 1. When the Command Input Voltage (VSP) is VSP ≤ 1.0 V, the Commutation Output is turned OFF. (for protection of Gate block)

- 2. When the Command Input Voltage is 1.0 V < VSP  $\le$  2.1 V (Refresh Operation), the Low-side Commutation Signal is turned ON at a fixed cycle (carrier cycle). ON duty= approx. 8 %

- 3. When Command Input Voltage is 2.1 V <VSP  $\le$  7.75 V, the Output ON Duy changes with 512 resolution, and when 5.4 V (typical)  $\le$  VSP, the Output ON Duty maintains the maximum value.

- In case of Square Wave Drive, the Low-side Commutation Signal is forced ON at a fixed cycle (carrier cycle). ON duty=  $8\,\%$

- In the Stop State, when VSP = 2.1 V or more is input, the Driving Signal is output after a Refresh Operation 1.5 msec. is completed.

- And in the Rotation State, when VSP = 2.1 V or more is input, the Driving Signal is output immediately.

- 4. When Command Input Voltage is 7.75 V < VSP ≤ 10 V, "High-voltage Input to VSP pin Operation Mode" is set.

Fig.10.6.2.1 A Mode of Analog Voltage Input to VSP pin

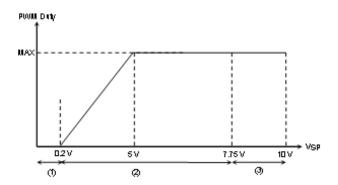

#### 10.6.3. Settings of Speed Command: B Mode of Analog Voltage Input to VSP pin

When the Speed Command is set to the "B Mode of Analog Voltage Input to VSP pin", by inputting analog voltage to the VSP pin, the output can be controlled and the motor speed is controlled as shown below.

- 1. When the Command Input Voltage (VSP) is VSP  $\leq$  0.2 V (Refresh Operation), the Low-side Commutation Signal is turned ON at a fixed cycle (carrier cycle). ON duty= approx. 8 %

- 2. When the Command Input Voltage is 0.2 V  $\leq$  VSP  $\leq$  7.75 V, the Output ON duty changes with 512 resolutions.

And when 5.0 V (typ.)  $\leq$  VSP, the Output ON Duty maintains the maximum value.

In case of Square Wave Drive, the Low-side Commutation Signal is forced ON at a fixed cycle (carrier cycle). ON duty=  $8\,\%$

In the Stop State, when VSP = 0.2 V or more is input, the Drive Signal is output after a Refresh Operation 1.5msec. is completed.

And in the Rotation State, when VSP = 0.2 V or more is input, the Drive Signal is output immediately.

3. When the Command Input voltage is 7.75 V  $\leq$  VSP  $\leq$  10 V, "High-voltage Input to VSP pin Operation Mode" is set.

Fig.10.6.3.1 B Mode of Analog Voltage Input to VSP pin

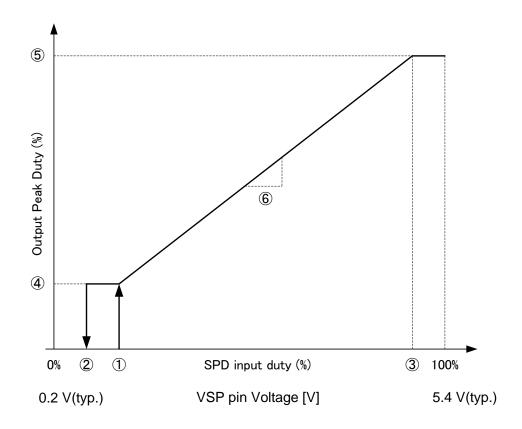

#### 10.6.4. Settings of Speed Command: Velocity Curve Mode of Analog Voltage Input to VSP pin

When the Speed Command is set to "Velocity Curve Mode of Analog Voltage Input to VSP pin", after setting the Speed Curve, the Output can be controlled by inputting an analog voltage within the range of 0.2 V to 5.4 V to the VSP pin as shown below, and then the motor speed is controlled.

Fig.10.6.4.1 Velocity Curve of Analog Voltage Input Mode at VSP pin

Note: When the Command Input Voltage is 7.75 V  $\,\leq$  VSP  $\,\leq\,$  10 V, "High-voltage Input to VSP pin Operation Mode" is set.

Table10.6.4.1 10.6.4. Settings of Velocity Curve

| Item                                 | Setting Range             | Setting Method        | Setting Resolution       | Resister                    |

|--------------------------------------|---------------------------|-----------------------|--------------------------|-----------------------------|

| ①Startup Duty<br>(Start Duty)        | 0 to 49.8 %               | STARTDUTY / 512       | 0.2 %                    | 1[7:0]<br>STARTDUTY[7:0]    |

| ②Stopping Duty<br>(Stop Duty)        | 0 to 49.6 %               | STOPDUTY x 2 / 512    | 0.4 %                    | 1[14:8]<br>STOPDUTY[6:0]    |

| ③Maximum Duty<br>(Max Duty)          | 50.2 to 100 %             | (MAXDUTY + 257) / 512 | 0.2 %                    | 2[7:0]<br>MAXDUTY[7:0]      |

| ④Minimum Output Duty<br>(Min Output) | 0 to 49.8 %               | STARTOUTDUTY / 512    | 0.2 %                    | 3[7:0]<br>STARTOUTDUTY[7:0] |

| ⑤Maximum Duty<br>(Max Output)        | Depending on 136          | N/A                   | N/A                      | N/A                         |

| ⑥Acceleration Slope<br>(Speed Slope) | 0 to 16<br>Output%/Input% | DUTYSLOPE/ 1024       | 1/1024<br>Output%/Input% | 4[13:0]<br>DUTYSLOPE[13:0]  |

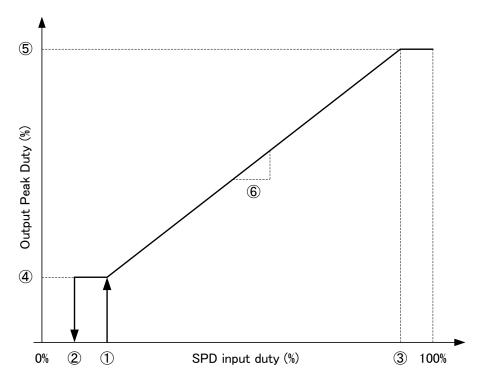

#### 10.6.5. Settings of Speed Command: Velocity Curve Mode of PWM Duty Input to VSP pin

When the Speed Command is set to "Velocity Curve Mode of PWM Duty Input to VSP pin", the Output is controlled with the ratio of the High and Low duty of the PWM Duty Input Signal to the VSP pin. and then the motor speed is controlled.

High active and Low active for the PWM Duty Input Signal is selectable.

The frequency range of the PWM Duty Input Signal is from 1 kHz to 100 kHz, and the recognizable duty resolution of the PWM Duty Input Signal is determined by the formula of (Oscillation Frequency fosc)/(Frequency of the PWM Duty Input Signal), and the upper limit of resolution is 512.

For example, under the setting of the Oscillation Frequency fosc = 10.24 MHz (typ.), when the PWM Duty Input Signal Frequency = 100 kHz, the Resolution = 10.24 MHz/100 kHz = 102, when the PWM Duty input signal Frequency = 20 kHz, the Resolution = 10.24 MHz/20 kHz = 512, when the PWM Duty input signal Frequency = 1 kHz, the recognizable duty resolution is calculated 10.24k from the formular of 10.24 MHz/1 kHz, however, it results in 512 because of the upper limit.

#### Table10.6.5.1 PWM Duty Input

| Settings                     | State                                                                                                                       |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| PWM Duty Input (High active) | When the PWM Duty Input is set to High, the motor output is turned ON, and when set to Low, the Motor Output is turned OFF. |

| PWM Duty input (Low active)  | When the PWM Duty Input is set to Low, the motor output is turned ON, and when set to High, the Motor Output is turned OFF. |

Fig. 10.6.5.1 Velocity Curve Mode of PWM Duty Input to VSP pin

Note: When the Command Input Voltage is 7.75 V < VSP  $\leq$  10 V, "High-voltage Input to VSP pin Operation Mode" is set.

Table10.6.5.2 Settings of Velocity Curve

| Item                                 | Setting Range             | Setting Method        | Setting Resolution       | Resister                        |

|--------------------------------------|---------------------------|-----------------------|--------------------------|---------------------------------|

| ①Startup Duty<br>(Start Duty)        | 0 to 49.8 %               | STARTDUTY / 512       | 0.2 %                    | 1[7:0]<br>STARTDUTY [7:0]       |

| ②Stopping Duty<br>(Stop Duty)        | 0 to 49.6 %               | STOPDUTY × 2 / 512    | 0.4 %                    | 1[14:8]<br>STOPDUTY [6:0]       |

| ③Maximum Duty<br>(Max Duty)          | 50.2 to 100 %             | (MAXDUTY + 257) / 512 | 0.2 %                    | 2[7:0]<br>MAXDUTY [7:0]         |

| ④Minimum Output Duty<br>(Min Output) | 0 to 49.8 %               | STARTOUTDUTY / 512    | 0.2 %                    | 3[7:0]<br>STARTOUTDUTY<br>[7:0] |

| ⑤Maximum Duty<br>(Max Output)        | Depending on ①③⑥          | N/A                   | N/A                      | N/A                             |

| ⑥Acceleration Slope<br>(Speed Slope) | 0 to 16<br>Output%/Input% | DUTYSLOPE/ 1024       | 1/1024<br>Output%/Input% | 4[13:0]<br>DUTYSLOPE [13:0]     |

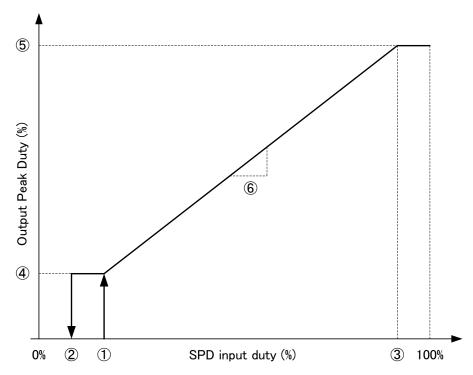

#### 10.6.6. Settings of Speed Command: Velocity Curve Mode of SPI Communication Input

When the Speed Command is set to "Velocity Curve Mode of SPI Communication Input", after setting the Speed Curve as shown below, the Output Duty is controlled by inputting command of 0 to 512 (513 or more also is judged as 512.) to the Speed Command register 13[15:6]TRQ\_DUTY[9:0] via SPI Communication, and then the Motor Speed is controlled.

Fig.10.6.6.1 Velocity Curve Mode of SPI Communication Input

| Item                                 | Setting Range             | Setting Method        | Setting Resolution       | Resister                        |

|--------------------------------------|---------------------------|-----------------------|--------------------------|---------------------------------|

| ①Startup Duty<br>(Start Duty)        | 0 to 49.8 %               | STARTDUTY / 512       | 0.2 %                    | 1[7:0]<br>STARTDUTY [7:0]       |

| ②Stopping Duty<br>(Stop Duty)        | 0 to 49.6 %               | STOPDUTY × 2 / 512    | 0.4 %                    | 1[14:8]<br>STOPDUTY [6:0]       |

| ③Maximum Duty<br>(Max Duty)          | 50.2 to 100 %             | (MAXDUTY + 257) / 512 | 0.2 %                    | 2[7:0]<br>MAXDUTY [7:0]         |

| ④Minimum Output Duty<br>(Min Output) | 0 to 49.8 %               | STARTOUTDUTY / 512    | 0.2 %                    | 3[7:0]<br>STARTOUTDUTY<br>[7:0] |

| ⑤Maximum Duty<br>(Max Output)        | Depending on ①③⑥          | N/A                   | N/A                      | N/A                             |

|                                      | 0 to 16<br>Output%/Input% | DUTYSLOPE / 1024      | 1/1024<br>Output%/Input% | 4[13:0]<br>DUTYSLOPE [13:0]     |

The Refresh Operation Valid or Invalid can be set with the register. Refresh Operation: To turn the Low-side Commutation Signal ON at a fixed cycle (carrier cycle). ON duty is approx. 8 %.

Table10.6.6.2 Refresh Operation Valid/Invalid

| Register settings<br>10[7]<br>BOOT_ON | Refresh Operation |

|---------------------------------------|-------------------|

| 0                                     | Invalid           |

| 1                                     | Valid             |

High-voltage Input to VSP pin Operation Mode Valid or Invalid is set with the register.

Table 10.6.6.3 High-voltage Input to VSP pin Operation Mode Valid/Invalid

| Register settings<br>13[0]<br>SHIP_MODE | High-voltage Input to VSP pin<br>Operation Mode |

|-----------------------------------------|-------------------------------------------------|

| 0                                       | Invalid                                         |

| 1                                       | Valid                                           |

#### 10.7. Settings of Lead Angle Function

The Lead Angle Value can be selected as shown below.

The Lead Angle Value is determined by the Speed Command Figure (SPD: Internal Speed Command Figure), which is controlled by the Acceleration/Deceleration setting (Duty\_Chg\_Limit). And the Lead Angle value is changed every 1 STEP at the reset timing of the Sine Wave Reset Method to be the set Lead Angle value.

**Table 10.7.1 Settings of Lead Angle Function**

| Register settings<br>7[15:13]<br>LA_TYPE[2:0] | Settings of Lead Angle Function                     |

|-----------------------------------------------|-----------------------------------------------------|

| 000                                           | Linear Curve Lead Angle: LAoffset Valid             |

| 001                                           | Linear Curve Lead Angle: Doffset Valid              |

| 010                                           | Quadratic Curve Lead Angle: LAoffset Valid          |

| 011                                           | Quadratic Curve Lead Angle: SPDoffset Valid         |

| 100                                           | Lead Angle of Quadratic Curve with Inflection Point |

| 101                                           | Fixed Lead Angle                                    |

| 110                                           | Lead Angle 0°                                       |

| 111                                           | Lead Angle 0°                                       |

**Table10.7.2 Settings of Lead Angle Function**

| Resister name            | No | Contents of Settings                                 | Input<br>range | Range of<br>Setting Figure | Resolution |

|--------------------------|----|------------------------------------------------------|----------------|----------------------------|------------|

| [6:0]<br>LA [6:0]        | 1  | Maximum Lead Angle value<br>/ Fixed Lead Angle value | 0 to 127       | 0 to 59.5 °                | 60/128     |

| 8[7:0]<br>MAX_SPD [7:0]  | 2  | SPD value of maximum Lead<br>Angle                   | 0 to 255       | 256 to 511                 | 1/512      |

| 9[15:8]<br>CHG_SPD [7:0] | 3  | SPD value of Quadratic Curve with Inflection Point   | 0 to 255       | 0 to 510                   | 2/512      |

| 8[15:8]                  | 4  | LA offset                                            | 0 to 63        | 0 to 29.5 °                | 60/128     |

| LA_OFF/SPD_OFF [7:0]     | 5  | SPD offset                                           | 0 to 255       | 0 to 255                   | 1/512      |

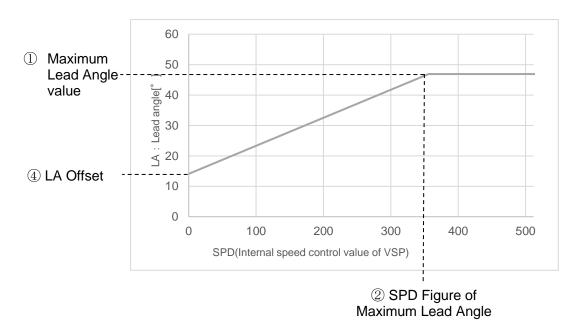

#### 10.7.1. Linear Curve Lead Angle: LA offset Valid

When "Lead angle of primary curve: LA offset valid" is selected, the Lead Angle indicates the behavior of a linear curve with respect to the Speed Command SPD (Internal Speed Command Figure) and can be set as shown below.

①The Maximum Lead Angle value is determined with the setting of LA x Resolution (60/128). Example: when the setting of LA = 100, the Maximum Lead Angle is  $100 \times 60 / 128 = 46.9$  °

②The SPD figure of maximum Lead Angle is determined with the setting of max\_spd setting + 256. Example: when the setting of max\_spd/chg\_spd = 100, the SPD value of Maximum Lead Angle is 100 + 256 = 356

4The LA offset is determined with the setting of la\_off/spd\_off x resolution (60/128). Example: when the setting of la\_off/spd\_off is 30, the LA offset is 30 x 60 / 128 = 14.1°.

Example: The Lead Angle when SPD=200 at the above settings is as follows. Lead Angle [°] = [{(LA-la\_off/spd\_off) / (max\_spd / chg\_spd+256)  $\times$  SPD} + la\_off/spd\_off]  $\times$  (60 / 128) Lead Angle [°] = [{(100-30) / (100 + 256)  $\times$  200} + 30]  $\times$  (60 / 128) Lead Angle [°] = 32.5

When LA < la\_off/spd\_off, LA-la\_off/spd\_off is 0.

Fig.10.7.1.1 Linear Curve Lead Angle: Settings of LA offset Valid

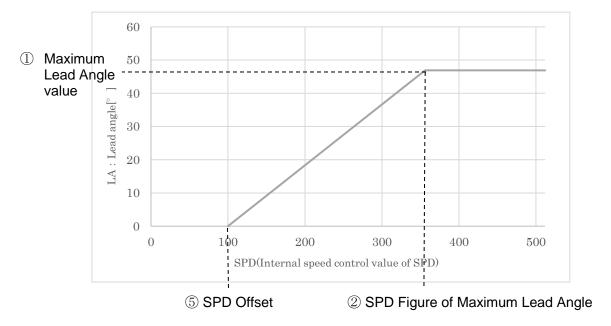

#### 10.7.2. Linear Curve Lead Angle: SPD offset Valid

When the "Linear curve Lead angle: SPD offset valid" is selected, the lead angle indicates the behavior of a linear curve with respect to the Speed Command SPD (Internal Speed Command Figure) and can be set as shown below.

①The Maximum Lead Angle value is determined with the setting of LA x Resolution (60 / 128). Example: when the setting of LA = 100, the Maximum Lead Angle is  $100 \times 60 / 128 = 46.9^{\circ}$

②The SPD figure of Maximum Lead Angle is determined with the setting of max\_spd setting + 256. Example: when the setting of max\_spd / chg\_spd = 100, the SPD value of Maximum Lead Angle is 100 + 256 = 356

⑤The SPD offset is determined with the setting of la\_off/spd\_off. Example: when the setting of la\_off/spd\_off is 100, SPD offset is 100.

Example: The Lead Angle when SPD = 200 at the above settings is as follows. Lead Angle [°] = LA × (SPD-la\_off/spd\_off) / (max\_spd / chg\_spd+256-la\_off/spd\_off) × (60 / 128) Lead Angle [°] = 100 × (200 - 100) / (100 + 256 -100) × (60 / 128) Lead Angle [°] = 18.3

When SPD < la\_off/spd\_off, Lead Angle [°] is 0.

Fig.10.7.2.1 Linear Curve Lead Angle: Settings of SPD offset Valid

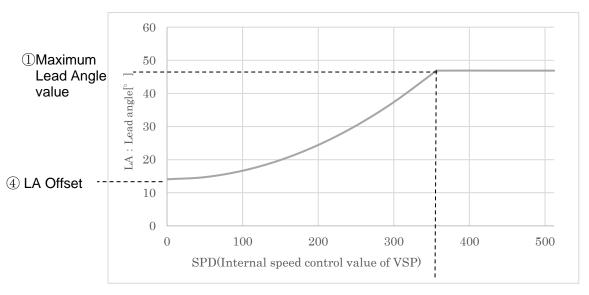

#### 10.7.3. Quadratic Curve Lead Angle: LAoffset Valid

When the "Quadratic curve Lead Angle: LAoffset valid" is selected, the lead angle indicates the behavior of a quadratic curve with respect to the Speed Command SPD (Internal Speed Command Figure) and can be set as follows.

①The Maximum Lead Angle value is determined with the setting of LA x Resolution (60/128). Example: when the setting of LA = 100, the Maximum Lead Angle is  $100 \times 60 / 128 = 46.9$ °

②The SPD figure of Maximum Lead Angle is determined with the setting of max\_spd setting + 256. Example: when the setting of max\_spd / chg\_spd = 100, the SPD value of maximum Lead Angle is 100 + 256 = 356

①The LA offset is determined with the setting of la\_off/spd\_off x Resolution (60/128). Example: when the setting of la\_off/spd\_off is 30, the LA offset is 30 x 60/128 = 14.1°.

Example: The Lead Angle when SPD=200 at the above settings is as follows. Lead Angle [°] = [{(LA-la\_off/spd\_off) / (max\_spd / chg\_spd + 256) ^2 x SPD^2} + la\_off/spd\_off] x (60 /1 28) Lead Angle [°] = [{(100 - 30) / (100 + 256)^2 x 200^2} + 30] x (60 / 128)

Lead Angle [°] = 22.9

When LA < la\_off/spd\_off, LA-la\_off/spd\_off is 0.

② SPD Figure of Maximum Lead Angle

Fig 10.7.3.1 Quadratic Curve Lead Angle: Settings of LAoffset Valid

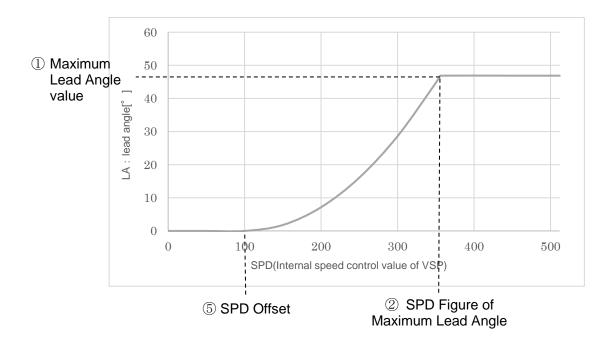

#### 10.7.4. Quadratic Curve Lead angle: SPD offset Valid

When the "Quadratic curve Lead Angle: SPD offset valid" is selected, the lead angle indicates the behavior of a quadratic curve with respect to the Speed Command SPD (Internal Speed Command value) and can be set as shown below.

①The Maximum Lead Angle value is determined with the setting of LA x Resolution (60 / 128). Example: when the setting of LA = 100, the Maximum Lead angle is  $100 \times 60 / 128 = 46.9$ °

②The SPD Figure of Maximum Lead Angle is determined with the setting of max spd setting + 256. Example: when the setting of max spd / chg spd = 100, the SPD value of maximum Lead angle is 100 + 256 = 356

⑤The SPD offset is determined with the setting of la\_off/spd\_off. Example: when the setting of la\_off/spd\_off is 100, SPD offset is 100.

Example: The Lead Angle when SPD=200 at the above settings is as follows. Lead Angle [°] = LA x (SPD-la off/spd off) ^2 / (max spd / chg spd + 256 - la off/spd off) ^2  $\times (60 / 128)$ Lead Angle [°] =  $100 \times (200-100)^2 / (100 + 256 - 100)^2 \times (60 / 128)$ Lead Angle [°] = 7.2

When SPD < la\_off/spd\_off, Lead Angle [°] is 0.

Fig10.7.4.1 Settings of Quadratic Curve Lead Angle: SPD offset Valid

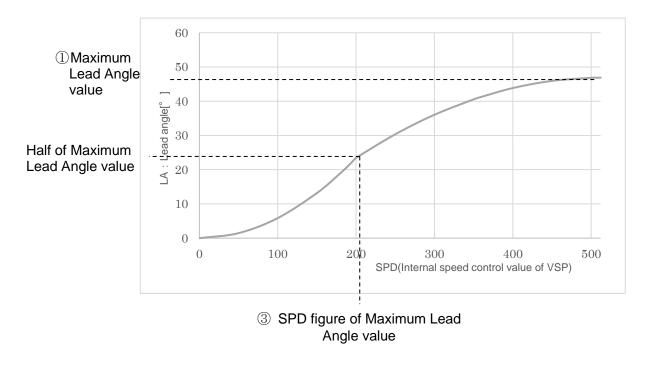

#### 10.7.5. 2 Lead Angle of Quadratic Curve with Inflection Point

When the "Lead Angle of Quadratic Curve with Inflection Point" is selected, the Lead Angle indicates the behavior of a quadratic curve with respect to the Speed Command SPD (Internal Speed Command value) and can be set as show below.

①The Maximum Lead Angle value is determined with the setting of LA x Resolution (60 / 128). Example: when the setting of LA = 100, the Maximum Lead Angle is  $100 \times 60 / 128 = 46.9$  °

3 The SPD Figure of Quadratic Curve with Inflection Point is determined with the setting of chg spd x 2. Example: when the setting of max spd/chg spd = 100, the SPD value of Quadratic Curve with Inflection point is  $100 \times 2 = 200$

Example: The Lead Angle when SPD=200 at the above settings is as follows. When the inflection point > SPD,

Lead Angle [°] = LA  $\times$  SPD^2 / {2  $\times$  (2  $\times$  max\_spd / chg\_spd)^2}  $\times$  (60 / 128)

Lead Angle [°] =  $100 \times 100^2 / \{2 \times (2 \times 100)^2\} \times (60 / 128)$

Lead Angle [°] = 5.9

Example: The Lead Angle when SPD=300 at the above settings is as follows. When the inflection point ≤ SP,

Lead Angle [°] =  $(LA - [\{LA \times (512 - SPD)^2\}) / \{2 \times (512 - 2 \times max\_spd / chg\_spd)^2\}]) \times (60 / 128)$

Lead Angle [°] =  $(100 - [\{100 \times (512 - 300)^2\}) / \{2 \times (512 - 2 \times 100)^2\}]) \times (60 / 128)$

Lead Angle [°] = 36.1

Fig. 10.7.5.1 Settings of Lead Angle of Quadratic Curve with Inflection Point

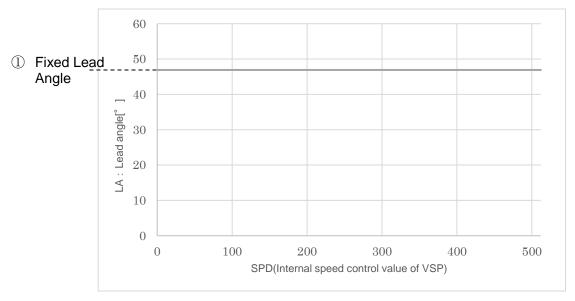

#### 10.7.6. Fixed Lead Angle

When the "Fixed Lead Angle" is selected, the Lead Angle is constant with respect to the Speed Command SPD (Internal Speed Command value) and can be set as follows.

①Fixed Lead Angle is determined with the setting of LA x resolution (60 / 128). Example: When LA setting = 100, the Maximum Lead Angle is  $100 \times 60 / 128 = 46.9^{\circ}$ .

Fig.10.7.6.1 Settings of Fixed Lead Angle

#### 10.7.7. Lead Angle 0°

When the "Lead Angle 0°" is selected, the Lead Angle remains 0° for any Speed Command SPD (Internal Speed Command Value).

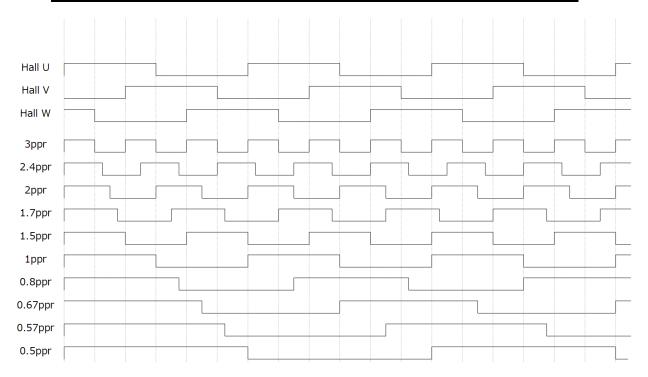

#### 10.8. Settings at FG pin

The Output Signal at the FG pin can be selected as shown below.

The Output Structure at the FG pin can also be selected.

The FG pin also plays the role of SDO for Serial Communication, but it can be selected to output the FG Function Signal even during the Serial Communication with the register settings.

Note: • As for the FG function, no Rotation Pulse Signal is output for rotation below 1 Hz, except for the 3 ppr and 1 ppr settings.

· When the FG pin is set as an open drain output and a pull-up resistor is connected to a separate external power supply without using the VREG pin, voltage may be supplied from the separate external power supply to the power supply of this device via the FG pin. Even though a voltage is supplied from the FG pin, this device is not abnormally controlled as long as the FG pin is used within the specification range. But please note that this phenomenon may occur.

Table 10.8.1 1 Selection of Output Signal Functions in Serial Communication at FG pin

| Register settings<br>1[15]<br>SR_FG | Output Signal at FG pin |

|-------------------------------------|-------------------------|

| 0                                   | SDO Function            |

| 1                                   | FG Function             |

Table 10.8.2 Selection of Output Structure at FG pin

| Register settings<br>11[4]<br>FG_OD | Selection of Output<br>Structure at FG pin |

|-------------------------------------|--------------------------------------------|

| 0                                   | Push-pull Output                           |

| 1                                   | Open Drain Output                          |

Table10.8.3 Settings of Functions at FG pin

| Register            | Poles                     | 2    | 4    | 6    | 8        | 10        | 12    | 14    | 16    |

|---------------------|---------------------------|------|------|------|----------|-----------|-------|-------|-------|

| settings<br>10[3:0] | Pole pairs                | 1    | 2    | 3    | 4        | 5         | 6     | 7     | 8     |

| FG_SEL              | ppr                       |      |      |      | Pulse pe | er revolu | ution |       |       |

| 0000                | 3.00                      | 3.00 | 6.00 | 9.00 | 12.00    | 15.00     | 18.00 | 21.00 | 24.00 |

| 0001                | 2.40                      | 2.40 | 4.80 | 7.20 | 9.60     | 12.00     | 14.40 | 16.80 | 19.20 |

| 0010                | 2.00                      | 2.00 | 4.00 | 6.00 | 8.00     | 10.00     | 12.00 | 14.00 | 16.00 |

| 0011                | 1.71                      | 1.71 | 3.43 | 5.14 | 6.86     | 8.57      | 10.29 | 12.00 | 13.71 |

| 0100                | 1.50                      | 1.50 | 3.00 | 4.50 | 6.00     | 7.50      | 9.00  | 10.50 | 12.00 |

| 0101                | 1.00                      | 1.00 | 2.00 | 3.00 | 4.00     | 5.00      | 6.00  | 7.00  | 8.00  |

| 0110                | 0.80                      | 0.80 | 1.60 | 2.40 | 3.20     | 4.00      | 4.80  | 5.60  | 6.40  |

| 0111                | 0.67                      | 0.67 | 1.33 | 2.00 | 2.67     | 3.33      | 4.00  | 4.67  | 5.33  |

| 1000                | 0.57                      | 0.57 | 1.14 | 1.71 | 2.29     | 2.86      | 3.43  | 4.00  | 4.57  |

| 1001                | 0.50                      | 0.50 | 1.00 | 1.50 | 2.00     | 2.50      | 3.00  | 3.50  | 4.00  |

| 1010                |                           |      |      |      |          |           |       |       |       |

| 1011                |                           |      |      |      |          |           |       |       |       |

| 1100                | Failure Detection Circust |      |      |      |          |           |       |       |       |

| 1101                | Failure Detection Signal  |      |      |      |          |           |       |       |       |

| 1110                |                           |      |      |      |          |           |       |       |       |

| 1111                |                           |      |      |      |          |           |       |       |       |

Fig.10.8.1 Timing Chart of Rotation Pulse Signal at FG pin

#### 10.9. Settings at DIR pin

By setting the registers, the DIR pin can be switched to the following functional pin.

The forward/reverse rotation can be set with the rotation direction input.

The short brake can be set with the short brake input.

As for the Failure Detection Input, the Failure Stare and the Normal Operation can be switched in the same way as the RES pin.

(However, the timing for releasing the Failure State is not the carrier frequency timing as with the RES Pin does, but an immediate release to the Normal operation.)

The Rotation Direction Input, the Short Brake input, and the Failure Detection Input can also be set with the registers.

- Note: Do not set the voltage to the DIR pin to 6.5 V or higher, which is outside range of the Operating Input Voltage, because the device is switched to the Test Mode.

- · During short brake state, the short brake condition is prioritized over SPD=0 and Refresh Operation.

Fig.10.9.1 Setting of Functions at DIR pin

| Register settings       |                  | Settings of input operation         |                          |                                                                |  |

|-------------------------|------------------|-------------------------------------|--------------------------|----------------------------------------------------------------|--|

| 12[2:1]<br>DIR_SEL[1:0] | 12[0]<br>DIR_INV | at DIR pin                          | Input voltage to DIR pin | State of Operation                                             |  |

|                         | 0                | Non-inverted Input of Rotation      | HIGH                     | Reverse Rotation                                               |  |

| 00                      | U                | Direction                           | LOW/OPEN                 | Forward Rotation                                               |  |

| 00                      | 1                | Inverted Input of Rotation          | HIGH                     | Forward Rotation                                               |  |

|                         | -                | Direction                           | LOW/OPEN                 | Reverse Rotation                                               |  |

|                         | 0                | Non-inverted Input of Forward       | HIGH                     | Forward Rotation                                               |  |

| 01                      | U                | Rotation                            | LOW/OPEN                 | Normal Operation                                               |  |

| 01                      | 1                | Inverted Input of Chart Brake       | HIGH                     | Normal Operation                                               |  |

|                         | '                | Inverted Input of Short Brake       | LOW/OPEN                 | Forward Rotation                                               |  |

|                         | 0                | Non-inverted Input of               | HIGH                     | Failure State: Motor Output OFF (Commutation Output = All Low) |  |

| 10                      |                  | Failure Detection                   | LOW/OPEN                 | Normal Operation                                               |  |

| 10                      |                  |                                     | HIGH                     | Normal Operation                                               |  |

|                         | 1                | Inverted Input of Failure Detection | LOW/OPEN                 | Failure State: Motor Output OFF (Commutation Output = All Low) |  |

| 11                      | 0                | Pogistor Sottings                   |                          | Note                                                           |  |

| 11                      | 1                | Register Settings                   | -                        | Note                                                           |  |

Note: The functions of the rotation direction input and short brake input that are not specified in the input operation settings at the DIR pin are the register settings.

As for the Failure Detection Input, either the register settings or the Failure Detection Input at the RES pin can be used to switch to the Failure State.

## **Table10.9.2 Register Settings of Rotation Direction Input**

| Register<br>12[4]<br>DIR | Rotation Direction |

|--------------------------|--------------------|

| 0                        | Forward Rotation   |

| 1                        | Reverse Rotation   |

## Table10.9.3 Register Settings of Short Break Input

| Register<br>12[3]<br>BRK_ON | Short Break      |

|-----------------------------|------------------|

| 0                           | Normal Operation |

| 1                           | Short Break      |

## Table10.9.4 Register Settings of Failure Detection Input at DIR pin

| Register<br>12[5]<br>RES | Failure Detection Input |

|--------------------------|-------------------------|

| 0                        | Normal Operation        |

| 1                        | Failure State           |

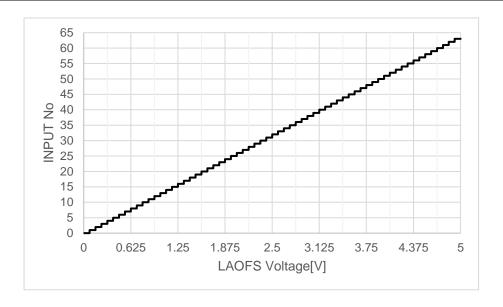

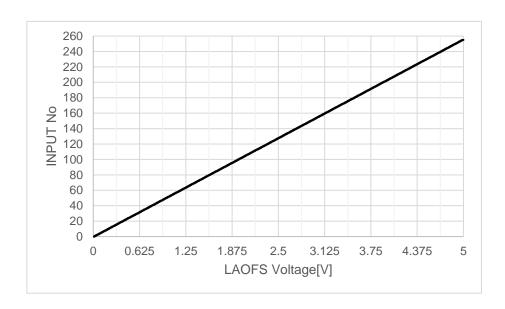

#### 10.10. Setting pins for TC78B043FNG (Settings for HTSSOP28)

In the TC78B043FNG, the control that enables a specific motor to rotate has already been written to NVM as the initial setting. And by adjusting each register setting from the 4 pins (LA, FGC, LATYPE, LAOFS), the motor can be rotated by this Initial Setting without setting registers via SPI Communication. When the default setting is insufficient to rotate the motor and a readjustment of the register setting is required, the readjustment can be performed via SPI Communication. Note: In the case of the TC78B043FTG (WQFN20), the registers of the four pins (LA pin, FGC pin, LATYPE pin, and LAOFS pin) are set Invalid. Please do not set them Valid, because the setting state is

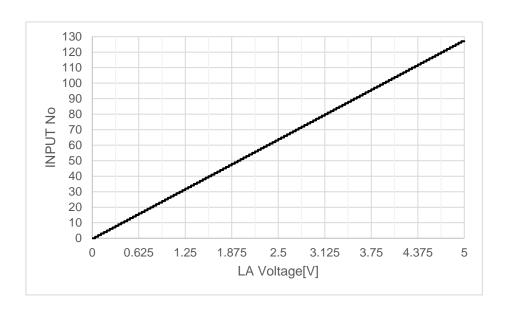

#### 10.11. Settings at LA pin

undefined when they set Valid.

By inputting voltage to the LA pin, the setting of the register LA (maximum Lead value and fixed Lead value) is performed.

And by setting the register Valid or Invalid, the LA pin setting or the Register: LA setting is selectable. For noise suppression, this device is designed as the settings do not change even though the input voltage fluctuates by ±2 LSB.

| Voltage to<br>LA pin | Register name     | Contents of Settings                          | Input<br>range | Range of Setting Figure | Resolution |

|----------------------|-------------------|-----------------------------------------------|----------------|-------------------------|------------|

| 0 to 5 V             | 7[6:0]<br>LA[6:0] | Maximum Lead Angle value<br>/Fixed Lead Angle | 0 to 127       | 0 to 59.5 °             | 60/128     |

Table10.11.1 Setting at LA pin

Table10.11.2 Settings of LA pin and Register: LA Valid/Invalid

| Register settings<br>11[1]<br>VIN_MODE1 | LA pin  | Register<br>7[6:0]<br>LA [6:0] |

|-----------------------------------------|---------|--------------------------------|

| 0                                       | Invalid | Valid                          |

| 1                                       | Valid   | Invalid                        |

Fig.10.11.1 Setting of LA Voltage at LA pin

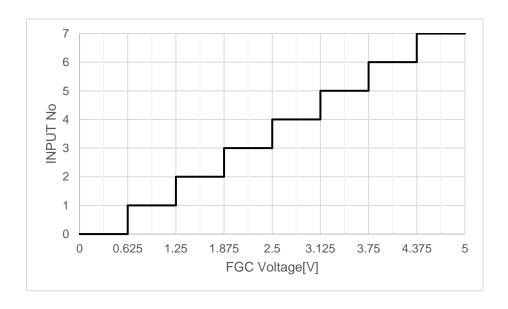

#### 10.12. Setting at FGC pin

By inputting a voltage to the FGC pin, the registers for the number of pulses to the FG pin and for the Sine Wave reset method can be set. At startup, the forced Commutation of Sine Wave (60° reset method)

And by setting the register Valid or Invalid, the setting of Pulse Number to the FG pin or the Register Setting is selectable.

| No | Voltage to FGC pin | Pulses Number<br>to FG pin | Sine Wave Reset Method |

|----|--------------------|----------------------------|------------------------|

| 7  | 4.375V to 5V       | 3 ppr                      | 60 °                   |

| 6  | 3.75V to 4.375V    | 2                          | CO % \ 2CO %           |

| 5  | 3.125V to 3.75V    | 3 ppr                      | 60 °⇔360 °             |

| 4  | 2.5.V to 3.125V    | 0.4 mm                     | 00 044 200 0           |

| 3  | 1.875V to 2.5V     | 2.4 ppr                    | 60 °⇔360 °             |

| 2  | 1.25V to 1.875V    | 0.4 mm                     | 000                    |

| 1  | 0.625V to 1.25V    | 2.4 ppr                    | 60 °                   |

| 0  | 0V to 0.625        | 2.4 ppr                    | 60 °⇔60 °/ 120 °       |

Table10.12.1 Settings at FGC pin

Table10.12.2 Settings of FGC pin and Register Valid/Invalid

| Register settings<br>11[0]<br>VIN_MODE0 | Settings at FGC pin | Register<br>10[3:0]<br>FG_SEL[3:0] | Register<br>2[15:12]<br>PWM_MODE[3:0] |

|-----------------------------------------|---------------------|------------------------------------|---------------------------------------|

| 0                                       | Invalid             | Valid                              |                                       |

| 1                                       | Valid               | Invalid                            |                                       |

Fig.10.12.1 Settings of FGC Voltage at FGC pin

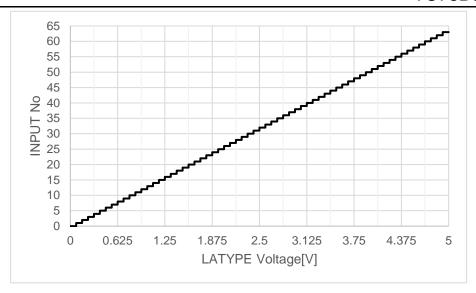

#### 10.13. Setting at LATYPE pin

By inputting a voltage to the LATYPE pin, the Lead Angle Function and for the stop sequence can be set. And by setting the register Valid or Invalid, setting at LATYPELA pin or the register setting is selectable. For noise suppression, this device is designed as the settings do not change even though the input voltage fluctuates by ±1 LSB.

Table10.13.1 Settings at LATYPE pin

| No       | Voltage to LATYPE pin | Lead Angle Function                            | Stopping<br>Sequence |

|----------|-----------------------|------------------------------------------------|----------------------|

| 63       | 4.92                  | Lead Angle in Quadratic Curve:                 |                      |

| 62       | 4.84                  | LAoffset Valid                                 |                      |

| 61       | 4.77                  |                                                |                      |

| 60       | 4.69                  | Lood Apple in Overdrotic Compa                 |                      |

| 59<br>58 | 4.61<br>4.53          | Lead Angle in Quadratic Curve: SPDoffset Valid |                      |

| 57       | 4.45                  | SPDoliset valid                                |                      |

| 56       | 4.38                  |                                                |                      |

| 55       | 4.30                  |                                                |                      |

| 54       | 4.22                  | Lead Angle in Linear Curve:                    |                      |

| 53<br>52 | 4.14<br>4.06          | LAoffset Valid                                 |                      |

| 51       | 3.98                  | LAdiiset valid                                 |                      |