Toshiba Bi-CMOS Linear Integrated Circuits Silicon Monolithic

# TB9084FTG

Automotive Gate Driver for Brushless Motor

# 1. Description

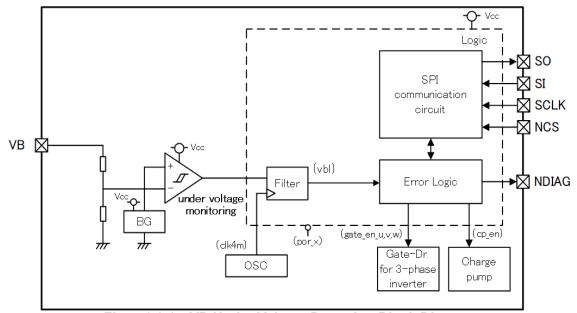

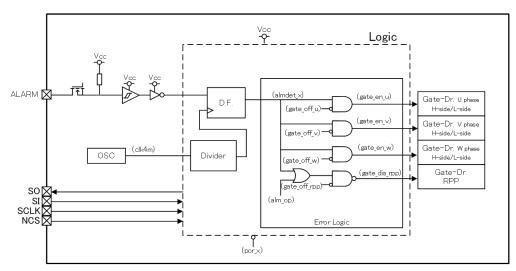

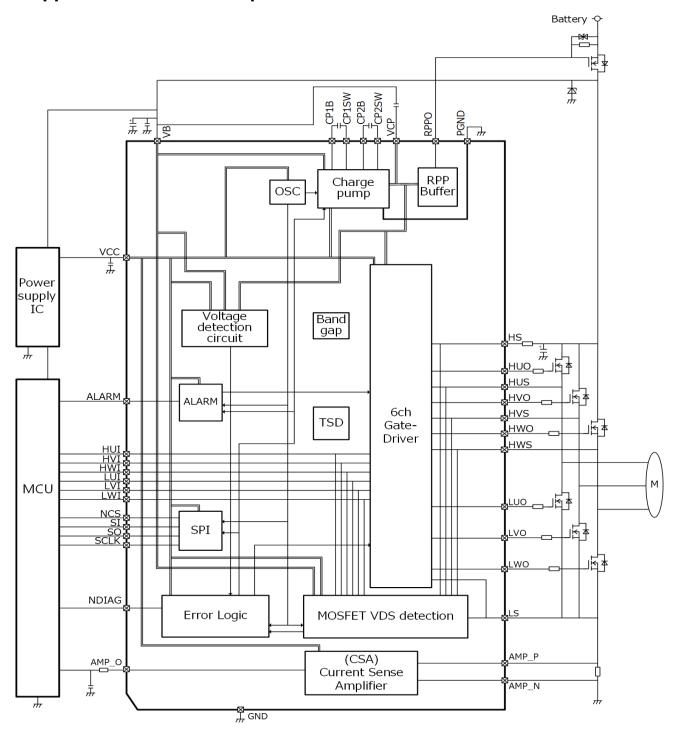

TB9084FTG is a gate driver IC for automotive brushless motors. It is equipped with a charge pump, motor current sensing circuit, oscillation circuit, SPI communication circuit, and multiple types of abnormality detection circuits. In addition, it allows abnormality detection conditions and reaction operation, after abnormality detection to be set by using SPI communication.

#### Weight: 95 mg (typ.)

# 2. Applications

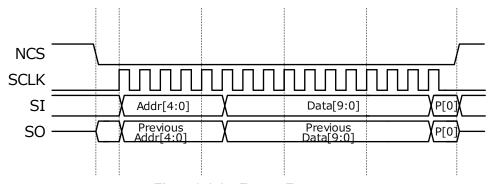

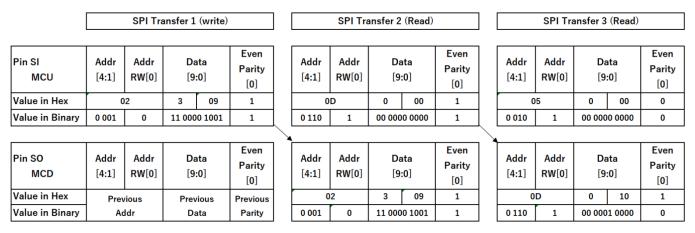

Motor generators, electric oil pumps. Automotive body system applications such as power sliding doors, and power tail gates.

#### 3. Features

- Used in a 12V battery system and a jump start environment (Operating voltage range: VB = 5.7 to 28V)

- MCU with 5V and 3.3V system IO ports controls this product (Operating voltage range: VCC = 3.0 to 5.5V)

- Low reset current at VCC=0V to prevent the battery from running out

- Can be used in a temperature environment for mechanically and electrically integrated type.

- Built-in charge pump circuit (VCP).

- Built-in gate drivers for driving 3-phase FETs (PWM control, up to 20kHz)

- Built-in gate driver (high-side switch) for driving a FET for reverse polarity protection (RPPO)

- Built-in motor current sensing circuit

- Built-in oscillation circuit, 4MHz(Typ.)

- Various built-in abnormality detection circuits VB, VCC, RPPO under voltage/VCC, VCP over voltage/Over temperature/VDS detection of 3-phase FET /Short to VB or GND fault detection for charge pump drive terminals (CP1SW, CP2SW) /SPI communication abnormality detection

- Built-in input circuit for gate driver emergency stop (ALRAM)

- Built-in SPI communication circuit

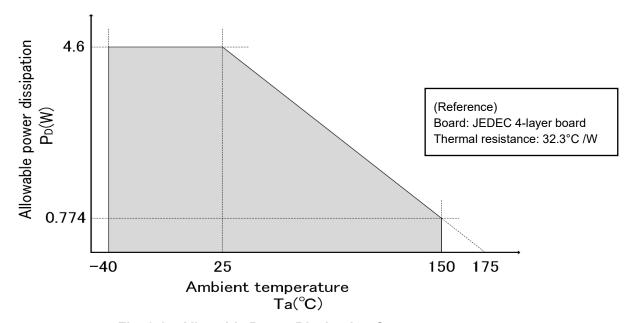

- Ambient temperature (Ta) = -40 to 150°C, Junction temperature (Tj) = -40 to 175°C

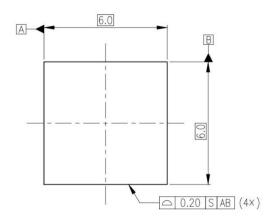

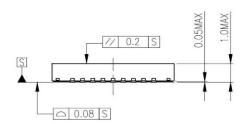

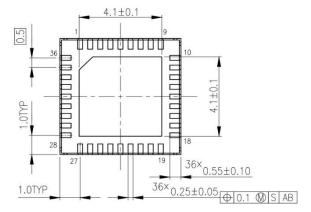

- Package: P-VQFN36-0606-0.50 (Wettable flank, 0.5mm pitch)

- AEC-Q100 (Rev-J), Q006 (Rev-A): Grade 0

Start of commercial production 2025-08

[Notes for Users]

All the functional blocks, circuits, etc. in the block diagrams may be omitted or simplified for explanatory purposes.

Determine the peripheral circuits after thorough evaluation and check on unit boards assuming the operating environment.

Please note that the contents may change without advance notice, because the document status is preliminary one. We apologize for any inconvenience.

When "[[G]]/RoHS COMPATIBLE," "[[G]]/RoHS [[Chemical symbol(s) of controlled substance(s)," "RoHS COMPATIBLE," or "RoHS COMPATIBLE, [[Chemicalsymbol(s) of controlled substance(s)]]>MCV" is written on the packing box label, this product conforms to the EU RoHS Directive (2011/65/EU) as described.

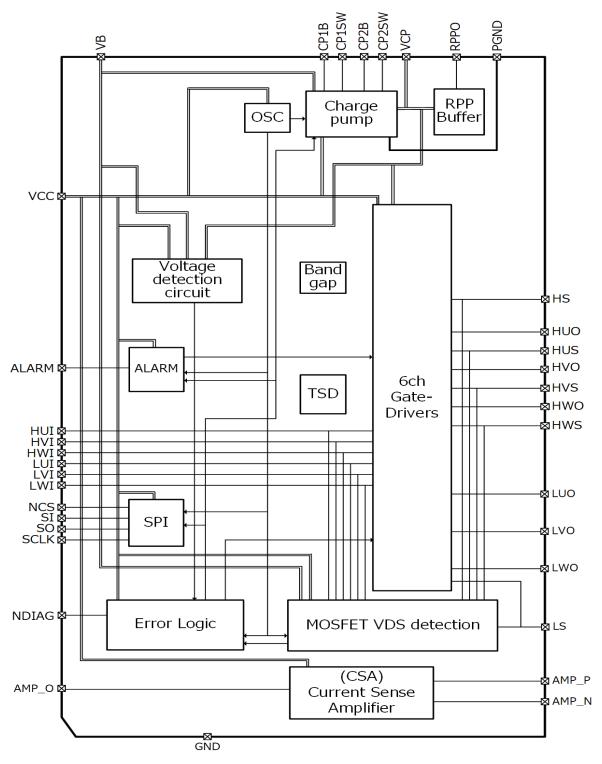

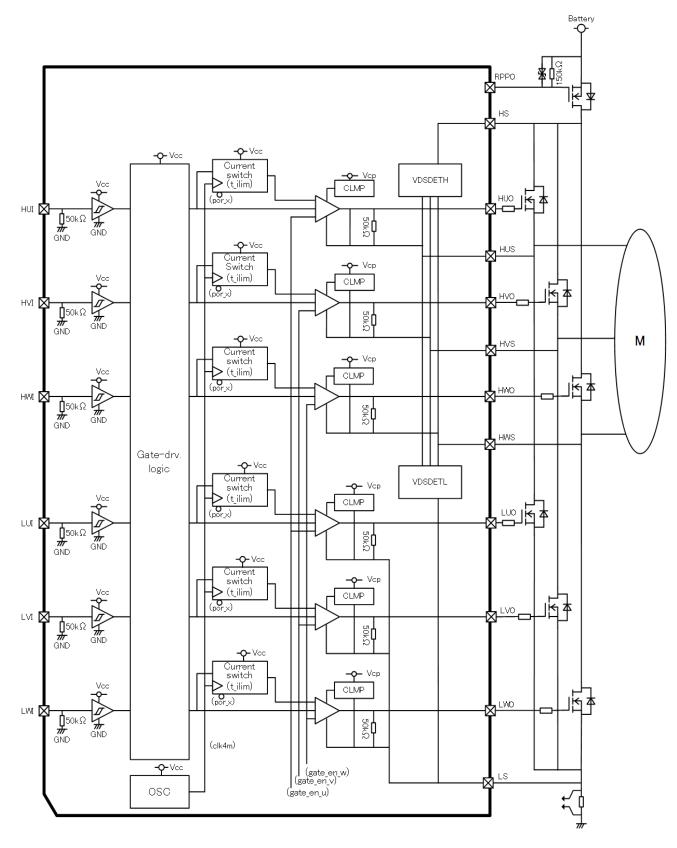

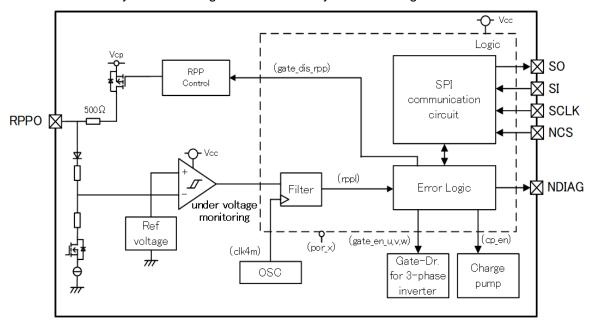

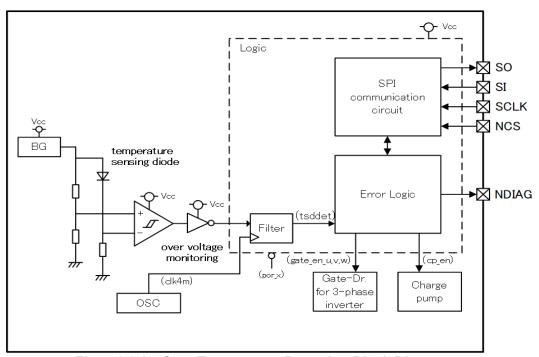

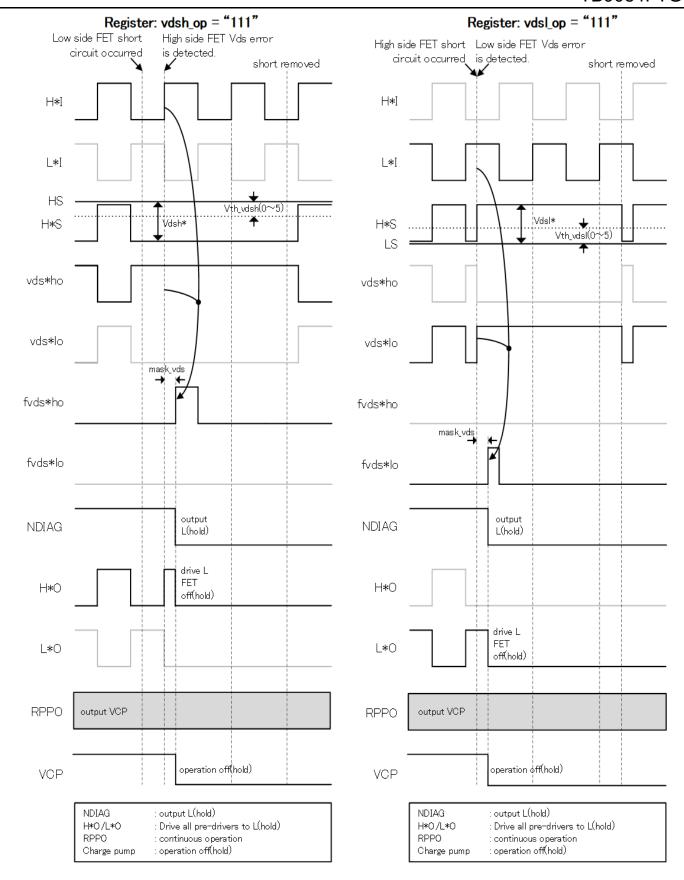

# 4. Block Diagram

Fig. 4.1 Block Diagram

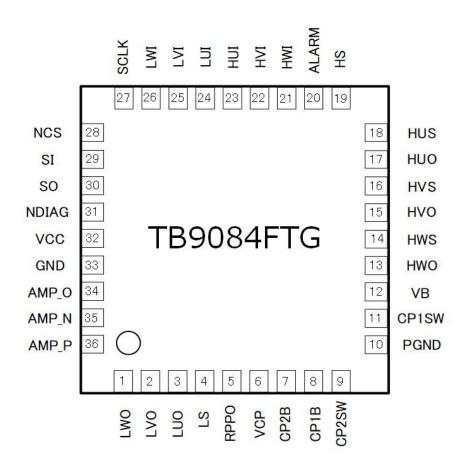

# 5. Pin Assignments Top view

Fig. 5.1 Pin Assignments (top view)

# 6. Pin Description

Table 6.1 Pin Description

| No. | Name  | I/O          | Function                                                                          | Pull-up/down<br>Resistance |  |  |

|-----|-------|--------------|-----------------------------------------------------------------------------------|----------------------------|--|--|

| 1   | LWO   | OUT          | Gate driver output (W phase low-side)                                             | Pull-down to LS            |  |  |

| 2   | LVO   | OUT          | Gate driver output (V phase low-side)                                             | Pull-down to LS            |  |  |

| 3   | LUO   | OUT          | Gate driver output (U phase low-side)                                             | Pull-down to LS            |  |  |

| 4   | LS    | IN           | Reference input for low-side gate drivers                                         | -                          |  |  |

| 5   | RPPO  | OUT          | Output for driving FET for reverse polarity protection                            | -                          |  |  |

| 6   | VCP   | Power supply | Charge pump voltage                                                               | Pull-down to VB            |  |  |

| 7   | CP2B  | I/O          | Charge pump 2 <sup>nd</sup> stage bias voltage                                    | -                          |  |  |

| 8   | CP1B  | I/O          | Charge pump 1 <sup>st</sup> stage bias voltage                                    | -                          |  |  |

| 9   | CP2SW | OUT          | Charge pump 2 <sup>nd</sup> stage drive output                                    | -                          |  |  |

| 10  | PGND  | GND          | Power ground                                                                      | -                          |  |  |

| 11  | CP1SW | OUT          | Charge pump 1 <sup>st</sup> stage drive output                                    | -                          |  |  |

| 12  | VB    | Power supply | External battery power supply                                                     | -                          |  |  |

| 13  | HWO   | OUT          | Gate driver output (W phase high-side)                                            | Pull-down to HWS           |  |  |

| 14  | HWS   | IN           | Gate driver reference input (W phase highside source)                             | -                          |  |  |

| 15  | HVO   | OUT          | Gate driver output (V phase high-side)                                            | Pull-down to HVS           |  |  |

| 16  | HVS   | IN           | Gate driver reference input (V phase highside source)                             | -                          |  |  |

| 17  | HUO   | OUT          | Gate driver output (U phase high side)                                            | Pull-down to HUS           |  |  |

| 18  | HUS   | IN           | Gate driver reference input (U phase high-<br>side source)                        | -                          |  |  |

| 19  | HS    | IN           | VDS detection input of 3-phase FET (high-side)                                    | -                          |  |  |

| 20  | ALARM | IN           | Gate driver emergency stop input                                                  | Pull-up to VCC             |  |  |

| 21  | HWI   | IN           | Gate driver input (W phase high-side)                                             | Pull-down to GND           |  |  |

| 22  | HVI   | IN           | Gate driver input (V phase high-side)                                             | Pull-down to GND           |  |  |

| 23  | HUI   | IN           | Gate driver input (U phase high-side)                                             | Pull-down to GND           |  |  |

| 24  | LUI   | IN           | 6-input mode (Polarity during power-on: "L") Gate driver input (U phase low-side) | Pull-down to GND           |  |  |

| 25  | LVI   | IN           | 6-input mode (Polarity during power-on: "L") Gate driver input (V phase low-side) | Pull-down to GND           |  |  |

| 26  | LWI   | IN           | 6-input mode (Polarity during power-on: "L") Gate driver input (W phase low-side) | Pull-down to GND           |  |  |

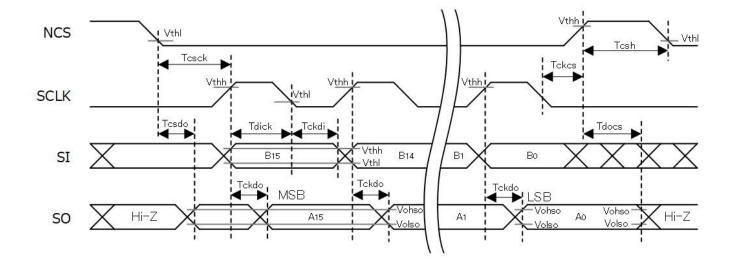

| 27  | SCLK  | IN           | SPI clock input                                                                   | Pull-down to GND           |  |  |

| 28  | NCS   | IN           | SPI chip select                                                                   | Pull-up to VCC             |  |  |

| 29  | SI    | IN           | SPI input                                                                         | Pull-down to GND           |  |  |

| 30  | SO    | OUT          | SPI output                                                                        | -                          |  |  |

| 31  | NDIAG | OUT          | Error output                                                                      | -                          |  |  |

| 32  | VCC   | Power supply | External 5V/3.3V power supply                                                     | -                          |  |  |

| 33  | GND   | GND          | Analog, digital ground                                                            | _                          |  |  |

| 34  | AMP O | OUT          | Current sensing amplifier output                                                  | -                          |  |  |

| 35  | AMP N | IN           | Current sensing amplifier (-) input                                               | -                          |  |  |

| 36  | AMP P | IN           | Current sensing amplifier (+) input                                               | -                          |  |  |

# 7. Functional Description

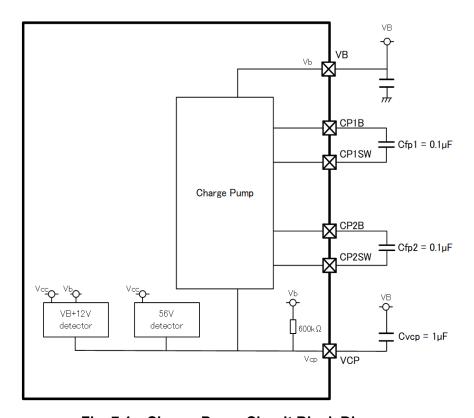

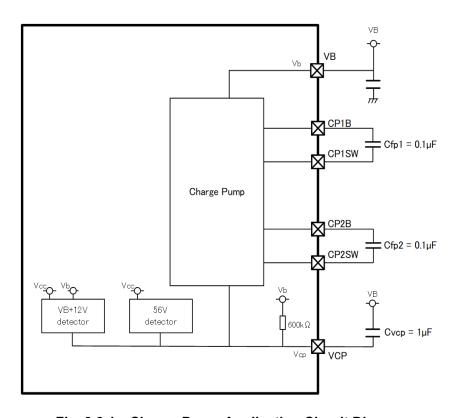

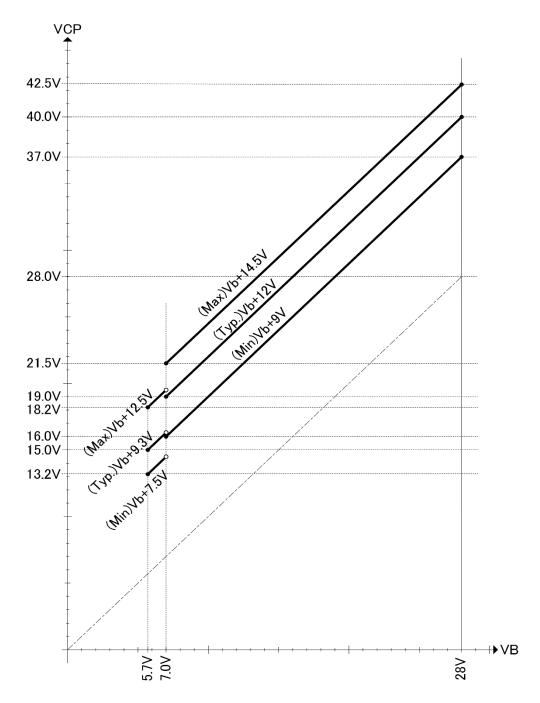

#### 7.1. Charge Pump Circuit

This product has a built-in charge pump circuit for the gate drivers to drive 3-phase FETs. The drive frequency is 250kHz (Typ.) as long as the switching operation is not stopped. With this drive frequency, the VB voltage is pumped up. The charge pump circuit requires two external ceramic capacitors.

The pumping up operation in the the circuit stops under the conditions below.

When Vcp > Vb+12V (Typ.) so that Vcp is not above the Vgs rating (±20V) of the 3-phase FET, its switching operation is stopped by the control of the internal circuit, and when Vcp≤Vb+12V (Typ.), its operation is resumed.

When Vb voltage is low and Vcp is lower than Vb+12V (Typ.), Vcp outputs characteristics depending on the charge pump circuit configuration and its capability.

In addition, when Vcp > 56V (Typ.) so that Vcp withstand voltage is not exceeded, detection operation is conducted depending on the register setting by SPI communication. And when Vcp≤56V (Typ.), detection release operation is conducted depending on the register setting by SPI communication as well. For details, see Chapter 7.6.5.

When the charge pump circuit is turned off after an abnormality detection, VCP voltage transitions to VB voltage.

Note: When a fault is detected and the charge pump circuit is turned off and a certain period has passed after the fault release, the motor operation is enabled. Details are shown in Chapter 7.6.

When the reset of this product is released, charge pump operation is started, and after the voltage has become sufficient, the gate driver operation is allowed. This sequence is to prevent the gate driver from malfunctioning. For details, see Fig. 7.6.1.2.

When an adjacent short circuit or a short to VB or ground of CP1SW terminal and CP2SW happen, the internal elements are protected with the abnormality detection circuits. The details are shown in chapter 7.6.8.

Fig. 7.1 Charge Pump Circuit Block Diagram

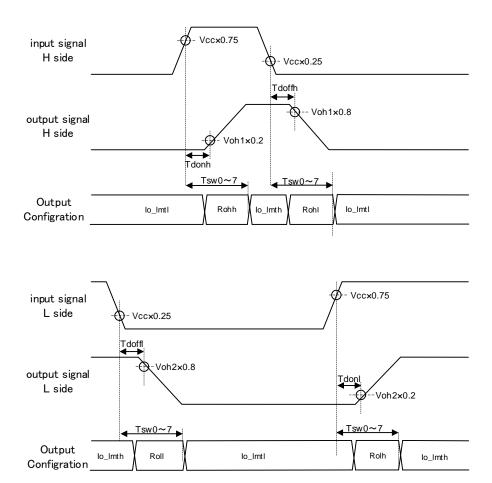

#### 7.2. Gate Driver Circuits

As a gate driver to drive external FETs (7 units), this product is equipped with gate drivers (6 units) for 3phase FETs and a gate driver (1 unit) for a FET for reverse polality protection.

### 7.2.1. Gate Drivers for Driving 3-Phase FETs

The gate driver circuits for 3-phase FETs are for high-side drive and low-side drive for motor drive. Each of the gate driver circuits for high-side drive and low-side drive has an input terminal. This input terminal turns off the gate driver when an open fault happens.

The gate driver circuit has 6 output terminals to drive a 3-phase FET. The output stage configuration is of a switch type, and an external series resistor is recommended depending on the operation speed needed for the 3-phase FET.

For a gate driver that drives a high-side FET, when VB voltage is high enough, voltage clamped at H\*S reference +10V is output. When VB voltage is low, charge pump voltage with GND reference is output via an internal switch so that enough voltage is applied to the FET gate, and the output voltage is 20V or lower not exceeding the Vgs withstand voltage of the FET. On the other hand, since a gate driver that drives a low-side FET is given Vcp power supply voltage enough to drive in the Vb operating voltage range, voltage clamped at LS reference +11V is always output. These outputs have electric current capability suitable for controlling FET gate that drives motors for applications shown in Chapter 2, and the propagation delay time from the input terminal to the output terminal and the relative deference time for on/off time and off/on time of high side and low side respectively on each phase are optimized. In addition, it has a pull-down resistor to stably turn the FET on and off while the motor's phase input is in Hi-Z state.

Note that when a 3-phase FET is turned off, the effect of the electric current from H\*S terminal of this product on the motor operation is negligible.

H\*S terminal and LS terminal are robust enough against noise exceeding VB and noise below GND.

Fig. 7.2.1.1 Gate Driver Circuits Block Diagram

### <High-side drive circuit, Low-side drive circuit>

A high-side drive circuit drives a high-side 3-phase FET. A low-side drive circuit drives a low-side 3-phase FET. This product is equipped with 3 channels of high-side and low-side circuits each. Input signals (HUI/HVI/HWI, LUI/LVI/LWI) are converted in the control block to generate output signals (HUO/HVO/HWO, LUO/LVO/LWO).

#### **Current Limit Function**

To protect this product from a short to power or ground, electric current of high-side drive and low-side drive circuits after a turn-on/turn-off is switched to a limited current (lo Imth/lo Imtl) after a set time "t ilim" ("000" to "111") of CONFIG4 register.

#### **Prohibited Input Detection**

Note: "\*" means u, v and w or U, V and W.

This function is to prevent through-current from being generated by both upper and lower FETs in the same phase being turned on by an input signal. The truth table is shown in Table 7.2.1.1. The behavior when H\*I=L\*I="H" regardless of the period when the gate driver is enabled or disable (gate en \*="H" or "L") can be selected by pl op register in CONFIG4.

When pl\* dis bit is "L," the input prohibition mode is enabled and the output is H\*O=L\*O="L." At this time, whether the status register is set to "H" or NDIAG="L" can be selected by ploop.

When pl\_op is set to "H," set err\_pl\_\* to "H." When pl\_op="L," do not set err\_pl\_\* to "H." NDIAG terminal follows the status register. To turn off a gate driver circuit for driving a 3-phase FET (6ch), drive the gate driver to "L" so that the FET that drives the motor is turned off. Turning off a gate driver circuit for driving a 3-phase FET (2ch) of a detected phase means driving the gate driver to "L" so that the H/L part FET of the detected phase is turned off.

When pl\* dis="H," detection of prohibited input itself is disabled, and the output can be H\*O=L\*O="H" For details of the internal signals (gate en \*) in the truth table, see chapter 7.7.

Table 7.2.1.1 I/O Truth Table (High-side, Low-side drive circuits)

FET Drive Circuit( "\*" means u, v and w or U, V and W)

| I E I BIIVO OIIV   |       | iio a, v ai |                     | -,    | , , ,  | ·   |          |                                          |                                    |                                       |                                          |  |  |  |  |     |     |     |     |   |                                       |

|--------------------|-------|-------------|---------------------|-------|--------|-----|----------|------------------------------------------|------------------------------------|---------------------------------------|------------------------------------------|--|--|--|--|-----|-----|-----|-----|---|---------------------------------------|

| Internal<br>Signal | Input |             | Register<br>Setting |       | Output |     | status   | Remarks                                  |                                    |                                       |                                          |  |  |  |  |     |     |     |     |   |                                       |

| (gate_en_*)        | H*I   | L*I         | pl*_dis             | pl_op | H*O    | L*O | err_pl_* |                                          |                                    |                                       |                                          |  |  |  |  |     |     |     |     |   |                                       |

|                    | "L"   | Х           | Х                   | Χ     |        |     | -        | Inactive                                 |                                    |                                       |                                          |  |  |  |  |     |     |     |     |   |                                       |

|                    | Χ     | "L"         | Х                   | Χ     |        |     | -        | illactive                                |                                    |                                       |                                          |  |  |  |  |     |     |     |     |   |                                       |

| "L"                | "H"   | "H"         |                     |       | "0"    | "0" | "L"      | "L"                                      | -                                  | Prohibited Input Mode, Without Status |                                          |  |  |  |  |     |     |     |     |   |                                       |

|                    |       |             | "H"                 | "0"   | "1"    |     |          | "set"                                    | Prohibited Input Mode, With Status |                                       |                                          |  |  |  |  |     |     |     |     |   |                                       |

|                    |       |             |                     |       |        | "1" | Χ        | Х                                        |                                    | -                                     | Prohibited Input Mode Disabled (U phase) |  |  |  |  |     |     |     |     |   |                                       |

|                    | "L"   | "L"         | Х                   | Χ     | "L"    | "L" | -        |                                          |                                    |                                       |                                          |  |  |  |  |     |     |     |     |   |                                       |

|                    | "L"   | "H"         | Х                   | Χ     | "L"    | "H" | -        | Active                                   |                                    |                                       |                                          |  |  |  |  |     |     |     |     |   |                                       |

| "H"                | "H"   | "L"         | Х                   | Χ     | "H"    | "L" | -        |                                          |                                    |                                       |                                          |  |  |  |  |     |     |     |     |   |                                       |

| 17                 |       |             |                     |       |        |     |          |                                          |                                    |                                       |                                          |  |  |  |  | "0" | "0" | "L" | "L" | - | Prohibited Input Mode, Without Status |

|                    | "H"   | "H"         | "0"                 | "1"   | "L"    | "L" | "set"    | Prohibited Input Mode, With Status       |                                    |                                       |                                          |  |  |  |  |     |     |     |     |   |                                       |

|                    |       |             | "1"                 | Χ     | "H"    | "H" | -        | Prohibited Input Mode Disabled (U phase) |                                    |                                       |                                          |  |  |  |  |     |     |     |     |   |                                       |

Note: X means "Don't care"

Note: NDIAG terminal is linked with the status. The status can be cleared by setting err pl \* cl bit.

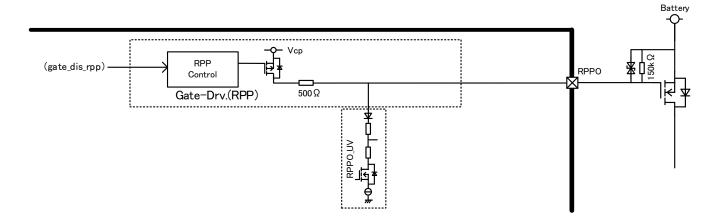

#### 7.2.2. Gate Driver for FET for Reverse Polarity Protection

The gate driver for FET for reverse polarity protection is a circuit that drives FET placed between the battery and 3-phase FETs. Even when the FET for reverse polarity protection is turned off with the battery correctly connected, the battery provides current to 3-phase FETs through the body diode of the FET. When the battery is reversely connected, by turning the FET off via RPPO terminal, reverse current to the battery is shut off. In addition, this product has built in a  $500\Omega$  output series resistor and a diode that shuts off reverse current from the ground of the under voltage detection circuit when reversely connected.

This product is equipped with a switch that shuts off current flowing from RPPO terminal to GND via RPPO UV in the reset state.

#### Drive Circuit for FET for Reverse polarity Protection (Gate-Drv.RPP)

The drive circuit for FET for reverse polarity protection is configured with a high-side switch. This switch is always ON as long as it has not received a disable signal (gate dis rpp).

Fig. 7.2.2.1 Gate Driver Circuit for FET for Reverse Polarity Protection

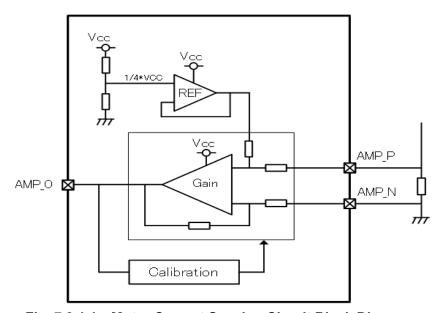

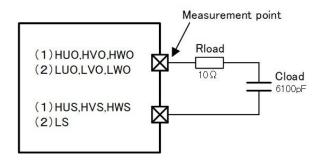

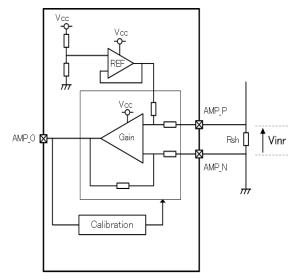

## 7.3. Current Sensing Circuit

#### 7.3.1. Configuration

This circuit has built in an amplifier for motor current sensing and an amplifier for generating reference voltage. The amplifier for generating reference voltage generates reference voltage based on Vcc voltage.

The motor current sensing amplifier amplifies differential voltage generated by the current flowing in external shunt resistor connected to the GND of the motor drive part. This amplified voltage is output from the reference voltage toward Vcc. Note that the direction of the motor current that can be sensed is from the power supply to GND only.

The gain can be set by SPI communication. The amplified voltage is output from AMP O, and it is recommended that external low-pass filter is inserted between AMP O and MCU to reduce noise. Performing calibration with no current flowing in the motor to correct offset variation among individual units improves output voltage accuracy. Note that the input voltage range in which this accuracy improvement can be expected is the one that has considered the voltage operating point of the shunt resistor in normal time. When a resistor is connected to the input terminal, it may cause another gain error.

In addition, this circuit has specific tolerance to noise of VCC power supply and noise around the shunt resistor.

Fig. 7.3.1.1 Motor Current Sensing Circuit Block Diagram

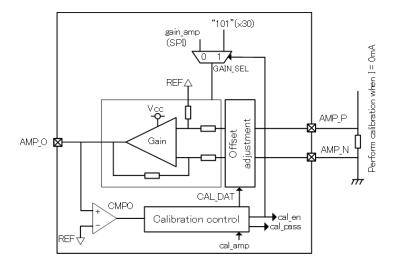

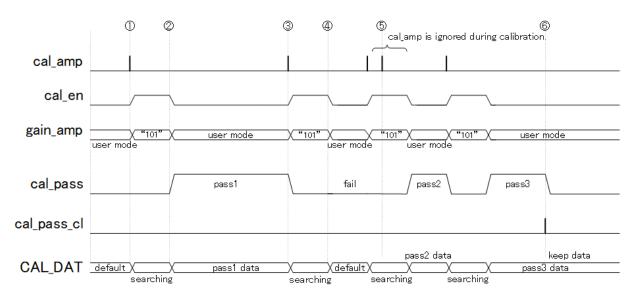

#### 7.3.2. Offset Calibration

Perform offset calibration when the input differential voltage is the same voltage (0V). When the input differential voltage is not zero, the calibration is not performed correctly.

By setting **CONFIG5** register: cal\_amp="1," calibration is started and cal\_en="1." During the calibration, gain amp ="101" (30 times) (fixed). During calibration, since the offset correction value is being searched for by comparing amplifier output and REF by changing CAL DAT. When the calibration is completed, cal en="0" and it is set to cal pass. When cal pass="1" is given, the result is kept as it is and used as an adjustment value. When cal pass="0" is given, the adjustment result is discarded and returned to the default value at reset. When next calibration is started, cal pass is automatically cleared to "0." By writing "1" to cal pass cl bit(STAT1 CLR), cal pass can be cleared at any time, but CAL DAT data is maintained. While cal en is "1," calibration is being performed, and even if cal amp is set during this period, it is discarded.

Fig. 7.3.2-1 Offset Calibration Block Diagram

Fig. 7.3.2-2 Performing Offset Calibration

Note: Please note that this product is not equipped with a function that automatically connects AMP P, and AMP N terminals to GND.

Note: Since this product adopts a single-shunt configuration, please select components while considering the increase current flowing through the shunt resistor compared to a three-shunt configuration.

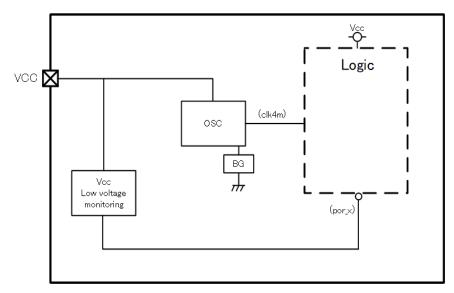

### 7.4. Oscillation Circuit

The oscillation circuit has built-in CR, and its frequency is 4MHz (Typ.).

Fig. 7.4.1 Oscillation Circuit Block Diagram

Fig. 7.4.2 Oscillation Circuit Timing Chart

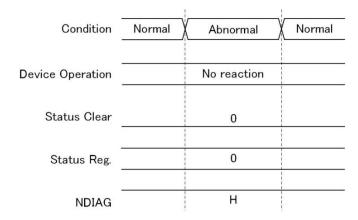

## 7.5. Abnormality Flag Output Function

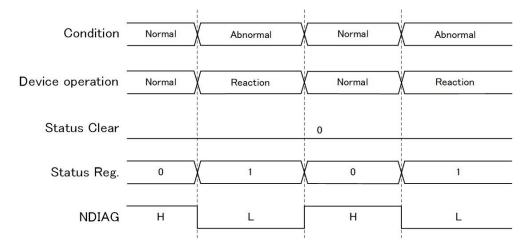

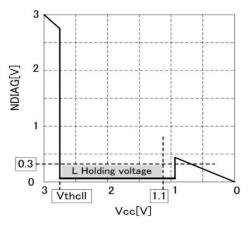

#### 7.5.1. NDIAG Terminal Output

When this product does not detect abnormality, NDIAG terminal outputs "H."

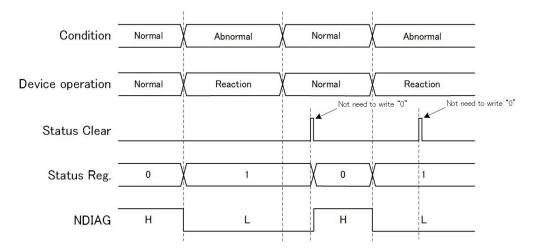

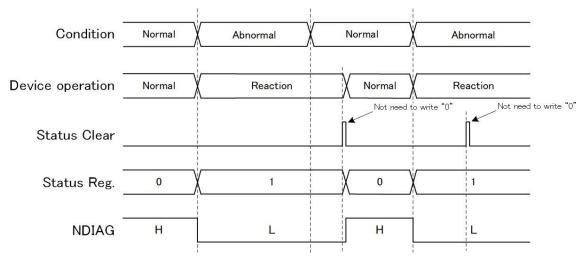

When this product has detected abnormality, NDIAG terminal outputs "L" or "H" depending on SPI communication setting.

Table 7.5.2.1 shows a list of abnormality detection functions in this product. In operation modes with "H" in the NDIAG column, NDIAG terminal does not become "L" even when an abnormality is detected. In operation modes with "L" in the NDIAG column, NDIAG terminal follows the status register of SPI communication (except VCC under voltage detection). While "1" is latched in the status register, NDIAG="L" is output, and returns to NDIAG="H" when all status registers are cleared to "0." In operation modes where the status register is not latched at "1," NDIAG returns to "NDIAG="H" when the abnormality detection is resolved even if the status register is not cleared.

To avoid MCU misdetection caused by NDIAG terminal output reversing from "L" to "H" when VCC voltage goes below the under voltage detection criterion, NDIAG terminal maintains "L" until specified VCC voltage.

#### 7.5.2. Status Registers in SPI communication

In settings with "-" in the Status Reg. column in Table 7.5.2.1, the status register does not become "1" even when abnormality is detected.

In settings with a status name in the Status Reg. column, "0" is set when abnormality is not detected, and "1" is set when abnormality is detected.

#### Status Clear

In settings with "-" in the Status Clear column in Table 7.5.2.1, the status bit is cleared accordingly when abnormality condition leaves.

In settings with a status clear name in the Status Clear column, when "1" is entered into the status register caused by abnormality detection, the bit remains latched after the abnormality leaves (NDIAG remains latched). To clear the latched bit, write "1" for the status clear bit (NDIAG returns to H).

When an abnormality condition doesn't leave, the latched bit cannot be cleared.

In settings with (Latched) written in the "Operation at Detection" column, it is latched with the written operation. To return to the normal operation when abnormality leaves, clear the status register. In settings with (Latched) not written in the "Operation at Detection" column, the operation accordingly returns to normal when the abnormality leaves even if the status register is not cleared.

**Table 7.5.2.1 Abnormality Detection Circuits**

| Abnormality<br>Detection<br>Circuit | Setting<br>Reg.<br>[Note 1] | Setti<br>ng<br>bit | Operation at Detection [Note 2] [Note 3]                                |                                                                      | Status<br>Reg.                                           | Status<br>Clear | NDI<br>AG |         |     |

|-------------------------------------|-----------------------------|--------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------|-----------------|-----------|---------|-----|

| VCC under<br>voltage                | None                        | 1                  | All gate drivers of 3-phase drive FETs to off.<br>Turn off charge pump. | -                                                                    | -                                                        | -               | "L"       |         |     |

| VB under                            | uvb<br>_op                  | "0"                | All gate drivers of 3-phase drive FETs to off.                          | -                                                                    |                                                          | uvb_cl          |           |         |     |

| voltage                             |                             | "1"                | All gate drivers of 3-phase drive FETs to off.<br>Turn off charge pump. | Х                                                                    | uvb                                                      | -               | "L"       |         |     |

|                                     | ovcp_op                     | "000"              | Disable detection.                                                      | Χ                                                                    | -                                                        | -               | "H"       |         |     |

|                                     |                             | ovcp_op_           | "001"                                                                   | Continue operation.                                                  | -                                                        |                 |           |         |     |

|                                     |                             |                    | "010"                                                                   | All gate drivers of 3-phase drive FETs to off.                       | -                                                        |                 |           |         |     |

| VCP over                            |                             |                    | ovcp op                                                                 |                                                                      | All gate drivers of 3-phase drive FETs to off (Latched). | -               | oven      | oven el | "[" |

| voltage                             |                             |                    |                                                                         | All gate drivers of 3-phase drive FETs to off. Turn off charge pump. | -                                                        | ovcp            | ovcp_cl   | _       |     |

|                                     |                             | "101"              | All gate drivers of 3-phase drive FETs to off (Latched).                | -                                                                    |                                                          |                 |           |         |     |

|                |           |           |                                                  |                                                  |                  | B9084                                          | ГІС                |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|----------------|-----------|-----------|--------------------------------------------------|--------------------------------------------------|------------------|------------------------------------------------|--------------------|------------|------------------------------------------------|----------------|---------|----|------|---|--|----------------------------------------------------------------------|--|--|--|--|

|                |           |           | Turn off charge pump (Latched)                   |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "000"     | Disable detection.                               | -                                                | -                | -                                              | "H"                |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "001"     | Continue operation.                              | -                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "010"     | All gate drivers of 3-phase drive FETs to off.   | -                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "044"     | All gate drivers of 3-phase drive FETs to off    | V                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| VCC over       | 01/00 00  |           | l(Latched).                                      | Χ                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| voltage        | ovcc_op   | "400"     | All gate drivers of 3-phase drive FETs to off.   | V                                                | ovcc             | ovcc_cl                                        | "L"                |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | 100       | Turn off charge pump.                            | Χ                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | All gate drivers of 3-phase drive FETs to off    |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "101"     | (Latched).                                       | -                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | Turn off charge pump (Latched).                  |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "000"     | Disable detection.                               | -                                                | -                | -                                              | "H"                |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "001"     | Continue operation.                              | Χ                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| RPP under      | uvrpp_o   | "∩1∩"     | All gate drivers of 3-phase and a gate driver of | Χ                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| voltage        |           | 010       | reverse polarity protection drive FETs to off.   |                                                  | uvrpp            | uvrpp_cl                                       | "L"                |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| voltage        | р         | "011"     | All gate drivers of 3-phase drive FETs to off.   | -                                                | uvipp            | uvipp_ci                                       | _                  |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "100"     | All gate drivers of 3-phase drive FETs to off    |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | (Latched).                                       |                                                  |                  |                                                | L                  |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | Disable detection.                               | -                                                | -                | -                                              | "H"                |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | Continue operation.                              | -                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "010"     | All gate drivers of 3-phase drive FETs to off.   | Χ                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                | tsd_op    | tsd op    | tsd on                                           | tsd on                                           | "011"            | All gate drivers of 3-phase drive FETs to off  | _                  |            |                                                | //• ·          |         |    |      |   |  |                                                                      |  |  |  |  |

| Thermal        |           |           |                                                  |                                                  |                  | (Latched).                                     |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| shutdown       |           | "100"     | All gate drivers of 3-phase drive FETs to off.   | _                                                | tsd              | tsd_cl                                         | "L"                |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | 100       | Turn off charge pump.                            | -                                                | -                |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | All gate drivers of 3-phase drive FETs to off    |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "101"     | (Latched).                                       | -                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | Turn off charge pump (Latched).                  |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | Disable detection.                               | -                                                | -                | -                                              | "H"                |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                | vdsh_op - |           | "001"                                            | Continue operation.                              | -                |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "010"     | H/L gate drivers of detected phase drive FETs to | -                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | ΙΟΠ                                              |                                                  | -                |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | vdsh_op   | "011"                                            | H/L gate drivers of detected phase drive FETs to | -                |                                                | vds_uh_            |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| Vds of 3-phase |           |           | vdsh_op                                          | vdsh_op                                          |                  |                                                |                    |            | "400"                                          | off (Latched). |         | ┨  | cl – | İ |  |                                                                      |  |  |  |  |

| FET            |           |           |                                                  |                                                  |                  | All gate drivers of 3-phase drive FETs to off. | -                  | vds_uh     | vds_vh_                                        | "L"            |         |    |      |   |  |                                                                      |  |  |  |  |

| (High side)    |           | "101"     | All gate drivers of 3-phase drive FETs to off    | Χ                                                | vds_vh<br>vds_wh | cl                                             |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           |                                                  |                                                  |                  |                                                |                    | (Latched). |                                                | VUS_WII        | vds_wh_ |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           |                                                  |                                                  |                  |                                                |                    | "110"      | All gate drivers of 3-phase drive FETs to off. | -              |         | cl |      |   |  |                                                                      |  |  |  |  |

|                |           |           |                                                  |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  | Turn off charge pump.  All gate drivers of 3-phase drive FETs to off |  |  |  |  |

|                |           |           |                                                  |                                                  |                  |                                                |                    |            | "111"                                          | (Latched).     |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | 111                                              | Turn off charge pump (Latched).                  | -                |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           |                                                  |                                                  |                  | "∩∩∩"                                          | Disable detection. | _          | _                                              | _              | "H"     |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | Continue operation.                              |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | 001       | H/L gate drivers of detected phase drive FETs to |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| Vds of 3-phase |           | "010" off | off                                              | -                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | H/L gate drivers of detected phase drive FETs to |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "011"     | off (Latched).                                   | -                                                |                  | vds_ul                                         |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "100"     | All gate drivers of 3-phase drive FETs to off.   | -                                                | vds_ul           | _cl                                            |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| FET            |           |           | All gate drivers of 3-phase drive FETs to off    | .,                                               | vds_vl           | vds_vl                                         | "L"                |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| (Low side)     |           | "101"     | (Latched).                                       | X                                                | vds_wl           | _cl                                            |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | All gate drivers of 3-phase drive FETs to off.   |                                                  | _                | vds_wl                                         |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "110"     | Turn off charge pump.                            | -                                                |                  | _cl                                            |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | All gate drivers of 3-phase drive FETs to off    |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           | "111"     | (Latched).                                       | -                                                |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           | Turn off charge pump (Latched).                  |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| CP1SW,         | cpsw_de   | "0"       | Continue operation                               | Х                                                | cp1sw            | cp1sw                                          | "L"                |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

|                |           |           |                                                  |                                                  |                  |                                                |                    |            |                                                |                |         |    |      |   |  |                                                                      |  |  |  |  |

| CP2SW<br>terminal<br>abnormality<br>detection | t_op  |     | All gate drivers of 3-phase drive FETs to off.<br>Turn off charge pump (Latched).                     | - | _det<br>cp2sw<br>_det            | _det_cl<br>cp2sw<br>_det_cl                           |     |

|-----------------------------------------------|-------|-----|-------------------------------------------------------------------------------------------------------|---|----------------------------------|-------------------------------------------------------|-----|

|                                               |       | "0" |                                                                                                       | Χ | -                                | -                                                     | "H" |

| Gate driver<br>prohibited<br>input            | pl_op | "1" | In the case of pl*_dis="L", H/L gate drivers of detected phase as prohibited input drive FETs to off. |   | err_pl_u<br>err_pl_v<br>err_pl_w | err_pl_u<br>_cl<br>err_pl_v<br>_cl<br>err_pl_w<br>_cl | "L" |

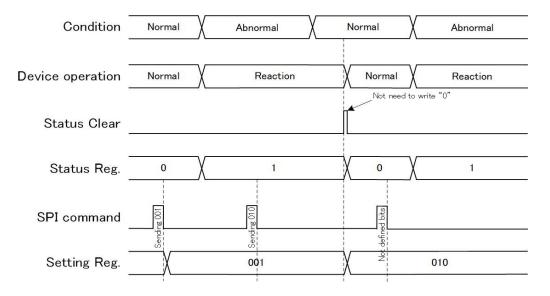

- [Note 1] The value of the setting register "xxxx\_op" for each detection function can be changed at any time, but the "xxxx op" setting is not reflected in the actual operation while the status register for its respective detection function is indicating that abnormality has been detected.

- [Note 2] When the charge pump is turned off, the internal driver is stopped and voltage around VB is output at VCP terminal.

- [Note 3] When all (7ch) gate driver circuits are turned off, the gate drivers are driven to "L" so that 3-phase FETs are turned off, and the high side switch is turned off so that the FET for reverse polarity protection is turned off. When gate driver circuits (6ch) for driving 3-phase FETs are turned off, the gate drivers are driven to "L" so that the FETs that drive the motor are turned off. When gate driver circuits (2ch) for driving 3-phase FETs of a detected phase are turned off, the gate drivers are driven to "L" so that both high side and low side FETs of the detected phase are turned off.

When Status Reg. is "-" and Status Clear is "-"

Fig. 7.5.2.2 When Operation at Detection is not "(Latched)," a bit name is in Status Reg. column, and no bit name is in Status Clear column

Fig. 7.5.2.3 When Operation at Detection is not "(Latched)," a bit name is in Status Reg. column, and a bit name is in Status Clear column

Fig. 7.5.2.4 When Operation at Detection is "(Latched)," a bit name is in Status Reg. column, and a bit name is in Status Clear column

Fig. 7.5.2.5 How to Change Setting Reg.

## 7.6. Abnormality Detection Circuits

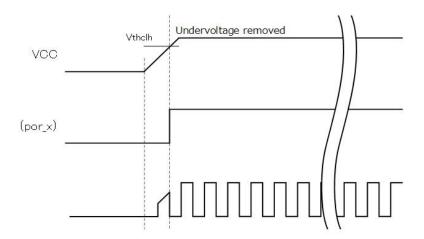

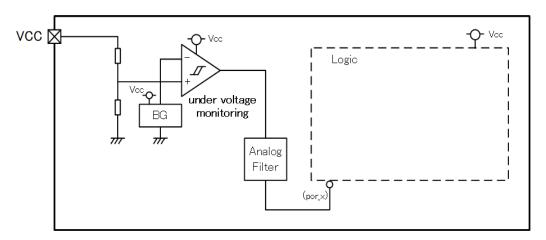

## 7.6.1. VCC Under Voltage Detection Function

The VCC under voltage detection circuit monitors voltage at VCC terminal to detect I under voltage. After detection, this product goes into a reset state. The detection comparator has hysteresis to prevent its output from chattering at the time of detection and detection release. In addition, this circuit ignores noise superimposed on VCC with a response time of 20us (Typ.).

Fig. 7.6.1.1 VCC Under Voltage Detection Block Diagram

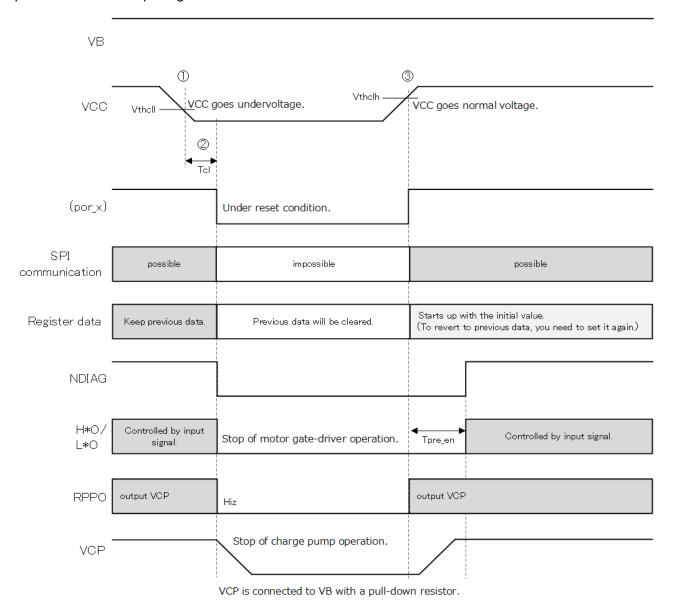

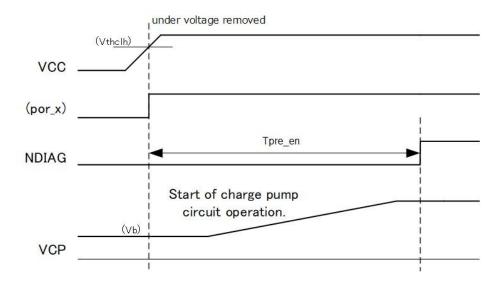

#### (1)VCC voltage goes down

When VCC voltage goes below the detected under voltage Vthcll, detection operation is started.

#### (2)VCC under voltage is detected

After a response time of Tcl, (por\_x)="L," NDIAG="L" is output, and the gate driver circuits for driving 3phase FETs are turned off. Until the under voltage is released, each circuit maintains its off state.

#### (3)VCC voltage recovers (Under voltage release)

When VCC voltage goes above Vthclh, the under voltage is released and (por x)="H."

Soon after that, charge pump circuit starts operation and the gate driver circuit for driving the FET for reverse polarity protection is turned on.

After Tpre en has passed from (por x)="H," NDIAG="H" is output, and the gate driver circuits for driving 3phase FETs follow input signals.

Fig. 7.6.1.2 VCC Under Voltage Detection Timing Chart

Note: When Vcc reaches the under voltage threshhold, this product goes into a reset state. Since the set values in digital circuits (such as set values using SPI) are cleared, resetting is required after the reset state is released.

Note: When Vcc under voltage is detected and the charge pump circuit is turned off, and NDIAG becomes "H" after Tpre en has passed since the release of Vcc under voltage release, the motor operation is enabled.

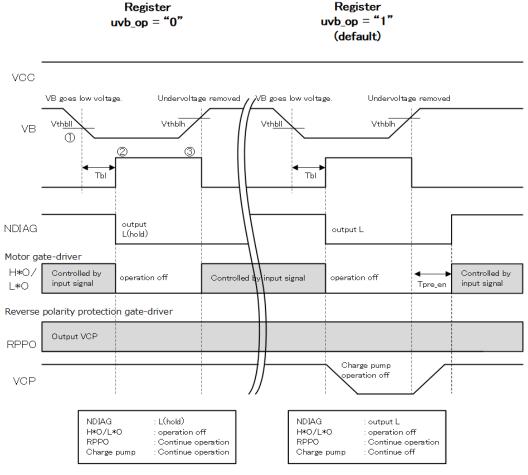

#### 7.6.2. VB Under Voltage Detection Function

The VB under voltage detection circuit monitors voltage at VB terminal to detect under voltage. The detection comparator has hysteresis to prevent its output from chattering at the time of detection and detection release. In addition, this circuit ignores noise superimposed on VB with a detection filtering time of 20us (Typ.).

In addition, SPI communication allows the operations below.

- Set operation after an abnormality has been detected.

- Read abnormality detection flag.

- Clear abnormality detection flag.

**VB Under Voltage Detection Block Diagram** Fig. 7.6.2.1

#### (1)VB voltage goes down

When VB voltage goes below the detected under voltage Vthbll, detection operation is started.

#### (2)VB under voltage is detected

After a detection filtering time of Tbl has passed, a under voltage state is detected by VB under voltage detection signal (vbl)="H," the status register: uvb="1" and "NDIAG="L."

The operation after detection can be selected between 2 modes via SPI communication.

The gate driver circuit for driving the FET for reverse polarity protection maintains its ON state.

In the case of register: uvb op="0," gate driver circuits for driving 3-phase FETs are turned off.

In the case of register: uvb op="1," the charge pump and gate driver circuits for driving 3-phase FETs are turned off.

Even if setting is changed during detection, the change is not effective, and after the detection is released and register: uvb is cleared, the changed setting becomes effective.

While under voltage is detected, register: uvb cannot be cleared, and NDIAG remains "L".

#### (3)VB voltage recovers (Under voltage release)

When VB voltage goes above Vthblh, it results in VB under voltage detection signal (vbl)="L," and under voltage is released.

In the case of register: uvb op="0," the status register: uvb="1" and NDIAG="L" are latched, and gate drivers for driving 3-phase FETs follow input signals. When register: uvb is cleared by SPI communication, after Tpre en has passed, NDIAG="H. is output"

In the case of register: uvb op="1," status register: uvb="0," NDIAG="H," and the charge pump circuit automatically recovers, and the gate driver circuits for driving 3-phase FETs follow the input signals.

Fig. 7.6.2.2 VB Under Voltage Detection Timing Chart

Note: When Vb under voltage is detected and the charge pump circuit is turned off, and NDIAG becomes "H" after Tpre en has passed since a release fo the Vb under voltage, the motor operation is enabled.

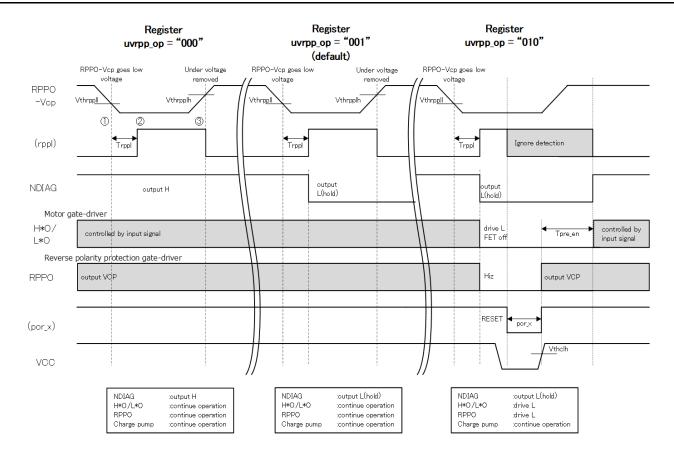

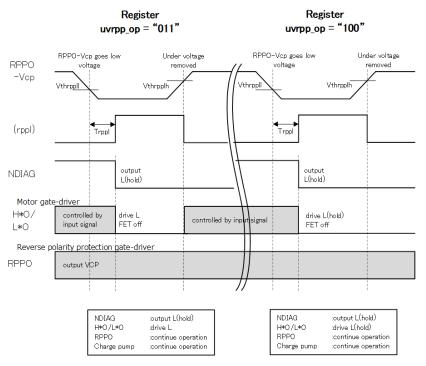

#### 7.6.3. RPPO Under Voltage Detection Function

The RPPO under voltage detection circuit monitors differential voltage between Vcp voltage and RPPO voltage to detect insufficient driving state for the FET for reverse polarity protection. The detection comparator has hysteresis to prevent its output from chattering at the time of detection and detection release. In addition, this circuit ignores noise superimposed on RPPO terminal with a detection filtering time of 20us (Typ.).

In addition, SPI communication allows the operations below.

- Set operation after an abnormality has been detected.

- Read abnormality detection flag. Clear abnormality detection flag.

Fig. 7.6.3.1 RPPO Under Voltage Detection Block Diagram

#### (1)RPPO voltage goes down

Vcp voltage and RPPO voltage are compared, and when the difference goes below the detected under voltage Vthrppll, the detection operation is started.

#### (2)RPPO under voltage is detected

After a detection filtering time of Trppl has passed, a under voltage state is detected by RPPO under voltage detection signal (rppl)="H", resulting in the status register: uvrpp="1" and NDIAG="L."

The detection operation can be selected among 5 modes via SPI communication.

Note that in the case of register: uvrpp op ="000," detection is disabled, and the status register: uvrpp="0" and NDIAG="H" are maintained, and each circuit continues its normal operation.

Whether RPPO terminal continues to be ON or is turned off after RPPO under voltage is detected can be selected by register setting.

Even if setting is changed during detection, the change is not effective, and after the detection is released and register: uvrpp is cleared, the changed setting becomes effective.

While under voltage is detected, register: uvrpp cannot be cleared, and NDIAG remains "L".

#### (3)RPPO voltage recovers (Under voltage release)

When register: uvrpp op="010" is output and under voltage is detected, RPPO terminal is also turned off. So, to recovery the state, VCC needs to be turned off once and turned on after a certain period. In this case, in a period of por x (L) and a period of Tpre en (L), differential voltage between VCP voltage and RPPO voltage can be generated. So, the detection is disabled.

When register: uvrpp op="011" is output and RPPO voltage is above Vthrpplh, it results in RPPO under voltage detection signal (rppl)="L" and the under voltage is released.

In the case of register: uvrpp op ="100," gate drivers for driving 3-phase FETs stay in their OFF state, and the status register: uvrpp="1" and NDIAG="L" are latched even when the under voltage is released.

When register: uvrpp is cleared by SPI communication, each circuit operates normally and NDIAG="H" is output

Fig. 7.6.3.2 RPPO Under Voltage Detection Timing Chart

Note: When RPPO under voltage is detected and Vcc is reset, the charge pump circuit is turned off. When Tpre\_en has passed since a release of Vcc reset and NDIAG becomes "H," the motor operation is enabled.

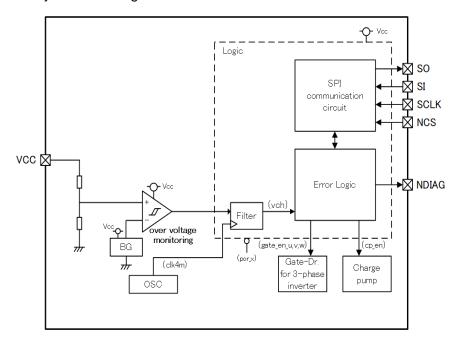

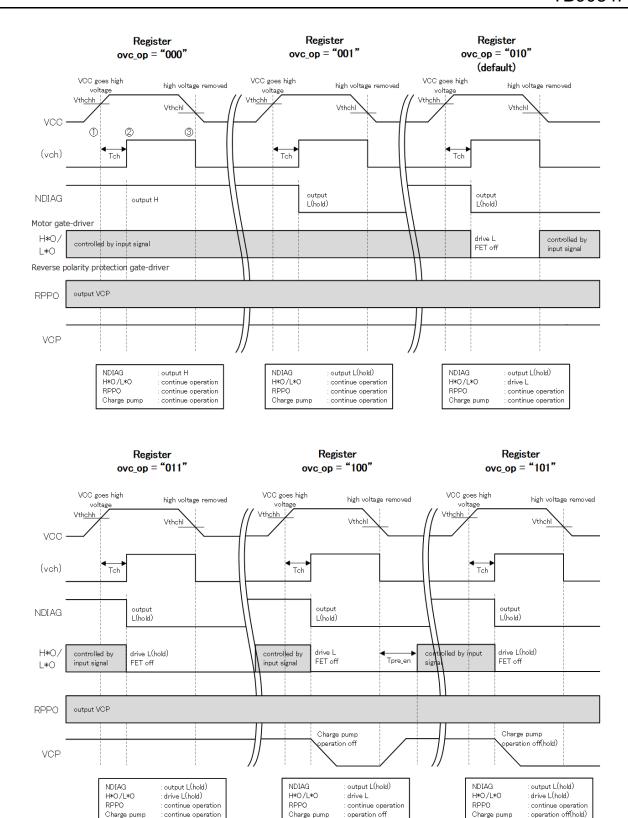

#### 7.6.4. VCC Over Voltage Detection Function

The VCC over voltage detection circuit monitors voltage at VCC terminal to detect over voltage. The detection comparator has hysteresis to prevent its output from chattering at the time of detection and detection release. In addition, this circuit ignores noise superimposed on VCC terminal with a detection filtering time of 20us

In addition, SPI communication allows the operations below.

- Set operation after an abnormality has been detected.

- Read abnormality detection flag.

- Clear abnormality detection flag.

Fig. 7.6.4.1 VCC Over Voltage Detection Block Diagram

#### (1)VCC voltage increases.

When VCC voltage goes above the detected over voltage Vthchh, detection operation is started.

#### (2)VCC over voltage is detected.

After a detection filtering time of Tch has passed, an over voltage state is detected by VCC over voltage detection signal (vch)="H," resulting in the status register: ovcc="1" and NDIAG="L."

Operation after detection can be selected from 6 modes via SPI communication.

In the case of register: ovcc\_op="001", each circuit continues its normal operation even when VCC over voltage is detected, but NDIAG="L" is latched.

However, in the case of register: ovcc\_op="000," even when VCC over voltage has been detected, NDIAG="H" is output and each circuit continues its normal operation.

Even if setting is changed during detection, the change is not effective, and after the detection is released and register: ovcc is cleared, the changed setting becomes effective.

While over voltage is detected, register: ovcc cannot be cleared and NDIAG remains "L".

#### (3)VCC voltage recovers (Over voltage release)

When VCC voltage going below Vthchl, it results in VCC over voltage detection signal (vch)="L" and the over voltage is released.

In the case of register: ovcc op="010" and the over voltage is released, gate drivers return to their normal operation, but NDIAG="L" remains latched.

In the case of register: ovcc op="011" even when the over voltage is released, OFF state of gate drivers remains latched and NDIAG="L" remains latched.

In the case of register: ovcc op ="100" and the over voltage is released, the charge pump and gate drivers return to their normal operation, but NDIAG="L" remains latched.

In the case of register: ovcc op ="101" even when the over voltage is released, OFF states of the charge pump and gate drivers remain latched and NDIAG="L" remains latched.

When register: ovcc is cleared by SPI communication, each circuit operates normally and NDIAG="H" is output.

Fig. 7.6.4.2 VCC Over Voltage Detection Timing Chart

Note: When Vcc over voltage is detected and the charge pump circuit is turned off, and NDIAG becomes "H" after Tpre\_en period has passed since the Vcc over voltage detection was released, the motor operation is enabled.

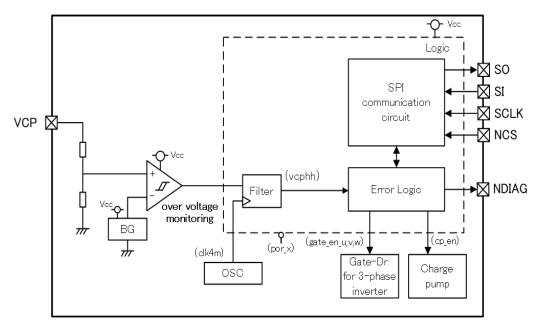

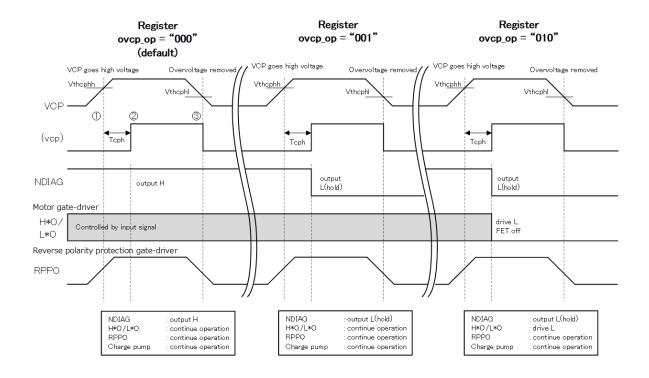

#### 7.6.5. VCP Over Voltage Detection Function

To avoid excessive over voltage applied on elements, this circuit detects over voltage of charge pump voltage VCP. The detection comparator has hysteresis to prevent its output from chattering at the time of detection and detection release. In addition, this circuit ignores noise superimposed on RPPO terminal with a detection filtering time of 20us (Typ.).

In addition, SPI communication allows the operations below.

- Set operation after an abnormality has been detected.

- Read abnormality detection flag.

- Clear abnormality detection flag.

Fig. 7.6.5.1 VCP Over Voltage Detection Block Diagram

#### (1)VCP voltage increases.

When VCP voltage goes above the detected over voltage Vthcphh, detection operation is started.

#### (2)VCP over voltage is detected.

After a detection filtering time of Tcph has passed, an over voltage state is detected by VCP over voltage detection signal (vcp)="H", resulting in the status register: ovcp="1" and NDIAG="L".

Operation after detection can be selected from 6 modes via SPI communication.

In the case of register: ovcp\_op="001", each circuit continues its normal operation even when VCP over voltage is detected, but NDIAG="L" is latched.

However, in the case of register: ovcp\_op="000," even when VCP over voltage is detected, NDIAG="H" is output and each circuit continues its normal operation.

Even if setting is changed during detection, the change is not effective, and after the detection is released and register: ovcp is cleared, the changed setting becomes effective.

While over voltage is detected, register: ovcp cannot be cleared and NDIAG remains "L".

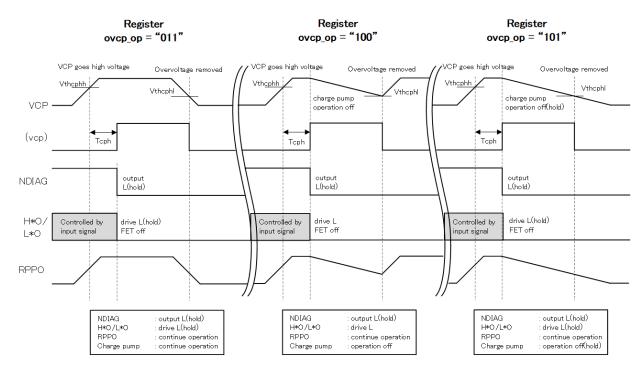

#### (3)VCP voltage recovers. (Over voltage release)

When VCP voltage goes below Vthcphl, it results in VCP over voltage detection signal (vcp)="L," and the over voltage is released.

In the case of register: ovcp\_op="010" and the over voltage is released, gate drivers return to their normal operation, but NDIAG="L" remains latched.

In the case of register: ocph\_op="011," even when the over voltage is released, OFF state of gate drivers remains latched and NDIAG="L" remains latched.

In the case of register: ocph\_op="100" and the over voltage is released, the charge pump and gate drivers return to their normal operation, but NDIAG="L" remains latched.

In the case of register: ocph\_op="101," even when the over voltage is released, OFF states of the charge pump and gate drivers remain latched and NDIAG="L" remains latched.

When register: ovcp is cleared by SPI communication, each circuit operates normally and NDIAG="H" is output.

Fig. 7.6.5.2 VCP Over Voltage Detection Timing Chart

#### 7.6.6. Over temperature Detection Function

The detection comparator has hysteresis to prevent its output from chattering at the time of detection and detection release. In addition, this circuit ignores noise superimposed on an internal node with a detection filtering time of 20us (Typ.) SPI communication allows the operations below.

- Set operation after abnormality has been detected.

- Read abnormality detection flag.

- Clear abnormality detection flag.

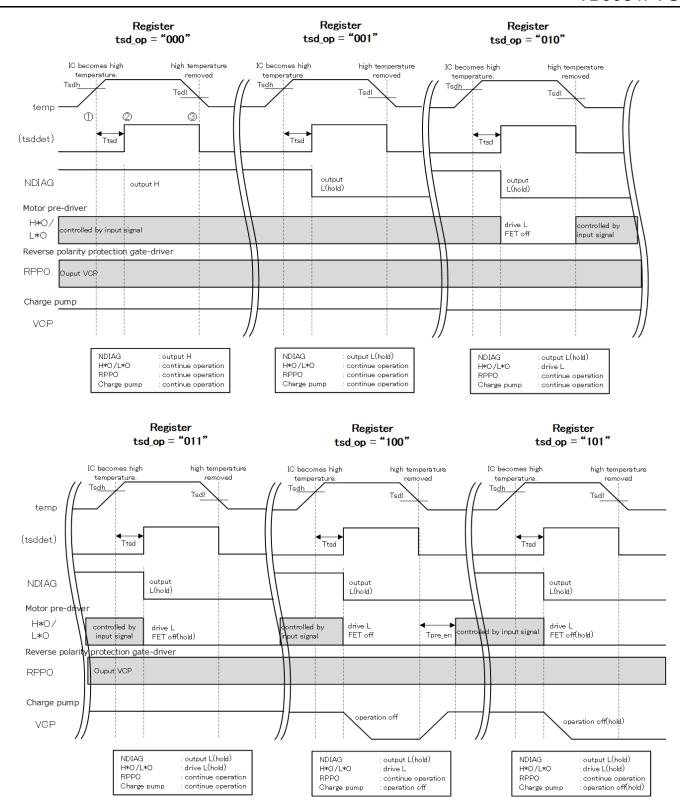

**Over Temperature Detection Block Diagram**

#### (1)Chip temperature rises.

When the temperature monitored by a sensor in this product goes above Tsdh, the detection operation is started.

#### (2)Over temperature is detected.

After a detection filtering time of Ttsd has passed, an over temperature state is detected by over temperature detection signal (tsddet)="H," resulting in the status register: tsd="1," and "NDIAG="L".

Operation after detection can be selected from 6 modes via SPI communication.

In the case of register: tsd op="001", each circuit continues its normal operation even when over temperature is detected, but NDIAG="L" is latched.

However, in the case of register: tsd op="000," even when over temperature is detected, NDIAG="H" is output and each circuit continues its normal operation.

Even if setting is changed during detection, the change is not effective, and after the detection is released and register: tsd is cleared, the changed setting becomes effective.

While over temperature is detected, register: tsd cannot be cleared and NDIAG remains "L".

#### (3)Over temperature detection is released.

When the temperature goes below Tsdl, it results in over temperature detection signal (tsddet)="L," and over temperature detection is released.

In the case of register: tsd\_op="010" and the over temperature is released, gate drivers return to their normal operation, but NDIAG="L" remains latched.

In the case of register: tsd op="011," even when the over temperature is released, OFF state of gate drivers remains latched and NDIAG="L" remains latched.

In the case of register: tsd op="100" and the over temperature is released, the charge pump and gate drivers return to their normal operation, but NDIAG="L" remains latched.

In the case of register: tsd op="101," even when the over temperature is released, OFF states of the charge pump and gate drivers remain latched and NDIAG="L" remains latched.

When register: tsd is cleared by SPI communication, each circuit operates normally and NDIAG="H" is output.

Fig. 7.6.6.2 Over Temperature Detection Timing Chart

Note: When over temperature is detected and the charge pump circuit is turned off, after Tpre en has passed since the over temperature was released, the motor operation is enabled.

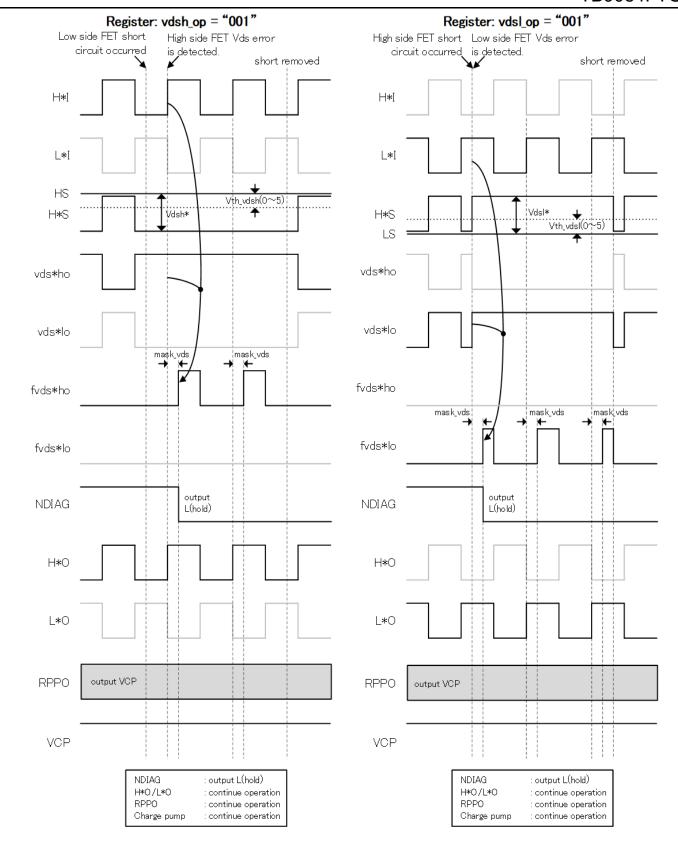

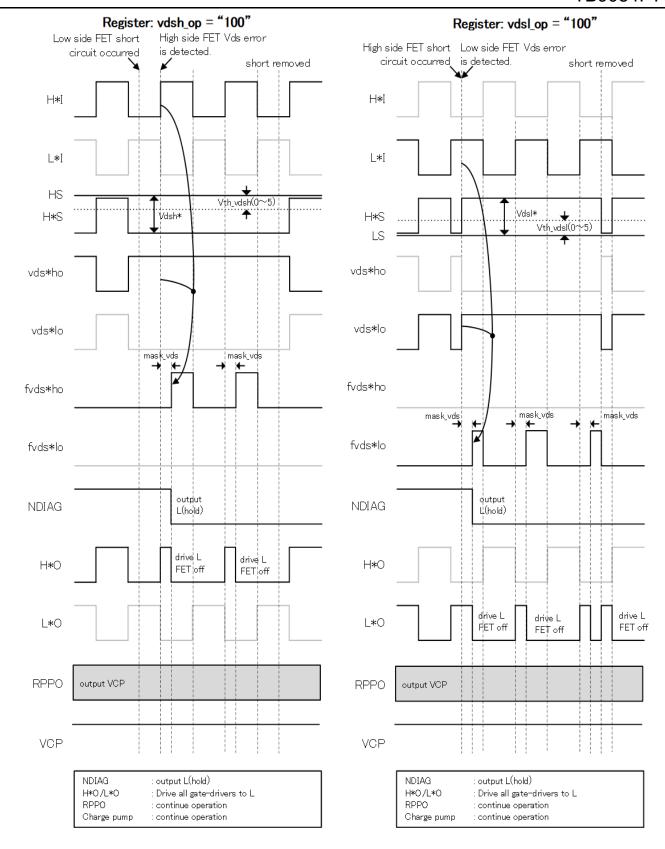

#### 7.6.7. VDS Detection Function for 3-Phase FETs

In ON state operation of 3-phase FETs, differential voltage between HS and H\*S terminals of this product is monitored for high-side FETs and differential voltage between H\*S and LS terminals of this product is monitored for low-side FETs to detect abnormality. The threshold voltage can be set by SPI communication for high-side FETs and low-side FETs each. In addition, to avoid detecting a state before reaching a complete ON state, a mask time after the input terminal receives an ON command has been prepared, and this time can be set by SPI communication. Higher voltage than the threshold voltage is detected as abnormal and "1" is stored at the status register for each phase and for each side.

Operation after abnormality has been detected can be set by SPI communication (<u>CONFIG2</u>). Two types of setting are available: the OFF state of gate driver circuits for driving 3-phase FETs is not latched and it is latched. In the former type as well, the gate driver circuits for driving 3-phase FETs remains latched their OFF state while the input terminal is receiving "H." In addition, in the "latched" setting, the "1" of the status register needs to be cleared to return to the normal operation.

In addition, SPI communicaton (CONFIG4) can enable/disable detection for each phase.

Fig. 7.6.7.1 Block Diagram of VDS Detection for 3-Phase FETs

**Table 7.6.7.1 VDS Detection Scenarios**

| Comparison by                        | Comparator     | Input Signal | Abnormal State          |

|--------------------------------------|----------------|--------------|-------------------------|

| Comparator                           | Output         |              |                         |

| $V_{HUS}$ - $V_{LS}$ > $V_{thvdsul}$ | (vdsulo) = "H" | LUI = "H"    | FET VDS abnormal at LUO |

| $V_{HVS}$ - $V_{LS}$ > $V_{thvdsvl}$ | (vdsvlo) = "H" | LVI = "H"    | FET VDS abnormal at LVO |

| $V_{HWS}-V_{LS} > V_{thvdswl}$       | (vdswlo) = "H" | LWI = "H"    | FET VDS abnormal at LWO |

| $V_{HS}$ - $V_{HUS}$ > $V_{thvdsuh}$ | (vdsuho) = "H" | HUI = "H"    | FET VDS abnormal at HUO |

| $V_{HS}$ - $V_{HVS}$ > $V_{thvdsvh}$ | (vdsvho) = "H" | HVI = "H"    | FET VDS abnormal at HVO |

| $V_{HS}$ - $V_{HWS}$ > $V_{thvdswh}$ | (vdswho) = "H" | HWI = "H"    | FET VDS abnormal at HWO |

Fig. 7.6.7.2 Short-Circuit Detection Timing Chart (In the case of register: vdsl\_op = vdsh\_op "000")

Fig. 7.6.7.3 Short-Circuit Detection Timing Chart (In the case of register: vdsl\_op = vdsh\_op "001")

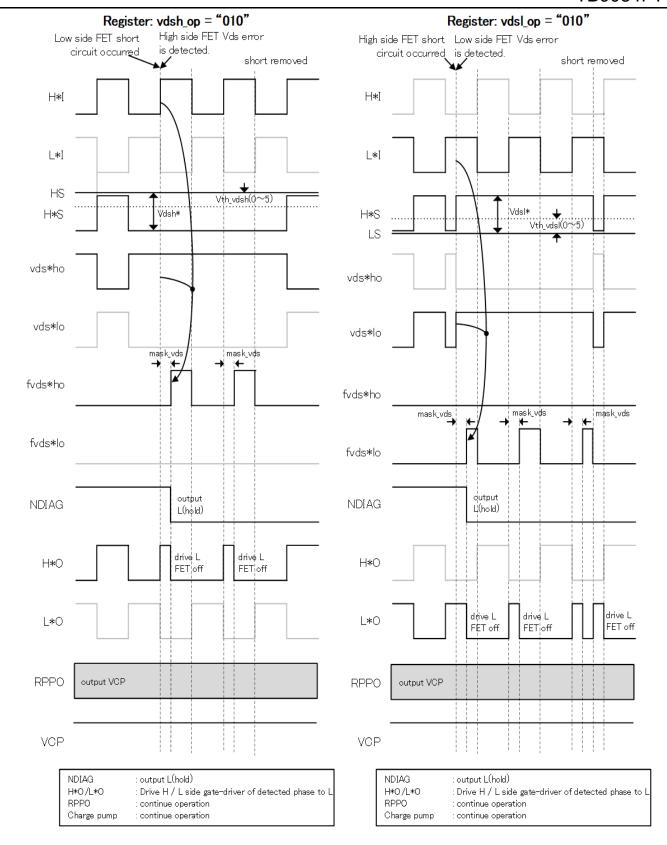

Fig. 7.6.7.4 Short-Circuit Detection Timing Chart (In the case of register: vdsl\_op = vdsh\_op "010")

Fig. 7.6.7.5 Short-Circuit Detection Timing Chart (In the case of register: vdsl\_op = vdsh\_op "011")

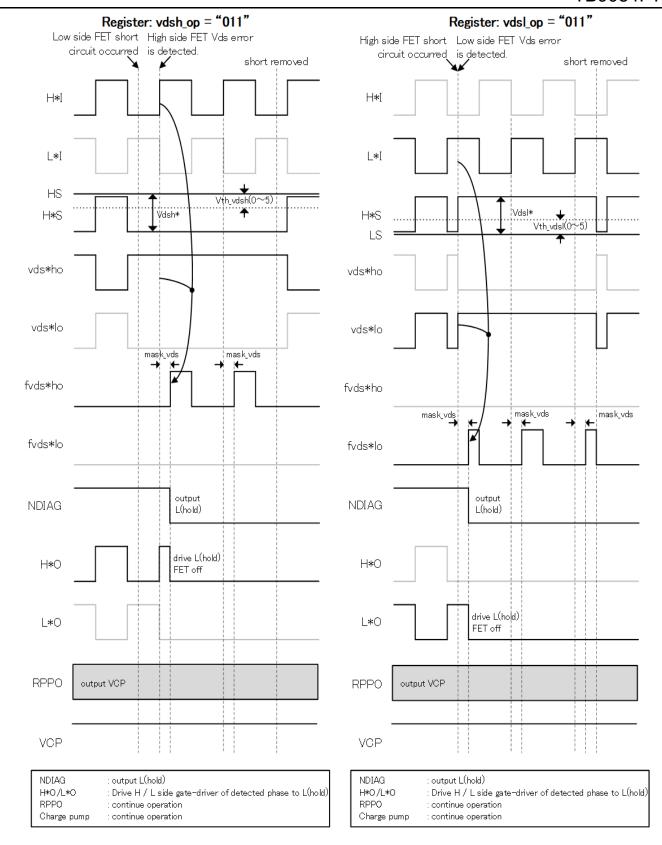

Fig. 7.6.7.6 Short-Circuit Detection Timing Chart (In the case of register: vdsl\_op = vdsh\_op "100")

Fig. 7.6.7.7 Short-Circuit Detection Timing Chart (In the case of register: vdsl\_op = vdsh\_op "101")

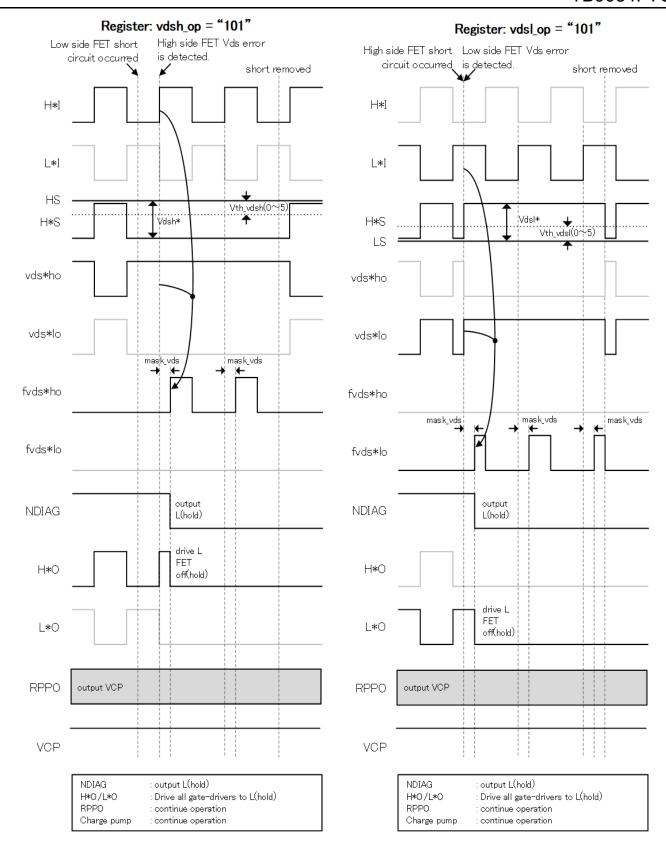

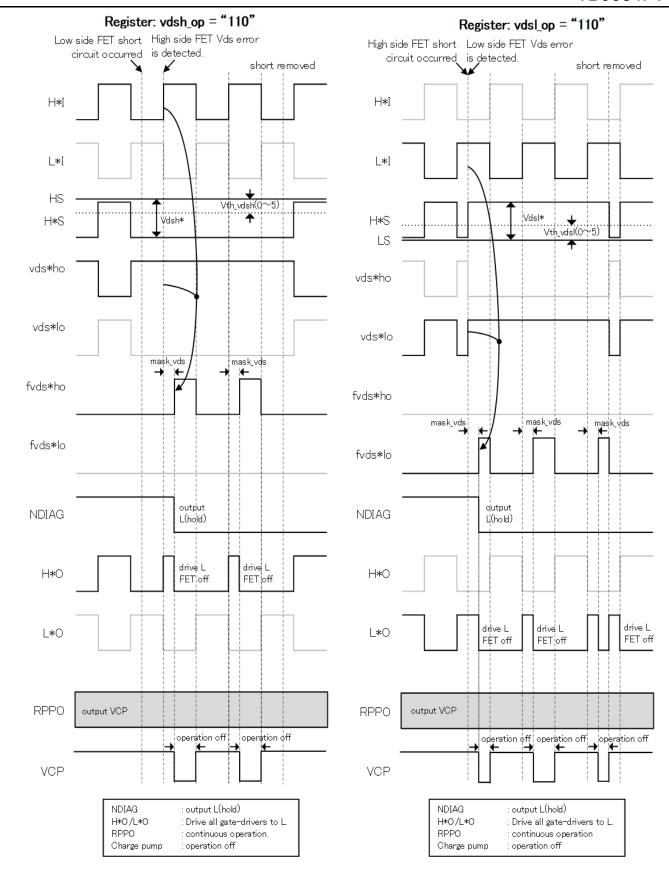

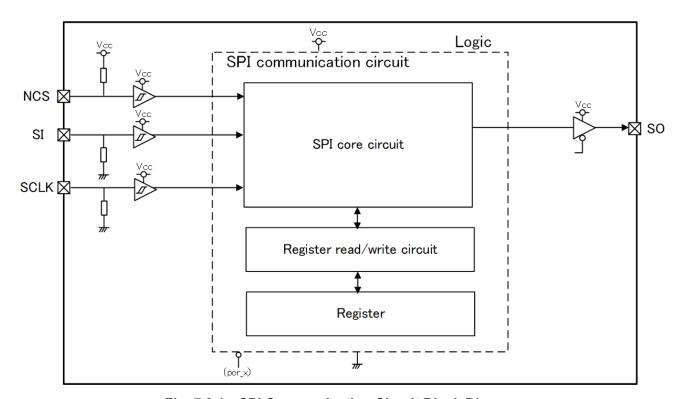

Fig. 7.6.7.8 Short-Circuit Detection Timing Chart (In the case of register: vdsl\_op = vdsh\_op "110")

Fig. 7.6.7.9 Short-Circuit Detection Timing Chart (In the case of register: vdsl\_op = vdsh\_op "111")

### 7.6.8. Abnormality Detection for CP1SW and CP2SW Terminals

This function detects abnormality for the following cases.

- Short-circuit with adjacent terminals for CP1SW and CP2SW each

- Short circuit to VB

- Short circuit to GND

- Short circuit of an external flying capacitor

In addition, SPI communication allows the operations below.

- Set operation after abnormality has been detected (CONFIG5).

- Read abnormality detection flag (flag for CP1SW and CP2SW each) (STAT1).

- Clear abnormality detection flag (clear flag for CP1SW and CP2SW each) (STAT1\_CLR).

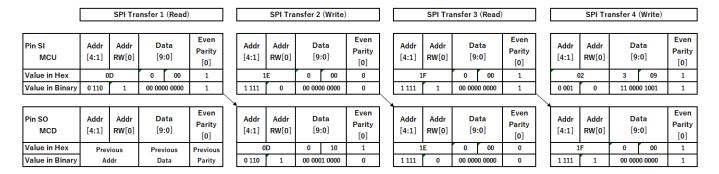

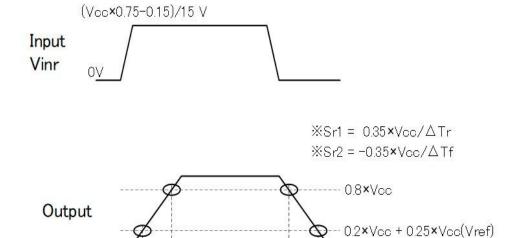

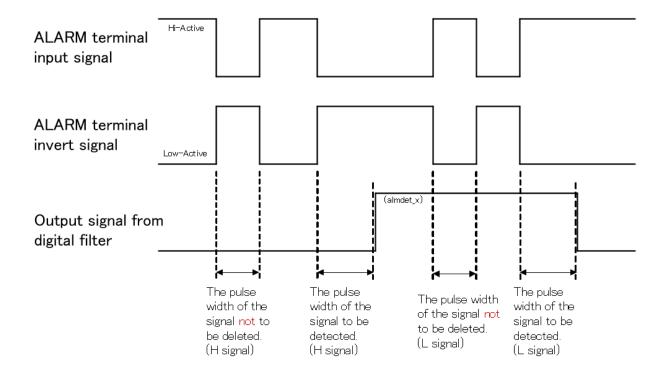

### 7.7. Alarm Input Circuit