# 面実装 SiC MOSFET 搭載 AI サーバー用 3kW 電源

# デザインガイド

RD265-DGUIDE-02

東芝デバイス&ストレージ株式会社

# 目次

| 1.   | はじめに                         | 3    |

|------|------------------------------|------|

| 2.   | 主な使用部品                       | 4    |

| 2.1. | SiC MOSFET TW092V65C         | 4    |

| 2.2. | SiC MOSFET TW027U65C         | 5    |

| 2.3. | パワーMOSFET TPW2900ENH         | 5    |

| 2.4. | パワーMOSFET TPM1R908QM         | 6    |

| 2.5. | SiC ショットキーバリアダイオード TRS12V65H | 6    |

| 2.6. | デジタルアイソレーター DCL540C01        | 7    |

| 3.   | 回路設計                         | 8    |

| 3.1. | AC ライン回路設計                   | 8    |

| 3.2  | PFC 回路設計                     | . 10 |

| 3.3  | 位相シフトフルブリッジ (PSFB) 回路設計      | . 16 |

| 3.4. | PSFB 回路の 1 次側と 2 次側の通信       | . 22 |

| 3.5. | ORing 回路設計                   | . 23 |

| 3.6  | 補助電源                         | . 24 |

# 1. はじめに

本デザインガイドは面実装 SiC MOSFET 搭載 AI サーバー用 3kW 電源 (以下、本デザイン) の各部回路の設計概要について解説します。

近年、生成 AI の急速な普及により、高速に AI 処理を実行できる AI サーバーの需要が高まっています。AI サーバーは、GPU (Graphics Processing Unit) や NPU (Neural Processing Unit) など、AI 処理で多用される行列演算に特化した複数コアのアクセラレーターを搭載しており、高い演算性能を発揮する一方で、大きな電力を必要とします。そのため、AI サーバー向け電源には高効率化、高電力化、省スペース化が求められるようになり、高電力密度化が必要不可欠になっています。本デザインは AC 180 ~ 264Vを入力し、セミブリッジレス PFC (Power Factor Correction) 回路、位相シフトフルブリッジ (Phase Shift Full Bridge:以下 PSFB) 回路により DC 50V、最大 3kWを出力します。出力 ORing 回路を搭載しており冗長運転が可能です。また電源内部の回路電源として必要な補助電源回路も内蔵しています。パワー素子をメイン基板と分離した形で実装することで出力当たりのメイン基板面積を縮小し、電源を小型化しています。

本デザインではセミブリッジレス PFC 回路に SiC MOSFET <u>TW092V65C</u> および SiC ショットキーバリアダイオード <u>TRS12V65H</u> を使用しています。 PSFB 回路には 1 次側フルブリッジ部に SiC ショットキーバリアダイオード内蔵の SiC MOSFET <u>TW027U65C</u> を、2 次側同期整流部にはパワーMOSFET <u>TPW2900ENH</u>を使用しています。2 次側のコントローラーからの絶縁ゲート信号 伝送にはデジタルアイソレーター <u>DCL540C01</u>を使用しています。また、出力 ORing 回路にはパワーMOSFET <u>TPM1R908QM</u> を使用しています。 これら当社最新の素子を使用することで、80PLUS Platinum (Vin = 230V、 Pout = 3kW) 級の高効率で コンパクトな電源を実現しています。

※80 PLUS:サーバーなどコンピューター用電源ユニットの効率規格

# 2. 主な使用部品

この章では本デザインに使用している主な部品について説明します。

#### 2.1. SiC MOSFET TW092V65C

セミブリッジレス PFC 回路のスイッチング用素子として SiC MOSFET <u>TW092V65C</u>を使用しています。 TW092V65C の主な特長は以下のとおりです。

- 第3世代チップデザイン (SiCショットキーバリアダイオード内蔵)

- 順方向電圧 (ダイオード) が低い: VDSF = -1.35V (標準)

- 高耐圧: V<sub>DSS</sub> = 650V

- オン抵抗が低い: R<sub>DS(ON)</sub> = 92mΩ (標準)

- しきい値が高く誤動作しにくい: Vth = 3.0 ~ 5.0V (VDS = 10V, ID = 0.6mA)

- 推奨駆動電圧: V<sub>GS\_on</sub> = 18V, V<sub>GS\_off</sub> = 0V

- 取り扱いが簡単なエンハンスメントタイプ

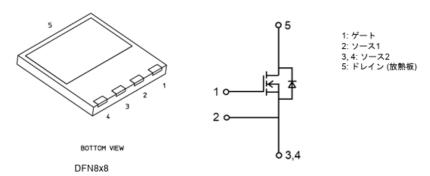

図2.1 TW092V65Cの外観と内部回路構成図

#### 2.2. SiC MOSFET TW027U65C

PSFB 回路の 1 次側に SiC MOSFET TW027U65C を使用しています。TW027U65C の主な特長は以下のとおりです。

- 第3世代チップデザイン (SiC ショットキーバリアダイオード内蔵)

- 順方向電圧 (ダイオード) が低い: V<sub>DSF</sub> = -1.35V (標準)

- 高耐圧: V<sub>DSS</sub> = 650V

- オン抵抗が低い: R<sub>DS(ON)</sub> = 27mΩ (標準)

- しきい値が高く誤動作しにくい: Vth = 3.0 ~ 5.0V (VDS = 10V, ID = 3mA)

- 推奨駆動電圧: V<sub>GS\_on</sub> = 18V, V<sub>GS\_off</sub> = 0V

- 取り扱いが簡単なエンハンスメントタイプ

図2.2 TW027U65Cの外観と内部回路構成図

# 2.3. パワーMOSFET TPW2900ENH

PSFB 回路の 2 次側同期整流部にパワーMOSFET <u>TPW2900ENH</u>を使用しています。TPW2900ENH の主な特長は以下のとおりです。

- スイッチングスピードが速い

- オン抵抗が低い: R<sub>DS(ON)</sub> = 24mΩ (標準) (V<sub>GS</sub> = 10V)

- 漏れ電流が低い: loss = 10µA (最大) (Vos = 200V)

- 取り扱いが簡単なエンハンスメントタイプ: Vth = 2.0 ~ 4.0V (VDS = 10V, ID = 1.0mA)

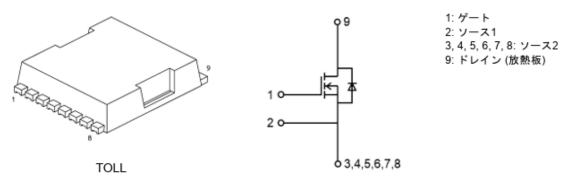

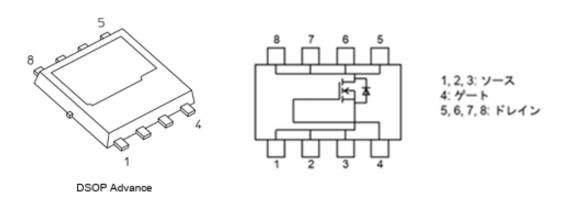

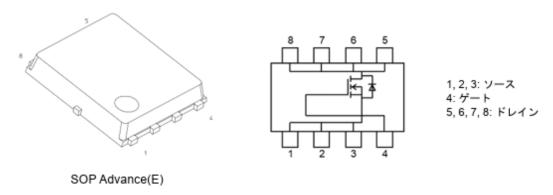

図2.3 TPW2900ENHの外観と内部回路構成図

## 2.4. パワーMOSFET TPM1R908QM

出力 Oring 回路にパワーMOSFET TPM1R908QM を使用しています。TPM1R908QM の主な特長は以下のとおりです。

- スイッチングスピードが速い

- ゲートスイッチ電荷量が小さい: Qsw = 35nC (標準)

- 出力電荷量が小さい: Qoss = 111nC (標準)

- オン抵抗が低い: R<sub>DS(ON)</sub> = 1.5mΩ (標準) (V<sub>GS</sub> = 10V)

- 漏れ電流が低い: I<sub>DSS</sub> = 10µA (最大) (V<sub>DS</sub> = 80V)

- 取り扱いが簡単なエンハンスメントタイプ: Vth = 2.5 ~ 3.5V (VDS = 10V, ID = 1.2mA)

図2.4 TPM1R908QMの外観と内部回路構成図

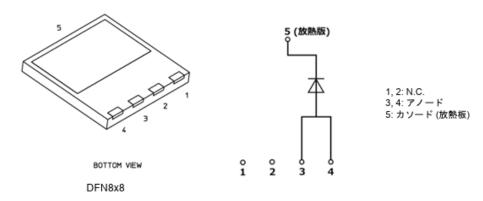

# 2.5. SiC ショットキーバリアダイオード TRS12V65H

セミブリッジレス PFC 回路の昇圧部に SiC ショットキーバリアダイオード <u>TRS12V65H</u>を使用しています。TRS12V65H の主な特長は以下のとおりです。

- 第3世代チップデザイン

- 順電圧が小さい: V<sub>F</sub> = 1.2V (標準)

- 総電荷量が小さい: Qc = 33nC (標準)

- 逆電流が小さい: I<sub>R</sub> = 2.4µA (標準)

図2.5 TRS12V65Hの外観と内部回路構成図

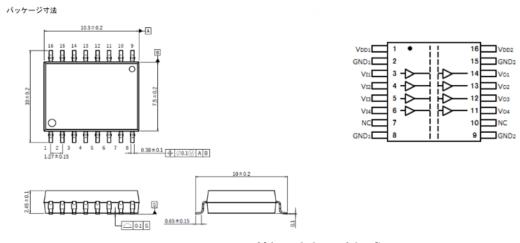

## 2.6. デジタルアイソレーター DCL540C01

PSFB 回路の 1 次側と 2 次側間の信号伝達に 4 チャネルのデジタルアイソレーター<u>DCL540C01</u>を使用しています。 DCL540C01 の主な特長は以下のとおりです。

● データ伝送速度: 150Mbps (最大)

● 電源電圧: 2.25V ~ 5.5V

● 動作温度範囲: -40°C ~ 110°C

● 伝搬遅延時間: 10.9ns (標準) (5.0V 動作時)

● デフォルト出力: High と Low のオプション

CMTI: ±100kV/µs絶縁耐圧: 5kVrms

● 安全規格:

UL: UL1577, File No. E519997

cUL: CSA Component Acceptance Service Notice No. 5A, File No. E519997

VDE: DIN VDE V 0884-11(VDE V 0884-11) Certificate No. 40055132

CQC: GB 4943.1-2022 Certificate No. CQC22001345018

図2.6 DCL540C01の外観と内部回路構成図

# 3. 回路設計

本デザインの回路設計のポイントを記載します。

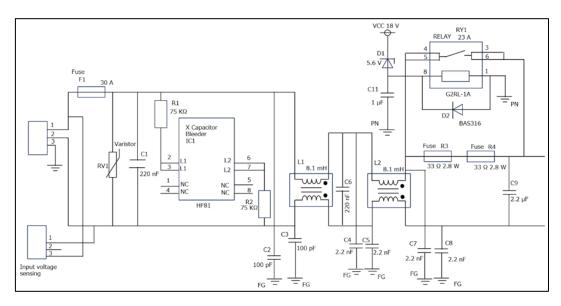

#### 3.1. AC ライン回路設計

本項では、本デザインの AC ラインの設計に関して説明します。本デザインの AC ライン回路を図 3.1 に示します。

図 3.1 AC ライン回路

# ヒューズ

AC ラインに異常電流が流れた際に、AC ラインを遮断するためのヒューズ (F1) を実装しています。AC ラインの最大電流値からヒューズを選定します。AC ライン入力電流最大値の実効値は以下の式で算出されます。

#### AC ライン入力電流最大値 = 最大電力÷電源効率÷力率÷入力電圧実効値 (min)

本デザインは入力が AC 200V のとき 3kW 出力の仕様です。もし、入力電圧によって PFC の電源効率が変わらなければ、 AC ライン入力電流最大値は入力電圧に関わらず同じ値となります。しかし、一般的に PFC の電源効率は入力電圧が低いと低くなるため、AC ライン最大電流値を算出する際は入力電圧が min 値の 180V で考えます。

最大電力 = 3kW、電源効率 = 90%、力率 = 1、入力電圧 (min 実効値) = 180V とすると、本デザインの AC ライン最大電流値は約 18.5A です。本デザインではマージンを考慮して、30A のヒューズを使用しています。ヒューズ選定時は、上記最大電流に加え、AC 電源投入時の突入電流、対応すべき安全規格を取得した製品であるかなども考慮する必要があります。

#### バリスター

AC ラインに誘導雷などによるサージ電圧が印加された際に、システムを保護するためのセラミックバリスター (RV1) を実装しています。バリスターは使用する AC ラインの電圧値に基づいて選定を行います。本デザインの入力最大電圧は実効値で264V、瞬時値で373Vであるため、これらの電圧にマージンを考慮してバリスター電圧560Vのバリスター(最大許容回路電圧AC350V、DC460V)を使用しています。バリスター選定時は上記電圧定格に加え、サージ電流耐量、エネルギー耐量などを考慮する必要があります。また、バリスターの故障モードはショートモードとなることが多いため、バリスター実装時は前段(AC入力側)へのヒューズ実装を推奨致します。

#### Xコンデンサー放電回路

AC 入力が切断された際、感電の危険がないように X コンデンサー(\*3-1) (C1、C6、C9) に蓄えられた電荷を速やかに放電する必要があります。本デザインでは X コンデンサー放電用 IC として、HF81 (IC1) を実装しています。本 IC は AC 電源が供給されているときに放電経路を遮断するため、システムの省電力化に貢献します。AC 電源喪失時、本 IC と外付け抵抗 (R1、R2) で構成される回路により、1 秒以内に X コンデンサーの電圧が初期値の 37%以下 (IEC62368) となるよう、X コンデンサーに蓄えられた電荷を放電することができます。本デザインは約 3uF の X コンデンサーが実装されているため、3uF を放電するのに必要な外付け抵抗 (75kΩ×2 個) を実装しています。なお、ノイズ対策などで X コンデンサーを変更する際は本 IC に接続する外付け抵抗値の変更が必要な場合があります。また、コストダウンのため、本 IC を放電用抵抗に変更することも可能です。しかしながら、その場合、AC 接続時は常時放電用抵抗による電力損失が発生しますので、システムの省電力要求を満足するかを確認する必要があります。

#### EMI 対策部品

コモンモードノイズ対策として Y コンデンサー (\*3-1) (C2、C3、C4、C5、C7、C8) とコモンモードチョーク (L1、L2) を、ディファレンシャルノイズ対策として X コンデンサー (C1、C6、C9) を実装しています。ノイズレベルは基板レイアウト、筐体設計の影響を受けます。必要に応じて上記部品を変更、削除、追加してください。なお、Y コンデンサーの容量を大きくすると、漏洩電流が増加するためシステムが要求される安全規格を満足するか確認する必要があります。

#### 突入電流対策部品

AC 電源投入時の突入電流を抑制するため、ヒューズ内蔵抵抗 (R3、R4) とリレー (RY1) を実装しています。正しい手順で本デザインを起動した場合、AC 電源投入時にリレー回路はオフしており、電流はヒューズ内蔵抵抗 (33Ω + 33Ω) 経由で流れるため突入電流を抑制することが可能です。リレー回路は AC 電源投入後に、内部 1 次側 18V 電源によってオンする仕様となっています。リレー回路がオンすると、より抵抗の低いリレーを経由して電流が流れるため、動作時の電力ロスを低減することができます。リレーをオン・オフする条件、タイミングがシステムの要求仕様を満足しているかを確認する必要があります。

#### (\*3-1) X コンデンサー、Y コンデンサー

X コンデンサーは電源ラインの線間に接続されているコンデンサーで線間を高周波的に短絡し、ノイズを低減します。Y コンデンサーは電源ラインと 基準グランド間に接続されるコンデンサーです。電源ラインの方へノイズが流れるのを防ぎます。

© 2025

#### 3.2. PFC 回路設計

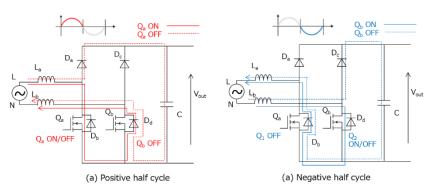

#### 3.2.1 セミブリッジレスPFC回路について

本デザイン回路の説明の前にセミブリッジレス PFC 回路の動作概要を説明します。一般的な電源回路では交流入力を整流した後、平滑コンデンサーを通し直流出力を生成しています。交流入力電流は入力電圧が平滑コンデンサー電圧よりも高い期間のみで流れ、正弦波状にはなりません。PFC 回路は入力電流を正弦波に近づけ、電源回路で発生してしまう入力電圧と電流の位相差を無くし、力率を 1 に近づける回路です。ブリッジレス PFC 回路は交流入力を全波整流するブリッジダイオード部と PFC の機能を統合した回路です。

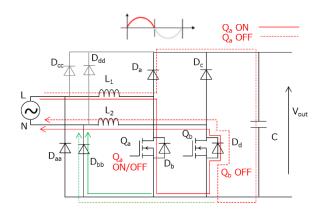

図 3.2 にブリッジレス PFC の基本回路構成と交流入力の半サイクル毎の電流経路を示します。交流入力の La 側が正の半サイクルでは Qa がスイッチングし、Da がその出力ダイオードとして PFC 動作を行います。この時、Qb はこの商用電源の半サイクル期間常時同期整流モードで動作し、交流入力の整流動作を行います。他方、負の半サイクル期間では Qb と Dc がスイッチング動作を行い、Qa が同期整流動作となります。

図 3.2 ブリッジレス PFC 回路動作

図 3.3 に本デザインで採用したセミブリッジレス PFC 回路の動作例を示します。上記ブリッジレス PFC 回路の交流入力側にダイオードを付加した構成です。2 つのダイオード(Daa、Dbb)を通して PFC 出力のグランドが入力ラインに接続され、入力ライン電圧はフローティングではなく、通常のグランド基準となります。よって PFC 回路の入力電圧はグランド基準の正弦波となります。その結果、上記ブリッジレス PFC 回路で問題となるノイズが抑制出来ます。

Dcc および Ddd は最初のスタートアップ中にコンデンサーC をピーク充電するための突入ダイオードです。コンデンサーがピーク充電され、コンバーターが動作し始めた以降の動作には寄与しません。図 3.3 に示すように、電流は Daa および Dbb を通って入力に戻ります。

図 3.3 セミブリッジレス PFC 回路動作

#### 3.2.2 本デザインのPFC回路

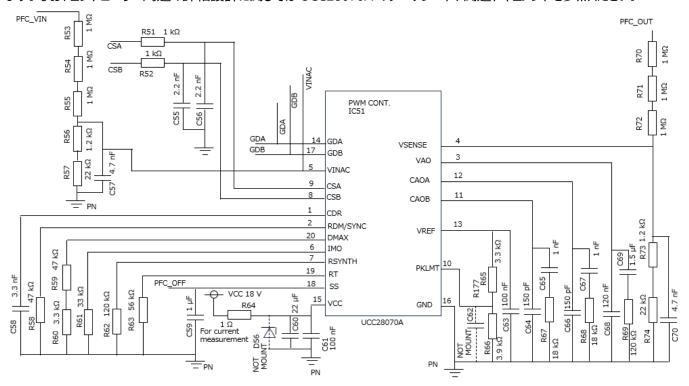

本デザインでは Texas Instruments 社製コントローラーUCC28070A (IC51、以下、PFC コントローラー) を用いたセミブリッジレス PFC 回路構成を採用しています。以下に本デザインのセミブリッジレス PFC 回路の基本的な設計項目に関して説明します。なお、コントローラー周辺の詳細設計に関しては UCC28070A のデータシート、関連ドキュメントを参照ください。

図 3.4 PFC 回路 1 (コントローラー周辺)

#### 出力電圧

PFC 回路の出力電圧 V<sub>PFC\_OUT</sub> は外付け抵抗 R70、R71、R72、R73、R74 によって設定することができます。出力電圧は上記抵抗で分割された出力端子センス電圧 VSENSE と PFC コントローラーの内部参照電圧 (3.0V) を比較することで制御されます。出力電圧設定値は以下の式で算出されます。

$$V_{out\_PFC} = \frac{3.0 \times (R70 + R71 + R72 + R73 + R74)}{(R73 + R74)}$$

なお、PFC 回路の出力電圧を変更する際は AC ライン電圧測定用の抵抗 R53、R54、R55、R56、R57 も同様の値に変更する必要があります。 PFC 回路の出力電圧の初期設定は R73 =  $1.2k\Omega$ , R74 =  $22k\Omega$ , R70 = R71 = R72 =  $1M\Omega$ となっており、約 391V です。必要に応じて上記抵抗値を変更し、所望の出力電圧値に設定してください。

#### スイッチング周波数

PFC 回路のスイッチング周波数 f<sub>PWM</sub> は PFC コントローラーの RT 端子に接続の外付け抵抗 R63 によって設定することができます。スイッチング周波数は以下の式で算出されます。

$$f_{PWM}(kHz) = \frac{7500}{R63 (k\Omega)}$$

© 2025

2025-10-6

スイッチング周波数の初期設定は R63 =  $75k\Omega$ となっており、100kHz です。必要に応じて R63 の抵抗値を変更し、所望の周波数に設定してください。

#### ソフトスタート

PFC 回路のソフトスタート時間は PFC コントローラーの SS 端子に接続の外付けコンデンサーC59 によって設定することができます。設定値は以下の式によって算出されます。

$$T_{SS}(s) = C59 \times \frac{2.25(V)}{10(\mu A)}$$

ソフトスタート時間の初期設定は C59 (Css) = 1µF となっており、約 225ms です。必要に応じて C59 の容量値を変更し、所望のソフトスタート時間に設定してください。ソフトスタート期間中にカレントリミッターが作動しないこと、ホールドアップ期間後の再スタート時に出力電圧が正常範囲に回復することを確認する必要があります。

#### カレントリミッター

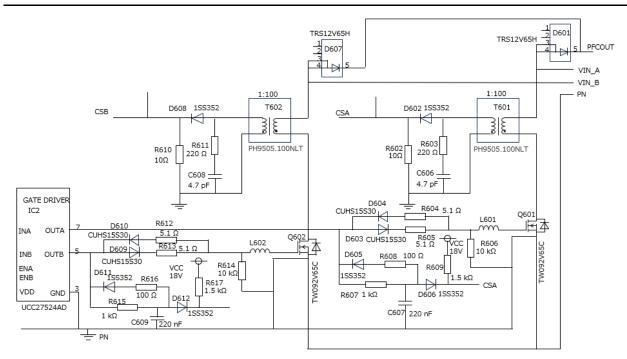

図 3.5 の PFC 回路のカレントリミッターはカレントトランス (T601、T602)、電流検出抵抗 (R602、R610)、PFC コントローラー (図 3.4) の VREF に接続のしきい値設定抵抗 (R65、R66) によって設定することができます。 検知した値は PFC コントローラーの CSA、CSB に入力され、電流がしきい値に到達すると、PFC コントローラーはゲートドライバーUCC27524AD の INA、INB に入力されるゲートドライブ用信号 (GDA、GDB) を Disable にします。 カレントリミットレベル I\_limit は以下の式によって算出されます。

$$I\_limit = \left(\frac{P_{PFC\_OUT} \times \sqrt{5}}{efficiency, \eta(\%) \times V_{inAC}} + \frac{\Delta I}{2}\right) \times \forall -$$

ジン (力率は 1 としています。)

カレントリミットレベルの初期設定は  $V_{inAC} = 180V$  の場合、 $P_{PFC_OUT} = 3333W$ 、効率 $\eta = 90\%$ 、以下の式から  $\Delta I = 10.2A$  としてマージン = 1.2 とすると 41.04A となっています。必要に応じて上記値を変更し、所望の電流値に設定してください。

$$ACin_{peak} = \frac{P_{PFC\_OUT} \times \sqrt{2}}{V_{inAC} \times \eta} = \frac{3333 \times \sqrt{2}}{180 \times 0.9} = 29.1$$

$$\Delta I = ACin_{peak} \times 35 \% = 10.2$$

図 3.5 PFC 回路 2 (パワーMOSFET 周辺)

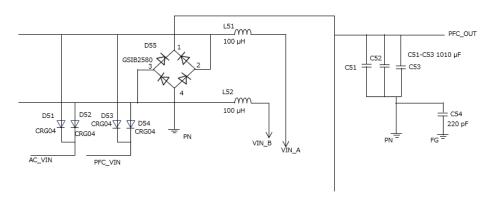

### ブリッジダイオード

本デザインはセミブリッジレス PFC 回路構成となっていますので、ブリッジダイオード D55 (図 3.6) の 2 ピン-1 ピン間ダイオード、および 3 ピン-1 ピン間ダイオードは、電源起動時の整流動作にのみ寄与し、それ以降の動作には寄与しません。本ブリッジダイオード (D55) をハーフブリッジダイオードと表面実装タイプのダイオードに変更することも可能です。表面実装タイプのダイオード使用時は突入電流をサポートできる定格の製品を選択する必要があります。

図 3.6 PFC 回路 3 (ブリッジダイオード、インダクター周辺)

#### 出力コンデンサー

出力コンデンサー (C51、C52、C53) の容量値はホールドアップタイム要件に基づいて算出しています。ホールドアップタイム  $T_{hold}$  は出力コンデンサーの容量を  $C_{out}$  (C51、C52、C53) 、出力電圧を  $V_{PFC\_OUT}$ 、出力電圧の下限電圧を  $V_{min}$ 、最大出力電力を  $P_{out}$  とします。出力電圧  $V_{PFC\_OUT}$  は回路が停止する最低動作電圧  $V_{min}$  になる保持時間  $V_{hold}$  の間、出力コンデンサー $V_{out}$  から出力電力  $V_{out}$  を供給するので以下の式が成り立ちます。

$$\frac{1}{2} \times C_{out} \times V_{PFC\_OUT}^2 - \frac{1}{2} C_{out} \times V_{min}^2 = P_{out} \times T_{hold}$$

© 2025

$$T_{hold} = C_{out} \times \frac{(V_{PFC\_OUT}^2 - V_{min}^2)}{2 \times P_{out}}$$

初期設定は C<sub>out</sub> = 3030μF、V<sub>PFC\_OUT</sub> = 391V、V<sub>min</sub> = 280V<sup>(\*3-2)</sup>、P<sub>out</sub> = 3kW であり、ホールドアップタイムは 37.6ms となります。システムに要求されるホールドアップタイムを満足できるよう出力コンデンサーの容量を調整願います。また、出力リップル仕様が要求された場合は出力リップル仕様を満たすのに必要な容量を算出し、ホールドアップタイムを満足する容量と比較し、大きい容量値を使用する必要があります。また、コンデンサー選定時には公差や経年劣化を考慮する必要があります。

(\*3-2)

今回の電源は DC-DC 分の入力監視回路を個別に搭載しています。その保護開始電圧が 280V です。

#### インダクター

図 3.6 の PFC 用インダクター (L51、L52) の選定はインダクターのリップル電流 $\Delta$ I を AC ラインのピーク入力電流値 (AC<sub>in\_peak</sub>) の 35%に設定することとし、入力電圧を  $V_{inAC}$ 、PFC 出力電圧を  $V_{PFC_OUT}$ 、スイッチング周波数を F、 PFC の電力変換効率を $\eta$  とすると、インダクター値は以下のとおり計算することができます。

$$ACin_{peak} = \frac{P_{PFC\_OUT} \times \sqrt{2}}{V_{inAC} \times \eta} = \frac{3333 \times \sqrt{2}}{180 \times 0.9} = 29.1$$

$$\Delta I = ACin_{\text{peak}} \times 35 \% = 10.2$$

本デザインでは  $P_{PFC_OUT} = 3333W$ 、 $V_{inAC} = 180V$ 、効率 $\eta = 90\%$ とします。インダクターの値は PFC のスイッチング素子 (MOSFET) のオン時に与える電圧の最大値、オン時間 (スイッチング時間  $T \times オンデューティー$ ) および電流変化 $\Delta I$  で表されます。

$$L = V \times \frac{dt}{di} = \sqrt{2} \times V_{inAC} \times \frac{T \times D}{\Delta I}$$

ここで Tを MOSFET のスイッチング周波数 Fで表すと以下のようになります。

$$T = \frac{1}{F}$$

また、PFC 回路のデューティーは以下の式で表されます。

$$D = \frac{V_{PFC\_OUT} - \sqrt{2} \times V_{inAC}}{V_{PFC\_OUT}}$$

インダクターL の式に TとD の式を代入して以下の式が得られます。

$$L = \sqrt{2} \times V_{inAC} \times \frac{(V_{PFC\_OUT} - V_{inAC})}{V_{PFC\_OUT} \times \Delta I \times F}$$

本デザインでは、 $V_{inAC}$  = 180V、 $V_{PFC\_OUT}$  = 391V、F = 100kHz、 $\Delta I$  = 10.2A とすると、L = 87.1 $\mu$ H となりますので 100 $\mu$ H を使用しています。

# 3.3. 位相シフトフルブリッジ (PSFB) 回路設計

#### 3.3.1 PSFB回路について

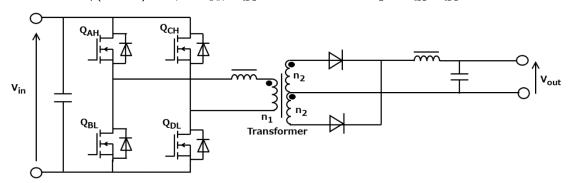

図3.7にPSFB回路のブロック図を示します。トランス(Transformer)の1次側はフルブリッジ回路で形成されています。 QahとQbLはそれぞれデューティー50%、位相差180度でスイッチングされます。QchとQbLも同様です。基本動作は、QahとQbLがオン/オフ状態を入れ替えた後、ある位相遅れ(シフト)をもってQchとQbLがオン/オフ状態を入れ替えます。この位相シフトの量により、対角線上に位置するQahとQbL、QbLとQchのオーバーラップの量が変わり2次側に伝達されるエネルギー量が決まります。出力される電圧は以下の式で表されます。一般に、QahとQbLのレグを「進みレグ」、QchとQbLのレグを「遅れレグ」と呼びます。PSFB回路はスイッチング素子がZero Volt Switching (ZVS)動作をすることによりスイッチング損失を大幅に低減できるため、大きな電力を扱うことが可能です。

$$V_{out} = \frac{n_2}{n_1} V_{in} \alpha$$

Vout: 出力電圧[V] Vin: 入力電圧[V]

n<sub>1</sub>: トランス 1 次側巻き線数 n<sub>2</sub>: トランス 2 次側巻き線数

a:位相シフトの割合 T1/(T1+T2) T<sub>1</sub>: Q<sub>AH</sub>、Q<sub>DL</sub>の同時オン時間 T<sub>2</sub>: Q<sub>BL</sub>、Q<sub>DL</sub>の同時オン時間

図 3.7 PSFB 回路

図 3.8 PSFB 波形

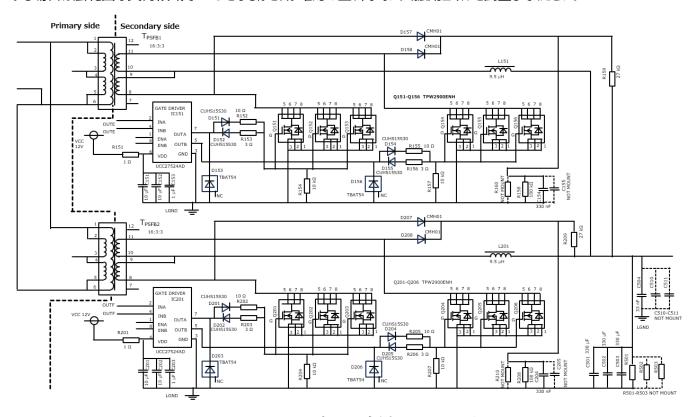

#### 3.3.2. 本デザインのPSFB回路

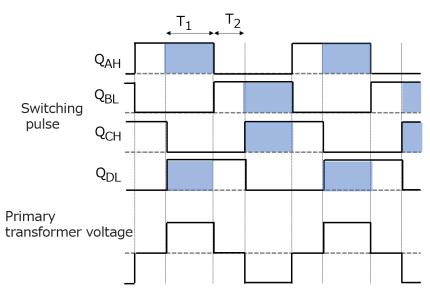

本デザインではセミブリッジレス PFC 回路の後段で 50V 出力を生成しています。広範囲な負荷領域で ZVS 動作が可能な Texas Instruments 社製コントローラーUCC28950 (IC251、以下、PSFB コントローラー) を用いることで高効率を実現しています。以下に、本デザインの PSFB 回路の基本的な設計項目に関して説明します。なお、コントローラー周辺の詳細設計に関しては UCC28950 のデータシート、関連ドキュメントなどをご参照ください。また、本デザインの詳細仕様に関してはリファレンスガイドをご参照ください。

図 3.9 PSFB 回路 1 (コントローラー周辺)

#### 出力電圧

PSFB 回路の出力電圧 Vout は図 3.9 の外付け抵抗 R266、R267、R279、R280、R281、R282、R283 によって設定する ことができます。設定値は上記抵抗と PSFB コントローラーUCC28950 の電圧設定用内部電圧 (VREF = 5.0V) によって以下式で算出されます。

$$V_{out}(V) = \frac{VREF(V) \times R267 \times (R279 + R280 + R280 + R282 + R283)}{(R266 + R267) \times (R282 + R283)}$$

PSFB 回路の出力電圧の初期設定は R266 =  $2.2k\Omega$ 、R267 =  $2.2k\Omega$ 、R279 =  $6.8k\Omega$ 、R280 =  $22k\Omega$ 、R281 =  $22k\Omega$ 、R282 =  $2.2k\Omega$ 、R283 =  $470\Omega$ となっており、 $V_{OUT}$  = 50V です。必要に応じて上記抵抗値を変更し、所望の出力電圧値に設定してください。

#### スイッチング周波数

PSFB 回路のスイッチング周波数 f<sub>PWM</sub> は IC の RT 端子と VREF 端子の間の外付け抵抗 R258、R259 によって設定することができます。スイッチング周波数は以下の式で算出されます。

$$f_{PWM}(kHz) = \frac{2.5 \times 10^3}{\left(\frac{R258(k\Omega) + R259(k\Omega)}{VREF(V) - 2.5} + 1\right)}$$

この式で、RT の単位は  $k\Omega$ 、VREF は V、 $f_{PWM}$  は kHz です。この式は経験的な近似であり、単位の対応はとれていません。スイッチング周波数の初期設定は、R258+R259 =  $45k\Omega$ となっており、約 130kHz です。必要に応じて上記抵抗値を変更し、所望の周波数に設定してください。

#### ソフトスタート

PSFB 回路のソフトスタート時間は SS/EN 端子とグランド間に接続された外付けのコンデンサーC251 と 25µA (typ) の内部 充電電流によって設定することができます。設定値は以下の式によって計算することができます。0.55V は SS/EN 端子電圧、VNI は EA + 端子の電圧です。

$$T_{SS}(s) = \frac{C251 \times (VNI + 0.55)}{25(\mu A)}$$

$$= \frac{C251 \times \left(\frac{VREF(V) \times R267}{R266 + R267} + 0.55\right)}{25(\mu A)}$$

R266 および R267 は 2.2kΩであり V<sub>REF</sub>は 5V、ソフトスタート時間の初期設定は C251 = 2.2μF となっており、268ms です。 必要に応じて C251 の容量値を変更し、所望のソフトスタート時間に設定してください。ソフトスタート期間中にカレントリミッターが作動しないことを確認する必要があります。

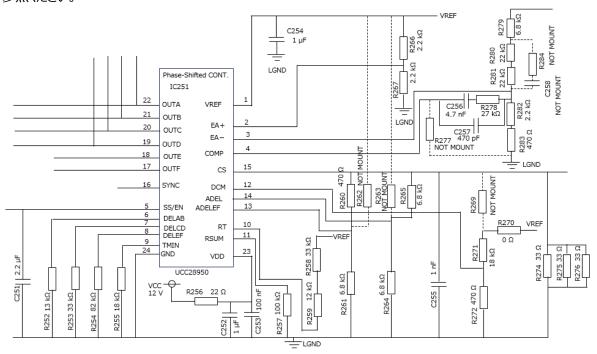

#### ゲート駆動回路

図 3.10 におけるゲート駆動回路の設計は電源効率と EMI ノイズに影響を与えます。一般的に、電源効率と EMI ノイズはトレードオフの関係にあるため、両者のバランスを取った設計を行う必要があります。 PSFB では ZVS を実施していますが、もしハードスイッチング領域が存在し、それが EMI ノイズの原因である場合は該当する MOSFET (Q701、Q702) のゲート直列抵抗(R705、R706、R708、R709) を大きな値に変更し、確認を行うことを推奨します。 PFC のゲート駆動回路と同様にターンオン時、ターンオフ時それぞれ独立して調整できる回路構成になっているため、 どちらかだけの調整で対応できる場合はシステムの電源効率への影響を低減できる可能性があります。

図 3.10 PSFB 回路 2 (1 次側 MOSFET 周辺)

## カレントリミッター

PSFB 回路のカレントリミッターは図 3.11 のカレントトランス (T101)、図 3.9 の PSFB コントローラーの CS 端子と GND 間に接続された電流検出抵抗 (R274//R275//R276)、電流制限しきい値 (2V) によって設定することができます。 CS に流れる電流と電流検出抵抗による電圧がしきい値に到達すると、 PSFB コントローラーは 1 次側の MOSFET を制御し、2 次側に異常な電流を流さないようにします。 カレントリミットレベルは以下の式で算出されます。

$$I\_limit = \frac{2.0}{(R274//R275//R276) \times transfomer\ turns\ ratio}$$

カレントリミッターの初期設定は R274//R275//R276 =  $11\Omega$ 、巻数比は 100:1 のため 18.2A となっています。必要に応じて上記値を変更し、所望の電流値に設定してください。

図 3.11 PSFB 回路 3 (カレントリミット回路)

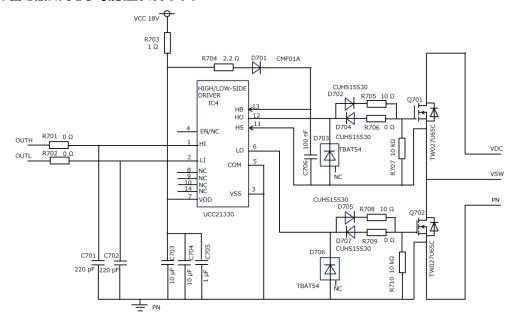

## トランス

PSFB における 2 次側回路を図 3.12 に示します。2 次側の同期整流回路はトランス T<sub>PSFB1</sub> と T<sub>PSFB2</sub> による 2 並列の回路 になっています。

PSFB 回路の定常状態における同期整流側のオンデューティーを 85%に設定すると、出力電圧が 50V なので、2 次側には 60V 程度の方形波が必要となります。本デザインの PFC 出力電圧は 391V であるため、トランス (Tpsfb1、Tpsfb2) の 1 次側と 2 次側の巻数比は 16:3:3 (センタータップ方式) を選択します。これにより、2 次側には 58.65V の方形波が発生することになります。その他、1 次-2 次間絶縁耐圧、巻線温度上昇、磁束飽和、コアロスなどを十分に考慮する必要があります。

また、本デザインではトランスのリーケージインダクタンスに加え共振用コイル (L101) を利用して ZVS を行っております。共振が不足すると ZVS が実現できず、電源効率低下や EMI ノイズ増大などの問題が発生する可能性があるため、トランスを変更する場合は広範囲な負荷領域で ZVS となるかどうか確認の上、同時に共振用コイルを調整してください。

図 3.12 PSFB 回路 4 (2 次側 MOSFET 周辺)

#### 出力コンデンサー

出力コンデンサーはシステムの要求する出力電圧リップル範囲によって決定します。出力電圧リップル  $V_{ripple}$  はスイッチングによって発生するリップル電流 $\Delta$ I と出力コンデンサーの ESR、容量 (Cap)、 ESLによって発生する各電圧の合成波形となります。センタータップにかかるスイッチングの電圧を  $V_{sw}$ 、出力電圧を  $V_{out}$ 、スイッチング周波数を F (図 3.12) とすると、ESR、 Cap、 ESLによって発生する電圧は以下の式で算出されます。

$$V_{ripple\ ESR} = \Delta I \times ESR$$

$$V_{\text{ripple\_Cap}} = \frac{\Delta I}{8 \times C_{\text{out}} \times F \times 2}$$

$$V_{ripple\_ESL} = \frac{V_{SW} \times ESL}{L}$$

ここで、

$$\Delta I = \frac{(V_{SW} - V_{out}) \times V_{out} \times 2(phases)}{V_{SW} \times F \times 2 \times L}$$

であり、 $V_{sw} = 58.65V$ 、 $V_{out} = 50V$ 、F = 130kHz、 $L = 9.5\mu H$  とすると、 $\Delta I = 5.97A$  となります。

各要素で発生する出力リップル電圧の大半は Vripple ESR です。

使用コンデンサー (C501~C503 EKZN630ELL331MJ25S) の ESR は 37m $\Omega$ で 3 並列使用のため 12.3m $\Omega$ となり、 $V_{ripple\_ESR}$ は

$$V_{rinnle\ ESR} = \Delta I \times ESR = 5.97 \times 12.3m = 73.4mV$$

となります。システムに要求されるリップル電圧を満足できるよう、出力コンデンサーの容量を調整する必要があります。また、負荷急変時に出力に発生するアンダーシュート、オーバーシュートが規定電圧範囲に入っていること、出力のコンデンサーの許容リップル電流が確保できていることも確認する必要があります。

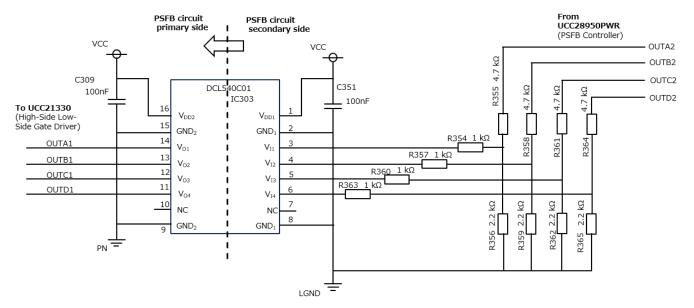

#### 3.4. PSFB 回路の 1 次側と 2 次側の通信

図 3.13 に示すように PSFB 回路の 1 次側と 2 次側の信号伝達に 4 チャネルのデジタルアイソレーター DCL540C01 を使用しています。2 次側に配置した PSFB コントローラーから出力された 1 次側フルブリッジ回路の MOSFET 駆動信号は DCL540C01 を通して送られます。

フォトカプラーが発光素子 (LED) と受光素子を同一パッケージに内蔵し、光を透過する樹脂により電気的絶縁し、LED のオン/オフにより信号を伝達する構造であるのに対して、デジタルアイソレーターは絶縁膜を備えた変調用チップと復調用チップを同一パッケージに内蔵し、磁界あるいは電界 (磁気結合) により信号を伝達する構造です。

DCL540C01は当社独自の磁気結合型絶縁伝送方式を採用することで高CMTI(\*3-2) 100kV/μs (min) を実現し、これによりノイズの影響を受けても誤動作しにくいため、機器の安定動作に貢献します。また、低パルス幅ひずみ3.0ns (max) と高速伝送レート150Mbps (max) を実現しているため、高速通信用途に適しています。

#### (\*3-2) コモンモード過渡耐性 (CMTI)

コモンモード(同相)ノイズは信号、GND両ラインに重畳し同じ方向に電流が流れるタイプのノイズです。独立した電源で駆動される回路間を電気的に絶縁しながら信号伝送を行うためにデジタルアイソレーターが使用されますが、このような場合においても一方の電位が変動する場合、コモンモードノイズは発生します。このコモンモードノイズによりスタンダードデジタルアイソレーター内部の1次(入力側)- 2次(出力側)間のカップリング容量に流れる変位電流があるレベルまで達するとデジタルアイソレーター、ひいてはシステムの誤動作の原因になります。従って、このようなコモンモードノイズに対する耐量はシステムを安定動作させるために重要となります。CMTIはこのようなGND間で発生する高スルーレートの過渡電圧に対応する能力をあらわしており、CMTIが大きいほどノイズに対して強く、絶縁が必要とされるアプリケーションでの応用に適していることを意味します。

図 3.13 デジタルアイソレーター (DCL540C01)

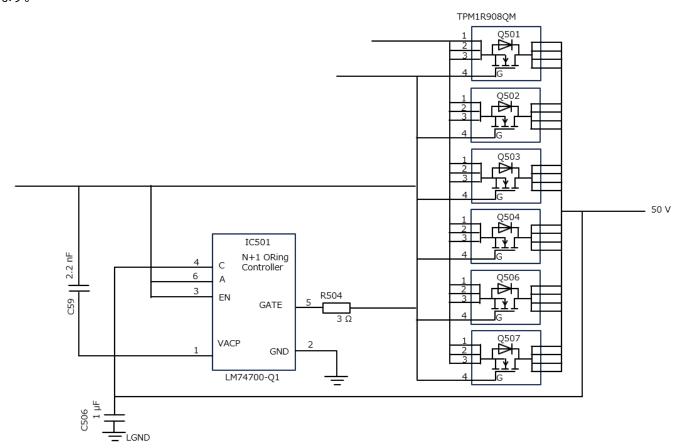

# 3.5. ORing 回路設計

本デザインは N+1 冗長運転の要求に対応できるよう、50V 出力に ORing 回路を実装しています。ORing 回路は Texas Instruments 社製コントローラーLM74700-Q1 (IC501) とオン・オフ用 MOSFET (Q501-Q504, Q506, Q507) によって構成されます。本デザインの出力と他の電源を並列に接続した状態で本デザインの出力電圧が他の電源の出力電圧より高い場合、ORing コントローラーはオン/オフ用 MOSFET をオンして出力に電流を供給します。本デザインの出力電圧が他の電源の出力電圧が他の電源の出力電圧が他の電源の出力電圧が他の電源の出力電圧が他の電源の出力電圧が他の電源の出力電圧が他の電源の出力電圧が他の電源の出力電圧が他の電源の出力電圧が他の電源の出力電圧が他の電源がら本デザインの出力電圧が他の電源が必要である。本デザインの ORing 回路詳細設計に関しては Texas Instruments 社製 LM74700-Q1 のデータシート、関連ドキュメントをご参照ください。オン/オフ用 MOSFET は最大負荷 (60A) 流した際に電圧ドロップ、オン抵抗による電力ロスがシステムの許容範囲となるように品種・数量を決定する必要があります。本デザインでは TPM1R908QM を 6pcs 実装しています。

図 3.14 ORing 回路

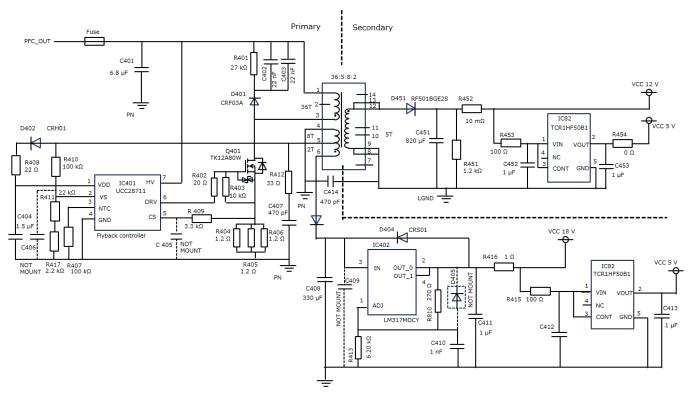

## 3.6. 補助電源

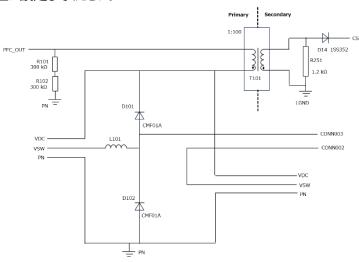

図 3.15 に補助電源回路を示します。本デザインでは各コントローラーや各 MOSFET 駆動 IC など必要な電力を供給するための補助電源を搭載し、交流入力のみで動作します。

補助電源は Texas Instruments 社製コントローラーUCC28711 を使用した電流断続モード (DCM) フライバック構成を採用し、レギュレーターIC と組み合わせて、1 次側用 18V および 5 V、2 次側用 12V および 5V を生成しています。

本項では、補助電源回路のトランス設計を説明します。回路の詳細設計に関しては UCC28711 のデータシートや関連ドキュメントを参照ください。

図 3.15 補助電源回路

#### 補助電源トランス設計

最大1次対2次巻線比N<sub>PS</sub> (max) は全負荷時の目標最大スイッチング周波数、最小入力コンデンサーバルク電圧、および 推定DCM共振時間によって決定できます。最初に目標スイッチング周波数とDCM共振時間に基づいて、オン時間と2次導通 時間の利用可能な最大合計デューティーサイクルD<sub>MAX</sub>を決定します。

$D_{MAX}$ は補助電源コントローラーの最大発振周波数 $f_{MAX}$ 、DCM共振時間 $t_R$  (ここでは、1/500kHzと仮定) を用いて、以下の式で算出されます。

D<sub>MAX</sub>が分かれば、1次巻線と2次巻線の最大巻数比を次の式で決定できます。D<sub>MAGCC</sub>は、定電流 (CC) 動作中の2次ダイオード導通デューティーサイクルとして定義されます。これは補助電源コントローラーによって内部的に0.425に設定されます。2次巻線の合計電圧はコンバーター出力電圧V<sub>OCV</sub>、2次整流器電圧V<sub>F</sub>、およびケーブル補償電圧 (V<sub>OCBC</sub>) の合計です。

$$D_{MAX} = 1 - \left(\frac{t_R}{2} \times f_{MAX}\right) - D_{MAGCC} = 1 - (1\mu s \times 100kHz) - 0.425 = 0.475$$

$$N_{PS(max)} = \frac{D_{MAX} \times V_{Bulk(min)}}{D_{MAGCC} \times (V_{OCV} + V_{F(D451-453)} + V_{OCBC})}$$

$$= \frac{0.475 \times 110V}{0.425 \times (12V + 0.68V)} = 9.7$$

Vocacはケーブル補償電圧ですが計算では省略しています。

ここで、1 次側巻き線の巻き数NPを36ターンとすると、2次側巻き線の巻き数Nsは以下の式で算出されます。

$$N_S > \frac{N_P}{N_{PS}} = \frac{36}{9.7} = 3.7$$

よって、本デザインでは2次側巻き線の巻き数Nsを5ターンとしました。

2次巻線と補助巻線のトランス巻数比 (Nas) は補助電源コントローラーの停止電圧VDD(off)とPSFBコントローラーの最小動作電圧Voccによって決まります。

$$N_{AS} = \frac{V_{DD(off)} + V_{FA(D402)}}{V_{OCC} + V_{F(D451-453)}} = \frac{(8.5 + 0.68)}{6.15 + 0.71} = 1.34$$

補助巻き線の巻き数NAUXは下記のとおり算出されます。

$$N_{AUX} = N_{AS} \times N_S = 1.34 \times 5 = 6.7$$

よって、本デザインでは補助巻き線の巻き数Nauxを8ターンとしました。

1 次側の制御電圧は、補助巻き線数を増やした出力から LDO (IC402) を介し 18V を生成しています。

# ご利用規約

本規約は、お客様と東芝デバイス&ストレージ株式会社(以下「当社」といいます)との間で、当社半導体製品を搭載した機器を設計する際に参考となるドキュメント及びデータ(以下「本リファレンスデザイン」といいます)の使用に関する条件を定めるものです。お客様は本規約を遵守しなければなりません。

# 第1条 禁止事項

お客様の禁止事項は、以下の通りです。

- 1. 本リファレンスデザインは、機器設計の参考データとして使用されることを意図しています。信頼性検証など、それ以外の目的には使用しないでください。

- 2. 本リファレンスデザインを販売、譲渡、貸与等しないでください。

- 3. 本リファレンスデザインは、高低温・多湿・強電磁界などの対環境評価には使用できません。

- 4. 本リファレンスデザインを、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用しないでください。

#### 第2条 保証制限等

- 1. 本リファレンスデザインは、技術の進歩などにより予告なしに変更されることがあります。

- 2. 本リファレンスデザインは参考用のデータです。当社は、データ及び情報の正確性、完全性に関して一切の保証をいたしません。

- 3. 半導体素子は誤作動したり故障したりすることがあります。本リファレンスデザインを参考に機器設計を行う場合は、誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウェア・ソフトウェア・システムに必要な安全設計を行うことをお願いします。また、使用されている半導体素子に関する最新の情報(半導体信頼性ハンドブック、仕様書、データシート、アプリケーションノートなど)をご確認の上、これに従ってください。

- 4. 本リファレンスデザインを参考に機器設計を行う場合は、システム全体で十分に評価し、お客様の責任において適用可否を判断して下さい。当社は、適用可否に対する責任は負いません。

- 5. 本リファレンスデザインは、その使用に際して当社及び第三者の知的財産権その他の権利に対する保証又は実施権の許諾を行うものではありません。

- 6. 当社は、本リファレンスデザインに関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をせず、また当社は、本リファレンスデザインに関する一切の損害(間接損害、結果的損害、特別損害、付随的損害、逸失利益、機会損失、休業損害、データ喪失等を含むがこれに限らない。)につき一切の責任を負いません。

#### 第3条 契約期間

本リファレンスデザインをダウンロード又は使用することをもって、お客様は本規約に同意したものとみなされます。本規約は予告なしに変更される場合があります。当社は、理由の如何を問わずいつでも本規約を解除することができます。本規約が解除された場合は、お客様は本リファレンスデザインを破棄しなければなりません。さらに当社が要求した場合には、お客様は破棄したことを証する書面を当社に提出しなければなりません。

#### 第4条 輸出管理

お客様は本リファレンスデザインを、大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用してはなりません。また、お客様は「外国為替及び外国貿易法」、「米国輸出管理規則」等、適用ある輸出関連法令を遵守しなければなりません。

#### 第5条 準拠法

本規約の準拠法は日本法とします。

#### 第6条 管轄裁判所

本リファレンスデザインに関する全ての紛争については、別段の定めがない限り東京地方裁判所を第一審の専属管轄裁判所とします。