Bi-CMOS 形リニア集積回路 シリコン モノリシック

# TB9M001FTG

車載用マイクロコントローラー内蔵 DC モーター向け IC

## 1. 概要

本製品 TB9M001FTG は、車載用マイクロコントローラー(MCU)に Arm® Cortex®-M0 processor、リレードライバー、LIN トランシーバーを統合した製品です。この IC は、車両のバッテリーレベルで動作する電源システムを備えており、外付けリレーを使用する DC モーターのアプリケーションに適しています。また、大容量のコードフラッシュとデータフラッシュを内蔵しており、LIN 制御のセカンダリーデバイスとして使用できます。待機時にはスタンバイモードに移行することで消費電力を削減します。

質量: 0.13 g (標準)

## 2. 用途

車載用（電動サンルーフ、電動ワイパー、パワーウィンドウ、パワーシート、用途）LIN 制御セカンダリーデバイス用

## 3. 特長

- MCU やリレードライバー、車両用電源システムなどの集積化によりシステムの小型化が実現可能

- LIN トランシーバー内蔵

\*\*\*\*\*

Arm、Cortex は、米国および／あるいはその他の国における Arm Limited(またはその子会社)の登録商標です。

\*\*\*\*\*

製品量産開始時期

2025-12-12

## 4. 機能

- Arm® Cortex®-M0 processor

- シリアルワイヤデバッグサポート

- 32 チャネル割り込みコントローラー1 サイクル乗算器

- 最大 40 MHz のクロック周波数

- 12KBytes ROM (ブートローダー、フラッシュ API), (incECC SEC/DED)

- 192KBytes Code Flash (incECC SEC/DED)

- 16KBytes Data Flash (incECC SEC/DED)

- 16KBytes SRAM (incECC SEC/DED)

- 32-bit Compare timers (DTIMER)

- 28-bit Capture timer (8 inputs, 6 measurement)

- WATCHDOG

- Power saving modes (CPU Sleep, Standby, CWU)

- 4 Legacy PWM Generator

- 14 General-purpose I/O Ports (GPIO)

- 10-bit A/D Converter (GADC) with 13 analog inputs (ADIN0-7, SWIN0-4)

- + internal temperature, VB, VCC

- 4 Low Side Drivers (LSD0-3)

- High Side Drivers (HSD0, HSD1)

- 9 High Voltage Input (SWIN0-4 + HPIN0-3)

- LDOs (LDO5V, LDO15V)

- Power On Reset (POR5V, PORL)

- 2 on-chip OSCs (IOSCH, IOSCL)

- External OSC

- PLL

- LIN ISO17987/SAEJ2602 transceiver + controller

- 2 full duplex serial interfaces (UART1, UART2), UART1 with LIN support

- SPI-I/F

- Thermal Shutdown (TSD)

- Package P-VQFN48-0707-0.50

- Single power supply from 6.0V~18V

- 温度範囲  $T_j = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$

- グリーンパッケージ (RoHS 対応)

- AEC-Q100 grade 1 準拠

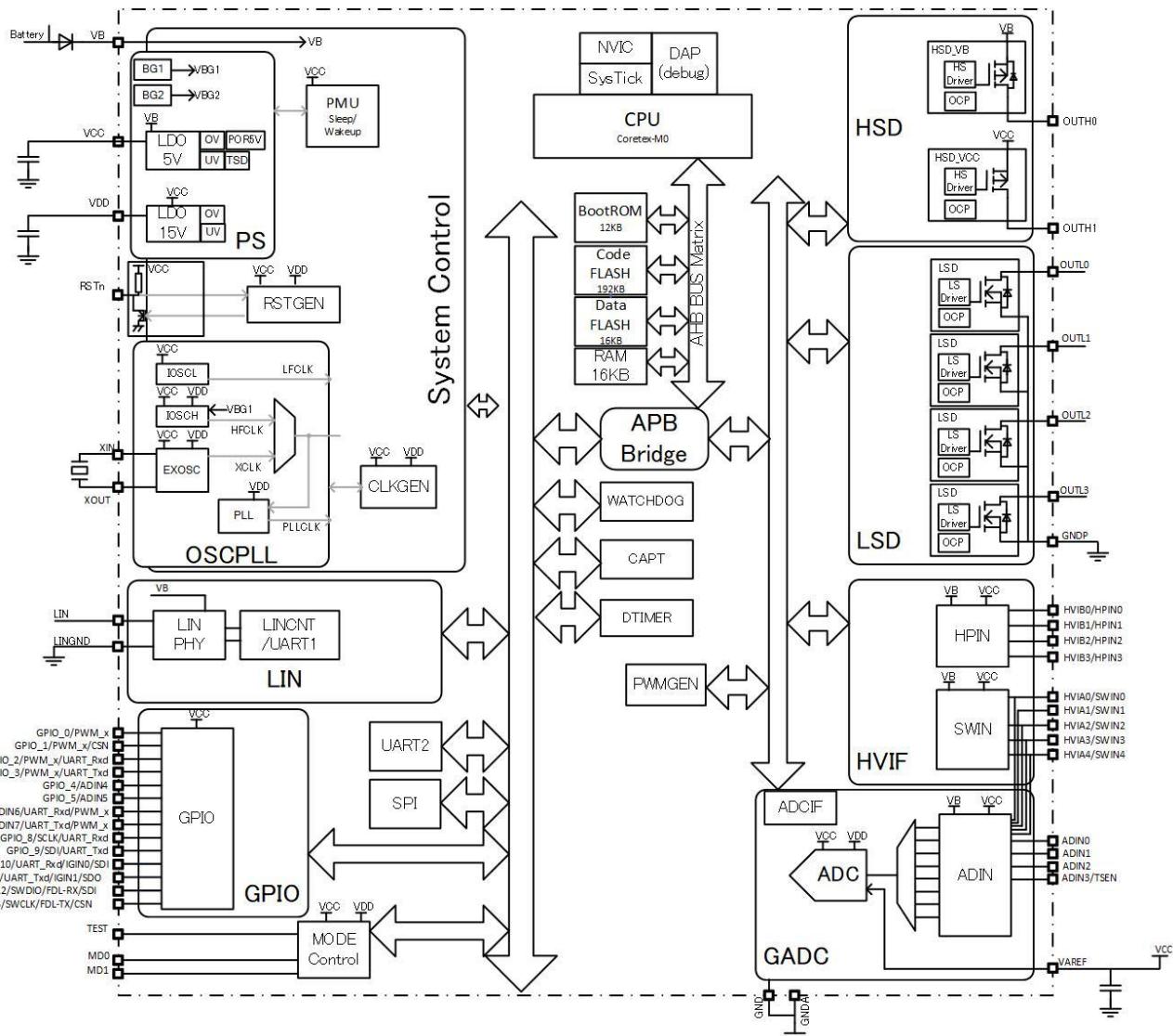

## 5. ブロック図

図 5.1 ブロック図

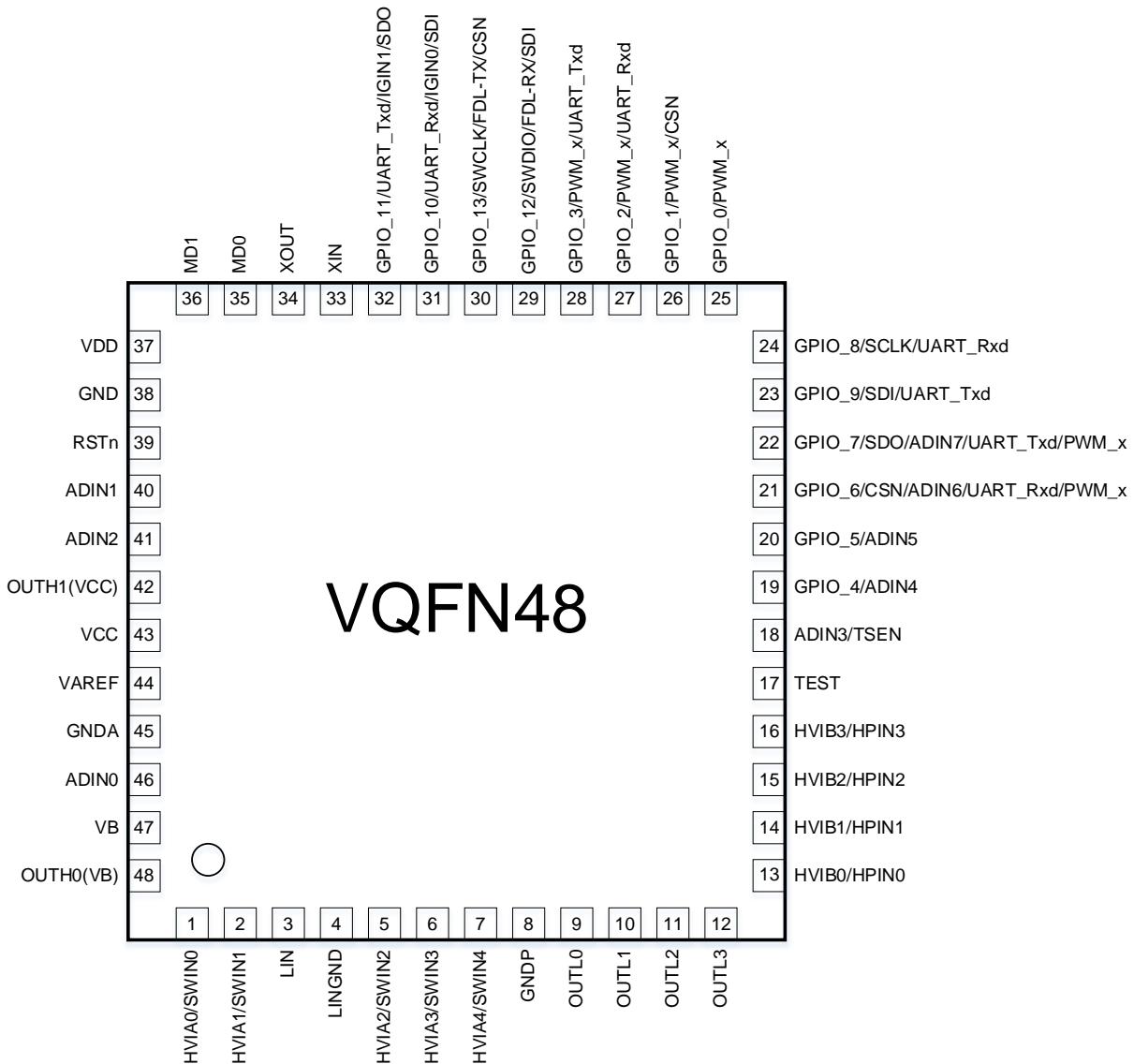

## 6. 端子配置図

(Top view)

図 6.1 端子配置図

## 7. 端子説明

表 7.1 端子説明

| 端子番号 | 名称                              | 入出力 | 端子説明              |

|------|---------------------------------|-----|-------------------|

| 1    | HVIA0/SWIN0                     | 入力  | 高耐圧論理入力／スイッチ入力    |

| 2    | HVIA1/SWIN1                     | 入力  | 高耐圧論理入力／スイッチ入力    |

| 3    | LIN                             | 入出力 | LIN 通信端子          |

| 4    | LINGND                          | -   | LIN 用 GND         |

| 5    | HVIA2/SWIN2                     | 入力  | 高耐圧論理入力／スイッチ入力    |

| 6    | HVIA3/SWIN3                     | 入力  | 高耐圧論理入力／スイッチ入力    |

| 7    | HVIA4/SWIN4                     | 入力  | 高耐圧論理入力／スイッチ入力    |

| 8    | GNDP                            | -   | GND (LSD 用)       |

| 9    | OUTL0                           | 出力  | Low Side ドライバー出力  |

| 10   | OUTL1                           | 出力  | Low Side ドライバー出力  |

| 11   | OUTL2                           | 出力  | Low Side ドライバー出力  |

| 12   | OUTL3                           | 出力  | Low Side ドライバー出力  |

| 13   | HVIB0/HPIN0                     | 入力  | 高耐圧論理入力／ホールセンサー入力 |

| 14   | HVIB1/HPIN1                     | 入力  | 高耐圧論理入力／ホールセンサー入力 |

| 15   | HVIB2/HPIN2                     | 入力  | 高耐圧論理入力／ホールセンサー入力 |

| 16   | HVIB3/HPIN3                     | 入力  | 高耐圧論理入力／ホールセンサー入力 |

| 17   | TEST                            | 入力  | テストモード選択          |

| 18   | ADIN3/TSEN                      | 入力  | ADC 入力／温度モニター     |

| 19   | GPIO_4/ADIN4                    | 入出力 | 汎用入出力ポート          |

| 20   | GPIO_5/ADIN5                    | 入出力 | 汎用入出力ポート          |

| 21   | GPIO_6/CSN/ADIN6/UART_Rxd/PWM_x | 入出力 | 汎用入出力ポート          |

| 22   | GPIO_7/SDO/ADIN7/UART_Txd/PWM_x | 入出力 | 汎用入出力ポート          |

| 23   | GPIO_9/SDI/UART_Txd             | 入出力 | 汎用入出力ポート          |

| 24   | GPIO_8/SCLK/UART_Rxd            | 入出力 | 汎用入出力ポート          |

| 25   | GPIO_0/PWM_x                    | 入出力 | 汎用入出力ポート          |

| 26   | GPIO_1/PWM_x/CSN                | 入出力 | 汎用入出力ポート          |

| 27   | GPIO_2/PWM_x/UART_Rxd           | 入出力 | 汎用入出力ポート          |

| 28   | GPIO_3/PWM_x/UART_Txd           | 入出力 | 汎用入出力ポート          |

| 29   | GPIO_12/SWDIO/FDL-RX/SDI        | 入出力 | 汎用入出力ポート          |

| 30   | GPIO_13/SWCLK/FDL-TX/CSN        | 入出力 | 汎用入出力ポート          |

| 31   | GPIO_10/UART_Rxd/IGIN0/SDI      | 入出力 | 汎用入出力ポート          |

| 32   | GPIO_11/UART_Txd/IGIN1/SDO      | 入出力 | 汎用入出力ポート          |

| 33   | XIN                             | 入力  | 外部オシレーター接続        |

| 34   | XOUT                            | 出力  | 外部オシレーター接続        |

| 35   | MD0                             | 入力  | モード選択             |

| 36   | MD1                             | 入力  | モード選択             |

| 37   | VDD                             | -   | 1.5V 電源出力         |

| 38   | GND                             | -   | GND               |

| 39   | RSTn                            | 入出力 | リセット入出力           |

| 40   | ADIN1                           | 入力  | ADC 入力            |

| 端子番号 | 名称         | 入出力 | 端子説明                        |

|------|------------|-----|-----------------------------|

| 41   | ADIN2      | 入力  | ADC 入力                      |

| 42   | OUTH1(VCC) | 出力  | High Side ドライバー出力 (VCC)     |

| 43   | VCC        | -   | 5V 電源出力                     |

| 44   | VAREF      | 入力  | ADC 用基準電圧入力                 |

| 45   | GNDA       | -   | GND                         |

| 46   | ADIN0      | 入力  | ADC 入力                      |

| 47   | VB         | -   | バッテリー入力                     |

| 48   | OUTH0(VB)  | 出力  | High Side ドライバー出力 (VB)      |

| -    | EP         | -   | Exposed pad, connect to GND |

| -    | Corner pin | -   | Corner pin, connect to GND  |

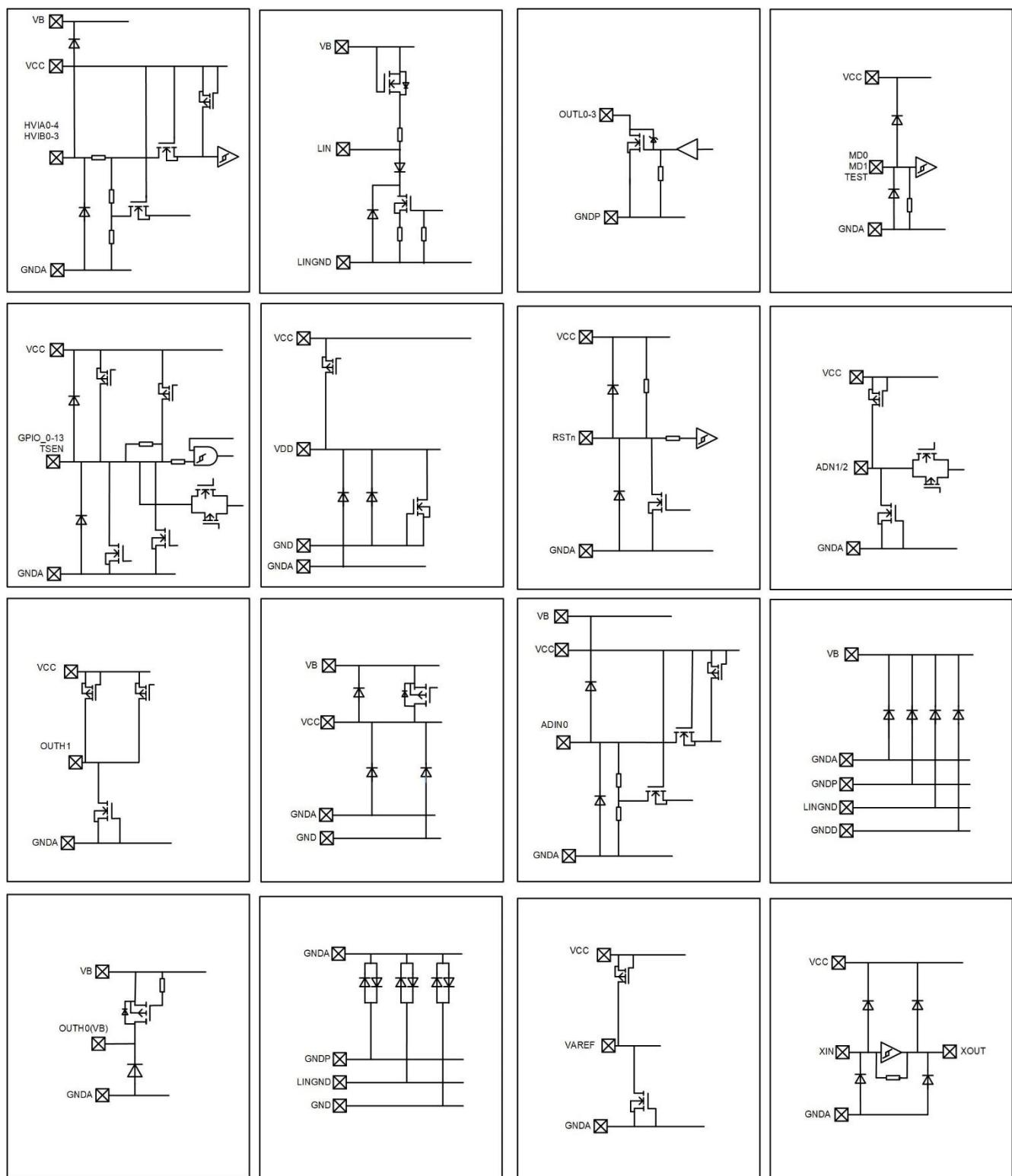

## 8. 入出力等価回路

図 8.1 入出力等価回路

## 9. 動作説明

### 9.1. CPU

- 本製品は、高性能・低消費電力な 32 ビットプロセッサー (Arm® Cortex®-M0 processor) が内蔵されています。ここでは、製品固有の情報について説明します。

#### 9.1.1. 概要

#### 9.1.2. Arm® Cortex®-M0 processor に関する情報

- 本製品で使用している Arm® Cortex®-M0 processor のリビジョンは以下のとおりです。

- CPU コアおよびそのアーキテクチャの詳細については、Arm® Cortex®-M0 processor のドキュメントセットをご参照ください。以下のリンクから入手可能です。

<http://infocenter.arm.com/help/index.jsp>

Armv6-M Architecture Reference Manual Issue.

Cortex-M0 Devices Generic User Guide Issue.

Cortex-M0 Technical Reference Manual Issue.

| Arm®プロセッサー名               | コアリビジョン |

|---------------------------|---------|

| Arm® Cortex®-M0 processor | r0p0-03 |

#### 9.1.3. 構成可能なオプション

- Arm® Cortex®-M0 processor は、一部のブロックについて実装するかどうかを選択することができます。

- 本製品での構成は以下のとおりです。

| 構成可能なオプション      | 実装        |

|-----------------|-----------|

| 割り込み本数          | 32 本      |

| エンディアン          | リトルエンディアン |

| SysTick Timer   | あり        |

| ウォッчポイントコンパレーター | 2 本       |

| ブレークポイントコンパレーター | 4 本       |

| ホールトデバッグ        | あり        |

| WIC             | なし        |

| デバッグポート         | シリアルワイヤ   |

| 乗算器             | 高速        |

- Arm® Cortex®-M0 processor には SysTick と呼ばれるシステムタイマーがあり、SysTick 例外を発生させることができます。

#### 9.1.4. 外部信号

- Arm® Cortex®-M0 processor デバッグ用として 2 線式のシリアルワイヤデバッグ SWD をサポートしています。

#### 9.1.5. モジュール構成

- Arm® Cortex®-M0 processor を搭載致します。

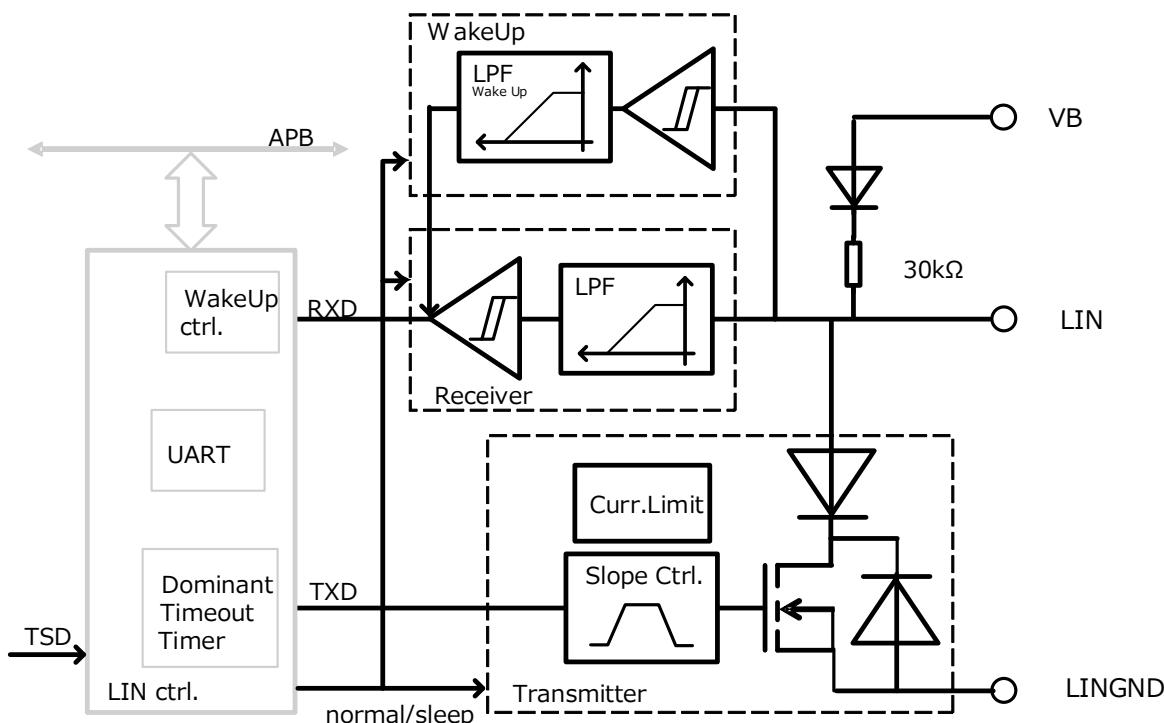

## 9.2. LINPHY

- 本製品は LIN の物理層を 1ch 内蔵しています(レスポンダー専用)。

- ISO 17987-4、ISO 17987-7 12V EPL (Electrical physical layer) 、および SAE J2602 に準拠する。

- IEC61000-4-2:2008 接触放電 (150pF,330 Ω) ±6kV の耐量を有します。

- 伝導ノイズを抑制するため、出力スロープ制御を持つ。

- スルーレート切り替え機能内蔵(低スロープモード <10kbps> / 通常スロープモード<20kbps> / Fast Baud Rate Mode<250kbps>)<>内は目安のボーレート。

- 出力ドライバーに、電流制限機能を持つ。

- 出力ドライバー近傍に TSD 回路を持つ。

- LIN BUS からの Wakeup 要求パルスを検出する回路を 1ch 持ち、検出通知を出力する。

- Wakeup パルス幅は電気的特性で規定された最大 150μs とする。

- システムコントローラーや PMU などはこの通知によってウェイクアップ処理を行い、低消費電力モードから Active モードへ遷移し、CPU へ割り込みを要求する。

図 9.2.1 LINPHY ブロック図

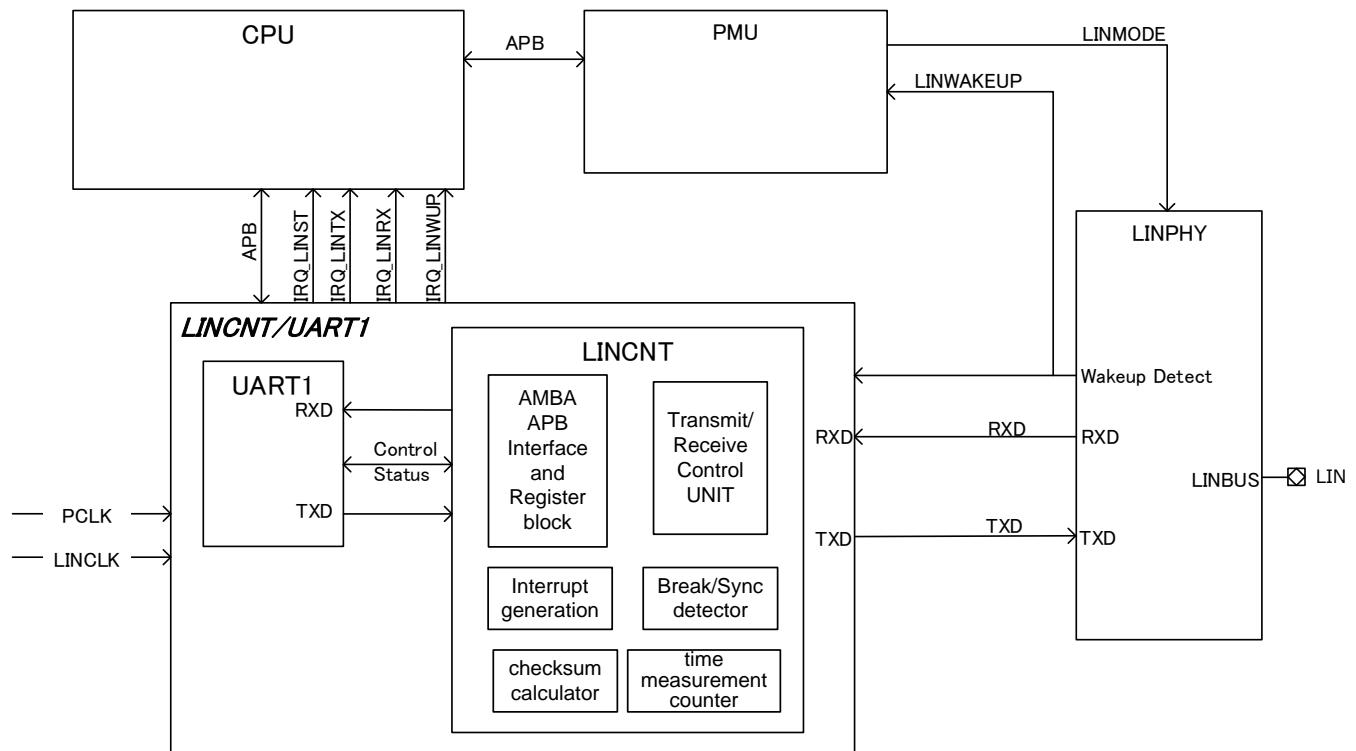

### 9.3. LINCNT/UART1

- ISO 17987:2016 LIN スタンダードに準拠

- LIN 通信はレスポンダー専用

- BREAK 検出機能

- 受信 Break 幅変更機能 (固定ボーレートモード時は 9.5Tbit/10.5Tbit、自動ボーレートモード時は 10Tbit/11Tbit)

- ボーレート調整機能 (Mode 選択可能)

- 固定ボーレートモード機能

- Sync による自動ボーレートモード機能

- ボーレート変更機能

- Wakeup 機能

- Wakeup 送信機能

- Wakeup 受信機能 (RXD low 期間測定機能)

- 送信・受信チェックサム計算アクセラレーターによる演算サポート機能搭載

- LINBUS アイドル期間検出機能

- ドミナントタイムアウト機能搭載

- レスポンススペース間隔設定機能 (0~7Tbit)

- インターバイトスペース間隔設定機能 (0~3Tbit)

- レスポンスフィールドのデータバイト数変更機能 (1~8byte)

- タイマー機能

- RXD low 期間測定機能

- Frame タイムアウト機能

- TXD low 期間測定機能

- RXD High 期間測定機能

- 割り込み機能

- 受信割り込み

- LIN Break フィールド受信割り込み

- LIN Sync フィールド受信割り込み

- LIN 受信完了受信割り込み

- 送信割り込み

- LIN 送信完了割り込み

- ステータス割り込み

- LIN Framing エラー割り込み

- LIN RXD low 期間測定機能割り込み

- LIN Frame タイムアウトエラー割り込み

- LIN Sync フィールド受信エラー割り込み

- LIN ビットエラー割り込み

- LIN TXD low 期間タイムアウト割り込み

- LIN RXD high 期間タイムアウト割り込み

図 9.3.1 LIN コントローラー内ブロック図

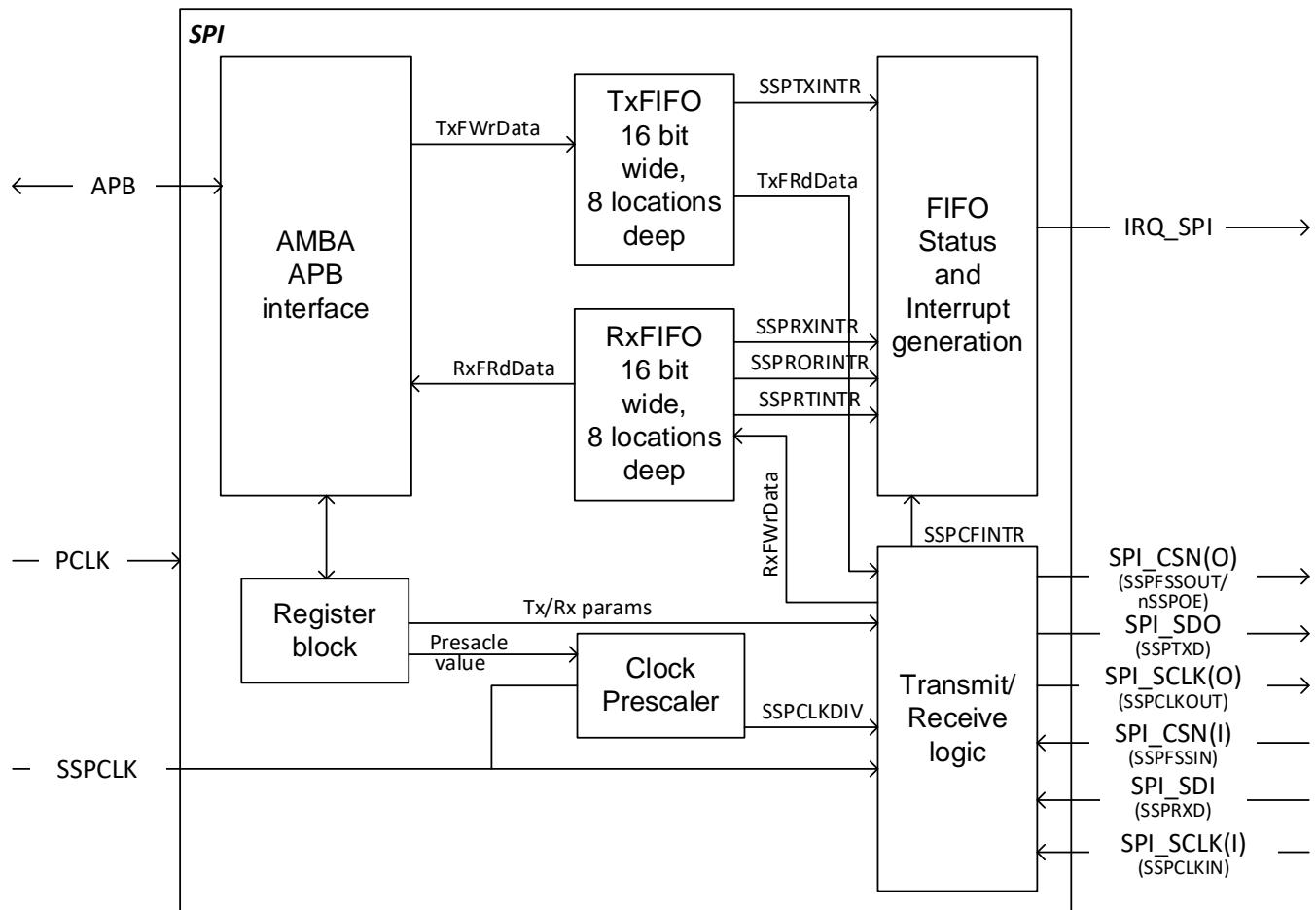

## 9.4. SPI

### 9.4.1. 外部信号

外部とは GPIO を介して接続されます。

図 9.4.1 SPI ブロック図

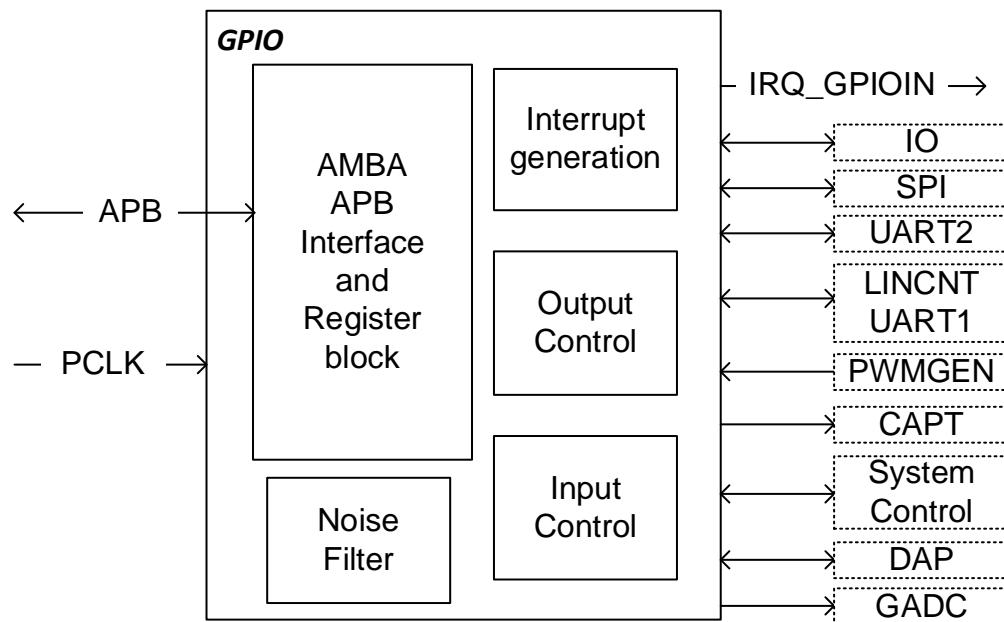

## 9.5. GPIO

- 本製品は、14 本の汎用入出力端子を持ちます。

- PullUp/PullDown 機能を使用することができます。

- Standby Mode 時の Wakeup 要因に使用することができる端子を 2 本持ちます。

- 上記 Wakeup 要因設定端子を割り込み要因として設定することも可能です。

- 4 本の Analog 入力機能のある PORTを持ちます。

- UART/SPI との通信用に設定することのできる複数の PORTを持ちます。

- 6 本の PWM の出力を設定することのできる PORTを持ちます。

- 6 本の CAPT のタイミング用入力に設定することのできる PORTを持ちます。

- 2 本の WakeUp または割り込み要因の入力に設定することのできる PORTを持ちます。

- SWD の Debug に使用する端子として設定することのできる複数の PORTを持ちます

図 9.5.1 GPIO ブロック図

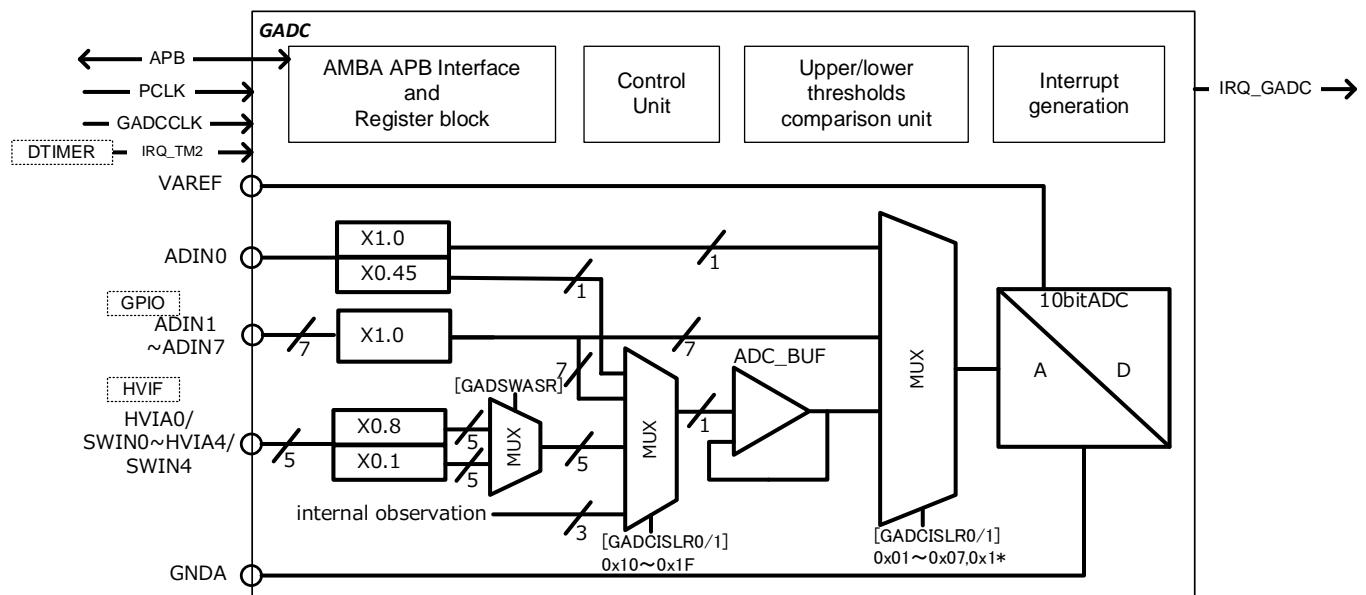

## 9.6. 10bit Analog Digital Converter (GADC)

- 10bit 逐次比較型 ADC(GADC)を 1 ユニット持ちます

- 24 系統のアナログ入力の測定を選択することができます。

- 最大で 12ch の測定を設定することができます。

- 12ch のうち 4ch は上限下限を設定し、範囲外の時に割り込みを発生することができます。

- 3 つの測定モードを持ちます。

- シングル変換・コマンドトリガーモード

レジスター書き込みにより測定を開始し、指定した測定を一通り実行後に停止します。

- コンティニュアス変換・コマンドトリガーモード

レジスター書き込みにより測定を開始し、指定した測定を繰り返します。

- コンティニュアス変換・タイマートリガーモード

タイマー同期により測定を開始し、指定した測定を繰り返します。(TIMER2 と連携)

\* TIMER1 とは連携できません

- 測定後に測定終了割り込みを発生することができます。

- ADINO 端子から入力を x1、または x0.45 倍に分圧した経路が選択可能です。

- 各 ADINx 端子には、図 8.1 端子など入出力回路図 に示されるように GND に対し分圧のための抵抗 (Min 500kΩ) を持ります。(この抵抗は x1 を選択しても切り離されません。)

図 9.6.1 GADC ブロック図

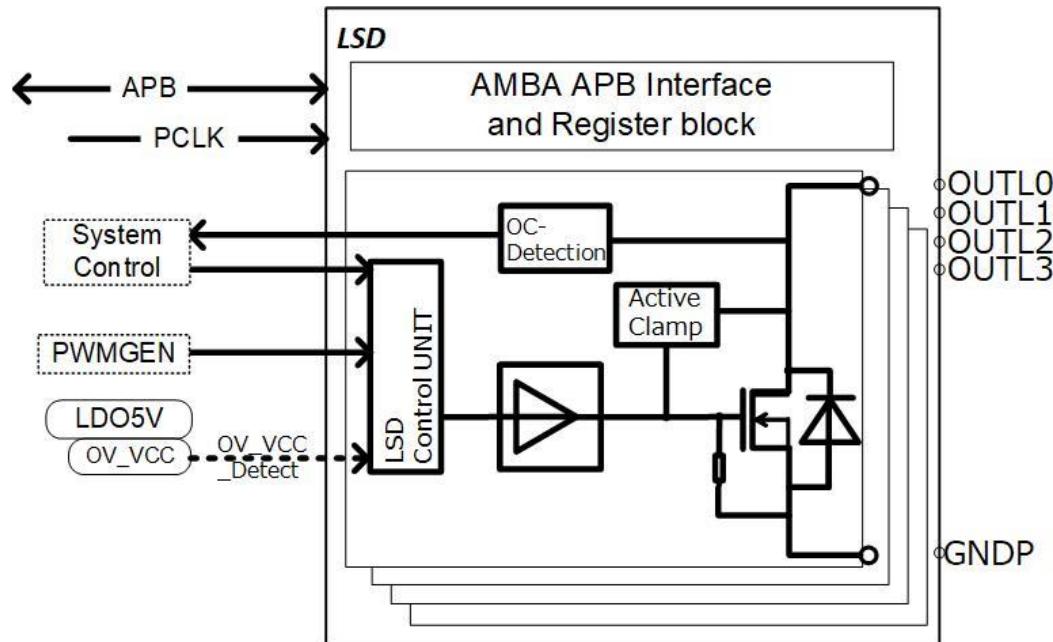

## 9.7. Low Side Drivers (LSD)

- LSD モジュールは、リレー駆動用 LowSide ドライバーを 4ch 持っています。

- 各 ch は過電流検知機能を持ち、検出時は対象の ch の出力を停止します。

- 各 ch は出力停止時の電圧上昇を抑えるために、アクティブクランプ回路を備えています。

- ドライバーの制御は、レジスター制御と PWM 制御を選択することができます

図 9.7.1 LSD ブロック図

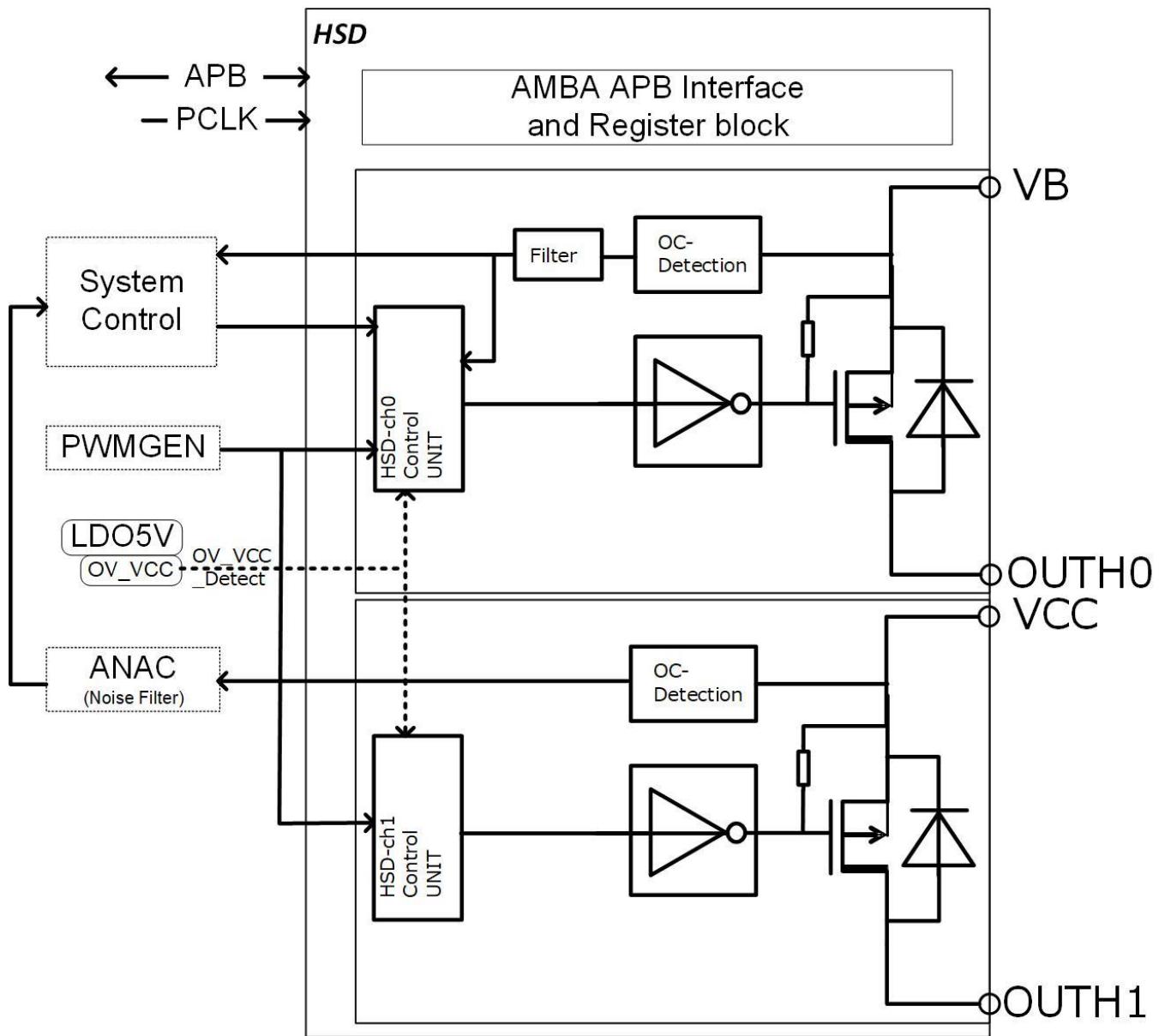

## 9.8. High Side Drivers (HSD)

- 2ch の High Side Driver を内蔵しています。VB (12V 系) の High Side Driver を 1ch、VCC(5V 系) の High Side Driver を 1ch。

- 各 High Side Driver は、過電流検知機能を持ちます。

- 各 High Side Driver は、レジスター制御と PWM 制御を選択することができます。

図 9.8.1 HSD ブロック図

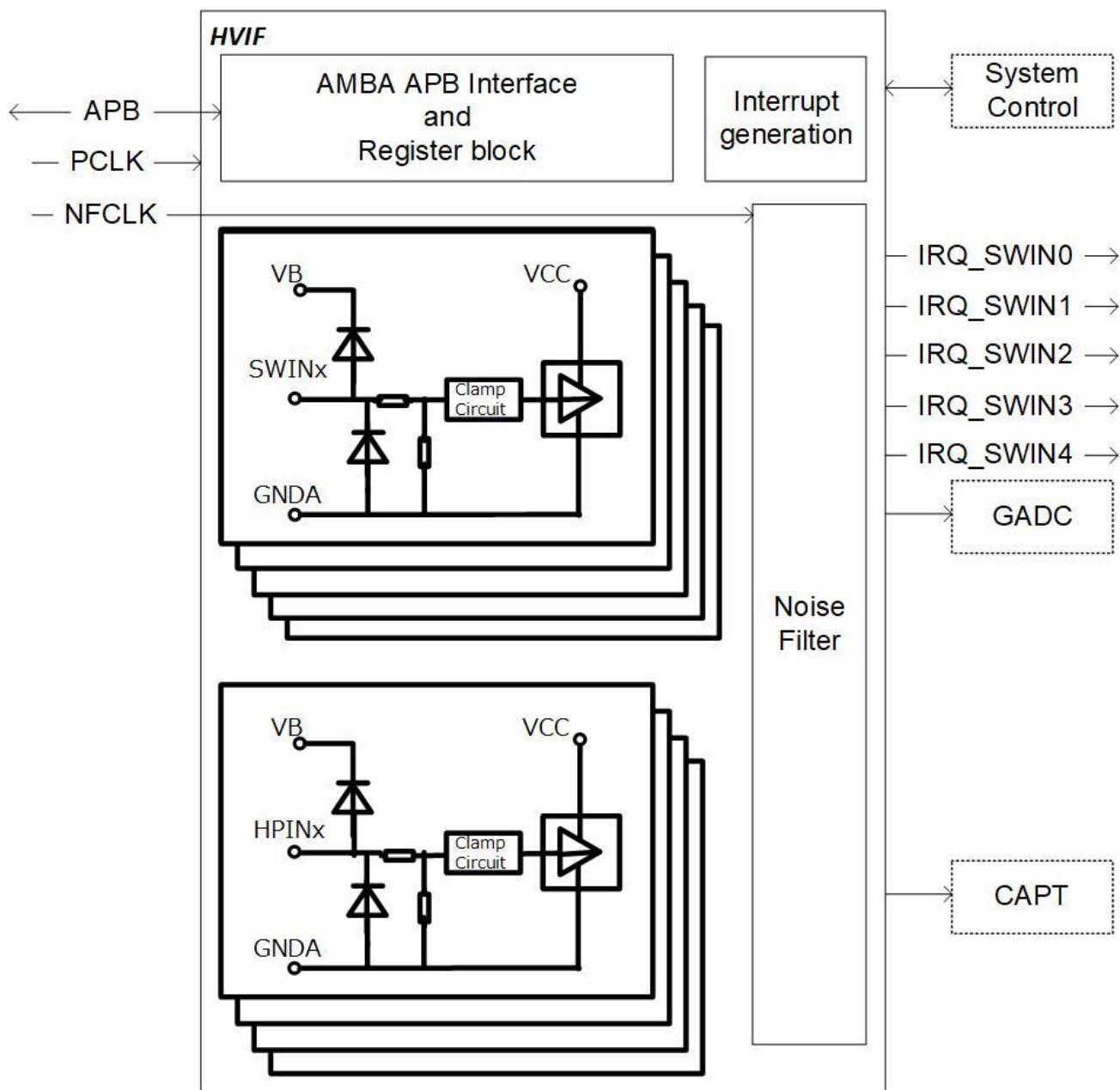

## 9.9. High Voltage Inputs (HVIF)

- Switch 入力用端子、5 入力

- Hall sensor 用入力端子、4 入力

- デジタルフィルターによるノイズ除去機能

- Switch 入力共通で 4 種設定可能

- Hall 入力共通で 4 種設定可能

- SWIN0-4 および HPIN0-3 端子は高電圧 (VB) 入力のため、プルダウン抵抗と内部回路保護のため クランプ回路を内蔵しています

図 9.9.1 HVIF ブロック図

## 9.10. メモリーマップ

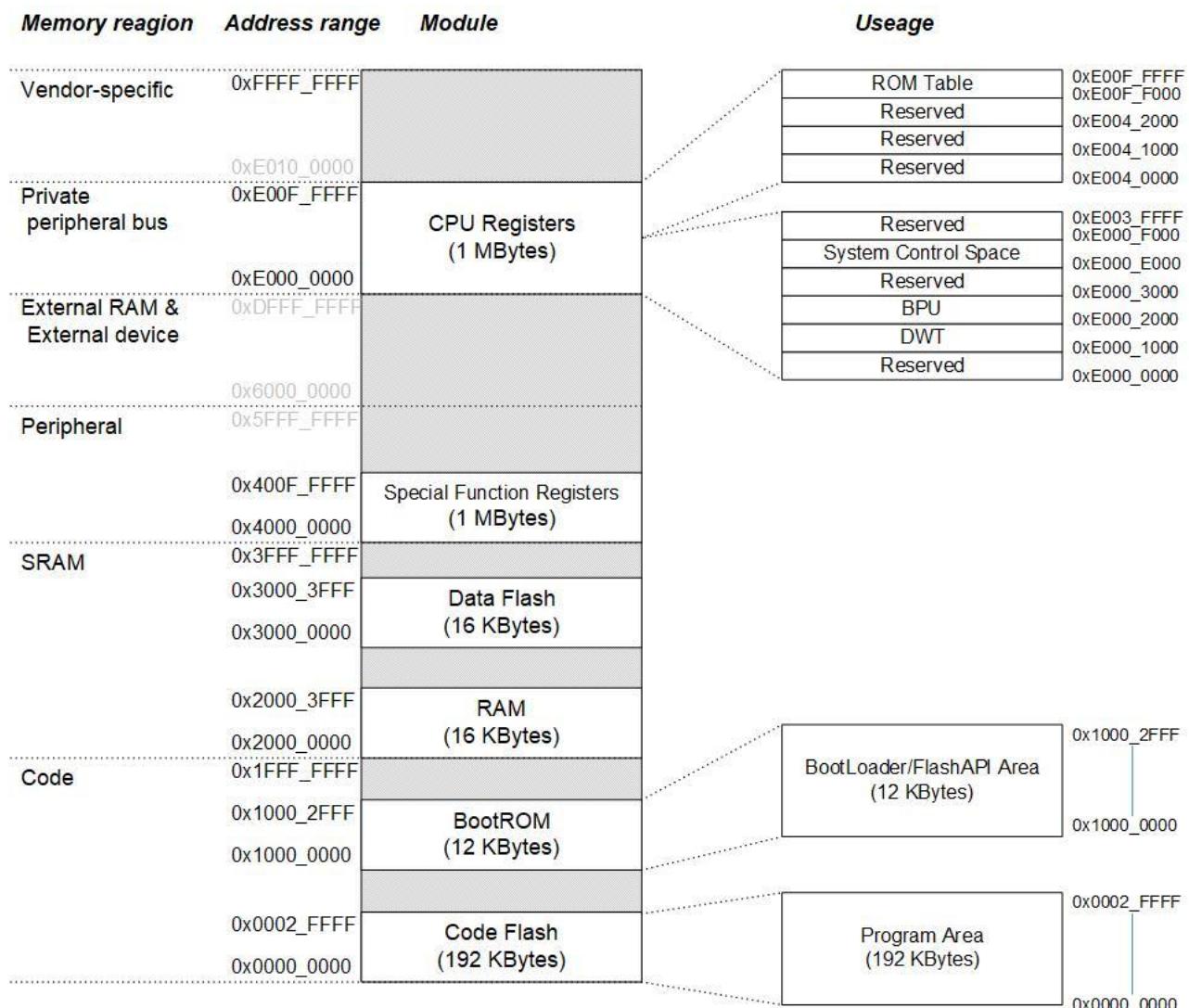

図 9.10.1 Memory Map (Normal and Debug Modes)

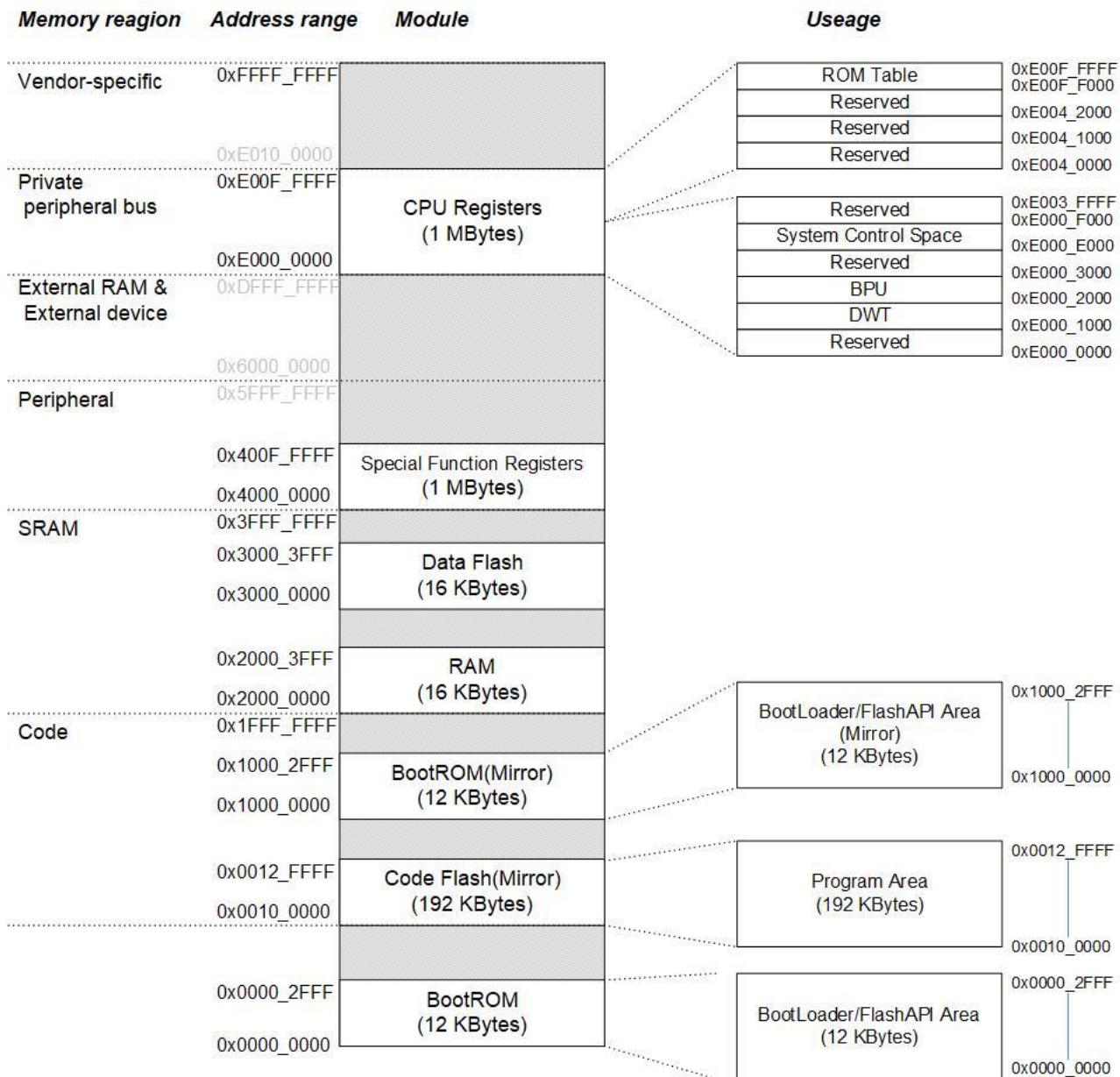

図 9.10.2 Memory Map (Flash Download Mode)

## 10. 電気的特性

### 10.1. 絶対最大定格

表 10.1 絶対最大定格

| 項目     | 記号    | 端子    | 条件                                                    | 規格値                       | Unit |

|--------|-------|-------|-------------------------------------------------------|---------------------------|------|

| 電源電圧 1 | VB1   | VB    |                                                       | -0.3~40                   | V    |

| 電源電圧 2 | VVCC  | VCC   |                                                       | -0.3~6.0                  | V    |

| 電源電圧 3 | VVDD  | VDD   |                                                       | -0.3~2.1                  | V    |

| 端子間電圧  | VGND  | 右記    | LINGND, GNDP, GND, GNDA                               | -0.3~0.3                  | V    |

| 入力電圧 1 | VLIN  | LIN   | VB1=6~18V の時                                          | -27~40                    | V    |

| 入力電圧 2 | VIN2  | 右記    | HVIA0~HVIA4<br>HVIB0~HVIB3, ADIN0                     | -0.3~VB1+0.3<br>(Max 40V) | V    |

| 入力電圧 3 | VIN3  | 右記    | GPIO_0~13, MD0, MD1, ADIN1~ADIN3,<br>VAREF, RSTn, XIN | -0.3~VVCC+0.3<br>(Max 6V) | V    |

| 出力電圧 1 | VOUT1 | LIN   | VB1=6~18V の時                                          | -27~40                    | V    |

| 出力電圧 2 | VOUT2 | OUTH0 |                                                       | -0.3~VB1+0.3<br>(Max 40V) | V    |

| 出力電圧 3 | VOUT3 | 右記    | GPIO_0~13, RSTn, OUTH1, XOUT                          | -0.3~VVCC+0.3<br>(Max 6V) | V    |

| 入力電流 1 | IIN1  | 右記    | OUTL0~3                                               | 0~0.8                     | A    |

| 動作温度   | Ta    | —     | —                                                     | -40~90                    | °C   |

| 保存温度   | Tstg  | —     | —                                                     | -55~150                   | °C   |

注:

- 絶対最大定格は瞬時たりとも超えてはならない規格です。絶対最大定格を超えると IC の破壊や劣化や損傷の原因となり、IC 以外に障害を与える恐れもあります。いかなる動作条件においても必ず絶対最大定格を超えないように設計を行ってください。また、ご使用に際しては、記載された動作範囲内でご使用ください。

- ±18V 以上の定格については印加時間に制約があります。18~28V(≤90min)、28~40V(≤400ms)。

### 10.2. 動作範囲

表 10.2 動作範囲

| 項目   | 記号   | 定格      | 単位 | 備考             |

|------|------|---------|----|----------------|

| 電源電圧 | VB1  | 18~27   | V  | 電気的特性は満足していません |

|      |      | 6~18    |    | -              |

|      |      | 4.8~6   |    | 電気的特性は満足していません |

| 動作温度 | Topr | -40~90  | °C | 周囲温度 Ta        |

|      |      | -40~150 |    | ジャンクション温度 Tj   |

## 10.3. IC 全般特性

表 10.3.1 電気的特性

(特に記載のない限り  $VB=6\sim18V$ ,  $VCC=4.8\sim5.2V$ ,  $VDD=1.45\sim1.55V$ ,  $Tj=-40\sim150^{\circ}C$ )

| 項目                                                    | 記号     | 端子 | 条件                                                                       | 規格値 |      |     | Unit    |

|-------------------------------------------------------|--------|----|--------------------------------------------------------------------------|-----|------|-----|---------|

|                                                       |        |    |                                                                          | Min | Typ. | Max |         |

| スタンバイ電流 1<br>(Standby Mode)                           | Istby1 | -  | $VB=12.0V$ , $Ta=25^{\circ}C$                                            | -   | -    | 20  | $\mu A$ |

| スタンバイ電流 2<br>(Standby Mode)<br>(Guaranteed by design) | Istby2 | -  | $VB=13.5V$ , $Ta<50^{\circ}C$                                            | -   | -    | 50  | $\mu A$ |

| スタンバイ電流 3<br>(CWU Mode)                               | Istby3 | -  | $VB=12V$ , $Ta=25^{\circ}C$<br>【Sleep】: 51ms、【PWU】: 125 $\mu s$ 設定時の平均電流 | -   | -    | 80  | $\mu A$ |

## 参考情報 :

$VB=12V$ 、常温、EXOSC 使用、SYSCLK=40MHz、LIN, ADC のみ動作状態、IC 外部負荷無しの条件において、消費電流（評価結果）は約 11mA となります。

消費電流は CPU 負荷、動作周波数など使用条件により変化します。

## 10.4. 5V/1.5V 電源回路

表 10.4.1 電気的特性

(特に記載のない限り  $VB=6\sim18V$ ,  $VCC=4.8\sim5.2V$ ,  $VDD=1.45\sim1.55V$ ,  $Tj=-40\sim150^{\circ}C$ )

| 項目                                                   | 記号        | 端子           | 条件                                                                                                                      | 規格値  |      |      | Unit |

|------------------------------------------------------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                                                      |           |              |                                                                                                                         | Min  | Typ. | Max  |      |

| Output voltage                                       | Vcc       | VCC<br>(注 1) | $Io = -10\mu A \sim -135mA$ (IC 内部の VCC/VDD 最大自己消費電流と OUTH1(max 65mA) の合計消費電流)                                          | 4.8  | 5    | 5.2  | V    |

| Limit current 1                                      | Icc_lim1  |              | $VCC \geq (4.0V)$                                                                                                       | -850 | -475 | -250 | mA   |

| Limit current 2<br>(注 3)                             | Icc_lim2  |              | $VCC \leq (3.0V)$                                                                                                       | -250 | -115 | -10  | mA   |

| Drop voltage<br>(Guaranteed<br>by design)            | Vdrop     |              | 以下の条件下における VB-VCC.<br>$VB = 4.5V$ , および<br>$Io = -10\mu A \sim -135mA$ (IC 内部の VCC/VDD 最大自己消費電流と OUTH1(max 65mA) の合計電流) | -    | -    | 0.5  | V    |

| Under release<br>voltage1(VCC)                       | Vccuvrel  |              | VCC 立ち上がり(UV_VCC)                                                                                                       | 4.20 | -    | 4.75 | V    |

| Under detect<br>voltage1(VCC)                        | Vccuvdet  |              | VCC 立ち下がり(UV_VCC)                                                                                                       | 4.00 | -    | 4.35 | V    |

| Over detect/<br>release<br>voltage (VCC)             | Vccovdet  |              |                                                                                                                         | 5.28 | -    | 5.72 | V    |

| Under release<br>voltage2 (VCC)                      | Vccporrel |              | VCC 立ち上がり(POR5V)                                                                                                        | 3.22 | 3.60 | 3.98 | V    |

| Under detect<br>voltage2 (VCC)                       | Vccpordet |              | VCC 立ち下がり(POR5V)                                                                                                        | 3.07 | 3.45 | 3.83 | V    |

| Output voltage 2                                     | Vdd       | VDD<br>(注 2) | $Io = -10\mu A \sim -60mA$ (IC 内部の VDD 最大自己消費電流)                                                                        | 1.45 | 1.5  | 1.55 | V    |

| Under release<br>voltage (VDD)                       | Vddporrel |              | VDD 立ち上がり                                                                                                               | 1.35 | -    | 1.45 | V    |

| Limit current                                        | Idd_lim3  |              |                                                                                                                         | -250 | -150 | -70  | mA   |

| Under detect<br>voltage (VDD)                        | Vddpordet |              | VDD 立ち下がり                                                                                                               | 1.30 | -    | 1.40 | V    |

| Over detect/<br>release<br>voltage (VDD)             | Vddovdet  |              |                                                                                                                         | 1.55 | -    | 1.65 | V    |

| Detection<br>temperature<br>(Specified by<br>design) | tsd       | -            |                                                                                                                         | 150  | 170  | 190  | °C   |

| Release<br>temperature<br>(Guaranteed by<br>design)  | tsrel     | -            |                                                                                                                         | 135  | -    | 175  | °C   |

注 1: VCC 端子には  $1.0\mu F$  以上の容量をできる限り端子付近に接続してください。注 2: VDD 端子には  $2.2\mu F$  以上の容量をできる限り端子付近に接続してください。

使用環境を想定した評価および確認を、ユニット基板上で十分に実施した上で、外付け回路を決定してください。

注 3: 【Standby】 / 【Sleep】 時の VCC における Limit Current は Limit Current 2 となります。

## 10.5. スイッチ／ホールセンサーIC 入力(High Voltage Inputs)

表 10.5.1 電気的特性

(特に記載のない限り  $VB=6\sim18V$ ,  $VCC=4.8\sim5.2V$ ,  $VDD=1.45\sim1.55V$ ,  $Tj=-40\sim150^{\circ}C$ )

| 項目         | 記号     | 端子           | 条件                                                                                         | 規格値          |      |              | Unit |

|------------|--------|--------------|--------------------------------------------------------------------------------------------|--------------|------|--------------|------|

|            |        |              |                                                                                            | Min          | Typ. | Max          |      |

| 入力電圧範囲     | Irange | SWINx, HPINx | 入力端子に抵抗 $10k\Omega$ を接続した上で抵抗の IC 側とは逆端の電圧。<br>High 側しきい値、または Low 側しきい値までコンパレーター出力を反転しないこと | -1           | -    | 18           | V    |

| High 側しきい値 | VIH    | SWINx, HPINx | SWINx, HPINx = L→H<br>入力抵抗 = $10k\Omega$                                                   | 0.65<br>×VCC | -    | -            | V    |

| Low 側しきい値  | VIL    | SWINx, HPINx | SWINx, HPINx = H→L<br>入力抵抗 = $10k\Omega$                                                   | -            | -    | 0.35<br>×VCC | V    |

| 入力電流 3     | IIH    | SWINx, HPINx | SWINx, HPINx = 0V                                                                          | -100         | -    | 1000         | nA   |

| 入力 NF      | Tnf    | SWINx, HPINx | フィルター設定 = $1.2\mu s$                                                                       | 1.14         | 1.2  | 1.26         | μs   |

| プルダウン抵抗    | Rpd    | SWINx, HPINx |                                                                                            | 500          | -    | -            | kΩ   |

## 10.6. 発振器

表 10.6.1 発振器 電気的特性

(特に記載のない限り  $VB=6\sim18V$ ,  $VCC=4.8\sim5.2V$ ,  $VDD=1.45\sim1.55V$ ,  $Tj=-40\sim150^{\circ}C$ )

| 項目                           | 記号    | 端子        | 条件                              | 規格値  |      |      | Unit |

|------------------------------|-------|-----------|---------------------------------|------|------|------|------|

|                              |       |           |                                 | Min  | Typ. | Max  |      |

| IOSCH Frequency (HFCLK)      | Fhclk | -         |                                 | 19.0 | 20   | 21.0 | MHz  |

| IOSCL Frequency (LFCLK)      | Flclk | -         |                                 | 27.2 | 32   | 36.8 | kHz  |

| External osc (注 1) Frequency | Exosc | XIN, XOUT | 使用可能な外付け Cellalock or X'tal の定数 | 16   | -    | 20   | MHz  |

注 1:

External OSC の外付け部品としましては、メーカーマッチングでご確認の上ご使用ください。

External OSC の外付け部品として CSTNE16MOVH3C000R0, CSTNE20MOVH3C000R0 にて動作確認済みです。

External OSC の外付け部品は  $\pm 0.2\%$ 以下のものを選択してください

## 10.7. Reset Generator &amp; 待機時間

表 10.7.1 Reset Generator 電気的特性

(特に記載のない限り  $VB=6\sim18V$ ,  $VCC=4.8\sim5.2V$ ,  $VDD=1.45\sim1.55V$ ,  $Tj=-40\sim150^{\circ}C$ )

| 項目              | 記号           | 端子       | 条件                                                                           | 規格値               |      |                   | Unit |

|-----------------|--------------|----------|------------------------------------------------------------------------------|-------------------|------|-------------------|------|

|                 |              |          |                                                                              | Min               | Typ. | Max               |      |

| 低レベル出力電圧        | VOL          | RSTn(出力) | $I_o = +5mA$                                                                 | 0                 | -    | 0.4               | V    |

| アナログ NF         | Tnf          | RSTn(入力) |                                                                              | 10                | 20   | 40                | μs   |

| WATCHDOG リセット時間 | Trst_wdt     | -        | WATCHDOG リセット要求の後 IC 内部遅延リセットが解除されるまでの時間(Flash busy 時を除く)                    | -                 | 70   | -                 | μs   |

| 起動安定待ち時間 1      | trst1        | -        | VCC 低電圧 1 復帰後 CPU のリセットが解除されるまでの時間                                           | -                 | -    | 8                 | ms   |

| 起動安定待ち時間 2      | trst2        | -        | Wakeup 検出から、LDO15V の安定後に CPU のリセットが解除されるまでの時間                                | -                 | -    | 2                 | ms   |

| 外部発振器 安定待ち時間    | Twait_ex_osc | -        | 村田製作所の 16MHz セラロック発振器 CSTNE16M0VH3C000R0 使用時、S/W による発振開始の設定後から、発振器が安定するまでの時間 | -                 | -    | 1                 | ms   |

| PLL 出力 安定待ち時間   | Twait_pll    | -        |                                                                              | -                 | -    | 140               | μs   |

| Pull up 抵抗      | Rpu          | RSTn     | VCC-RSTn 端子間                                                                 | 30                | 50   | 100               | kΩ   |

| RSTn 入力電圧       | VIH          | RSTn(入力) |                                                                              | 0.75 $\times VCC$ | -    | -                 | V    |

| RSTn 入力電圧       | VIL          | RSTn(入力) |                                                                              | -                 | -    | 0.25 $\times VCC$ | V    |

## 10.8. Data Flash 特性

表 10.8.1 Data Flash 電気的特性

(特に記載のない限り VB=6~18V, VCC=4.8~5.2V, VDD=1.45~1.55V, Tj=-40~150°C)

| 項目              | 記号      | 端子 | 条件                        | 規格値 |                                                    |      | Unit   |

|-----------------|---------|----|---------------------------|-----|----------------------------------------------------|------|--------|

|                 |         |    |                           | Min | Typ.                                               | Max  |        |

| バス周波数(注 1)      | FbusDT  | -  |                           | -   | -                                                  | 42   | MHz    |

| リード周波数          | FrdDT   | -  |                           | -   | -                                                  | 10.5 | MHz    |

| データ保持時間 1       | Tret1DT | -  | Tj=85°C, 10k 回の書き込み/消去の後  | 20  | -                                                  | -    | 年      |

| データ保持時間 2       | Tret2DT | -  | Tj=85°C, 100k 回の書き込み/消去の後 | 5   | -                                                  | -    | 年      |

| Flash 容量        | -       | -  |                           | -   | 16                                                 | -    | KBytes |

| データアクセス<br>サイズ  | DaccDT  | -  | 読み出し                      | -   | Word(32bit)<br>/Half<br>word(16bit)<br>/Byte(8bit) | -    | -      |

| 消去ブロック<br>サイズ   | DdelDT  | -  |                           | -   | 2                                                  | -    | KBytes |

| 消去ブロック時間        | TdelDT  | -  | 1 ブロック(2KBytes)           | -   | 6.8                                                | -    | ms     |

| 書き込み<br>ブロックサイズ | DwrDT   | -  |                           | 8   | -                                                  | 128  | Bytes  |

| 書き込みブロック<br>時間  | TwrDT   | -  | 2Word-32Word(同一ページ内)      | -   | 2.4                                                | -    | ms     |

注 1: バス周波数に合わせて Flash リードアクセスの wait 設定を変更する必要があります。

## 10.9. Code Flash 特性

表 10.9.1 Code Flash 電気的特性

(特に記載のない限り VB=6~18V, VCC=4.8~5.2V, VDD=1.45~1.55V, Tj=-40~150°C)

| 項目              | 記号      | 端子 | 条件                      | 規格値 |                 |      | Unit   |

|-----------------|---------|----|-------------------------|-----|-----------------|------|--------|

|                 |         |    |                         | Min | Typ.            | Max  |        |

| バス周波数(注 1)      | FbusCF  | -  |                         | -   | -               | 42   | MHz    |

| リード周波数          | TrdCF   | -  |                         | -   | -               | 10.5 | MHz    |

| データ保持時間 1       | Tret1CF | -  | Tj=85°C, 1k 回の書き込み/消去の後 | 20  | -               | -    | 年      |

| Flash 容量        | -       | -  |                         | -   | 192             | -    | KBytes |

| データアクセス<br>サイズ  | DaccCF  | -  | 読み出し/書き込みに同じ            | -   | Word<br>(32bit) | -    | -      |

| 消去時間            | Tdel    | -  | 192KBytes               | -   | 200             | -    | ms     |

| 書き込み時間          | Twr     | -  |                         | -   | 5               | -    | s.     |

| 消去ブロック<br>サイズ   | DdelCF  | -  |                         | -   | 8               | -    | KBytes |

| 消去ブロック時間        | TdelCF  |    | 1 ブロック(8KBytes)         | -   | 6.8             | -    | ms     |

| 書き込みブロック<br>サイズ | DwrCF   | -  |                         | -   | 128             | -    | Bytes  |

| 書き込みブロック<br>時間  | TwrCF   | -  | 32Word                  | -   | 2.4             | -    | ms     |

注 1: バス周波数に合わせて Flash リードアクセスの wait 設定を変更する必要があります。

## 10.10. LIN 特性

表 10.10.1 LIN 電気的特性

(特に記載のない限り  $VB=6\sim18V$ ,  $VCC=4.8\sim5.2V$ ,  $VDD=1.45\sim1.55V$ ,  $Tj=-40\sim150^{\circ}C$ )

| 項目                                                     | 記号                     | 端子  | 条件                                                                                                                                                                                                  | 規格値  |      |                 | Unit      |

|--------------------------------------------------------|------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------|-----------|

|                                                        |                        |     |                                                                                                                                                                                                     | Min  | Typ. | Max             |           |

| Supply voltage range                                   | $V_{VB}$               | VB  | ECU operating voltage range (Param 9)                                                                                                                                                               | 8.0  | -    | 18.0            | V         |

| Supply voltage range                                   | $V_{SUP}$              | VB  | Note : Param 10 of LIN configuration is defined 7.0V(min), IC requires 6.0V(min) on 5V regulator.                                                                                                   | 6.0  | -    | 18.0            | V         |

| Supply voltage MAX Ratings                             | $V_{SUP\_NON\_OP}$     | VB  | Voltage range with in which the device is not destroyed.<br>An optional time limit for the maximum value shall be at least 400ms. No guarantee of correct operation (Param 11)                      | -0.3 | -    | 40              | V         |

| BUS MAX Ratings                                        | $V_{BUS\_MAX\_RATING}$ | LIN | Voltage range with in which the device is not destroyed (Param 82)<br>An optional time limit for the maximum value shall be at least 400ms. No guarantee of correct operation.                      | -27  | -    | 40              | V         |

| Receiver threshold voltage, recessive to dominant edge | $V_{th\_rec}$          | LIN | Low Voltage: Recessive Input Threshold (SAE)                                                                                                                                                        | 0.4  | -    | 0.53            | $V_{SUP}$ |

| Receiver threshold voltage, dominant to recessive edge | $V_{th\_dom}$          | LIN | High Voltage: Dominant Input Threshold (SAE)                                                                                                                                                        | 0.47 | -    | 0.6             | $V_{SUP}$ |

| BUS current limitation                                 | $I_{BUS\_LIM}$         | LIN | Current Limitation for Driver dominant state driver on $V_{BUS} = V_{BAT\_maxd}$ (Param 12)                                                                                                         | 40   | -    | 200             | mA        |

| Leakage current(dominant)                              | $I_{BUS\_PAS\_dom}$    | LIN | Input leakage current at the receiver incl. slave pull-up resistor as specified in Param 26 driver off $V_{BUS} = 0V$ $V_{BAT} = 12V$ (Param 13)                                                    | -1   | -    | -               | mA        |

| Leakage current(recessive)                             | $I_{BUS\_PAS\_rec}$    | LIN | Driver off $8V < V_{BAT} < 18V$ , $8V < V_{BUS} < 18V$ , $V_{BUS} > V_{BAT}$ (Param 14)                                                                                                             | -    | -    | 20              | $\mu A$   |

| Leakage current                                        | $I_{BUS\_NO\_GND}$     | LIN | Control unit disconnected from ground GNDDevice = $V_{SUP}$ $0V < V_{BUS} < 18V$ $V_{BAT} = 12V$ Loss of local ground shall not affect communication in the residual network (Param 15)             | -1   | -    | 1               | mA        |

| Leakage current                                        | $I_{BUS\_NO\_BAT}$     | LIN | $V_{BAT}$ disconnected $V_{SUP} = GND$ $0V < V_{BUS} < 18V$ Node shall sustain the current that can flow under this condition. Bus shall remain operational under this condition (Param 16 and SAE) | -    | -    | 23              | $\mu A$   |

| Voltage of Receiver dominant state                     | $V_{BUS\_dom}$         | LIN | Receiver dominant state Note: Param 17 of LINPHY configuration is not defined minimum voltage (Param 17)                                                                                            | -27  | -    | $0.4 \times VB$ | V         |

| 項目                                                   | 記号             | 端子  | 条件                                                                                                                                                                                                                               | 規格値   |      |       | Unit             |

|------------------------------------------------------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------------|

|                                                      |                |     |                                                                                                                                                                                                                                  | Min   | Typ. | Max   |                  |

| <b>Voltage of Receiver recessive state</b>           | $V_{BUS\_rec}$ | LIN | Receiver recessive state (Param 18)                                                                                                                                                                                              | 0.6   | -    | -     | $V_{SUP}$        |

| <b>Receiver center voltage</b>                       | $V_{BUS\_CNT}$ | LIN | $V_{BUS\_CNT} = (V_{th\_dom} + V_{th\_rec})/2$ (Param 19)                                                                                                                                                                        | 0.475 | -    | 0.525 | $V_{SUP}$        |

| <b>Receiver hysteresis</b>                           | $V_{HYS}$      | LIN | $V_{HYS} = V_{th\_rec} - V_{th\_dom}$ (Param 20 and SAE)                                                                                                                                                                         | 0.07  | -    | 0.175 | $V_{SUP}$        |

| <b>Duty cycle D1<br/>(for worst case at 20 kbps)</b> | D1             | LIN | $THRec(max) = 0,744 \times V_{SUP}$ ;<br>$THDom(max) = 0,581 \times V_{SUP}$ ;<br>$V_{SUP} = 7,0 \text{ V} \sim 18 \text{ V}$ ;<br>$tBIT = 50\mu\text{s}$ ;<br>$D1 = tBus\_rec(min)/(2 \times tBIT)$ (Param 27)<br>$<PHYFBRM>=0$ | 0.396 | -    | -     | -                |

| <b>Duty cycle D2<br/>(for worst case at 20 kbps)</b> | D2             | LIN | $THRec(min) = 0,422 \times V_{SUP}$ ;<br>$THDom(min) = 0,284 \times V_{SUP}$ ;<br>$V_{SUP} = 7,6 \text{ V} \sim 18 \text{ V}$ ;<br>$tBIT = 50\mu\text{s}$ ;<br>$D2 = tBus\_rec(max)/(2 \times tBIT)$ (Param 28)<br>$<PHYFBRM>=0$ | -     | -    | 0.581 | -                |

| <b>Duty cycle D3<br/>(for worst case at 10 kbps)</b> | D3             | LIN | $THRec(max) = 0,778 \times V_{SUP}$ ;<br>$THDom(max) = 0,616 \times V_{SUP}$ ;<br>$V_{SUP} = 7,0 \text{ V} \sim 18 \text{ V}$ ;<br>$tBIT = 96\mu\text{s}$ ;<br>$D3 = tBus\_rec(min)/(2 \times tBIT)$ (Param 29)<br>$<PHYFBRM>=0$ | 0.417 | -    | -     | -                |

| <b>Duty cycle D4<br/>(for worst case at 10 kbps)</b> | D4             | LIN | $THRec(min) = 0,389 \times V_{SUP}$ ;<br>$THDom(min) = 0,251 \times V_{SUP}$ ;<br>$V_{SUP} = 7,6 \text{ V} \sim 18 \text{ V}$ ;<br>$tBIT = 96\mu\text{s}$ ;<br>$D4 = tBus\_rec(max)/(2 \times tBIT)$ (Param 30)<br>$<PHYFBRM>=0$ | -     | -    | 0.59  | -                |

| <b>Propagation delay</b>                             | $t_{rx\_pd}$   | LIN | Propagation delay of receiver (Param 31)<br>- bus dominant to RxD LOW<br>- bus recessive to RxD HIGH<br>$<PHYFBRM>=0$                                                                                                            | -     | -    | 6     | $\mu\text{s}$    |

| <b>Receiver delay symmetry</b>                       | $t_{rx\_sym}$  | LIN | Symmetry of receiver propagation delay rising edge with respect to falling edge (Param 32)<br>$<PHYFBRM>=0$                                                                                                                      | -2    | -    | 2     | $\mu\text{s}$    |

| <b>Bus pull-up resistance</b>                        | $R_{SLAVE}$    | LIN | internal resistance (Param 26)                                                                                                                                                                                                   | 20    | 30   | 60    | $\text{k}\Omega$ |

| <b>Bus pull-up resistance</b>                        | $R_{MASTER}$   | LIN | The serial diode is mandatory. Only for valid for transceiver with integrated master pull-up resistor (Param 25) external resistance                                                                                             | 900   | -    | 1100  | $\Omega$         |

| <b>LIN input capacity<br/>(Guaranteed by design)</b> | $C_{SLAVE}$    | LIN | Capacitance of slave node (Param 37)<br>$250\text{pF} \sim 220\text{pF} = 30\text{pF}$ max                                                                                                                                       | -     | -    | 30    | $\text{pF}$      |

| 項目                                         | 記号              | 端子  | 条件                                                           | 規格値 |      |     | Unit      |

|--------------------------------------------|-----------------|-----|--------------------------------------------------------------|-----|------|-----|-----------|

|                                            |                 |     |                                                              | Min | Typ. | Max |           |

| Over temperature detection threshold       | $T_{OT}$        | -   | (Guaranteed by IC design)                                    | 150 | -    | 190 | °C        |

| Over temperature detection hysteresis      | $\Delta T_{OT}$ | -   | (Guaranteed by IC design)                                    | -   | 10   | -   | °C        |

| Current consumption in Sleep Mode          | $I_{sleep}$     | VB  | VB=12V, RT=25°C, only working LIN bus<br>Wakeup signal       | -   | -    | 3   | µA        |

| Dominant time for bus Wakeup               | $t_{WAKE}$      | LIN | Wakeup pulse width from LIN bus                              | 30  | -    | 150 | µs        |

| Turn off time to [Sleep]                   | $t_{sleep}$     | -   | Turn off time from 【Active】 to<br>【Sleep】 or 【Standby】 state | -   | -    | 1   | ms        |

| Wake-up threshold voltage                  | $V_{BUSwk}$     | LIN | Threshold voltage for Wakeup signal detection                | 0.4 | 0.5  | 0.6 | $V_{SUP}$ |

| ESD Susceptibility HBM pins LIN vs. LINGND | $V_{ESDLIN}$    | LIN | IEC61000-4-2 Conducted HBM                                   | -6  | -    | 6   | kV        |

| ESD Susceptibility HBM pins LIN vs. LINGND | $V_{ESDLIN3}$   | LIN | AEC-Q100-002                                                 | -6  | -    | 6   | kV        |

## 10.11. 12V High Side ドライバー (HSD\_VB) 特性

表 10.11.1 HSD\_VB 電気的特性

(特に記載のない限り VB=6~18V, VCC=4.8~5.2V, VDD=1.45~1.55V, Tj=-40~150°C)

| 項目             | 記号     | 端子             | 条件                                                                           | 規格値 |      |      | Unit |

|----------------|--------|----------------|------------------------------------------------------------------------------|-----|------|------|------|

|                |        |                |                                                                              | Min | Typ. | Max  |      |

| オン抵抗           | RonH0  | OUTH0<br>(12V) | Id = -100mA                                                                  | 1   | -    | 5    | Ω    |

| 過電流検出電流        | IdetH0 | OUTH0<br>(12V) |                                                                              | -   | -    | -200 | mA   |

| ターンオン<br>遅延時間  | TonH0  | OUTH0<br>(12V) | [HSDCR]<HSDGC0>により HSD0 を ON してから、VBx10%を超えるまでの時間<br>負荷回路 : CL=30pF、RL=100Ω  | 2   | -    | 50   | μs   |

| ターンオフ<br>遅延時間  | ToffH0 | OUTH0<br>(12V) | [HSDCR]<HSDGC0>により HSD0 を OFF してから、VBx90%を下回るまでの時間<br>負荷回路 : CL=30pF、RL=100Ω | 2   | -    | 50   | μs   |

| 出力リーク電流        | IILH0  | OUTH0<br>(12V) | OUTH0= OFF, OUTH0=0V                                                         | -5  | -    | 5    | μA   |

| 過電流検出<br>フィルター | TnfH0  | OUTH0<br>(12V) |                                                                              | -   | -    | 5    | μs   |

## 10.12. 5V High Side ドライバー (HSD\_VCC) 特性

表 10.12.1 HSD\_VCC 電気的特性

(特に記載のない限り VB=6~18V, VCC=4.8~5.2V, VDD=1.45~1.55V, Tj=-40~150°C)

| 項目            | 記号     | 端子            | 条件                                                                             | 規格値  |      |      | Unit |

|---------------|--------|---------------|--------------------------------------------------------------------------------|------|------|------|------|

|               |        |               |                                                                                | Min  | Typ. | Max  |      |

| オン抵抗          | RonH1  | OUTH1<br>(5V) | Id = -65mA                                                                     | -    | 4    | 7    | Ω    |

| 過電流検出電流       | IdetH1 | OUTH1<br>(5V) |                                                                                | -250 | -    | -100 | mA   |

| ターンオン<br>遅延時間 | TonH1  | OUTH1<br>(5V) | [HSDCR]<HSDGC1>により HSD1 を ON してから、VCCx10%を超えるまでの時間<br>負荷回路 : RL=320Ω, CL=30pF  | 2    | -    | 50   | μs   |

| ターンオフ<br>遅延時間 | ToffH1 | OUTH1<br>(5V) | [HSDCR]<HSDGC1>により HSD1 を OFF してから、VCCx90%を下回るまでの時間<br>負荷回路 : RL=320Ω, CL=30pF | 2    | -    | 50   | μs   |

| 出力リーク電流       | IILH1  | OUTH1<br>(5V) | OUTH1= OFF, OUTH1=0V                                                           | -1   | -    | 1    | μA   |

## 10.13. Low Side ドライバー特性

表 10.13.1 Low Side ドライバー 電気的特性

(特に記載のない限り  $VB=6\sim18V$ ,  $VCC=4.8\sim5.2V$ ,  $VDD=1.45\sim1.55V$ ,  $Tj=-40\sim150^{\circ}C$ )

| 項目              | 記号      | 端子    | 条件                                                                                                     | 規格値  |      |      | Unit     |

|-----------------|---------|-------|--------------------------------------------------------------------------------------------------------|------|------|------|----------|

|                 |         |       |                                                                                                        | Min  | Typ. | Max  |          |

| オン抵抗            | RonLx   | OUTLx | $Id = 115mA$                                                                                           | 0.4  | -    | 6    | $\Omega$ |

| ターンオン<br>遅延時間   | TonLx   | OUTLx | [LSDCR]<LSDGCx>により LSDx を ON してから OUTLx = $0.9 \times VB$ を下回るまでの時間<br>負荷回路 : RL160 $\Omega$ 、CL=30pF  | 1    | -    | 50   | $\mu s$  |

| ターンオフ<br>遅延時間   | ToffLx  | OUTLx | [LSDCR]<LSDGCx>により LSDx を OFF してから OUTLx = $0.1 \times VB$ を上回るまでの時間<br>負荷回路 : RL160 $\Omega$ 、CL=30pF | 1    | -    | 50   | $\mu s$  |

| Active clamp 電圧 | VacLx   | OUTLx | $Id = 115mA$ at off                                                                                    | -    | -    | 35   | V        |

| 出力リーク電流         | IleakLx | OUTLx | OUTLx=0V、または OUTLx=VB                                                                                  | -10  | -    | 10   | $\mu A$  |

| 過電流検出電流         | IdetLx  | OUTLx |                                                                                                        | 210  | -    | 800  | mA       |

| 過電流検出<br>フィルター  | TnfLx   | OUTLx |                                                                                                        | 1.14 | 1.2  | 1.26 | $\mu s$  |

## 10.14. 10bit ADC 特性

表 10.14.1 10bit ADC 電気的特性

(特に記載のない限り  $VB=6\sim18V$ ,  $VCC=4.8\sim5.2V$ ,  $VDD=1.45\sim1.55V$ ,  $Tj=-40\sim150^{\circ}C$ )

| 項目         | 記号   | 端子          | 条件                                              | 規格値   |      |       | Unit    |

|------------|------|-------------|-------------------------------------------------|-------|------|-------|---------|

|            |      |             |                                                 | Min   | Typ. | Max   |         |

| 変換時間       | Tcv  | -           | セトリング + 変換時間、<br>GADCCLK=10MHz                  | -     | 16.4 | -     | $\mu s$ |

| DNL エラー    | DNL  | -           |                                                 | -1.5  | -    | 1.5   | LSB     |

| INL エラー    | INL  | -           |                                                 | -2.5  | -    | 2.5   | LSB     |

| 総合誤差       | Err  | -           |                                                 | -3    | -    | 3     | LSB     |

| 入力分圧比 1    | Rad1 | ADIN0       | ADIN0 端子→バッファー入力分圧比<br>入力レンジ 0.8V~VAREF         | 0.429 | 0.45 | 0.473 | —       |

| 入力分圧比 2    | Rad2 | SWIN0<br>~4 | SWINx(X=0~4)端子→バッファー入力分<br>圧比<br>入力レンジ 0.5~4.0V | 0.762 | 0.8  | 0.840 | —       |

| アンプ誤差(注 1) | Eamp | -           | バッファー入出力誤差                                      | -10   | -    | 10    | mV      |

| 入力クランプ電圧   | Vclp | ADIN0       | <GADCISLx[4:0]>=0x00 の時                         | 3.4   | -    | -     | V       |

注 1: アンプ誤差は ADC\_BUF 欄において「有」の input を選択した場合に加算される誤差となります。

## 10.15. DC 特性

表 10.15.1 DC 電気的特性

(特に記載のない限り  $VB=6\sim18V$ ,  $VCC=4.8\sim5.2V$ ,  $VDD=1.45\sim1.55V$ ,  $Tj=-40\sim150^{\circ}C$ )

| 項目           | 記号  | 端子 | 条件                                                                                                               | 規格値          |      |              | Unit |

|--------------|-----|----|------------------------------------------------------------------------------------------------------------------|--------------|------|--------------|------|

|              |     |    |                                                                                                                  | Min          | Typ. | Max          |      |

| 入力電圧         | VIH | 右記 | GPIO_X(0~13), MD0, MD1                                                                                           | 0.75<br>×VCC | -    | -            | V    |

| 入力電圧         | VIL | 右記 | GPIO_X(0~13), MD0, MD1                                                                                           | -            | -    | 0.25<br>×VCC | V    |

| Pullup 抵抗    | Rpu | 右記 | GPIO_X(0~13)                                                                                                     | 30           | 50   | 100          | KΩ   |

| Pull down 抵抗 | Rpd | 右記 | GPIO_X(0~13), MD0, MD1                                                                                           | 30           | 50   | 100          | KΩ   |

| 出力電圧         | VOH | 右記 | GPIO_X(0~13)<br>負荷条件<br><GPIO_Sx>=00 : -1mA<br><GPIO_Sx>=01 : -2mA<br><GPIO_Sx>=10 : -4mA<br><GPIO_Sx>=11 : -6mA | 0.8<br>×VCC  | -    | -            | V    |

| 出力電圧         | VOL | 右記 | GPIO_X(0~13)<br>負荷条件<br><GPIO_Sx>=00 : 1mA<br><GPIO_Sx>=01 : 2mA<br><GPIO_Sx>=10 : 4mA<br><GPIO_Sx>=11 : 6mA     | -            | -    | 0.2<br>×VCC  | V    |

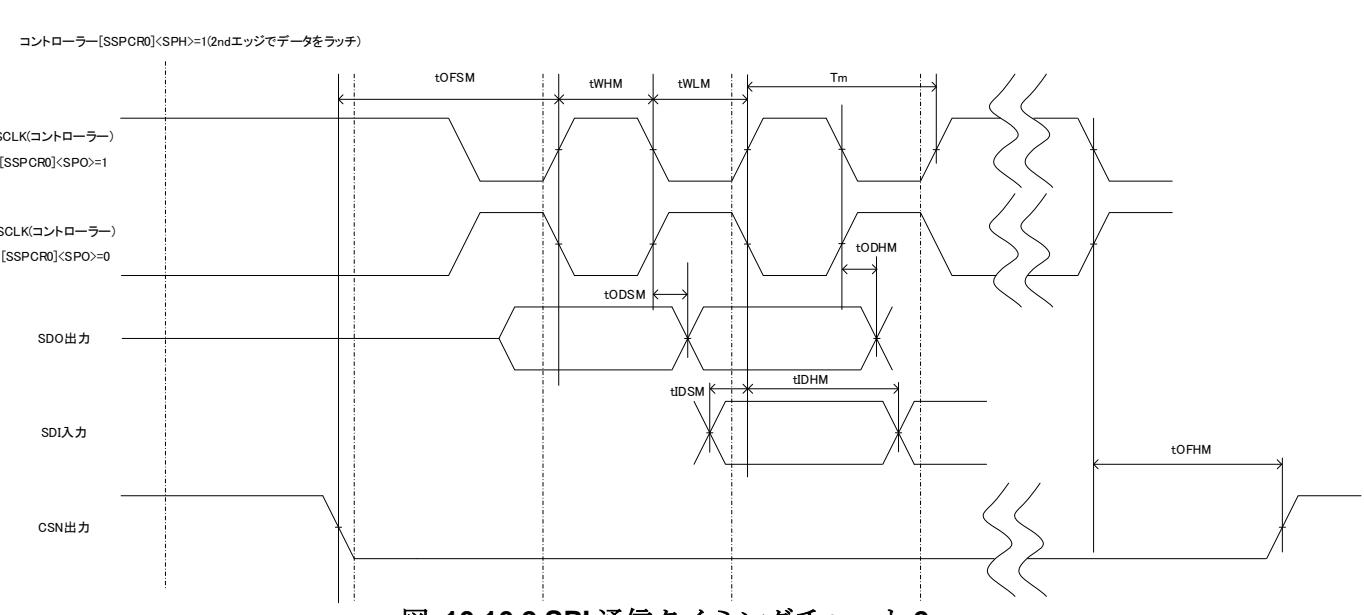

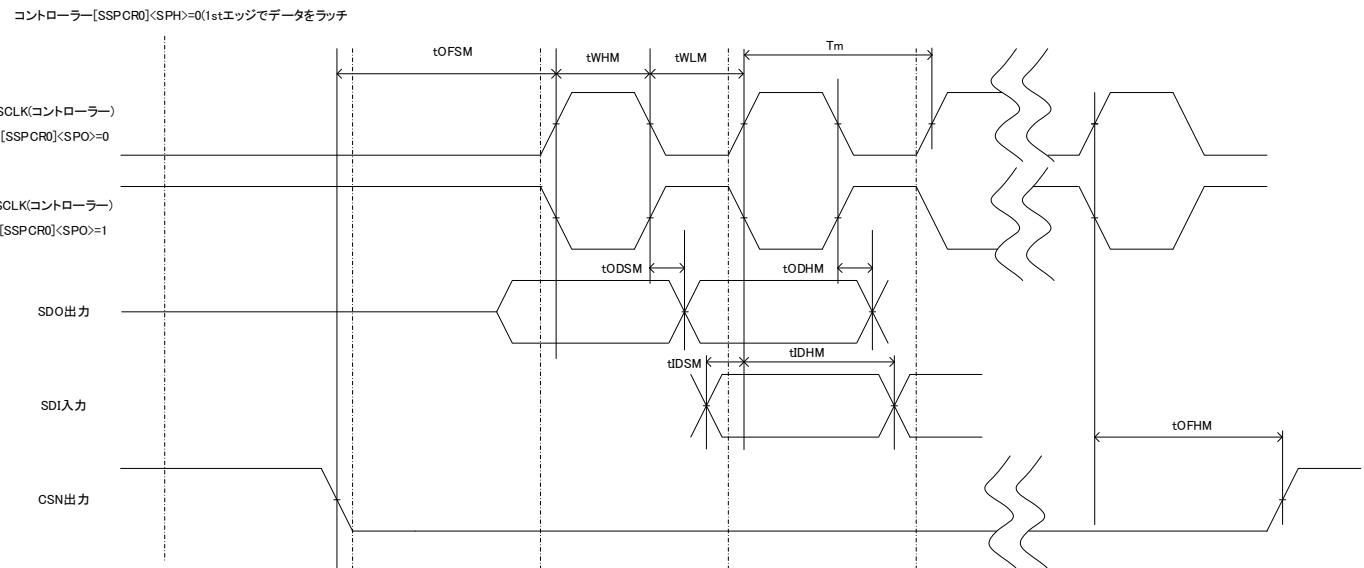

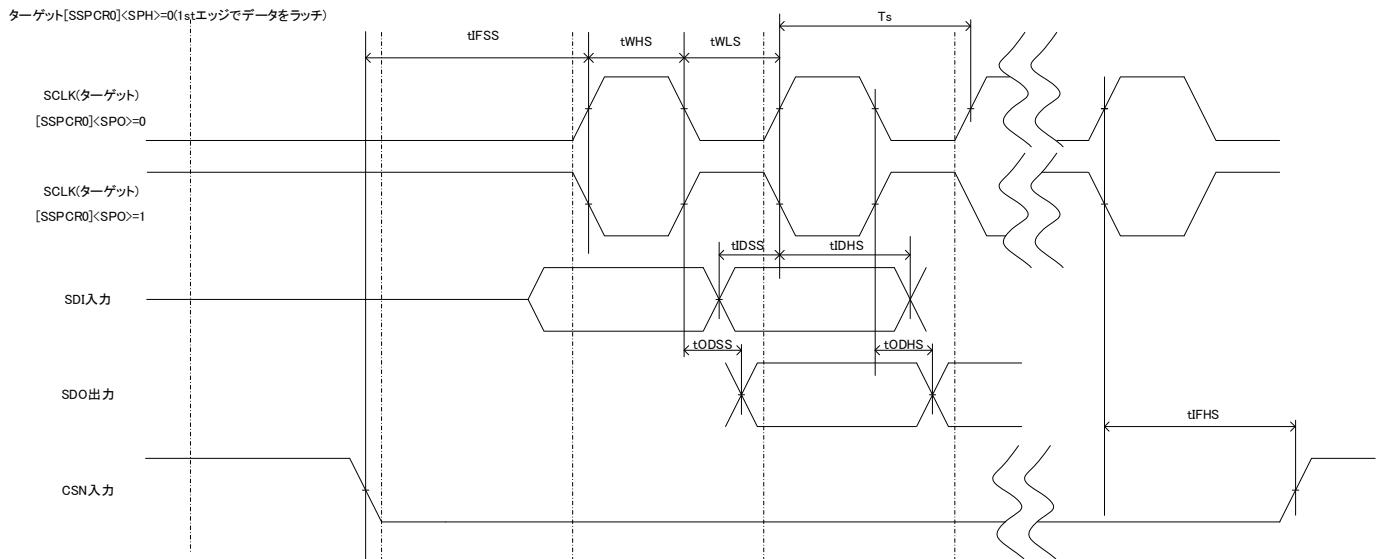

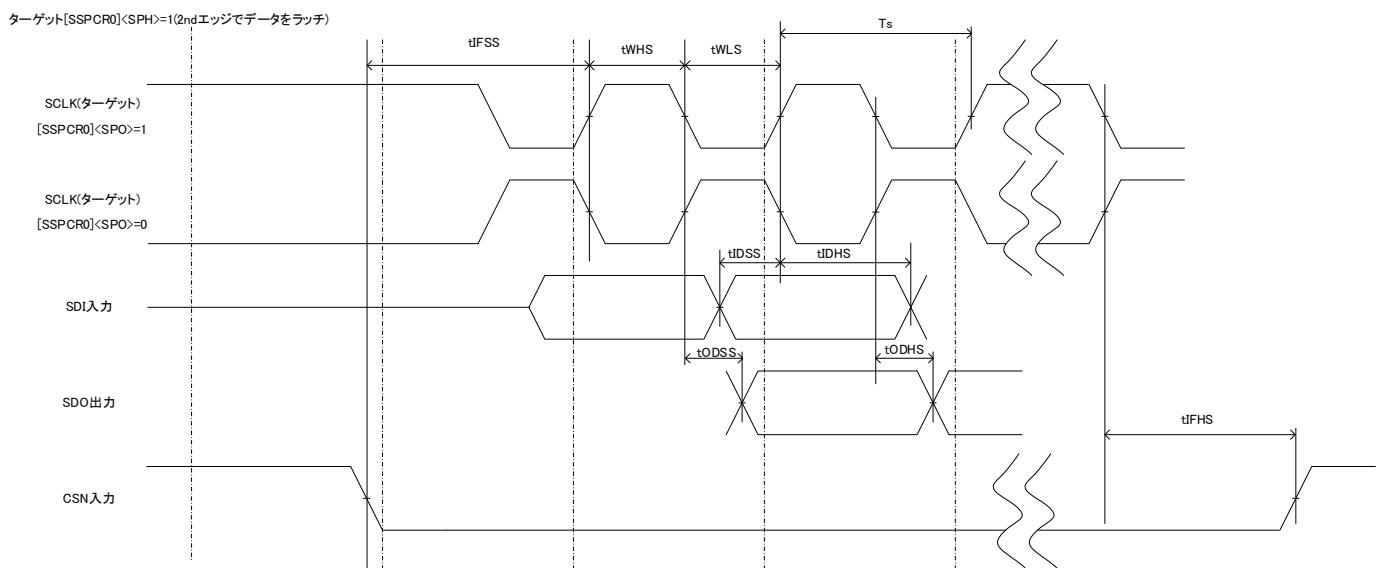

## 10.16. SPI 特性

表 10.16.1 SPI 電気的特性

(特に記載のない限り  $VB=6\sim18V$ ,  $VCC=4.8\sim5.2V$ ,  $VDD=1.45\sim1.55V$ ,  $Tj=-40\sim150^{\circ}C$ )

| 項目                                                  | 記号    | 端子          | 条件 | 規格値                                      |      |           | Unit |

|-----------------------------------------------------|-------|-------------|----|------------------------------------------|------|-----------|------|

|                                                     |       |             |    | Min                                      | Typ. | Max       |      |

| SCLK 周期 (コントローラー)                                   | Tm    | SCLK        |    | T(注 1)<br>m(注 3)<br>$\geq 250\text{ ns}$ | -    | -         | ns   |

| SCLK 周期 (ターゲット)                                     | Ts    |             |    | T(注 1)<br>n(注 2)<br>$\geq 1\mu\text{s}$  | -    | -         | ns   |

| コントローラーモード時 SCLK クロック "Low" レベルパルス幅                 | tWLM  |             |    | 0.4                                      | -    | 0.6       | Tm   |

| コントローラーモード時 SCLK クロック "High" レベルパルス幅                | tWLM  |             |    | 0.4                                      | -    | 0.6       | Tm   |

| ターゲットモード時 SCLK クロック "Low" レベルパルス幅                   | tWLS  |             |    | 0.4                                      | -    | 0.6       | Ts   |

| ターゲットモード時 SCLK クロック "High" レベルパルス幅                  | tWHS  |             |    | 0.4                                      | -    | 0.6       | Ts   |

| コントローラーモード時 SCLK クロック立ち上がり/立ち下がり エッジ → 出力データ有効      | tODSM |             |    | -                                        | -    | 50        | ns   |

| コントローラーモード時 SCLK クロック立ち上がり/立ち下がり エッジ → 出力データ保持      | tODHM |             |    | -20                                      | -    | -         | ns   |

| コントローラーモード時 SCLK クロック立ち上がり/立ち下がり エッジ → 入力データ有効 遅延時間 | tIDSM |             |    | 55                                       | -    | -         | ns   |

| コントローラーモード時 SCLK クロック立ち上がり/立ち下がり エッジ(入力データ保持)       | tIDHM |             |    | 100                                      | -    | -         | ns   |

| SPI コントローラーモード時 CSN 有効 → SCLK クロック立ち上がり/立ち下がり エッジ   | tOFSM | CSN<br>SCLK |    | T(注 1)<br>m(注 3)<br>- 50                 | -    | -         | ns   |

| ターゲットモード時 SCLK クロック立ち上がり/立ち下がり エッジ(出力データ有効遅延時間)     | tODSS | SCLK        |    | -                                        | -    | $3T + 90$ | ns   |

| ターゲットモード時 SCLK クロック立ち上がり/立ち下がり エッジ(出力データ保持)         | tODHS |             |    | $2T$<br>(注 1)                            | -    | -         | ns   |

| ターゲットモード時 SCLK 立ち上がり/立ち下がりエッジ (入力データ有効遅延時間)         | tIDSS |             |    | 10                                       | -    | -         | ns   |

| ターゲットモード時 SCLK クロック立ち上がり/立ち下がり エッジ → 入力データ保持        | tIDHS |             |    | $3T$<br>(注 1)<br>+ 20                    | -    | -         | ns   |

| ターゲットモード時 CSN 有効 → SCLK クロック立ち上がり/立ち下がり エッジ         | tIFSS | CSN<br>SCLK |    | T(注 1)<br>n(注 2)<br>- 20                 | -    | -         | ns   |

| コントローラーモード時 SCLK クロック立ち上がり/立ち下がり エッジ → CSN 入力デアサート  | tOFHM |             |    | T(注 1)<br>m(注 3)<br>- 50                 | -    | -         | ns   |

| ターゲットモード時 SCLK クロック立ち上がり/立ち下がり エッジ → CSN 入力デアサート    | tIFHS |             |    | T(注 1)<br>n(注 2)<br>- 20                 | -    | -         | ns   |

- 注 1: T は SSPCLK 周期 (40MHz 時は 25ns)

注 2: n は SCLK 周期と SSPCLK 周期の比( $n \geq 12$ )

注 3: m は SCLK 周期と SSPCLK 周期の比( $65024 \geq m \geq 2$ )

注 4: SPI は設計保証となります。

図 10.16.3 SPI 通信タイミングチャート 3

図 10.16.4 SPI 通信タイミングチャート 4

## 10.17. UART 特性

表 10.17.1 UART 電気的特性

（特に記載のない限り  $VB=6\sim18V$ ,  $VCC=4.8\sim5.2V$ ,  $VDD=1.45\sim1.55V$ ,  $Tj=-40\sim150^{\circ}C$ ）

| 項目    | 記号 | 端子                      | 条件 | 規格値 |      |     | Unit |

|-------|----|-------------------------|----|-----|------|-----|------|

|       |    |                         |    | Min | Typ. | Max |      |

| 転送レート | -  | UART0_TXD,<br>UART0_RXD |    | -   | -    | 1   | Mbps |

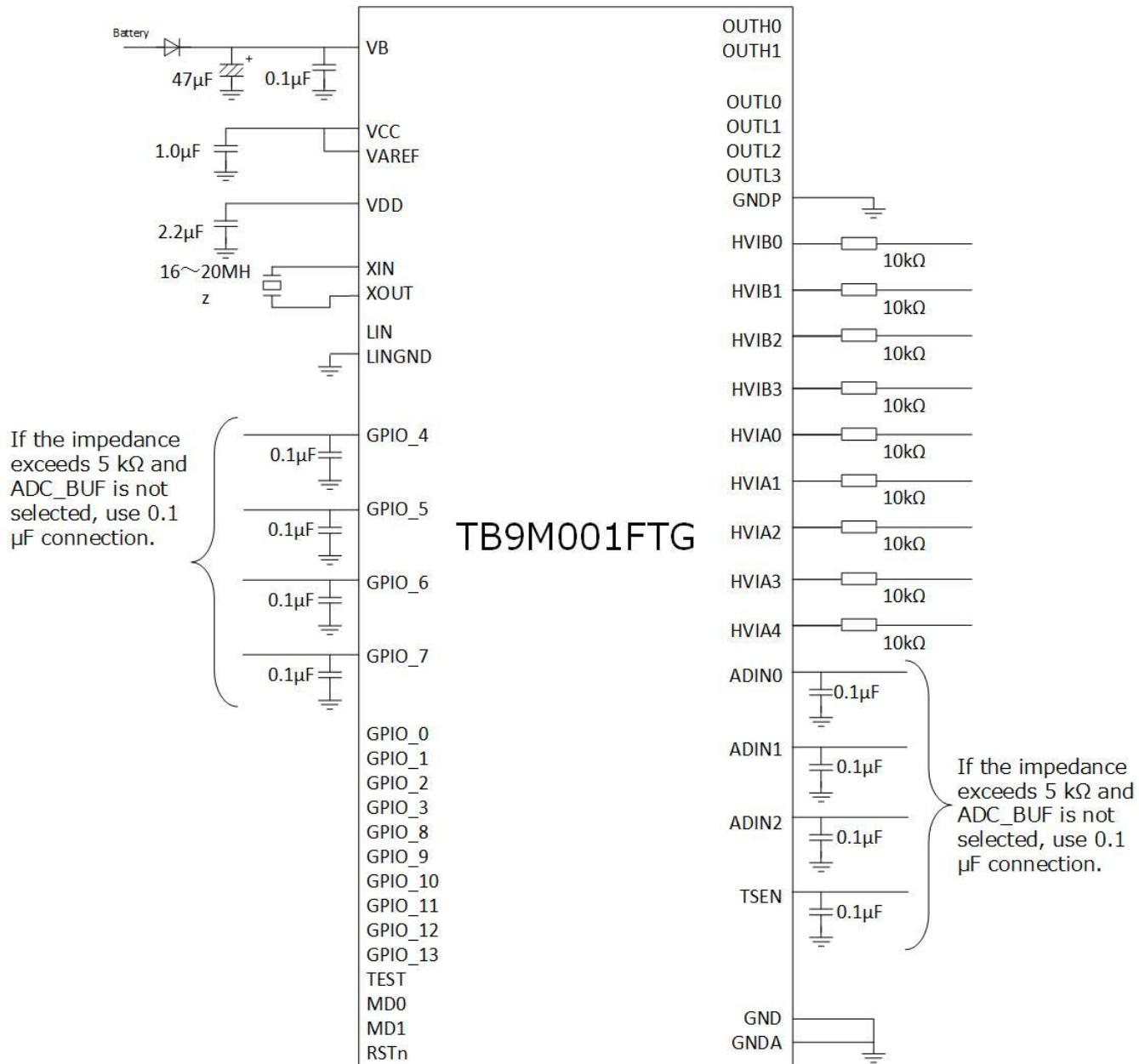

## 11. 應用回路例

図 11.1 應用回路例

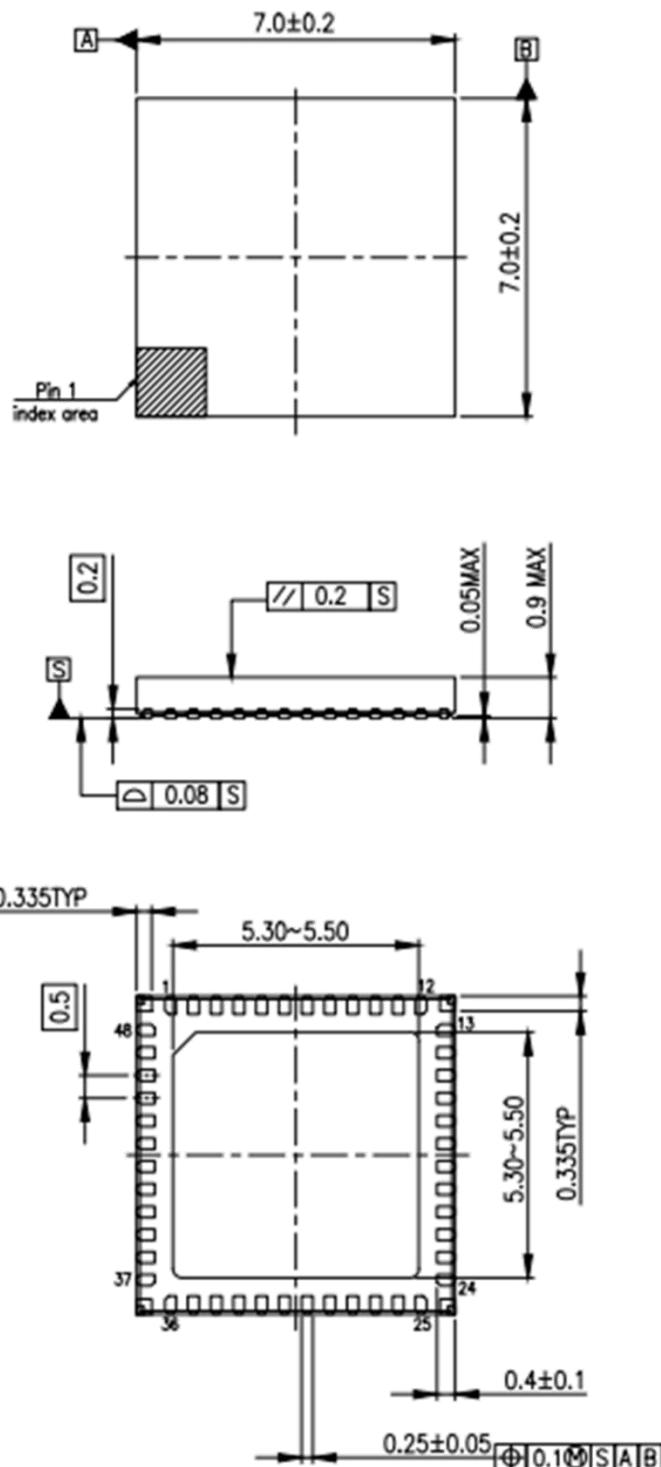

## 12. 外形図

## 12.1. 外形寸法図

Package dimensions

P-VQFN48-0707-0.50-005

"Unit:mm"

質量: 0.13 g (標準)

図 12.1 外形寸法図

**12.2. 現品表示**

品名 : TB9M001FTG

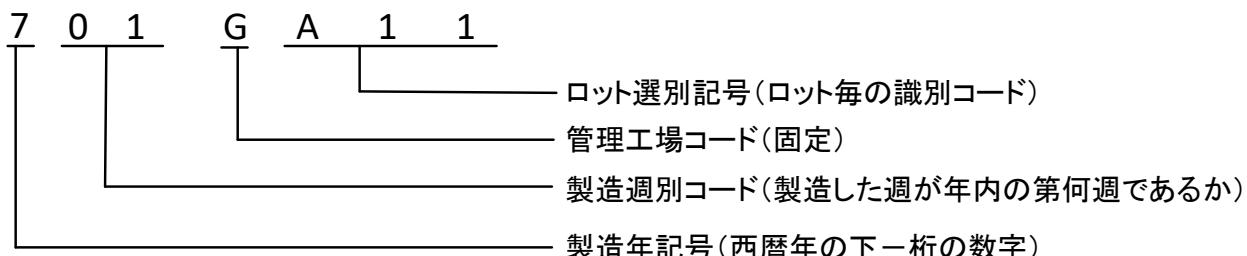

**図 12.2 現品表示****ロットコード内訳(表示例)**

## 13. 使用上のご注意およびお願い事項

### 13.1. 使用上の注意事項

- (1) 絶対最大定格は複数の定格の、どの1つの値も瞬時たりとも超えてはならない規格です。複数の定格のいずれに対しても超えることができません。絶対最大定格を超えると破壊、損傷および劣化の原因となり、破裂・燃焼による傷害を負うことがあります。

- (2) 過電流の発生やICの故障の場合に大電流が流れ続けないように、適切な電源ヒューズを使用してください。ICは絶対最大定格を超えた使い方、誤った配線、および配線や負荷から誘起される異常パルスノイズなどが原因で破壊することあり、この結果、ICに大電流が流れ続けることで、発煙・発火に至ることがあります。破壊における大電流の流入出を想定し、影響を最小限にするため、ヒューズの容量や溶断時間、挿入回路位置などの適切な設定が必要となります。

### 13.2. 使用上の留意点

- (1) 過電流保護回路過電流制限回路

(通常: カレントリミッタ回路)はどのような場合でもICを保護するわけではありません。動作後は、速やかに過電流状態を解除するようお願いします。絶対最大定格を超えた場合など、ご使用方法や状況により、過電流制限回路が正常に動作しなかったり、動作する前にICが破壊したりすることがあります。また、動作後、長時間過電流が流れ続けた場合、ご使用方法や状況によっては、ICが発熱などにより破壊することがあります。

- (2) 熱遮断回路

熱遮断回路(通常: サーマルシャットダウン回路)は、どのような場合でもICを保護するわけではありません。動作後は、速やかに発熱状態を解除するようお願いします。絶対最大定格を超えて使用した場合など、ご使用法や状況により、熱遮断回路が正常に動作しなかったり、動作する前にICが破壊したりすることがあります。

## 製品取り扱い上のお願い

株式会社東芝およびその子会社と関係会社を以下「当社」といいます。

本資料に掲載されているハードウェア、ソフトウェアおよびシステムを以下「本製品」といいます。

- 本製品に関する情報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を得て本資料を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

- 当社は品質、信頼性の向上に努めていますが、半導体・ストレージ製品は一般に誤作動または故障する場合があります。本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウェア・ソフトウェア・システムに必要な安全設計を行うことをお願いします。なお、設計および使用に際しては、本製品に関する最新の情報（本資料、仕様書、データシート、アプリケーションノート、半導体信頼性ハンドブックなど）および本製品が使用される機器の取扱説明書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

- 本製品は、特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な財産損害を引き起こす恐れ、あるいは社会に深刻な影響を及ぼす恐れのある機器（以下“特定用途”といいます）に使用されることを意図されていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇宙機器、医療機器（ヘルスケア除く）、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連機器、昇降機器、発電関連機器などが含まれますが、本資料に個別に記載する用途は除きます。特定用途に使用された場合には、当社は一切の責任を負いません。なお、詳細は当社営業窓口まで、または当社 Web サイトのお問い合わせフォームからお問い合わせください。

- 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

- 本製品を、国内外の法令、規則および命令により、製造、使用、販売を禁止されている製品に使用することはできません。

- 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社および第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に関して、明示的にも黙示的にも一切の保証（機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。）をしておりません。

- 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替および外国貿易法」、「米国輸出管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず当社営業窓口までお問い合わせください。本製品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査の上、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は一切の責任を負いかねます。