## Application Processor Lite ApP Lite

# **TZ1000 Series**

# **Reference Manual**

# **MCU Overview**

**Revision 1.3**

2018-01

## **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

## Table of Contents

| Preface                                  | 5  |

|------------------------------------------|----|

| Intended Audience                        | 5  |

| Conventions in this document             | 5  |

| 1. Summary                               | 6  |

| 1.1. Features                            | 6  |

| 2. Description                           | 7  |

| 3. Features                              | 8  |

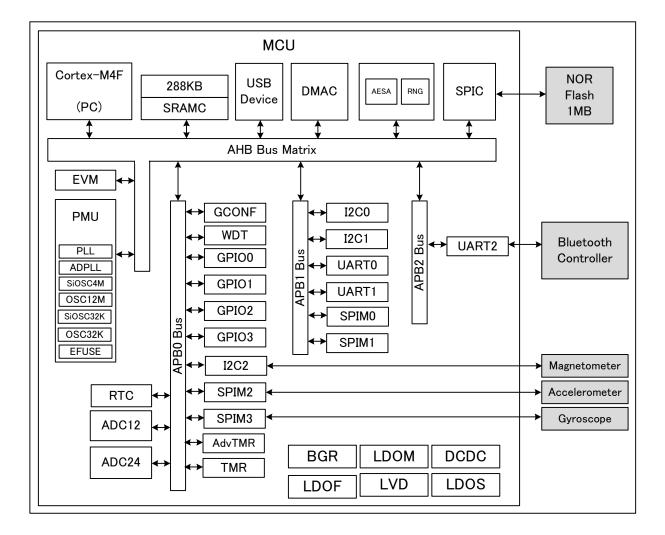

| 3.1. Block Diagram                       | 8  |

| 3.2. MCU Summary                         | 9  |

| 3.2.1. CPU Core                          | 9  |

| 3.2.2. Memories                          |    |

| 3.2.3. System                            |    |

| 3.2.4. Peripherals                       |    |

| 4. Boot Mode                             |    |

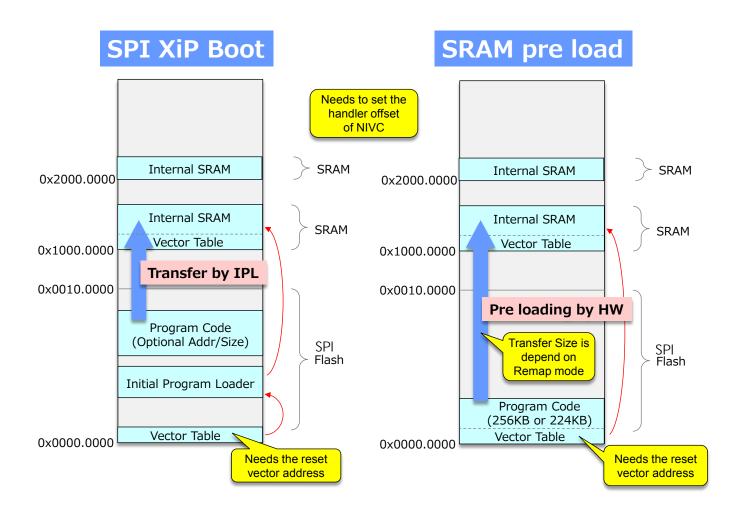

| 4.1. SRAM pre load setting               | 15 |

| 4.2. Address Remap setting               |    |

| 4.3. SPI Flash Access Mode setting       | 16 |

| 4.4. SPI Flash Power Supply Mode setting | 16 |

| 4.5. SPI Flash Direct Access Mode Setup  | 17 |

| 4.6. SPI Flash Erase Mode                | 17 |

| 5. Address Map                           | 18 |

| 5.1. Remap                               | 18 |

| 5.2. Address Mapping                     | 18 |

| 6. Revision History                      | 21 |

| RESTRICTIONS ON PRODUCT USE              | 22 |

|                                          |    |

## List of Figures

| Figure 3.1 Block Diagram        |  |

|---------------------------------|--|

| Figure 4.1 SRAM pre load images |  |

| Figure 5.1 Address Map (1)      |  |

| Figure 5.2 Address Map (2)      |  |

## List of Tables

| Table 4.1 | Boot Mode           | 13 |

|-----------|---------------------|----|

| Table 4.2 | Boot Mode Setting   | 14 |

|           | Remap Table         |    |

| Table 5.2 | Address Map regions | 18 |

|           | Revision History    |    |

\* Arm, AMBA, Cortex, and Thumb are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. CoreSight is a trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved.

\* All other trademarks and trade names are properties of their respective owners.

4 / 22

#### Preface

This document provides the specification for the MCU Overview designed for the TZ1000 Series.

#### **Intended Audience**

This document is intended for the following users.

Driver software developers.

System designers

#### Conventions in this document

- The numerical values are expressed as follows. Hexadecimal number: 0xABC

Decimal number: 123 or 0d123 - Only when it needs to be explicitly shown that they are decimal numbers. Binary number: 0b111 - It is possible to omit the "0b" when the number of bit can be distinctly understood from a sentence.

- "\_N" is added to the end of signal names to indicate low active signals.

- It is called "assert" that a signal moves to its active level, "deassert" to its inactive level.

- When two or more signal names are referred, they are described like as [3:0]. [3:0] shows four signal names 3, 2, 1, and 0 together.

- The characters surrounded by [] defines the register. Example: [ABCD]

- "n" substitutes suffix number of two or more same kind of registers, fields, and bit names. Example: [XYZ1], [XYZ2], and [XYZ3] to [XYZn]

- The bit range of a register is written like as [3:0]. Example: Bit[3:0] expresses the range of bits 3 to 0.

- The configuration value of a register is expressed by either the hexadecimal number or the binary number. Example: [ABCD].EFG = 0x01 (hexadecimal), [XYZn].VW = 1 (binary)

- Word and Byte represent the following bit length.

| Byte:        | 8-bit  |

|--------------|--------|

| Half word:   | 16-bit |

| Word:        | 32-bit |

| Double word: | 64-bit |

- Unless otherwise specified, register access supports only word access.

- The register defined as reserved must not be rewritten. Moreover, don't use the read value.

- Properties of each bit in a register are expressed as follows.

- R: Read only

- W: Write only

W1C: Write 1 Clear - The corresponding bit is cleared (=0) when "1" is written to this bit.

- W1S: Write 1 Set The corresponding bit is set (=1) when "1" is written to this bit.

- R/W: Read and Write are possible.

- R/W0C: Read/Write 0 Clear

- R/W1C: Read/Write 1 Clear

- R/W1S: Read/Write 1 Set

RS/WC: Read Set/Write Clear - Set after read operation, cleared after write operation.

- The value read from the bit having default value of "—" is unknown.

- When a register containing both of writable bits and read-only bits is written, read-only bits should be written with their default value. In the cases that default is "—," follow the definition of each register.

- Reserved bits of the Write-only register should be written with their default value. In the cases that default is "—," follow the definition of each register.

## 1. Summary

The MCU is a family of microcontrollers which adopts a high performance 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor.

The MCU incorporates 288 KB SRAM, and all functions which are necessary to compose a one-chip wearable device.

The MCU supports a variety of peripheral interfaces such as the USB Device mode, UART, SPI, and I<sup>2</sup>C. These interfaces allow the MCU to easily connected to the MEMS sensors with digital interfaces, such as atmospheric pressure sensors and moisture sensors. The MCU also incorporates a 12-bit ADC and a 24-bit  $\Delta\Sigma$ ADC. Without any special analog front-end devices, this 24-bit  $\Delta\Sigma$ ADC allows the MCU to be directly connected to a photo diode for pulse sensing, a photoelectric sensor and a wide variety of sensors, such as a gas sensor. This contributes to reducing the total system cost.

## 1.1. Features

- CPU Core

- Arm Cortex-M4 with FPU processor running at up to 48 MHz

- Floating Point Unit (FPU)

- Memory Protection Unit (MPU)

- Arm<sup>®</sup> Thumb<sup>®</sup>-2 instruction set

- Memories

- 288 KB embedded SRAM

- System Functions

- Embedded linear and switching voltage regulator for single power supply operation

- Brown-out Detectors

- Crystal oscillators: 12 MHz for CPU and USB, 32.768 kHz for RTC

- High precision 4 MHz factory trimmed internal RC oscillator

- Low power 32 kHz internal RC oscillator

- Peripherals

- USB 2.0 Device: 12 Mbps, 1 port 4 bidirectional endpoints

- Two Master/Slave I<sup>2</sup>C interface up to 400 kbps

- Two UART

- Two SPI Master with chip selects signals

- One 4-channel ADC with 12 bits resolution

- One 3-channel Delta-Sigma ADC with 24 bits resolution

- Advanced Encryption System (AES) Engine with 128/192/256-bit key length

- True random number generator

- 24 general purpose IOs (GPIO)

- Real-time clock which supports calender mode

- Watchdog timer

- Four 16-bit Advanced Timer/Counter channels with capture, compare and PWM mode

- Two 32-bit Timer/Counter channels

- One 8 channels DMA controller

- Single Power Supply

- Voltage range: 2.1 to 3.6 V or 1.71 to 1.89 V.

## 2. Description

The MCU adopts a high performance 32-bit Arm Cortex-M4 with FPU processor. The Cortex-M4 with FPU processor consists of a floating point processor unit, a memory protection unit, and a flexible interrupt controller. It supports many kinds of real time OS.

The MCU can select the most suitable power supply voltage and circuit to its operating frequency. Users can achieve lower power consumption in their applications to use the power saving mode.

The MCU includes a low power and as large capacity as 288 KB of SRAM which is used to store program codes and data. The MCU can realize an activity meter and other devices without any other components.

An ASE engine and a random number generator are incorporated for a security function. The AES complies with FIPS (Federal Information Processing Standard) Publication 197, Advanced Encryption Standard. It can select a key length among 128 bits, 192 bits, and 256 bits, and executes the encryption and decryption without any processes of the processor.

The random number generator has passed the random number test of NIST SP800-22 (National Institute of Standards and Technology Special Publication 800-22), and it can be used for the bases of keys and others.

The 8 channel DMA controllers perform the data transfer between the SRAM and the peripheral such as the UART or between the SRAMs without any processes of the processor. The data transfer engine (SRAMC) in the SRAM controller enables the data transfer between the SRAMs without passing the data buses.

The MCU also incorporates a 12-bit ADC and a 24-bit  $\Delta\Sigma$ ADC. Without any special analog front-end devices, this 24-bit  $\Delta\Sigma$ ADC allows the MCU to be directly connected to a photo diode for pulse sensing, photoelectric sensors with small output voltage like for ECG measure application and a wide variety of sensors, such as a gas sensor. This contributes to reducing the total system cost.

## 3. Features

## 3.1. Block Diagram

Figure 3.1 Block Diagram

### 3.2. MCU Summary

#### 3.2.1. CPU Core

Arm Cortex-M4 with FPU processor Instruction set Architecture: Armv7E-M architecture Single Precision floating point unit with IEEE 754 compliant Supports SIMD and MAC DSP extension instructions Tumb2 instruction set Memory protection unit Integrated bit manipulation instructions & bit banding Operating Frequency: selectable from 32 kHz to 48 MHz Debug function: Arm® CoreSight<sup>TM</sup> component V7 debug architecture with JTAG debug port

#### 3.2.2. Memories

| Memory size: | 288  KB |

|--------------|---------|

|              |         |

#### 3.2.3. System

Embedded voltage linear and switching regulator (1.2 V/1.1 V/1.0 V/0.9 V) Embedded LDO (1.7 V) High precision 4 MHz internal Silicon oscillator Low power 32 kHz internal Silicon oscillator Analog PLL up to 48 MHz for whole system and USB with reference clock 12 MHz Digital PLL up to 48 MHz with reference clock 32 kHz

AES Accelerator (AESA)

AES accelerator engine with 128, 192, 256-bit key length Compliant with FIPS 197 (Advanced Encryption Standard) Encryption/Decryption with dedicated DMA engine Supported 3 block cipher modes of operation (ECB, CBC, CTR)

#### True Random Number Generator (RNG)

Generates 32-bit true random number NIST SP800-22 (NIST special publication 800-22) passed

#### Real Time Clock (RTC)

Clock (hour, minute and second) Calendar (month, week, date and leap year) Selectable 12(am/pm) and 24 hour display Time adjustment + or – 30 seconds Alarm interrupt Periodic interrupt BCD format for calendar data

#### Watch Dog Timer (WDT)

32-bit Timer with interrupt and reset when timeout

#### DMA Controller (SDMAC)

8 Channels

Each channel has source and destination pair Programmable source and destination addresses Addressing mode can be increment, decrement or no change Handshaking interfaces for source and destination peripherals UART, I<sup>2</sup>C, SPI, ADC12, ADC24

#### Timer (TMR)

32-bit down Counter Selectable 32-bit/16-bit count mode Two Channels Operation Mode One shot timer mode Periodic timer mode Free running timer mode Pre-scale unit generating timer clock  $(\times 1, \times 1/16, \times 1/256)$

#### Advanced Timer (AdvTMR)

16-bit down Counter

Selectable 16-bit/8-bit count mode

Input capture function for each channel

Output compare function for each channel

Four Channels

#### Operation Mode

One shot timer mode

Periodic timer mode

Free running timer mode

Pre-scale unit generating timer clock

(×1,×1/2, ×1/4, ×1/8, ×1/32, ×1/128, ×1/512, ×1/1024)

Timing selection of input capture

(Pulse, Rising edge, Falling edge, both edges)

PWM (Pulse Width Modulation) operation that uses output compares function

#### 3.2.4. Peripherals

SPI for general purpose (SPIM) Four Channels SPI Clock up to 6 MHz FIFO Depth Ch0, Ch1: RX FIFO 8, TX FIFO 8 Ch2, Ch3: RX FIFO 8, TX FIFO 2

SPI for NOR flash connection (SPIC) Quad SPI Clock up to 48 MHz Application eXecute-In-Place (XIP) Hardware image transferring feature to internal SRAM Programmable source and destination address

#### UART (UART)

Three Channels FIFO Depth RX FIFO 12, TX FIFO 8 Programmable baud rate generator Input reference clock; up to 16 MHz Data rate up to 1 Mbps Division of reference clock by (1×16) to (65535×16) Hardware flow control Fully-programmable serial interface characteristics Data can be 5, 6, 7, or 8 bits Even, odd, stick, or no-parity bit generation and detection 1 or 2 stop bit generation

#### $I^2C$

Three Channels Transfer mode; Standard mode (100 kbps), Fast mode (400 kbps) Master or slave I<sup>2</sup>C operation 7-bit or 10-bit addressing 7-bit combined format transfers Bulk transfer mode FIFO Depth RX FIFO 6, TX FIFO 6

# TOSHIBA

#### USB

Compliant with Universal Serial Bus Specification revision 2.0 Supports Full Speed (12 Mbps) One port, four endpoints Endpoint 1-3 can be configured as interrupt/bulk transfer mode Internal DMA Controller

#### GPIO

32 Pins Individually programmable as input or output Interrupt generation capability from a transition or level condition Pull-up/pull-down resistors configurable

12-bit Analog to Digital Convertor (ADC12)

Successive approximation type 12 bits resolution Conversion time: 17 cycles at 1 to 12 MHz Four channel analog inputs Selectable conversion mode (Single/One-time scan/Cyclic scan) FIFO Depth 8 for each channel

24-bit Analog to Digital Convertor (ADC24)

Delta-Sigma type up to 24 bits resolution Three channel differential analog inputs Conversion time: 4130 cycles at 24 bits resolution Selectable conversion mode (Single/One-time scan/Cyclic scan) FIFO Depth 16 for each channel Configurable analog front end

## 4. Boot Mode

The MCU supports the several boot modes to switch the boot function. It is possible to select the boot mode by setting the state of the external pins, before de-asserting reset.

The pins of the boot mode is exclusively for an input. The Boot mode can be set by fixing to H (MCU\_VDD33) or L (VSS) externally. In addition, these pins cannot be changed during operation. The value needs to be set before de-asserting reset.

The pin name for boot modes and its function are described below. Refer to "Table 4.1 Boot Mode."

| PIN NAME      | FUNCTION                                                                                                                                                                                                          |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | SRAM pre load setting<br>H/W pre load from SPI Flash to SRAM is selected at the time of boot.                                                                                                                     |

| MCU_BOOTMODE0 | 0: SPI (XiP) Boot Mode<br>Pre load is not performed from SPI Flash to SRAM.<br>1: SRAM pre load & SPI (XiP) Boot Mode<br>Pre load is performed from SPI Flash to SRAM.                                            |

| MCU_BOOTMODE1 | Address Remap setting<br>The size of Code area and SRAM area is selected. Regarding the address<br>of Code and SRAM area, refer to "5. Address Map."<br>0: Remap0 Mode<br>Code area = 256 KB, SRAM area = 32 KB   |

|               | 1: Remap1 Mode<br>Code area = 224 KB, SRAM area = 64 KB                                                                                                                                                           |

| MCU_BOOTMODE2 | SPI Flash Access Boot Mode setting<br>The access mode to SPI Flash at the time of boot and the return from<br>RTC/STOP mode is selected.                                                                          |

|               | 0: Single Access Boot Mode<br>1: Quad Access Boot Mode                                                                                                                                                            |

| MCU BOOTMODE3 | SPI Flash Power Supply Mode setting<br>The power supply source for SPI Flash is selected                                                                                                                          |

|               | 0: Internal LDO mode<br>1: External Power Supply mode                                                                                                                                                             |

|               | SPI Flash Direct Access mode / Erase mode setting<br>It is possible to write the program code to the SPI flash memory directly via<br>the other external pins by the FLASH Writer, or erase the SPI flash memory. |

| MCU_BOOTMODE4 | 0: Normal Boot Mode<br>1: SPI Flash Direct Access Mode / Erase Mode<br>When using these modes, MCU_BOOTMODE[2:0] signals are necessary to<br>be set to 0b000 or 0b111.                                            |

| MCU_BOOTMODE         Description |   | MCU_I                      | воот | MODE | E | Description                               |

|----------------------------------|---|----------------------------|------|------|---|-------------------------------------------|

|                                  |   | Description                |      |      |   |                                           |

| Normal Mode                      | L | *                          | *    | *    | L | SPI (XiP) Boot Mode                       |

|                                  | L | *                          | *    | *    | Н | SRAM pre load & SPI (XiP) Boot Mode       |

|                                  | L | *                          | *    | L    | * | Remap0 Mode (Code = 256 KB, SRAM = 32 KB) |

|                                  | L | *                          | *    | Н    | * | Remap1 Mode (Code = 224 KB, SRAM = 64 KB) |

|                                  | L | *                          | L    | *    | * | SPI Flash Single Access Boot Mode         |

|                                  | L | *                          | Н    | *    | * | SPI Flash Quad Access Boot Mode           |

|                                  | L | L                          | *    | *    | * | Internal LDO mode                         |

|                                  | * | External Power Supply mode |      |      |   |                                           |

| SPI Flash writing<br>Mode        | Н | *                          | L    | L    | L | SPI Flash Direct Access Mode              |

| SPI Flash Erase<br>Mode          | Н | *                          | Н    | Н    | Н | SPI Flash Erase Mode                      |

Table 4.2 Boot Mode Setting

Note: When using MCU\_BOOTMODE[3-0] to select the normal boot mode, MCU\_BOOTMODE4 is necessary to be tied to 0.

## 4.1. SRAM pre load setting

User can select the SPI XiP Boot mode or SRAM pre load mode.

- SPI (XiP) Boot Mode

- The preload from SRAM does not perform but it boots directly from SPI Flash.

- Transmitting the contents of SPI Flash to SRAM needs to perform by code in SPI Flash.

- The code on Flash needs to define addresses, such as the SPI Flash code area which is a transmitting agency, SRAM area used as a transmission place, and handler.

- SRAM pre load & SPI (XiP) Boot Mode

- According to the setting of MCU\_BOOTMODE1 port (Remap), the code size of 256 KB from address 0 in SPI Flash or 224 KB are transmitted by H/W. The transmission place address is written to the code area of a head 0x1000.0000. For details, refer to "5. Address Map."

- MCU BOOTMODE1 = L: 256 KB (Remap0 code area)

- MCU BOOTMODE1 = H : 224 KB (Remap1 code area)

- Reset of  $\overline{CPU}$  is released by H/W after completing the transmission to SRAM from SPI Flash.

- CPU starts code fetch (XiP) from SPI Flash.

- The address 0x4 of SPI Flash needs to be set the reset vector address to jump to the SRAM.

- CPU fetches a code from the above-mentioned SRAM address, and continues a boot process.

- On the SRAM code, the place of handler needs to redefine to SRAM.

## 4.2. Address Remap setting

Two kinds of address maps which are Code/SRAM different area can be selected. This two kinds of address map is switched by MCU\_BOOTMODE1 port.

Refer to "5. Address Map" for each address map of Remap 0/1.

- Remap0 Mode

- Code area: 256 KB

- SRAM area: 32 KB

- Remap1 Mode

- Code area: 224 KB

- SRAM area: 64 KB

## 4.3. SPI Flash Access Mode setting

This mode determines the access mode to SPI Flash. User can select the Single mode or Quad mode.

- Single Access Boot Mode

- It is used to access the SPI flash memory with single access mode.

- Also when it changes to Quad Access Mode by S/W after boot, it operates by Single Access Mode at the time of reset and the return from RTC/STOP mode.

- In addition, while operating with XiP to fetch the code from SPI Flash, A change in Quad mode by S/W is not permitted. For details, refer to "SPIC data sheet."

- Quad Access Boot Mode

- It is used to access the SPI flash memory with quad access mode.

- In order to use Quad Access Mode, Quad Enable of SPI Flash is needed to set effectively beforehand.

- In JTAG ICE or SPI Flash direct access mode, when a code is written in SPI Flash, since Quad Enable bit of SPI Flash is 0 (Single) at the time of initial shipment, Quad Enable bit is needed to set 1 after finishing writing the code.

## 4.4. SPI Flash Power Supply Mode setting

This mode determines the power supply source for SPI Flash. User can select the internal LDO or external power supply.

- Internal LDO mode

- Internal LDO is selected for SPI Flash power supply.

- This LDO is dedicated for SPI Flash and supply voltage is tuned to 1.7 V.

- External Power Supply mode

- External power supply is selected for SPI Flash power supply.

- Power switch located between MCU\_VDD33 pin and internal power line for SPI Flash is enabled so that the power can be supplied from external power source.

- Note: The supply voltage specifications are not identical for these two power supply mode. Please refer Electrical Specification section for details.

TOSHIBA

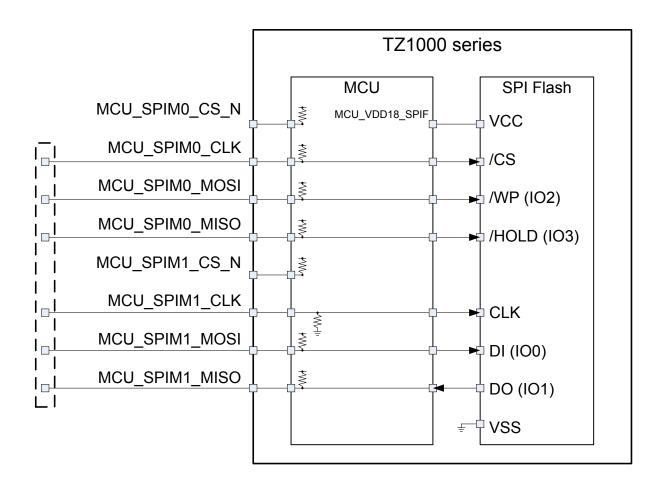

## 4.5. SPI Flash Direct Access Mode Setup

Using an external SPI Flash writer, it is used when writing a code in SPI Flash in a package.

| External pins  | <b>Connection with SPI Flash</b> | Description                                |

|----------------|----------------------------------|--------------------------------------------|

| MCU_SPIM0_CS_N | —                                | pull-up                                    |

| MCU_SPIM0_CLK  | /CS                              | _                                          |

| MCU_SPIM0_MOSI | /WP (IO2)                        | If not using, it is necessary to fix to H. |

| MCU_SPIM0_MISO | /HOLD (IO3)                      | If not using, it is necessary to fix to H. |

| MCU_SPIM1_CS_N | —                                | pull-up                                    |

| MCU_SPIM1_CLK  | CLK                              | _                                          |

| MCU_SPIM1_MOSI | DI (IO0)                         | _                                          |

| MCU_SPIM1_MISO | DO (IO1)                         | _                                          |

Note 1: It is possible to use only Single Access Mode in this flash direct access mode. Dual and Quad Access does not support in this mode.

Note 2: In this mode, MCU\_SPIM0\_CS\_N and MCU\_SPIM1\_CS\_N pin are pull-up, in order to avoid the SPI Slave Device of SPIM0/SPIM1 on Board at the time of Flash writing.

Note 3: MCU\_SPIM0\_\*, MCU\_SPIM1\_\* signals are driven by MCU\_VDD33.

## 4.6. SPI Flash Erase Mode

This mode is used to erase the SPI Flash. In order to erase the SPI Flash, set up MCU\_BOOTMODE[4]/[2:0], and then de-assert reset. 14 seconds after de-assert reset, erase operation is complete.

## 5. Address Map

This chapter explains the address map of the MCU section.

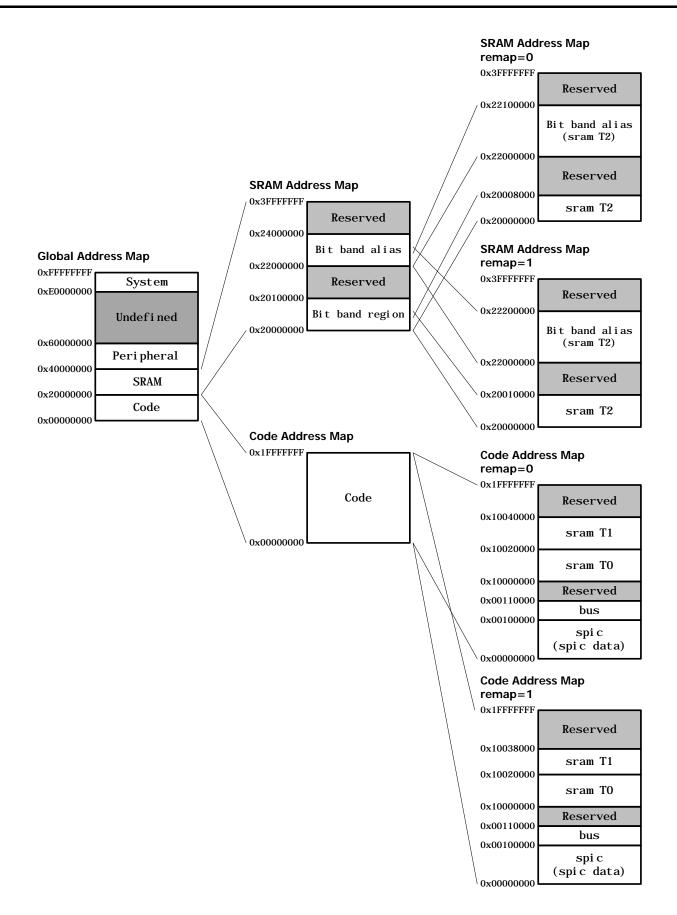

## 5.1. Remap

The address map of SRAMs can be remapped by external pin (MCU\_BOOTMODE1). This pin cannot be changed during operation. It is necessary to fix the level before deasserting reset. Refer to the chapter 4 for the detail of Boot Mode.

The difference of the address map by remapping is as in the following Table 5.1. Any addresses other than SRAM are the same.

| Region  | remap 0                           | remap 1                           |

|---------|-----------------------------------|-----------------------------------|

| —       | MCU_BOOTMODE1 = 0                 | MCU_BOOTMODE1 = 1                 |

| SRAM T0 | 128 KB (0x10000000 to 0x1001FFFF) | 128 KB (0x10000000 to 0x1001FFFF) |

| SRAM T1 | 128 KB (0x10020000 to 0x1003FFFF) | 96 KB (0x10020000 to 0x10037FFF)  |

| SRAM T2 | 32 KB (0x20000000 to 0x20007FFF)  | 64 KB (0x20000000 to 0x2000FFFF)  |

| Table 5.1 | Poman Tablo |

|-----------|-------------|

| Table 5.1 | Remap Table |

## 5.2. Address Mapping

Figure 5.1 Address Map (1), Figure 5.2 Address Map (2) show the address map of MCU chip which has embedded 288 KB SRAM memories, a lot of peripheral blocks and SPI for flash in package. Refer to Table 5.2 for each region of address map.

| Address Map                     | Region                                                                                                                                                     |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Code                            | Instruction fetches are performed over the ICode bus. Data accesses are performe over the DCode bus.                                                       |  |

| SRAM<br>(Bit band region)       | Instruction fetches and data accesses are performed over the system bus.                                                                                   |  |

| SRAM<br>(Bit band alias)        | Alias region. Data accesses are aliases. Instruction accesses are not aliases.                                                                             |  |

| Peripheral<br>(Bit band region) | Instruction fetches and data accesses are performed over the system bus.                                                                                   |  |

| Peripheral<br>(Bit band region) | Alias region. Data accesses are aliases. Instruction accesses are not aliases.                                                                             |  |

| Undefined                       | Undefined area.                                                                                                                                            |  |

| System                          | System segment for vendor system peripherals. This memory region is XN, and so instruction fetches are prohibited. An MPU, if present, cannot change this. |  |

| Table 5.2 | Address | Map regions |

|-----------|---------|-------------|

|-----------|---------|-------------|

## TOSHIBA

Figure 5.1 Address Map (1)

**Global Address Map**

System

0xFFFFFFF

0xE0000000

| Peripheral | Address | Мар |

|------------|---------|-----|

|------------|---------|-----|

| renpiiciai    | Addiess Map                    |

|---------------|--------------------------------|

| 0x5FFFFFFF    | Reserved                       |

| 0x44000000    | Resei veu                      |

| //            | Bit band alias<br>(peripheral) |

| // 0x42000000 | (per i pilei ai )              |

| //            | Reserved                       |

| 0x400C0000    | usb2fs                         |

| 0x40080000    | Reserved                       |

| 0x40071000    |                                |

| 0x40070000    | uart2                          |

| 0x40066000    | Reserved                       |

| 0x40065000    | uart1                          |

| 0x40064000    | uart0                          |

| 0x40063000    | i 2c1                          |

| 0x40062000    | i 2c0<br>spi m1                |

| 0x40061000    | spim0                          |

| 0x40060000    | -                              |

| 0x4004F000    | Reserved                       |

| 0x4004E000    | gpi o3                         |

| 0x4004D000    | gpi o2                         |

| 0x4004C000    | gpi o1                         |

| 0x4004B000    | gpi o0                         |

| 0x4004A000    | gconf<br>adcc24                |

| 0x40049000    | adcc12                         |

| 0x40048000    | spi m3                         |

| 0x40047000    | spim2                          |

| 0x40046000    | Reserved                       |

| 0x40045000    | i 2c2                          |

| 0x40044000    | wdt                            |

| 0x40043000    | tmr                            |

| 0x40042000    | advtmr                         |

| 0x40041000    | rtclv                          |

| 0x40040000    | Reserved                       |

| 0x40024000    | evm                            |

| 0x40023000    | sramc                          |

| 0x40022000    | rng                            |

| 0x40021000    | aesa                           |

| 0x40020000    | Reserved                       |

| 0x40006000    | sdmac                          |

| 0x40005000    | spi c                          |

| 0x40004000    | pmul v                         |

| 0x40000000    | T                              |

|               |                                |

| System Address Map | C |

|--------------------|---|

|--------------------|---|

| 0xFFFFFFFF               |              |

|--------------------------|--------------|

| 0xE0100000               | Reserved     |

| 0xE0100000               | ROM Tabl e   |

| 0xE0042000               | External PPB |

|                          | Reserved     |

| 0xE0041000<br>0xE0040000 | TPI U        |

|                          | Reserved     |

| 0xE000F000<br>0xE000E000 | SCS          |

|                          | Reserved     |

| 0xE0003000               | FPB          |

| 0xE0002000               | DWT          |

| 0xE0001000               | I TM         |

| - 0xE0000000             |              |

#### Peripheral Address Map

|            | Undefined   | Periphera  | i Address Map   | /  |

|------------|-------------|------------|-----------------|----|

| 0x60000000 | Underrined  | 0x5FFFFFF  | Reserved        | '/ |

| 0x40000000 | Peri pheral | 0x44000000 |                 | // |

| 0x40000000 | SRAM        | 0x42000000 | Bit band alias  | /  |

| 0x00000000 | Code        | ]          | Reserved        |    |

| 0x0000000  |             |            | Bit band region |    |

|            |             | \0x4000000 |                 | 1  |

Figure 5.2 Address Map (2)

## 6. Revision History

| Revision | Date       | Description                                                                                                                  |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------|

| 0.1      | 2014-03-12 | Newly released                                                                                                               |

| 0.2      | 2014-07-16 | Revised for rev 2.0: added bus address region to Figure 5.1.                                                                 |

| 0.3      | 2014-09-29 | Modified for VDD33 = 1.8 V specification.<br>Deleted Debug section.                                                          |

| 0.4      | 2014-10-07 | Added "4.6. SPI Flash Erase Mode" section.                                                                                   |

| 0.5      | 2014-10-22 | Deleted "3.2.1. Configuration Summary" section.<br>Corrected Power Supply Voltage from 2.0 V to 2.1 V in section 1.1.        |

| 0.6      | 2014-12-17 | Corrected "SPI Flash Direct Access Mode" of Table 4.2.<br>Corrected UART maximum data rate in section 3.2.5.                 |

| 1.0      | 2015-01-21 | Official version.                                                                                                            |

| 1.1      | 2015-04-09 | Modified 1.8 V Voltage range in section 1.1.                                                                                 |

| 1.2      | 2015-06-08 | Revised Peripherals GPIO in Section 3.2.4.                                                                                   |

| 1.3      | 2018-01-25 | Changed header, footer and the last page.<br>Changed corporate name and descriptions.<br>Modified Arm logo and descriptions. |

#### Table 6.1 Revision History

#### **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

## **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**