# TC78B002FTG/FNG 使用上の注意点

Rev. A

## 概要

TC78B002FTG/FNG は、出力トランジスタに DMOS 素子を採用したファンモータ用単相全波ドライバ IC です。 低いオン抵抗の DMOS 出力ドライバおよび PWM 駆動方式の採用により、高効率の駆動が可能です。

本資料は設計の補助を目的とする参考資料です。 最終機器設計時部品パラツキや使用条件等を十分考慮して設計をお願いします。

# **TOSHIBA**

## 目次

| 概  | 要                                | 1    |

|----|----------------------------------|------|

| 目  | 次                                | 2    |

| 义  | 目次                               | 3    |

| 表  | 目次                               | 4    |

| 1. | 電源電圧                             | 5    |

| 2. | 出力電流                             | 6    |

| 3. | 入力信号                             | 7    |

|    | 3.1. VSP、VMI 入力                  | 7    |

|    | 3.2. VSOFT、VOFF 入力               | 9    |

|    | 3.3. LA 入力                       | . 10 |

| 4. | 保護回路                             | . 11 |

|    | 4.1. ロック保護 (内部発振周波数 10MHz、通常回転時) | 11   |

|    | 4.2. ロック検出時間 (内部発振周波数 10MHz)     | . 12 |

|    | 4.3. 電流リミット                      | . 13 |

|    | 4.4. 過電流遮断(ISD)                  | . 14 |

|    | 4.5. 熱遮断(TSD)                    | . 16 |

|    | 4.6. 低電圧誤動作防止(UVLO)              | . 16 |

| 5. | 発振回路(OSC)                        | .17  |

| 6. | 応用回路例                            | .19  |

| 7. | 基板設計時の注意点                        | .23  |

| 8. | IC の消費電力                         | .25  |

| 9. | IC の許容損失                         | .27  |

| 10 | ). 使用上のご注意およびお願い事項               | .28  |

| 刬  | 品取り扱い上のお願い                       | 29   |

## 図目次

| 図 1.1 相切替時、モータ回生電流 による VM 端子電圧が上昇する例            | 5  |

|-------------------------------------------------|----|

| 図 1.2 保護動作で出力段全 OFF 時、モータ回生電流による VM 端子電圧が上昇する例  | 5  |

| 図 1.3 VM 端子電圧上昇対策例                              | 6  |

| 図 3.1 VSP 電圧と出力 Duty の関係                        | 7  |

| 図 3.2 VMI 設定時の VSP 電圧と出力 Duty の関係               | 7  |

| 図 3.3 出力スタート時動作波形例 (起動時出力 Duty=50%)             | 8  |

| 図 3.4 出力停止時動作波形例                                | 8  |

| 図 3.5 IC 動作波形例 (ソフトスイッチングなし)                    | 9  |

| 図 3.6 IC 動作波形例 (ソフトスイッチング期間 30.9°)              | 9  |

| 図 3.7 IC 動作波形例 (OFF 期間 30.9°)                   | 9  |

| 図 3.8 IC 動作波形例 (ソフトスイッチング期間 30.9°、OFF 期間 16.9°) | 9  |

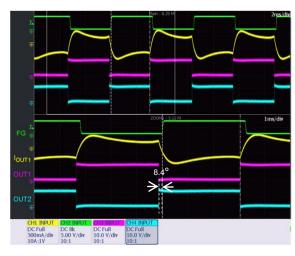

| 図 3.9 IC 動作波形例 (進角 8.4°)                        | 10 |

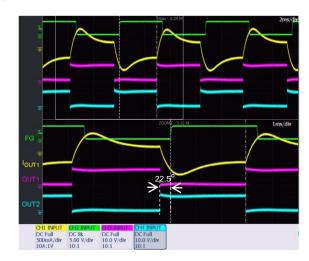

| 図 3.10 IC 動作波形例 (進角 22.5°)                      | 10 |

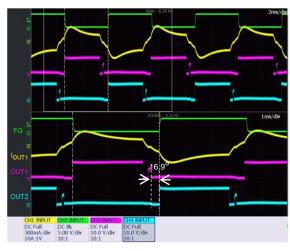

| 図 3.11 IC 動作波形例 (OFF 期間 16.9°、進角 16.9°)         | 10 |

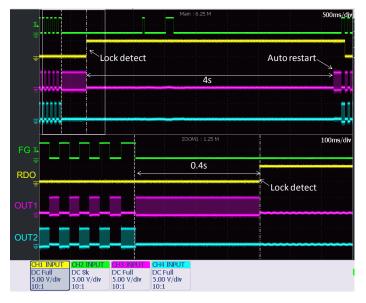

| 図 4.1 ロック保護動作波形例                                | 11 |

| 図 4.2 クイックスタート動作波形例                             | 11 |

| 図 4.3 通常回転時ロック検出時間                              | 12 |

| 図 4.4 起動時ロック検出時間                                | 12 |

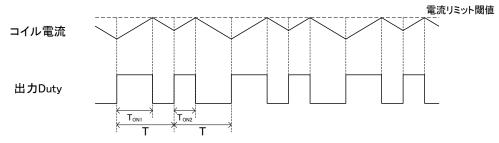

| 図 4.5 出力 Duty が 100%未満の場合の電流リミット動作イメージ          | 13 |

| 図 4.6 出力 Duty が 100%時の電流リミット動作イメージ 1            | 13 |

| 図 4.7 出力 Duty が 100%時の電流リミット動作イメージ 2            | 13 |

| 図 4.8 サブハーモニック発振発生時の出力波形イメージ                    | 14 |

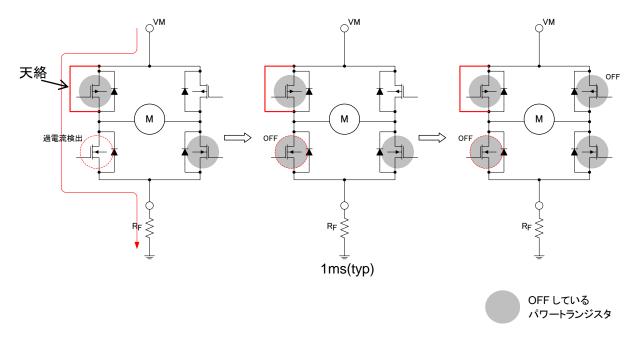

| 図 4.9 出力端子天絡時の動作イメージ                            | 14 |

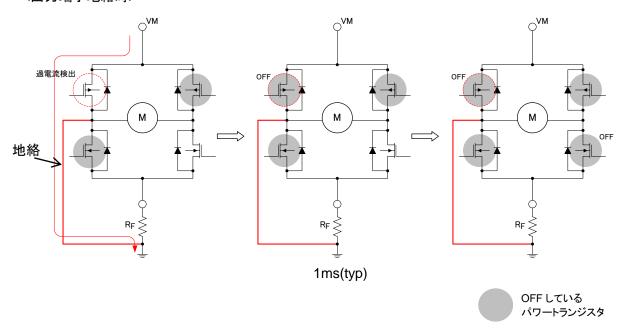

| 図 4.10 出力端子地絡時の動作イメージ                           | 15 |

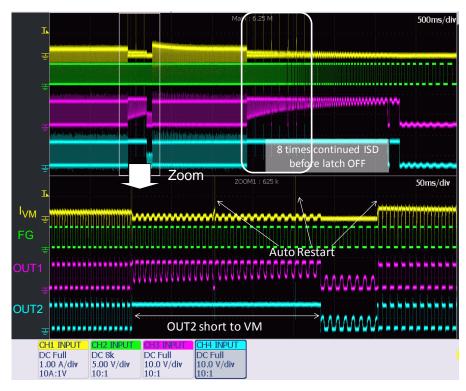

| 図 4.11 出力端子天絡時の動作例                              | 15 |

| 図 4.12 出力端子地絡時の動作例                              | 16 |

| 図 5.1 発振回路の等価回路                                 |    |

| 図 5.2 外付け抵抗と発振周波数(typ 値)の関係                     | 17 |

| 図 6.1 応用回路例                                     | 19 |

| 図 6.2 FR/RDO 端子プルアップ例                           | 20 |

| 図 6.3 ホール入力電圧範囲                                 | 21 |

| 図 6.4 ホール信号 振幅・ヒステリシス                           | 21 |

| 図 6.5 温度によるホール信号振幅変化の例                          | 21 |

| 図 6.6 Level shifter 回路例                         | 22 |

| 図 6.7 Level shifter 回路定数例                       | 22 |

# **TOSHIBA**

## **CONFIDENTIAL**

## TC78B002FTG/FNG Application Note

|   | 図 7.1 | QFN パッケージ 基板レイアウトイメージ2            | 23 |

|---|-------|-----------------------------------|----|

|   | 図 7.2 | 2 SSOP パッケージ 基板レイアウトイメージ2         | 23 |

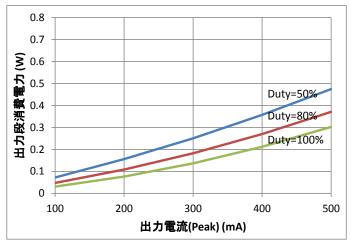

|   | 図 8.1 | 矩形波駆動時 出力段の消費電力2                  | 26 |

|   | 図 8.2 | 2 正弦波駆動時 出力段の消費電力2                | 26 |

|   |       |                                   |    |

| 表 | 目次    |                                   |    |

|   | 表 1.1 | 電源電圧の動作範囲                         | 5  |

|   | 表 5.1 | Rosc により変動する特性1                   | 8  |

|   | 表 8.1 | ソフトスイッチングのステップと出力 Duty 比率の関係2     | 26 |

|   | 表 9.1 | 400mA 矩形波駆動時 Tj と Ta・出力 Duty の関係2 | 27 |

## 1. 電源電圧

TC78B002FTG/FNG を使用するにあたり、IC の VM 端子へ電源電圧の印加が必要です。 VM 電源電圧の絶対最大定格は 18V ですが、動作範囲の 3.5~16V の範囲内で使用してください。

| 項目        | 記号                 | 動作範囲     | 単位 |

|-----------|--------------------|----------|----|

| 通常動作電源電圧  | VM <sub>opr1</sub> | 5.5 ~ 16 | V  |

| 低電圧動作電源電圧 | VM <sub>opr2</sub> | 3.5~5.5  | V  |

表 1.1 電源電圧の動作範囲

注: 絶対最大定格は瞬時たりとも超えてはならない規格です。 動作電源電圧範囲内で使用してください。

この IC の出力は PWM 制御機能を搭載しています。 VSP 電圧により出力 PWM の Duty を制御し、モータの回転速度を調整できます。 PWM 制御機能を使用する場合、 VM 電源電圧は「通常動作電源電圧」範囲内で使用してください。

PWM 制御せず、電源電圧制御でモータの回転速度を調整するアプリケーションに使用する場合、電源電圧調整可能な範囲をより広く取るために、「低電圧動作電源電圧」範囲を設けています。VM 電源電圧を「低電圧動作電源電圧」の範囲で使用する場合、VSP 端子を Vreg にプルアップして使用してください。

#### 【低電圧動作電源電圧の範囲で使用する際の注意点】

低電圧動作時、出力抵抗などの電気的特性は VM=12V 時と比べ変わります。詳細については、仕様書にある電気的特性参考データの該当部分を参照してください。

低電圧動作時、Vreg 電源電圧の低下と共に、IC 内部の A/D 変換回路の基準電圧も低くなります。IC 制御用端子の電圧を Vreg 電圧から抵抗分圧して作る場合には A/D 変換結果にほとんど変化はありませんが、外部から直接電圧入力する場合は、変換結果が変わる場合があります。特に VSP 端子電圧が外部入力された場合、低電圧動作時出力 Duty が変わる可能性があります。VSP 端子を Vreg にプルアップして使用する場合は、出力 Duty がフル Duty に固定されるため、問題はありません。

この IC 起動時の出力 Duty は 50%固定なので、電源電圧が低いと起動時のトルクが足りず起動できない場合があります。その場合は電源電圧を上げて起動してください。

#### 【モータ回生電流による VM 端子電圧上昇の対策について】

モータの回生電流により、VM 端子電圧が上昇することがあります。特に逆接防止ダイオードが使用されている場合は電流が電源へ回生できないため、VM 端子電圧が上昇します。回生電流による電圧上昇を含め、VM 端子電圧が絶対最大定格を超えないように使用してください。

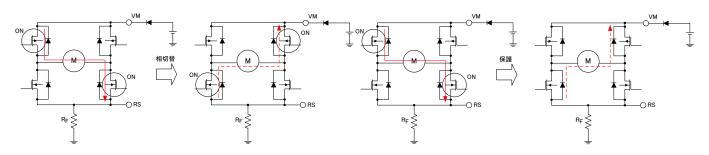

図 1.1 相切替時、モータ回生電流 による VM 端子電圧が上昇する例

図 1.2 保護動作で出力段全 OFF 時、 モータ回生電流による VM 端子電圧が上昇する例

IC のソフトスイッチング機能を使用することにより、相切替前にモータに流す電流を抑えられます。相切替時の回生電流をゼロに近づけることで、相切替時の電圧上昇を抑えられます。

また出力段全 OFF 後、回生電流による電圧上昇を抑えるために、この IC では出力段全 OFF する前に、PWM OFF の期間を設けています。PWM OFF 期間中、下側回生でモータの回生電流を減衰させます。ただし、モータ回転中に電源遮断などの異常が発生した場合、回生電流が減衰できないので、電源ラインに回生電流

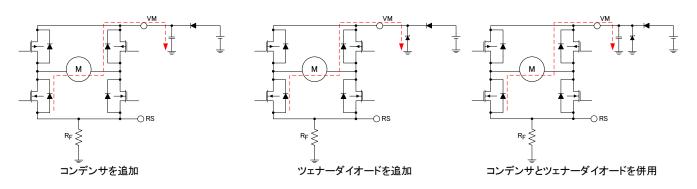

を吸収するため、VM 端子へコンデンサかツェナーダイオード、または両方を入れて、回生電流による電圧上昇を 16V 以内に抑えてください。ツェナーダイオードは回生電流による電圧上昇を抑えることができる他に、外部入力電圧が過電圧の場合でも回路保護が可能です。ツェナーダイオードを使用する場合、モータ通常動作時にツェナーダイオードに電流が流れないように、ツェナー電圧の値は通常動作電圧以上かつ 16V 以下の仕様のものを選定してください。

図 1.3 VM 端子電圧上昇対策例

この IC は単一電源であり、特に電源投入や遮断のための手順はありません。外部から VSP 電圧を入力してモータの回転速度を制御する場合、電源電圧が不安定な状態でモータを動作させると異常な動作の原因になるので、VM 電源電圧が安定な状態になってから VSP 電圧を入力しモータを動作させることを推奨します。 VSP 電圧を Vreg にプルアップして使用する場合、VSP 電圧は IC 内部で生成されるため、問題はありません。

電源遮断時、モータの回生電流による VM 端子の電圧が上昇する可能性がありますので、モータが停止してから、電源を遮断することを推奨します。 VSP 電圧を Vreg にプルアップして使用する場合や、最小出力 Duty を設定する場合、電源遮断時に VM 端子の電圧が絶対最大定格を超えないことを確認してください。

Vreg 電源電圧は IC 内部のレギュレータで生成されますので、外部から電圧を印加しないでください。Vreg 端子に 0.1uF の電源安定用コンデンサを接続してください。また IC の動作時は、IC の GND 端子を基準にして、Vreg 電圧は 5.5V 以内にしてください。電源安定用コンデンサを IC の近くに配置してください。コンデンサの GND と IC GND の間には、スイッチング電流経路がないように配線してください。詳細は「7.基板設計時の注意点」を参考にしてください。

Vreg 電源電圧を抵抗分圧してホール素子のバイアス電圧や IC 制御端子の電圧として使用することができますが、内部レギュレータの能力以上に電流を引かないでください。出力電流は絶対最大定格の 10mA 以内で使用してください。

## 2. 出力電流

絶対最大定格は1.5Aです。絶対最大定格は、瞬時たりとも超えてはならない規格です。モータ起動時の突入電流、ロック時電流などでも絶対最大定格以内になるように設計してください。

使用可能な平均出力電流は、使用条件(周囲温度や基板実装方法等)によって増減します。T<sub>j</sub> は 150℃ を超えないようにマージンをもって設計してください。詳細は「8. IC の消費電力」「9. IC の許容損失」を参考にしてください。

## 3. 入力信号

#### 3.1. VSP、VMI 入力

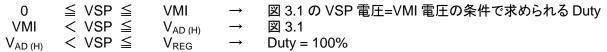

IC の出力 Duty は 7-bit AD コンバータを経由して、VSP 端子電圧と VMI 端子電圧によって制御されます。

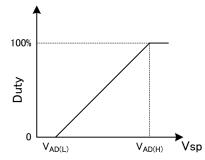

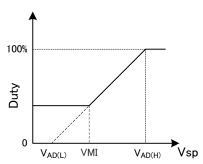

VSP 端子の電圧は 7-bit AD コンバータでデジタル化され、内部ロジックがそのデータを使用して出力 PWMの Duty を制御します。 VSP 端子入力電圧と出力 Duty の関係は下記のとおりです。

注: V<sub>SP</sub> 電圧 V<sub>AD(L)</sub>から V<sub>AD(H)</sub>の 100 ステップに 応じて、出力 Duty は 1%ずつ変化します。

図 3.1 VSP 電圧と出力 Duty の関係 V<sub>AD(L)</sub>=0.55V(typ) V<sub>AD(H)</sub>=3.9V(typ)

VMI 端子に VAD(L)以上の電圧が印加されると最小出力 Duty が設定されます。VSP 端子入力電圧と出力 Duty の関係は下記のとおりです。

図 3.2 VMI 設定時の VSP 電圧と出力 Duty の関係

VMI 端子に入力する電圧は VREG 端子電圧から抵抗分圧して供給してください。

VSP 端子電圧と VMI 端子電圧のどちらが 0.55V を超えるとモータを起動します。

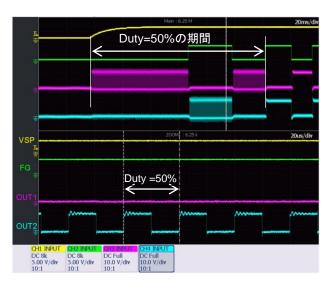

起動時、ホール信号の周波数が 5Hz 以上になるまで出力 Duty は 50%固定です。5Hz 以上になると、VSP電圧と VMI 電圧によって出力 Duty は変化します。起動時の波形例を図 3.3 に示します。

起動時の出力 Duty は 50%固定なので、高い VSP 電圧でもモータ起動時の突入電流を抑えることができます。また低い VSP 電圧でもある程度の起動トルクが出せますが、電源電圧が低い場合は起動トルクが足りず起動できない可能性があります。低い電源電圧で起動させる場合は、十分に評価を行ってください。

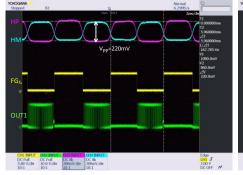

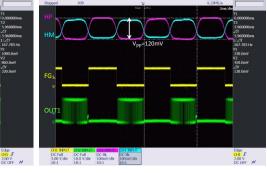

図 3.3 出力スタート時動作波形例 (起動時出力 Duty=50%)

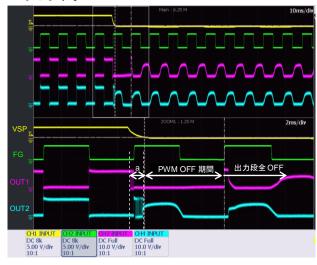

VSP 端子電圧とVMI 端子電圧と両方 0.55V 以下になると、モータを駆動するための出力を停止します。出力 段全 OFF にする前に、PWM OFF の期間を設けています。PWM OFF 期間中、下側回生でモータの回生電流 を減衰させます。そのため、出力段全 OFF する時に電源への回生電流を抑えることができます。波形例を図 3.4 に示します。

図 3.4 出力停止時動作波形例

注:aの期間中、VSP 端子電圧の降下により出力 Duty が変化します。

#### 3.2. VSOFT、VOFF 入力

VSOFT 端子と VOFF 端子の電圧によって IC のソフトスイッチング機能を制御できます。

ソフトスイッチング機能とは通電相の切り替え前後に OFF 期間とソフトスイッチング期間を挿入します。ソフトスイッチング機能はモータ振動の軽減や相切り替え時の VM 電圧上昇の抑制に有効です。

VSOFT 端子電圧は VOFF 端子電圧より高い場合、全期間(OFF 期間 + ソフトスイッチング期間)の電気角は VSOFT 端子電圧により決まり、OFF 期間の電気角は VOFF 端子電圧により決まります。

VSOFT 端子電圧は VOFF 端子電圧より低い場合、ソフトスイッチング期間はなく、OFF 期間のみとなります。 OFF 期間の電気角は VOFF 端子電圧により決まります。

VSOFT 端子とVOFF 端子の電圧は 7-bit AD コンバータを経由してデジタル化されます。内部ロジックがそのデータを使用してソフトスイッチングの制御を行います。VSOFT 端子と VOFF 端子に入力する電圧は VREG端子電圧から抵抗分圧して供給してください。

#### 例 1:VSOFT=0, VOFF=0V

図 3.5 IC 動作波形例 (ソフトスイッチングなし)

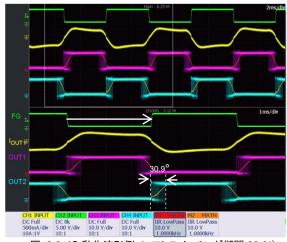

#### 例 2: VSOFT=1.55V, VOFF=0V

図 3.6 IC 動作波形例 (ソフトスイッチング期間 30.9°)

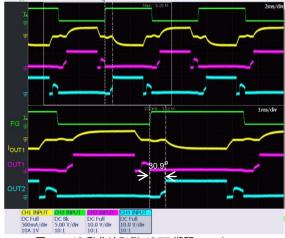

#### 例 3: VSOFT=0V, VOFF=1.55V

図 3.7 IC 動作波形例 (OFF 期間 30.9°)

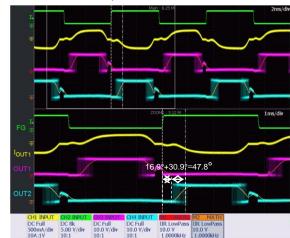

## 例 4: VSOFT=2.40V, VOFF=0.9V

図 3.8 IC 動作波形例 (ソフトスイッチング期間 30.9°、OFF 期間 16.9°)

## 3.3. LA 入力

LA 端子の電圧によって通電タイミングはホール信号に対して最大 22.5°の進角まで補正できます。進角制御によりモータ電流の位相とモータ誘起電圧の位相を合わせることができます。モータの効率向上を図れます。

図 3.9 IC 動作波形例 (進角 8.4°)

#### 例 2:LA=2.2V

図 3.10 IC 動作波形例 (進角 22.5°)

また、進角の設定はソフトスイッチング期間・OFF 期間と併用することにより、通電相切替前の回生電流を抑えられ、相切替後直ちにモータに電流が流れます。

#### 例 3: VOFF=0.9V, LA=1.7V

図 3.11 IC 動作波形例 (OFF 期間 16.9°、進角 16.9°)

LA 端子に入力する電圧は VREG 端子電圧から抵抗分圧して供給してください。

## 4. 保護回路

この IC は以下の機能を内蔵しています。如何なる場合でも IC を保護するものではありません。 必ず絶対最大定格以内でご使用ください。出力短絡、出力天絡/地絡の場合、回路動作の前に IC が破壊する 場合があります。

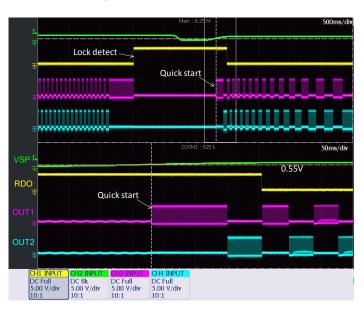

#### 4.1. ロック保護 (内部発振周波数 10MHz、通常回転時)

モータ回転中に 0.4 秒以上ホール信号のゼロクロスが検出できない場合、ロック保護が動作します。

ホール信号のゼロクロスが検出されたかどうかは FG 信号で観測できます。ゼロクロスが検出されると FG 信号出力の状態が変わります。0.4 秒以上 FG 信号の状態が変わらない場合、ロック状態と認識します。

FG 信号の状態について、ロック保護動作と関係なく、ホール信号のゼロクロスを検出すると、FG 信号の状態が変わります。

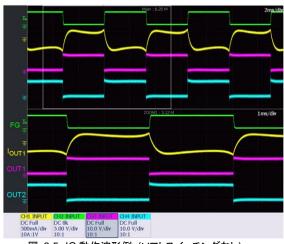

モータを駆動するための出力は、ロック保護動作後 OFF になります。また、ロック状態検出から4 秒後に自動復帰します。自動復帰時は、通常起動と同じ 50%の出力 Duty から起動します。モータのロックを解除しないまま自動復帰する場合、出力開始の 0.4 秒後に再度ロック保護動作が行われ、ロック解除まで 4 秒間停止・0.4 秒間動作を繰り返します。

RDO 信号はモータのロック状態を示す信号です。ロック状態を認識すると、「H」になります。自動復帰で出力開始後、ホール信号のゼロクロスを2回検出すれば、RDO信号は「L」に戻ります。

ロック検出時間と自動復帰までの時間は内部発振周波数に依存します。詳細は「5.発振回路」を参照してください。

ロック保護動作期間中、外部から VSP 端子電圧を 0.55V 以下にして、VSP 信号応答時間(max)の 10ms 経過の後、再度 0.55V 以上にすると直ちに再起動します(クイックスタート)。

図 4.1 ロック保護動作波形例

図 4.2 クイックスタート動作波形例

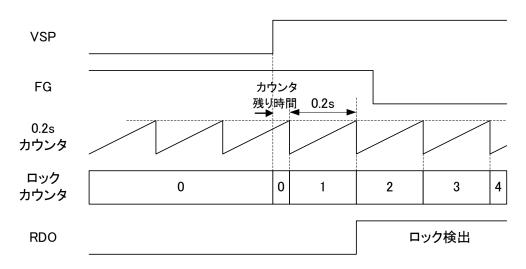

#### 4.2. ロック検出時間 (内部発振周波数 10MHz)

ロックの検出時間については、

- ・通常回転時、FG のエッジで内部カウンタをリセットし、0.4 秒後にロック検出します。

- ・起動時のみ、FG のリセットが働かないため、最短 0.2 秒でロック保護が動作する可能性があります。

図 4.3 通常回転時ロック検出時間

通常回転時にロック検出しない場合、FG のエッジで 0.2s カウンタをリセットします。

FG のエッジが来ない場合、0.2 秒後に 0.2s カウンタがオーバーフローします。0.2s カウンタがオーバーフローすると、ロックカウンタがカウントアップします。ロックカウンタのカウンタ値が 2 になると、ロック検出します。そのため、ロック検出のタイミングは最後の FG のエッジから 0.4 秒後になります。

図 4.4 起動時ロック検出時間

VSP が 0.55V 以下、モータを駆動するための出力が停止している場合、ロックカウンタは 0 に固定されますが、 0.2s カウンタは通常にカウントアップします。

VSP が 0.55V 以上になると、ロックカウンタがカウントアップできるようになります。VSP が 0.55V 以上になる タイミングで、0.2s カウンタのカウントが既に進んでいるため、ロック検出時間はカウンタ残り時間(0~0.2 秒) + 0.2 秒になります。ロック検出時間まで FG のエッジが来ない場合、ロック保護が動作します。

ロック保護動作後、自動で再起動する場合、再起動するタイミングは 0.2s カウンタと連動していますので、ロック検出時間は 0.4 秒になります。

クイックスタートを使用する場合、ロック検出時間は起動時と同じ 0.2s 秒~0.4 秒です。

ロック検出時間が短く起動性を確保できない場合は、起動時の電源電圧を上げるか、内部発振周波数を低め に設定することによって起動性を向上できます。内部発振周波数の詳細は「5.発振回路」を参照してください。

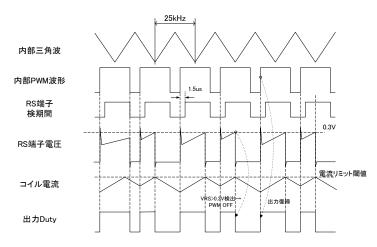

#### 4.3. 電流リミット

モータに流れる電流は抵抗  $R_F$ により検出します。抵抗  $R_F$ の電圧が電流リミット検出電圧  $V_{RS}$ =0.3V(typ)になると電流リミット回路が働きます。

電流リミット回路が動作する電流値 Iour = 過電流検出電圧 VRS / 検出抵抗 RF

$R_F=0.62\Omega$  の時、 $I_{OUT}=0.3V(typ)/0.62\Omega=484mA$  になると、電流リミット回路が働きます。

ただし、RS 端子のノイズ対策のため、出力 PWM ON から 1.5us の間、マスク期間を設けています。マスク期間内に RS 端子電圧が 0.3V を超えても電流リミット回路は動作しません。

電流リミット回路動作時、上側の出力パワートランジスタをOFF し、出力PWMをOFFにします。次の内部三角波のピークのタイミングで電流リミットを解除し、内部PWMのONタイミングで上側の出力パワートランジスタをONして出力が復帰します。

出力 Duty が 100%未満の場合、電流リミット回路動作によって出力 PWM の Duty が変化するように見える場合があります。動作イメージを図 4.5 に示します。

図 4.5 出力 Duty が 100%未満の場合の電流リミット動作イメージ

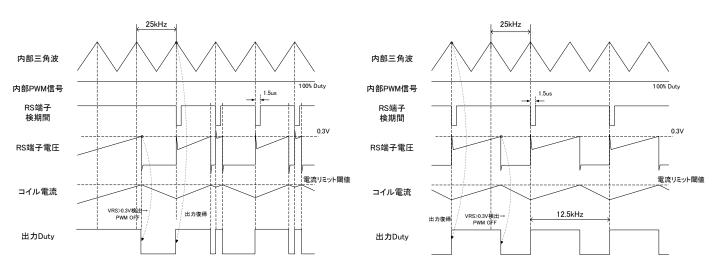

出力 Duty が 100%の場合、出力復帰のタイミングは内部三角波のピークのタイミングになります。電流リミット 検出のタイミングと復帰のタイミングによって、出力 PWM の周波数が変化するように見える場合もあります。 図 4.7 のように、復帰から電流リミット検出までの時間が内部三角波の一周期以上の場合、PWM 周波数が 12.5kHz(もしくは 25kHz の整数分の一)になります。PWM の周波数が 20kHz 以下になると、可聴領域に入る ので、可聴ノイズの原因になります。

図 4.6 出力 Duty が 100%時の電流リミット動作イメージ 1 出力 PWM の Duty が変化します

図 4.7 出力 Duty が 100%時の電流リミット動作イメージ 2 出力 PWM の周波数が変化します

また、電流リミット回路動作により、オン期間がスイッチング周期の整数倍で変動する可能性があります。これをサブハーモニック発振と呼びます。

#### (ご参考)

図 4.8 サブハーモニック発振発生時の出力波形イメージ

サブハーモニック発振は電流リミット動作の原理によるもので、異常動作ではありません。サブハーモニック発振により、PWM 周波数の整数分の一の周波数成分が生じ、可聴ノイズの原因になることがあります。

電流リミット動作により発生した可聴ノイズが実使用に与える影響は評価の上判断してください。

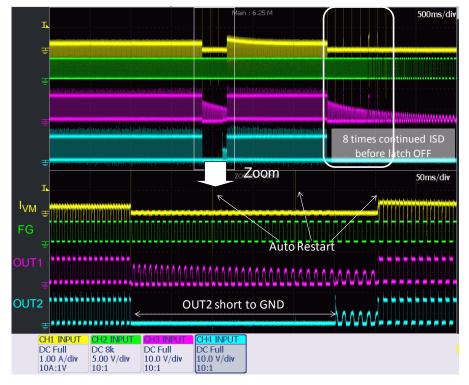

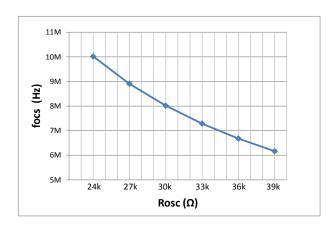

#### 4.4. 過電流遮断(ISD)

4 つのパワートランジスタに流れる電流を個別に検出し、電流値が設定値を超えると該当する出力パワートランジスタを OFF にして、1ms(typ)後、全ての出力パワートランジスタを OFF にします。

#### <出力端子天絡時>

図 4.9 出力端子天絡時の動作イメージ

#### <出力端子地絡時>

図 4.10 出力端子地絡時の動作イメージ

過電流検出回路にはタイマカウンタが内蔵されています。過電流を検出してから 100ms(typ)後出カパワートランジスタ OFF 状態から自動復帰します。過電流が継続した場合、OFF→自動復帰の動作を繰り返します。連続8回過電流遮断(ISD)動作した場合、自動復帰せず OFF 状態を維持します。VSP の再投入もしくは電源の再投入で OFF 状態を解除します。

#### <出力端子天絡時動作例>

図 4.11 出力端子天絡時の動作例

<出力端子地絡時動作例>

図 4.12 出力端子地絡時の動作例

#### 4.5. 熱遮断(TSD)

Tj が 170℃(typ)以上になると熱遮断回路(TSD)が動作し、上側の出力パワートランジスタを OFF にします。 PWM OFF 期間を 1ms(typ)経過した後、全ての出力パワートランジスタを OFF にします。

Tj が 130℃(typ)以下に戻ると出力を復帰します。

#### 4.6. 低電圧誤動作防止(UVLO)

VM 電源電圧と VREG 端子電圧を監視して、いずれかが 2.9V(typ)以下になると低電圧と判定し出力回路を OFF にします。両方の電圧が 3.2V(typ)以上に戻ると通常動作に戻ります。

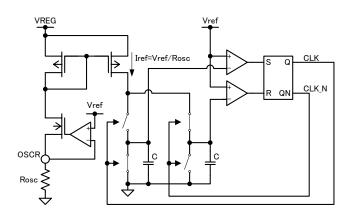

## 5. 発振回路(OSC)

OSCR 端子に外付け抵抗(R<sub>OSC</sub>)を接続し、CR 発振を行い、内部で基準クロックを作ります。 発振回路の等価回路を図 5.1 に示します。

OSC 回路の発振周波数は、以下の式で近似されます。

$f_{OSC} = Iref/(2xCxVref) = (Vref/R_{OSC}) / (2xCxVref) = 1/(2xCxR_{OSC})$

C: IC 内部の等価容量 C=2.08pF (typ)

Rosc: OSCR 端子外付け抵抗

外付け抵抗が 24kΩ の場合、発振周波数は

$f_{OSC} = 1 / (2 \times 2.08e-12 \times 24000) = 10MHz(typ.)$

外付け抵抗が 39kΩ の場合、発振周波数は

$f_{OSC} = 1 / (2 \times 2.08e - 12 \times 39000) = 6.2MHz(typ.)$

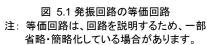

図 5.2 外付け抵抗と発振周波数(typ 値)の関係

IC の動作範囲は 5~12MHz です。IC 内部の発振回路のバラツキは約 $\pm$ 20%です。このバラツキを考慮して、外付け抵抗を  $24k\Omega$ ~ $39k\Omega$  の間に設定してください。また外付け抵抗は精度が $\pm$ 1%以内のものを使用してください。

外付け抵抗の抵抗値が大きい場合、外部からのノイズの影響を受けやすくなるため、できるだけ IC の近くに接続してください。詳細について「7. 基板設計時の注意点」に参考してください。

外付け抵抗定数変更で発振周波数を変更した場合、出力 PWM 周波数やロック検出時間など内部クロックに依存する特性も変動します。Rosc が  $24k\Omega$  と  $39k\Omega$  の時に変動する特性については表 5.1 を参照してください。

| 変化する特性         |                      | Rosc = 24kΩ |       |       | Rosc = 39kΩ |         |         |

|----------------|----------------------|-------------|-------|-------|-------------|---------|---------|

| 2.107 017.12   | ×12 / Ø14111         |             | typ   | max   | min         | typ     | max     |

| 内部発振周波数        | fosc                 | 8MHz        | 10MHz | 12MHz | 5.0MHz      | 6.2MHz  | 7.4MHz  |

| PMW 周波数        | f <sub>PWM</sub>     | 20kHz       | 25kHz | 30kHz | 12.5kHz     | 15.5kHz | 18.6kHz |

| ロック検出 ON 期間    | T <sub>ON</sub>      | 0.32s       | 0.4s  | 0.48s | 0.5s        | 0.65s   | 0.8s    |

| ロック検出 OFF 期間   | T <sub>OFF</sub>     | 3.2s        | 4s    | 4.8s  | 5s          | 6.5s    | 8s      |

| 起動時ロック検出 ON 期間 | T <sub>ON(min)</sub> | 0.16s       | 0.2s  | 0.24s | 0.25s       | 0.32s   | 0.4s    |

| VSP 信号応答時間     | T <sub>VSP</sub>     | _           | _     | 10ms  | _           | _       | 20ms    |

| 電流リミット検出マスク時間  | T <sub>mask</sub>    | 1.2us       | 1.5us | 1.8us | 1.9us       | 2.4us   | 3.0us   |

| 過電流遮断回路マスク期間   | TISDMASK             | 1.6us       | 2us   | 2.4us | 2.5us       | 3.2us   | 4.0us   |

| 過電流遮断回路 OFF 期間 | T <sub>ISDOFF</sub>  | 80ms        | 100ms | 120ms | 125ms       | 160ms   | 200ms   |

| ソフトスイッチング切り替え  | 周波数                  | 4Hz         | 5Hz   | 6Hz   | 2.5Hz       | 3.1Hz   | 3.7Hz   |

| 昇圧防止 PWM OFF   | 期間                   | 0.8ms       | 1ms   | 1.2ms | 1.3ms       | 1.6ms   | 2ms     |

| ホール入力デジタルフィル   | /タ時間                 | 20us        | 25us  | 30us  | 32us        | 41us    | 50us    |

表 5.1 Rosc により変動する特性

低い内部発振周波数を使用する場合、特に下記特性が変動しますので、十分に確認の上使用してください。

- ・PWM 周波数が低くなります。20kHz 以下の可聴領域に入ると、可聴ノイズの原因になります。

- ・ロック検出 ON 期間が長くなります。ロック保護動作までの通電時間が長くなるので、ロック時にモータの温度上昇が問題ないか十分に確認してください。電流リミット閾値を低めに設定することでモータの温度上昇を抑えることができます。

- ・電流リミット検出マスク時間が長くなります。マスク期間中では、電流が電流リミット閾値を超えても電流リミット回路が動作しません。

- ・ホール入力デジタルフィルタ時間が長くなります。ホール信号のノイズ対策のため、デジタルフィルタ時間を設けています。デジタルフィルタにより相切り替え認識まで位相の遅延が発生します。この位相遅延はモータの回転速度に依存します。

Rosc=24kΩ 時、フィルタ時間は 25us(typ)です。

- 4 極モータ、回転数 3000RPM の場合、位相遅延は 0.9°です。

- 4 極モータ、回転数 6000RPM の場合、位相遅延は 1.8°です。

Rosc=39kΩ 時、フィルタ時間は 41us(tvp)です。

- 4 極モータ、回転数 3000RPM の場合、位相遅延は約 1.5°です。

- 4 極モータ、回転数 6000RPM の場合、位相遅延は約 3.0°です。

- モータ回転数が高い場合、位相遅延の影響を十分に評価して使用してください。

## 6. 応用回路例

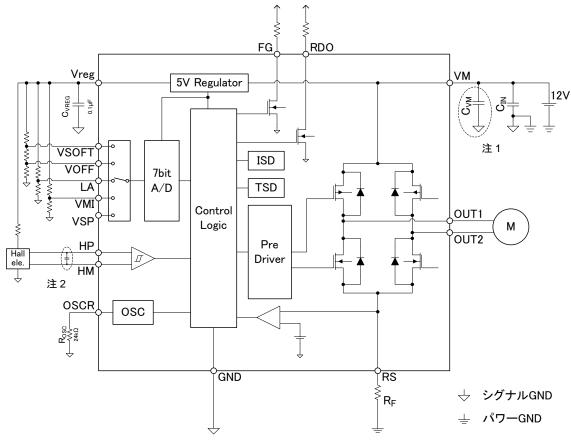

注 1: コンデンサ C<sub>VM</sub> は高周波ノイズ対策用として必要に応じて接続してください。

注 2: ホール信号の入力コンデンサはノイズによる誤検出防止用として必要に応じて接続してください。

図 6.1 応用回路例

#### (1) 電源端子用コンデンサ

電源電圧安定化、およびノイズリジェクトのため各端子へ適切な値のコンデンサを接続してください。なお、コンデンサはできるだけIC の近くに接続してください。特にセラミックコンデンサをIC 近傍に接続することで高い周波数の電源変動やノイズ抑制に効果的です。

| 項目                              | 部品            | 標準値   | 推奨範囲              |

|---------------------------------|---------------|-------|-------------------|

| VM-GND間 (C <sub>IN</sub> )      | セラミック/電解コンデンサ | 10μF  | 2.2 <b>∼</b> 22µF |

| Vreg-GND 間 (C <sub>VREG</sub> ) | セラミックコンデンサ    | 0.1µF | 0.1∼0.47µF        |

注:モータ負荷条件や基板パターンなどによっては、各部品を省く、推奨値以外のコンデンサを使用するなども可能です

VM-GND 間のコンデンサを IC から 10mm 以内に配置することを推奨します。

VM-GND 間のコンデンサが基板レイアウト上 IC と離れて配置され、高い周波数の電源変動に対して十分な効果が得られない場合には、IC の VM・GND 端子の直近に 0.1 uF 前後のコンデンサ  $C_{\text{VM}}$  の追加を推奨します。

Vreg-GND 間コンデンサの GND とIC の GND 端子の間に、スイッチング電流を流す経路がないように設計してください。詳細について「7.基板設計時の注意点」を参考してください。

### (2) GND 配線について

IC の GND 端子をシグナル GND に接続してください。 Vreg 端子のコンデンサ、OSCR 端子の抵抗もシグナル GND に最短で接続してください。 VSOFT、 VOFF、 LA と VMI 端子の電圧は Vreg 電圧から抵抗分圧して供給する場合、分圧抵抗の GND もシグナル GND に接続してください。

シャント抵抗 R<sub>F</sub>の GND をパワーGND に接続してください。

シグナル GND とパワーGND をコンデンサ  $C_{IN}$ で一点接地してください。コンデンサ  $C_{IN}$ を IC のできるだけ近い位置に配置してください。詳細について「7. 基板設計時の注意点」に参考してください。

## (3) シャント抵抗

シャント抵抗  $R_F$ に大電流が流れますので、定格を十分注意しマージンをもって選んでください。 モータ動作時、シャント抵抗にかかる電力は最大  $P=0.3Vx0.3V/R_F$ です。 例えば、 $R_F=0.62\Omega$  時、P=0.145W となりますので、定格電力は 0.25W 以上の抵抗を使用してください。

## (4) VMI、VSOFT、VOFF、LA 設定用抵抗

VMI、VSOFT、VOFF と LA は VREG から抵抗分圧よって設定してください。 VSOFT、VOFF は 32 ステップ制御できますので、精度  $\pm 1\%$ 以内の抵抗を使用してください。 また抵抗値が大きい場合、ノイズの影響を受けやすいため、300k $\Omega$ 以下の抵抗を使用してください。

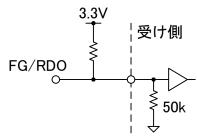

## (5) FG/RDO プルアップ抵抗

FG 端子とRDO 端子はオープンドレインのため、High レベルを出力するためには外部電源にプルアップする必要があります。プルアップ抵抗の抵抗値の推奨範囲は 10~100 kΩです。ただし、FG 信号/RDO 信号の受け側の入力端子の入力電流を確認し High レベル電圧を確保できるようにプルアップ抵抗を選定してください。

図 6.2 FR/RDO 端子プルアップ例

例えば、図 6.2 のように受け側の入力端子は  $50k\Omega$  プルダウンされている場合、FG/RDO 端子を 3.3V に  $100k\Omega$  でプルアップすると、High レベル時の電圧が  $3.3V/(100k\Omega+50k\Omega)\times50k\Omega=1.1V$  となり、受け側で High レベルを認識できなくなる可能性があります。High レベル時の電圧を 2V 以上にするため、 $30k\Omega$  以下の抵抗を使用してください。

FG 端子、RDO 端子を使用しない場合、端子をオープンにしてください。

## (6) ホール素子抵抗

VREGの5V電源からホール素子へ電源を供給する場合、ホール素子の最大入力電流を超えないように、電 流制限用抵抗をホール素子の電源端子に追加してください。ホール素子入力抵抗の温度特性を考慮しマージ ンをもって設計してください。ホール素子の最大入力電流が 10mA の場合、510Ωの抵抗を推奨します。

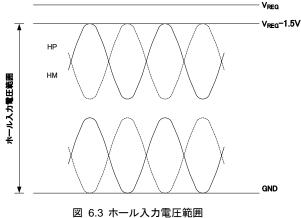

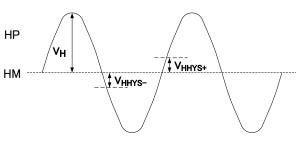

ホール素子抵抗によるホール素子の振幅が変化します。ホール信号を正しく認識できる電圧範囲は図 6.3 に 示します。

図 6.4 ホール信号 振幅・ヒステリシス

ホール信号の切り替えを正しく認識させるためにはホール素子の振幅 V<sub>H</sub> は 40mV 以上にする必要がありま す。またホールアンプはヒステリシスが付いています。ホール信号波形は正弦波、振幅 VH=100mV の場合、ヒ ステリシスによる相切り替え遅延は約5.7° (typ)、振幅 VH=200mV の場合、ヒステリシスによる相切り替え遅延 は約2.9°(tvp)です。ホール振幅が小さい場合、切り替えタイミングの位相ズレが大きくなるため、できるだけホ ール素子の振幅を広げてください。

ホールの温度特性によって、ホール信号の振幅が変化します。

a.低温時:ホール信号振幅 220mV

b.常温時:ホール信号振幅 120mV

c.高温時:ホール信号振幅 90mV

図 6.5 温度によるホール信号振幅変化の例

この IC のソフトスイッチング期間はホール信号の周期により決まります。ホール信号の振幅はソフトスイッチ ングの期間に影響を与えません。できるだけホール信号の振幅を大きくしてください。

また、VM 電源からホール素子に電源を供給すると、IC の発熱を抑えることができます。その場合は、ホール 素子の最大定格、ホール信号の電圧範囲、および VM 電源の変動やノイズの影響を注意して設計してくださ い。

## (7) パルス Duty 入力 — アナログ電圧 変換回路例

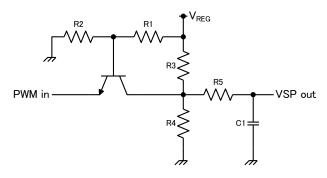

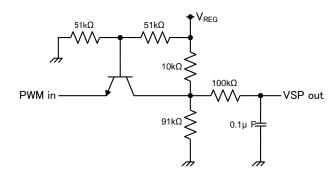

外部からの速度制御信号がアナログ電圧ではなくパルス Duty の場合、パルス Duty からアナログ電圧への変換回路が必要です。パルス Duty 信号 (PWM in)の High 側が 5V の場合、RC フィルタでパルス Duty 信号からアナログ電圧(VSP out)に変換できます。

パルス Duty 信号の High 側が 3.3V の場合、Level shifter 回路が必要となります。

Level shifter 回路の例を図 6.6 に示します。R1 と R2 の抵抗分圧で PWM 信号の閾値が設定できます。 R3 と R4 の抵抗分圧で PWM Duty=100%時の出力電圧を設定できます。 Duty と出力電圧の関係は下記式で近似できます。

$VSP = 5V \times R4 / (R3 + R4) \times Duty$

R5とC1は電圧を平滑化するためのRCフィルタとなります。入力PWMの周波数によって調整してください。 回路定数の一例は図6.7に示します。

図 6.6 Level shifter 回路例

図 6.7 Level shifter 回路定数例

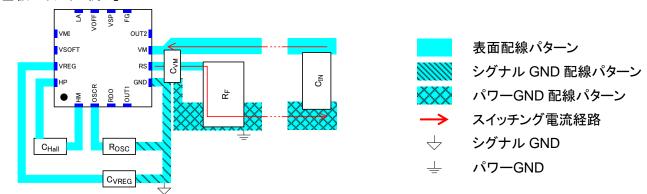

### 7. 基板設計時の注意点

特に VM, RS, GND パターンへは大電流が流れることが想定されるため、配線インピーダンスなどの影響を受けないよう十分な配線パターンを確保してください。なお IC の出力段が PWM スイッチングをする時、出力スルーレートが速いため、基板配線インピーダンスのインダクタ成分により電源・GND が揺れやすいので、十分に注意してください。

#### 【基板レイアウト例 1】

図 7.1 QFN パッケージ 基板レイアウトイメージ 注:図は一定の縮尺で描かれていません

注:図は一定の縮尺で描かれていません

- ・スイッチング電流を流すラインをできるだけ太く短くしてください。

- ・VM-GND 間のコンデンサをできるだけ IC 端子の近くに配置してください。基板電源入り口に入力電圧平滑用コンデンサがあっても、IC との距離が離れている場合、配線インピーダンスの L 成分の影響で、PWM スイッチング時 VM 電源電圧変動や、IC の GND 電圧変動を十分に抑えられない可能性があります。必ず IC の VM・GND 端子の近くに VM-GND 間コンデンサを入れてください。この場合、VM-GND 間コンデンサは小容量(0.01uF~0.1uF)のコンデンサでも効果が得られますが、十分評価の上、コンデンサを選定してください。

- ・Vreg-GND 間コンデンサを IC の近くに配置してください。Vreg 電圧を安定化するためには、コンデンサの GND と IC の GND 端子の間の配線を短くして、かつスイッチング電流を流す経路がないように設計してください。IC の動作時は、IC の GND 端子を基準にして、Vreg 端子の電圧が 5.5V 以内であることを確認してください。PWM スイッチング時、IC の GND がマイナス側に振れるので、IC の GND 端子と Vreg 端子間の電圧が 5.5V より大きい場合、VM-GND 間コンデンサを強化してください。

- ・発振回路基準電流設定用抵抗 Rosc を IC の近くに配置してください。Rosc の GND と IC の GND 端子の間にスイッチング電流を流す経路がないように設計してください。

- ・ジャンパーが必要な場合、GND ラインより出力ラインに入れるほうが回路動作への影響が少なくなります。

- ・ホール信号ノイズ除去用コンデンサを付ける場合、IC の HP と HM 端子の近くに配置してください。コンデンサの容量については、0.01µF~0.1µF を推奨します。

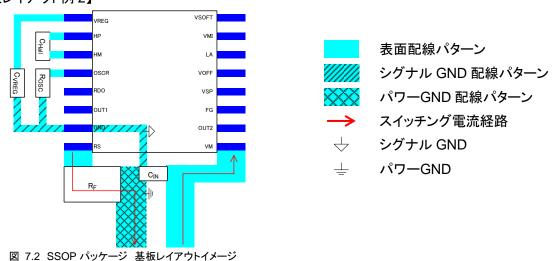

SSOP パッケージで基板を設計する場合、同じくGND 周りの配線パターンを十分注意して設計してください。 【基板レイアウト例 2】

基板設計時、ご参考のランドパターン寸法は以下になります。

#### 注意

- ・特に表示がない限り、寸法数字の単位はミリメートルです。

- ・本資料は JEITA ET-7501 Level 3 に準じた参照用の図です。 当社は、図および情報の正確性、完全性に関して一切の保証をいたしません。

- ・お客様にて各種条件(はんだ付け条件など)を十分評価し、お客様の責任において調整を行ってください。

- ・本資料の図は実際の形状や寸法を正確に示すものではありません。図から採寸などで現品の寸法を見積も るなど、その値で設計しないでください。

- ・設計および使用に際しては、本製品に関する最新の情報および本製品が使用される機器の取扱説明書など をご確認の上、これに従ってください。

IC 裏面の放熱パッドから、基板の GND パターンへ熱を逃がすことで、IC の発熱を効率よく逃がすことが可能です。そのため、極力 IC 周辺部に GND エリアを確保してください。また多層基板の場合、層間の熱抵抗を下げるためにはサーマルビアを配置してください。

## 8. IC の消費電力

IC が消費する電力については、大枠、ロジック部の消費電力、内部レギュレータの消費電力と出力段の消費電力の3つの部分に分けることができます。

$$P(total) = P(logic) + P(reg) + P(out)$$

..... (式 1)

P(total): IC の消費電力

P(logic): ロジック部の消費電力

P(reg): 内部レギュレータの消費電力

P(out): 出力段の消費電力

#### ・ロジック部の消費電力

ロジック部の消費電力は以下のように計算できます。

$$P(logic) = V_M \times I_{VM}$$

..... (式 2)

VM=12V の場合、I<sub>VM</sub>=3mA (typ)。 (式 2)から P(logic)=12V × 3mA = 36mW

・内部レギュレータの消費電力

Vreg 電源をホール素子などの外付け部品の電源として使用する場合、内部レギュレータの消費電力は以下のように計算できます。

$$P(reg) = (V_M - Vreg) \times I_{Vreg}$$

..... (式 3)

VM=12V の場合、I<sub>Vrea</sub>=5mA (typ)。 (式 3)から P(reg)=(12V-5V) × 5mA = 35mW

・ 出力段の消費電力

出力段の消費電力は、

PWM ON の時は上下 MOSFET の消費電力

PWM OFF の時は下側回生ダイオード、下側 MOSFET の消費電力、

および電流回生時 IC 内部のバイアス電流による消費電力。 バイアス電流はモノリシックによる寄生電流を含む電流です。電流回生時のバイアス電流は回生電流の約6%です。

$$P(out) = I_{out} \times I_{out} \times R_{on(H+L)} \times Duty + (I_{out} \times V_F + I_{out} \times I_{out} \times R_{on(L)} + VM \times I_{bias}) \times (1-Duty) \qquad \cdots \qquad (\vec{x} \ 4)$$

出力段の消費電力は制御方法・出力ピーク電流・出力 Duty 等の条件に依存します。

出力電流が 400mA の矩形波、出力 Duty=80%の場合、(式 4)から P(400mA,80%)=0.4A×0.4A×1.6Ω×0.8 + (0.4A×1V + 0.4A×0.4A×0.8Ω + 12V×400mA×6%) ×0.2 =0.368W

ソフトスイッチング機能を使う場合、出力電流を正弦波に近づけることができます。ソフトスイッチングは最大 16 ステップです。各ステップの出力 PWM Duty 比率を表 8.1 に示します。

| 表 8.1 プラトスイッテングのステップと出力 Duty 比率の関係 |         |      |         |      |         |  |

|------------------------------------|---------|------|---------|------|---------|--|

| Step                               | 出力比率(%) | Step | 出力比率(%) | Step | 出力比率(%) |  |

| 1                                  | 4       | 7    | 59      | 13   | 94      |  |

| 2                                  | 14      | 8    | 67      | 14   | 97      |  |

| 3                                  | 25      | 9    | 74      | 15   | 99      |  |

| 4                                  | 34      | 10   | 80      | 16   | 100     |  |

| 5                                  | 42      | 11   | 86      |      |         |  |

| 6                                  | 52      | 12   | 91      |      |         |  |

車 Q 1 ソフトフィッチングのフテップと出力 Dub, 比索の関係

出力電流がピーク 400mA の正弦波、出力 PWM Duty が最大 80%の条件では、下記式で近似計算できます。 P(sin)={ P(400mAx 4%,80%x 4%) +P(400mAx14%,80%x14%)+P(400mAx25%,80%x25%)

- + P(400mA×34%,80%×34%)+P(400mA×42%,80%×42%)+P(400mA×52%,80%×52%)

- + P(400mA×59%.80%×59%)+P(400mA×67%,80%×67%)+P(400mA×74%.80%×74%)

- + P(400mA×80%.80%×80%)+P(400mA×86%,80%×86%)+P(400mA×91%.80%×91%)

- + P(400mA×94%.80%×94%)+P(400mA×97%.80%×97%)+P(400mA×99%.80%×99%)

- + P(400mA×100%,80%×100%)} / 16

=0.270W

P(400mA×4%,80%×4%)は矩形波駆動時、駆動電流=400mA×4%、出力 Duty=80%×4%条件の消費電力。 (式 4)から計算できます。

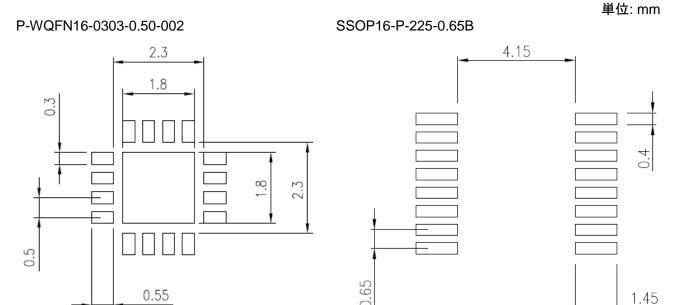

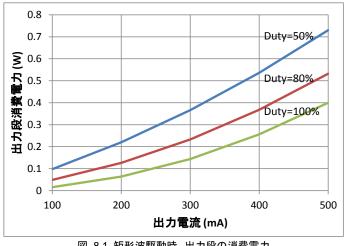

出力段の消費電力は制御方法・出力ピーク電流・出力 Duty 等の条件に依存します。図 8.1 は矩形波駆動時の 出力段消費電力、図8.2は正弦波駆動時の出力段消費電力の近似計算結果です。

図 8.1 矩形波駆動時 出力段の消費電力

図 8.2 正弦波駆動時 出力段の消費電力

#### ·IC の消費電力

最終的な消費電力 P(total)は、以下のように計算できます。

出力電流が 400mA の矩形波、出力 Duty=80%の場合

P(total) = P(logic) + P(reg) + P(out)

= 0.036W + 0.035W + 0.368W

= 0.439W

上記計算値を参考に、基板などにおける熱設計に関して十分実装評価を行った上、放熱設計をしてください。

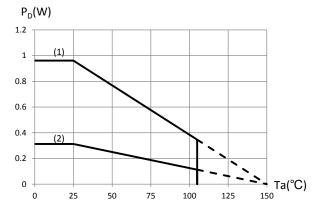

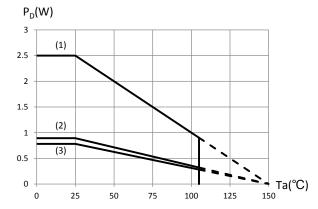

## 9. IC の許容損失

周囲環境温度  $(T_a)$  とジャンクション温度  $(T_j)$ 、およびジャンクションから周囲温度間の熱抵抗 $(R_{th(j-a)})$ の関係式は以下のとおりです。

$T_i = T_a + P_{(total)} \times R_{th(i-a)}$

ジャンクション温度 $(T_j)$ の絶対最大定格は 150°Cです。許容可能な消費電力  $P_{(total)}$ は  $T_a$ ,  $R_{th(j-a)}$ に依存します。周囲環境温度が高い場合、許容可能な消費電力はその分小さくなります。また熱抵抗が大きい場合、許容可能な消費電力はその分小さくなります。

#### (ご参考) 許容損失ー周囲環境温度の関係について

#### TC78B002FNG (SSOP16)

- (1) 基板実装時 R<sub>th(j-a)</sub>=130℃/W (40mm×30mm×1.6mm 2 層 FR-4 基板)

- (2) IC 単体 R<sub>th(j-a)</sub>=400°C/W

#### TC78B002FTG (QFN16)

- (1) 基板実装時 R<sub>th(j-a)</sub>=50°C/W (74mm×74mm×1.6mm 4 層 FR-4 基板)

- (2) 基板実装時 R<sub>th(j-a)</sub>=140°C/W (74mm×74mm×0.6mm 2 層 FR-4 基板)

QFN パッケージを片面基板に実装する場合(R<sub>th(j-a)</sub>=160℃/W と仮定)、前記 P<sub>(total)</sub> =0.439W の使用条件では、

- ・周辺温度 0°Cでモータを使用する場合 Tj = 0°C + 160°C/W × 0.439 (W) = 70°C

- ・周辺温度 25℃でモータを使用する場合 Tj = 25℃ + 160℃/W × 0.439 (W) = 95℃

- •周辺温度 60°Cでモータを使用する場合 Tj = 60°C + 160°C/W × 0.439 (W) = 130°C

- •周辺温度 80℃でモータを使用する場合 Tj = 80℃ + 160℃/W × 0.439 (W) = 150℃

表 9.1 400mA 矩形波駆動時 Tj と Ta・出力 Duty の関係 QFN パッケージ Rth(j-a)=160°C/W

| Tj (°C) | Duty=80% | Duty=100% |  |  |

|---------|----------|-----------|--|--|

| 0       | 70       | 52        |  |  |

| 25      | 95       | 77        |  |  |

| 60      | 130      | 112       |  |  |

| 80      | 150      | 132       |  |  |

#### ICの発熱を改善するには、

- ・片面基板から多層基板にして、熱抵抗を低減します。

- ・VM 電源からホール素子に電源を供給し、内部レギュレータの消費電力を低減します。 などの方法が考えられます。

105℃以内に抑えて使用してください。 T<sub>i(ave)</sub>=T<sub>i(ON)</sub> × ON Duty + T<sub>i(OFF)</sub> × OFF Duty

周辺温度 60°Cの環境で、平均 1 日 8 時間で動作する場合、 T<sub>i(ave)</sub>= 130°C×(8hr/24hr) + 60°C×(16hr/24hr) = 83.3°C

上記計算値を参考に、熱設計に関して十分実装評価を行った上、マージンをもって放熱設計をしてください。

また、ジャンクション温度が高いと IC の劣化が速くなります。より確かな信頼性を持たせるためには Ti(ave)を

## 10. 使用上のご注意およびお願い事項

#### · 使用上の注意事項

- (1) 絶対最大定格は複数の定格の、どの 1 つの値も瞬時たりとも超えてはならない規格です。 複数の定格のいずれに対しても超えることができません。絶対最大定格を超えると破壊、損傷および劣 化の原因となり、破裂・燃焼による傷害を負うことがあります。

- (2) 過電流の発生や IC の故障の場合に大電流が流れ続けないように、適切な電源ヒューズを使用してください。IC は絶対最大定格を超えた使い方、誤った配線、および配線や負荷から誘起される異常パルスノイズなどが原因で破壊することがあり、この結果、IC に大電流が流れ続けることで、発煙・発火に至ることがあります。破壊における大電流の流出入を想定し、影響を最小限にするため、ヒューズの容量や溶断時間、挿入回路位置などの適切な設定が必要となります。

#### 使用上の留意点

(1) 過電流検出回路

過電流検出回路はどのような場合でもICを保護するわけではありません。動作後は、速やかに過電流 状態を解除するようお願いします。

絶対最大定格を超えた場合など、ご使用方法や状況により、過電流制限回路が正常に動作しなかったり、動作する前に IC が破壊したりすることがあります。また、動作後、長時間過電流が流れ続けた場合、 ご使用方法や状況によっては、IC が発熱などにより破壊することがあります。

#### (2) 熱遮断回路

熱遮断回路 (通常: サーマルシャットダウン回路) は、どのような場合でも IC を保護するわけではありません。動作後は、速やかに発熱状態を解除するようお願いします。

絶対最大定格を超えて使用した場合など、ご使用法や状況により、熱遮断回路が正常に動作しなかったり、動作する前に IC が破壊したりすることがあります。

## 製品取り扱い上のお願い

- 本資料に掲載されているハードウェア、ソフトウェアおよびシステム(以下、本製品という)に関する情報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を得て本資料 を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

- ●当社は品質、信頼性の向上に努めていますが、半導体・ストレージ製品は一般に誤作動または故障する場合があります。本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウエア・ソフトウエア・システムに必要な安全設計を行うことをお願いします。なお、設計および使用に際しては、本製品に関する最新の情報(本資料、仕様書、データシート、アプリケーションノート、半導体信頼性ハンドブックなど)および本製品が使用される機器の取扱説明書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

- 本製品は、特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な財産損害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下"特定用途"という)に使用されることは意図されていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇宙機器、医療機器、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連機器、昇降機器、電力機器、金融関連機器などが含まれますが、本資料に個別に記載する用途は除きます。特定用途に使用された場合には、当社は一切の責任を負いません。なお、詳細は当社営業窓口までお問い合わせください。

- 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

- 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用することはできません。

- 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をしておりません。

- 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、「米国輸出管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず当社営業窓口までお問い合わせください。本製品の ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査の上、かか る法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は一切の 責任を負いかねます。