### Application Processor Lite ApP Lite

# **TZ1000 Series**

# **Reference Manual**

# **MCU Power Management Unit**

**Revision 1.6**

2018-02

### **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

### Table of Contents

| Preface                                                          |    |

|------------------------------------------------------------------|----|

| Intended Audience                                                | 10 |

| Conventions in this document                                     | 10 |

| Terms and Abbreviations                                          | 11 |

| 1. Overview                                                      |    |

| 2. Block Diagram                                                 |    |

| 3. Address Map                                                   |    |

| 4. Function                                                      |    |

| 4.1. Clock and Reset                                             |    |

| 4.1.1. Clock Distribution Diagram                                | 17 |

| 4.1.2. Clock Source                                              |    |

| 4.1.3. Clock Domain                                              | 19 |

| 4.1.3.1. Maximum operating frequency of each clock domain        |    |

| 4.1.4. Clock Source Control                                      |    |

| 4.1.4.1. OSC12M                                                  |    |

| 4.1.4.2. OSC32K                                                  |    |

| 4.1.4.3. SIOSC4M                                                 | 24 |

| 4.1.4.4. SIOSC32K                                                | 25 |

| 4.1.4.5. PLL                                                     |    |

| 4.1.4.6. ADPLL                                                   |    |

| 4.1.5. DFS Control                                               |    |

| 4.1.6. Clock Source Change for CPU TraceClock                    |    |

| 4.1.7. Setting 32.768 kHz clock                                  |    |

| 4.1.8. MCU_OSC32KOUT Control                                     |    |

| 4.1.9. Reset Control                                             |    |

| 4.1.9.1. Software Reset                                          |    |

| 4.1.9.2. Hardware reset                                          |    |

| 4.1.9.3. WDT reset                                               |    |

| 4.1.9.4. LOCKUP reset                                            |    |

| 4.1.9.5. SYSRESETREQ reset                                       |    |

| 4.1.9.6. BrownOut reset                                          |    |

| 4.1.9.7. WDT/LOCKUP/SYSRESETREQ reset in the debugger connection |    |

| 4.1.9.8. Reset Cause Summary<br>4.1.10. Clock Gating Control     |    |

| 4.1.10.1 Dynamic Clock Gating                                    |    |

| 4.1.11. Clock Gating Control Linked to Reset Control             |    |

| 4.2. Power Control                                               |    |

| 4.2.1. Power Circuit                                             |    |

| 4.2.2. Power Supply Domain                                       |    |

| 4.2.3. Power Domain Control                                      |    |

| 4.2.3.1 Power Shut-down and Return Control                       |    |

| 4.2.3.2. Retention Transition and Return Control                 |    |

|                                                                  |    |

| 4.2.3.3. PM Domain Control                                                                           | 39 |

|------------------------------------------------------------------------------------------------------|----|

| 4.2.3.4. PU Domain Control                                                                           | 39 |

| 4.2.3.5. PF/PC/PD/PS0/PS1/PS2/PE/PP1/PA12/PA24 Domain Control                                        | 40 |

| 4.2.3.6. PEFUSE Domain Control                                                                       | 41 |

| 4.2.3.7. PPLL Domain control                                                                         | 41 |

| 4.2.3.8. PADPLL Domain control                                                                       | 42 |

| 4.2.4. Sensor Power Supply Pin Control                                                               | 43 |

| 4.2.4.1. Gyroscope Power Supply Pin Control (MCU_VDD33_GYRO_OUT)                                     | 43 |

| 4.2.4.2. Magnetometer Power Supply Pin Control (MCU_VDD33_MAG_OUT)                                   | 43 |

| 4.2.4.3. Accelerometer Power Supply Pin Control (MCU_VDD33_ACC_OUT)                                  | 44 |

| 4.2.4.4. SPI Flash Memory Power Supply Pin Control                                                   | 44 |

| 4.3. Power Mode Transition Control                                                                   | 45 |

| 4.3.1. Power Mode Transition Diagram                                                                 | 47 |

| 4.3.2. VoltageMode                                                                                   | 48 |

| 4.3.2.1. VoltageMode Transition Specification                                                        | 48 |

| 4.3.2.2. Voltage Circuit Switch procedure                                                            | 48 |

| 4.3.2.3. VoltageMode Transition procedure                                                            | 48 |

| 4.3.2.4. The available clock source in VoltageMode                                                   | 49 |

| 4.3.2.5. The necessary procedure to VoltageMode transition                                           | 50 |

| 4.3.3. PowerMode                                                                                     | 51 |

| 4.3.3.1. ACTIVE-WFI Mode                                                                             | 51 |

| 4.3.3.1.1. ACTIVE-WFI Transition and Return<br>4.3.3.1.1.1. ACTIVE-WFI Transition Control            |    |

| 4.3.3.1.1.2. ACTIVE-WFI Return Control                                                               |    |

| 4.3.3.2. SLEEP0/1/2 Mode                                                                             |    |

| 4.3.3.2.1. SLEEP0/1/2 Transition and Return<br>4.3.3.2.1.1. SLEEP0/1/2 Transition Control            |    |

| 4.3.3.2.1.2. SLEEP0/1/2 Return Control (when the CPU SLEEPING is set)                                | 54 |

| 4.3.3.2.1.3. SLEEP0/1/2 Return Control (When the CPU SLEEPDEEP is set)                               |    |

| 4.3.3.3. WAIT/WAIT-RETENTION Mode<br>4.3.3.3.1. WAIT/WAIT-RETENTION Transition and Return            |    |

| 4.3.3.3.1.1. WAIT/WAIT-RETENTION Transition Control.                                                 | 55 |

| 4.3.3.3.1.2. WAIT/WAIT-RETENTION Return Control                                                      |    |

| 4.3.3.4. RETENTION Mode<br>4.3.3.4.1. RETENTION Transition and Return                                |    |

| 4.3.3.4.1.1. RETENTION Transition Control                                                            | 58 |

| 4.3.3.4.1.2. RETENTION Return Control                                                                |    |

| 4.3.3.5. RTC/STOP Mode<br>4.3.3.5.1. RTC/STOP Transition and Return                                  |    |

| 4.3.3.5.1.1. RTC/STOP Transition Control                                                             | 61 |

| 4.3.3.5.1.2. RTC/STOP return control                                                                 |    |

| 4.3.3.6. Relationship of PowerMode, VoltageMode, Power Domain Control, Clock Source and Clock Domain |    |

|                                                                                                      |    |

| 4.4. Boot Sequence                                                                                   |    |

| 4.4.1. Power Supply Sequence                                                                         |    |

| 4.4.1.1. SPI Power internal supply mode (BOOTMODE3 = 0)                                              |    |

| 4.4.1.2. SPI Power External Supply Mode (BOOTMODE3 = 1)                                              |    |

| 4.4.2. Start-up Sequence                                                                             |    |

| 4.5. BrownOut Control                                                                                |    |

| 4.5.1. Precaution                                                                                    |    |

| 4.6. IO Control                                                                                      | 71 |

|    | 4.6.1. IO Buffer Control               | 71   |

|----|----------------------------------------|------|

|    | 4.6.2. IO Buffer Control and PowerMode | 72   |

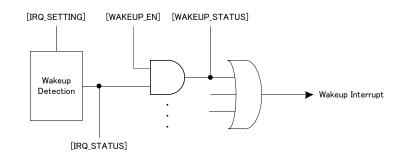

|    | 4.6.3. Wakeup Interrupt Detection      | 73   |

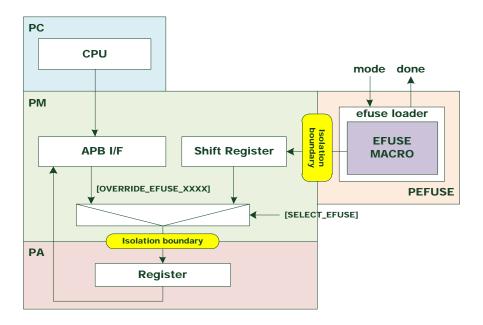

| 4  | 4.7. EFUSE Function                    | 76   |

| 5. | Details of Registers                   | . 77 |

| Ę  | 5.1. CG_ON_POWERDOMAIN                 | 77   |

| Ę  | 5.2. CG_OFF_POWERDOMAIN                | 78   |

| Ę  | 5.3. DCG_POWERDOMAIN                   | 79   |

| Ę  | 5.4. SRST_ON_POWERDOMAIN               | 80   |

| Ę  | 5.5. SRST_OFF_POWERDOMAIN              | 81   |

| Ę  | 5.6. CG_ON_PM_0                        | 81   |

| Ę  | 5.7. CG_ON_PM_1                        | 82   |

| Ę  | 5.8. CG_ON_PM_2                        | 83   |

| Ę  | 5.9. CG_ON_PE                          | 84   |

| Ę  | 5.10. CG_ON_PF                         | 85   |

| Ę  | 5.11. CG_ON_PD                         | 85   |

| Ę  | 5.12. CG_ON_PU                         | 86   |

| Ę  | 5.13. CG_ON_PA12                       | 86   |

| Ę  | 5.14. CG_ON_PA24                       | 87   |

|    | 5.15. CG_ON_PP1                        |      |

| Ę  | 5.16. CG_ON_HARDMACRO                  | 88   |

| Ę  | 5.17. CG_ON_REFCLK                     | 88   |

|    | 5.18. CG_OFF_PM_0                      |      |

| Ę  | 5.19. CG_OFF_PM_1                      | 90   |

| Ę  | 5.20. CG_OFF_PM_2                      | 91   |

| Ę  | 5.21. CG_OFF_PE                        | 92   |

| Ę  | 5.22. CG_OFF_PF                        | 92   |

| Ę  | 5.23. CG_OFF_PD                        | 93   |

| Ę  | 5.24. CG_OFF_PU                        | 93   |

| Ę  | 5.25. CG_OFF_PA12                      | 94   |

| Ę  | 5.26. CG_OFF_PA24                      | 94   |

| Ę  | 5.27. CG_OFF_PP1                       | 95   |

| Ę  | 5.28. CG_OFF_HARDMACRO                 | 96   |

| Ę  | 5.29. CG_OFF_REFCLK                    | 96   |

| Ę  | 5.30. DCG_PM_0                         | 96   |

| Ę  | 5.31. DCG_PM_1                         | 97   |

| Ę  | 5.32. DCG_PM_2                         | 98   |

| Ę  | 5.33. DCG_PE                           | 99   |

| Ę  | 5.34. DCG_PF                           | 100  |

| Ę  | 5.35. DCG_PD                           | 100  |

| Ę  | 5.36. DCG_PU                           | 101  |

| Ę  | 5.37. DCG_PA12                         | 101  |

| 5.38. DCG_PA24         | 101 |

|------------------------|-----|

| 5.39. DCG_PP1          | 102 |

| 5.40. CLKREQ_CONFIG_PE | 103 |

| 5.41. SRST_ON_PM_0     | 103 |

| 5.42. SRST_ON_PM_1     | 104 |

| 5.43. SRST_ON_PM_2     | 105 |

| 5.44. SRST_ON_PE       | 105 |

| 5.45. SRST_ON_PF       | 106 |

| 5.46. SRST_ON_PD       | 106 |

| 5.47. SRST_ON_PU       | 107 |

| 5.48. SRST_ON_PA12     | 107 |

| 5.49. SRST_ON_PA24     | 108 |

| 5.50. SRST_ON_PP1      | 108 |

| 5.51. SRST_OFF_PM_0    | 109 |

| 5.52. SRST_OFF_PM_1    | 109 |

| 5.53. SRST_OFF_PM_2    | 110 |

| 5.54. SRST_OFF_PE      | 111 |

| 5.55. SRST_OFF_PF      | 111 |

| 5.56. SRST_OFF_PD      | 112 |

| 5.57. SRST_OFF_PU      | 112 |

| 5.58. SRST_OFF_PA12    | 113 |

| 5.59. SRST_OFF_PA24    | 113 |

| 5.60. SRST_OFF_PP1     | 114 |

| 5.61. CTRL_MODETRAN    | 115 |

| 5.62. CSM_MAIN         | 115 |

| 5.63. CSM_CPUTRC       | 116 |

| 5.64. CSM_CPUST        | 116 |

| 5.65. CSM_USBI         | 116 |

| 5.66. CSM_UART0        | 117 |

| 5.67. CSM_UART1        | 117 |

| 5.68. CSM_UART2        | 118 |

| 5.69. CSM_ADCC12A      | 118 |

| 5.70. CSM_ADCC24A      | 119 |

| 5.71. PRESCAL_MAIN     | 119 |

| 5.72. PRESCAL_CPUST    | 120 |

| 5.73. PRESCAL_USBI     | 121 |

| 5.74. PRESCAL_UART0    | 122 |

| 5.75. PRESCAL_UART1    | 123 |

| 5.76. PRESCAL_UART2    | 124 |

| 5.77. PRESCAL_ADCC12A  | 125 |

| 5.78. PRESCAL_ADCC24A  | 126 |

| 5.79. CONFIG_OSC12M    | 126 |

|                        |     |

| 5.80. CONFIG_PLL_0                   | 127 |

|--------------------------------------|-----|

| 5.81. CONFIG_PLL_1                   | 127 |

| 5.82. CONFIG_ADPLL_0                 | 128 |

| 5.83. CONFIG_ADPLL_1                 | 128 |

| 5.84. CONFIG_DCDC_LVREG_1            | 129 |

| 5.85. CONFIG_LDOF_0                  | 129 |

| 5.86. OVERRIDE_EFUSE_OSC12M          | 130 |

| 5.87. SELECT_EFUSE                   | 130 |

| 5.88. EFUSE_REVISIONID               | 131 |

| 5.89. EFUSE_BOOTSEQ                  | 132 |

| 5.90. EFUSE_SIOSC4M                  | 132 |

| 5.91. BROWNOUTRESET                  | 133 |

| 5.92. MOVE_VOLTAGE_START             | 133 |

| 5.93. MOVE_POWER_VOLTAGE_MODE        | 134 |

| 5.94. POWERDOMAIN_CTRL               | 135 |

| 5.95. POWERDOMAIN_CTRL_MODE          | 135 |

| 5.96. POWERDOMAIN_CTRL_STATUS        | 136 |

| 5.97. POWERDOMAIN_CTRL_MODE_FOR_WAIT | 137 |

| 5.98. POWERDOMAIN_CTRL_MODE_FOR_WRET | 137 |

| 5.99. POWERDOMAIN_CTRL_MODE_FOR_RET  | 138 |

| 5.100. VOLTAGEMODE_SETTING           | 139 |

| 5.101. WAITTIME_LDOF                 | 139 |

| 5.102. WAITTIME_PSW                  | 140 |

| 5.103. WAITTIME_DVSCTL               | 140 |

| 5.104. POWERMODE_SLEEP_CG_ON         | 141 |

| 5.105. POWERMODE_SLEEP_PRESCAL       | 142 |

| 5.106. CG_ON_PC_SCRT                 | 143 |

| 5.107. CG_OFF_PC_SCRT                | 143 |

| 5.108. CG_ON_PA                      | 144 |

| 5.109. CG_OFF_PA                     | 144 |

| 5.110. SRST_ON_PA                    | 145 |

| 5.111. SRST_OFF_PA                   | 145 |

| 5.112. CSM_RTC                       | 145 |

| 5.113. RTCLV_RSYNC_SETTING           | 146 |

| 5.114. CONFIG_OSC32K                 | 146 |

| 5.115. CONFIG_SIOSC32K               | 147 |

| 5.116. CONFIG_SIOSC4M                | 147 |

| 5.117. CONFIG_DCDC_HVREG             | 147 |

| 5.118. CONFIG_LVD_0                  | 148 |

| 5.119. CONFIG_LDOM_0                 | 148 |

| 5.120. CONFIG_LDOM_1                 | 149 |

| 5.121. CONFIG_LDOS_0                 | 149 |

| 5.122. CONFIG_LDOS_1           | 150 |

|--------------------------------|-----|

| 5.123. OVERRIDE_EFUSE_OSC32K   | 150 |

| 5.124. OVERRIDE_EFUSE_SIOSC32K | 151 |

| 5.125. OVERRIDE_EFUSE_SIOSC4M  | 151 |

| 5.126. OVERRIDE_EFUSE_BGR_0    | 151 |

| 5.127. OVERRIDE_EFUSE_BGR_1    | 152 |

| 5.128. STATUS_LVPWR            | 152 |

| 5.129. STATUS_LVRST            | 153 |

| 5.130. BROWNOUTMODE            | 154 |

| 5.131. CTRL_IO_AON_0           | 154 |

| 5.132. CTRL_IO_AON_1           | 155 |

| 5.133. CTRL_IO_AON_2           | 155 |

| 5.134. CTRL_IO_AON_3           | 156 |

| 5.135. CTRL_IO_AON_4           | 157 |

| 5.136. CTRL_IO_AON_5           | 157 |

| 5.137. CTRL_IO_AON_6           | 157 |

| 5.138. PSW_PU                  | 158 |

| 5.139. PSW_EFUSE               | 159 |

| 5.140. PSW_PLL                 | 159 |

| 5.141. PSW_ADPLL               | 160 |

| 5.142. PSW_IO_USB              | 160 |

| 5.143. PSW_HARDMACRO           | 160 |

| 5.144. ISO_PU                  | 161 |

| 5.145. ISO_EFUSE               | 161 |

| 5.146. ISO_PLL                 | 162 |

| 5.147. ISO_ADPLL               | 162 |

| 5.148. IRQ_SETTING_0           | 163 |

| 5.149. IRQ_SETTING_1           | 163 |

| 5.150. IRQ_STATUS              | 164 |

| 5.151. WAKEUP_EN               | 165 |

| 5.152. WAKEUP_STATUS           |     |

| 5.153. CTRL_CDBGPWRUPREQ       | 166 |

| 6. Revision History            |     |

| RESTRICTIONS ON PRODUCT USE    |     |

### List of Figures

| Figure 2.1  | Block diagram                                                 | 13 |

|-------------|---------------------------------------------------------------|----|

| Figure 4.1  | Clock distribution diagram                                    | 17 |

| Figure 4.2  | Prescaler output (CD_MPIER/CD_PPIER0·1·2/CD_SPIC/CD_USBB)     | 20 |

| Figure 4.3  | Prescaler output (CD_UART0·1·2/CD_CPUST/CD_USBI/CD_ADCC12·24) | 21 |

| Figure 4.4  | Peripheral circuit structure of the CSM_RTC                   | 30 |

| Figure 4.5  | Clock Gating Control linked to Reset Control                  | 36 |

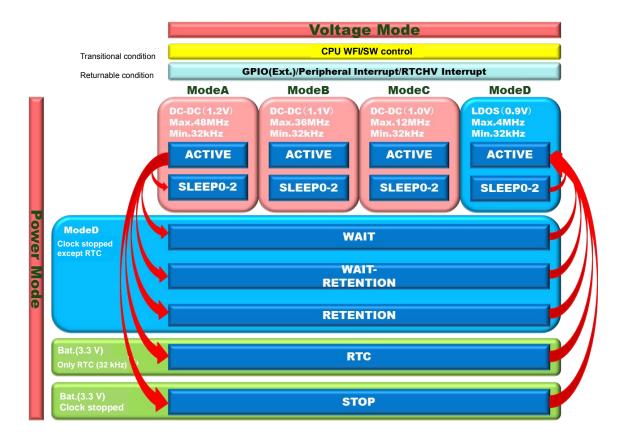

| Figure 4.6  | Power mode                                                    | 45 |

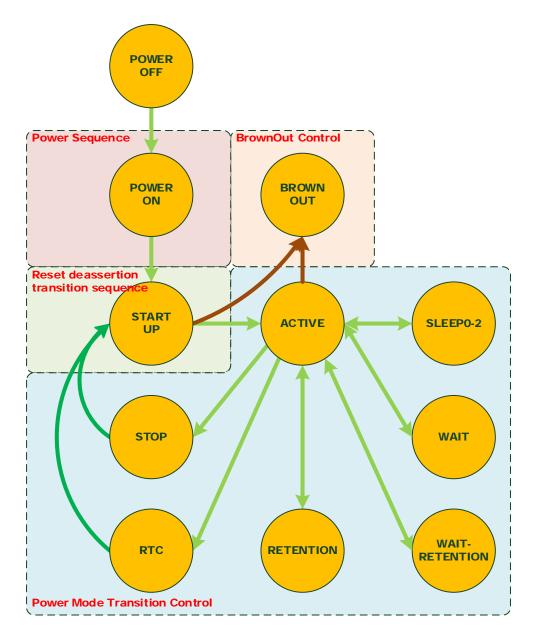

| Figure 4.7  | Power mode transition diagram                                 | 47 |

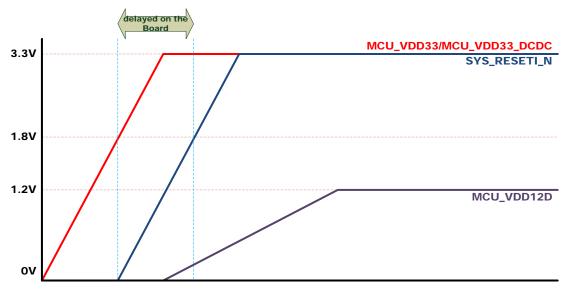

| Figure 4.8  | Power supply sequence (BOOTMODE3 = 0)                         | 68 |

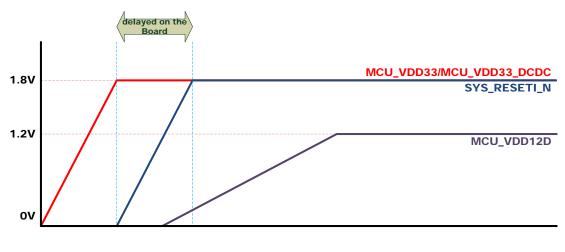

| Figure 4.9  | Power supply sequence (BOOTMODE3 = 1)                         | 68 |

| Figure 4.10 | wakeup detection circuit                                      | 73 |

| Figure 4.11 | EFUSE load                                                    | 76 |

### List of Tables

| Table 1.1  | Terms and abbreviations                                          |    |

|------------|------------------------------------------------------------------|----|

| Table 3.1  | MCU Power Management Unit Register Map                           |    |

| Table 4.1  | Clock Source                                                     |    |

| Table 4.2  | Prescaler                                                        |    |

| Table 4.3  | Maximum operating frequency of each clock domain                 |    |

| Table 4.4  | Clock and Reset state                                            |    |

| Table 4.5  | Power domain                                                     |    |

| Table 4.6  | Power mode                                                       |    |

| Table 4.7  | The available clock source in VoltageMode                        |    |

| Table 4.8  | Clock gating target block                                        |    |

| Table 4.9  | The initialized or not initialized register by RTC and STOP mode |    |

| Table 4.10 | ACTIVE/SLEEP0 Mode                                               | 64 |

| Table 4.11 | SLEEP1/SLEEP2 Mode                                               |    |

| Table 4.12 | WAIT/WAIT-RETENTION/RETENTION Mode                               |    |

| Table 4.13 | RTC/STOP Mode                                                    |    |

| Table 4.14 | IO buffer function                                               | 71 |

| Table 4.15 | IO control register                                              | 72 |

| Table 4.16 | Wakeup interrupt register                                        |    |

| Table 6.1  | Revision History                                                 |    |

|            |                                                                  |    |

\* All other company names, product names, and service names mentioned herein may be trademarks of their respective companies.

#### Preface

This document provides the specification for the MCU Power Management Unit designed for the TZ1000 Series.

#### **Intended Audience**

This document is intended for the following users.

Driver software developers.

System designers

#### **Conventions in this document**

| • The following notational conventions apply to numbers: |                                                                 |  |

|----------------------------------------------------------|-----------------------------------------------------------------|--|

| Hexadecimal number:                                      | 0xABC                                                           |  |

| Decimal number:                                          | 123 or 0d123 - Only when it should be explicitly indicated that |  |

|                                                          | the number is decimal.                                          |  |

| Binary number:                                           | 0b111 - It is possible to omit the "0b" when the number of      |  |

|                                                          | bit can be distinctly understood from a sentence.               |  |

- Low active signals are indicated with a name suffixed with "\_N".

- A signal is asserted when it goes to its active level while it is deasserted when it goes to its inactive level.

- A set of multiple signals may be referred to as [m:n]. Example: S[3:0] indicates four signals, S3, S2, S1 and S0, collectively.

- In the text, register names are enclosed in brackets []. Example: [ABCD]

- A set of multiple registers, fields or bits of the same type may be described collectively using "n". Example: *[XYZ1], [XYZ2]*, and *[XYZ3]* to *[XYZn]*

- A range of register bits are referred to as [m:n]. Example: [3:0] indicates a range from bit 3 to bit 0.

- Values set in registers are indicated using either a hexadecimal or binary number.

- Example: *[ABCD]*.EFG = 0x01 (hexadecimal), *[XYZn]*.VW = 1 (binary)

- Words and bytes are defined as follows:

| Byte:       | 8 bits   |

|-------------|----------|

| Halfword:   | 16 bits  |

| Word:       | 32  bits |

| Doubleword: | 64 bits  |

• Register bit attributes are defined as follows:

| - Hogister bit at | the defined as follows.                                                       |

|-------------------|-------------------------------------------------------------------------------|

| R:                | Read-only                                                                     |

| W:                | Write-only                                                                    |

| W1C:              | Clear by write of 1 - A write of "1" clears the corresponding bit to 0.       |

| W1S:              | Set by write of 1 - A write of "1" sets the corresponding bit to 1.           |

| R/W:              | Read/Write                                                                    |

| R/W0C:            | Read/Clear by write of 0                                                      |

| R/W1C:            | Read/Clear by write of 1                                                      |

| R/W1S:            | Read/Set by write of 1                                                        |

| RS/WC:            | Set by read/Clear by write - Set after a read and cleared after a data write. |

| - D               | $\cdot$                                                                       |

- Registers only support word access unless otherwise specified.

- Any registers defined as Reserved in the text must not be rewritten. Also, any values read from such registers should not be used.

- Any bits for which default values are defined as "—" would return undefined values if read.

- When a data is written to a register containing both writable and read-only (R) bit fields, its default values should be written to read-only (R) bit fields. For any bit fields with default values defined as "—," refer to the definitions of the relevant register.

- Default values should be written to any reserved bit fields in a write-only register. For any bit fields with default values defined as "—," refer to the definitions of the relevant register.

#### Terms and Abbreviations

These specifications introduce a part of the terms and abbreviation which they used.

| Table 1.1 Terms and abbreviations |                                                                                                                                                                                                    |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Term                              | Description                                                                                                                                                                                        |

| PMU                               | Power Management Unit                                                                                                                                                                              |

| DCG                               | Dynamic Clock Gating                                                                                                                                                                               |

| BOR                               | Brown Out Reset                                                                                                                                                                                    |

| BGR                               | Band Gap Reference                                                                                                                                                                                 |

| LVD                               | Level Voltage Detector                                                                                                                                                                             |

| ADPLL                             | All Digital Phase Locked Loop                                                                                                                                                                      |

| SIOSC                             | Silicon Oscillator                                                                                                                                                                                 |

| PSW                               | Power Switch                                                                                                                                                                                       |

| MCU_SYS_RESET_N                   | HW Reset Pin                                                                                                                                                                                       |

| RetentionFF                       | Two powers of VDDB (regular ON) and VDDC are<br>supplied to the FF which consists of a Set/Reset FF and<br>a latch. Low power consumption is done by the VDDC<br>shut-down at the Retention state. |

| SAVE                              | The signal for holding data to the latch in RetentionFF                                                                                                                                            |

| RSTR                              | The signal for returning the data held in the latch in RetentionFF.                                                                                                                                |

| RetentionSRAM                     | Only memory data is held using the RET/WAIT signal.<br>Two powers of VDDB/VDDC are supplied like<br>RetentionFF, and low power consumption is done by the<br>VDDC shut-down.                       |

| RET                               | The Retention signal used by RetentionSRAM or it may be used as an abbreviation of Retention.                                                                                                      |

| WAIT                              | The Retention signal used by RetentionSRAM<br>The difference from RET is no VDDC shut-down.<br>The power supply of the Row decoder is shut down by<br>PSW in the SRAM.                             |

| WFI (state)                       | It indicates that the WFI, WFE and SEV instruction are executed.                                                                                                                                   |

| Table 1 1 | Torms and | abbreviations |

|-----------|-----------|---------------|

|           | ierms and | appreviations |

### 1. Overview

This document describes about the PMU (Power Management Unit) module. The function outlines are shown as follows.

- Clock control

- Clock source control

- Clock domain

- Clock source selection

- Prescaler (division) function

- Clock gating control

- Dynamic clock gating

- Request for releasing clock gating

- 32.768 kHz Clock out control

- Reset control

- Software reset

- Hardware reset

- WDT reset

- LOCKUP reset

- SYSRESETREQ reset

- Power supply control

- Power supply circuit

- Power supply domain

- Power domain control

- Power supply shut-down control

- Retention control

- Power mode

- Power mode shift sequence

- VoltageMode: Power supply and voltage change control (DVS control)

- PowerMode: Power state control

- Boot sequence

- Power supply sequence

- Start-up sequence

- BrownOut control

- Brown Out interrupt

- Brown Out reset

- IO Control

- IO Buffer control

- IO Retention control

- IO Output Buffer reset control

- IO Input Buffer stand-by control

- WakeUp interrupt control

- EFUSE load function

- Override function

### 2. Block Diagram

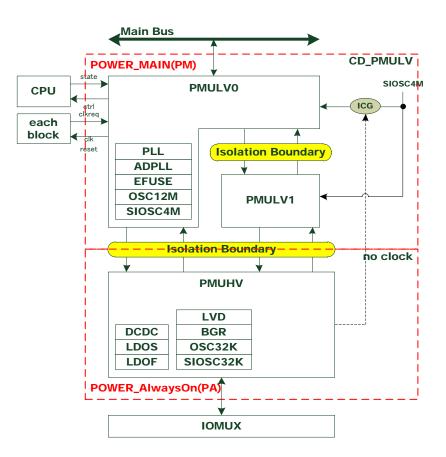

The outline of the internal blocks of this module and a connection relation with each block are shown in Figure 2.1. PMU consists of three blocks, PMUHV, PMULV0, and PMULV1. The PMULV0 and PMULV1 are collectively called PMULV.

Figure 2.1 Block diagram

- PMUHV: It belongs to PA domain (refer to 4.2.2 Power Supply Domain), and there is no clock in this block. This block is always supplied with the power.

- \* OSC32K and SIOSC32K are the clocks for RTC.

- DCDC: Supplies from 1.0 to 1.2 V

- LDOS: Supplies 0.9 V

- LDOF: Supplies 1.8 V for SPI

- LVD: The voltage detector for detecting 3.3 V

- BGR: The block which generates the reference voltage to each LDO and LVD

- PMULV0: It belongs to PM domain (refer to 4.2.2 Power Supply Domain), and operates with PMULV CLK which is driven by SIOSC4M.

- Almost all the functions as PMULV are managed. It has connected with a main bus by APB3 protocol, and has an asynchronous relation.

- PMULV1: It belongs to PM domain (refer to 4.2.2 Power Supply Domain), and operates with PMULV\_CLK which is driven by SIOSC4M.

- The function of a part of PMULV is managed.

### 3. Address Map

| Table 3.1 M          | ICU Power Manag | gement | <b>Unit Register M</b> | lap            |

|----------------------|-----------------|--------|------------------------|----------------|

| Register Name        | Туре            | Width  | Reset Value            | Address Offset |

| CG ON POWERDOMAIN    | RŴ              | 32     | 0x0000 0F82            | 0x0000 0000    |

| CG OFF POWERDOMAIN   | RW              | 32     | 0x0000 003D            | 0x0000 0004    |

| DCG POWERDOMAIN      | RW              | 32     | 0x0000 0000            | 0x0000 0010    |

| SRST ON POWERDOMAIN  | RW              | 32     | 0x0000 0F82            | 0x0000 0020    |

| SRST OFF POWERDOMAIN | RW              | 32     | 0x0000 0021            | 0x0000 0024    |

| CG ON PM 0           | RW              | 32     | 0x0050 0000            | 0x0000 0100    |

| CG ON PM 1           | RW              | 32     | 0x3FA8 AAB7            | 0x0000 0104    |

| CG ON PM 2           | RW              | 32     | 0x0001 0FF1            | 0x0000 0108    |

| CG ON PE             | RW              | 32     | 0x0000 000F            | 0x0000 0110    |

| CG ON PF             | RW              | 32     | 0x0000 0000            | 0x0000 0120    |

| CG ON PD             | RW              | 32     | 0x0000 0001            | 0x0000 0128    |

| CG ON PU             | RW              | 32     | 0x0000 001D            | 0x0000 012C    |

| CG ON PA12           | RW              | 32     | 0x0000 0007            | 0x0000 0134    |

| CG ON PA24           | RW              | 32     | 0x0000 0007            | 0x0000 0138    |

| CG ON PP1            | RW              | 32     | 0x0000 FFF1            | 0x0000 013C    |

| CG ON HARDMACRO      | RW              | 32     | 0x0000 0000            | 0x0000 0140    |

| CG ON REFCLK         | RW              | 32     | 0x0001 0001            | 0x0000 0148    |

| CG OFF PM 0          | RW              | 32     | 0x0F80 0000            | 0x0000 0180    |

| CG OFF PM 1          | RW              | 32     | 0x0000 0000            | 0x0000 0184    |

| CG OFF PM 2          | RW              | 32     | 0x0000 0000            | 0x0000 0188    |

| CG OFF PE            | RW              | 32     | 0x0000 0000            | 0x0000 0190    |

| CG OFF PF            | RW              | 32     | 0x0000 0007            | 0x0000 01A0    |

| CG OFF PD            | RW              | 32     | 0x0000 0000            | 0x0000 01A8    |

| CG OFF PU            | RW              | 32     | 0x0000 0000            | 0x0000 01AC    |

| CG OFF PA12          | RW              | 32     | 0x0000 0000            | 0x0000 01B4    |

| CG_OFF_PA24          | RW              | 32     | 0x0000 0000            | 0x0000 01B8    |

| CG_OFF_PP1           | RW              | 32     | 0x0000 0000            | 0x0000 01BC    |

| CG_OFF_HARDMACRO     | RW              | 32     | 0x0001 0001            | 0x0000 01C0    |

| CG_OFF_REFCLK        | RW              | 32     | 0x0000 0000            | 0x0000 01C8    |

| DCG_PM_0             | RW              | 32     | 0x0000 0000            | 0x0000 0200    |

| DCG_PM_1             | RW              | 32     | 0x0000 0000            | 0x0000 0204    |

| DCG_PM_2             | RW              | 32     | 0x0000 0000            | 0x0000 0208    |

| DCG_PE               | RW              | 32     | 0x0000 0000            | 0x0000 0210    |

| DCG_PF               | RW              | 32     | 0x0000 0000            | 0x0000 0220    |

| DCG_PD               | RW              | 32     | 0x0000 0000            | 0x0000 0228    |

| DCG_PU               | RW              | 32     | 0x0000 0000            | 0x0000 022C    |

| DCG_PA12             | RW              | 32     | 0x0000 0000            | 0x0000 0234    |

| DCG_PA24             | RW              | 32     | 0x0000 0000            | 0x0000 0238    |

| DCG_PP1              | RW              | 32     | 0x0000 0000            | 0x0000 023C    |

| CLKREQ_CONFIG_PE     | RW              | 32     | 0x0002 0002            | 0x0000 0290    |

| SRST_ON_PM_0         | RW              | 32     | 0x0050 0000            | 0x0000 0300    |

| SRST_ON_PM_1         | RW              | 32     | 0x3F08 009F            | 0x0000 0304    |

| SRST_ON_PM_2         | RW              | 32     | 0x0001 0FF1            | 0x0000 0308    |

| SRST_ON_PE           | RW              | 32     | 0x0000 0005            | 0x0000 0310    |

| SRST_ON_PF           | RW              | 32     | 0x0000 0000            | 0x0000 0320    |

| SRST_ON_PD           | RW              | 32     | 0x0000 0001            | 0x0000 0328    |

| SRST_ON_PU           | RW              | 32     | 0x0000 001D            | 0x0000 032C    |

| SRST_ON_PA12         | RW              | 32     | 0x0000 0003            | 0x0000 0334    |

| SRST_ON_PA24         | RW              | 32     | 0x0000 0003            | 0x0000 0338    |

| SRST_ON_PP1          | RW              | 32     | 0x0000 FFF1            | 0x0000 033C    |

| SRST_OFF_PM_0        | RW              | 32     | 0x0900 0000            | 0x0000 0380    |

| SRST_OFF_PM_1        | RW              | 32     | 0x0000 0000            | 0x0000 0384    |

| SRST_OFF_PM_2        | RW              | 32     | 0x0000 0000            | 0x0000 0388    |

| SRST_OFF_PE          | RW              | 32     | 0x0000 0000            | 0x0000 0390    |

| · – – –              | 1               |        |                        |                |

| Table 3.1 | MCU Power Management Unit Register Map |

|-----------|----------------------------------------|

|-----------|----------------------------------------|

|                                  |          |          | I           |                            |

|----------------------------------|----------|----------|-------------|----------------------------|

| SRST_OFF_PF                      | RW       | 32       | 0x0000 000F | 0x0000 03A0                |

| SRST_OFF_PD                      | RW       | 32       | 0x0000 0000 | 0x0000 03A8                |

| SRST_OFF_PU                      | RW       | 32       | 0x0000 0000 | 0x0000 03AC                |

| SRST_OFF_PA12                    | RW       | 32       | 0x0000 0000 | 0x0000 03B4                |

| SRST_OFF_PA24                    | RW       | 32       | 0x0000 0000 | 0x0000 03B8                |

| SRST_OFF_PP1                     | RW       | 32       | 0x0000 0000 | 0x0000 03BC                |

| CTRL MODETRAN                    | RW       | 32       | 0x0000 0000 | 0x0000 0400                |

| CSM MAIN                         | RW       | 32       | 0x0000 0000 | 0x0000 0404                |

| CSM CPUTRC                       | RW       | 32       | 0x0000 0000 | 0x0000 0408                |

| CSM CPUST                        | RW       | 32       | 0x0000 0000 | 0x0000 040C                |

| CSM USBI                         | RW       | 32       | 0x0000 0000 | 0x0000 0410                |

| CSM UARTO                        | RW       | 32       | 0x0000 0000 | 0x0000 0414                |

| CSM UART1                        | RW       | 32       | 0x0000 0000 | 0x0000 0418                |

| CSM UART2                        | RW       | 32       | 0x0000 0000 | 0x0000 041C                |

| CSM ADCC12A                      | RW       | 32       | 0x0000 0000 | 0x0000 0420                |

| CSM ADCC24A                      | RW       | 32       | 0x0000 0000 | 0x0000 0424                |

| PRESCAL MAIN                     | RW       | 32       | 0x0000 0011 | 0x0000 0484                |

| PRESCAL CPUST                    | RW       | 32       | 0x0000 0001 | 0x0000 048C                |

| PRESCAL USBI                     | RW       | 32       | 0x0000 0000 | 0x0000 048C                |

| PRESCAL_USBI                     | RW       | 32       | 0x0000 0000 | 0x0000 0490                |

| PRESCAL_UART1                    | RW       | 32<br>32 | 0x0000 0000 | 0x0000 0494<br>0x0000 0498 |

| PRESCAL_UART1<br>PRESCAL_UART2   | RW       | 32<br>32 | 0x0000 0000 | 0x0000 0498<br>0x0000 049C |

| PRESCAL_UARTZ<br>PRESCAL_ADCC12A | RW       | 32<br>32 | 0x0000 0000 | 0x0000 049C                |

|                                  |          | 32<br>32 |             |                            |

| PRESCAL_ADCC24A                  | RW       |          | 0x0000 0000 | 0x0000 04A4                |

| CONFIG_OSC12M                    | RW       | 32       | 0x0000 0000 | 0x0000 0500                |

| CONFIG_PLL_0                     | RW       | 32       | 0x0000 0001 | 0x0000 0508                |

| CONFIG_PLL_1                     | RW       | 32       | 0x0000 0093 | 0x0000 050C                |

| CONFIG_ADPLL_0                   | RW       | 32       | 0x0000 7008 | 0x0000 0510                |

| CONFIG_ADPLL_1                   | RW       | 32       | 0x0000 0000 | 0x0000 0514                |

| CONFIG_DCDC_LVREG_1              | RW       | 32       | 0x0000 0000 | 0x0000 0528                |

| CONFIG_LDOF_0                    | RW       | 32       | 0x0000 0003 | 0x0000 0530                |

| OVERRIDE_EFUSE_OSC12M            | RW       | 32       | 0x0000 0007 | 0x0000 0580                |

| SELECT_EFUSE                     | RW       | 32       | 0x0000 0000 | 0x0000 05C0                |

| EFUSE_REVISIONID                 | RO       | 32       |             | 0x0000 05DC                |

| EFUSE_BOOTSEQ                    | RO       | 32       | <u> </u>    | 0x0000 05E0                |

| EFUSE_SIOSC4M                    | RO       | 32       | <u> </u>    | 0x0000 05E4                |

| BROWNOUTRESET                    | RW       | 32       | 0x0000 0000 | 0x0000 0600                |

| MOVE_VOLTAGE_START               | RW       | 32       | 0x0000 0000 | 0x0000 0700                |

| MOVE_POWER_VOLTAGE_MODE          | RW       | 32       | 0x0000 0000 | 0x0000 0704                |

| POWERDOMAIN_CTRL                 | RW       | 32       | 0x0000 0000 | 0x0000 0710                |

| POWERDOMAIN_CTRL_MODE            | RW       | 32       | 0x0014 4004 | 0x0000 0714                |

| POWERDOMAIN_CTRL_STATUS          | RO       | 32       | 0x0014 4004 | 0x0000 0718                |

| POWERDOMAIN_CTRL_MODE_FOR_WAI    |          |          |             |                            |

| μ                                | RW       | 32       | 0x0000 03F0 | 0x0000 0720                |

| POWERDOMAIN_CTRL_MODE_FOR_WR     |          | 00       |             | 00000.0704                 |

|                                  | RW       | 32       | 0x00A8 ABF8 | 0x0000 0724                |

| POWERDOMAIN CTRL MODE FOR RET    | RW       | 32       | 0x00A8 AAA8 | 0x0000 0728                |

| VOLTAGEMODE SETTING              | RW       | 32       | 0x0000 0000 | 0x0000 0730                |

| WAITTIME LDOF                    | RW       | 32       | 0x001E 001E | 0x0000 0740                |

| WAITTIME PSW                     | RW       | 32       | 0x000F 000F | 0x0000 0744                |

| WAITTIME DVSCTL                  | RW       | 32       | 0x00A0 1E1E | 0x0000 0748                |

| POWERMODE SLEEP CG ON            | RW       | 32       | 0x0000 0000 | 0x0000 0780                |

| POWERMODE SLEEP PRESCAL          | RW       | 32       | 0x0000 0000 | 0x0000 0790                |

| CG ON PC SCRT                    | RW       | 32       | 0x0000 0000 | 0x0000 1124                |

| CG OFF PC SCRT                   | RW       | 32       | 0x0000 0004 | 0x0000 1124                |

| CG ON PA                         | RW       | 32<br>32 | 0x0000 000B | 0x0000 2000                |

|                                  | RW<br>RW | 32<br>32 |             |                            |

| CG_OFF_PA                        |          |          | 0x0000 0000 | 0x0000 2010                |

| SRST_ON_PA                       | RW       | 32       | 0x0000 0001 | 0x0000 2020                |

| SRST_OFF_PA                      | RW       | 32       | 0x0000 0000 | 0x0000 2030                |

| CSM RTC RW 32 0x00                 | 00 0000 |             |

|------------------------------------|---------|-------------|

|                                    | 00 0000 | 0x0000 2080 |

|                                    | 00 0000 | 0x0000 20C0 |

|                                    | 00 0000 | 0x0000 2100 |

|                                    | 00 0000 | 0x0000 2104 |

|                                    | 00 0001 | 0x0000 2108 |

|                                    | 00 0013 | 0x0000 210C |

|                                    | 00 0003 | 0x0000 2118 |

| CONFIG_LDOM_0 RW 32 0x00           | 00 0000 | 0x0000 2120 |

| CONFIG_LDOM_1 RW 32 0x00           | 00 0003 | 0x0000 2124 |

| CONFIG_LDOS_0 RW 32 0x00           | 00 0000 | 0x0000 2130 |

| CONFIG_LDOS_1 RW 32 0x00           | 00 0003 | 0x0000 2134 |

|                                    | 00 0000 | 0x0000 2180 |

| OVERRIDE_EFUSE_SIOSC32K RW 32 0x00 | 00 0000 | 0x0000 2184 |

| OVERRIDE_EFUSE_SIOSC4M RW 32 0x00  | 00 0000 | 0x0000 2188 |

| OVERRIDE_EFUSE_BGR_0 RW 32 0x00    | 00 0000 | 0x0000 2190 |

| OVERRIDE_EFUSE_BGR_1 RW 32 0x00    | 07 1F00 | 0x0000 2194 |

| STATUS_LVPWR RW 32 0x00            | 00 0000 | 0x0000 2200 |

| STATUS_LVRST RW 32 —               |         | 0x0000 2204 |

| BROWNOUTMODE RW 32 0x00            | 00 0000 | 0x0000 2210 |

| CTRL_IO_AON_0 RW 32 0x00           | 00 0001 | 0x0000 2300 |

| CTRL_IO_AON_1 RW 32 0x00           | 00 0000 | 0x0000 2304 |

| CTRL_IO_AON_2 RW 32 0x00           | 00 0000 | 0x0000 2308 |

| CTRL_IO_AON_3 RW 32 0x00           | 00 0000 | 0x0000 230C |

| CTRL_IO_AON_4 RW 32 0x00           | 00 0001 | 0x0000 2310 |

| CTRL_IO_AON_5 RW 32 0x00           | 00 0000 | 0x0000 2314 |

| CTRL_IO_AON_6 RW 32 0x00           | 00 0000 | 0x0000 2318 |

| PSW_PU RW 32 0x00                  | 00 0000 | 0x0000 2420 |

| PSW_EFUSE RW 32 0x00               | 00 0003 | 0x0000 2440 |

| PSW_PLL RW 32 0x00                 | 00 0000 | 0x0000 2444 |

| PSW_ADPLL RW 32 0x00               | 00 0000 | 0x0000 2448 |

| PSW_IO_USB RW 32 0x00              | 00 0000 | 0x0000 2450 |

| PSW_HARDMACRO RW 32 0x00           | 00 0000 | 0x0000 2454 |

| ISO_PU RW 32 0x00                  | 00 0003 | 0x0000 2520 |

| ISO_EFUSE RW 32 0x00               | 00 0000 | 0x0000 2540 |

|                                    | 00 0003 | 0x0000 2544 |

| ISO_ADPLL RW 32 0x00               | 00 0003 | 0x0000 2548 |

| IRQ_SETTING_0 RW 32 0x00           | 00 0000 | 0x0000 2700 |

| IRQ_SETTING_1 RW 32 0x00           | 00 0000 | 0x0000 2704 |

| IRQ_STATUS RW 32 0x00              | 00 0000 | 0x0000 2708 |

| WAKEUP_EN RW 32 0x00               | 00 0000 | 0x0000 270C |

| WAKEUP_STATUS RO 32 0x00           | 00 0000 | 0x0000 2710 |

| CTRL CDBGPWRUPREQ RW 32 0x00       | 00 0001 | 0x0000 2808 |

### 4. Function

#### 4.1. Clock and Reset

#### 4.1.1. Clock Distribution Diagram

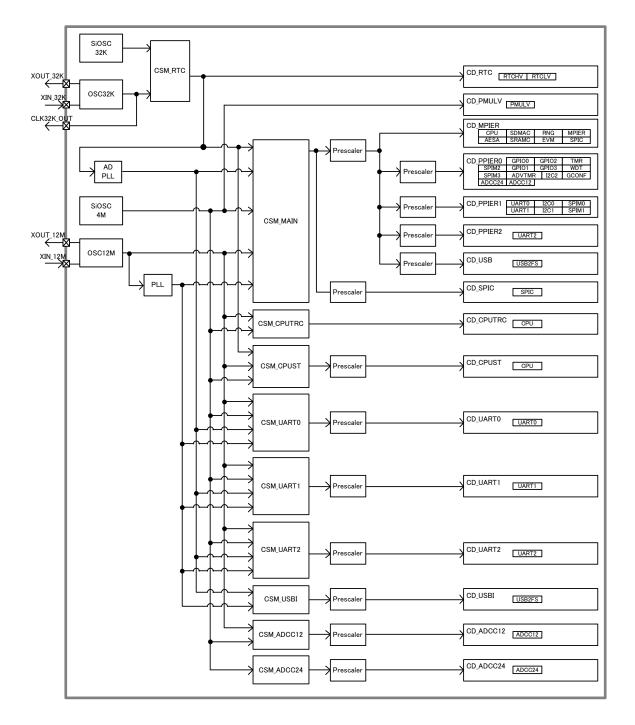

The following figure shows the clock distribution diagram. The clock domain (except for some domains) is constituted by a clock source select circuit and a prescaler. Each block belongs to a clock domain.

- Clock source is selected by the clock source change circuit.

- The selected clock is divided by the prescaler.

The clock source select circuit is common for six domains, CD\_MPIER, CD\_PPIER0, CD\_PPIER1, CD\_PPIER2, CD\_SPIC, and CD\_USB. The prescalers for 5 domains other than CD\_MPIER are using the prescaler output for CD\_MPIER as their clock sources.

#### Figure 4.1 Clock distribution diagram

#### 4.1.2. Clock Source

Six clock sources are included.

- OSC32K

- Attach a crystal oscillator or an oscillation device outside.

- Source oscillating frequency: 32.768 kHz

- SIOSC32K

- A built-in self-oscillation oscillator. Since it is not so accurate compared with an external oscillator, optimization by trimming is required.

- Source oscillating frequency: 32.768 kHz

- SIOSC4M

- A built-in self-oscillation oscillator.

- Since it is not so accurate compared with an external oscillator, optimization by trimming is required.

- Source oscillating frequency: 4 MHz

- ADPLL

- It is All Digital PLL which uses OSC32K or SIOSC32K as the reference clock.

- ADPLL cannot be used unless the reference clock is operating.

- In the case to select SIOSC32K as the reference clock, the USB block is not able to comply with the standard.

- Source oscillating frequency: 48 MHz

- OSC12M

- Attach a crystal oscillator or an oscillation device outside.

- Source oscillating frequency: 12 MHz

- PLL

- It is PLL which uses OSC12M as the reference clock.

- PLL cannot be used unless the reference clock is operating.

- Source oscillating frequency: 12/24/36/48 MHz (Setting available)

#### 4.1.3. Clock Domain

The two following tables summarize the clock source select circuit and the prescaler which constitute the circuits in each clock domain.

| Cleak           |                     | Frequency                 |                    |                               |              | Clock Source | e            |              |      |      |

|-----------------|---------------------|---------------------------|--------------------|-------------------------------|--------------|--------------|--------------|--------------|------|------|

| Clock<br>Domain | Clock Source<br>Mux | (Max/Min)                 | OSC32K<br>SIOSC32K | SIOSC4M                       | ADPLL        | OSC12M       | OSC12M3      | PLL          | PLL3 | PLL9 |

| CD_MPIER        |                     | 48 MHz/32.768 kHz         |                    |                               |              |              |              |              |      |      |

| CD_PPIER0       |                     | 12 MHz/32.768 kHz         |                    |                               |              |              |              |              |      |      |

| CD_PPIER1       | CSM_MAIN            | 12 MHz/32.768 kHz         | ,                  | ,                             | 1            | ,            |              | ,            |      |      |

| CD_PPIER2       |                     | 12 MHz/32.768 kHz         | $\checkmark$       | $\overline{\mathbf{\Lambda}}$ | v            | v            | _            | $\checkmark$ | _    |      |

| CD_SPIC         |                     | 48 MHz/32.768 kHz         |                    |                               |              |              |              |              |      |      |

| CD_USBB         |                     | 48 MHz/24 MHz             |                    |                               |              |              |              |              |      |      |

| CD_RTC          | CSM_RTC             | 32.768 kHz                | $\checkmark$       | _                             |              | —            | —            | _            | —    | —    |

| CD_CPUTRC       | CSM_CPUTRC          | 12 MHz/4 MHz              | —                  | √                             | _            | √            | —            | _            | _    | —    |

| CD_CPUST        | CSM_CPUST           | 12 MHz/32.768 kHz         | √                  | √_                            | _            | √            | —            | _            | _    | _    |

| CD_PMULV        | CSM_PMULV           | 4 MHz                     | —                  | <u>√</u>                      | _            | —            | —            | _            | _    | —    |

| CD_UART0        | CSM_UART0           | 18 MHz/32.768 kHz<br>(*1) | √                  | ⊻                             | √            | √            | —            | ~            | _    | _    |

| CD_UART1        | CSM_UART1           | 18 MHz/32.768 kHz<br>(*1) | √                  | √                             | √            | √            | —            | ~            | —    | _    |

| CD_UART2        | CSM_UART2           | 18 MHz/32.768 kHz<br>(*2) | √                  | √                             | $\checkmark$ | ~            | _            | ~            | _    | _    |

| CD_USBI         | CSM_USB             | 48 MHz                    | _                  | _                             | ~            | _            | _            | >            | —    | —    |

| CD_ADCC12       | CSM_ADCC12          | 12 MHz/1 MHz              | —                  | <u>√</u>                      | √            | √            | √            | √            | √    | √    |

| CD_ADCC24       | CSM_ADCC24          | 4 MHz                     | —                  | √                             | √            | —            | $\checkmark$ | ~            |      | √    |

Note:  $\checkmark$  shows Selectable.

Note:  $\underline{\checkmark}$  shows a clock source which is selectable and is selected at the initial state.

Note: — shows Un-selectable.

Note: OSC12M3 indicates OSC12M divided by 3.

Note: PLL3 indicates PLL divided by 3. When using PLL = 24 MHz, it can use.

Note: PLL9 indicates PLL divided by 9. When using PLL = 36 MHz, it can use.

\*1: When using CD\_PPIER1 = 12 MHz, it is restrained with CD\_UART0/1  $\leq$  5/3 x CD\_PPIER1.

\*2: When using CD\_PPIER2 = 12 MHz, it is restrained with CD\_UART2  $\leq$  5/3 x CD\_PPIER2.

| Clock     |              | Feature                                 | Defau        | It Value              |

|-----------|--------------|-----------------------------------------|--------------|-----------------------|

| Domain    | Clock Gating | Dividing Ratio 1/n                      | Clock Gating | <b>Dividing Ratio</b> |

| CD_MPIER  | $\checkmark$ | n = 1,2,3,4,5,6,7,8,9,10,12,18,24,36,48 | Not Gated    | 1                     |

| CD_PPIER0 | $\checkmark$ | n = 1,2,3,4,5,6,7,8,9,10,12,18,24,36,48 | Gated        | N/A                   |

| CD_PPIER1 | $\checkmark$ | n = 1,2,3,4,5,6,7,8,9,10,12,18,24,36,48 | Gated        | N/A                   |

| CD_PPIER2 | $\checkmark$ | n = 1,2,3,4,5,6,7,8,9,10,12,18,24,36,48 | Gated        | N/A                   |

| CD_SPIC   | $\checkmark$ | n = 1,2,3,4,5,6,7,8,9,10,12,18,24,36,48 | Not Gated    | 1                     |

| CD_USBB   | $\checkmark$ | n = 1, 2                                | Gated        | N/A                   |

| CD_RTC    | N/A          | N/A                                     | N/A          | N/A                   |

| CD_CPUTRC | N/A          | N/A                                     | N/A          | N/A                   |

| CD_CPUST  | $\checkmark$ | n = 1,2,3,4,5,6,7,8,9,10,12,18,24,36,48 | Not Gated    | 1                     |

| CD_PMULV  | N/A          | N/A                                     | N/A          | N/A                   |

| CD_UART0  | $\checkmark$ | n = 1,2,3,4,5,6,7,8,9,10,12,18,24,36,48 | Gated        | N/A                   |

| CD_UART1  | $\checkmark$ | n = 1,2,3,4,5,6,7,8,9,10,12,18,24,36,48 | Gated        | N/A                   |

| CD_UART2  | $\checkmark$ | n = 1,2,3,4,5,6,7,8,9,10,12,18,24,36,48 | Gated        | N/A                   |

| CD_USBI   | √            | n = 1                                   | Gated        | N/A                   |

| Table 4.2 P | Prescaler |

|-------------|-----------|

|-------------|-----------|

| Clock     |              | Feature                                                                                                                                                      |              | Default Value         |  |  |

|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|--|--|

| Domain    | Clock Gating | Dividing Ratio 1/n                                                                                                                                           | Clock Gating | <b>Dividing Ratio</b> |  |  |

| CD_ADCC12 | J            | SIOSC4M: n = 1,2,4<br>OSC12M: n = 1,2,4,6,12<br>OSC12M3: n = 1<br>PLL: n = 2,4,6,8,12,18,24,36,48<br>PLL3: n = 1<br>PLL9: n = 1<br>ADPLL: n = 4,6,8,12,24,48 | Gated        | N/A                   |  |  |

| CD_ADCC24 | ✓            | SIOSC4M: n = 1<br>OSC12M3: n = 1<br>PLL/ADPLL: n = 6,12<br>PLL9: n = 1                                                                                       | Gated        | N/A                   |  |  |

| ClockSource    |                                  |

|----------------|----------------------------------|

| CD_MPIER       |                                  |

| Prescaler(1/1) |                                  |

|                |                                  |

| Prescaler(1/2) |                                  |

| Prescaler(1/3) |                                  |

| •              |                                  |

| •              |                                  |

| Prescaler(1/n) |                                  |

|                | PPIER1/CD_PPIER2/CD_SPIC/CD_USBB |

| *CD_MPIER:di   |                                  |

| Prescaler(1/1) |                                  |

| Prescaler(1/2) |                                  |

| Prescaler(1/3) |                                  |

|                |                                  |

|                |                                  |

|                |                                  |

Figure 4.2 Prescaler output (CD\_MPIER/CD\_PPIER0.1.2/CD\_SPIC/CD\_USBB)

CD\_MPIER : CLKOUT<sub>CD\_MPIER</sub> = f<sub>CSMSEL</sub>/P<sub>PRESCAL</sub> CD\_PPIER0 ·1 ·2/CD\_SPIC/CD\_USBB: CLKOUT = CLKOUT<sub>CD\_MPIER</sub>/P<sub>PRESCAL</sub>

| *fcsmsel   | The clock source frequency supplied by CSM_MAIN                      |

|------------|----------------------------------------------------------------------|

| *Pprescal: | "n" value determined by PRESCAL which can be specified by the domain |

| ClockSource    |  |

|----------------|--|

| Prescaler(1/1) |  |

| Prescaler(1/2) |  |

| Prescaler(1/3) |  |

| Prescaler(1/n) |  |

#### Figure 4.3 Prescaler output (CD\_UART0.1.2/CD\_CPUST/CD\_USBI/CD\_ADCC12.24)

$CLKOUT = f_{CSMSEL}/P_{PRESCAL}$

| *fcsmsel: | The clock source frequency supplied by CSM_MAIN |

|-----------|-------------------------------------------------|

|-----------|-------------------------------------------------|

$P_{PRESCAL}$ : "n" value determined by PRESCAL which can be specified by the domain

#### 4.1.3.1. Maximum operating frequency of each clock domain

Maximum operating frequency of each clock domain is different in each mode of VoltageMode (refer to 4.3.2. VoltageMode), which will be described later. The table below is the maximum operating frequency of each clock domain.

In addition, please check the individual document of each block about the clock constraints of each block.

| Clock Domain |            | Voltag     | eMode      |            |

|--------------|------------|------------|------------|------------|

| CIOCK Domain | ModeA      | ModeB      | ModeC      | ModeD      |

| CD_MPIER     | 48 MHz     | 36 MHz     | 12 MHz     | 4 MHz      |

| CD_PPIER0    | 12 MHz     | 9 MHz      | 4 MHz      | 4 MHz      |

| CD_PPIER1    | 12 MHz     | 9 MHz      | 4 MHz      | 4 MHz      |

| CD_PPIER2    | 12 MHz     | 9 MHz      | 4 MHz      | 4 MHz      |

| CD_SPIC      | 48 MHz     | 36 MHz     | 12 MHz     | 4 MHz      |

| CD_USBB      | 48 MHz     | —          | —          | —          |

| CD_RTC       | 32.768 kHz | 32.768 kHz | 32.768 kHz | 32.768 kHz |

| CD_CPUTRC    | 12 MHz     | 9 MHz      | 4 MHz      | 4 MHz      |

| CD_CPUST     | 12 MHz     | 12 MHz     | 4 MHz      | 1 MHz      |

| CD_PMULV     | 4 MHz      | 4 MHz      | 4 MHz      | 4 MHz      |

| CD_UART0     | 16 MHz     | 12 MHz     | 4 MHz      | 4 MHz      |

| CD_UART1     | 16 MHz     | 12 MHz     | 4 MHz      | 4 MHz      |

| CD_UART2     | 16 MHz     | 12 MHz     | 4 MHz      | 4 MHz      |

| CD_USBI      | 48 MHz     | —          | —          | —          |

| CD_ADCC12    | 12 MHz     | 9 MHz      | 4 MHz      | 4 MHz      |

| CD_ADCC24    | 4 MHz      | 4 MHz      | 4 MHz      | 4 MHz      |

Table 4.3

Maximum operating frequency of each clock domain

\* —: inoperable

#### 4.1.4. Clock Source Control

roshiba

Clock source can starts and stops by software. Each chapter indicates start-up and stop procedures.

#### 4.1.4.1. OSC12M

(Clock start-up procedure)

- (1) The start-up signal is asserted.

- 1 is written to [CONFIG\_OSC12M].

- (2) Wait tSTART until the clock is stabilized Refer to "Technical Data Sheet Hardware Specification 7.5.1 XOSC12M" about tSTART.

- (3) The clock start-up completes.

(Clock stop procedure)

- (1) The start-up signal is deasserted.

- 0 is written to [CONFIG\_OSC12M].OSC12M\_EN.

- (2) The clock stop completes.

#### 4.1.4.2. OSC32K

(Clock start-up procedure)

- (1) The start-up signal is asserted.

- 1 is written to [CONFIG\_OSC32K].OSC32K\_EN.

- (2) Wait tSTART until the clock is stabilized Refer to "Technical Data Sheet Hardware Specification 7.5.2 XOSC32K" about tSTART.

- (3) The boost signal is disabled for low power consumption.

- 1 is written to [CONFIG\_OSC32K]. OSC32K\_BOOST\_DISABLE.

- (4) Wait tSTBL until the clock is stabilized Refer to "Technical Data Sheet Hardware Specification 7.5.2 XOSC32K" about tSTBL.

- (5) The clock start-up completes.

(Clock stop procedure)

- (1) The boost signal is enabled.

- 0 is written to [CONFIG\_OSC32K]. OSC32K\_BOOST\_DISABLE

- (2) The start-up signal is deasserted.

0 is written to [CONFIG\_OSC32K].OSC32K EN

- (3) The clock stop completes.

(Trimming value change procedure)

The trimming value should be changed in the stop state of the clock and the reset state of the used block.

The trimming value can be set up to the EFUSE value or an arbitrary value in the OVERRIDE register. The data indicated to EFUSE is usually used.

\*Refer to 4.7. EFUSE Function, for the EFUSE and OVERRIDE registers.

[In the case of using EFUSE data]

- (1) The clock stop procedure should be performed if the clock is in the state of operating.

- (2) The trimming value indicated to EFUSE is selected.

- 0 is written to [SELECT\_EFUSE].SEL\_EFUSE\_OSC32K.

- (3) The data of (2) is set.

- [OVERRIDE\_EFUSE\_OSC32K] is written.

- The preset value of EFUSE selected by (2) is used as the write data.

- (4) Changing the trimming value is completed.

[In the case of using an arbitrary value in the OVERRIDE register]

- (1) The clock stop procedure should be performed if the clock is in the state of operating.

- (2) The OVERRIDE register is selected.

- 1 is written to [SELECT\_EFUSE].SEL\_EFUSE\_OSC32K.

- (3) OVERRIDE register is set.

- 0b0000 is written to [OVERRIDE\_EFUSE\_OSC32K].OVERRIDE\_EFUSE\_OSC32K\_RSV.

- An arbitrary value is written to [OVERRIDE\_EFUSE\_OSC32K].OVERRIDE\_EFUSE\_OSC32K\_TRIMIN\_VREF\_GMBIAS.

- An arbitrary value is written to [OVERRIDE\_EFUSE\_OSC32K].OVERRIDE\_EFUSE\_OSC32K\_TRIMIN.

- (4) Changing the trimming value is completed.

#### 4.1.4.3. SIOSC4M

Starting or stopping control of SIOSC4M cannot be done by software.

(Trimming value change procedure)

The setting of a trimming value should be performed by software after the Start-up Sequence.

Moreover, after returning from the RTC/STOP state in the power mode mentioned later (refer to 4.3.3.5. RTC/STOP Mode for details), the trimming value needs to be set up again, since it is initialized.

The trimming value can be set up to the EFUSE value or an arbitrary value in the OVERRIDE register. The data indicated to EFUSE is usually used.

\*Refer to 4.7. EFUSE Function, for the EFUSE and OVERRIDE registers.

- (1) OVERRIDE register is selected.

- 1 is written to [SELECT\_EFUSE].SEL\_EFUSE\_SiOSC4M.

- (2) The trimming value is loaded.

1 is written to [CONFIG\_SiOSC4M].SiOSC4M CTRIM LAT.

- (3) When you set the EFUSE data, read the [EFUSE\_SiOSC4M] register. The setting value changes by the state of VoltageMode (4.3.2. VoltageMode) The case of ModeA: uses [EFUSE\_SiOSC4M].EFUSE\_SiOSC4M\_CTRIM\_MODEA. The case of ModeB: uses [EFUSE SiOSC4M].EFUSE SiOSC4M\_CTRIM\_MODEB.

The case of ModeC: uses *[EFUSE\_SIOSC4M]*.EFUSE\_SIOSC4M\_CTRIM\_MODEL.

- The case of ModeD: uses *[EFUSE\_SiOSC4M]*.EFUSE\_SiOSC4M CTRIM MODED.

- (4) OVERRIDE register is set.

- The value of (3) or an arbitrary value is written to [OVERRIDE\_EFUSE\_SiOSC4M].OVERRIDE\_EFUSE\_SiOSC4M\_CTRIM

- The setting value of the register is used as the write data.

- (5) The loading signal of the trimming value is deasserted.

- 0 is written to *[CONFIG\_SiOSC4M]*.SiOSC4M\_CTRIM\_LAT.

#### 4.1.4.4. SIOSC32K

(Clock start-up procedure)

- (1) The start-up signal is asserted.

- 1 is written to [CONFIG\_SIOSC32K].SIOSC32K\_EN.

- (2) Wait tSTASO32Kµs until the clock is stabilized Refer to "Technical Data Sheet Hardware Specification 7.5.2 XOSC32K" about tSTASO32K.

- (3) The clock start-up completes.

(Clock stop procedure)

- (1) The start-up signal is deasserted.

- 0 is written to [CONFIG\_SIOSC32K].SIOSC32K EN.

- (2) The clock stop completes.

(Trimming value change procedure)

The trimming value should be changed in the stop state of the clock and the reset state of the used block.

The trimming value can be set up to the EFUSE value or an arbitrary value in the OVERRIDE register. The data indicated to EFUSE is usually used.

\* Refer to 4.7. EFUSE Function, for the EFUSE and OVERRIDE registers.

[In the case of using EFUSE data]

- (1) The clock stop procedure should be performed if the clock is in the state of operating.

- (2) The trimming value indicated to EFUSE is selected.

- 0 is written to [SELECT\_EFUSE].SEL\_EFUSE\_SIOSC32K.

- (3) The data of (2) is set.

- [OVERRIDE\_EFUSE\_SIOSC32K] is written.

- The preset value of EFUSE selected by (2) is used as the write data.

- (4) Changing the trimming value is completed.

[In the case of using an arbitrary value in the OVERRIDE register]

- (1) The clock stop procedure should be performed if the clock is in the state of operating.

- (2) The OVERRIDE register is selected.

- 1 is written to [SELECT\_EFUSE].SEL\_EFUSE\_SIOSC32K.

- (3) OVERRIDE register is set.

- An arbitrary value is written to [OVERRIDE\_EFUSE\_SIOSC32K].OVERRIDE\_EFUSE\_SIOSC32K\_TRIMIN\_FREQ.

- (4) Changing the trimming value is completed.

#### 4.1.4.5. PLL

(Clock start-up procedure)

- (1) OSC12M used as a reference clock should be started up. Refer to 4.1.4.1. OSC12M for details.

- (2) If the PLL power supply is in the OFF state, the PLL should be supplied with the power according to the power supply procedure before the clock start-up (4.2.3.7. PPLL Domain control).

- (3) The starting signal is changed to the bypass mode.

- 1 is written to [CONFIG\_PLL\_0].PLL\_BP.

- (4) Wait 100 μs.

- (5) The starting signal is changed to the normal mode.

- 0 is written to [CONFIG\_PLL\_0].PLL\_BP.

- (6) Wait 100  $\mu$ s until lock-up.

- (7) The clock start-up is completed.

(Clock stop procedure)

- (1) The starting signal is changed to the bypass mode.

- 1 is written to [CONFIG\_PLL\_0].PLL\_BP.

- (2) When changing the PPLL domain into the power supply OFF state after the clock stop, the power supply shut-down procedure (4.2.3.7. PPLL Domain control) should be performed.

- (3) The reference clock is stopped.

- 0 is written to [CONFIG\_OSC12M].OSC12M\_EN.

\* The procedure of (3) should not be followed when OSC12M as a reference clock is used as clock source of the clock domain.

(Change procedure of the multiplied ratio)

Change of the multiplied ratio should be performed in the state of the clock stop.

- (1) allow the changes made by the software

- 1 is written to *[CONFIG\_PLL\_0]*.PLL\_SWEN.

- (2) The starting signal is changed to the bypass mode.

- 1 is written to [CONFIG\_PLL\_0].PLL\_BP.

- (3) The multiplied ratio is changed.

- The setting value is written to [CONFIG\_PLL\_1].ND.

- (4) Perform (3) of the PLL clock start-up procedure and the subsequent ones.

- (5) don't allow the changes made by the software

- 0 is written to *[CONFIG\_PLL\_0]*.PLL\_SWEN.

#### 4.1.4.6. ADPLL

(Clock start-up procedure)

- (1) The reference clock is either SIOSC32K or OSC32K. The clock source of SIOSC32K or OSC32K should be started up. Refer to 4.1.4. Clock Source Control.

- (2) If the PADPLL domain is in a power supply OFF state, the PADPLL domain is supplied with the power according to a power supply procedure before the clock start-up (4.2.3.8. PADPLL Domain control).

- (3) Set to 32.768 kHz clock for ADPLL refer to 4.1.7. Setting 32.768 kHz clock.

- (4) The starting signal is asserted.

1 is written to [CONFIG\_ADPLL\_0].ENPLL.

- (5) Wait 8 ms until lock-up.

- (6) The clock start-up is completed.

(Clock stop procedure)

- (1) The starting signal is deasserted.

- 0 is written to *[CONFIG\_ADPLL\_0]*.ENPLL.

- (2) When changing the PADPLL domain into a power supply OFF state after the clock stop, the power supply shut-down procedure (4.2.3.8. PADPLL Domain control) should be performed.

- (3) The reference clock is stopped.

- If the reference clock is OSC32K, please refer to 4.1.4.2 OSC32K.

- If the reference clock is SISOC32K, please refer to 4.1.4.4 SIOSC32K.

\* The procedure of (3) should not be followed when 32.768 kHz as a reference clock is used in the RTC block.

(High-speed lock-up procedure)

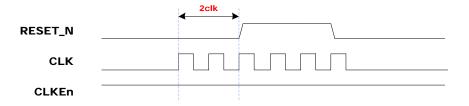

When ADPLL is started, the lock-up time can be shortened. When using this mode, it is necessary to fetch the data (NTWDATA) required for a high-speed lock-up before the stop of ADPLL. ADPLL is always updating and outputting NTWDATA with synchronizing the reference clock (= 32.768 kHz). The data issued by ADPLL is fetched by writing 1 to *[CONFIG\_ADPLL\_1]*. ADPLL\_NTWOUT\_LAT EN.

The value is updated with synchronizing the reference clock when the bit is1. Note that the data used for a high-speed lock-up needs to be one after a lock-up.

Since data fetching is performed with synchronizing the reference clock (= 32.768 kHz) of ADPLL, at least 2 clocks @ 32.768 kHz or more are needed to fetch the data.

\* The stop refers to such as the clock stop and the power supply OFF.

- (1) The starting signal is asserted.

- 1 is written to [CONFIG\_ADPLL\_0].ENPLL.

- (2) Wait 100 ns.

- (3) The fetch signal is asserted.

- 1 is written to [CONFIG\_ADPLL\_1].NTWMODE.

- (4) Wait 100 μs.

- (5) The fetch signal is deasserted.

0 is written to [CONFIG\_ADPLL\_1].NTWMODE.

- (6) Wait 2 ms.

#### (NTW data fetch)

- (1) The fetch signal is asserted after the start-up procedure (4).

- 1 is written to [CONFIG\_ADPLL\_1]. ADPLL\_NTWOUT\_LATEN.

- (2) Wait 2 clocks of the reference clock of the ADPLL.

#### 4.1.5. DFS Control

DFS control is performed by the combination of a clock source change and a prescaler setting. The changing clock source must be done in the state that two clock sources before and after changing are started. When changing clock source, it is necessary that the target clock source is started up and the clock becomes stable in advance. Refer to 4.1.4 Clock Source Control, for the start-up of the clock source.

Depending on the oscillating frequency of the clock source, the setting order of a clock source change and the prescaler setting is changed. The Source oscillating frequency can be checked via a register. Moreover, note that the PLL source oscillating frequency may change according to the set value.

The change of the clock source can be omitted to make only the change of prescaler. The change of the prescaler can be omitted to make only the change of the clock source.

| Control Register                       |       | Control                                                                                                              |  |  |  |  |  |

|----------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [CSM_****]                             | Write | The target clock source is specified. For detail, refer to Register specification.                                   |  |  |  |  |  |

|                                        | Read  | The setting value which is written can be read.                                                                      |  |  |  |  |  |

| [PRESCAL_****]                         | Write | The setting value of the dividing ration of the frequency is specified. Refer to Register specification for details. |  |  |  |  |  |

| [************************************* | Read  | The setting value which is written can be read.                                                                      |  |  |  |  |  |

Refer to the Reference Manual of each block about some constraints and necessary procedures of it by the change of frequency. It means that there is no constraints about the block described below.

- Refer to the Chapter 5 of the latest TZ1000 Series Reference Manual MCU Processor and core peripherals.

- Refer to the Chapter 4.11 of the latest TZ1000 Series Reference Manual MCU SPI Flash Controller.

- Refer to the Chapter 4.2.3 of the latest TZ1000 Series Reference Manual MCU SRAM Controller.

- Refer to the Chapter 4.3.1 of the latest TZ1000 Series Reference Manual MCU 12-bit Analog to Digital Converter.

- Refer to the Chapter 4.3.1 of the latest TZ1000 Series Reference Manual MCU 24-bit Analog to Digital Converter.

- Refer to the Chapter 5.2.1 of the latest TZ1000 Series Reference Manual MCU USB Device controller.

- Refer to the Chapter 4.5 of the latest TZ1000 Series Reference Manual MCU AES Accelerator.

- Refer to the Chapter 4.4 of the latest TZ1000 Series Reference Manual MCU Random Number Generator.

- Refer to the Chapter 5.14.1 of the latest TZ1000 Series Reference Manual MCU I<sup>2</sup>C Master/Slave Interface.

- Refer to the Chapter 5.7.1 of the latest TZ1000 Series Reference Manual MCU Universal asynchronous receiver/transmitter.

- Refer to the Chapter 5.5.1 of the latest TZ1000 Series Reference Manual MCU Timer/Counter.

- Refer to the Chapter 5.11.1 of the latest TZ1000 Series Reference Manual MCU Advanced Timer/Counter.

- Refer to the Chapter 5.4.1 of the latest TZ1000 Series Reference Manual MCU Watchdog Timer.

- Refer to the Chapter 4.9.3 of the latest TZ1000 Series Reference Manual MCU Real Time Clock Counter.

- Refer to the Chapter 6.3 of the latest TZ1000 Series Reference Manual MCU Event Control Block.

(When changed to a low clock source from a high clock source oscillating frequency)

- (1) The clock source is changed.

- [CSM\_\*\*\*\*].CSMSEL\_\*\*\*\* is written.

- (2) The prescaler is changed.

- [PRESCAL\_\*\*\*\*].PRESEL\_\*\*\*\* is written.

(When changed to a high clock source from a low clock source oscillating frequency)

- (1) The prescaler is changed.

- [PRESCAL\_\*\*\*\*].PRESEL\_\*\*\*\* is written.

- (2) The clock source is changed.

- [CSM\_\*\*\*\*].CSMSEL\_\*\*\*\* is written.

#### 4.1.6. Clock Source Change for CPU TraceClock

The following procedure is needed for changing the CSM\_CPUTRC. Although the SIOSC4M is always operating, the OSC12M may stop. When the change target is the OSC12M, perform starting it up in advance.

(The change to the OSC12M from the SIOSC4M)

- (1) The CPU TraceClock supply is stopped.

- 1 is written to [CG\_ON\_PC\_SCRT]. CG\_cputrcclk\_cpu\_traceclk.

- (2) The clock source is changed to the OSC12M.

- 1 is written to [CSM\_CPUTRC].CSMSEL\_CPUTRC.

- (3) The CPU TraceClock supply is resumed.

- 1 is written to [CG\_OFF\_PC\_SCRT]. CG\_cputrcclk\_cpu\_traceclk.

(The change to the SIOSC4M from OSC12M)

- (1) The CPU TraceClock supply is stopped.

- 1 is written to [CG\_ON\_PC\_SCRT]. CG\_cputrcclk\_cpu\_traceclk.

- (2) The clock source is changed to the SIOSC4M.

- 0 is written to [CSM\_CPUTRC].CSMSEL\_CPUTRC.

- (3) The CPU TraceClock supply is resumed.

- 1 is written to [CG\_OFF\_PC\_SCRT]. CG\_cputrcclk\_cpu\_traceclk.

- (4) The OSC12M is stopped if it is not used in other blocks.

- Refer to 4.1.4. Clock Source Control, for the clock stop procedure.

#### 4.1.7. Setting 32.768 kHz clock

Refer to 4.1.4. Clock Source Control, for the start-up procedure of the clock source.

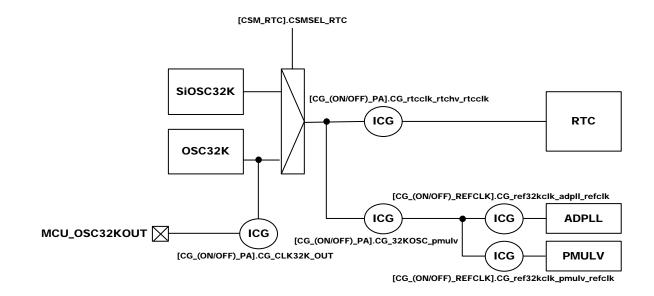

Figure 4.4 Peripheral circuit structure of the CSM\_RTC

Before changing, the reset or clock gating should be performed to the modules which are operating with the 32.768 kHz clock. Start-up of the target clock source should be also performed in advance.

(The change to the SIOSC32K from OSC32K)

- (1) The clock supply after selection of the OSC32K and the SIOSC32K is stopped before the change.