# TB67H302HG

# **Usage considerations**

## Summary

The TB67H302HG is a dual H-bridge driver for a DC brush motor. Either the direct PWM mode or the constant current PWM mode may be selected.

# Contents

| Summ  | nary                                                   | 1  |

|-------|--------------------------------------------------------|----|

| Conte | nts                                                    | 2  |

| 1.    | Power supply                                           | 3  |

| 2.    | Output current                                         | 3  |

| 3.    | Output ON-Resistance                                   | 3  |

| 4.    | Output Residual Voltage                                | 3  |

| 5.    | Control input                                          | 3  |

| 6.    | Input/Output function                                  | 4  |

| 7.    | Selection of Direct PWM mode/Constant current PWM mode | 5  |

| 8.    | Power dissipation                                      | 6  |

| 9.    | Application circuit                                    | 7  |

| 10.   | Short-Circuits between adjacent pins in the TB67H302HG | 11 |

| REST  | RICTIONS ON PRODUCT USE 1                              | 2  |

|       |                                                        |    |

### 1. Power supply

### (1) Operating range of power supply voltage

| Characteristics      | Symbol          | Operating voltage range | Unit |

|----------------------|-----------------|-------------------------|------|

| Power supply voltage | V <sub>CC</sub> | 8 to 42                 | V    |

Ensure that the power supply voltage does not exceed 42V which is the upper limit of the operating range of Vcc, although the absolute maximum rating of Vcc is 50V.

#### (2) Power on/Shut down sequence

Before applying VCC, set STBY = L (standby mode) or IN1A= IN1B= IN2A= IN2B=L to avoid a malfunction. Before shutdown, also set STBY = L (standby mode) or IN1A= IN1B= IN2A= IN2B=L.

## 2. Output current

The absolute maximum rating is 5.0 A per phase, and the upper limit of operating current is 4.5 A per phase. The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Do not exceed any of these ratings.

The average permissible current is restricted by total power dissipation. Please use the IC within the range of the power dissipation.

## 3. Output ON-Resistance

Output ON-resistances for H-bridge: 0.4  $\Omega$  typical and 0.6  $\Omega$  maximum (upper and lower sum) with a test condition of the  $I_{out}$  = 4.0 A

## 4. Output Residual Voltage

The residual voltages of the ALERT1 and ALERT2 output pins are up to 0.5 V each where Io = 1 mA.

## 5. Control input

### (1) Input IN1, IN2, and PWM signals

Output mode can be chosen by IN1, IN2, or PWM input.

Input signals of the 3 V system can also be acceptable to control the IC because  $V_{IN}$  (H) is 2.2 V and  $V_{IN}$  (L) is 0.8 V.

Pull down resistor of 100 k $\Omega$  (typ.) is incorporated.

## (2) STBY input

All output transistors are off by setting STBY pin to low level (standby mode).

Input signals of the 3 V system can also be acceptable to control the IC because  $V_{IN}$  (H) is 2.2 V and  $V_{IN}$  (L) is 0.8 V.

The status of the IC becomes a standby mode when the input is open because a pull down resistor of 100  $k\Omega$  (typ.) is incorporated,

### (3) V<sub>ref</sub> input

In the constant current PWM mode, the voltage which corresponds to the desired current should be applied to VrefA and VrefB terminal.

In the direct PWM mode, both of VrefA terminal and VrefB terminal should be connected to SGND.

# 6. Input/Output function

# SELECT = L (Direct PWM mode)

|    | Inj  | out  |     | Output |      |                 |  |  |  |  |  |  |

|----|------|------|-----|--------|------|-----------------|--|--|--|--|--|--|

| SB | IN1  | IN2  | PWM | OUT1   | OUT2 | Mode            |  |  |  |  |  |  |

| н  | н    | н    | Н   | L      | L    | Short brake     |  |  |  |  |  |  |

|    |      |      | L   | E.     | E    |                 |  |  |  |  |  |  |

| н  | L    | н    | Н   | L      | Н    | Forward/Reverse |  |  |  |  |  |  |

|    |      |      | L   | L      | L    | Short brake     |  |  |  |  |  |  |

| н  | н    |      | Н   | Н      | L    | Reverse/Forward |  |  |  |  |  |  |

| п  | п    | L    | L   | L      | L    | Short brake     |  |  |  |  |  |  |

|    | L    |      | Н   |        | FF   | Stor            |  |  |  |  |  |  |

| Н  | L    | L    | L   | (H     | i-Z) | Stop            |  |  |  |  |  |  |

|    | 11/1 | 11/1 | Н   |        | FF   | Otomoliku       |  |  |  |  |  |  |

| L  | H/L  | H/L  | L   | (H     | i-Z) | Standby         |  |  |  |  |  |  |

# SELECT = H (Constant current PWM mode)

|    | I      | nput  |                     | Output |             |                                              |  |  |  |  |  |

|----|--------|-------|---------------------|--------|-------------|----------------------------------------------|--|--|--|--|--|

| SB | IN1    | IN2   | PWM                 | OUT1   | OUT2        | Mode                                         |  |  |  |  |  |

| н  | н      | н     | Н                   | 1      | I           | Short brake                                  |  |  |  |  |  |

|    | 11     | 11    | L                   | L      | L           | Short blake                                  |  |  |  |  |  |

| н  | L      | н     | Н                   | L      | н           | Constant current PWM, Forward<br>(OUT2→OUT1) |  |  |  |  |  |

|    |        |       | L                   | L      | Short brake |                                              |  |  |  |  |  |

| н  | н      | L     | Н                   | Н      | L           | Constant current PWM, Reverse<br>(OUT1→OUT2) |  |  |  |  |  |

|    |        |       | L                   | L      | L           | Short brake                                  |  |  |  |  |  |

| н  |        |       | L L H OFF<br>(Hi-Z) |        | Stop        |                                              |  |  |  |  |  |

| П  | L      | L     | L                   | (□     | I-∠)        | Сюр                                          |  |  |  |  |  |

| L  | H/L    | H/L   | Н                   | -      | FF<br>i-Z)  | Standby                                      |  |  |  |  |  |

| L  | · // L | 1 I/L | L                   | (Th    | i-∠)        | Glandby                                      |  |  |  |  |  |

# 7. Selection of Direct PWM mode/Constant current PWM mode

SELECT = L: operating direct PWM, SELECT = H: operating constant-current PWM

- (1) In case of direct PWM:

- $\cdot$  RSA should be connected to PGNDA.

- RSB should be connected to PGNDB.

- $\boldsymbol{\cdot}$  Vref A and Vref B should be connected to SGND.

(2) In case of constant-current PWM:

- $\cdot$  RSA and RSB should be connected to current detection resistors RNFA and RNFB respectively.

- Configuration of output current is as follows;

- Ach  $Io = (1/3 \times VrefA) \div RNFA$

- Bch Io =  $(1/3 \times VrefB) \div RNFB$

The average current tends to be lower than the setting current because of the peak current detection system.

Set RNFA, RNFB, VrefA and VrefB as follows;  $0.11\Omega \leq RNFA \leq 0.5\Omega, \ 0.11\Omega \leq RNFB \leq 0.5\Omega, \ 0.3V \leq VrefA \leq 1.95V \text{ and } 0.3V \leq VrefB \leq 1.95V$

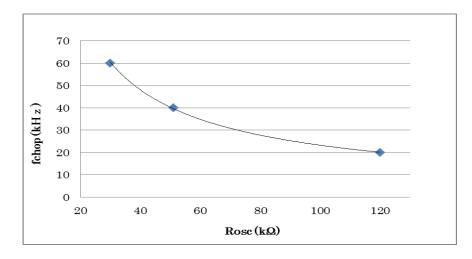

Triangle wave is generated internally by CR oscillation by connecting external resistor to OSC terminal. Rosc should be from  $30k\Omega$  to  $120k\Omega$ . The relation of Rosc and fchop is shown in below table and figure approximately. The values of fchop of the below table are just design target values. They are not tested for pre-shipment.

| Rosc(kΩ) | fchop(kHz) |      |     |  |  |  |  |  |  |  |  |  |  |

|----------|------------|------|-----|--|--|--|--|--|--|--|--|--|--|

|          | Min        | Тур. | Max |  |  |  |  |  |  |  |  |  |  |

| 30       | -          | 60   | -   |  |  |  |  |  |  |  |  |  |  |

| 51       | -          | 40   | -   |  |  |  |  |  |  |  |  |  |  |

| 120      | -          | 20   | -   |  |  |  |  |  |  |  |  |  |  |

## 8. Power dissipation

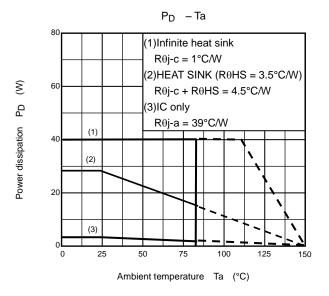

PD-Ta curve of the TB67H302HG in each mounted condition are shown below.

Power consumption-in-each-excitation mode is calculated at a rough estimate as follows;

#### **PWM Duty = 100%**

$P = V_{CC} \times I_{CC} + I_{O}^2 \times Ron (U + L) \times Number of phases$

The higher the ambient temperature is, the lower the power dissipation becomes.

Thermal performances should be planned to allow a significant margin by referring to the PD-Ta characteristic data.

The relation between an ambient temperature and a junction temperature is calculated by the formula below. Be sure to set the junction temperature 150°C or less.

$Tj = P \times R_{th (j-a)} + Ta$

$R_{th \; (j \cdot a)}$  . Thermal resistance between junction and ambient temperature

Ta: Ambient temperature

Pay attention that Rth (j-a) depends on the usage circumstances (ex. mounted board).

#### **PWM drive**

$P = V_{CC} \times I_{CC} + I_0^2 \times Ron (U + L) \times duty \times Number of phases$

Vcc = Power supply voltage (V) Icc = Consumption current of control system (A) Ron (U + L) = Output ON resistance (Upper + Lower) (Ω) Io = Output current (A) duty = Duty (%) Number of phases = 2 phases (In a practical use, there must be some switching losses.)

Please confirm the operation in the actual conditions because thermal characteristics depend on the thermal performance of the board and the transient characteristics in the mounted state.

Heat radiation can be improved by laying out the GND pattern of the print circuit board widely. If necessary, a heat sink should be installed for further improvement of the heat radiation.

# TOSHIBA

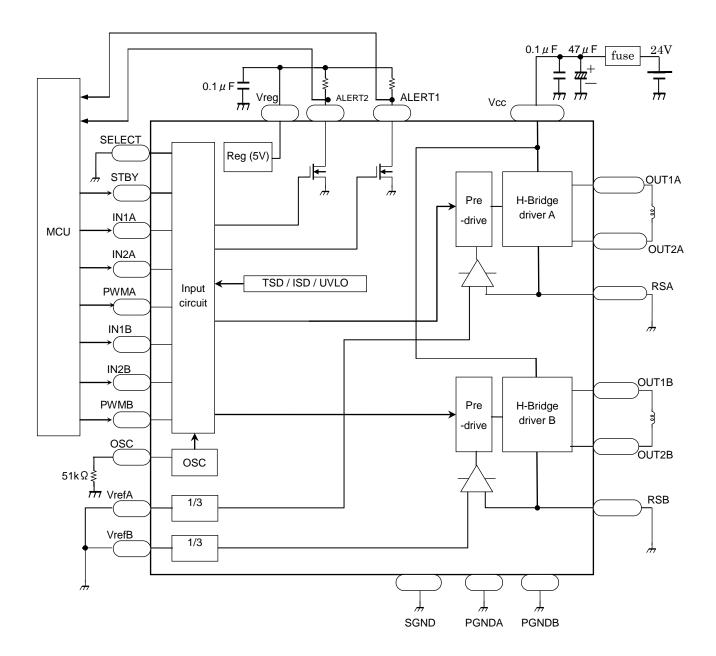

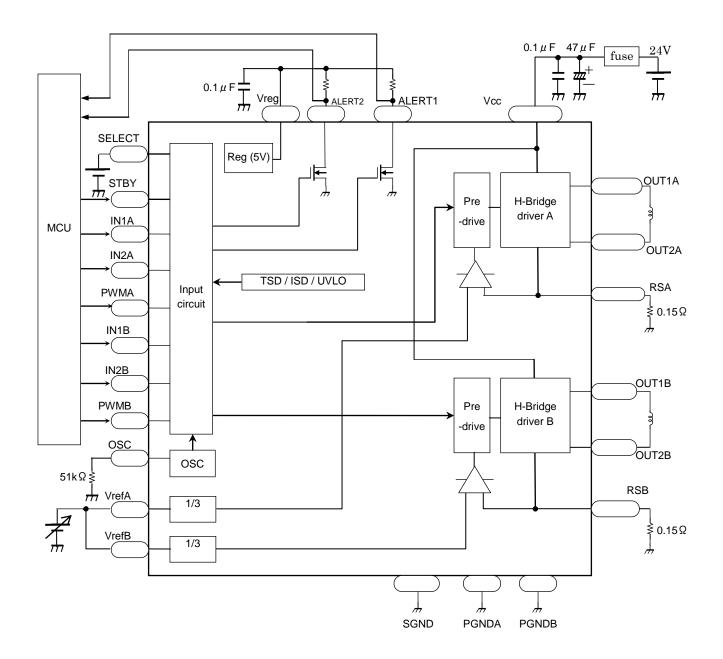

# 9. Application circuit

### (1)Direct PWM

Set SELECT "L" in direct PWM drive.

RSA should be connected to PGNDA. RSB should be connected to PGNDB.

VrefA and VrefB should be connected to SGND each.

# TOSHIBA

Note 1: Generally, some ICs are highly sensitive to electrostatic discharge. When handling them, ensure that the environment is protected against electrostatic discharge.

- Note 2: Capacitors for the power supply lines should be connected as close to the IC as possible.

- Note 3: Pay attention for wire layout of PCB not to allow GND line to have large common impedance.

- Note 4: External capacitor connecting to Vreg should be 0.1µF. Pay attention for the wire between this capacitor and Vreg terminal and the wire between this capacitor and SGND not to be influenced by noise.

- Note 5: The IC may not operate normally when large common impedance is existed in GND line or the IC is easily influenced by noise. For example, if the IC operates continuously for a long time under the circumstance of large current and high voltage, the output according to the input control signal may be different from the I/O function table of this document. And so, the IC may not operate normally. To avoid this malfunction, make sure to conduct Note.2 to Note.4 and evaluate the IC enough before using the IC.

- Note 6: Utmost care is necessary in the design of the power supply lines, GND lines, and output lines since the IC may be destroyed by short-circuiting between outputs, air contamination faults, or faults due to improper grounding, or by short-circuiting between contiguous pins. They may destroy not only the IC but also peripheral parts and may contribute to injuries for users. Over current may continue to flow in the IC because of this destruction and cause smoke or ignition of the IC. Expect the volume of this over current and add an appropriate power supply fuse in order to minimize the effects of the over current. Capacity of the fuse, fusing time, and the inserting position in the circuit should be configured suitably.

- Note 7: The power supply voltage of 42 V and the output current of 4.5 A are the upper limits of the operating range. Therefore, make sure to have enough margins within these operating ranges (derating design) by considering the power supply variation, the external resistance, and the electrical characteristics of the IC. If either of the voltage or current exceeds the upper limits of the operating range, the IC may not operate normally.

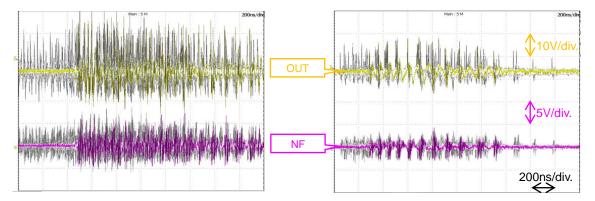

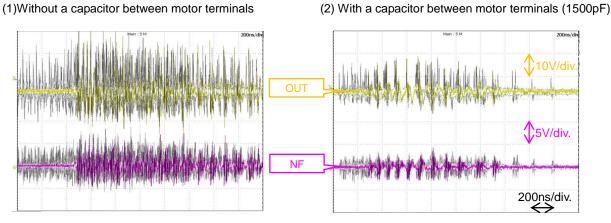

- Note 8: As for a brush motor, the noise, which is generated from the brushes in the motor during the motor rotation, influences on the IC operation. For example, it may cause a malfunction of the ISD circuit and then finally the IC may not work normally. In this case, connect a capacitor between the motor terminals in order to reduce the noise.

The appropriate value of the capacitor depends on the magnitude of the noise and the inductance of the motor coil. Please determine the value according to each actual equipment and condition. The connecting position of the capacitor should be conformed because the effect of the capacitor is different depending on the position of the capacitor which is near the IC or the motor.

For your information, example waveforms are shown as follows to check an amount of noise depending on whether with a capacitor or not.

(2) With a capacitor between motor terminals (1500pF)

(This is an example experiment with the condition under which noise can be generated frequently on purpose.)

(2)Constant current PWM

Set SELECT "H" in constant-current PWM drive.

RSA should be connected to PGNDA via RNFA. RSB should be connected to PGNDB via RNFB. Output current is set as follows;

Ach Io =  $(1/3 \times VrefA) \div RNFA$

Bch  $Io = (1/3 \times VrefB) \div RNFB$

Set RNFA, RNFB, VrefA and VrefB as follows;  $0.11\Omega \leq RNFA \leq 0.5\Omega, \ 0.11\Omega \leq RNFB \leq 0.5\Omega, \ 0.3V \leq VrefA \leq 1.95V$  and  $0.3V \leq VrefB \leq 1.95V$

# TOSHIBA

- Note 1: Generally, some ICs are highly sensitive to electrostatic discharge. When handling them, ensure that the environment is protected against electrostatic discharge.

- Note 2: Capacitors for the power supply lines should be connected as close to the IC as possible.

- Note 3: Current detection resistance (RNF) should be connected as close as the IC as possible.

- Note 4: Pay attention for wire layout of PCB not to allow GND line to have large common impedance.

- Note 5: External capacitor connecting to Vreg should be 0.1µF. Pay attention for the wire between this capacitor and Vreg terminal and the wire between this capacitor and SGND not to be influenced by noise.

- Note 6: The IC may not operate normally when large common impedance is existed in GND line or the IC is easily influenced by noise. For example, if the IC operates continuously for a long time under the circumstance of large current and high voltage, the output according to the input control signal may be different from the I/O function table of this document. And so, the IC may not operate normally. To avoid this malfunction, make sure to conduct Note.2 to Note.5 and evaluate the IC enough before using the IC.

- Note 7: Utmost care is necessary in the design of the power supply lines, GND lines, and output lines since the IC may be destroyed by short-circuiting between outputs, air contamination faults, or faults due to improper grounding, or by short-circuiting between contiguous pins. They may destroy not only the IC but also peripheral parts and may contribute to injuries for users. Over current may continue to flow in the IC because of this destruction and cause smoke or ignition of the IC. Expect the volume of this over current and add an appropriate power supply fuse in order to minimize the effects of the over current. Capacity of the fuse, fusing time, and the inserting position in the circuit should be configured suitably.

- Note 8: The power supply voltage of 42 V and the output current of 4.5 A are the upper limits of the operating range. Therefore, make sure to have enough margins within these operating ranges (derating design) by considering the power supply variation, the external resistance, and the electrical characteristics of the IC. If either of the voltage or current exceeds the upper limits of the operating range, the IC may not operate normally.

- Note 9: As for a brush motor, the noise, which is generated from the brushes in the motor during the motor rotation, influences on the IC operation. For example, it may cause a malfunction of the ISD circuit and then finally the IC may not work normally. In this case, connect a capacitor between the motor terminals in order to reduce the noise. The appropriate value of the capacitor depends on the magnitude of the noise and the inductance of the motor coil. Please determine the value according to each actual equipment and condition. The connecting position of the capacitor should be conformed because the effect of the capacitor is different depending on the position of the capacitor which is near the IC or the motor.

For your information, example waveforms are shown as follows to check an amount of noise depending on whether with a capacitor or not.

(This is an example experiment with the condition under which noise can be generated frequently on purpose.)

## 10. Short-Circuits between adjacent pins in the TB67H302HG

In the TB67H302HG, the term "adjacent pin" includes a pin diagonally closest to a given pin. For example, pin 3 has four adjacent pins: 1, 2, 4 and 5.

Depending on the specified voltage and current, a large current might abruptly flow through the TB67H302HG in case of a short-circuit between any adjacent pins that are listed below. If the large current persists, it may lead to a smoke emission.

- 1) Pins 14 and 15

- 2) Pins 15 and 16

Therefore, to avoid a continuous overcurrent due to the above-described short-circuit and allow the TB67H302HG to be fail-safe, an appropriate fuse should be added at the right place, or overcurrent shutdown circuitry should be added to the power supply. The rated current of a fuse may vary depending on actual applications and its characteristics. Thus, an appropriate fuse must be selected experimentally.

We confirmed that some adjacent terminals may lead to smoke or burst as a result of our short-circuit test between adjacent terminals without fuse. These adjacent terminals are indicated by a table below.

|            |        |    | Pin No., Pin symbol |        |            |        |            |        |            |        |        |       |            |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

|------------|--------|----|---------------------|--------|------------|--------|------------|--------|------------|--------|--------|-------|------------|------------|------------|-----------------|-----|-------|-------|--------|------|--------|-----------------|------|-----|------|--------|

|            |        |    | ALERT1              | SGND   | SELECT     | VrefA  | VrefB      | Vcc    | STBY       | IN1B   | IN2B   | OUT2B | RSB        | OUT1B      | PGNDB      | OUT2A           | RSA | OUT1A | PGNDA | IN1A   | IN2A | Vcc    | PWMA            | PWMB | osc | Vreg | ALERT2 |

| _          |        |    | 1                   | 2      | 3          | 4      | 5          | 6      | 7          | 8      | 9      | 10    | 11         | 12         | 13         | 14              | 15  | 16    | 17    | 18     | 19   | 20     | 21              | 22   | 23  | 24   | 25     |

|            | ALERT1 | 1  | $\searrow$          |        |            |        |            |        |            |        |        |       |            |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

|            | SGND   | 2  | 0                   | $\geq$ |            |        |            |        |            |        |        |       |            |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

|            | SELECT | 3  | 0                   | 0      | $\searrow$ |        |            |        |            |        |        |       |            |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

|            | VrefA  | 4  |                     | 0      | 0          | $\geq$ |            |        |            |        |        |       |            |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

|            | VrefB  | 5  |                     |        | 0          | 0      | $\searrow$ |        |            |        |        |       |            |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

|            | Vcc    | 6  |                     |        |            | 0      | 0          | $\geq$ |            |        |        |       |            |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

|            | STBY   | 7  |                     |        |            |        | 0          | 0      | $\searrow$ |        |        |       |            |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

|            | IN1B   | 8  |                     |        |            |        |            | 0      | 0          | $\geq$ |        |       |            |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

|            | IN2B   | 9  |                     |        |            |        |            |        | 0          | 0      | $\geq$ |       |            |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

| _          | OUT2B  | 10 |                     |        |            |        |            |        |            | Ο      | 0      |       |            |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

| Pin symbol | RSB    | 11 |                     |        |            |        |            |        |            |        | 0      | 0     | $\searrow$ |            |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

| ı sy       | OUT1B  | 12 |                     |        |            |        |            |        |            |        |        | 0     | Ο          | $\searrow$ |            |                 |     |       |       |        |      |        |                 |      |     |      |        |

|            | PGNDB  | 13 |                     |        |            |        |            |        |            |        |        |       | 0          | 0          | $\searrow$ |                 |     |       |       |        |      |        |                 |      |     |      |        |

| Pin No.,   | OUT2A  | 14 |                     |        |            |        |            |        |            |        |        |       |            | Ο          | 0          | $\overline{\ }$ |     |       |       |        |      |        |                 |      |     |      |        |

| Ŀ.         | RSA    | 15 |                     |        |            |        |            |        |            |        |        |       |            |            | 0          | Δ               | /   |       |       |        |      |        |                 |      |     |      |        |

|            | OUT1A  | 16 |                     |        |            |        |            |        |            |        |        |       |            |            |            | 0               | Δ   | Ϊ     |       |        |      |        |                 |      |     |      |        |

|            | PGNDA  | 17 |                     |        |            |        |            |        |            |        |        |       |            |            |            |                 | 0   | 0     | Ϊ     |        |      |        |                 |      |     |      |        |

|            | IN1A   | 18 |                     |        |            |        |            |        |            |        |        |       |            |            |            |                 |     | 0     | 0     | $\geq$ |      |        |                 |      |     |      |        |

|            | IN2A   | 19 |                     |        |            |        |            |        |            |        |        |       |            |            |            |                 |     |       | О     | 0      | /    |        |                 |      |     |      |        |

|            | Vcc    | 20 |                     |        |            |        |            |        |            |        |        |       |            |            |            |                 |     |       |       | 0      | О    | $\geq$ |                 |      |     |      |        |

|            | PWMA   | 21 |                     |        |            |        |            |        |            |        |        |       |            |            |            |                 |     |       |       |        | О    | 0      | $\overline{\ }$ |      |     |      |        |

|            | PWMB   | 22 |                     |        |            |        |            |        |            |        |        |       |            |            |            |                 |     |       |       |        |      | 0      | 0               |      |     |      |        |

|            | OSC    | 23 |                     |        |            |        |            |        |            |        |        |       |            |            |            |                 |     |       |       |        |      |        | 0               | 0    |     |      |        |

|            | Vreg   | 24 |                     |        |            |        |            |        |            |        |        |       |            |            |            |                 |     |       |       |        |      |        |                 | 0    | 0   |      |        |

|            | ALERT2 | 25 |                     |        |            |        |            |        |            |        |        |       |            |            |            |                 |     |       |       |        |      |        |                 |      | 0   | 0    |        |

(Legend) O: No smoking, firing, burst.

$\Delta$ : Possibility to smoke or burst.

# **RESTRICTIONS ON PRODUCT USE**

- Toshiba Corporation, and its subsidiaries and affiliates (collectively "TOSHIBA"), reserve the right to make changes to the information in this document, and related hardware, software and systems (collectively "Product") without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any

applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.