Weight: 0.137 (g)

TOSHIBA CD Process Integrated Circuit Silicon Monolithic

**TC78S122FTG**

## PWM Chopper Type Dual-Stepping Motor Driver

The TC78S122FTG is a PWM chopper type dual-stepping motor driver.

Two stepping motor drivers can drive up to four brushed DC motors. Incorporating two pairs of H-bridge drivers, the TC78S122FTG can drive two DC motors or a single stepping motor.

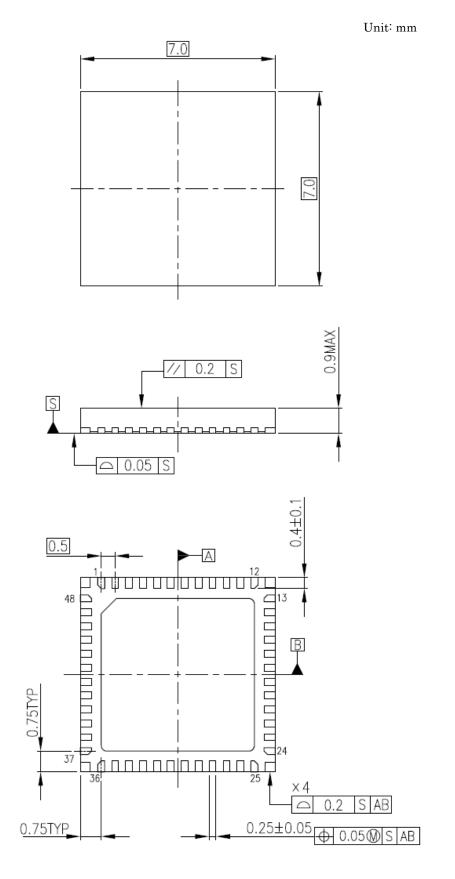

# QFN48-P-0707-0.50

## Features

- Single-chip motor driver for bipolar stepping motor control

- Monolithic IC structured by CD process.

- Low ON-resistance:  $R_{on} = 0.6 \Omega$

In large mode, ON-resistance of combined H-bridges ( $R_{on}$ ) is 0.3  $\Omega$ .

- Over-current detection (ISD), thermal shutdown (TSD) and V<sub>M</sub> power-on reset circuits

- Since the IC incorporates the V<sub>CC</sub> regulator for internal circuit operation, an external power supply (5 V) is not required.

- Package: QFN48

- Maximum output withstand voltage: 40 V (max)

- Output current: 2.0 A (max) in DC Motor (S) mode; 1.5 A (max) in Stepping Motor (S) mode

- Chopping frequency can be set by external capacitor and resistor. High-speed chopping is possible at 100 kHz or higher.

© 2016-2017 Toshiba Electronic Devices & Storage Corporation

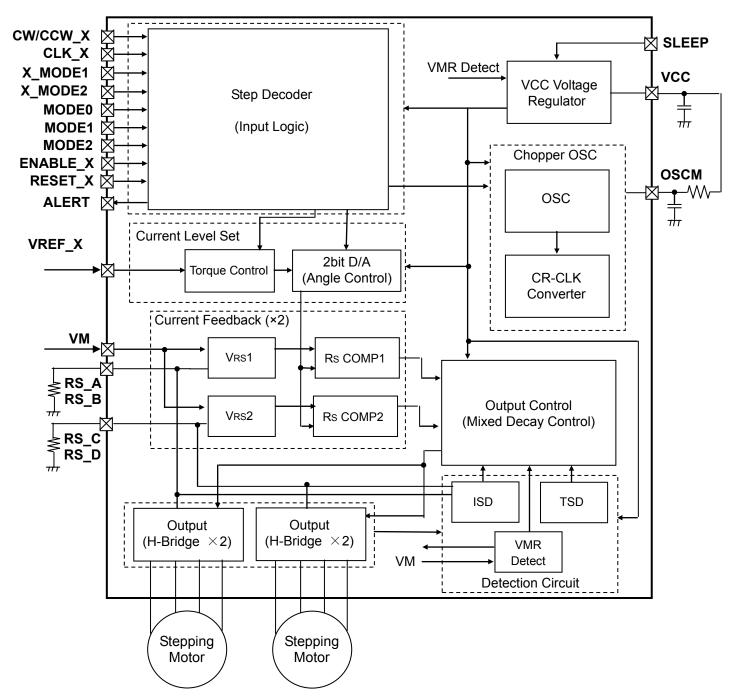

## Block Diagram(Stepping Motor(S) × 2-ch Control Mode)

\* "X" means the ellipsis of AB / CD of each Ch. (CW/CCW\_X,CLK\_X,X\_MODE1,X\_MODE2,ENABLE\_X,RESET\_X)

Note: GND wiring: We recommend that a heat sink be grounded at all points, and the board be grounded at only one GND pin for single point ground. Take the heat dissipation into consideration when designing the board. When in controlling the setting pins for each mode by SW, those pins should be pulled up to power supply like V<sub>CC</sub> or pulled down to GND not to go into a high-impedance (Hi-Z) state. Utmost care is necessary in the design of the output line, V<sub>M</sub> line and GND line since IC may be destroyed due to short-circuit between outputs, to supply, or to ground. Especially for those pins that are connected to power supply and get a large current flow (such as V<sub>M</sub>, RS, OUT and GND), they should be properly wired; otherwise troubles including destruction may occur to this IC. If the logic input pins are not wired properly, malfunction that would destroy the IC may occur due to a large current exceeding the absolute maximum ratings. Care should be taken in the design of board layouts and implementation of the IC.

## **Pin Assignment**

| PIN No. | Pin name             | (DStepper(S) × 2                                                       | @DC(L) × 2                   | (3)Stepper(L)                    | (\$DC(S)×4                                         | ⑤DC(L)+Stepper(S)                                                | <pre>⑤DC(S) × 2</pre>                              |  |

|---------|----------------------|------------------------------------------------------------------------|------------------------------|----------------------------------|----------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------|--|

| 1       | MO CD                | CDoh MO pin                                                            | CDoh IN 1 Pin                | -                                | Coh IN 1 pin                                       | CDah                                                             | MO pin                                             |  |

| 2       | CD MODE2             | CDch step resolution mode setting                                      | -                            | -                                | Doh IN 2 pin                                       | CDch step resolution mode setting                                |                                                    |  |

| 3       | OUT C-               | Cch output pin(-)                                                      | CDch output pin(-)           |                                  | Coh output pin(-)                                  |                                                                  |                                                    |  |

| 4       | RS_C                 | Cch sensing Rs connection pin                                          |                              | Rs Connection pin                | Con output pin(-)<br>Coh sensing Rs connection pin |                                                                  |                                                    |  |

| 5       | RS C                 | Cch sensing Rs connection pin                                          |                              | Re Connection pin                |                                                    | Cch sensing Rs connection pin                                    |                                                    |  |

| 6       | OUT C+               | Cch output pin(+)                                                      |                              | tput pin(+)                      |                                                    | Coh output pin(+)                                                |                                                    |  |

| 7       | OUT D+               | Dch output pin(+)                                                      |                              | tput pin(+)                      |                                                    | Dch output pin(+)                                                |                                                    |  |

| 8       | RS D                 | Den output pin(+)                                                      |                              | a Connection pin                 |                                                    | Doh sensing Rs connection pin                                    |                                                    |  |

| 9       | RS D                 | Dch sensing Rs connection pin                                          |                              | Re Connection pin                |                                                    | Dch sensing Rs connection pin                                    |                                                    |  |

| 10      | OUT D-               | Deh output pin(-)                                                      |                              | tput pin(-)                      |                                                    | Doh output pin(-)                                                |                                                    |  |

| 11      | CD MODE1             | CDch step resolution mode setting                                      | -                            | -                                | Doh IN 1 pin                                       |                                                                  | ition mode setting                                 |  |

| 12      | VREF A               | Ach Vref input                                                         |                              | /ref input                       | Ach Vref input                                     | ABoh Vref input                                                  | Ach Vref input                                     |  |

| 13      | VREF B               | Bch Vref input                                                         | Abui                         |                                  | Bch Vref input                                     |                                                                  | Bch Vref input                                     |  |

| 14      | VREF C               | Coh Vref input                                                         | CD                           | /ref入力                           | Coh Vref input                                     | Coh Vref input                                                   | Coh Vref input                                     |  |

| 15      | VREF_D               | Dch Vref input                                                         | 004                          | -                                | Dch Vref input                                     | Dch Vref input                                                   | Dch Vref input                                     |  |

| 16      | OSCM                 | Don vret input                                                         |                              | Setting pip of oscille           | tion circuit frequency for choppin                 |                                                                  | Den vret input                                     |  |

| 17      | VCC                  |                                                                        |                              |                                  |                                                    | Ig.                                                              |                                                    |  |

| 18      | GND                  | Monitoring pin for internal generated 5V bias<br>GND                   |                              |                                  |                                                    |                                                                  |                                                    |  |

| 19      | VM                   | GNU<br>VM power input pin                                              |                              |                                  |                                                    |                                                                  |                                                    |  |

| 20      | VM                   |                                                                        |                              |                                  | power input pin                                    |                                                                  |                                                    |  |

| 20      | SLEEP                |                                                                        |                              | V #                              | Sleep pin                                          |                                                                  |                                                    |  |

| 21      | ALERT                |                                                                        |                              |                                  | Alert pin                                          |                                                                  |                                                    |  |

| 22      |                      | ABoh CLK input                                                         | ABch PWM pin                 | CLK input                        | Ach PWM pin                                        | ABch PWM pin                                                     | Ach PWM pin                                        |  |

| 23      | ENABLE AB            | ABon CLK Input<br>ABoh ENABLE input                                    | ABON PWM pin                 | ENABLE input                     | Boh PWM pin                                        | ABON PWM pin                                                     | Boh PWM pin                                        |  |

| 25      | CLK CD               | CDoh CLK input                                                         | CDoh PWM pin                 | -                                | Coh PWM pin                                        | CDoh CLK input                                                   | CDoh CLK input                                     |  |

| 25      | ENABLE_CD            | CDon CLK Input                                                         | GDon PWM pin                 | -                                | Doh PWM pin                                        | CDon CLK Input                                                   | CDoh ENABLE input                                  |  |

| 20      | OUT A-               | Ach output pin(-)                                                      | - ABab au                    | tout pin(-)                      | Ach output pin(-)                                  | ABoh output pin(-)                                               | Ach output pin(-)                                  |  |

| 28      | RS_A                 | Ach sensing Rs connection pin                                          |                              | tput pin(-)<br>Re connection pin |                                                    | ABch sensing Rs connection pin                                   |                                                    |  |

| 28      | RS A                 | Ach sensing Rs connection pin                                          |                              | ts connection pin                |                                                    | ABch sensing Rs connection pin<br>ABch sensing Rs connection pin |                                                    |  |

| 30      | OUT_A+               | Ach sensing is connection pin<br>Ach output pin(+)                     |                              | tput pin(+)                      | Ach sensing Rs connection pin<br>Ach output pin(+) | ABch output pin(+)                                               | Ach sensing Rs connection pin<br>Ach output pin(+) |  |

| 30      | OUT_A+               | Boh output pin(+)                                                      |                              | tput pin(+)                      | Boh output pin(+)                                  | ABch output pin(+)<br>ABch output pin(+)                         | Boh output pin(+)                                  |  |

| 32      | RS_B                 | Boh sensing Rs connection pin                                          |                              | tput pin(+)<br>Rs connection pin |                                                    | ABch sensing Rs connection pin                                   |                                                    |  |

| 32      | RS B                 | Bch sensing Rs connection pin<br>Bch sensing Rs connection pin         |                              | ts connection pin                |                                                    | ABch sensing Rs connection pin<br>ABch sensing Rs connection pin |                                                    |  |

| 34      | OUT B-               | Bch output pin(-)                                                      |                              | tput pin(-)                      | Bch output pin(-)                                  | ABch output pin(-)                                               | Bch output pin(-)                                  |  |

| 35      | D TBLANK AB          | ABch Decay setting pin                                                 | Tblank setting pin           |                                  | Tblank setting pin                                 |                                                                  | etting pin                                         |  |

| 36      |                      | Abon Decay setting pin                                                 | i biank setting pin          | -                                | NC                                                 | I I DIAMK 8                                                      | ornig bii                                          |  |

| 30      | D TBLANK CD          | CDch Decay setting pin                                                 | Tblank setting pin           | CDch Decay setting pin           |                                                    | ODah Daaa                                                        | y setting pin                                      |  |

| 38      | MODE2                | "H" input fixed                                                        | "H" input fixed              | "H" input fixed                  | "H" input fixed                                    | "L" input fixed                                                  | "L" input fixed                                    |  |

| 39      | MODE2<br>MODE1       | "H" input fixed                                                        | "H" input fixed              | "L" input fixed                  | "L" input fixed                                    | "H" input fixed                                                  | "H" input fixed                                    |  |

| 39      | MODEI                | "H" input fixed                                                        | "L" input fixed              | "H" input fixed                  | L input fixed                                      | "H input fixed                                                   | "L" input fixed                                    |  |

| 40      | VM                   | n input fixed                                                          |                              |                                  | l power input pin                                  | i input fixed                                                    |                                                    |  |

| 41      | VM<br>VM             |                                                                        |                              |                                  | l power input pin<br>I power input pin             |                                                                  |                                                    |  |

| 42      | NC                   |                                                                        |                              | VN                               | NC                                                 |                                                                  |                                                    |  |

| 43      | CW CCW AB            | ABoh CW/CCW pin                                                        | ABoh IN2 pin                 | CW/CCW pin                       | Ach IN2 pin                                        | ABoh IN2 pin                                                     | Ach IN2 pin                                        |  |

| 44      | MO AB                | ABoh CW/CCW pin<br>ABoh MO pin                                         | ABon INZ pin<br>ABoh IN1 pin | MO pin                           | Ach IN2 pin<br>Ach IN1 pin                         | ABoh IN2 pin<br>ABoh IN1 pin                                     | Ach IN2 pin<br>Ach IN1 pin                         |  |

| 45      | AB MODE2             | ABch MO pin<br>ABch step resolution mode setting                       | ABCh IN1 pin<br>-            | MO pin<br>Mode setting           | Ach IN1 pin<br>Boh IN2 pin                         | ABch IN1 pin                                                     | Ach IN1 pin<br>Boh IN2 pin                         |  |

| 40      | AB_MODE2<br>AB_MODE1 | ABch step resolution mode setting<br>ABch step resolution mode setting |                              |                                  | Bon IN2 pin<br>Boh IN1 pin                         | -                                                                | Bon IN2 pin<br>Boh IN1 pin                         |  |

| 4/      | CW CCW CD            | ABch step resolution mode setting<br>CDch CW/CCW pin                   | CDoh IN2 pin                 | Mode setting                     | Coh IN1 pin                                        |                                                                  | CCW pin                                            |  |

| 40      | 04_004_00            | ODen OW/OOW pin                                                        | ODON INZ PIÑ                 |                                  | U OON INZ PIN                                      | L GDen Cw                                                        |                                                    |  |

\* When Large mode is used, please use to connect the corresponding pins to each other.

Descriptions of Motor Drive Modes

- (1) Stepping Motor (S)  $\times$  2 control mode pin name and assignment

- (2) DC Motor (L)  $\times$  2 control mode pin name and assignment

- (3) Stepping Motor (L)  $\times$  1 control mode pin name and assignment

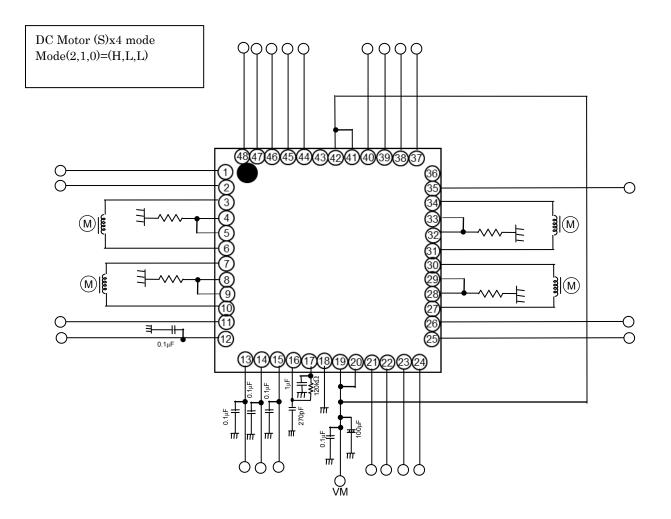

- (4) DC Motor (S)  $\times$  4 control mode pin name and assignment

- (5) Stepping Motor (S)  $\times$  1 control mode + DC Motor (L)  $\times$  1 control mode pin name and assignment

- (6) Stepping Motor (S)  $\times$  1 control mode + DC Motor (S)  $\times$  2 control mode pin name and assignment

\* In the modes that include DC Motor (S) mode, the D\_TBLANK can be separately set for each channel pair, channels A and B and channels C and D.

Channels A and B: D\_TBLANK\_AB pin

Channels C and D: D\_TBLANK\_CD pin

The motor drive Mode (2, 1, 0) = (L, L, H) is provided only for production test and must not be used during normal operation.

- Note 1: In Combination mode, such as Stepping Motor (L) and DC Motor (L) modes, the impedance outside the IC should be balanced.

- Note 2: In Large mode, if the impedance of wiring to mutually connected output transistors is unbalanced, the current that flows through the transistor also becomes unbalanced and may exceed the absolute maximum rating of the transistor, thus permanently damaging the transistors.

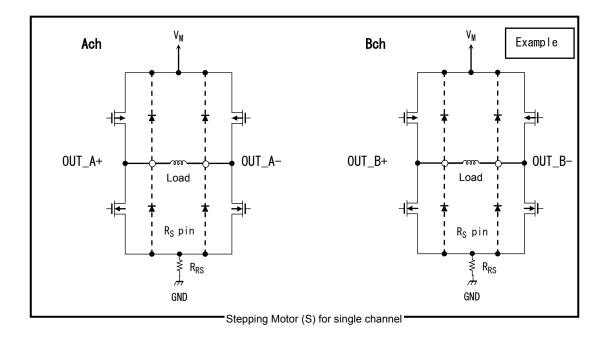

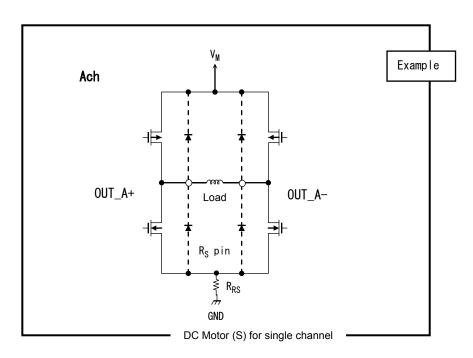

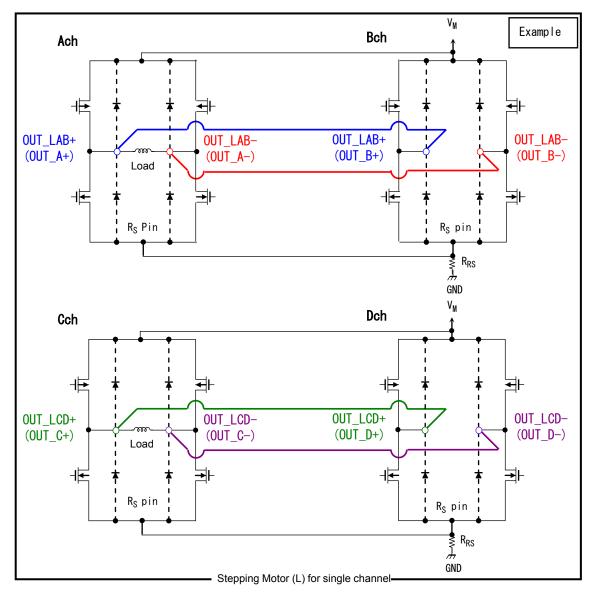

■H-bridge Combination (connection method) for Each Type of Motor Driver

• Stepping Motor (S) Combination

• DC Motor (S) Combination

• ... Indicates an IC output pin connected to a motor.

• Stepping Motor (L) Combination

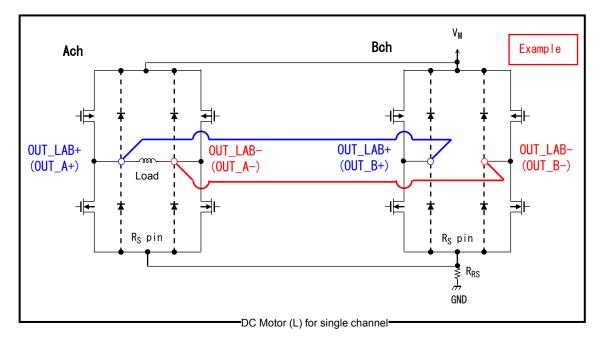

## DC Motor (L) Combination

• ... Indicates an IC output pin connected to a motor.

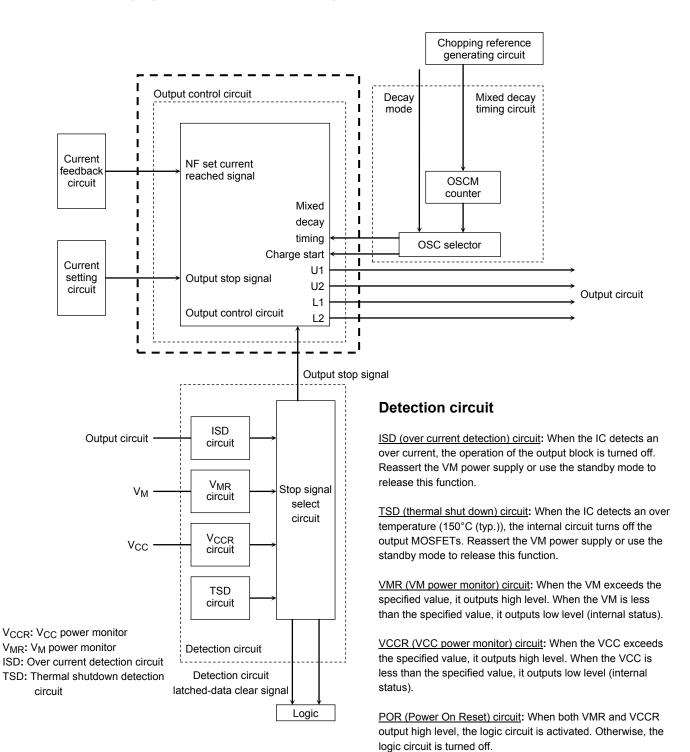

## Output Control Circuit, Current Feedback Circuit, and Current Setting Circuit for Motor Driver

Note: Logic input pins are internally connected to pull-down resistors of about 100 k $\Omega$ .

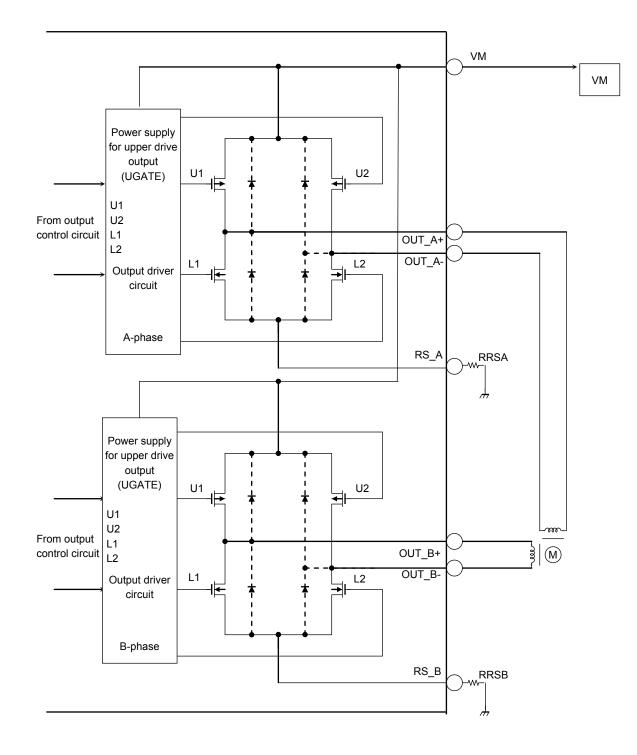

## Output Equivalent Circuit of A/B-phase (C/D conforms to A/B.)

## 1. Function Table for Motor Drive Mode Selection

Motor drive modes can be selected depending on the type of motors to be driven.

The configuration of H-bridge drivers and control category are changed according to the selected mode.

There is basically no need to change drive modes during motor operation. Thus, the TC78S122FTG does not support dynamic mode switching.

Changing the settings of these pins changes the functions and timing of control pins.

The setting of mode select pins must not be changed after the TC78S122FTG is powered on.

| Mode 0 | Mode 1 | Mode 2 | Drive Mode                                                 |

|--------|--------|--------|------------------------------------------------------------|

| Н      | Н      | Н      | Stepping Motor (S) $\times$ 2                              |

| L      | Н      | Н      | DC Motor (L) (Combination) $\times$ 2                      |

| Н      | L      | н      | Stepping Motor (L) (Combination) $\times$ 1                |

| L      | L      | н      | DC Motor (S) × 4                                           |

| Н      | Н      | L      | DC Motor (L) (Combination) $\times$ 1 + Stepping Motor (S) |

| L      | Н      | L      | DC Motor (S) $\times$ 2 + Stepping Motor (S)               |

| Н      | L      | L      | Inhibited (For production test only)                       |

| L      | L      | L      | Standby mode                                               |

## • Stepping Motor Mode

This mode is used to drive stepping motors.

The tBLANK time is specified as a fixed analog value (about 300 ns). Each motor is controlled via two logic control inputs, PHASE (current direction) and ENABLE (ON/OFF), and via the Vref input for constant-current control.

### • Brushed DC Motor Mode

This mode is used to drive brushed DC motors.

The tBLANK time can be specified as a fixed analog value, or as four OSC cycles in digital tBLANK mode, where OSC is a reference signal for chopper circuit.

When DC motors are driven under PWM control, a discharge current spike can occur due to a varistor. To prevent this current spike from erroneously tripping the constant-current sensor, the constant-current sensor is digitally blanked for a period of time that is determined by tBLANK, which is derived from the OSC signal.

Using this blanking function enables constant-current limiter control, as well as external PWM control. An over-current can be observed only during blank times.

### • Combination Mode

The Combination mode, such as DC Motor (L) and Stepping Motor (L) modes, can be selected when two units of H-bridges with the same characteristics are operated in parallel.

In this mode, the actual ON-resistance is reduced by half while the current capability is doubled. (Specifications actually include the thermal capacitance as well. See electrical characteristics for more details.)

To use this mode, the power supply, ground, and output pins that have identical names should be shorted together on the board.

At the same time, the wirings of a board should be routed to balance the impedance at each pin. Otherwise, the shorted pins may experience a current imbalance and more current may flow into either one of them than the other.

## 2. Stepping Motor mode Function

### (1) CLK Function

The electrical angle leads one by one in the manner of the clocks. The clock signal is reflected to the electrical angle on the rising edge.

| CLK_AB<br>CLK_CD | Function                                                  |

|------------------|-----------------------------------------------------------|

| Rise             | The electrical angle leads one by one on the rising edge. |

| Fall             | Remains at the same position.                             |

### (2) **ENABLE Function**

The ENABLE pin controls whether the current is allowed to flow through a given phase for a stepper motor drive. This pin selects whether the motor is stopped in off mode or activated. The pin should be fixed to the low level at power-on or power-off of the TC78S122FTG.

| ENABLE_AB<br>ENABLE_CD | Function                                                |

|------------------------|---------------------------------------------------------|

| н                      | Output transistors are enabled (Normal operation mode). |

| L                      | Output transistors are disabled (High impedance: Z).    |

## (3) CW/CCW Function and output pin function (Output logic at charge starting)

The CW/CCW pin switches rotation direction of stepping motors.

| CW/CCW_AB<br>CW/CCW_CD | Input function     | OUT (+) | OUT (-) |  |

|------------------------|--------------------|---------|---------|--|

| Х                      | L                  | OFF     | OFF     |  |

| н                      | Clock-wise         | Н       | L       |  |

| L                      | Counter clock-wise | L       | Н       |  |

X: Don't care

## (4) Step resolution Mode Select Function

| AB_MODE1<br>CD_MODE1 | AB_MODE2<br>CD_MODE2 | Function                                                      |

|----------------------|----------------------|---------------------------------------------------------------|

| L                    | L                    | Fixed electrical angle<br>(Initial setting of Full step: 45°) |

| L                    | Н                    | Half step                                                     |

| н                    | L                    | Full step                                                     |

| Н                    | Н                    | Quarter step                                                  |

In the case of AB/CD\_MODE1=L, and AB/CD\_MODE2=L, the electrical angle is reset and fixed to 45°, which is the initial value in the full step mode.

## 3. D\_TBLANK Function (DC Motor MODE only)

| D_TBLANK_AB<br>D_TBLANK_CD | Motor Drive Mode                 |

|----------------------------|----------------------------------|

| L                          | OFF: Digital tBLANK Time = OSC×0 |

| Н                          | ON: Digital tBLANK Time = OSC×4  |

\* If it is set to "L", only analog tBLANK width can be available.

## 4. Decay Switching Function (Stepping Motor MODE only)

| D_TBLANK_AB<br>D_TBLANK_CD | Constant current control mode                           |

|----------------------------|---------------------------------------------------------|

| L                          | Mixed Decay:37.5% fixed                                 |

| Н                          | Mixed Decay: 12.5 %( During the current decay is 37.5%) |

## 5. Control Signal Functions in Brushed DC Motor Mode

|                 | Control Input       |                   | State of the Output Stage |               |                 |  |

|-----------------|---------------------|-------------------|---------------------------|---------------|-----------------|--|

| MO_X<br>X_MODE1 | CW/CCW_X<br>X_MODE2 | CLX_X<br>ENABLE_X | OUT_X+                    | OUT_X-        | Mode            |  |

| Н               | Н                   | H<br>L            | L                         | L             | Short brake     |  |

|                 | н                   | Н                 | L                         | Н             | Forward/reverse |  |

| L               | 11                  | L                 | L                         | L             | Short brake     |  |

| Н               | I                   | Н                 | Н                         | L             | Reverse/forward |  |

| 11              | L                   | L                 | L                         | L             | Short brake     |  |

| L               | L                   | <u> </u>          | OFF<br>(Hi-z)             | OFF<br>(Hi-z) | Stop            |  |

Note: "X" means the ellipsis of AB/CD of each Ch. (CW/CCW\_X, X\_MODE1, X\_MODE2, MO\_X,

CLX\_X and ENABLE\_X)

### • External PWM Control Function

The motor speed can be controlled by applying 0V and 5V (higher than TTL level) PWM signals to the PWM pin.

In PWM mode, the PWM chopper circuit alternates between on and short brake.

When the PWM speed control is not required, the PWM pin (short brake pin) should be held high level.

When the constant-current limiter is used, the TC78S122FTG enters 37.5% Mixed Decay mode after an output current reaches the predefined current value. Since the dead band time is internally inserted to prevent a shoot-through current eliminating, the special arrangement is not required.

The short brake function is disabled in Stepping Motor mode (Large or Small).

Stepping motors can also be driven in Brushed DC motor mode.

To perform such operation, the short brake function should not be used and the D\_TBLANK pin should be set low level.

At the same time, input signal functions should also be confirmed.

## 6. SLEEP Function

In the SLEEP pin, it is possible to control the low power consumption mode (VCC OFF) and the normal operation mode (VCC ON).

When SLEEP pin is low level, VCC regulator is turned OFF, completely logic will stop.

After SLEEP pin is set to high level, it can return to the normal operation mode in 1ms.

| SLEEP | Function                             |

|-------|--------------------------------------|

| L     | Low power consumption mode (VCC OFF) |

| Н     | Normal operation mode (VCC ON)       |

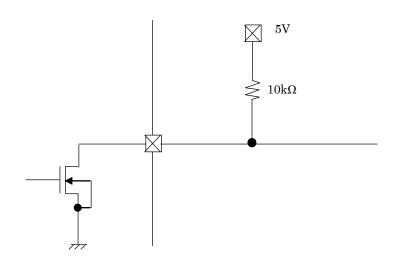

## 7. ALERT Function

The ALERT pin outputs low level when an error occasion (TSD/ISD) is detected.

The ALERT is an open drain output pin. When the output pin is pulled up to the VCC with resistance, the low level is output (MOSFET ON) at the Reset, and the high level (internal Hi-Z) is output at the non-reset. Please connect it to the VCC.

## Absolute Maximum Ratings (Ta=25°C)

| Characteristics                     | Symbol      | Rating     | Unit | Remarks      |

|-------------------------------------|-------------|------------|------|--------------|

| Motor power supply                  | VM          | 40         | V    |              |

| Motor output voltage                | VOUT        | 40         | V    |              |

|                                     | IOUT_(ST_S) | 2.0        | Α    |              |

| Motor output ourropt (Note 4)       | IOUT_(ST_L) | 3.0        | А    |              |

| Motor output current (Note 1)       | IOUT_(DC_S) | 3.5        | А    | (tw ≤ 500ns) |

|                                     | IOUT_(DC_L) | 5.0        | А    | (tw ≤ 500ns) |

| Internal Logic power supply         | VCC         | 6.0        | V    |              |

| Logio input voltago                 | VIN(H)      | 6.0        | V    |              |

| Logic input voltage                 | VIN(L)      | -0.4       | V    |              |

| Power dissipation (single) (Note 2) | PD          | 1.3        | W    |              |

| Operating temperature               | TOPR        | -20 to 85  | °C   |              |

| Storage temperature                 | TSTR        | -55 to 150 | °C   |              |

| Junction temperature                | Tj(max)     | 150        | °C   |              |

- Note 1: As a guide, the maximum output current should be kept below 1.4 A per phase. The maximum output current may be further limited in view of thermal considerations, depending on ambient temperature and board conditions.

- Note 2: Stand-alone (Ta =  $25^{\circ}$ C) When Ta exceeds  $25^{\circ}$ C, it is necessary to do the derating with 10.4mW/°C.

- Ta: Ambient temperature

- Topr: Ambient temperature while the TC78S122FTG is active

- Tj: Junction temperature while the TC78S122FTG is active. The maximum junction temperature is limited by the thermal shutdown (TSD) circuitry.

It is advisable to keep the maximum current below a certain level so that the maximum junction temperature, Tj (MAX), will not exceed 120°C.

## Caution) Absolute maximum ratings

The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Do not exceed any of these ratings.

Exceeding the rating (s) may cause device breakdown, damage or deterioration, and may result in injury by explosion or combustion.

The value of even one parameter of the absolute maximum ratings should not be exceeded under any circumstances. The TC78S122FTG does not have overvoltage detection circuit. Therefore, the device is damaged if a voltage exceeding its rated maximum is applied.

All voltage ratings, including supply voltages, must always be followed. The other notes and considerations described later should also be referred to.

## **Operation Ranges(Ta=0 to 85°C)**

| Characteristics                        | Symbol         | Test<br>Circuit | Test Condition            | Min | Тур. | Мах  | Unit |

|----------------------------------------|----------------|-----------------|---------------------------|-----|------|------|------|

| Internal logic power<br>supply voltage | VCC            | DC              | (Automatically generated) | 4.5 | 5.0  | 5.5  | V    |

| Motor power supply<br>voltage          | VM             | DC              | _                         | 8   | 24   | 38   | V    |

|                                        | lout<br>(ST_S) | DC              | Ta = 25°C per phase       |     | 0.8  | 1.5  |      |

| Motor output current                   | lout<br>(ST_L) | DC              | Ta = 25°C per phase       |     | 1.5  | 2.1  | А    |

|                                        | lout<br>(DC_S) | DC              | Ta = 25°C per phase       |     | 1.0  | 2.0  | A    |

|                                        | lout<br>(DC_L) | DC              | Ta = 25°C per phase       | _   | 2.0  | 3.8  |      |

| Logic input voltage                    | VIN            | DC              | —                         | GND | 3.3  | 5.0  | V    |

| Chopping frequency setting range       | fchop          | DC              | VCC=5.0V                  | 40  | 100  | 150  | kHz  |

| Vref voltage                           | Vref           | DC              | VM=24V                    | GND | 3.0  | 4.0  | V    |

| Current detect pin<br>voltage          | VRS            | DC              | VM=24V                    | 0   | ±1.0 | ±1.5 | V    |

Note: Use the maximum junction temperature  $(T_j)$  at 120°C or less. The Maximum current cannot be used under certain thermal conditions.

## Electrical Characteristics 1 (Unless otherwise specified, Ta=25°C, VM=24 V)

| Characteristics                                                      |                                             | Symbol                            | Test<br>Circuit  | Test Condition                                                                 | Min | Тур. | Мах | Unit |

|----------------------------------------------------------------------|---------------------------------------------|-----------------------------------|------------------|--------------------------------------------------------------------------------|-----|------|-----|------|

| Logic input voltage                                                  | jic input voltage High VIH Logic input pins |                                   | Logic input pins | 2.2                                                                            |     | 5.5  |     |      |

| (Other than SLEEP pin)                                               | Low                                         | VIL                               | DC               | (Other than SLEEP pin)                                                         |     | _    | 0.8 | V    |

| Logic input voltage High<br>(SLEEP pin only) Low                     |                                             | VIH                               |                  |                                                                                | 2.0 |      | 5.5 | V    |

|                                                                      |                                             | VIL                               | DC               | SLEEP pin only                                                                 | GND |      | 0.6 |      |

| Logic input hyster<br>voltage                                        | esis                                        | His                               | DC               | Logic input pins                                                               | 0.3 | 0.4  | 0.5 | V    |

|                                                                      | <b>1</b>                                    | IIN(H)                            | 50               | VIN=5V, Input pins with                                                        |     | 50   | 75  | μA   |

| Logic input curre                                                    | ent                                         | llN(L)                            | DC               | resistor                                                                       |     |      | 1   |      |

| MO,ALERT output v                                                    | voltage                                     | V <sub>OL</sub>                   | DC               | IOL=4mA output: Low                                                            | _   | _    | 0.5 | V    |

| Current consumption<br>(VM pin)                                      |                                             | IM1                               |                  | Output=OPEN<br>(ENABLE ALL=L),<br>MOSFET=OFF                                   | _   | 2    | 3   |      |

|                                                                      |                                             | IM2                               | DC               | Output=OPEN,<br>fPWM=100kHz<br>Logic operate,<br>MOSFET=OFF                    | _   | 3.5  | 5   | mA   |

|                                                                      |                                             | IM3                               |                  | Output=OPEN<br>Function mode(Full step)                                        |     | 8    | 10  |      |

|                                                                      |                                             | IM4                               |                  | SLEEP=L<br>VCC regulator = OFF                                                 | _   | 10   | 20  | μA   |

| Output leakage                                                       | Output leakage side                         |                                   |                  | VM=24V, Vout=0V,<br>ENABLE ALL=L                                               | -1  | _    | _   | μA   |

| current                                                              | Lower<br>side                               | IOL                               | DC               | VM=Vout=24V,<br>ENABLE ALL=L                                                   |     | _    | 1   | μΑ   |

| Output current diffe                                                 | rential                                     | ∆lout1                            | DC               | lout=1.0A                                                                      | -5  |      | 5   | %    |

| Output current setting<br>differential                               |                                             | ∆lout2                            | DC               | lout=1.0A                                                                      | -5  | _    | 5   | %    |

| RS pin current                                                       |                                             | IRS                               | DC               | VRS=0V, VM=24V,<br>ENABLE ALL=L<br>(MOSFET = OFF)                              |     |      | 10  | μΑ   |

| Output transistor<br>drain-source ON-resistance<br>(H-side + L-side) |                                             | Ron (DS:<br>H-side +<br>L-side) S |                  | lout=1.0A,<br>Tj=25°C, Drain-source,<br>(Upper + Lower)<br>Small Mode          | 0.4 | 0.6  | 0.8 | Ω    |

|                                                                      |                                             | Ron (DS:<br>H-side +<br>L-side) L | DC               | lout=1.0A,VCC=5.0V,<br>Tj=25°C, Drain-source,<br>(Upper + Lower)<br>Large Mode | _   | 0.3  | 0.4 | 52   |

| Characteristics                                              | Symbol     | Test<br>Circuit | Test Condition | Min   | Тур.  | Мах   | Unit |

|--------------------------------------------------------------|------------|-----------------|----------------|-------|-------|-------|------|

| Vref input voltage                                           | VREF       | DC              | VM=24V,VCC=5V  | GND   | 3.0   | 4.0   | V    |

| Vref input current                                           | IREF       | DC              | VREF=3.0V      | _     | 0     | 1     | μA   |

| VCC output voltage                                           | VCC        | DC              | ICC=5.0mA      | 4.5   | 5.0   | 5.5   | V    |

| VCC output current                                           | ICC        | DC              | VCC=5.0V       | _     | 2.5   | 5     | mA   |

| Vref attenuation ratio                                       | VREF(gain) | DC              | VREF=2.0V      | 1/5.2 | 1/5.0 | 1/4.8 |      |

| TSD temperature (Note 1)                                     | TjTSD      | DC              | —              | 140   | 150   | 170   | °C   |

| VM return voltage                                            | VMR        | DC              | —              | 6.8   | 7.0   | 7.3   | V    |

| Detection current of over-current detection circuit (Note 2) | ISD        | DC              | _              | 2.1   | 4.0   | 5.0   | А    |

## Electrical Characteristics 2 (Unless otherwise specified, Ta=25°C, VM=24 V)

Note 1: Thermal shut down (TSD) circuit

When the IC junction temperature reaches the specified value and become overheated under irregular conditions causing the TSD circuit to be activated, the internal halt circuit is activated shutting down all the outputs to off. When the temperature is set between 140 °C (min) to 170 °C (max), the TSD circuit operates (design target value). When the TSD circuit is operating, the output operation can be returned by re-starting the VM power supply or setting the standby mode. The TSD function aims at detecting abnormal heating of ICs. Please avoid positively using the TSD function.

Note 2: Over-current detection (ISD) circuit

When the current exceeding the specified value flows to the output under irregular conditions, the internal halt circuit is activated switching all the outputs to off. The dead band time is set to avoid the incorrect operation by switching. (For details, refer to "ISD Dead Band Time and ISD Operating Time.") When the ISD function is operating, the output is stopped until power-on-reset of the VM power supply. The output operation can be returned by re-starting the VM power supply or setting the standby mode. The ISD function aims at detecting abnormal current of ICs. Please avoid positively using the ISD function.

Note 3: The circuit is designed to avoid EMF or leakage current when the logic signal is inputted in the state that the VM voltage is not supplied. But for fail-safe, please control the logic signal timing correctly in order that the motor may not operate before the VM power is resupplied.

## Back-EMF

• While a motor is rotating, there is a timing at which power is fed back to the power supply. At that timing, the motor current recirculates back to the power supply due to the effect of the motor back-EMF. If the power supply does not have enough sink capability, the power supply and output pins of the device might rise above the rated voltages. The magnitude of the motor back-EMF varies with usage conditions and motor characteristics. It must be fully verified that there is no risk that the device or other components will be damaged or fail due to the motor back-EMF.

## Cautions on Overcurrent Shutdown (ISD) and Thermal Shutdown (TSD)

- The ISD and TSD circuits are only intended to provide temporary protection against irregular conditions such as an output short circuit; they do not necessarily guarantee complete IC safety.

- If the device is used beyond the specified operating ranges, these circuits may not operate properly: then the device may be damaged owing to an output short circuit.

- The ISD circuit is only intended to provide temporary protection against an output short circuit. If such a condition persists for a long time, the device may be damaged owing to overstress. Overcurrent conditions must be removed immediately by external hardware.

## **IC Mounting**

Do not insert devices in the wrong orientation or incorrectly. Otherwise, it may cause device breakdown, damage and/or deterioration.

# AC Electrical Characteristics (Unless otherwise specified, Ta = 25°C, $V_M$ = 24V, Load = 6.8 mH/5.7 $\Omega$ )

| Characteristics                                | Symbol                       | Test<br>Circuit | Test Condition                                          |     | Тур. | Мах  | Unit |

|------------------------------------------------|------------------------------|-----------------|---------------------------------------------------------|-----|------|------|------|

| Logic input frequency                          | fLogic                       | AC              | _                                                       |     | —    | 200  | kHz  |

|                                                | tCLK(H)                      |                 |                                                         | 300 | _    | _    | ns   |

| CLK input internal filter width                | tCLK(L)                      | AC              |                                                         | 250 | _    | _    |      |

|                                                | tr                           | AC              | Output loads 6.0 ml 1/5.7 o                             | 60  | 120  | 200  | ns   |

| Output transistor switching characteristic     | tf                           |                 | Output load: 6.8 mH/5.7 $\Omega$                        | 30  | 70   | 130  |      |

|                                                | tpLH                         |                 | Between Signal and OUT Output load: 6.8 mH/5.7 $\Omega$ | _   | 120  | 500  |      |

|                                                | tpHL                         |                 |                                                         |     | 120  | 500  |      |

| N                                              | tBLANK_AB(L)<br>tBLANK_CD(L) | AC              | lout=0.6A,VM=24V,<br>Analog tBLANK width                | 450 | 550  | 700  | ns   |

| Noise rejection dead band time                 | tBLANK_AB(H)<br>tBLANK_CD(H) | AC              | lout=0.6A,OSC=1.6MHz,<br>4×OSC setting                  | 2.0 | 2.5  | 3.0  | μS   |

| OSCM reference signal<br>oscillation frequency | fOSCM                        | AC              | C C <sub>osc</sub> =270pF,R <sub>osc</sub> =120kΩ       |     | 1600 | 2000 | kHz  |

| Chopping frequency range                       | fchop                        | AC              | Output operation (lout=1.0A)                            | 40  | 100  | 150  | kHz  |

| Chopping frequency                             | fchop                        | AC              | Output operation (lout=1.0A)<br>OSC=1.6MHz              | _   | 100  | _    | kHz  |

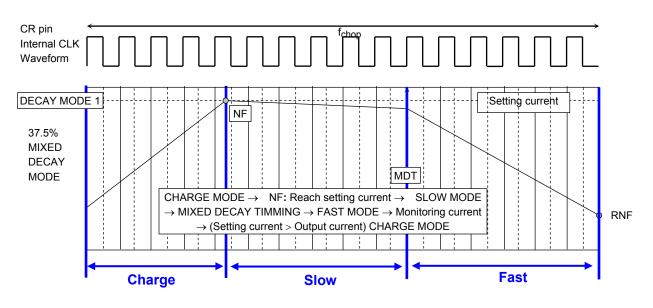

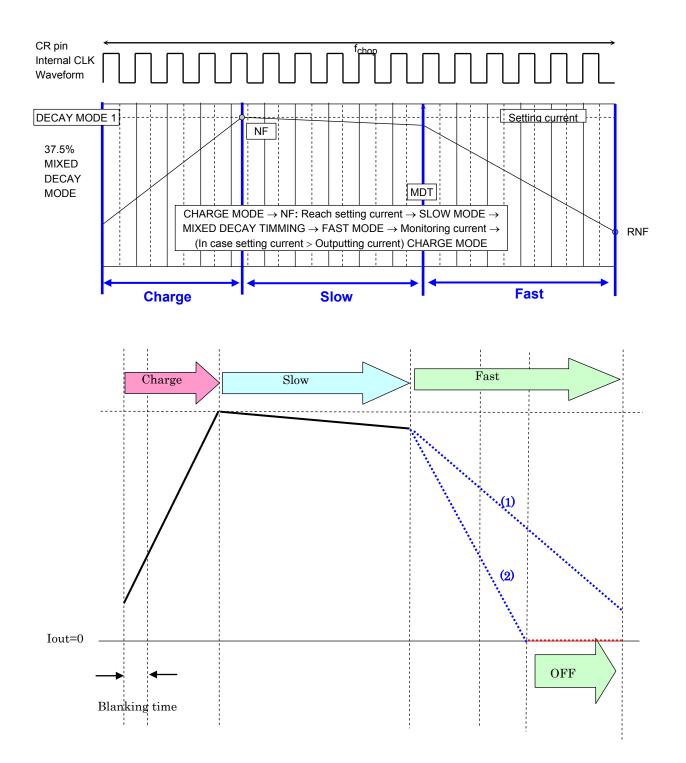

## Decay Mode1:Charge to Slow to Fast

## Mixed Decay Mode / Detecting zero point

Status (1): When Fast -> Charge operation starts before reaching zero point (Iout = 0A) Status (2): When reaching zero point (Iout = 0A)

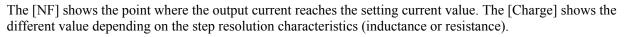

Mixed Decay mode: Charge -> NF: Reaching setting current -> Slow -> Fast -> Charge -> ...

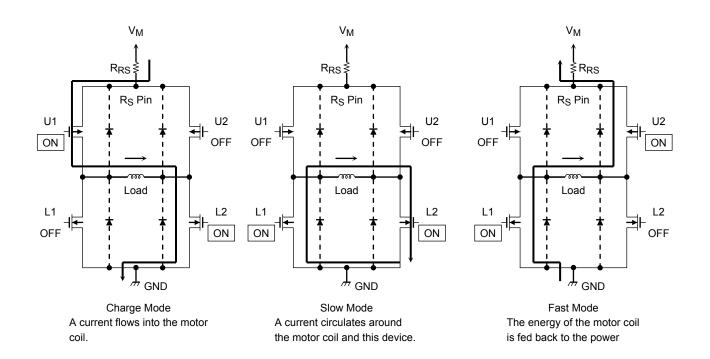

## **Output Transistor Operating Modes**

## **Output Transistor Operating Function**

| CLK         | U1  | U2  | L1  | L2  |

|-------------|-----|-----|-----|-----|

| Charge Mode | ON  | OFF | OFF | ON  |

| Slow Mode   | OFF | OFF | ON  | ON  |

| Fast Mode   | OFF | ON  | ON  | OFF |

Note: This table shows an example of when the current flows as indicated by the arrows in the figures shown above. If the current flows in the opposite direction, refer to the following table.

| CLK         | U1  | U2  | L1  | L2  |

|-------------|-----|-----|-----|-----|

| Charge Mode | OFF | ON  | ON  | OFF |

| Slow Mode   | OFF | OFF | ON  | ON  |

| Fast Mode   | ON  | OFF | OFF | ON  |

The TC78S122FTG switches among Charge, Slow-Decay and Fast-Decay modes automatically for constant-current control. The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

## Calculation of the Setting Output Current

For PWM constant-current control, the TC78S122FTG uses a clock generated by OSCM oscillator. The peak output current can be set via the current-sensing resistor ( $R_{RS}$ ) and the reference voltage ( $V_{ref}$ ), as follows:

lout (Max) = Vref (gain) x  $\frac{Vref (V)}{RRS (\Omega)}$

Vref (gain): Vref decay ratio is 1 / 5.0 (typ.).

Ex.: In case of 100% setting,

When Vref = 3.0 V, Torque = 100%, and RRS = 0.51  $\Omega$ ,

constant current output of the motor (peak current) is calculated as follows;

$I_{out} = 3.0 \text{ V} / 5.0 / 0.51 \Omega = 1.18 \text{ A}.$

## **OSCM** oscillation frequency

For OSCM oscillation frequency, the frequency can be changed by an external capacitor and a resistor.

By changing the frequency of the OSCM, the chopping frequency can be also changed.

Please perform the adjustment of chopping frequency referring to the following table.

| Chopping [kHz] | C [pF] | <b>R [k</b> Ω] |

|----------------|--------|----------------|

| 150            | 150    | 180            |

| 140            | 180    | 100            |

| 130            | 180    | 150            |

| 120            | 220    | 100            |

| 110            | 180    | 220            |

| 100            | 270    | 120            |

| 90             | 330    | 68             |

| 80             | 330    | 130            |

| 70             | 390    | 130            |

| 60             | 470    | 120            |

| 50             | 560    | 180            |

| 40             | 820    | 68             |

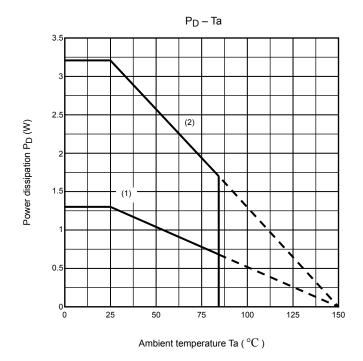

## PD – Ta (Package Power Dissipation)

- (1) IC only:  $R_{th (j-a)}$ : 113°C/W

- (2) When mounted on the board (100 mm  $\times$  200 mm  $\times$  1.6 mm 2layer board: 37°C/W (typ.))

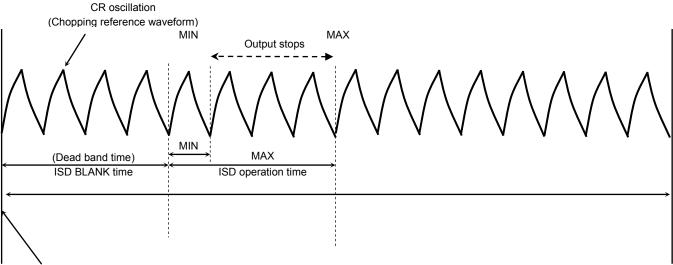

## **Operating Time for Over-current Detection Circuit**

ISD Dead Band Time and ISD Operating Time

When over-current starts to flow into the output stage (Over-current state starts)

The over-current detection circuit has a dead band time to prevent erroneous detection of  $I_{RR}$  or spike current at switching. The dead band time being synchronized with the frequency of the OSC for setting chopping frequency is expressed as follows.

Dead band time  $=4 \times CR$  time

Time required to stop the output after over-current flows into the output stage is expressed as follows.

Minimum time:  $4 \times CR$  time

Maximum time: 8 × CR time

Note that the above-mentioned operating times are achieved only when over-current flows as it is expected. Depending on the timing of output control mode, the circuit may not be triggered.

Thus, to ensure safe operation, please insert a fuse in the motor power supply.

The capacity of the fuse is determined according to the usage conditions. Please select one whose capacity does not exceed the power dissipation for the IC to avoid any operating problems.

## • tBLANK (noise rejection dead band time)

The TC78S122FTG has two different dead band times (blank times) for different motors to be driven so as to prevent malfunctions because of switching noise.

### (1) Analog tBLANK Functions (in Stepping Motor Mode)

The noise rejection dead band time (analog tBLANK) defined by the AC characteristics of the motor block is fixed within the IC. It is mainly used to avoid misjudging the  $I_{RR}$  (diode recovery current) when a stepping motor is driven by constant current.

It is fixed within the IC and thus cannot be altered.

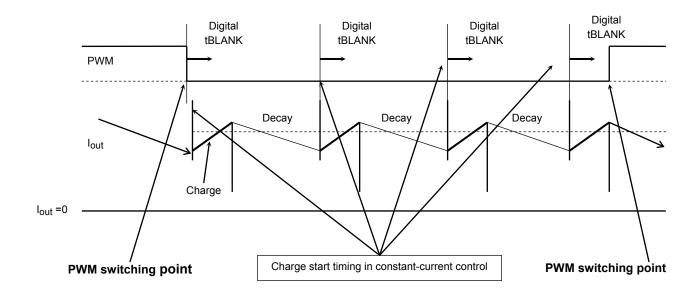

### (2) Digital tBLANK (in Brushed DC Motor mode)

In addition to analog tBLANK, the digital tBLANK time, which is set in the initial mode select, is generated digitally from an external chopping period. This blank time is used to prevent false detections of over-current conditions due to recovery currents of a varistor generated during PWM operation of DC motors in DC Motor mode.

When Stepping Motor mode is selected via the mode select pins, the digital tBLANK time is nullified (0  $\mu$ s) and the analog tBLANK time, which is internally fixed, becomes effective.

Since this blank time is generated based on the OSCM signal, the time can be adjusted by changing the OSCM signal frequency.

(Please note that the characteristics other than the blank time, such as motor chopping frequency and the dead band time inserted at power on, are also changed when the OSCM signal frequency is changed.)

## Digital tBLANK Insertion Timing in Brushed DC Motor Mode

The digital tBLANK time is inserted immediately after the switching timing of externally applied PWM signals, CLK\_X, ENABLE\_X (such as the switching timing between short brake and charging), and also when the charging in constant-current chopper drive is started.

The digital tBLANK time becomes effective only in DC Motor mode.

The TC78S122FTG enters 37.5% Mixed-Decay mode when starting DC motor operation. In this mode, the TC78S122FTG stays in Charge mode for the first 4 CLK cycles of the whole period, which is also a digital tBLANK time. Thus, depending on the timing, operation mode might be switched directly to Fast-Decay mode.

## Application Circuit Example

The values shown in the following figure are typical values. For input conditions, see the Operating Ranges.

Note: It is recommended that a bypass capacitor is added if necessary. The GND wiring must become one-point-earth as much as possible.

The example of an applied circuit is for reference, and enough evaluation should be done before the mass-production design.

Any licenses to any industrial property rights are not granted.

## **Package Dimensions**

QFN48-P-0707-0.50

Weight: 0.137 g (typ.)

## Notes on Contents

### (1) Block Diagrams

Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.

### (2) Equivalent Circuits

The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

### (3) Timing Charts

Timing charts may be simplified for explanatory purposes.

### (4) Application Circuits

The application circuits shown in this document are provided for reference purposes only. Thorough evaluation is required, especially at the mass production design stage.

Any license to any industrial property rights is not granted by providing these examples of application circuits.

### (5) Test Circuits

Components in the test circuits are used only to obtain and confirm the device characteristics. These components and circuits are not guaranteed to prevent malfunction or failure from occurring in the application equipment.

## **IC Usage Considerations**

### Notes on Handling of ICs

- The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Do not exceed any of these ratings.

Exceeding the rating(s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion

- (2) Do not insert devices in the wrong orientation or incorrectly. Make sure that the positive and negative terminals of power supplies are connected properly. Otherwise, the current or power consumption may exceed the absolute maximum rating, and exceeding the rating(s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion. In addition, do not use any device that is applied the current with inserting in the wrong orientation or incorrectly even just one time.

- (3) Use an appropriate power supply fuse to ensure that a large current does not continuously flow in case of over-current and/or IC failure. The IC will fully break down when used under conditions that exceed its absolute maximum ratings, when the wiring is routed improperly or when an abnormal pulse noise occurs from the wiring or load, causing a large current to continuously flow and the breakdown can lead smoke or ignition. To minimize the effects of the flow of a large current in case of breakdown, appropriate settings, such as Fast-blow fuse capacity, fusing time and insertion circuit location, are required.

- (4) If your design includes an inductive load such as a motor coil, incorporate a protection circuit into the design to prevent device malfunction or breakdown caused by the current resulting from the inrush current at power ON or the negative current resulting from the back electromotive force at power OFF. IC breakdown may cause injury, smoke or ignition. Use a stable power supply with ICs with built-in protection functions. If the power supply is unstable, the protection function may not operate, causing IC breakdown. IC breakdown may cause injury, smoke or ignition.

(5) Carefully select external components (such as inputs and negative feedback capacitors) and load components (such as speakers), for example, power amp and regulator.

If there is a large amount of leakage current such as input or negative feedback capacitor, the IC output DC voltage will increase. If this output voltage is connected to a speaker with low input withstand voltage, over-current or IC failure can cause smoke or ignition. (The over-current can cause smoke or ignition from the IC itself.) In particular, please pay attention when using a Bridge Tied Load (BTL) connection type IC that inputs output DC voltage to a speaker directly.

## Points to Remember on Handling of ICs

(1) Over-current Protection Circuit

Over-current protection circuits (referred to as current limiter circuits) do not necessarily protect ICs under all circumstances. If the Over-current protection circuits operate against the over-current, clear the over-current status immediately.

Depending on the method of use and usage conditions, such as exceeding absolute maximum ratings can cause the over-current protection circuit to not operate properly or IC breakdown before operation. In addition, depending on the method of use and usage conditions, if over-current continues to flow for a long time after operation, the IC may generate heat resulting in breakdown.

(2) Thermal Shutdown Circuit

Thermal shutdown circuits do not necessarily protect ICs under all circumstances. If the thermal shutdown circuits operate against the over temperature, clear the heat generation status immediately. Depending on the method of use and usage conditions, such as exceeding absolute maximum ratings can cause the thermal shutdown circuit to not operate properly or IC breakdown before operation.

(3) Heat Radiation Design

In using an IC with large current flow such as power amp, regulator or driver, please design the device so that heat is appropriately radiated, not to exceed the specified junction temperature (Tj) at any time and condition. These ICs generate heat even during normal use. An inadequate IC heat radiation design can lead to decrease in IC life, deterioration of IC characteristics or IC breakdown. In addition, please design the device taking into considerate the effect of IC heat radiation with peripheral components.

(4) Back-EMF

When a motor rotates in the reverse direction, stops or slows down abruptly, a current flow back to the motor's power supply due to the effect of back-EMF. If the current sink capability of the power supply is small, the device's motor power supply and output pins might be exposed to conditions beyond absolute maximum ratings. To avoid this problem, take the effect of back-EMF into consideration in system design.

## **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. **TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS**.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. **TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.**

## **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**