# 32 ビット RISC マイクロコントローラ **TXZ** ファミリ

リファレンスマニュアル バウンダリスキャン (BSC-A)

**Revision 1.2**

2017-07

東芝デバイス&ストレージ株式会社

# 目次

| 序章                     | 4  |

|------------------------|----|

| 関連するリファレンスマニュアル        | 4  |

| 表記規約                   | 5  |

| 用語・略語                  | 7  |

| 1. 概要                  | 8  |

| 2. 構成                  | 9  |

| 3. 動作説明·機能説明           | 10 |

| 3.1. 命令レジスタ            | 10 |

| 3.2. バウンダリスキャンレジスタ     | 11 |

| 3.3. TAP コントローラ        | 11 |

| 3.3.1. TAP コントローラのリセット | 11 |

| 3.3.2. コントローラの状態       | 12 |

| 3.4. テストアクセスポート(TAP)   | 14 |

| 3.5. バウンダリスキャン順序       | 15 |

| 4. 命令レジスタ説明            | 15 |

| 4.1. EXTEST 命令         | 15 |

| 4.2. SAMPLE/PRELOAD 命令 | 16 |

| 4.3. BYPASS 命令         | 17 |

| 4.4. CLAMP 命令          | 17 |

| 4.5. HIGHZ 命令          | 17 |

| 5. 使用上のご注意およびお願い事項     | 17 |

| 6. 改訂履歴                | 18 |

| 制具取り扱い上のお願い            | 10 |

# 図目次

| 図 2.1        | JTAG 開発ツールとの接続例                 | 9  |

|--------------|---------------------------------|----|

|              | 命令レジスタ                          |    |

| 図 3.2        | 命令レジスタのシフト方向                    | 10 |

| 図 3.3        | バイパスレジスタの機能                     | 11 |

| 図 3.4        |                                 |    |

| 図 3.5        |                                 | 15 |

| 図 4.1        |                                 |    |

| 図 4.2        | SAMPLE が選択されているときのテストデータの流れ     | 16 |

| 図 4.3        | PRELOAD が選択されているときのテストデータの流れ    | 16 |

|              | BYPASS レジスタが選択されているときのテストデータの流れ |    |

|              | 表目次                             |    |

| 表 1.1        |                                 | 8  |

|              | 信号一覧表                           |    |

|              | モード設定端子                         |    |

| 表 3.1        | JTAG の命令レジスタのビット構成              | 10 |

| <b>基</b> 6 1 | 과닭屠麻                            |    |

# 序章

関連するリファレンスマニュアル

|        | 文書名 |  |

|--------|-----|--|

| データシート |     |  |

| 入出力ポート |     |  |

| 製品個別情報 |     |  |

#### 表記規約

数値表記は以下の規則に従います。

16 進数表記: 0xABC

10 進数表記: 123 または 0d123 (10 進表記であることを示す必要のある場合だけ使用)

2進数表記: 0b111 (ビット数が本文中に明記されている場合は「0b」を省略可)

ローアクティブの信号は信号名の末尾に「N」で表記します。

● 信号がアクティブレベルに移ることを「アサート (assert)」アクティブでないレベルに移ることを「デアサート (deassert)」と呼びます。

複数の信号名は [m:n]とまとめて表記する場合があります。例: S[3:0] は S3,S2,S1,S0 の 4 つの信号名をまとめて表記しています。

本文中 / で囲まれたものはレジスタを定義しています。

例: [ABCD]

同種で複数のレジスタ、フィールド、ビット名は「n」で一括表記する場合があります。

例: [XYZ1], [XYZ2], [XYZ3] →[XYZn]

● 「レジスタ一覧」中のレジスタ名でユニットまたはチャネルは「x」で一括表記しています。

ユニットの場合、「x」はA,B,C...を表します。

例: [ADACRO], [ADBCRO], [ADCCRO]→[ADxCRO]

チャネルの場合、「x」は0,1,2,..を表します。

例: [T32A0RUNA], [T32A1RUNA], [T32A2RUNA]→[T32AxRUNA]

レジスタのビット範囲は [m:n] と表記します。例: [3:0] はビット3から0の範囲を表します。

レジスタの設定値は16進数または2進数のどちらかで表記されています。

例: **[ABCD]**<EFG> = 0x01 (16 進数)、 **[XYZn]**<VW> = 1 (2 進数)

ワード、バイトは以下のビット長を表します。

バイト: 8 ビット ハーフワード: 16 ビット

ワード: 32 ビット

ダブルワード: 64 ビット

レジスタ内の各ビットの属性は以下の表記を使用しています。

R: リードオンリー

W: ライトオンリー

R/W: リード / ライト

- 断りのない限り、レジスタアクセスはワードアクセスだけをサポートします。

- 本文中の予約領域「Reserved」として定義されたレジスタは書き換えを行わないでください。 また、読み出した値を使用しないでください。

- Default 値が「一」となっているビットから読み出した値は不定です。

- 書き込み可能なビットフィールドと、リードオンリー「R」のビットフィールドが共存するレジス タに書き込みを行う場合、リードオンリー「R」のビットフィールドには Default 値を書き込んでく ださい。

Default 値が「一」となっている場合は、個々のレジスタの定義に従ってください。

- ライトオンリーのレジスタのReserved ビットフィールドには Default 値を書き込んでください。 Default 値が「一」となっている場合は、個々のレジスタの定義に従ってください。

- 書き込みと読み出しで異なる定義のレジスタへのリードモディファイライト処理は行わないでくだ さい。

ARM, Cortex ねよい Inumb はARM Limited(またはその子会社)のEUまたはその他の国における登録商標です。 All rights reserved.

ARM®

FLASH については、米国 SST 社 (Silicon Storage Technology, Inc) からライセンスを受けた Super Flash® 技術を使用しています。 Super Flash®は SST 社の登録商標です。

本資料に記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している 場合があります。

### 用語•略語

この仕様書で使用されている用語・略語を記載します。

JTAG Joint Test Action Group

# 1. 概要

本製品には、Joint Test Action Group (JTAG) 規格に適合するインタフェースが用意されています。

絶えず高密度化していく集積回路 (IC)、表面実装デバイス、プリント回路基板 (PCB) に両面実装されるコンポーネント、および埋め込み穴の発達によって、内部基板とチップの接続という物理的接触に依存する内部回路テストは次第に使いにくくなってきました。IC が高度に複雑化してきたため、こうしたチップをすみずみまで実行するテストは大規模化し、作成が難しくなってきました。

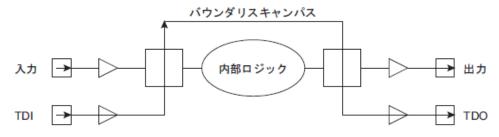

この難しさに対する解決策の1 つとして開発されたのが、「バウンダリスキャン」回路です。バウンダリスキャン回路とは、各ピンとピンに接続されている IC の内部回路との間に設けられる一連のシフトレジスタのことです。通常動作時、それらのバウンダリスキャンセルはバイパスされますが、IC がテストモードになると、テストプログラムの指示に従ってスキャンセルからシフトレジスタパスに沿ってデータが送られ、各種の診断テストが実行されます。テストのときには JTAGインタフェース(TCK, TMS, TDI, TDO および TRST N という 5 種類の信号)が使われます。

JTAG バウンダリスキャンメカニズム (この章では「JTAG メカニズム」と呼びます) により、プロセッサ、プロセッサが接続されているプリント回路基板、および回路基板上の他のコンポーネントの間の接続をテストできます。

JTAG メカニズムそのものには、プロセッサ自体をテストする機能はありません。

この章では、バウンダリスキャン、インタフェースで使われるピンと信号に触れながら、このインタフェースについて説明しています。

表1.1 機能概要

| 機能分類   | 説明                                                                                                                                                                                                                                       |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 規格     | IEEE Standard 1149.1 • 1990 (Includes IEEE Standard 1149.1a • 1993)                                                                                                                                                                      |  |

| 命令     | 標準命令 (BYPASS, SAMPLE/PRELOAD, EXTEST)                                                                                                                                                                                                    |  |

|        | HIGHZ 命令                                                                                                                                                                                                                                 |  |

|        | CLAMP 命令                                                                                                                                                                                                                                 |  |

| IDCODE | なし                                                                                                                                                                                                                                       |  |

| 端子     | <ul> <li>バウンダリスキャンレジスタ(BSR)対象外端子</li> <li>発振回路 (X1, X2, XT1, XT2)専用端子</li> <li>JTAG 制御端子 (BSC)</li> <li>電源/GND (AD コンバータと DA コンバータ基準電源端子を含む)</li> <li>制御端子(TDI/TDO/TMS/TCK/TRST_N)</li> <li>レギュレータ端子</li> <li>リセット端子(RESET_N)</li> </ul> |  |

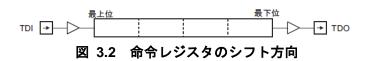

# 2. 構成

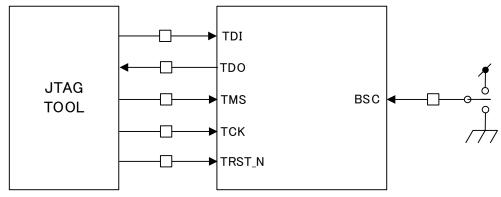

JTAG 対応の開発ツールを、JTAG インタフェースに接続し、デバッグをサポートします。デバッグに関しては、使用する開発ツールの仕様を確認してください。

図2.1 JTAG開発ツールとの接続例

表2.1 信号一覧表

| No. | 信号名    | 信号名称                        | I/O | 参照リファレンスマニュアル |

|-----|--------|-----------------------------|-----|---------------|

| 1   | TDI    | JTAG シリアルデータ入力              | 入力  | 入出力ポート        |

| 2   | TDO    | JTAG シリアルデータ出力              | 出力  | 入出力ポート        |

| 3   | TMS    | JTAG テストモード選択               | 入力  | 入出力ポート        |

| 4   | TCK    | JTAG シリアルクロック入力             | 入力  | 入出力ポート        |

| 5   | TRST_N | JTAG テストリセット入力              | 入力  | 入出力ポート        |

| 6   | BSC    | ICE/JTAG テスト選択入力(準拠イネーブル信号) | 入力  | データシート        |

表2.2 モード設定端子

| モード設定端子(BSC) | 動作モード                         |

|--------------|-------------------------------|

| 0            | Debug Mode として使用できます。         |

| 1            | Boundary Scan Mode として使用できます。 |

# 3. 動作説明 · 機能説明

プロセッサには、次の JTAG コントローラとレジスタが内蔵されています。

- 命令レジスタ

- バウンダリスキャンレジスタ

- バイパスレジスタ

- デバイス識別レジスタ

- テストアクセスポート (TAP) コントローラ

JTAG の基本動作は、TAP コントローラステートマシンが TMS 入力信号をモニタすることです。実行が開始されると、TAP コントローラは実行されるテスト機能を決定します。これは、JTAG 命令レジスタ (IR) のローディングとデータレジスタ (DR) を介してのシリアルデータスキャンを開始します。データスキャンは TMS ピンの状態で次の状態に遷移します。選択されるデータレジスタは命令レジスタの内容で決められます。

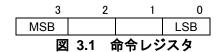

## 3.1. 命令レジスタ

JTAG の命令レジスタには、シフトレジスタを基本とする 4 個のセルが含まれています。このレジスタは、実施対象のテストとアクセスされるテストデータレジスタの両方またはその一方を選択するために使います。表 3.1 の組み合わせに従って、バウンダリスキャンレジスタかバイパスレジスタが選択されます。

選択されるデータレジスタ 命令コード 命令 (MSB → LSB) 0000 **EXTEST** バウンダリスキャンレジスタ 0001 SAMPLE/PRELOAD バウンダリスキャンレジスタ 0100 ~ 1110 0010 HIGHZ バイパスレジスタ 0011 **CLAMP** バイパスレジスタ 1111 **BYPASS** バイパスレジスタ

表3.1 JTAG の命令レジスタのビット構成

命令レジスタのフォーマットは以下のとおりです。

命令コードは、最下位ビットから命令ジレスタにシフトされます。

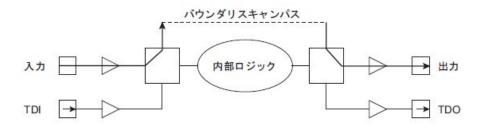

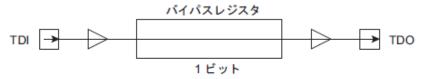

バイパスレジスタは1 ビット幅です。TAP コントローラが Shift-DR (バイパス) 状態のとき、TDI ピンのデータはバイパスレジスタにシフトインされ、バイパスレジスタの出力は TDO 出力ピンにシフトアウトされます。

バイパスレジスタとは、簡単に言えば、特定のテストに必要でない基板レベルの直列バウンダリスキャンチェーン内のデバイスをバイパスできるようにする、迂回のための回路です。バウンダリスキャンチェーン内のバイパスレジスタの論理的な位置は 図 3.3 のとおりです。

バイパスレジスタを使用すれば、基板レベルテスト時にバウンダリスキャンレジスタへのアクセスが 速くなります。

図 3.3 バイパスレジスタの機能

# 3.2. バウンダリスキャンレジスタ

バウンダリスキャンレジスタには、何本かのアナログ出力信号、制御信号を除く全てに入出力があります。 本製品のピンは Shift-DR 状態からバウンダリスキャンレジスタの中へスキャンインすることによって任意のパターンをドライブすることができます。プロセッサに入るデータは、バウンダリスキャンレジスタを許可して Capture-DR 状態のときにシフトすることにより検査されます。

バウンダリスキャンレジスタは、シフトレジスタを基本とするパスです。このパス内のセルは、入力 と出力が端子に接続されています。

TDI 入力はバウンダリスキャンレジスタの最下位ビット (LSB) に取り込まれ、バウンダリスキャンレジスタの最上位ビット (MSB) は TDO 出力から取り出されます。

## 3.3. TAP コントローラ

プロセッサには、IEEE JTAG 規格に規定されている 16 ステートの TAP コントローラが実現されています。

#### 3.3.1. TAP コントローラのリセット

TAP コントローラのステートマシンは、次の方法によりリセット状態になります。

TRST\_N 信号入力のアサート (Low) により、TAP コントローラはリセットされます。または、プロセッサのリセット解除後 TMS を 1 にした状態で、TCK 入力の立ち上がりエッジを連続 5 個入力する

ことで TAP コントローラはリセットされます。TMS を 1 に保てば、リセット状態が保たれます。

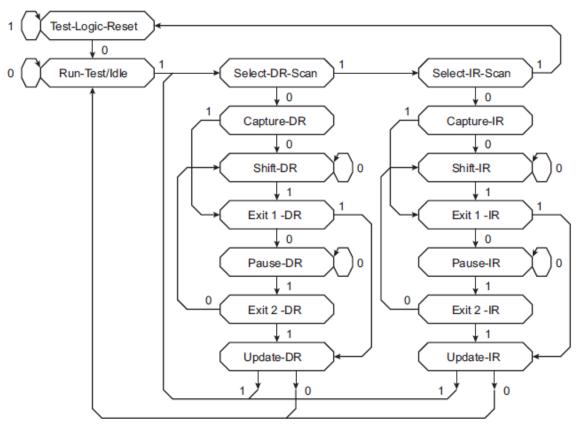

#### 3.3.2. コントローラの状態

図 3.4 に TAP コントローラの状態遷移図を示します。TCK の立ち上がりエッジで、TMS が 0 か 1 のどちらの値を取るかによって TAP コントローラの状態が変化します。状態の遷移を示す矢印のわきに TMS の取る値を示します。

図 3.4 TAPコントローラ状態遷移図

以下コントローラの各状態について説明します。図 3.4 の左側のカラムはデータカラムで右側のカラムは命令カラムです。データカラムと命令カラムはそれぞれデータレジスタ (DR)、命令レジスタ (IR)を表します。

#### - Test-Logic-Reset

TAP コントローラが Reset 状態の場合は、デフォルトとしてデバイス識別レジスタが選択されます。バウンダリスキャンレジスタの最上位 1 ビットは 0 にクリアされ、出力はディセーブルされます。

TMS が 1 の期間は、TAP コントローラは Test-Logic-Reset 状態を保持します。 Test-Logic-Reset 状態のとき TMS に 0 を入力すると、TAP コントローラは Run-Test/Idle 状態に遷移します。

#### - Run-Test/Idle

Run-Test/Idle 状態では、組み込み自己テスト (BIST) 0命令など特定の命令が設定されているときのみ、IC はテストモードになります。Run-Test/Idle 状態で実行されない命令に対しては、現在の命令により選択されているテストデータレジスタは前の状態を保持します。

TMS が 0 の期間は、TAP コントローラは Run-Test/Idle 状態を保持します。TMS に 1 を入力すると、TAP コントローラは Select-DR-Scan 状態に遷移します。

#### Select-DR-Scan

Select-DR-Scan 状態はTAP コントローラの一時的な状態です。ここでは、IC が特別な動作をすることはありません。

TAP コントローラが Select-DR-Scan 状態のとき TMS に 0 を入力すると Capture-DR 状態に遷移します。TMS に 1 を入力すると命令カラムの Select-IR-Scan 状態に遷移します。

#### Select-IR-Scan

Select-IR-Scan 状態は TAP コントローラの一時的な状態です。ここでは IC が特別な動作をすることはありません。

TAP コントローラが Select-IR-Scan 状態のとき、TMS に 0 を入力すると Capture-IR 状態に遷移します。TMS に 1 を入力すると TAP コントローラは Test-Logic-Reset 状態に戻ります。

#### Capture-DR

TAP コントローラが Capture-DR 状態のとき、命令レジスタによって選択されたデータレジスタがパラレル入力をもっている場合、データがデータレジスタにパラレルにロードされます。データレジスタにパラレル入力がない場合、あるいは選択されたテストデータレジスタにデータをロードする必要がない場合は、データレジスタは前の状態を保持します。

TAP コントローラが Capture-DR 状態のとき TMS に 0 を入力すると、Shift-DR 状態に 遷移します。TMS に 1 を入力すると TAP コントローラは Exit 1-DR 状態に遷移します。

#### Shift-DR

TAP コントローラが Shift-DR 状態のとき、TDI-TDO 間に接続されたデータレジスタは シリアルにデータをシフトアウトします。

TAP コントローラが Shift-DR 状態のとき、TMS が 0 のあいだ Shift-DR 状態を保持します。TMS に 1 を入力すると TAP コントローラは Exit 1-DR 状態に遷移します。

#### Exit 1-DR

Exit 1-DR 状態は TAP コントローラの一時的な状態です。

TAP コントローラが Exit 1-DR 状態のとき、TMS に 0 を入力すると Pause-DR 状態に 遷移します。TMS に 1 を入力すると Update-DR 状態に遷移します。

#### Pause-DR

Pause-DR 状態は命令レジスタによって選択されたデータレジスタのシフト動作を一時的に停止します。命令レジスタ、データレジスタは現在の状態を保持します。

TAP コントローラが Pause-DR 状態のとき、TMS が 0 のあいだ、この状態を保持します。TMS に 1 を入力すると Exit 2-DR 状態に遷移します。

#### Exit 2-DR

Exit 2-DR 状態は TAP コントローラの一時的な状態です。

TAP コントローラが Exit 2-DR 状態のとき、TMS に 0 を入力すると、Shift-DR 状態に戻ります。TMS に 1 を入力すると Update-DR 状態に遷移します。

#### Update-DR

Update-DR 状態では、TCK の立ち上がりエッジに同期してパラレル出力をもっているレジスタからデータをパラレルに出力します。パラレル出力ラッチをもっているデータレジスタはシフト中にデータを出力することはなく、この状態でのみデータを出力します。

TAP コントローラが Update-DR 状態のとき TMS に 0 を入力すると Run-Test/Idle 状態 に遷移します。 TMS に 1 を入力すると Select-DR-Scan 状態に遷移します。

#### Capture-IR

Capture-IR 状態ではデータは命令レジスタにパラレルにロードされます。ロードされるデータは"0001"です。Capture-IR 状態は命令レジスタのテストに使用します。命令レジスタの故障はロードされたデータをシフトアウトすることにより検出できます。

TAP コントローラが Capture-IR 状態のとき TMS に 0 を入力すると Shift-IR 状態に遷移します。 TMS に 1 を入力すると Exit 1-IR 状態に遷移します。

#### Shift-IR

Shift-IR 状態では、命令レジスタが TDI-TDO 間に接続され、TCK の立ち上がりエッジに同期してロードされたデータをシリアルにシフトアウトします。

TAP コントローラが Shift-IR 状態のとき TMS が 0 のあいだ、この状態を保持します。 TMS に 1 を入力すると、Exit 1-IR 状態に遷移します。

#### - Exit 1-IR

Exit 1-IR 状態は TAP コントローラの一時的な状態です。

TAP コントローラが Exit 1-IR 状態のとき TMS に 0 を入力すると、Pause-IR 状態に遷移します。TMS に 1 を入力すると Update-IR 状態に遷移します。

#### Pause-IR

Pause-IR 状態は命令レジスタのシフト動作を一時的に停止する状態です。命令レジスタとデータレジスタはそのままの状態を保持します。

TAP コントローラが Pause-IR 状態のとき、TMS が 0 のあいだ、この状態を保持します。 TMS に 1 を入力すると Exit 2-IR 状態に遷移します。

#### - Exit 2-IR

Exit 2-IR 状態は TAP コントローラの一時的な状態です。

TAP コントローラが Exit 2-IR 状態のとき、TMS に 0 を入力すると、Shift-IR 状態に遷移します。TMS に 1 を入力すると Update-IR 状態に遷移します。

#### Update-IR

Update-IR 状態は命令レジスタにシフトされた命令を TCK の立ち上がりエッジに同期してパラレルに出力し、命令を更新します。

TAP コントローラが Update-IR 状態のとき、TMS に 0 を入力すると、Run-Test/Idle 状態に遷移します。TMS に 1 を入力すると、Select-DR-Scan 状態に遷移します。

# 3.4. テストアクセスポート(TAP)

テストアクセスポート (TAP) は、5 個の信号ピン  $TRST_N$ 、TDI、TDO、TMS、および TCK で構成 されます。直列のテストデータ、命令、および実施するテストの制御は、この 5 個の信号ピンを通じて 送受信されます。

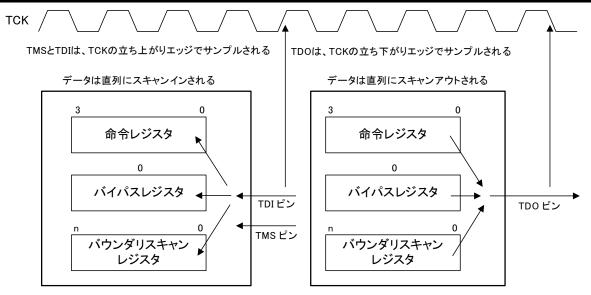

図 3.5 のように、 データは 3 本のレジスタ (命令レジスタ、バイパスレジスタ、バウンダリスキャンレジスタ) のうちの 1 本に TDI ピンから直列にスキャンインされるか、またはその 3 本のレジスタの 1 本から TDO ピンにスキャンアウトされます。

TMS 入力は、主 TAP コントローラステートマシンの状態遷移を制御するものです。TCK 入力は直列 JTAG データが同期してシフトされるようにする専用のテストクロックであり、チップ固有クロックやシステムクロックには依存していません。

図 3.5 JTAG テストアクセスポート

TDI ピンと TMS ピンのデータは、入力クロック信号 TCK の立ち上がりエッジでサンプルされます。 TDO ピンのデータは、クロック信号 TCK の立ち下がりエッジで変化します。

## 3.5. バウンダリスキャン順序

バウンダリスキャン順序はリファレンスマニュアルの「製品個別情報」の章を参照してください。

# 4. 命令レジスタ説明

# 4.1. EXTEST 命令

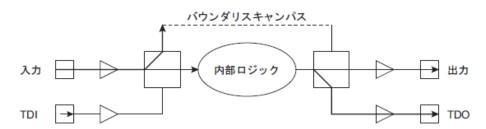

EXTEST 命令は外部接続テストに使用します。EXTEST 命令では、出力端子の BSR セルは Update-DR 時にテストパターンを出力し、入力端子の BSR セルは Capture-DR 時にテスト結果を取り込みます。

通常、EXTEST 命令を選択するまえに SAMPLE/PRELOAD 命令を使ってバウンダリスキャンレジスタを初期化します。バウンダリスキャンレジスタを初期化しておかないと、Update-DR 状態で不確定なデータが伝送され、IC 間でバスのコンフリクトが起こる可能性があります。 EXTEST 命令が選択されているあいだのデータの流れを図 4.1 にしめします。

図 4.1 EXTEST 命令が選択されているときのテストデータの流れ

次に外部接続テストの基本的なテスト手順を示します。

- 1. TAP コントローラを初期化して、Test-Logic-Reset 状態にします。

- 2. 命令レジスタに SAMPLE/PRELOAD 命令をロードします。これによりバウンダリスキャンレジスタが TDI-TDO 間に接続されます。

- 3. 確定したデータをシフトインすることにより、バウンダリスキャンレジスタを初期化します。

- 4. 最初のテストデータをバウンダリスキャンレジスタにロードします。

- 5. 命令レジスタに EXTEST 命令をロードします。

- 6. 入力端子に印加されているデータを入力用バウンダリスキャンレジスタに取り込みます。

- 7. 取り込んだデータをシフトアウトすると同時に、次のテストパターンをシフトインします。

- 8. 出力用バウンダリスキャンレジスタにシフトインされたテストパターンを出力端子に出力します。

- 9. 6 から 8 をテストパターンごとに繰り返します。

## 4.2. SAMPLE/PRELOAD 命令

この命令は TDI-TDO 間をバウンダリスキャンレジスタで接続します。名前が示すとおり、SAMPLE/PRELOAD 命令には次の 2 つの機能があります。

SAMPLE は IC の I/O パッドを観測するのに使います。SAMPLE が I/O パッドを観測しているあいだ、内部ロジックは IC の I/O 端子から切り離されません。SAMPLE は Capture-DR 状態で実行します。通常動作中、TCK の立ち上がりエッジで IC の I/O 端子の値を読み取ることが SAMPLE の主な用途です。図 4.2 に SAMPLE/PRELOAD 命令の SAMPLE を実行しているあいだのデータの流れを示します。

図 4.2 SAMPLE が選択されているときのテストデータの流れ

PRELOAD は他の命令を選択するまえに、バウンダリスキャンレジスタを初期化するのに使います。例えば、前に述べたように EXTEST 命令を選択するまえに PRELOAD を用いてバウンダリスキャンレジスタを初期化します。PRELOAD はシステムロジックの通常動作に影響を与えずに、バウンダリスキャンレジスタにデータをシフトします。図 4.3 に SAMPLE/PRELOAD 命令の PRELOAD を実行しているあいだのデータの流れを示します。

図 4.3 PRELOAD が選択されているときのテストデータの流れ

### 4.3. BYPASS 命令

BYPASS 命令は IC を制御、観測する必要がないテストの場合に、バイパスレジスタを TDI-TDO 間に接続することにより IC をバイパスする最短のシリアルパスを構成します。BYPASS 命令はチップ上のシステムロジックの通常動作には影響を与えません。図 4.4 に示すように BYPASS 命令が選択されているあいだ、データはバイパスレジスタを通ります。

図 4.4 BYPASS レジスタが選択されているときのテストデータの流れ

# 4.4. CLAMP 命令

CLAMP は PRELOAD 命令によって設定されたバウンダリスキャンレジスタの値を出力し、かつバイパス動作を行います。

CLAMP 命令は TDI と TDO 間に BYPASS レジスタを選択します。

## 4.5. HIGHZ 命令

HIGHZ 命令 は内部論理回路からの出力を Disable 状態にします。HIGHZ 命令が実行されると、3 ステート出力をハイ・インピーダンス状態にします。

HIGHZ 命令も TDI と TDO 間に BYPASS レジスタを選択します。

# 5. 使用上のご注意およびお願い事項

本節では、当プロセッサで採用している JTAG バウンダリスキャン処理の注意点について説明します。

- JTAG 回路のリセット解除は下記の2種類のどちらかの手順を選択してください。

- TRST Nをアサートして JTAG 回路を初期化後デアサート

- TMS 端子=1 の状態で、TCK に 5 クロック以上供給

- JTAGバウンダリスキャンテスト(BSC端子を"1"にして行う動作)とNORMALモード(BSC端子を"0" にして行う動作)を切り替える場合は電源を立ち上げ直してください。

- TRST\_N 端子が無い製品の場合、テストロジックリセットは TMS=1 のまま TCK の立ち上がりエッジを 5 回入力してください。

- 外部リセット(RESET\_N)期間中 BSC は使用できません。

# 6. 改訂履歴

表6.1 改訂履歴

| Revision | Date       | Description                                                                                                                                                                                         |  |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.0      | 2017-02-07 | 新規                                                                                                                                                                                                  |  |

| 1.1      | 2017-04-17 | ・表 1.1 の機能分類(命令)の"ただし書き"を削除と機能分類(端子)にリセット端子を追加<br>・表 2.2 の動作モードの説明見直し<br>・「2. 構成」に記載していた" TRST_N 端子が無い製品の場合"の説明は、「5.使用上のご注意およびお願い事項」に移動<br>・外部リセット(RESET_N)期間中 BSC が使用できないことを「5.使用上のご注意およびお願い事項」に追記 |  |

| 1.2      | 2017-07-14 | ・社名変更による変更<br>表紙<br>商標の見直し<br>製品取り扱い上のお願いの差し替え<br>・5. 使用上のご注意およびお願い事項<br>2 項目目の●の表記(JTAG バウンダリスキャン)を見直し                                                                                             |  |

#### 製品取り扱い上のお願い

株式会社東芝およびその子会社ならびに関係会社を以下「当社」といいます。 本資料に掲載されているハードウエア、ソフトウエアおよびシステムを以下「本製品」といいます。

- 本製品に関する情報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を得て本 資料を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

- 当社は品質、信頼性の向上に努めていますが、半導体・ストレージ製品は一般に誤作動または故障する場合があります。本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウエア・ソフトウエア・システムに必要な安全設計を行うことをお願いします。なお、設計および使用に際しては、本製品に関する最新の情報(本資料、仕様書、データシート、アプリケーションノート、半導体信頼性ハンドブックなど)および本製品が使用される機器の取扱説明書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

- 本製品は、特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な財産損害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下"特定用途"という)に使用されることは意図されていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇宙機器、医療機器、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連機器、昇降機器、電力機器、金融関連機器などが含まれますが、本資料に個別に記載する用途は除きます。特定用途に使用された場合には、当社は一切の責任を負いません。なお、詳細は当社営業窓口までお問い合わせください。

- 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

- ◆ 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用することはできません。

- ◆ 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及 び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をしておりません。

- 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あるいは その他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、「米国輸出 管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず当社営業窓口までお問い合わせください。本製品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査の上、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は一切の責任を負いかねます。

# 東芝デバイス&ストレージ株式会社