# 32 ビット RISC マイクロコントローラ TMPM3H グループ(1)

リファレンスマニュアル クロック制御と動作モード (CG-M3H(1)-D)

**Revision 3.1**

2019-07

東芝デバイス&ストレージ株式会社

## 目次

| 序早                           | 5  |

|------------------------------|----|

| 関連するドキュメント                   | 5  |

| 表記規約                         | 6  |

| 用語・略語                        | 8  |

| 1. 概要                        | 9  |

| 2. クロック制御                    | 10 |

| 2.1. クロックの種類                 | 10 |

| 2.2. リセット動作による初期値            | 10 |

| 2.3. クロック系統図                 |    |

| 2.4. ウォーミングアップ機能             | 12 |

| 2.4.1. 高速発振用ウォーミングアップカウンタ    |    |

| 2.4.2. 低速発振用ウォーミングアップカウンタ    | 13 |

| 2.4.3. ウォーミングアップタイマの使用方法     | 13 |

| 2.5. fsys 用クロック逓倍回路(PLL)     | 14 |

| 2.5.1. リセット解除後の PLL 設定       | 14 |

| 2.5.2. PLL 逓倍値の計算式と設定例       | 14 |

| 2.5.3. 動作中の PLL 逓倍値の変更       | 15 |

| 2.5.4. PLL 動作開始/停止/切り替えシーケンス | 16 |

| 2.6. システムクロック                | 17 |

| 2.6.1. システムクロックの設定方法         | 17 |

| 2.7. クロック供給設定機能              | 19 |

| 2.8. クロックの端子出力機能             | 19 |

| 2.9. プリスケーラクロック              | 19 |

| 3. 動作モード                     | 20 |

| 3.1. 動作モードの詳細                | 20 |

| 3.1.1. 各モードの特長               | 20 |

| 3.1.2. 低消費電力モード              | 21 |

| 3.1.3. 低消費電力モードの選択           | 21 |

| 3.1.4. 低消費電力モードにおける周辺機能状態    | 22 |

| 3.2. モード状態遷移                 | 23 |

| 3.2.1. IDLE モード遷移フロー         | 23 |

| 3.2.2. STOP1 モード遷移フロー        | 24 |

| 3.2.3. STOP2 モード遷移フロー        | 24 |

| 3.3. 低消費電力モードからの復帰           |    |

| 3.3.1. 低消費電力モードの解除ソース        |    |

| 3.3.2. 低消費電力モード遷移時のウォーミングアップ |    |

| 3.3.3. STOP2 モードからの復帰        | 29 |

## **TOSHIBA**

| 3   | 3.4. モード遷移によるクロック動作                                  | 30   |

|-----|------------------------------------------------------|------|

|     | 3.4.1. NORMAL→IDLE→NORMAL 動作モード遷移                    | 30   |

|     | 3.4.2. NORMAL→STOP1→NORMAL 動作モード遷移                   | 30   |

|     | 3.4.3. NORMAL→STOP2→RESET→NORMAL 動作モード遷移             | 31   |

| 4.  | レジスタの説明                                              | 32   |

| 4   | - 1. レジスター覧                                          | 32   |

| 4   | l.2. レジスタ詳細                                          | 33   |

|     | 4.2.1. [CGPROTECT] (CG ライトプロテクトレジスタ)                 | 33   |

|     | 4.2.2. [CGOSCCR] (発振制御レジスタ)                          | 33   |

|     | 4.2.3. <i>[CGSYSCR]</i> (システムクロック制御レジスタ)             | 34   |

|     | 4.2.4. <i>[CGSTBYCR]</i> (スタンバイ制御レジスタ)               | 35   |

|     | 4.2.5. <i>[CGSCOCR]</i> (SCOUT 出力制御レジスタ)             | 35   |

|     | 4.2.6. <i>[CGPLL0SEL]</i> (fsys 用 PLL セレクトレジスタ)      | 36   |

|     | 4.2.7. [CGWUPHCR] (高速発振ウォーミングアップレジスタ)                | 36   |

|     | 4.2.8. <i>[CGWUPLCR]</i> (低速発振ウォーミングアップレジスタ)         | 37   |

|     | 4.2.9. <i>[CGF</i> SYS <i>ENA]</i> (fsys 供給停止レジスタ A) | 38   |

|     | 4.2.10. <i>[CGFSYSENB]</i> (fsys 供給停止レジスタ B)         | 40   |

|     | 4.2.11. <i>[CGSPCLKEN]</i> (ADC、トレース用クロック供給停止レジスタ)   | 41   |

|     | 4.2.12. <i>[RLMLOSCCR]</i> (低速発振制御レジスタ)              | 41   |

|     | 4.2.13. <i>[RLMSHTDNOP]</i> (電源遮断制御レジスタ)             | 41   |

|     | 4.2.14. <i>[RLMPROTECT]</i> (RLM ライトプロテクトレジスタ)       | 42   |

| 5.  | 製品別情報                                                | 43   |

| 5   | 5.1. [CGFSYSENA]                                     | 43   |

| 5   | 5.2. [CGFSYSENB]                                     | 44   |

| 6.  | 改訂履歴                                                 | . 45 |

| 411 |                                                      | 4-7  |

## 図目次

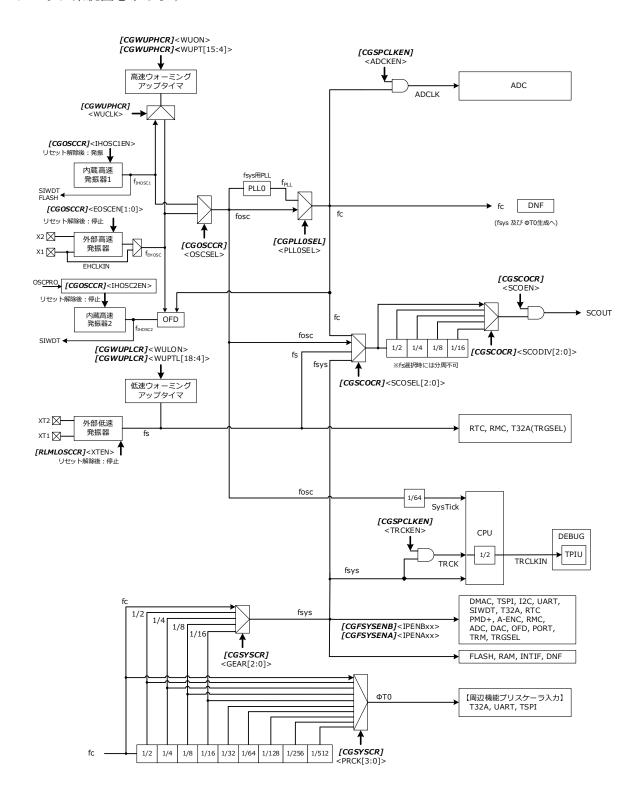

| 図 2.1 | クロック系統図                                         | 11 |

|-------|-------------------------------------------------|----|

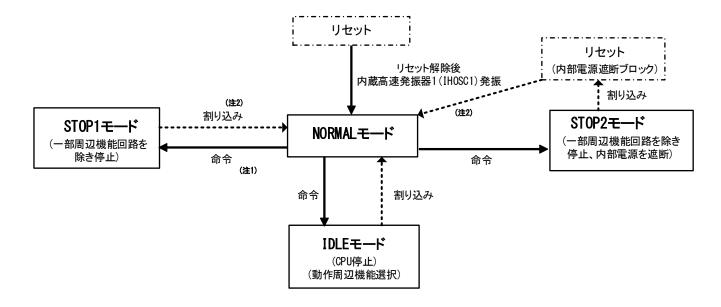

| 図 3.1 | 状態遷移                                            | 23 |

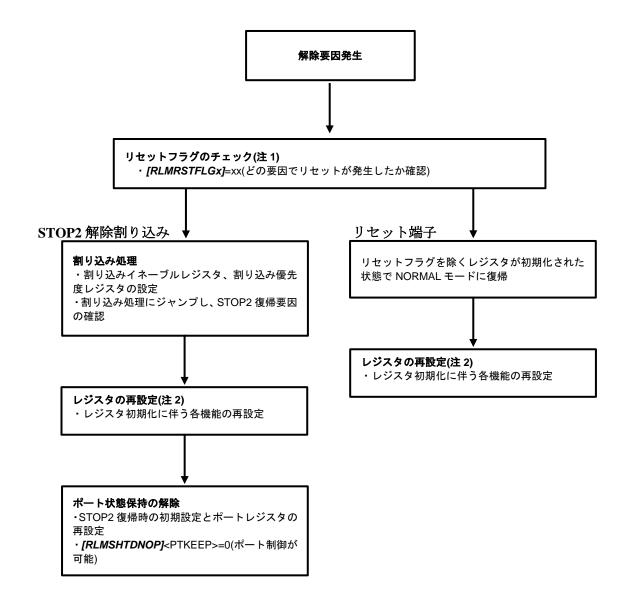

| 図 3.2 | ? STOP2 モード復帰フロー                                | 29 |

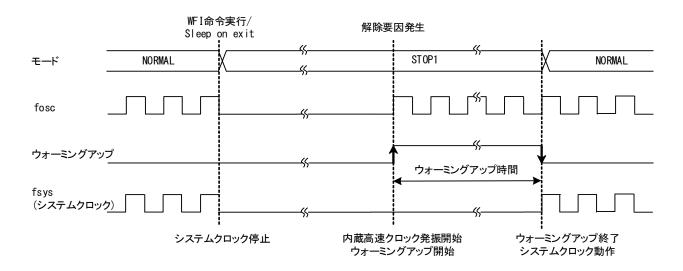

| 図 3.3 | 3 NORMAL→STOP1→NORMAL 動作モード遷移                   | 30 |

| 図 3.4 | I NORMAL→STOP2→RESET→NORMAL 動作モード遷移             | 31 |

|       | 表目次                                             |    |

| 表 2.1 | [CGPLL0SEL] <pll0set[23:0]>設定詳細</pll0set[23:0]> | 14 |

|       | 2 PLL 補正值(例)                                    |    |

|       | 3 PLL0SET 設定値(例)                                |    |

| 表 2.4 | ↓ 動作周波数(単位:MHz)例                                | 17 |

| 表 2.5 | 5 SCOUT 端子使用可否一覧                                | 19 |

| 表 3.1 |                                                 | 21 |

| 表 3.2 | 2 低消費電力モード別 ブロック動作状態一覧                          | 22 |

| 表 3.3 | 3 解除ソース-覧                                       | 26 |

| 表 3.4 | <b>↓ ウォーミングアップ</b>                              | 28 |

| 表 5.1 | [CGFSYSENA]の製品別割り当て                             | 43 |

|       |                                                 |    |

| 表 6.1 | 改訂履歴                                            | 45 |

## 序章

関連するドキュメント

| 文書名       |

|-----------|

| 例外        |

| 電源とリセット動作 |

#### 表記規約

数値表記は以下の規則に従います。

16 進数表記: 0xABC

10 進数表記: 123 または 0d123 (10 進表記であることを示す必要のある場合だけ使用)

2 進数表記: 0b111 (ビット数が本文中に明記されている場合は「0b」を省略可)

● ローアクティブの信号は信号名の末尾に「\_N」で表記します。

● 信号がアクティブレベルに移ることを「アサート (assert)」アクティブでないレベルに移ることを「デアサート (deassert)」と呼びます。

● 複数の信号名は [m:n]とまとめて表記する場合があります。

例: S[3:0] はS3.S2.S1.S0の4つの信号名をまとめて表記しています。

◆ 本文中 [] で囲まれたものはレジスタを定義しています。

例: [ABCD]

● 同種で複数のレジスタ、フィールド、ビット名は「n」で一括表記する場合があります。

例: [XYZ1], [XYZ2], [XYZ3] → [XYZn]

「レジスター覧」中のレジスタ名でユニットまたはチャネルは「x」で一括表記しています。

ユニットの場合、「x」は A, B, C... を表します。

例: [ADACR0], [ADBCR0], [ADCCR0]→[ADxCR0]

チャネルの場合、「x」は 0.1.2... を表します。

例: [T32A0RUNA], [T32A1RUNA], [T32A2RUNA]→[T32AxRUNA]

● レジスタのビット範囲は [m:n] と表記します。

例: [3:0] はビット3から0の範囲を表します。

レジスタの設定値は16進数または2進数のどちらかで表記されています。

例: [ABCD]<EFG> = 0x01 (16 進数)、 [XYZn]<VW> = 1 (2 進数)

ワード、バイトは以下のビット長を表します。

バイト: 8 ビット ハーフワード: 16 ビット ワード: 32 ビット ダブルワード: 64 ビット

レジスタ内の各ビットの属性は以下の表記を使用しています。

R: リードオンリー W: ライトオンリー R/W: リード / ライト

- 断りのない限り、レジスタアクセスはワードアクセスだけをサポートします。

- 本文中の予約領域「Reserved」として定義されたレジスタは書き換えを行わないでください。 また、読み出した値を使用しないでください。

- Default 値が「―」となっているビットから読み出した値は不定です。

- 書き込み可能なビットフィールドと、リードオンリー「R」のビットフィールドが共存するレジスタに書き込みを行う場合、リードオンリー「R」のビットフィールドには Default 値を書き込んでください。

Default 値が「—」となっている場合は、個々のレジスタの定義に従ってください。

- ライトオンリーのレジスタの Reserved ビットフィールドには Default 値を書き込んでください。Default 値が「―」となっている場合は、個々のレジスタの定義に従ってください。

- 書き込みと読み出しで異なる定義のレジスタへのリードモディファイライト処理は行わないでください。

6 / 47 2019-07-23

Arm,Cortex および Thumb は Arm Limited(またはその子会社)の US またはその他の国における 登録商標です。 All rights reserved.

FLASH メモリについては、米国 SST 社 (Silicon Storage Technology, Inc.) からライセンスを受けた Super Flash®技術を使用しています。Super Flash®は SST 社の登録商標です。

本資料に記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している 場合があります。

#### 用語・略語

この仕様書で使用されている用語・略語の一部を記載します。

ADC Analog to Digital Converter

A-ENC Advanced Encoder input Circuit

CG Clock control and Operation Mode

DAC Digital to Analog Converter

DNF Digital Noise Filter

ELOSC External Low speed Oscillator EHOSC External High speed Oscillator fsys Frequency of SYSTEM Clock IHOSCx Internal High speed Oscillator X

INT Interrupt

I<sup>2</sup>C Inter-Integrated Circuit

I2CS I<sup>2</sup>C wake up circuit from Standby mode

LVD Voltage Detection Circuit NMI Non-Maskable Interrupt

OFD Oscillation Frequency Detector

PMD+ Programmable Motor Control Circuit Plus

POR Power On Reset Circuit

RMC Remote control Signal Preprocessor RLM Reset LOSC<Low Power> Manager

SCOUT Source Clock Output

SIWDT Clock Selective Watchdog Timer

TPIU Trace Port Interface Unit TRGSEL Trigger Selection circuit

TSPI Toshiba Serial Peripheral Interface

T32A 32-bit Timer Event counter

UART Universal Asynchronous Receiver Transmitter

## 1. 概要

クロック/モード制御ブロックでは、クロックギアやプリスケーラクロックの選択、発振器のウォーミングアップなどを設定することが可能です。

また、動作モードとして NORMAL モードと低消費電力モードがあり、使用方法に応じモード遷移を行うことで消費電力を抑えることができます。

クロックに関連する機能としては以下のようなものがあります。

- システムクロックの制御

- プリスケーラクロックの制御

## 2. クロック制御

## 2.1. クロックの種類

クロックの一覧を以下に示します。

EHCLKIN:外部から入力されるクロック

fosc: 内部発振回路で生成されるクロックと X1、X2 端子より入力されるクロックの選択後

のクロック

f<sub>PLL</sub>: PLLにより逓倍されたクロック

fc : [CGOSCCR]<OSCSEL>で選択されたクロック(高速クロック)

fs : 外部低速発振器から出力されるクロック

fsys : [CGSYSCR]<GEAR[2:0]>で選択されたシステムクロック

$\phi$ TO : [CGSYSCR]<PRCK[3:0]>で選択されたクロック (プリスケーラクロック)

f<sub>IHOSC1</sub>: 内蔵高速発振器 1 で生成されるクロックf<sub>IHOSC2</sub>: 内蔵高速発振器 2 で生成されるクロック

ADCLK: AD コンバータ用変換クロック

TRCLKIN:デバッグ回路(ETM)のトレース機能用クロック

#### 2.2. リセット動作による初期値

リセット動作により、クロック設定は下記のような状態に初期化されます。

外部高速発振器: 停止内蔵高速発振器 1: 発振内蔵高速発振器 2: 停止外部低速発振器: 停止PLL(逓倍回路): 停止

ギアクロック : fc(分周なし)

#### 2.3. クロック系統図

クロック系統図を示します

図 2.1 クロック系統図

### 2.4. ウォーミングアップ機能

ウォーミングアップ機能は、自動で高速発振用ウォーミングアップカウンタを起動する STOP1 モード 解除時の発振安定時間を確保するための機能の他、外部発振器や内蔵発振器の安定待ちのために高速発振/低速発振それぞれの専用ウォーミングアップカウンタを使用したカウントアップタイマとしても使用可能です。

この章では、ウォーミングアップタイマ用レジスタへの設定方法と、カウントアップタイマとして使用する場合について説明しています。STOP1 モード解除時の詳細説明については、「3.3.2. 低消費電力モード遷移時のウォーミングアップ」を参照してください。

#### 2.4.1. 高速発振用ウォーミングアップカウンタ

高速発振専用ウォーミングアップカウンタとして、16ビットのアップカウンタを内蔵しています。STOP1 モードへ遷移前に設定する場合も、下記の計算式で算出し、下位4ビットを切り捨てて、上位12ビットへ設定します。レジスタは、*[CGWUPHCR]*<WUPT[15:4]>に設定することになります。設定値が0の場合でも、下位4bit分のカウントを実行するため、16を減算しています。

#### <計算式>

ウォーミングアップカウンタ値(16 ビット) = (ウォーミングアップ時間(s) ÷ クロック周期(s)) - 16

(例) 発振器 10MHz(クロック周期 100ns)で、ウォーミング時間 5ms を設定する場合 ウォーミングアップカウンタ値(16 ビット) = (5ms ÷ 100ns) - 16 = 50000 - 16 = 49984 = 0xC340

レジスタへは、上位 12 ビットを設定しますので、下記のように設定します。 *[CGWUPHCR]*<WUPT[15:4]> = 0xC34

10MHz の場合、 $0 \le <$ WUPT[15:4]>  $\le 0$ xFFF の設定範囲のため、ウォーミングアップ時間は、1.6µs  $\sim 6.5536$ ms となります。

#### 2.4.2. 低速発振用ウォーミングアップカウンタ

低速発振専用ウォーミングアップカウンタとして、19 ビットのアップカウンタを内蔵しています。下記の計算式で算出し、下位 4 ビットを切り捨てて、上位 15 ビットへ設定します。レジスタは、[CGWUPLCR]<WUPTL[18:4]>に設定することになります。設定値が0の場合でも、下位4bit分のカウントを実行するため、16を減算しています。

<計算式>

ウォーミングアップカウンタ値(19 ビット) = (ウォーミングアップ時間(s) ÷ クロック周期(s))- 16

(例) 発振器 32kHz(クロック周期 31.25μs)で、ウォーミング時間 50ms を設定する場合 ウォーミングアップカウンタ値(19 ビット) = (50ms ÷ 31.25μs) - 16 = 1600 - 16 = 1584 = 0x00630

レジスタへは、上位 15 ビットを設定しますので、下記のように設定します。 [CGWUPLCR]<WUPTL[18:4]>=0x0063

32kHz の場合、 $0 \le <$ WUPTL[18:4]>  $\le 0$ x7FFF の設定範囲のため、ウォーミングアップ時間は、500μs ~ 16.384s となります。

#### 2.4.3. ウォーミングアップタイマの使用方法

ウォーミングアップ機能の使用方法を説明します。

(1)クロックの選択

高速発振の場合は、ウォーミングアップカウンタでカウントするクロック種別(内蔵発振/外部発振)を、*[CGWUPHCR]*<WUCLK>で選択します。

- (2) ウォーミングアップカウンタ設定値の算出 ウォーミングアップ時間は、高速発振/低速発振用のカウンタへ任意の値が設定可能です。それ ぞれの計算式から算出し、設定してください。

- (3) ウォーミングアップの開始および終了確認

ソフトウエア (命令) によりウォーミングアップの開始および終了確認を行う場合、 [CGWUPHCR]<WUON> (または[CGWUPLCR]<WULON>) へ "1"を設定することでウォーミングアップカウントスタートします。終了は[CGWUPHCR]<WUEF> (または[CGWUPLCR]<WULEF>) が "1" → "0" になることで判別します。 "1"でウォーミングアップ中、 "0"で終了を示します。 カウント終了後、カウンタはリセットされて初期状態に戻ります。

カウンタ動作中に*[CGWUPHCR]*<WUON>(または*[CGWUPLCR]*<WULON>)へ"0"を書き込んでも、強制終了にはなりません。"0"書き込みは無視されます。

注1) ウォーミングアップタイマは発振クロックで動作しているため、発振周波数にゆらぎがある場合は誤差を含みます。従って概略時間としてとらえる必要があります。

## 2.5. fsys 用クロック逓倍回路(PLL)

クロック逓倍回路は、高速発振器の出力クロック fosc の周波数(6MHz  $\sim$ 12MHz)に最適な条件で逓倍した  $f_{PLL}$  クロック(最大 40MHz)を出力する回路です。これにより、発振器への入力周波数は低く内部クロックは高速にすることが可能です。

#### 2.5.1. リセット解除後の PLL 設定

PLL はリセット解除後、ディセーブルです。

PLLを使用するためには、[CGPLL0SEL]<PLL0ON>が"0"の状態で、[CGPLL0SEL]<PLL0SET>の逓倍値の設定を行った後、PLL の初期化時間として約 $100\,\mu$ s 経過後に、<PLL0ON> を"1" に設定してPLL の動作を開始します。その後、ロックアップ時間約 $400\,\mu$ s 経過後に、[CGPLL0SEL]<PLL0SEL>を"1" に設定することにより、fosc を逓倍した $f_{PLL}$  クロックを使用することができます。

なお、PLL 動作が安定するまでの時間は、ウォーミングアップ機能などを用いて確保する必要があります。

#### 2.5.2. PLL 逓倍値の計算式と設定例

PLL 逓倍値を設定する[CGPLL0SEL]<PLL0SET[23:0]>の内訳詳細を下記に示します。

| PLL0SET の内訳 | 機能          |                                              |              |  |  |  |  |  |

|-------------|-------------|----------------------------------------------|--------------|--|--|--|--|--|

| [23:17]     | 補正値設定       | fosc/450k の商(整数)。表 2.2                       | を参照してください    |  |  |  |  |  |

| [16:14]     | fosc 設定     | 111: 20 < fosc≤24 (unit: MF                  | Hz)          |  |  |  |  |  |

|             |             | 011: 10 <fosc≤20< th=""><th></th></fosc≤20<> |              |  |  |  |  |  |

|             |             | 010: Reserved                                |              |  |  |  |  |  |

|             |             | 001: 6≤fosc≤10                               |              |  |  |  |  |  |

| 140,407     | <del></del> | 000: Reserved                                |              |  |  |  |  |  |

| [13:12]     | 分周設定        | 00: Reserved                                 |              |  |  |  |  |  |

|             |             | 01: 2 分周 (×1/2)                              |              |  |  |  |  |  |

|             |             | 10: 4 分周 (×1/4)                              |              |  |  |  |  |  |

|             |             | 11: 8 分周 (×1/8)                              |              |  |  |  |  |  |

| [11:8]      | 小数部         | 0000: 0.0000                                 | 1000: 0.5000 |  |  |  |  |  |

|             | 逓倍設定        | 0001: 0.0625                                 | 1001: 0.5625 |  |  |  |  |  |

|             |             | 0010: 0.1250                                 | 1010: 0.6250 |  |  |  |  |  |

|             |             | 0011: 0.1875                                 | 1011: 0.6875 |  |  |  |  |  |

|             |             | 0100: 0.2500                                 | 1100: 0.7500 |  |  |  |  |  |

|             |             | 0101: 0.3125                                 | 1101: 0.8125 |  |  |  |  |  |

|             |             | 0110: 0.3750                                 |              |  |  |  |  |  |

| [7.0]       | ±5 301 ±5   | 0111: 0.4375                                 | 1111: 0.9375 |  |  |  |  |  |

| [7:0]       | 整数部         | 0x00: 0                                      |              |  |  |  |  |  |

|             | 逓倍設定        | 0x01: 1                                      |              |  |  |  |  |  |

|             |             | 0x02: 2                                      |              |  |  |  |  |  |

|             |             | 0xFD: 253                                    |              |  |  |  |  |  |

|             |             | 0xFE: 254                                    |              |  |  |  |  |  |

|             |             | 0xFF: 255                                    |              |  |  |  |  |  |

表 2.1 [CGPLL0SEL]<PLL0SET[23:0]>設定詳細

注) 逓倍値は、<PLL0SET[7:0]>(整数部)と<PLL0SET[11:8]>(小数部)の合算です。

f<sub>PLL</sub>は、以下の計算式で表されます。

$f_{PLL} = f_{OSC} \times (\textit{[CGPLL0SEL]} < PLL0SET[7:0] > + \textit{[CGPLL0SEL]} < PLL0SET[11:8] >) \times (\textit{[CGPLL0SEL]} < PLL0SET[13:12] >)$

※ (f<sub>PLL</sub>≤ 最大動作周波数)

- 注1) 周波数精度の絶対値は保証しません。

- 注2) 小数部逓倍設定にリニアリティはありません。

表 2.2 PLL補正値(例)

| fosc(MHz) | <pll0set[23:17]>(10 進、整数値)</pll0set[23:17]> |

|-----------|---------------------------------------------|

| 6.00      | 14                                          |

| 8.00      | 18                                          |

| 10.00     | 23                                          |

| 12.00     | 27                                          |

PLL 補正値は、以下で求めることができます  $f_{osc}$ =6.0MHz 時、6.0/0.45 = 13.33  $\rightarrow$  14; 小数部は切り上げ

[CGPLLOSEL]<PLLOSET[23:0]>の主な設定例を、下記に示します。

入力周波数( $f_{OSC}$ )を、PLL で逓倍、分周し、目的とするクロック周波数( $f_{PLL}$ )を生成します。

分周値は、1/2、1/4、1/8から選択します。

また、逓倍後の周波数は次の範囲で設定してください。200MHz≤(fosc×逓倍値)≤320MHz

表 2.3 PLL0SET 設定値(例)

| fosc(MHz) | 逓倍値     | 分周値 | f <sub>PLL</sub> (MHz) | <pll0set[23:0]></pll0set[23:0]> |

|-----------|---------|-----|------------------------|---------------------------------|

| 6.00      | 53.3125 | 1/8 | 39.98                  | 0x1C7535                        |

| 8.00      | 40.0000 | 1/8 | 40.00                  | 0x247028                        |

| 10.00     | 32.0000 | 1/8 | 40.00                  | 0x2E7020                        |

| 12.00     | 26.6250 | 1/8 | 39.94                  | 0x36FA1A                        |

#### 2.5.3. 動作中の PLL 逓倍値の変更

PLL 逓倍クロック動作中に、逓倍値の変更を行う場合、まず[CGPLLOSEL]<br/>

PLL逓倍クロックを使用しない設定に切り替えます。そして、[CGPLLOSEL]<br/>

PLLのST>=0 を読み出し、<br/>

逓倍クロックを使用しない設定に切り替わったことを確認した後、[CGPLLOSEL]<br/>

PLLのON> を"0" として PLL を停止します。

その後、[CGPLL0SEL]<PLL0SET>の逓倍値を変更し、PLL の初期化時間として約 100 μ s 経過後に、[CGPLL0SEL]<PLL0ON> を"1" に設定して PLL の動作を開始します。

その後、ロックアップ時間、約 400  $\mu$  s 経過後に、[CGPLL0SEL] < PLL0SEL> を"1" に設定します。最後に、[CGPLL0SEL] < PLL0ST> をリードし、切り替わったことを確認します。

#### 2.5.4. PLL 動作開始/停止/切り替えシーケンス

#### 2.5.4.1. fc 設定 (PLL 停止→PLL 動作)

fc 設定として、PLL 停止状態から PLL 動作状態への切り替え手順例は、下記のようになります。

| ≪切り替え前の状態≫                          |                                   |  |  |  |  |

|-------------------------------------|-----------------------------------|--|--|--|--|

| [CGPLL0SEL] <pll0on> = 0</pll0on>   | fsys 用 PLL 動作が停止                  |  |  |  |  |

| [CGPLLOSEL] <pll0sel> = 0</pll0sel> | fsys 用 PLL 選択が PLL 未使用(fosc)      |  |  |  |  |

| [CGPLL0SEL] <pll0st> = 0</pll0st>   | fsys 用 PLL 選択ステータスが PLL 未使用(fosc) |  |  |  |  |

|   | ≪切り替え手順 例≫                                 |                                                          |  |  |  |  |  |

|---|--------------------------------------------|----------------------------------------------------------|--|--|--|--|--|

| 1 | [CGPLLOSEL] <pll0set> = 0xX</pll0set>      | PLL 逓倍値設定を選択する                                           |  |  |  |  |  |

| 2 | 100µs 以上 待つ                                | 逓倍設定後の待ち時間                                               |  |  |  |  |  |

| 3 | [CGPLL0SEL] <pll0on> = 1</pll0on>          | fsys 用 PLL 動作を発振にする                                      |  |  |  |  |  |

| 4 | 400µs 以上 待つ                                | PLL 出力クロック安定待ち時間                                         |  |  |  |  |  |

| 5 | [CGPLL0SEL] <pll0sel> = 1</pll0sel>        | fsys 用 PLL 選択を PLL 使用(f <sub>PLL</sub> )にする              |  |  |  |  |  |

| 6 | <i>[CGPLL0SEL]</i> <pll0st> を リード</pll0st> | fsys 用 PLL 選択ステータスが PLL 使用(f <sub>PLL</sub> )(=1)になるまで待つ |  |  |  |  |  |

注)1~4は、切り替え前の状態が[CGPLLOSEL]<PLLOON>=1の場合は不要です。

PLL 出力クロックが安定した状態から切り替える場合は、5,6のみの実行でPLL 動作状態へ切り替え可能です。

#### 2.5.4.2. fc 設定 (PLL 動作→PLL 停止)

fc 設定として、PLL 動作状態から PLL 停止状態への切り替え手順例は、下記のようになります。

| ≪切り替え前の状態≫                          |                                  |  |  |  |  |  |

|-------------------------------------|----------------------------------|--|--|--|--|--|

| [CGPLL0SEL] <pll0on> = 1</pll0on>   | fsys 用 PLL 選択が発振                 |  |  |  |  |  |

| [CGPLL0SEL] <pll0sel> = 1</pll0sel> | fsys 用 PLL 選択が PLL 使用(fPLL)      |  |  |  |  |  |

| [CGPLLOSEL] <pll0st> = 1</pll0st>   | fsys 用 PLL 選択ステータスが PLL 使用(fPLL) |  |  |  |  |  |

| ≪切り替え手順 例≫ |                                     |                                              |  |  |  |  |

|------------|-------------------------------------|----------------------------------------------|--|--|--|--|

| 1          | [CGPLLOSEL] <pll0sel> = 0</pll0sel> | fsys 用 PLL 選択を PLL 未使用(fosc)にする              |  |  |  |  |

| 2          | [CGPLLOSEL] <pllost> を リード</pllost> | fsys 用 PLL 選択ステータスが PLL 未使用(fosc)(=0)になるまで待つ |  |  |  |  |

| 3          | [CGPLL0SEL] <pll0on> =0</pll0on>    | fsys 用 PLL 動作を停止にする                          |  |  |  |  |

#### 2.6. システムクロック

システムクロックの源振として、内蔵高速発振クロック、外部高速発振クロック(発振子接続またはクロック入力)が使用可能です。

システムクロックは*[CGSYSCR]*<GEAR[2:0]> (クロックギア)で分周が可能です。設定は動作中に変更可能ですが、レジスタ書き込み後、実際にクロックが切り替わるまでに fc で最大 16 クロックの時間が必要です。クロック切り替えの完了は、*[CGSYSCR]*<GEARST[2:0]>で確認してください。

注)タイマカウンタなどの周辺機能の動作中にクロックギアを切り替えないようにしてください。

発振周波数、PLL 逓倍値などで設定した周波数 fc に対するクロックギア比(1/1  $\sim$  1/16)による動作周波数例を下記 に示します。

| 外部発振  | 外部クロック入力 | 内蔵発振<br>IHOSC1(MHz) | PLL<br>逓倍値<br>(八田後) | 最大<br>周波数<br>(fc)(MHz) |       |      | コックギ<br>L=ON |      |      |     |     | ロック <del>:</del><br>L=OF |      |      |

|-------|----------|---------------------|---------------------|------------------------|-------|------|--------------|------|------|-----|-----|--------------------------|------|------|

| (MHz) | (MHz)    |                     | (分周後)               | (IC)(IVITZ)            | 1/1   | 1/2  | 1/4          | 1/8  | 1/16 | 1/1 | 1/2 | 1/4                      | 1/8  | 1/16 |

| 6     | 6        | _                   | 6.625               | 39.75                  | 39.75 | 19.9 | 9.94         | 4.97 | 2.48 | 6   | 3   | 1.5                      | -    | -    |

| 8     | 8        | _                   | 5                   | 40                     | 40    | 20   | 10           | 5    | 2.5  | 8   | 4   | 2                        | 1    | -    |

| 10    | 10       | 10                  | 4                   | 40                     | 40    | 20   | 10           | 5    | 2.5  | 10  | 5   | 2.5                      | 1.25 | -    |

| 12    | 12       | _                   | 3.3125              | 39.75                  | 39.75 | 19.9 | 9.94         | 4.97 | 2.48 | 12  | 6   | 3                        | 1.5  | -    |

表 2.4 動作周波数(単位:MHz)例

#### 2.6.1. システムクロックの設定方法

#### 2.6.1.1. fosc 設定(内蔵発振→外部発振)

fosc 設定として、内蔵高速発振 1(IHOSC1)から外部高速発振(EHOSC)への切り替え手順例を下記に示します。

| ≪切り替え前の状態≫                          |                              |

|-------------------------------------|------------------------------|

| [CGOSCCR] <ihosc1en> = 1</ihosc1en> | 内蔵高速発振器 1 が発振                |

| [CGOSCCR] <oscsel> = 0</oscsel>     | fosc 用高速発振選択が内部(IHOSC1)      |

| [CGOSCCR] <oscf> = 0</oscf>         | fosc 用高速発振選択ステータスが内部(IHOSC1) |

| X1/X2 端子に発振子を接続(注)                  |                              |

注)発振子以外は接続しないでください。

|   | ≪切り替えシーケンス例≫                                                                 |                                                              |  |  |  |

|---|------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|

| 1 | <b>[PHPDN]</b><br>bit[1:0]> = 00<br><b>[PHIE]</b><br>bit[1:0]> = 00          | X1/X2 端子のプルダウンをディセーブル<br>X1/X2 端子の入力制御をディセーブル                |  |  |  |

| 2 | [CGOSCCR] <eoscen[1:0]> = 01</eoscen[1:0]>                                   | 外部発振器の動作選択を外部高速発振器(EHOSC)                                    |  |  |  |

| 3 | [CGWUPHCR] <wuclk> = 1<br/>[CGWUPHCR]<wupt[15:4]> = 任意値</wupt[15:4]></wuclk> | 高速発振ウォーミングアップクロック選択を外部(EHOSC)<br>ウォーミングアップカウンタ設定値へ発振器安定時間を設定 |  |  |  |

| 4 | [CGWUPHCR] <wuon> = 1</wuon>                                                 | 高速発振ウォーミングアップをスタートする                                         |  |  |  |

| 5 | [CGWUPHCR] <wuef>をリード</wuef>                                                 | 高速発振ウォーミングアップ終了(=0)になるまで待つ                                   |  |  |  |

| 6 | [CGOSCCR] <oscsel> = 1</oscsel>                                              | fosc 用高速発振選択を外部(EHOSC)へ                                      |  |  |  |

| 7 | [CGOSCCR] <oscf>をリード</oscf>                                                  | fosc 用高速発振選択ステータスが外部(=1)になるまで待つ                              |  |  |  |

| 8 | [CGOSCCR] <ihosc1en> = 0</ihosc1en>                                          | 内蔵高速発振器 1 を停止                                                |  |  |  |

#### 2.6.1.2. fosc 設定(内蔵発振→外部クロック入力)

$f_{osc}$ 設定として、内蔵高速発振器 1(IHOSC1)から外部クロック入力(EHCLKIN)への切り替え手順例を下記に示します。

| ≪切り替え前の状態≫                          |                              |

|-------------------------------------|------------------------------|

| [CGOSCCR] <ihosc1en> = 1</ihosc1en> | 内蔵高速発振器 1 が発振                |

| [CGOSCCR] <oscsel> = 0</oscsel>     | fosc 用高速発振選択が内部(IHOSC1)      |

| [CGOSCCR] <oscf> = 0</oscf>         | fosc 用高速発振選択ステータスが内部(IHOSC1) |

| EHCLKIN へのクロック入力                    | 適正電圧範囲で入力してください。             |

|   | ≪切り替えシーケンス例≫                                              |                                                |

|---|-----------------------------------------------------------|------------------------------------------------|

| 1 | [PHPDN] <bit[0]> = 0 [PHIE]<bit[0]> = 1</bit[0]></bit[0]> | X1 端子のプルダウンをディセーブル<br>X1/EHCLKIN 端子の入力制御をイネーブル |

| 2 | [CGOSCCR] <eoscen[1:0]> = 10</eoscen[1:0]>                | 外部発振器の動作選択を外部クロック入力(EHCLKIN)にする                |

| 3 | [CGOSCCR] <oscsel> = 1</oscsel>                           | fosc 用高速発振選択を外部クロックへ                           |

| 4 | [CGOSCCR] <oscf> をリード</oscf>                              | fosc 用高速発振選択ステータスが外部(=1)になるまで待つ                |

| 5 | [CGOSCCR] <ihosc1en> = 0</ihosc1en>                       | 内蔵高速発振器 1 を停止                                  |

#### 2.6.1.3. fosc 設定(外部発振/外部クロック入力→内蔵発振)

$f_{osc}$ 設定として、外部発振器(EHOSC)動作状態または外部クロック入力(EHCLKIN)動作状態から、内蔵高速発振器 1(IHOSC1)への切り替え手順例を下記に示します。

| ≪切り替え前の状態≫                                       |                                  |

|--------------------------------------------------|----------------------------------|

| [CGOSCCR] <eoscen[1:0]> = 01 or 10</eoscen[1:0]> | 外部発振器の動作選択が外部発振器(EHOSC)か外部クロック入力 |

| [CGOSCCR] <oscsel> = 1</oscsel>                  | fosc 用高速発振選択が外部(EHOSC)           |

| [CGOSCCR] <oscf> = 1</oscf>                      | fosc 用高速発振選択ステータスが外部(EHOSC)      |

|   | ≪切り替えシーケンス例≫                               |                                 |

|---|--------------------------------------------|---------------------------------|

| 1 | [CGOSCCR] <ihosc1en> = 1</ihosc1en>        | 内蔵高速発振器 1 を発振する                 |

| 2 | [CGOSCCR] <ihosc1f> をリード</ihosc1f>         | 内蔵高速発振安定フラグが発振安定(=1)になるまで待つ     |

| 3 | [CGOSCCR] <oscsel> = 0</oscsel>            | fosc 用高速発振選択を内部クロック(IHOSC1)へ    |

| 4 | [CGOSCCR] <oscf> をリード</oscf>               | fosc 用高速発振選択ステータスが内部(=0)になるまで待つ |

| 5 | [CGOSCCR] <eoscen[1:0]> = 00</eoscen[1:0]> | 外部発振器の動作選択を未使用にする               |

#### 2.7. クロック供給設定機能

本製品には、周辺機能に対してクロック供給 On/Off 機能があり、使用しない周辺機能に対して、クロック供給を停止することで消費電流を削減することができます。

リセット解除後は、一部の周辺機能を除き、クロックが供給されていない状態です。

詳細は、「4.2.5. / CGSCOCR / (SCOUT 出力制御レジスタ)」を参照してください。

使用する機能のクロックを供給するには、[CGFSYSENA]、[CGFSYSENB]、[CGSPCLKEN]の該当のビットを"1"に設定します。

レジスタの詳細は、「4.レジスタの説明」を参照してください。

#### 2.8. クロックの端子出力機能

本製品には、クロックの端子出力機能があります。出力可能なクロックとして、低速クロック fs、高速発振 fosc、高速クロック fc、システムクロック fsys を SCOUT 端子から出力できます。

SCOUT 端子の動作モード別使用可否状態を示します。

動作モード SCOUT 選択 NORMAL/IDLE STOP1 STOP2 fosc 0 × × 0 fc X × 0 fs 0 0 × × fsvs

表 2.5 SCOUT端子使用可否一覧

## 2.9. プリスケーラクロック

周辺機能には、それぞれにクロック $\phi$ TO を分周するプリスケーラがあります。これらのプリスケーラへ入力するクロック $\phi$ TO は、*[CGSYSCR]*<PRCK[3:0]>で分周することが可能です。リセット後の $\phi$ TO は、fc が選択されます。

レジスタ書き込み後、実際にクロックが切り替わるまでに fc で最大 512 クロックの時間が必要です。 クロック切り替えの完了は、**/CGSYSCR/**<PRCKST[3:0]>で確認してください。

注)タイマカウンタなどの周辺機能の動作中にプリスケーラクロックを切り替えないようにしてください。

## 3. 動作モード

この製品には、動作モードとして NORMAL モードと低消費電力モード(IDLE,STOP1,STOP2)があり、使用方法に応じモード遷移を行うことで消費電力を抑えることができます。

#### 3.1. 動作モードの詳細

#### 3.1.1. 各モードの特長

NORMAL、低消費電力モードの特長は次のとおりです。

#### • NORMAL モード

CPUコア、および周辺回路を動作させるモードです。リセット解除後は、NORMALモードとなります。

低消費電力モードは以下のとおりです。

#### 低消費電力モード

- IDLEモード

CPU が停止するモードです。

周辺機能は各周辺機能のレジスタ、クロック供給設定機能などにより、動作/停止を行ってください。

注) IDLE モード中は CPU によるウォッチドッグタイマのクリアができませんので注意してくだい。

#### - STOP1モード

内蔵高速発振器も含めて全ての内部回路が停止するモードです。

ただし、外部低速発振器を発振させて STOP1 モードに遷移した場合、RTC は動作します。

STOP1モード が解除されると内蔵高速発振器1(IHOSC1)が発振を開始し、NORMAL モードへ復帰します。

STOP1 モードに遷移する前に、STOP1 解除に使用しない割り込みは禁止してください。

#### - STOP2モード

一部の機能を保持して内部電源を遮断するモードです。STOP1 モード より大幅な電力の消費を抑えることができます。STOP2モード が解除されると、電源遮断ブロックに対して電源を投入し、リセットシーケンスが実行され、NORMAL モードへ復帰します。

電源遮断ブロックとは、STOP2モードで電源供給を遮断する機能です。

STOP2 モードに遷移する前に STOP2 解除要因にしない割り込みは禁止し、 [RLMSHTDNOP]<PTKEEP>=1 の設定を必ず行い各ポートの状態を保持してください。

出力/Pull up や、入力許可は、ポートキープ機能に設定したときの状態を保持します。また、外部割り込みは入力を継続します。

STOP2 モードでは以下の回路を除き電源遮断が行われます。

- ■外部低速発振器(ELOSC)

- •RTC

- BackUp RAM

- ■Port 端子状態

- •LVD

- •RLM

- •IA

- •I<sup>2</sup>C ウェイクアップ

低消費電力モードでの電源遮断の詳細は、「3.1.4 低消費電力モードにおける周辺機能状態」を参照してください。

#### 3.1.2. 低消費電力モード

各低消費電力動作へ遷移するには、スタンバイコントロールレジスタ[CGSTBYCR]<STBY[1:0]>でIDLE/STOP1/STOP2モードを選択し、WFI命令を実行します。WFI 命令によって低消費電力モードへ遷移した場合、低消費電力モードからの復帰はリセットまたは割り込み発生により行われます。割り込みで復帰する場合には、設定を行っておく必要があります。詳細はリファレンスマニュアルの「例外」の「割り込み」章を参照してください。

- 注1) 本製品ではイベントによる復帰はサポートしていないため、WFE (Wait For Event)による低消費電力モードへの 遷移は行わないでください。

- 注2) 本製品は、Cortex-M3 コアの SLEEPDEEP による低消費電力モードはサポートしていません。システム制御レジスタの<SLEEPDEEP>ビットは設定しないでください。

#### 3.1.3. 低消費電力モードの選択

低消費電力モード選択は、[CGSTBYCR]<STBY[1:0]>の設定で選択されます。下表 に<STBY[1:0]>の設定より選択されるモードを示します。

表 3.1 低消費電力モード選択

| モード   | [CGSTBYCR] <stby[1:0]></stby[1:0]> |

|-------|------------------------------------|

| IDLE  | 00                                 |

| STOP1 | 01                                 |

| STOP2 | 10                                 |

注)上記の設定以外は行わないでください。

#### 3.1.4. 低消費電力モードにおける周辺機能状態

各モードにおける周辺機能(ブロック)の動作状態を表 3.2 に示します。 なお、リセット解除後は、一部のブロックを除きクロックが供給されない状態となります。 必要に応じて、[CGFSYSENA]、[CGFSYSENB]、[CGSPCLKEN]を設定しクロック供給を許可してくだ さい。

表 3.2 低消費電力モード別 ブロック動作状態一覧

| Block             |             |        |           | STO    | OP1    | STOP2(注 1) |        |

|-------------------|-------------|--------|-----------|--------|--------|------------|--------|

|                   |             | NORMAL | IDLE      | ELOSC  | ELOSC  | ELOSC      | ELOSC  |

|                   |             |        |           | On     | Off    | On         | Off    |

| Processor co      | re          | 0      | _         |        |        | ×          | ×      |

| DMAC              |             | 0      | 0         | l      | 1      | ×          | ×      |

| 1/0               | 端子状態        | 0      | 0         | 0      | 0      | 〇(注 4)     | O(注 4) |

| I/O port          | レジスタ        | 0      | 0         | _      | _      | ×          | ×      |

| ADC               | ı           | 0      | 0         | _      | _      | ×          | ×      |

| DAC               |             | 0      | 0         | _      | _      | ×          | ×      |

| UART              |             | 0      | 0         | _      | _      | ×          | ×      |

| I <sup>2</sup> C  |             | 0      | 0         | 一(注 3) | 一(注 3) | ×(注 3)     | ×(注 3) |

| TSPI              |             | 0      | 0         | l      | l      | ×          | ×      |

| PMD+              |             | 0      | 0         | 1      | 1      | ×          | ×      |

| A-ENC             |             | 0      | 0         | 1      |        | ×          | ×      |

| T32A              |             | 0      | 0         | 1      | -      | ×          | ×      |

| TRGSEL            |             | 0      | 0         | 1      | 1      | ×          | ×      |

| RTC               |             | 0      | 0         | 0      | _      | 0          | _      |

| RMC               |             | 0      | 0         | 0      | _      | ×          | ×      |

| SIWDT             |             | 0      | 〇(注 2)    |        | _      | ×          | ×      |

| LVD               |             | 0      | 0         | 0      | 0      | 0          | 0      |

| OFD               |             | 0      | 0         |        | _      | ×          | ×      |

| TRM               |             | 0      | 使用不可      |        | _      | ×          | ×      |

| CG                |             | 0      | 0         | 0      | 0      | ×          | ×      |

| PLL               |             | 0      | 0         | _      | _      | ×          | ×      |

| 外部高速発振            |             | 0      | 0         | _      | _      | ×          | ×      |

|                   | 器 1(IHOSC1) | 0      | 0         | _      | _      | ×          | ×      |

| 内蔵高速発振器 2(IHOSC2) |             | 0      | 0         | _      | _      | ×          | ×      |

| 外部低速発振器(ELOSC)    |             | 0      | 0         | 0      | _      | 0          | _      |

| RLM               |             | 0      | 0         | 0      | 0      | 0          | 0      |

| Flash Code ROM    |             |        |           |        |        | データ        | データ    |

| Flash Data ROM    |             | アクセス   | アクセス      | データ    | データ    | 保持         | 保持     |

| RAM               |             | 可能     | 能 可能(注 5) | 保持     | 保持     | ×          | ×      |

| Backup RAM        |             |        |           |        |        | データ保持      | データ保持  |

- 〇:動作可能

- -:対象のモードに遷移すると自動的に周辺回路へのクロックが停止

- ×:対象モードに遷移すると自動的にモジュールへの供給電源が遮断、復帰時はリセットにより初期 化

- 注1) 周辺機能が動作していないことを確認し、STOP2 モードに遷移するようにしてください。

- 注2) プロテクトモード A のみ。それ以外の場合は、IDLE モードへ遷移する前に SIWDT を停止してください。

- 注3) アドレス一致 WakeUp 機能のみ使用できます

- 注4) ポートの状態は[RLMSHTDNOP]<PTKEEP>を"1"に設定したときの状態が保持されます。

- 注5) CPU以外のデータアクセス(R/W)する周辺機能(DMA など)がバスマトリクス上で接続されていない場合は、データ保持となります。

#### 3.2. モード状態遷移

図 3.1 状態遷移

- 注1) 復帰時にウォーミングアップが必要となります。ウォーミングアップ時間の設定はSTOP1 モードに入る前のモード (NORMAL モード)で設定する必要があります。

- 注2) STOP2 モードからの復帰時はリセットの割り込み処理ルーチンに分岐し、STOP1 モードからの復帰時は割り込み起動要因の処理ルーチンに分岐します。

#### 3.2.1. IDLE モード遷移フロー

IDLE へ遷移する場合は、以下の順番で設定してください。

IDLE モードは割り込みで解除されますので、IDLE モードへ遷移する前に割り込みの設定を行ってください。IDLE モード解除に使用可能な割り込みは「3.3.1. 低消費電力モードの解除ソース」を参照してください。解除に使用しない割り込み、および使用できない割り込みは禁止してください。

|   | 遷移手順                                          |                             |  |  |  |

|---|-----------------------------------------------|-----------------------------|--|--|--|

| 1 | [SIWDxEN] <wdte>=0</wdte>                     | SIWDT をディセーブルにする            |  |  |  |

| 2 | <b>[SIWDxCR]</b> <wdcr[7:0]>=0xB1</wdcr[7:0]> | SIWDT をディセーブルにする            |  |  |  |

| 3 | <i>[FCSR0]</i> <rdybsy>をリード</rdybsy>          | Flash が Ready 状態(=1)になるまで待つ |  |  |  |

| 4 | [CGSTBYCR] <stby[1:0]>=00</stby[1:0]>         | 低消費電力モード選択を IDLE にする        |  |  |  |

| 5 | [CGSTBYCR] <stby[1:0]>をリード</stby[1:0]>        | 4 のレジスタライトを確認する(=00)        |  |  |  |

| 6 | WFI 命令実行                                      | IDLE へ遷移する                  |  |  |  |

#### 3.2.2. STOP1 モード遷移フロー

STOP1 へ遷移する場合は、以下の順番で設定してください。

STOP1 モードは割り込みで解除されますので、STOP1 モードへ遷移する前に割り込みの設定を行ってください。STOP1 モード解除に使用可能な割り込みは「3.3.1. 低消費電力モードの解除ソース」を参照してください。解除に使用しない割り込み、および使用できない割り込みは禁止してください。

|    | 遷移手順 (Normal モードから)                           |                                         |  |  |  |

|----|-----------------------------------------------|-----------------------------------------|--|--|--|

| 1  | [SIWDxEN] <wdte>=0</wdte>                     | SIWDT をディセーブルにする                        |  |  |  |

| 2  | <i>[SIWDxCR]</i> <wdcr[7:0]>=0xB1</wdcr[7:0]> | SIWDT をディセーブルにする                        |  |  |  |

| 3  | <i>[FCSR0]</i> <rdybsy>をリード</rdybsy>          | Flash が Ready 状態(=1)になるまで待つ             |  |  |  |

| 4  | [CGWUPHCR] <wuef>をリード</wuef>                  | 高速発振ウォーミングアップ終了(=0)を確認する                |  |  |  |

|    | [CGWUPHCR] <wuclk>=0</wuclk>                  | 高速発振ウォーミングアップクロック選択を内部(IHOSC1)にする       |  |  |  |

| 5  | [CGWUPHCR] <wupt[15:4]>="任意值"</wupt[15:4]>    | 高速発振ウォーミングアップカウンタ設定値を STOP1 復帰に必要な時     |  |  |  |

|    | [CGWOPHCK] <wop1[15.4]>= 任息恒</wop1[15.4]>     | 間に設定する                                  |  |  |  |

| 6  | [CGSTBYCR] <stby[1:0]>=01</stby[1:0]>         | 低消費電力モード選択を STOP1 にする                   |  |  |  |

| 7  | [CGPLL0SEL] <pll0sel>=0</pll0sel>             | fsys 用 PLL 選択を PLL 未使用(fosc)にする         |  |  |  |

| 8  | <i>[CGPLL0SEL]</i> <pll0st>をリード</pll0st>      | fsys 用 PLL 選択ステータスが PLL 未使用になるまで待つ(=0)  |  |  |  |

| 9  | [CGPLL0SEL] <pll0on>=0</pll0on>               | fsys 用 PLL 動作を停止する                      |  |  |  |

| 10 | [CGOSCCR] <ihosc1en>=1</ihosc1en>             | 内蔵高速発振器 1 を発振にする                        |  |  |  |

| 11 | [CGOSCCR] <oscsel>=0</oscsel>                 | fosc 用高速発振選択を内部(IHOSC1)にする              |  |  |  |

| 12 | [CGOSCCR] <oscf>をリード</oscf>                   | fosc 用高速発振選択ステータスが内部(IHOSC1)(=0)になるまで待つ |  |  |  |

| 13 | [CGOSCCR] <eoscen[1:0]>=00</eoscen[1:0]>      | 外部発振の動作選択を未使用にする                        |  |  |  |

| 14 | [CGOSCCR] <ihosc2en>=0</ihosc2en>             | OFD 用内蔵高速発振器 2(IHOSC2)を停止する             |  |  |  |

| 15 | [CGOSCCR] <eoscen[1:0]>をリード</eoscen[1:0]>     | 13 のレジスタライトを確認する(=00)                   |  |  |  |

| 16 | [CGOSCCR] <ihosc2f>をリード</ihosc2f>             | OFD 用内蔵高速発振器 2 の内蔵発振安定フラグが"0"になるまでまつ    |  |  |  |

| 17 | WFI 命令実行                                      | STOP1 へ遷移する                             |  |  |  |

|    |                                               |                                         |  |  |  |

注) SIWDT の A モードを使用する場合は、1,2,14,16 の処理は不要です。

#### 3.2.3. STOP2 モード遷移フロー

STOP2 へ遷移する場合は、以下の順番で設定してください。

STOP2 モードは割り込みで解除されますので、STOP2 モードへ遷移する前に割り込みの設定を行ってください。STOP2 モード解除に使用可能な割り込みは「3.3.1. 低消費電力モードの解除ソース」を参照してください。解除に使用しない割り込み、および使用できない割り込みは禁止してください。

|    | 遷移シーケンス(Normal モードから)                                                        |                                         |  |  |  |  |

|----|------------------------------------------------------------------------------|-----------------------------------------|--|--|--|--|

| 1  | [SIWDxEN] <wdte>=0</wdte>                                                    | SIWDT をディセーブルにする                        |  |  |  |  |

| 2  | <i>[SIWDxCR]</i> <wdcr[7:0]>=0xB1</wdcr[7:0]>                                | SIWDT をディセーブルにする                        |  |  |  |  |

| 3  | <i>[FCSR0]</i> <rdybsy>をリード</rdybsy>                                         | Flash が Ready 状態(=1)になるまで待つ             |  |  |  |  |

| 4  | [RLMSHTDNOP] <ptkeep>=1</ptkeep>                                             | IO 制御信号を保持させる                           |  |  |  |  |

| 5  | [CGSTBYCR] <stby[1:0]>=10</stby[1:0]>                                        | 低消費電力モード選択を STOP2 にする                   |  |  |  |  |

| 6  | [CGPLL0SEL] <pll0sel>=0</pll0sel>                                            | fsys 用 PLL 選択を PLL 未使用(fosc)にする         |  |  |  |  |

| 7  | <i>[CGPLL0SEL]</i> <pll0st>をリード</pll0st>                                     | fsys 用 PLL 選択ステータスが PLL 未使用になるまで待つ(=0)  |  |  |  |  |

| 8  | [CGPLL0SEL] <pll0on>=0</pll0on>                                              | fsys 用 PLL 動作を停止する                      |  |  |  |  |

| 9  | [CGOSCCR] <ihosc1en>=1</ihosc1en>                                            | 内蔵高速発振器 1 を発振にする                        |  |  |  |  |

| 10 | [CGOSCCR] <oscsel>=0</oscsel>                                                | fosc 用高速発振選択を内部(IHOSC1)にする              |  |  |  |  |

| 11 | [CGOSCCR] <oscf>をリード</oscf>                                                  | fosc 用高速発振選択ステータスが内部(IHOSC1)(=0)になるまで待つ |  |  |  |  |

| 12 | [CGOSCCR] <eoscen[1:0]>=00</eoscen[1:0]>                                     | 外部発振の動作選択を未使用にする                        |  |  |  |  |

| 13 | [CGOSCCR] <ihosc2en>=0</ihosc2en>                                            | OFD 用内蔵高速発振器 2 を停止する                    |  |  |  |  |

| 14 | [CGOSCCR] <eoscen[1:0]>をリード</eoscen[1:0]>                                    | 12 のレジスタライトを確認する(=00)                   |  |  |  |  |

| 15 | [CGOSCCR] <ihosc2f>をリード</ihosc2f>                                            | OFD 用内蔵高速発振器 2 の内蔵発振安定フラグが"0"になるまでまつ    |  |  |  |  |

| 16 | [RLMRSTFLG0] <stop2rstf>=0<br/>[RLMRSTFLG0]<pinrstf>=0</pinrstf></stop2rstf> | STOP2 リセットフラグ/リセット端子フラグをクリア(注 1)        |  |  |  |  |

| 17 | WFI 命令実行 ←                                                                   | STOP2 へ遷移する                             |  |  |  |  |

| 18 | ジャンプ命令                                                                       | 17 へ戻す                                  |  |  |  |  |

注1) リセットフラグレジスタ[RLMRSTFLG0]については、リファレンスマニュアルの「例外」を参照してください。

注2) SIWDT の A モードを使用する場合は、1,2,13,15 の処理は不要です。

## 3.3. 低消費電力モードからの復帰

#### 3.3.1. 低消費電力モードの解除ソース

低消費電力モードからの解除は、割り込み、マスク不能割り込み、リセットによって行うことができます。使用できるスタンバイ解除ソースは、低消費電力モードにより決まります。 詳細を下表に示します。

表 3.3 解除ソース一覧 低消費電力モード

|     | 低消費電力モード           |                                                                                                                         |        | STOP1 | STOP2 |

|-----|--------------------|-------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|

|     |                    | INT00、INT01、INT02 (注 1)                                                                                                 | 0      | 0     | 0     |

|     |                    | INT03 ~ INT15 (注 1)                                                                                                     | 0      | 0     | ×     |

|     |                    | INTI2CWUP                                                                                                               | 0      | 0     | 0     |

|     |                    | INTRTC                                                                                                                  | 0      | 0     | 0     |

|     |                    | INTEMG0,INTOVV0,INTPMD0                                                                                                 | 0      | ×     | ×     |

|     |                    | INTENC00, INTENC01                                                                                                      | 0      | ×     | ×     |

|     |                    | INTADAPDA,INTADAPDB                                                                                                     | 0      | ×     | ×     |

|     |                    | INTADACP0,INTADACP1,INTADATRG                                                                                           | 0      | ×     | ×     |

|     | 割り込み               | INTADASGL,INTADACNT                                                                                                     | 0      | ×     | ×     |

|     |                    | INTTxRX,INTTxTX,INTTxERR                                                                                                | 0      | ×     | ×     |

|     |                    | INTI2Cx, INTI2CxAL, INTI2CxBF, INTI2CxNA                                                                                | 0      | ×     | ×     |

| 解除  |                    | INTUARTxRX,INTUARTxTX,INTUARTxERR                                                                                       | 0      | ×     | ×     |

| ソース |                    | INTT32AxA,INTT32AxACAP0,INTT32AxACAP1<br>INTT32AxB,INTT32AxBCAP0,INTT32BxBCAP1<br>INTT32AxC,INTT32AxCCAP0,INTT32CxCCAP1 | 0      | ×     | ×     |

|     |                    | INTDMAATC,INTDMAAERR                                                                                                    | 0      | ×     | ×     |

|     |                    | INTRMC                                                                                                                  | 0      | 0     | ×     |

|     |                    | INTFLCRDY,INTFLDRDY                                                                                                     | 0      | ×     | ×     |

|     | SysTick 割り込み       |                                                                                                                         | 0      | ×     | ×     |

|     | マスク不能割り込み (INTWDT) |                                                                                                                         | 〇(注 2) | ×     | ×     |

|     | マスク不能割り込み (INTLVD) |                                                                                                                         | 0      | 0     | 0     |

|     | リセット(SIWDT)        |                                                                                                                         | 〇(注 2) | ×     | ×     |

|     | リセット(L\            | /D)                                                                                                                     | 0      | 0     | 0     |

|     | リセット(O             | FD)                                                                                                                     | 0      | ×     | ×     |

|     | リセット (F            | RESET 端子)                                                                                                               | 0      | 0     | 0     |

○:解除後、割り込み処理を開始します

×:解除に使用できません

注 1) INT00~INT15(外部割り込み 00~15)は、立ち上がり/立ち下り/レベルのいずれかを選択することができます。設定の詳細はリファレンスマニュアル「例外」を参照してください。

注 2) プロテクトモード A のみ。それ以外の場合は、IDLE モードへ遷移する前に SIWDT を停止してください。

#### ● 割り込み要求による解除

割り込みによって低消費電力モードを解除する場合、CPU で割り込みが検出されるよう準備しておく必要があります。STOP1、STOP2 モードの解除に使用する割り込みは、CPU の設定の他に INTIF で割り込み検出の設定を行う必要があります。

● マスク不能割り込み(NMI)による解除

NMI の要因には WDT 割り込み(INTWDT,プロテテクトモード A のみ)と LVD 割り込み(INTLVD)があります。

リセットによる解除

リセットは全ての低消費電力モードからの解除を行うことができます。 リセットで解除した場合には、解除後 NORMAL モードで全てのレジスタが初期化された状態になります。

• SysTick 割り込みによる解除

SysTick 割り込みは IDLE モードでのみ使用可能です。

割り込みの詳細に関しては、リファレンスマニュアル「例外」の「割り込み」章を参照してください。

## 3.3.2. 低消費電力モード遷移時のウォーミングアップ

モード遷移時、内部回路の安定のためウォーミングアップが必要な場合があります。 STOP1 モードから NORMAL モードへの遷移では、自動的に内部発振が選択されウォーミングアップ 用カウンタが起動されます。ウォーミングアップ時間経過後にシステムクロックの出力が開始されます。

このため、STOP1 モードに遷移する命令を実行する前に、[CGWUPHCR] <WUPT[15:4]>でウォーミングアップ時間の設定を行ってください。設定方法については、「2.4.1 高速発振用ウォーミングアップカウンタ」を参照してください。

各動作モード遷移時におけるウォーミングアップ設定の有無を下表 に示します。

表 3.4 ウォーミングアップ

| 動作モード遷移        | ウォーミングアップ設定 |

|----------------|-------------|

| NORMAL → IDLE  | 不要          |

| NORMAL → STOP1 | 不要          |

| NORMAL → STOP2 | 不要          |

| IDLE → NORMAL  | 不要          |

| STOP1 → NORMAL | 必要          |

| STOP2 → NORMAL | 不要          |

#### 3.3.3. STOP2 モードからの復帰

STOP2 モード解除要因割り込み発生からの復帰フローは以下のとおりです。

図 3.2 STOP2モード復帰フロー

- 注1) STOP2 をリセット端子で解除した場合、リセットフラグは、"STOP2 リセットフラグ"と" リセット端子フラグ"の両方が成立します。

- 注2) レジスタ初期化範囲は、割り込みによる STOP2 解除とリセット端子による STOP2 解除で 異なります。それぞれのリセット範囲の詳細は、リファレンスマニュアル「電源とリセット動作」を参照してください。

## 3.4. モード遷移によるクロック動作

モード遷移の際の、クロック動作について以下に示します。

#### 3.4.1. NORMAL→IDLE→NORMAL 動作モード遷移

IDLE モードは、CPUが停止するモードです。周辺機能へのクロック供給は、設定状態を保持します。必要に応じて、各周辺機能のレジスタ、クロック供給設定機能などにより、動作/停止を行ってください。IDLE 状態から、NORMAL モードへの復帰時にウォーミングアップは行いません。

IDLE モードへ遷移する命令 (WFI) 実行後、プログラムカウンタは次の行を示して CPU 停止状態となります。解除ソースにより、CPU 再起動となり、割り込み許可状態の場合、先に解除ソースの割り込み処理を経て、遷移命令 (WFI) の次の行を実行することになります。

#### 3.4.2. NORMAL→STOP1→NORMAL 動作モード遷移

STOP1 モードから NORMAL モードへ復帰する場合、ウォーミングアップは自動的に起動します。 STOP1 モードへ遷移する前に[CGWUPHCR]<WUPT[15:4]>へウォーミングアップ時間(24 $\mu$ s以上)の設定を行ってください。

図 3.3 NORMAL→STOP1→NORMAL 動作モード遷移

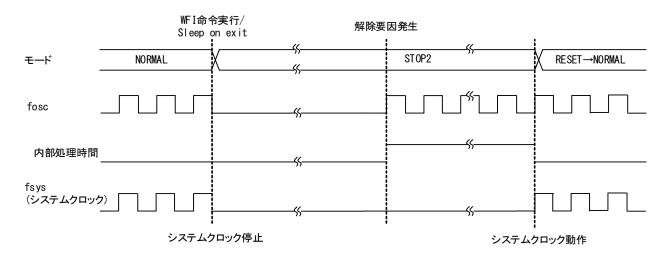

#### 3.4.3. NORMAL→STOP2→RESET→NORMAL 動作モード遷移

リセットで NORMAL モードへ復帰する場合、ウォーミングアップは行われません。 リセット以外で NORMAL モードへ復帰する場合でもリセットの割り込み処理ルーチンへ分岐します。 STOP2 モード解除後は内部電源遮断ブロックに対してリセット動作が行われます。ただし、電源遮断されていないブロックに対して初期化は行ないません。

図 3.4 NORMAL→STOP2→RESET→NORMAL 動作モード遷移

## 4. レジスタの説明

## 4.1. レジスター覧

CG 関連のレジスタとアドレスを以下に示します。

| 周辺機能       | チャネル/ユニット | ベースアドレス |            |

|------------|-----------|---------|------------|

| クロック/モード制御 | CG        | _       | 0x400F3000 |

| 低速発振/電源制御  | RLM       | _       | 0x4003E400 |

#### クロック/モード制御

| レジスタ名                 | アドレス(Base+) |        |

|-----------------------|-------------|--------|

| CG ライトプロテクトレジスタ       | [CGPROTECT] | 0x0000 |

| 発振制御レジスタ              | [CGOSCCR]   | 0x0004 |

| システムクロック制御レジスタ        | [CGSYSCR]   | 0x0008 |

| スタンバイ制御レジスタ           | [CGSTBYCR]  | 0x000C |

| SCOUT 出力制御レジスタ        | [CGSCOCR]   | 0x0010 |

| fsys 用 PLL セレクトレジスタ   | [CGPLL0SEL] | 0x0020 |

| 高速発振ウォーミングアップレジスタ     | [CGWUPHCR]  | 0x0030 |

| 低速発振ウォーミングアップレジスタ     | [CGWUPLCR]  | 0x0034 |

| fsys 供給停止レジスタ A       | [CGFSYSENA] | 0x0050 |

| fsys 供給停止レジスタ B       | [CGFSYSENB] | 0x0054 |

| ADC、トレース用クロック供給停止レジスタ | [CGSPCLKEN] | 0x005C |

| Reserved              | _           | 0x0060 |

#### 低速発振/電源制御 (注)

| レジスタ名            | アドレス(Base+)  |        |

|------------------|--------------|--------|

| 低速発振制御レジスタ       | [RLMLOSCCR]  | 0x0000 |

| 電源遮断制御レジスタ       | [RLMSHTDNOP] | 0x0001 |

| RLM ライトプロテクトレジスタ | [RLMPROTECT] | 0x000F |

注)バイト単位でアクセスするレジスタです。ビットバンドアクセス不可。

## 4.2. レジスタ詳細

## **4.2.1.** [CGPROTECT] (CG ライトプロテクトレジスタ)

| Bit  | Bit Symbol   | リセット後 | Туре | 機能                                                                                         |

|------|--------------|-------|------|--------------------------------------------------------------------------------------------|

| 31:8 | -            | 0     | R    | リードすると"0"が読めます。                                                                            |

| 7:0  | PROTECT[7:0] | 0xC1  | R/W  | CG レジスタライトプロテクト(本レジスタ以外の全て)制御 0xC1:CG レジスタへのライト許可(プロテクト解除) 0xC1 以外:CG レジスタへのライト禁止(プロテクト有効) |

## 4.2.2. [CGOSCCR] (発振制御レジスタ)

| Bit   | Bit Symbol  | リセット後 | Туре | 機能                                                                                                    |

|-------|-------------|-------|------|-------------------------------------------------------------------------------------------------------|

| 31:20 | -           | 0     | R    | リードすると"0"が読めます。                                                                                       |

| 19    | IHOSC2F     | 0     | R    | IHOSC2 用内蔵発振安定フラグ<br>0:停止またはウォームアップ中<br>1:発振安定                                                        |

| 18:17 | -           | 0     | R    | リードすると"0"が読めます。                                                                                       |

| 16    | IHOSC1F     | 1     | R    | IHOSC1 用内蔵発振安定フラグ<br>0:停止またはウォームアップ中<br>1:発振安定                                                        |

| 15:10 | -           | 0     | R    | リードすると"0"が読めます。                                                                                       |

| 9     | OSCF        | 0     | R    | fosc 用高速発振器選択ステータス<br>0: 内蔵高速発振器 1(IHOSC1)<br>1: 外部高速発振器(EHOSC)                                       |

| 8     | OSCSEL      | 0     | R/W  | fosc 用高速発振器選択 (注 1)<br>0: 内蔵高速発振器 1(IHOSC1)<br>1: 外部高速発振器(EHOSC)                                      |

| 7:4   | -           | 0     | R    | リードすると"0"が読めます。                                                                                       |

| 3     | IHOSC2EN    | 0     | R/W  | OFD 用内蔵高速発振器 2(IHOSC2) (注 2)<br>0:停止<br>1:発振                                                          |

| 2:1   | EOSCEN[1:0] | 00    | R/W  | 外部高速発振器の動作選択(EHOSC)(注 3)<br>00: 外部発振未使用<br>01: 外部高速発振(EHOSC)<br>10: 外部クロック入力(EHCLKIN)<br>11: Reserved |

| 0     | IHOSC1EN    | 1     | R/W  | 内蔵高速発振器 1(IHOSC1)<br>0: 停止<br>1: 発振                                                                   |

注1) 設定変更した場合、書き込み値が*[CGOSCCR]*<OSCF>ビットに、反映されていることを確認後、 次の操作を行うようにしてください。

注2) [SIWDxOSCCR]<OSCPRO>=1 (SIWDT のライトプロテクトが有効)の場合は、設定しても変更されません。

注3) 外部高速クロック(発振子接続)を使用する場合は必ず"01"を設定してください。

## 4.2.3. [CGSYSCR] (システムクロック制御レジスタ)

| Bit   | Bit Symbol  | リセット後 | Туре | 機能                                                                                                                                                                                                     |

|-------|-------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:28 | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                        |

| 27:24 | PRCKST[3:0] | 0000  | R    | プリスケーラクロック(ФТ0)選択ステータス<br>0000: fc 0100: fc/16 1000: fc/256<br>0001: fc/2 0101: fc/32 1001: fc/512<br>0010: fc/4 0110: fc/64 1010 - 1111: Reserved<br>0011: fc/8 0111: fc/128                          |

| 23:19 | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                        |

| 18:16 | GEARST[2:0] | 000   | R    | システムクロック(fsys)のギア選択ステータス<br>000: fc 100: fc/16<br>001: fc/2 101 - 111: Reserved<br>010: fc/4<br>011: fc/8                                                                                              |

| 15:12 | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                        |

| 11:8  | PRCK[3:0]   | 0000  | R/W  | プリスケーラクロック(ΦT0)選択<br>0000: fc 0100: fc/16 1000: fc/256<br>0001: fc/2 0101: fc/32 1001: fc/512<br>0010: fc/4 0110: fc/64 1010 - 1111: Reserved<br>0011: fc/8 0111: fc/128<br>周辺機能に供給するプリスケーラクロックを選択します。 |

| 7:3   | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                        |

| 2:0   | GEAR[2:0]   | 000   | R/W  | システムクロック(fsys)のギア選択<br>000: fc 100: fc/16<br>001: fc/2 101 - 111: Reserved<br>010: fc/4<br>011: fc/8                                                                                                   |

## 4.2.4. [CGSTBYCR] (スタンバイ制御レジスタ)

| Bit  | Bit Symbol | リセット後 | Туре | 機能                                                               |

|------|------------|-------|------|------------------------------------------------------------------|

| 31:2 | -          | 0     | R    | リードすると"0"が読めます。                                                  |

| 1:0  | STBY[1:0]  | 00    | R/W  | 低消費電力モード選定<br>00: IDLE<br>01: STOP1<br>10: STOP2<br>11: Reserved |

## **4.2.5.** [CGSCOCR] (SCOUT 出力制御レジスタ)

| Bit  | Bit Symbol  | リセット後 | Туре | 機能                                                                                              |

|------|-------------|-------|------|-------------------------------------------------------------------------------------------------|

| 31:7 | -           | 0     | R    | リードすると"0"が読めます。                                                                                 |

| 6:4  | SCODIV[2:0] | 000   | R/W  | SCOUT 分周選択(注 1)(注 2)<br>000:分周なし 100:16 分周<br>001:2 分周 101-111:Reserved<br>010:4 分周<br>011:8 分周 |

| 3:1  | SCOSEL[2:0] | 000   | R/W  | SCOUT ベースクロック選択(注 1)<br>000:fosc 100-111:Reserved<br>001:fc<br>010:fs<br>011:fsys               |

| 0    | SCOEN       | 0     | R/W  | SCOUT 出力許可<br>0: 禁止<br>1: 許可                                                                    |

**注1)** <SCOSEL[2:0]>で"011:fsys"を選択時は、<SCODIV[2:0]>で"000:分周なし"は選択できません。

**注2)** <**SCOSEL**[2:0]>で"010:fs"を選択時は、強制的に分周なしが選択されます。

## 4.2.6. [CGPLL0SEL] (fsys 用 PLL セレクトレジスタ)

| Bit  | Bit Symbol    | リセット後    | Туре | 機能                                                     |

|------|---------------|----------|------|--------------------------------------------------------|

| 31:8 | PLL0SET[23:0] | 0x000000 | R/W  | PLL 逓倍設定<br>逓倍設定については、"2.5.2PLL 逓倍値の計算式と設定例"を参照してください。 |

| 7:3  | -             | 0        | R    | リードすると"0"が読めます。                                        |

| 2    | PLL0ST        | 0        | R    | fsys 用 Clock 選択ステータス<br>0: fosc<br>1: f <sub>PLL</sub> |

| 1    | PLL0SEL       | 0        | R/W  | fsys 用 Clock 選択<br>0: fosc<br>1: f <sub>PLL</sub>      |

| 0    | PLL0ON        | 0        | R/W  | fsys 用 PLL 動作<br>0: 停止<br>1: 発振                        |

## 4.2.7. [CGWUPHCR] (高速発振ウォーミングアップレジスタ)

| Bit   | Bit Symbol | リセット後 | Туре | 機能                                                                                                      |

|-------|------------|-------|------|---------------------------------------------------------------------------------------------------------|

| 31:20 | WUPT[15:4] | 0x800 | R/W  | ウォーミングアップタイマの計算値 16 ビットの上位 12 ビットの値を設定します。<br>ウォーミングアップタイマの設定については、"2.4.1 高速発振用ウォーミングアップカウンタ"を参照してください。 |

| 19:16 | WUPT[3:0]  | 0000  | R    | ウォーミングアップタイマの計算値 16 ビットの下位 4 ビットの値で、<br>0x0 固定です。                                                       |

| 15:9  | -          | 0     | R    | リードすると"0"が読めます。                                                                                         |

| 8     | WUCLK      | 0     | R/W  | ウォーミングアップクロック選択 (注 1)<br>0: 内蔵高速発振器(IHOSC1)<br>1: 外部高速発振器(EHOSC)                                        |

| 7:2   | -          | 0     | R    | リードすると"0"が読めます。                                                                                         |

| 1     | WUEF       | 0     | R    | ウォーミングアップタイマステータス (注 2)<br>0: ウォーミングアップ終了<br>1: ウォーミングアップ中                                              |

| 0     | WUON       | 0     | W    | ウォーミングアップタイマ制御<br>0: don't care<br>1: ウォーミングアップスタート                                                     |

注1) STOP1復帰時のウォーミングアップは、内蔵発振器で行ってください。外部発振器を選んでSTOP1 から遷移することは禁止です。

注2) ウォーミングアップ中(<WUEF>=1)は、レジスタの書き換え禁止です。設定は、<WUEF>=0のときに 行ってください。

## 4.2.8. [CGWUPLCR] (低速発振ウォーミングアップレジスタ)

| Bit   | Bit Symbol  | リセット後  | Туре | 機能                                                                                                      |

|-------|-------------|--------|------|---------------------------------------------------------------------------------------------------------|

| 31:27 | -           | 0      | R    | リードすると"0"が読めます。                                                                                         |

| 26:12 | WUPTL[18:4] | 0x4000 | R/W  | ウォーミングアップタイマの計算値 19 ビットの上位 15 ビットの値を設定します。<br>ウォーミングアップタイマの設定については、"2.4.2 低速発振用ウォーミングアップカウンタ"を参照してください。 |

| 11:8  | WUPTL[3:0]  | 0000   | R    | ウォーミングアップタイマの計算値 19 ビットの下位 4 ビットの値で、<br>0x0 固定です。                                                       |

| 7:2   | -           | 0      | R    | リードすると"0"が読めます。                                                                                         |

| 1     | WULEF       | 0      | R    | ウォーミングアップタイマステータス (注 1)<br>0: ウォーミングアップ終了<br>1: ウォーミングアップ中                                              |

| 0     | WULON       | 0      | W    | ウォーミングアップタイマ制御<br>0: don't care<br>1: ウォーミングアップスタート                                                     |

注1) ウォーミングアップ中(<WULEF>=1)は、レジスタの書き換え禁止です。設定は、<WULEF>=0のときに行ってください。

## 4.2.9. [CGFSYSENA] (fsys 供給停止レジスタ A)

| Bit | Bit Symbol | リセット後 | Туре  | 機能                                 |

|-----|------------|-------|-------|------------------------------------|

|     | -          |       |       | T32A ch5 のクロックイネーブル                |

| 31  | IPENA31    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

|     |            |       |       | T32A ch4 のクロックイネーブル                |

| 30  | IPENA30    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

|     |            |       |       | T32A ch3 のクロックイネーブル                |

| 29  | IPENA29    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

|     |            |       |       | T32A ch2 のクロックイネーブル                |

| 28  | IPENA28    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

| 07  | IDENIA 07  | 0     | D 44/ | T32A ch1 のクロックイネーブル                |

| 27  | IPENA27    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給<br>T32A ch0 のクロックイネーブル   |

| 26  | IPENA26    | 0     | R/W   | 132A ChO のクロックイネーブル<br>  0: クロック停止 |

| 20  | IFENAZO    | U     | IK/VV | 1: クロック供給                          |

|     |            |       |       | UART ch2 のクロックイネーブル                |

| 25  | IPENA25    | 0     | R/W   | 0: クロック停止                          |

| 23  | II LIVAZO  |       | 10,44 | 1: クロック供給                          |

|     |            |       |       | UART ch1 のクロックイネーブル                |

| 24  | IPENA24    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

|     |            |       |       | UART ch0 のクロックイネーブル                |

| 23  | IPENA23    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

|     |            |       |       | I <sup>2</sup> C ch2 のクロックイネーブル    |

| 22  | IPENA22    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

|     |            |       |       | I <sup>2</sup> C ch1 のクロックイネーブル    |

| 21  | IPENA21    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

|     | IDENIAGO   |       | D 44/ | I <sup>2</sup> C ch0 のクロックイネーブル    |

| 20  | IPENA20    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

| 19  | IPENA19    | 0     | D AA/ | TSPI ch1 のクロックイネーブル<br>0: クロック停止   |

| 19  | IPENATS    | U     | R/W   | 0: クロック停止 1: クロック供給                |

|     |            |       |       | TSPI ch0 のクロックイネーブル                |

| 18  | IPENA18    | 0     | R/W   | 0: クロック停止                          |

| 10  | II LIVATO  |       | 10,44 | 1: クロック供給                          |

|     |            |       |       | A-ENC ch0 のクロックイネーブル               |

| 17  | IPENA17    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

|     |            |       |       | PMD+ ch0 のクロックイネーブル                |

| 16  | IPENA16    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

|     |            |       |       | DMAC Unit A のクロックイネーブル             |

| 15  | IPENA15    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

|     |            |       |       | PORT R のクロックイネーブル                  |

| 14  | IPENA14    | 0     | R/W   | 0: クロック停止                          |

|     |            |       |       | 1: クロック供給                          |

| 13  | IPENA13    | 0     | R/W   | PORT P のクロックイネーブル                  |

| 13  | II LINAID  | 0     | 11/77 | 0: クロック停止                          |

| 1: クロック供給   PORT N のクロックイネーブル   O: クロック停止   1: クロック供給   PORT M のクロックイネーブル   O: クロック停止   1: クロック供給   PORT M のクロックイネーブル   O: クロック停止   1: クロック供給   PORT M のクロックイネーブル   O: クロック作本   D: クロックイネーブル   D: クロックイネーブル   D: クロック作本   D: クロックイネーブル   D: クロックイネーブル |    |         |   |     | 4 内口…与供价          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------|---|-----|-------------------|

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |         |   |     |                   |

| 1: クロック供給                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |         |   |     |                   |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12 | IPENA12 | 0 | R/W | 1 1 1 1 1         |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |         |   |     |                   |

| 1: クロック供給   PORT L のクロックイネーブル   O: クロック停止   1: クロック供給   PORT K のクロックイネーブル   O: クロック停止   1: クロック供給   PORT K のクロックイネーブル   O: クロック停止   1: クロック供給   PORT J のクロックイネーブル   O: クロック停止   1: クロック供給   PORT J のクロックイネーブル   O: クロック停止   1: クロック供給   PORT J のクロックイネーブル   O: クロック供給   PORT G のクロックイネーブル   O: クロック停止   1: クロック供給   PORT G のクロックイネーブル   O: クロック停止   1: クロック供給   PORT F のクロックイネーブル   O: クロック停止   1: クロック供給   PORT E のクロックイネーブル   O: クロック停止   1: クロック停止   1: クロック存止   1: クロック件と   1: クロック件と   1: クロック件と   1: クロック件と   1: クロックイネーブル   O: クロック停止   1: クロックイネーブル   O: クロックイネーブル   O: クロック停止   1: クロックイネーブル   O: クロック将止   1: クロックイネーブル   O: クロック停止   1: クロック件と   1: クロックイネーブル   O: クロック停止   1: クロックイネーブル   O: クロック存止   1: クロックイネーブル   O: クロック存止   1: クロックイネーブル   O: クロック存止   1: クロックイネーブル   O: クロックイネーブル   O: クロック件注   1: クロックイネーブル   O: クロックイネーブル   PORT B のクロックイネーブル   O: クロック件と   1: クロックイネーブル   O: クロック件と   1: クロックイネーブル   O: クロックイネーブル   O: クロック件と   1: クロックイネーブル   O: クロック件と   1: クロックイネーブル   O: クロックイネーブル   O: クロックイネーブル   O: クロックイネーブル   O: クロックイネーブル   O: クロック件と   1: クロックイネーブル   O: クロックイネー |    |         |   |     |                   |

| PORT L のクロックイネーブル                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11 | IPENA11 | 0 | R/W |                   |