# 32 ビット RISC マイクロコントローラ

# TXZファミリ

リファレンスマニュアル

RAM パリティ (RAMP-A)

**Revision 1.1**

2018-07

東芝デバイス&ストレージ株式会社

### 目次

| 序章                                          | 4       |

|---------------------------------------------|---------|

| 関連するドキュメント                                  | 4       |

| 表記規約                                        | 5       |

| 用語・略語                                       | 7       |

| 1. 概要                                       | 8       |

| 2. 構成                                       | 8       |

| 3. 動作説明                                     | 9       |

| 3.1. パリティデータ                                | 9       |

| 3.2. 動作                                     | 9       |

| 3.3. エラーの検出                                 | 10      |

| 4. レジスタ説明                                   | 11      |

| 4.1. レジスター覧                                 | 11      |

| 4.2. レジスタ詳細                                 | 12      |

| 4.2.1. <i>[RPARCTL]</i> (RAM パリティ制御レジスタ)    | 12      |

| 4.2.2. <i>[RPARST]</i> (RAM パリティステータスレジスタ)  | 12      |

| 4.2.3. [RPARCLR] (RAM パリティステータスクリアレジ        | スタ)13   |

| 4.2.4. <i>[RPAREAD0]</i> (RAM パリティエラーアドレスレジ | スタ 0)14 |

| 5. 使用方法の例                                   | 15      |

| 5.1. 実行例 1                                  | 15      |

| 5.2. 実行例 2                                  | 15      |

| 6. 改訂履歴                                     | 16      |

| 製品取り扱い上のお願い                                 | 17      |

## **TOSHIBA**

|       | 図目次                                         |   |

|-------|---------------------------------------------|---|

| 図 3.1 | RAM パリティ回路の構成図<br>RAM パリティ動作<br>RAM アドレス例 1 | 9 |

|       | RAM アドレス例 2                                 |   |

|       |                                             |   |

### 表目次

| 表 2.1 | 信号一覧表 | . 8 |

|-------|-------|-----|

| 表 6.1 | 改訂履歴  | 16  |

### 序章

関連するドキュメント

| 文書名    |

|--------|

| 製品個別情報 |

| 例外     |

#### 表記規約

• 数値表記は以下の規則に従います。

16 進数表記: 0xABC

10 進数表記: 123 または 0d123 (10 進表記であることを示す必要のある場合だけ使用)

2 進数表記: 0b111 (ビット数が本文中に明記されている場合は「0b」を省略可)

ローアクティブの信号は信号名の末尾に「N」で表記します。

● 信号がアクティブレベルに移ることを「アサート (assert)」アクティブでないレベルに移ることを「デアサート (deassert)」と呼びます。

複数の信号名は [m:n]とまとめて表記する場合があります。例: S[3:0] は S3,S2,S1,S0 の 4 つの信号名をまとめて表記しています。

本文中 / で囲まれたものはレジスタを定義しています。

例: [ABCD]

• 同種で複数のレジスタ、フィールド、ビット名は [n] で一括表記する場合があります。 例: [XYZ1], [XYZ2], [XYZ3]  $\rightarrow$  [XYZn]

「レジスター覧」中のレジスタ名でユニットまたはチャネルは「x」で一括表記しています。

「レジスター覧」中のレジスタ名でユニットまたはチャネルは「x」で一括表記しています。 ユニットの場合、「x」は A,B,C...を表します。

例: [ADACR0], [ADBCR0], [ADCCR0]→[ADxCR0]

チャネルの場合、「x」は0,1,2...を表します。

例: [T32A0RUNA], [T32A1RUNA], [T32A2RUNA]→[T32AxRUNA]

レジスタのビット範囲は [m:n] と表記します。例: [3:0] はビット3から0の範囲を表します。

レジスタの設定値は16進数または2進数のどちらかで表記されています。

例: [ABCD]<EFG>=0x01(16進数)、[XYZn]<VW>=1(2進数)

ワード、バイトは以下のビット長を表します。

バイト: 8 ビット ハーフワード: 16 ビット ワード: 32 ビット ダブルワード: 64 ビット

レジスタ内の各ビットの属性は以下の表記を使用しています。

R: リードオンリー W: ライトオンリー R/W: リード / ライト

- 断りのない限り、レジスタアクセスはワードアクセスだけをサポートします。

- 本文中の予約領域「Reserved」として定義されたレジスタは書き換えを行わないでください。 また、読み出した値を使用しないでください。

- Default 値が「一」となっているビットから読み出した値は不定です。

- 書き込み可能なビットフィールドと、リードオンリー「R」のビットフィールドが共存するレジス タに書き込みを行う場合、リードオンリー「R」のビットフィールドには Default 値を書き込んでく ださい。

Default 値が「一」となっている場合は、個々のレジスタの定義に従ってください。

- ライトオンリーのレジスタのReserved ビットフィールドには Default 値を書き込んでください。 Default 値が「—」となっている場合は、個々のレジスタの定義に従ってください。

- 書き込みと読み出しで異なる定義のレジスタへのリードモディファイライト処理は行わないでくだ さい。

Arm,Cortex および Thumb は Arm Limited(またはその子会社)の US またはその他の国における登録商標です。 All rights reserved.

FLASHメモリについては、米国SST社(Silicon Storage Technology, Inc.)からライセンスを受けたSuper Flash®技術を使用しています。Super Flash®は SST 社の登録商標です。

本資料に記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している 場合があります。

### 用語・略語

この仕様書で使用されている用語・略語の一部を記載します。

RAM Random Access Memory

INT Interrupt

### 1. 概要

RAM パリティの主な機能は、以下のとおりです。

| 機能分類       | 機能           | 動作説明                                 |

|------------|--------------|--------------------------------------|

| RAM パリティ制御 | パリティデータ生成    | RAM への書き込み時にパリティデータを生成して格納します。       |

|            | パリティ判定       | RAM からの読み出し時にパリティ判定を行いエラー検出をします。     |

| エラー検出      | エラーステータス     | ステータスレジスタに RAM エリアごとのエラーステータスを格納します。 |

|            | エラ一発生アドレス    | アドレスレジスタに RAM エリアごとのエラー発生アドレスを格納します。 |

| 割り込み       | RAM パリティ割り込み | パリティエラーが発生すると INTPARI を発生します。        |

### 2. 構成

RAM パリティ回路はパリティ機能制御回路、パリティ生成・判定回路から構成されます。

図 2.1 RAMパリティ回路の構成図

表 2.1 信号一覧表

| No | 信号名     | 信号名称         | 1/0 | 参照リファレンスマニュアル |

|----|---------|--------------|-----|---------------|

| 1  | INTPARI | RAM パリティ割り込み | 出力  | 例外,製品個別情報     |

#### 3. 動作説明

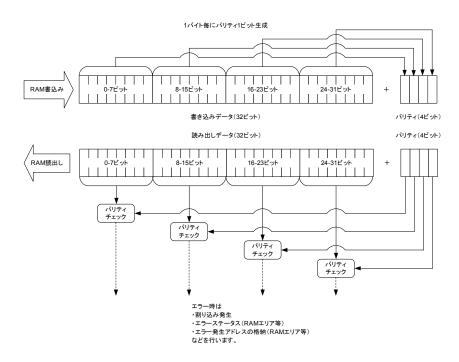

RAM パリティ機能は、RAM へ書き込み時にパリティデータを生成します。RAM 読み出し時はパリティデータを同時に読み出しパリティチェック(判定)します。パリティエラーが検出された場合にはRAM パリティ割り込み(INTPARI)を発生します。

#### 3.1. パリティデータ

パリティは RAM のデータ 1 バイトごとに 1 ビットが付与されます。 したがって 1 ワード(32 ビット) では 4 ビット分がパリティデータとして追加されます。

注) パリティデータは偶数パリティで生成されますが、パリティデータだけを直接操作することは できません。

#### 3.2. 動作

[RPARCTL]<RPAREN>でパリティエラー機能制御の許可/禁止の選択、[RPARCTL]<RPARF>でパリティエラー検出時の割り込み出力制御の許可/禁止の選択ができます。

リセット後は、[RPARCTL]<RPAREN>=1 (パリティエラー機能許可)、[RPARCTL]<RPARF>=0 (割り込み禁止)となっています。

パリティ機能を正しく使用するためには、最初にRAMの全てのエリアの初期化(注)を行ってください。 その後、割り込みの設定をしてください。

注) RAM の初期値は不定のため、RAM 読み出しの前に[RPARCTL]<RPAREN>=1(許可), [RPARCTL]<RPARF>=0 (割り込み禁止)の設定で RAM の初期化(データ書き込み)が必要です。

図 3.1 RAMパリティ動作

### 3.3. エラーの検出

RAM パリティエラーは、INTPARI の発生で検出されたことが分かります。

INTPARI割り込みサービスルーチンでRAMパリティステータスレジスタ[RPARST]<RPARFGn>=1(エラー発生)となっていることで発生した RAM エリアが分かります。エラーが発生した RAM エリアに対応する RAM パリティエラーアドレスレジスタ[RPAREADn]を読むことで具体的なエラー発生アドレスを取得できます。

注) RAM エリアの割り当てアドレスは製品ごとに異なります。製品のリファレンスマニュアル「製品個別情報」を参照してください。

### 4. レジスタ説明

### 4.1. レジスター覧

RAM パリティ制御レジスタとアドレスを以下に示します。

| 周辺機能     | Function name | Channel/Unit | Base address |

|----------|---------------|--------------|--------------|

| RAM パリティ | RAMP          | -            | 0x400BBB00   |

| レジスタ名                 | Base Address(Base+) |        |

|-----------------------|---------------------|--------|

| RAM パリティ制御レジスタ        | [RPARCTL]           | 0x0000 |

| RAM パリティステータスレジスタ     | [RPARST]            | 0x0004 |

| RAM パリティステータスクリアレジスタ  | [RPARCLR]           | 0x0008 |

| RAM パリティエラーアドレスレジスタ 0 | [RPAREAD0]          | 0x000C |

| RAM パリティエラーアドレスレジスタ 1 | [RPAREAD1]          | 0x0010 |

| RAM パリティエラーアドレスレジスタ 2 | [RPAREAD2]          | 0x0014 |

| RAM パリティエラーアドレスレジスタ 3 | [RPAREAD3]          | 0x0018 |

| RAM パリティエラーアドレスレジスタ 4 | [RPAREAD4]          | 0x001C |

| RAM パリティエラーアドレスレジスタ 5 | [RPAREAD5]          | 0x0020 |

| RAM パリティエラーアドレスレジスタ 6 | [RPAREAD6]          | 0x0024 |

| RAM パリティエラーアドレスレジスタ 7 | [RPAREAD7]          | 0x0028 |

#### 4.2. レジスタ詳細

### 4.2.1. [RPARCTL] (RAM パリティ制御レジスタ)

| Bit  | Bit Symbol | リセット後 | Туре | 機能                                           |

|------|------------|-------|------|----------------------------------------------|

| 31:2 | _          | 0     | R    | リードすると"0"が読めます。                              |

| 1    | RPARF      | 0     | R/W  | パリティエラ―発生時、割り込み要求出力制御(注 2)<br>0: 禁止<br>1: 許可 |

| 0    | RPAREN     | 1     | R/W  | パリティエラー機能制御(注 1)(注 2)<br>0: 禁止<br>1: 許可      |

- 注 1) <RPAREN>=0 (禁止)にすると、RAM 書き込み時のパリティ生成、パリティビットの格納、および、RAM 読み出し時のパリティチェック(判定)を行いません。

- 注 2) RAM の初期値は不定のため、RAM 読み出しの前に<RPAREN>=1 (許可)、<RPARF>=0 (割り込み禁止)の設定で RAM の初期化(データ書き込み)が必要です。

### 4.2.2. [RPARST] (RAM パリティステータスレジスタ)

| Bit  | Bit Symbol | リセット後 | Туре | 機能                                                              |

|------|------------|-------|------|-----------------------------------------------------------------|

| 31:8 | _          | 0     | R    | リードすると"0"が読めます。                                                 |

| 7    | RPARFG7    | 0     | R    | RAM パリティエラー ステータスフラグ 7 (RAM エリア 7)<br>0: エラー発生していない<br>1: エラー発生 |

| 6    | RPARFG6    | 0     | R    | RAM パリティエラー ステータスフラグ 6 (RAM エリア 6)<br>0: エラー発生していない<br>1: エラー発生 |

| 5    | RPARFG5    | 0     | R    | RAM パリティエラー ステータスフラグ 5 (RAM エリア 5)<br>0: エラー発生していない<br>1: エラー発生 |

| 4    | RPARFG4    | 0     | R    | RAM パリティエラー ステータスフラグ 4 (RAM エリア 4)<br>0: エラー発生していない<br>1: エラー発生 |

| 3    | RPARFG3    | 0     | R    | RAM パリティエラー ステータスフラグ 3 (RAM エリア 3)<br>0: エラー発生していない<br>1: エラー発生 |

| 2    | RPARFG2    | 0     | R    | RAM パリティエラー ステータスフラグ 2 (RAM エリア 2)<br>0: エラー発生していない<br>1: エラー発生 |

| 1    | RPARFG1    | 0     | R    | RAM パリティエラー ステータスフラグ 1 (RAM エリア 1)<br>0: エラー発生していない<br>1: エラー発生 |

| 0    | RPARFG0    | 0     | R    | RAM パリティエラー ステータスフラグ 0 (RAM エリア 0)<br>0: エラー発生していない<br>1: エラー発生 |

注 1) パリティエラーが発生すると、エラーとなったデータのアドレスが含まれる RAM エリアのフラグ<RPARFGn>が"1"になります。実際のエラーアドレスは"1"になった<RPARFGn>と対応する(同一のn値の) RAM パリティエラーアドレスレジスタn ([RPAREADn])で確認してください。

例:n=0 の場合はRAM パリティエラーアドレスレジスタ 0 ([RPAREAD0])。

- 注2) 各ステータスフラグは[RPARCLR]レジスタの該当ビットを"1"にするとクリアされます。

- 注 3) ステータスフラグ<RPARFGn>=1(エラー発生)のときに同じエリア n 内の別アドレスでパリティエラーが起きた場合、パリティエラーアドレス格納レジスタ([RPAREADn])は更新されません。

#### 4.2.3. [RPARCLR] (RAM パリティステータスクリアレジスタ)

| Bit  | Bit Symbol | リセット後 | Туре | 機能                                                                     |

|------|------------|-------|------|------------------------------------------------------------------------|

| 31:8 | _          | 0     | R    | リードすると"0"が読めます。                                                        |

| 7    | RPARCLR7   | 0     | W    | RAM パリティエラー ステータスフラグ 7 のクリア (RAM エリア 7)<br>0: -<br>1: ステータスをクリアする(注 1) |

| 6    | RPARCLR6   | 0     | W    | RAM パリティエラー ステータスフラグ 6 のクリア (RAM エリア 6)<br>0: -<br>1: ステータスをクリアする(注 1) |

| 5    | RPARCLR5   | 0     | W    | RAM パリティエラー ステータスフラグ 5 のクリア (RAM エリア 5)<br>0: -<br>1: ステータスをクリアする(注 1) |

| 4    | RPARCLR4   | 0     | W    | RAM パリティエラー ステータスフラグ 4 のクリア (RAM エリア 4)<br>0: -<br>1: ステータスをクリアする(注 1) |

| 3    | RPARCLR3   | 0     | W    | RAM パリティエラー ステータスフラグ 3 のクリア (RAM エリア 3)<br>0: -<br>1: ステータスをクリアする(注 1) |

| 2    | RPARCLR2   | 0     | W    | RAM パリティエラー ステータスフラグ 2 のクリア (RAM エリア 2)<br>0: -<br>1: ステータスをクリアする(注 1) |

| 1    | RPARCLR1   | 0     | W    | RAM パリティエラー ステータスフラグ 1 のクリア (RAM エリア 1)<br>0: -<br>1: ステータスをクリアする(注 1) |

| 0    | RPARCLR0   | 0     | W    | RAM パリティエラー ステータスフラグ 0 のクリア (RAM エリア 0)<br>0: -<br>1: ステータスをクリアする(注 1) |

- 注 1) 該当 RAM エリアのビットを"1"にすると、その RAM エリアのエラーステータスがクリアされます。

- 注2) フラグクリアと同時にエラーが発生した場合、エラー検出が優先されます。

- 注3) エラーアドレスの確認はフラグクリア前に行ってください。

### 4.2.4. [RPAREAD0] (RAM パリティエラーアドレスレジスタ 0)

[RPAREAD0]にはRAM エリア 0 の中でエラーが発生したアドレスが格納されます。 [RPAREAD1]~[RPAREAD7]も同様の構成、動作です。

| Bit  | Bit Symbol | リセット後      | Туре | 機能                                                                   |

|------|------------|------------|------|----------------------------------------------------------------------|

| 31:0 | RPAREADD0  | 0x00000000 | R    | RAM パリティエラ一発生アドレス<br>0x00000000: エラー発生無し<br>0x200XXXXX: エラーが発生したアドレス |

注) エラーステータスフラグ[*RPARST*]<RPARFG0>が"1"の間は、同じエリア 0 内の別アドレスでエラーが発生してもエラーアドレス[*RPAREAD0*]<RPAREADD0>は更新されません。

### 5. 使用方法の例

#### 5.1. 実行例 1

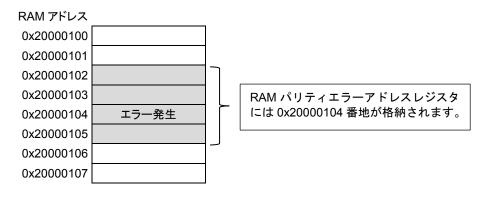

32 ビットアクセスで 0x20000102 番地をリードすると、0x20000102 番地から 0x20000105 番地の内容が読みだされます。 0x20000104 番地でパリティエラーが起きた場合、RAM パリティエラーアドレスレジスタ [RPAREADn] には、0x20000104 番地が格納されます。

図 5.1 RAMアドレス例1

#### 5.2. 実行例 2

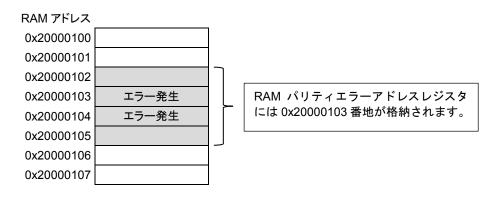

32 ビットアクセスで 0x20000102 番地をリードすると、0x20000102 番地から 0x20000105 番地の内容が読みだされます。0x20000103 番地と 0x20000104 番地でパリティエラーが起きた場合、RAM パリティエラーアドレスレジスタ [RPAREADn]には、0x20000103 番地が格納されます。

32 ビットアクセス時に複数の番地でパリティエラーが発生した場合、小さい方のアドレスが格納されます。2 カ所目以降のアドレスでのパリティエラー検出はできません。

図 5.2 RAMアドレス例2

### 6. 改訂履歴

表 6.1 改訂履歴

| Revision | Date       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 2017-07-13 | 新規                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.1      | 2018-07-06 | ・関連するドキュメント<br>タイトル: リファレンスマニュアル→ドキュメント<br>・2.構成<br>図 2.1 タイトル: RAM パリティ→RAM パリティ回路<br>図内 追記: "INTPARI"<br>削除: 左側のバス線<br>表 2.1 信号名称: パリティエラー割り込み要求信号→RAM パリティ割り込み<br>・3.2.動作<br>2 段目: パリティ機能許可→パリティエラー機能許可<br>エラー発生時割り込み禁止→割り込み禁止<br>注): <rparen>→[RPARCTL]<rparen><br/><rparf>→[RPARCTL]<rpare><br/>・4.1.レジスター覧<br/>ベースアドレスー覧 変更: RAMPARITY→RAMP<br/>・4.2.1.~4.2.4. タイトル記述変更:<br/>レジスタ名(レジスタ記号)→レジスタ記号(レジスタ名)<br/>・4.2.2. Type 変更: R/W→R<br/>注 1): "「" と "」" を削除<br/>注 3): "ステータスフラグ<rparfgn>=0(エラー発生していない)・・・" 削除<br/>・4.2.4. Bit Symbol 項, 注): RPAREADD→RPAREADDO<br/>機能項: "上記以外は無効です。" を削除<br/>・5.使用方法の例<br/>図 5.1、図 5.2: メモリアドレス→RAM アドレス</rparfgn></rpare></rparf></rparen></rparen> |

#### 製品取り扱い上のお願い

株式会社東芝およびその子会社ならびに関係会社を以下「当社」といいます。 本資料に掲載されているハードウエア、ソフトウエアおよびシステムを以下「本製品」といいます。

- 本製品に関する情報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

- ◆ 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を得て本 資料を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

- 当社は品質、信頼性の向上に努めていますが、半導体・ストレージ製品は一般に誤作動または故障する場合があります。本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウエア・ソフトウエア・システムに必要な安全設計を行うことをお願いします。なお、設計および使用に際しては、本製品に関する最新の情報(本資料、仕様書、データシート、アプリケーションノート、半導体信頼性ハンドブックなど)および本製品が使用される機器の取扱説明書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

- 本製品は、特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な財産損害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下"特定用途"という)に使用されることは意図されていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇宙機器、医療機器、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連機器、昇降機器、電力機器、金融関連機器などが含まれますが、本資料に個別に記載する用途は除きます。特定用途に使用された場合には、当社は一切の責任を負いません。なお、詳細は当社営業窓口までお問い合わせください。

- 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

- ◆ 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用することはできません。

- ◆ 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をしておりません。

- 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あるいは その他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、「米国輸出 管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず当社営業窓口までお問い合わせください。本製品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査の上、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は一切の責任を負いかねます。