# 32 ビット RISC マイクロコントローラ TMPM3H グループ(2)

リファレンスマニュアル 例外 (EXCEPT-M3H(2))

**Revision 3.0**

2018-07

東芝デバイス&ストレージ株式会社

# 目次

| 序章                                                  | 5  |

|-----------------------------------------------------|----|

| 関連するドキュメント                                          | 5  |

| 表記規約                                                | 6  |

| 用語・略語                                               | 8  |

| 1. 概要                                               | 9  |

| 1.1. 種類                                             | 9  |

| 1.2. 処理の流れ                                          | 10 |

| 1.2.1. 例外要求と検出                                      | 11 |

| 1.2.2. 例外の処理と割り込み処理ルーチンへの分岐(横取り)                    | 13 |

| 1.2.3. 割り込み処理ルーチンの実行                                | 14 |

| 1.2.4. 例外からの復帰                                      | 15 |

| 2. リセット例外                                           | 16 |

| 3. SysTick                                          | 17 |

| 4. 割り込み                                             | 17 |

| 4.1. マスク不能割り込み(NMI)                                 | 17 |

| 4.2. マスク可能割り込み                                      |    |

| 4.3. 割り込み要求                                         | 18 |

| 4.3.1. 経路                                           | 18 |

| 4.3.2. 割り込み要求の発生                                    | 21 |

| 4.3.3. 割り込み要求のモニタ                                   | 21 |

| 4.3.4. 割り込み要因の伝達                                    | 21 |

| 4.3.5. 外部割り込み端子を使用する際の注意                            | 21 |

| 4.4. 要因一覧                                           | 22 |

| 4.4.1. 結合割り込みについて                                   | 29 |

| 4.5. 割り込み検知レベル                                      | 32 |

| 4.5.1. 低消費電力モード解除時の注意                               | 32 |

| 4.6. 処理手順                                           | 33 |

| 4.6.1. 処理の流れ                                        | 33 |

| 4.6.2. 準備                                           | 34 |

| 4.6.3. 検出(INTIF)                                    | 36 |

| 4.6.4. 検出(CPU)                                      | 36 |

| 4.6.5. CPU の処理                                      | 36 |

| 4.6.6. 割り込み処理ルーチンでの処理(要因の取り下げ)                      | 37 |

| 5. 例外/ 割り込み関連レジスタ                                   | 38 |

| 5.1. レジスター覧                                         | 38 |

| 5.2. 割り込み制御レジスタ A                                   | 44 |

| 5.2.1. [IANIC00] (マスク不能割り込み A コントロールレジスタ 00)        | 44 |

| 5.2.2. [IAIMC00~03,16,17] (割り込み A モードコントロールレジスタ xx) | 44 |

| -<br>5.3. 割り込み制御レジスタ B                                       | 46  |

|--------------------------------------------------------------|-----|

| 5.3.1. [IBNIC00] (マスク不能割り込み B コントロールレジスタ 00)                 | 46  |

| 5.3.2. [IBIMC000~065,066~093,094] (割り込み B モードコントロールレジスタ xxx) | 46  |

| 5.4. リセットフラグレジスタ                                             | 48  |

| 5.4.1. [RLMRSTFLG0] (リセットフラグレジスタ 0)                          | 48  |

| 5.4.2. [RLMRSTFLG1] (リセットフラグレジスタ 1)                          | 49  |

| 5.5. 割り込みモニタレジスタ                                             | 50  |

| 5.5.1. [IMNFLGNMI] (マスク不能割り込みモニタフラグレジスタ)                     | 50  |

| 5.5.2. [IMNFLG1] (割り込みモニタフラグレジスタ 1)                          | 50  |

| 5.5.3. [IMNFLG3] (割り込みモニタフラグレジスタ 3)                          | 51  |

| 5.5.4. [IMNFLG4] (割り込みモニタフラグレジスタ 4)                          | 53  |

| 5.5.5. [IMNFLG5] (割り込みモニタフラグレジスタ 5)                          | 55  |

| 5.6. NVIC レジスタ                                               | 57  |

| 5.6.1. SysTick 制御およびステータスレジスタ                                | 57  |

| 5.6.2. SysTick リロード値レジスタ                                     | 57  |

| 5.6.3. SysTick 現在値レジスタ                                       | 57  |

| 5.6.4. SysTick 較正値レジスタ                                       | 58  |

| 5.6.5. 割り込み制御用レジスタ                                           | 59  |

| 5.6.5.1. 割り込みイネーブルセットレジスタ                                    | 59  |

| 5.6.5.2. 割り込みイネーブルクリアレジスタ                                    | 65  |

| 5.6.5.3. 割り込み保留セットレジスタ                                       | 71  |

| 5.6.5.4. 割り込み保留クリアレジスタ                                       | 77  |

| 5.6.6. 割り込み優先度レジスタ                                           | 83  |

| 5.6.7. ベクタテーブルオフセットレジスタ                                      | 84  |

| 5.6.8. アプリケーション割り込みおよびリセット制御レジスタ                             | 85  |

| 5.6.9. システムハンドラ優先度レジスタ                                       | 86  |

| 5.6.10. システムハンドラ制御および状態レジスタ                                  | 87  |

| 6. 製品別の割り込み要因一覧                                              | 88  |

| 6.1. ТМРМЗНQ,ТМРМЗНР,ТМРМЗНN,ТМРМЗНМ,ТМРМЗНL                 | 88  |

| 7. 改訂履歴                                                      | 98  |

| 製品取り扱い上のお願い                                                  | 100 |

表 6.8

#### 図目次 表目次 表 1.1 表 1.2 表 4.1 表 4.2 割り込み要因一覧(マスク不能割り込み)......22 割り込み要因一覧(割り込み制御レジスタ A)......22 表 4.3 割り込み要因一覧(割り込み制御レジスタ B) (1/6)......23 表 4.4 割り込み要因一覧(割り込み制御レジスタ B) (2/6)......24 割り込み要因一覧(割り込み制御レジスタ B) (3/6)......25 表 4.6 割り込み要因一覧(割り込み制御レジスタ B) 表 4.7 表 4.10 結合割り込み一覧(1).......29 結合割り込み一覧(3).......31 表 4.12 表 6.1 割り込み要因一覧(1/6).......88 表 6.2 割り込み要因一覧(2/6).......89 表 6.3 割り込み要因一覧(3/6).......90 割り込み要因一覧(4/6)......91 表 6.4 表 6.5 割り込み要因一覧(6/6).......93 表 6.6

割り込み番号 158(1/2).......94割り込み番号 158(2/2).......95

割り込み番号 160(1/2).......96

# 序章

# 関連するドキュメント

| 文書名                                  |

|--------------------------------------|

| 電源とリセット動作                            |

| 周波数検知回路                              |

| クロック選択式ウォッチドッグタイマ                    |

| 電圧検知回路                               |

| クロック制御と動作モード                         |

| Arm® ドキュメンテーションセット Cortex®-M3 プロセッサ編 |

#### 表記規約

数値表記は以下の規則に従います。

16 進数表記: 0xABC

10 進数表記: 123 または 0d123 (10 進表記であることを示す必要のある場合だけ使用)

2 進数表記: 0b111 (ビット数が本文中に明記されている場合は「0b」を省略可)

ローアクティブの信号は信号名の末尾に「N」で表記します。

● 信号がアクティブレベルに移ることを「アサート (assert)」アクティブでないレベルに移ることを 「デアサート (deassert)」と呼びます。

複数の信号名は [m:n]とまとめて表記する場合があります。例: S[3:0] は S3,S2,S1,S0 の 4 つの信号名をまとめて表記しています。

本文中 / で囲まれたものはレジスタを定義しています。

例: [ABCD]

● 同種で複数のレジスタ、フィールド、ビット名は「n」で一括表記する場合があります。

例: [XYZ1], [XYZ2], [XYZ3] → [XYZn]

「レジスタ一覧」中のレジスタ名でユニットまたはチャネルは「x」で一括表記しています。

ユニットの場合、「x」は A,B,C...を表します。

例: [ADACR0], [ADBCR0], [ADCCR0]→[ADxCR0]

チャネルの場合、「x」は0,1,2,...を表します。

例: [T32A0RUNA], [T32A1RUNA], [T32A2RUNA]→[T32AxRUNA]

レジスタのビット範囲は [m:n] と表記します。例: [3:0] はビット3から0の範囲を表します。

レジスタの設定値は16進数または2進数のどちらかで表記されています。

例: [ABCD]<EFG> = 0x01 (16 進数)、 [XYZn]<VW> = 1 (2 進数)

ワード、バイトは以下のビット長を表します。

バイト: 8 ビット ハーフワード: 16 ビット ワード: 32 ビット

ダブルワード: 64 ビット

レジスタ内の各ビットの属性は以下の表記を使用しています。

R: リードオンリー W: ライトオンリー R/W: リード / ライト

- 断りのない限り、レジスタアクセスはワードアクセスだけをサポートします。

- 本文中の予約領域「Reserved」として定義されたレジスタは書き換えを行わないでください。 また、読み出した値を使用しないでください。

- Default 値が「一」となっているビットから読み出した値は不定です。

- 書き込み可能なビットフィールドと、リードオンリー「R」のビットフィールドが共存するレジス タに書き込みを行う場合、リードオンリー「R」のビットフィールドには Default 値を書き込んで ください。

Default 値が「一」となっている場合は、個々のレジスタの定義に従ってください。

- ライトオンリーのレジスタの Reserved ビットフィールドには Default 値を書き込んでください。 Default 値が「─」となっている場合は、個々のレジスタの定義に従ってください。

- 書き込みと読み出しで異なる定義のレジスタへのリードモディファイライト処理は行わないでくだ さい。

Arm,Cortex および Thumb は Arm Limited(またはその子会社)の US またはその他の国における 登録商標です。 All rights reserved.

FLASH メモリについては、米国 SST 社 (Silicon Storage Technology, Inc) からライセンスを受けた Super Flash®技術を使用しています。Super Flash®は SST 社の登録商標です。

本資料に記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している 場合があります。

## 用語・略語

この仕様書で使用されている用語・略語の一部を記載します。

ADC Analog to Digital Converter

A-ENC Advanced Encoder input Circuit

A-PMD Advanced Programmable Motor Control Circuit

DAC Digital to Analog Converter

DMAC Direct Memory Access Controller

DNF Digital Noise Filter

IA Interrupt control register A

IB Interrupt control register B

IMCxx Interrupt Mode Control xx

IMNFLGNMI Interrupt Monitor Flag NMI

IMNFLGx Interrupt Monitor Flag x

INT Interrupt

INTIF Interrupt Interface Logic I<sup>2</sup>C Inter-Integrated Circuit

I2CS I<sup>2</sup>C wake-up circuit from Stand-by mode

LVD Voltage Detection Circuit

NICxx Non maskable Interrupt Control xx NVIC Nested Vectored Interrupt Controller OFD Oscillation Frequency Detector

RLMRSTFLGx RLM Reset Flag x

RMC Remote control signal preprocessor

RTC Real Time Clock

SIWDT Clock Selective Watchdog Timer

TRGSEL Trigger Selection circuit

TRM Trimming circuit

TSPI Toshiba Serial Peripheral Interface T32A 32-bit Timer Eevent Counter

UART Universal Asynchronous Receiver Transmitter

例外は CPU のアーキテクチャと深くかかわる部分ですので、必要に応じて「Arm®ドキュメンテーション Cortex®-M3 プロセッサ編」 もご覧ください。

# 1. 概要

例外は CPU に対し現在実行中の処理を中断して別の処理に移ることを要求するものです。

例外には、何らかの異常な状態が起こったときや例外を発生する命令を実行したときに発生するものと、外部端子や周辺機能からの割り込み要求信号といった、ハードウエアによる要因で発生する割り込みがあります。

全ての例外は優先度に従ってCPU内にあるネスト型ベクタ割り込みコントローラ(NVIC)によって処理されます。例外が発生すると、CPUはそのときの状態をスタックに退避し、割り込み処理ルーチンへ分岐します。割り込み処理ルーチンの実行後、スタックに退避した情報は自動的に復帰されます。

# 1.1. 種類

例外には以下のようなものがあります。

それぞれの例外の詳細な内容は、「Arm ドキュメンテーション Cortex-M3 プロセッサ編」を参照してください。

- ・リセット

- マスク不能割り込み(NMI)

- ハードフォールト

- メモリ管理

- バスフォールト

- 用法フォールト

- SVCall (スーパバイザコール)

- デバッグモニタ

- PendSV

- SysTick

- 外部割り込み

# 1.2. 処理の流れ

例外/割り込みの処理の流れの概略を以下に示します。以下の説明でハードウエアによる処理とソフトウエアによる処理を示しています。

それぞれの処理の内容について、後続の節で説明します。

| 処理                     | 内容                                | 説明      |

|------------------------|-----------------------------------|---------|

| INTIF/CPU が<br>例外を検出   | INTIF/CPU が例外要求を検出します。            | 1.2.1 節 |

| CPU が例外を処理             | CPU が例外処理を行います。                   | 1.2.2 節 |

| CPU が割り込み<br>処理ルーチンへ分岐 | 検出した例外に応じた割り込み処理ルーチンへ分岐しま<br>す。   | 1.2.2 節 |

| 割り込み処理ルーチン<br>実行       | 必要な処理を行います。                       | 1.2.3 節 |

| 例外からの復帰                | 別の割り込み処理ルーチンまたはもとのプログラムに復<br>帰します | 1.2.4 節 |

## 1.2.1. 例外要求と検出

#### (1) 例外要求の発生

例外は、CPU の命令実行、メモリアクセス、外部割り込み端子や周辺機能からの割り込み要求などにより発生します。

CPUの命令実行による例外の要求は、例外を発生する命令の実行や、命令実行中の異常が要因で発生します。

メモリアクセスによる例外の要求は、実行不可領域からの命令フェッチや、フォールト領域へのアクセスにより発生します。

外部割り込み端子や周辺機能による例外の要求は、個々の機能要因により発生します。INTIF を経由する割り込みについては、割り込み制御レジスタの設定が必要になります。詳細は「4. 割り込み」の節で説明します。

## (2) 例外の検出

複数の例外が同時に検出された場合には、CPUは優先度に従って最も優先度の高い例外を選択します。 各例外の優先度は以下のとおりです。"構成可能"と記載された例外は、優先度を設定することができます。また、メモリ管理、バスフォールト、用法フォールトは許可/禁止を選択することができます。 禁止された例外が発生した場合にはハードフォールトとして扱われます。

| 例外        | 優先度    | 要因                                                                                     | オフセット       |

|-----------|--------|----------------------------------------------------------------------------------------|-------------|

| リセット      | -3(最高) | リセット端子、SIWDT リセット、POR リセット、OFD リセット、LVD リセット、STOP2 解除リセット、SYSRESETREQ リセット、LOCKUP リセット | 0x00        |

| マスク不能割り込み | -2     | SIWDT, LVD                                                                             | 0x08        |

| ハードフォールト  | -1     | より優先度の高いフォールトの処理中、または禁止されているために<br>発生できないフォールト                                         | 0x0C        |

| メモリ管理     | 構成可能   | MPU (メモリ保護ユニット) からの例外<br>実行不可(XN) (Execute Never) 領域からの命令フェッチ                          | 0x10        |

| バスフォールト   | 構成可能   | メモリマップのハードフォールト領域に対するアクセス                                                              | 0x14        |

| 用法フォールト   | 構成可能   | 未定義命令の実行や、命令実行によって発生するその他のエラー                                                          | 0x18        |

| 予約        | -      |                                                                                        | 0x1C - 0x28 |

| SVCall    | 構成可能   | SVC 命令によるシステムサービスの呼び出し                                                                 | 0x2C        |

| デバッグモニタ   | 構成可能   | CPU がフォールト中でないときのデバッグモニタ                                                               | 0x30        |

| 予約        | -      |                                                                                        | 0x34        |

| PendSV    | 構成可能   | 保留可能なシステムサービスへの要求                                                                      | 0x38        |

| SysTick   | 構成可能   | システムタイマからの通知                                                                           | 0x3C        |

| 外部割り込み    | 構成可能   | 外部割り込み端子や周辺機能(注)                                                                       | 0x40        |

表 1.1 例外の種類と優先度

注) 割り込みは、製品により要因が異なります。具体的な要因と番号については、「4.4 要因一覧」を参照してください。

#### (3) 優先度の設定

#### ・優先度レベル

外部割り込みの優先度は、割り込み優先度レジスタで、それ以外の例外はシステムハンドラ優先度レジスタで該当する<PRI n>に設定します。

<PRI\_n>は、構成を変更することが可能になっており、優先度設定のためのビット数は製品により3ビット~8ビットのいずれかになります。このため、設定できる優先度の範囲も製品により異なります。

8ビットの構成の場合、優先度は $0\sim255$ のレベルを設定できます。最も高い優先度は"0"です。複数の要因を同じ優先度に設定した場合、番号の小さい例外の優先度が高くなります。

TMPM3H グループ(2)では、<PRI\_n[7:0]>の上位 4 ビットを実装しています。優先度は  $0\sim15$  のレベルです。

#### ・優先度のグループ化

優先度をグループ化することもできます。アプリケーション割り込みおよびリセット制御レジスタの <PRIGROUP> を設定することで、<PRI\_n>を横取り優先度とサブ優先度に分割することができます。

優先度はまず横取り優先度で判定され、横取り優先度が同じ場合サブ優先度で判定されます。サブ優 先度も同じ場合は例外番号の小さいほうが優先度が高くなります。

表 1.2 に優先度のグループ化の設定についてまとめます。表中の横取り優先度数、サブ優先度数は、 <PRI n>が 8 ビット構成の場合の数です。

| ADDICTION OF                            | <pri_i< th=""><th>n[7:0]&gt;</th><th></th><th></th></pri_i<> | n[7:0]>        |         |        |

|-----------------------------------------|--------------------------------------------------------------|----------------|---------|--------|

| <prigroup[2:0]><br/>の設定</prigroup[2:0]> | 横取り<br>フィールド                                                 | サブ優先度<br>フィールド | 横取り優先度数 | サブ優先度数 |

| 000                                     | [7:1]                                                        | [0]            | 128     | 2      |

| 001                                     | [7:2]                                                        | [1:0]          | 64      | 4      |

| 010                                     | [7:3]                                                        | [2:0]          | 32      | 8      |

| 011                                     | [7:4]                                                        | [3:0]          | 16      | 16     |

| 100                                     | [7:5]                                                        | [4:0]          | 8       | 32     |

| 101                                     | [7:6]                                                        | [5:0]          | 4       | 64     |

| 110                                     | [7]                                                          | [6:0]          | 2       | 128    |

| 111                                     | なし                                                           | [7:0]          | 1       | 256    |

表 1.2 優先度のグループ化設定

注) <PRI\_n>の構成が8ビットより小さい場合、下位ビットは"0"となります。例えば、4ビット構成の場合、<PRI\_n[7:4]>で優先度が設定され、<PRI\_n[3:0]>は"0000"になります。

# 1.2.2. 例外の処理と割り込み処理ルーチンへの分岐(横取り)

例外により、実行中の処理を中断して割り込み処理ルーチンへ分岐する動作を"横取り"と呼びます。

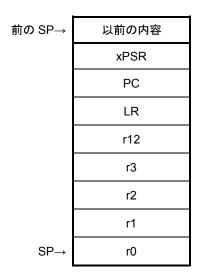

## (1) レジスタの退避

例外を検出すると、CPUは8つのレジスタの内容を退避します。退避するレジスタと退避の順序は以下のとおりです。

- 1. プログラムカウンタ(PC)

- 2. プログラムステータスレジスタ(xPSR)

- 3.  $r0 \sim r3$

- 4. r12

- 5. リンクレジスタ(LR)

レジスタの退避が終了すると、SPは8ワード分減らされます。レジスタ退避終了後のスタックの状態は以下のようになっています。

#### (2) 割り込み処理ルーチンのフェッチ

レジスタの退避と同時に CPU は割り込み処理ルーチンの命令フェッチを行います。

各例外の割り込み処理ルーチンの先頭番地をベクタテーブルに準備しておきます。ベクタテーブルはリセット後、コード領域の 0x00000000 番地に置かれます。ベクタテーブルは、ベクタテーブルオフセットレジスタを設定することでコード空間またはSRAM空間の任意のアドレスに置くことができます。また、ベクタテーブルにはメインスタックの初期値を設定します。

## (3) 後着

割り込み処理ルーチンの実行前に、検出した例外よりも優先度の高い例外を検出した場合、CPUは優先度の高い例外の処理に移行します。これを後着と呼びます。

後着の場合、CPUは新たに検出された例外の割り込み処理ルーチンのフェッチをあらためて行い、分岐しますが、再度レジスタの内容を退避することはありません。

#### (4) ベクタテーブルの構成

ベクタテーブルの構成は以下のとおりです。

最初の4ワード(スタックの初期値、リセット、マスク不能割り込み、ハードフォールトの割り込み処理ルーチンアドレス)は必ず設定する必要があります。

その他の例外については、割り込み処理ルーチンのアドレスを必要に応じて準備します。

| オフセット     | 例外        | 内容             | 備考 |

|-----------|-----------|----------------|----|

| 0x00      | リセット      | メインタスクの初期化     | 必須 |

| 0x04      | リセット      | 割り込み処理ルーチンアドレス | 必須 |

| 0x08      | マスク不能割り込み | 割り込み処理ルーチンアドレス | 必須 |

| 0x0C      | ハードフォールト  | 割り込み処理ルーチンアドレス | 必須 |

| 0x10      | メモリ管理     | 割り込み処理ルーチンアドレス | 任意 |

| 0x14      | バスフォールト   | 割り込み処理ルーチンアドレス | 任意 |

| 0x18      | 用法フォールト   | 割り込み処理ルーチンアドレス | 任意 |

| 0x1C~0x28 | 予約        |                |    |

| 0x2C      | SVCall    | 割り込み処理ルーチンアドレス | 任意 |

| 0x30      | デバッグモニタ   | 割り込み処理ルーチンアドレス | 任意 |

| 0x34      | 予約        |                |    |

| 0x38      | PendSV    | 割り込み処理ルーチンアドレス | 任意 |

| 0x3C      | SysTick   | 割り込み処理ルーチンアドレス | 任意 |

| 0x40      | 外部割り込み    | 割り込み処理ルーチンアドレス | 任意 |

## 1.2.3. 割り込み処理ルーチンの実行

割り込み処理ルーチンでは、発生した例外に応じて必要な処理を行います。割り込み処理ルーチンはユーザが準備します。

割り込み処理ルーチンでは、通常の処理プログラムに戻ったときに再度同じ割り込みが発生しないよう、割り込み要求の取り下げなどの処理が必要になる場合があります。

割り込みについての詳細は「4割り込み」の節で説明します。

割り込み処理ルーチンの実行中に現在処理中の例外よりも優先度の高い例外を検出した場合、CPUは現在実行中の割り込み処理ルーチンを中断し新たに検出された例外の処理を行います。

## 1.2.4. 例外からの復帰

#### (1) 割り込み処理ルーチンからの復帰先

割り込み処理ルーチン終了時の状態により復帰先が決まります。

- テールチェイン

- 保留中の例外が存在し、中断されている例外処理がないかまたは中断されているどの例外よりも優先度が高い場合、保留中の例外の割り込み処理ルーチンへ復帰します。 このとき、スタックの退避と復帰は省略されます。この動作をテールチェインと呼びます。

- 処理が中断されている割り込み処理ルーチンへ復帰 保留中の例外がない場合、または存在しても処理が中断されている例外の優先度が高い場合、中断されている例外の割り込み処理ルーチンへ復帰します。

- 元のプログラムへ復帰 保留中の例外も処理が中断されている例外もない場合、元のプログラムへ復帰します。

#### (2) 復帰処理

CPU は、割り込み処理ルーチンから復帰する際に以下の処理を行います。

- レジスタの復帰

退避していた 8 つのレジスタ(PC, xPSR, r0~r3, r12, LR)を復帰し SP を調整します。

- 割り込み番号のロード 退避していた xPSR から現在有効な割り込み番号をロードします。この割り込み番号によって CPU はどの割り込みに復帰するかを制御します。

- SP の選択 例外(ハンドラモード) へ復帰する場合、SP は SP\_main です。スレッドモードへ復帰する場合、SP は SP main または SP process です。

# 2. リセット例外

リセット例外には、以下の要因があります。

リセットの要因を確認するためには、リセットフラグレジスタの[RLMRSTFLGn]を参照してください。

- リセット端子によるリセット例外 リセット端子を"Low"にしたのち、"High"にすることによりリセット例外が発生します。

- POR によるリセット例外

POR によるリセット例外を発生する機能があります。POR の詳細はリファレンスマニュアルの「電源とリセット動作」を参照してください。

- OFD によるリセット例外

OFD によるリセット例外を発生する機能があります。OFD の詳細はリファレンスマニュアルの「周波数検知回路」を参照してください。

- SIWDT によるリセット例外 SIWDT にリセット例外を発生する機能があります。SIWDT の詳細はリファレンスマニュアルの「クロック選択式ウォッチドッグタイマ」を参照してください。

- LVD によるリセット例外

LVD にリセット例外を発生する機能があります。LVD の詳細はリファレンスマニュアルの「電圧検知回路」を参照してください。

- STOP2 解除によるリセット例外

STOP2 モード解除によりリセット例外が発生します。STOP2 モードの詳細はリファレンスマニュアルの「クロック制御と動作モード」を参照してください。

- <SYSRESETREQ>によるリセット例外

NVIC レジスタの、アプリケーション割り込みおよびリセット制御レジスタの

<SYSRESETREQ> をセットすることで、リセット例外を発生させることができます。

- LOCKUP によるリセット例外

回復不能な例外が発生すると Cortex-M3 コアは LOCKUP 信号を出力し、リセット例

外が発生します。LOCKUP の詳細は「Arm ドキュメンテーションセット Cortex-M3 プロセッサ編」を参照してください。

# 3. SysTick

SysTick は、CPU の持つシステムタイマを使用した割り込み機能です。

SysTick リロード値レジスタに値を設定し、SysTick 制御およびステータスレジスタで機能をイネーブルにすると、リロード値レジスタに設定された値がカウンタへリロードされカウントダウンを開始します。カウンタが"0" になると SysTick 例外を発生します。また、例外を保留しフラグでタイマが"0"になったことを確認することもできます。

# 4. 割り込み

この節では、割り込み要求の伝わる経路、要因、必要な設定について説明します。

# 4.1. マスク不能割り込み(NMI)

マスク不能割り込みには、以下の要因があります。

- SIWDT によるマスク不能割り込み SIWDT にマスク不能割り込みを発生する機能があります。

- LVD によるマスク不能割り込み LVD にマスク不能割り込みを発生する機能があります。

# 4.2. マスク可能割り込み

マスク可能割り込みの要因については、「4.4. 要因一覧」の割り込み制御レジスタ A、割り込み制御レジスタ B を参照してください。

# 4.3. 割り込み要求

割り込みは、割り込み要因ごとに割り込み要求信号により CPU へ通知されます。CPU は、優先順位付けを行い、最も優先度の高い割り込みを発生します。

## 4.3.1. 経路

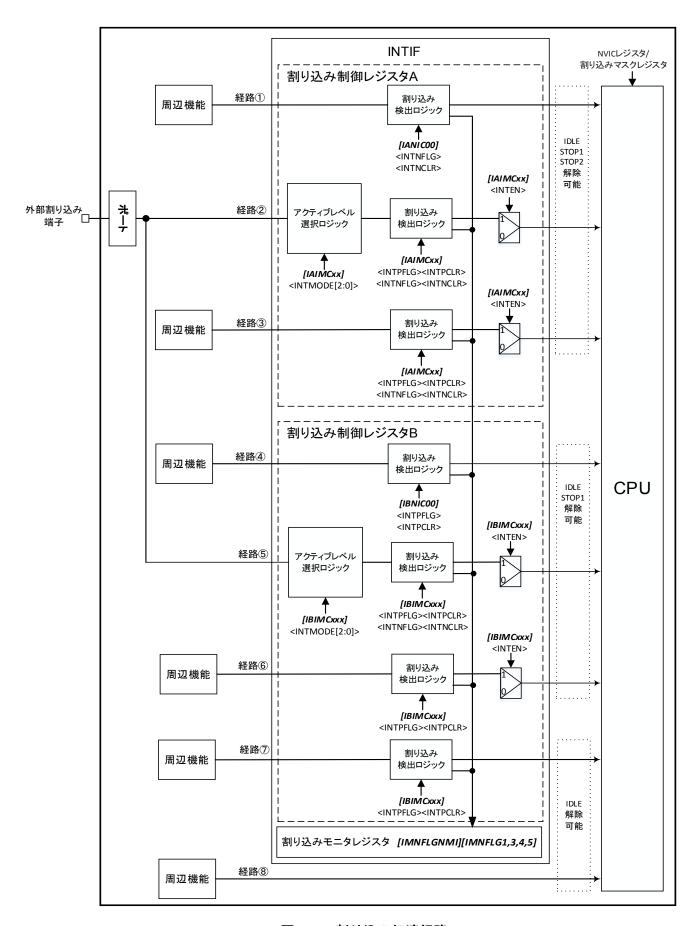

割り込みは、低消費電力モードからの解除にも使用可能で要因により経路が異なります。

図 4.1 割り込み伝達経路に割り込み伝達の経路を表 4.1 割り込み伝達経路の説明に割り込み伝達の経路の説明を示します。

- IDLE、STOP1、STOP2 モードを解除可能な割り込み IDLE、STOP1、STOP2 モードを解除可能な割り込みは、INTIF を経由し INTIF 内の割り 込み制御レジスタ A で制御され CPU へ通知されます。(経路①②③)

- IDLE、STOP1 モードを解除可能な割り込み

IDLE、STOP1 モードを解除可能な割り込みは、INTIF を経由し INTIF 内の割り込み制御レジスタ B で制御され CPU へ通知されます。(経路④⑤⑥)

- IDLE モードを解除可能な割り込み IDLE モードを解除可能な割り込みの一部の要因は INTIF を経由(経路⑦)し割り込み制御 レジスタ B で制御されますがその他の要因は INTIF を経由せず(経路⑧)直接 CPU へ通知されます。

低消費電力モード解除に関わらず INTIF を経由した割り込み要因を使用する場合は、割り込み制御レジスタ A または B の設定が必要です。

低消費電力モード解除要因の詳細については、リファレンスマニュアル「クロック制御と動作モード」の「低消費電力モードの解除ソース」の章を参照してください。

図 4.1 割り込み伝達経路

## 表 4.1 割り込み伝達経路の説明

| 経路  | 割り込み<br>番号                  | 割り込み要求                          | 経路説明                                                                                                                       |

|-----|-----------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 1   | -                           | 電圧検知回路割り込み                      | マスク不能割り込みです。<br>INTIF を経由して CPU に入力される経路です。<br>割り込み制御レジスタ A( <i>[IANIC00]</i> )で割り込み解除設定をします。                              |

| 2   | 0, 1, 2, 13                 | 外部割り込み<br>(00, 01, 02, 13)      | ポートの割り込み要求が INTIF を経由して CPU に入力される経路です。<br>要因ごとに割り込み制御レジスタ A( <b>[IAIMCxx]</b> ) で割り込み検知レベルの選択、割り込み解除、割り込み要求の許可/禁止を設定します。  |

| (3) | 50                          | I <sup>2</sup> C 低消費電力動作解除      | INTIF を経由して CPU に入力される経路です。<br>割り込み制御レジスタ A( <b>[IAIMCxx]</b> ) で割り込み解除、割り込み要                                              |

|     | 162                         | RTC 割り込み                        | 求の許可/禁止を設定します。                                                                                                             |

| 4   | -                           | ウォッチドッグタイマ割り込み                  | マスク不能割り込みです。<br>INTIF を経由して CPU に入力される経路です。<br>割り込み制御レジスタ B( <b>[IBNIC00]</b> )で割り込み解除設定をします。                              |

| (5) | 3~12,<br>14~22              | 外部割り込み<br>(03~12,14~31)         | ポートの割り込み要求が INTIF を経由して CPU に入力される経路です。<br>要因ごとに割り込み制御レジスタ B( <b>[IBIMCxxx]</b> ) で割り込み検知レベルの選択、割り込み解除、割り込み要求の許可/禁止を設定します。 |

| 6   | 163                         | リモコン割り込み                        | INTIF を経由して CPU に入力される経路です。<br>割り込み制御レジスタ B( <b>[IBIMC094]</b> )で割り込みの許可/禁止を設<br>定します。                                     |

| 7   | 158~161                     | DMAC 転送終了割り込み,<br>転送エラー割り込み (注) | INTIF を経由して CPU に入力される経路です。<br>要因ごとに割り込み制御レジスタ B( <b>[IBIMCxxx]</b> )で割り込み解除設<br>定をします。                                    |

| 8   | 23~49,<br>51~157<br>164~165 | その他の割り込み                        | INTIF を経由せず、直接 CPU に割り込み要求が入力される経路です。                                                                                      |

注) DMAC 転送終了割り込みは、1 つの割り込み番号に複数チャネルの割り込みが結合された割り込みです。詳細は「4.4.1. 結合割り込みについて」を参照してください。

#### 4.3.2. 割り込み要求の発生

割り込み要求は、割り込み要求に割り当てられた外部割り込み端子、周辺機能、割り込み要因に割り当てられた NVIC レジスタの割り込み保留セットレジスタの設定により発生します。

- 外部割り込み端子からの割り込み 外部割り込み端子を使用する場合、ポートの制御レジスタで端子を割り込み機能に設定 します。

- 周辺機能の割り込み 周辺機能の割り込みを使用する場合、使用する周辺機能で割り込み要求が発生されるよう設定する必要があります。設定の詳細については各章を参照ください。

- 割り込み要求の強制的な発生 NVIC の割り込み保留セットレジスタの該当するビットをセットすることで、割り込み 要求を強制的に発生させることができます。

CPUは、割り込み要求の"High"レベルを割り込みとして認識します。

## 4.3.3. 割り込み要求のモニタ

INTIF には、割り込みモニタフラグを備えています。フラグをモニタすることで割り込み要求が発生していることが分かります。複数の割り込み要求を1つの割り込み要因で受けている場合、割り込みモニタレジスタで割り込み要求を判断することができます。詳細は、「4.4. 要因一覧」を参照してください。

## 4.3.4. 割り込み要因の伝達

割り込み制御レジスタを経由しない割り込み要求は、直接CPUに接続されます。低消費電力モードの解除要因として使用できる割り込みなど、INTIFを経由してCPUに接続される割り込みは、INTIFの割り込み制御レジスタの設定が必要です。割り込みを低消費電力モードの解除要因として使用する場合は"High"レベルがCPUに伝達されます。INTIFで割り込み検知レベル、割り込み許可/禁止の設定をしてください。なお、外部割り込みについては次項の注意事項に留意してください。

## 4.3.5. 外部割り込み端子を使用する際の注意

外部割り込みを使用する際には、予期しない割り込みが発生しないよう以下の点に留意してください。

外部割り込み端子からの入力信号は、入力ディセーブル(*[PxIE]*<PxmIE>=0)の場合"Low"となります。 割り込み制御レジスタで*[IAIMCxx]*<INTMODE>を"Low"としていた場合、入力ディセーブルの状態でも外部割り込み端子が"Low"と認識されその状態で割り込みを有効にするとそのまま CPU に伝わり割り込みが発生します。割り込み端子入力を"High"レベルとして入力イネーブルにし、その後 CPU割り込み許可設定を行ってください。

# 4.4. 要因一覧

マスク不能割り込み(NMI)の割り込み要因を表 4.2に示します。マスク不能割り込み(NMI)の要因解除の設定を割り込み制御レジスタ A と割り込み制御レジスタ B で行います。

割り込み制御 割り込みモニタ 割り込み要因 割り込み要求 レジスタ レジスタ [IMNFLGNMI] INTLVD 電圧検知回路割り込み [IANIC00] <INT000FLG> [IMNFLGNMI] INTWDT0 ウォッチドッグタイマ割り込み [IBNIC00] -<INT016FLG>

表 4.2 割り込み要因一覧(マスク不能割り込み)

割り込み制御レジスタAの割り込み要因一覧を表 4.3に示します。これら割り込み要因は、低消費電力モード解除要因とすることができます。低消費電力モード解除検出の各種設定、割り込み許可/禁止を割り込み制御レジスタAで行います。

| 割り込み<br>番号 | 割り込み要因    | 割り込み要求                     | 割り込み制御 レジスタ | 割り込みモニタ<br>レジスタ                             |

|------------|-----------|----------------------------|-------------|---------------------------------------------|

| 0          | INT00     | 外部割り込み端子 00                | [IAIMC00]   | <i>[IMNFLG1]</i><br><int032flg></int032flg> |

| 1          | INT01     | 外部割り込み端子 01                | [IAIMC01]   | <i>[IMNFLG1]</i><br><int033flg></int033flg> |

| 2          | INT02     | 外部割り込み端子 02                | [IAIMC02]   | <i>[IMNFLG1]</i><br><int034flg></int034flg> |

| 13         | INT13     | 外部割り込み端子 13                | [IAIMC03]   | <i>[IMNFLG1]</i><br><int035flg></int035flg> |

| 50         | INTI2CWUP | I <sup>2</sup> C 低消費電力動作解除 | [IAIMC16]   | [IMNFLG1]<br><int048flg></int048flg>        |

| 162        | INTRTC    | RTC 割り込み                   | [IAIMC17]   | [IMNFLG1]<br><int049flg></int049flg>        |

表 4.3 割り込み要因一覧(割り込み制御レジスタA)

割り込み制御レジスタ B の要因一覧を表 4.4~表 4.9 に示します。一部の割り込みは、割り込み許可/禁止の設定を割り込み制御レジスタ B で行います。

表 4.4 割り込み要因一覧(割り込み制御レジスタB) (1/6)

| 割り込み<br>番号 | 割り込み要因   | 割り込み要求      | 割り込み制御レジスタ | 割り込みモニタ<br>レジスタ                             |

|------------|----------|-------------|------------|---------------------------------------------|

| 3          | INT03    | 外部割り込み端子 03 | [IBIMC066] | [IMNFLG5]<br><int162flg></int162flg>        |

| 4          | INT04    | 外部割り込み端子 04 | [IBIMC067] | [IMNFLG5]<br><int163flg></int163flg>        |

| 5          | INT05    | 外部割り込み端子 05 | [IBIMC068] | [IMNFLG5]<br><int164flg></int164flg>        |

| 6          | INT06    | 外部割り込み端子 06 | [IBIMC069] | [IMNFLG5]<br><int165flg></int165flg>        |

| 7          | INT07    | 外部割り込み端子 07 | [IBIMC070] | <i>[IMNFLG5]</i><br><int166flg></int166flg> |

| 8          | INT08    | 外部割り込み端子 08 | [IBIMC071] | [IMNFLG5]<br><int167flg></int167flg>        |

| 9          | INT09    | 外部割り込み端子 09 | [IBIMC072] | [IMNFLG5]<br><int168flg></int168flg>        |

| 10         | INT10    | 外部割り込み端子 10 | [IBIMC073] | [IMNFLG5]<br><int169flg></int169flg>        |

| 11         | INT11    | 外部割り込み端子 11 | [IBIMC074] | [IMNFLG5]<br><int170flg></int170flg>        |

| 12         | INT12    | 外部割り込み端子 12 | [IBIMC075] | [IMNFLG5]<br><int171flg></int171flg>        |

| 14         | INT14    | 外部割り込み端子 14 | [IBIMC076] | [IMNFLG5]<br><int172flg></int172flg>        |

| 15         | INT15    | 外部割り込み端子 15 | [IBIMC077] | [IMNFLG5]<br><int173flg></int173flg>        |

| 16         | INT16    | 外部割り込み端子 16 | [IBIMC078] | [IMNFLG5]<br><int174flg></int174flg>        |

| 17         | INT17_18 | 外部割り込み端子 17 | [IBIMC079] | [IMNFLG5]<br><int175flg></int175flg>        |

|            |          | 外部割り込み端子 18 | [IBIMC080] | [IMNFLG5]<br><int176flg></int176flg>        |

|            |          | 外部割り込み端子 19 | [IBIMC081] | [IMNFLG5]<br><int177flg></int177flg>        |

| 18         | INT19 22 | 外部割り込み端子 20 | [IBIMC082] | [IMNFLG5]<br><int178flg></int178flg>        |

|            |          | 外部割り込み端子 21 | [IBIMC083] | [IMNFLG5]<br><int179flg></int179flg>        |

|            |          | 外部割り込み端子 22 | [IBIMC084] | [IMNFLG5]<br><int180flg></int180flg>        |

|            |          | 外部割り込み端子 23 | [IBIMC085] | [IMNFLG5]<br><int181flg></int181flg>        |

| 19         | INT23 26 | 外部割り込み端子 24 | [IBIMC086] | [IMNFLG5]<br><int182flg></int182flg>        |

|            |          | 外部割り込み端子 25 | [IBIMC087] | [IMNFLG5]<br><int183flg></int183flg>        |

|            |          | 外部割り込み端子 26 | [IBIMC088] | [IMNFLG5]<br><int184flg></int184flg>        |

| 20         | INT27_28 | 外部割り込み端子 27 | [IBIMC089] | [IMNFLG5]<br><int185flg></int185flg>        |

| 20         | 27_20    | 外部割り込み端子 28 | [IBIMC090] | [IMNFLG5]<br><int186flg></int186flg>        |

| 21         | INT29    | 外部割り込み端子 29 | [IBIMC091] | [IMNFLG5]<br><int187flg></int187flg>        |

| 22         | INT30_31 | 外部割り込み端子 30 | [IBIMC092] | [IMNFLG5]<br><int188flg></int188flg>        |

|            |          | 外部割り込み端子 31 | [IBIMC093] | <i>[IMNFLG5]</i><br><int189flg></int189flg> |

# 表 4.5 割り込み要因一覧(割り込み制御レジスタB) (2/6)

| 割り込み<br>番号 | 割り込み要因    | 割り込み要求                 | 割り込み制御 レジスタ | 割り込みモニタ レジスタ |

|------------|-----------|------------------------|-------------|--------------|

| 23         | INTEMG0   | A-PMD ch0 EMG 割り込み     |             |              |

| 24         | INTOVV0   | A-PMD ch0 OVV 割り込み     |             |              |

| 25         | INTPMD0   | A-PMD ch0 PWM 割り込み     |             |              |

| 26         | INTENC00  | エンコーダ ch0 割り込み 0       |             |              |

| 27         | INTENC01  | エンコーダ ch0 割り込み 1       |             |              |

| 28         | INTADAPDA | ADC PMD トリガプログラム変換終了 A |             |              |

| 29         | INTADAPDB | ADC PMD トリガプログラム変換終了 B |             |              |

| 30         | INTADACP0 | ADC 監視割り込み 0           |             |              |

| 31         | INTADACP1 | ADC 監視割り込み 1           |             |              |

| 32         | INTADATRG | ADC 汎用トリガプログラム変換終了     |             |              |

| 33         | INTADASGL | ADC 単独プログラム変換終了        |             |              |

| 34         | INTADACNT | ADC 連続プログラム変換終了        |             |              |

| 35         | INTT0RX   | TSPI ch0 受信            |             |              |

| 36         | INTT0TX   | TSPI ch0 送信            |             |              |

| 37         | INTT0ERR  | TSPI ch0 エラー           |             |              |

| 38         | INTT1RX   | TSPI ch1 受信            |             |              |

| 39         | INTT1TX   | TSPI ch1 送信            |             |              |

| 40         | INTT1ERR  | TSPI ch1 エラー           |             |              |

| 41         | INTT2RX   | TSPI ch2 受信            |             |              |

| 42         | INTT2TX   | TSPI ch2 送信            |             |              |

| 43         | INTT2ERR  | TSPI ch2 エラー           |             |              |

| 44         | INTT3RX   | TSPI ch3 受信            |             |              |

| 45         | INTT3TX   | TSPI ch3 送信            |             |              |

| 46         | INTT3ERR  | TSPI ch3 エラー           |             |              |

| 47         | INTT4RX   | TSPI ch4 受信            |             |              |

| 48         | INTT4TX   | TSPI ch4 送信            |             |              |

| 49         | INTT4ERR  | TSPI ch4 エラー           |             |              |

# 表 4.6 割り込み要因一覧(割り込み制御レジスタB) (3/6)

| 割り込み<br>番号 | 割り込み要因      | 割り込み要求                            | 割り込み制御 レジスタ | 割り込みモニタ<br>レジスタ |

|------------|-------------|-----------------------------------|-------------|-----------------|

| 51         | INTI2C0     | I <sup>2</sup> C ch0 通信終了         |             |                 |

| 52         | INTI2C0AL   | I <sup>2</sup> C ch0 アービトレーションロスト |             |                 |

| 53         | INTI2C0BF   | I <sup>2</sup> C ch0 バスフリー        |             |                 |

| 54         | INTI2C0NA   | I <sup>2</sup> C ch0 No ACK       |             |                 |

| 55         | INTI2C1     | I <sup>2</sup> C ch1 通信終了         |             |                 |

| 56         | INTI2C1AL   | I <sup>2</sup> C ch1 アービトレーションロスト |             |                 |

| 57         | INTI2C1BF   | I <sup>2</sup> C ch1 バスフリー        |             |                 |

| 58         | INTI2C1NA   | I <sup>2</sup> C ch1 No ACK       |             |                 |

| 59         | INTI2C2     | I <sup>2</sup> C ch2 通信終了         |             |                 |

| 60         | INTI2C2AL   | I <sup>2</sup> C ch2 アービトレーションロスト |             |                 |

| 61         | INTI2C2BF   | I <sup>2</sup> C ch2 バスフリー        |             |                 |

| 62         | INTI2C2NA   | I <sup>2</sup> C ch2 No ACK       |             |                 |

| 63         | INTI2C3     | I2C ch3 通信終了                      |             |                 |

| 64         | INTI2C3AL   | I <sup>2</sup> C ch3 アービトレーションロスト |             |                 |

| 65         | INTI2C3BF   | I <sup>2</sup> C ch3 バスフリー        |             |                 |

| 66         | INTI2C3NA   | I <sup>2</sup> C ch3 No ACK       |             |                 |

| 67         | INTUART0RX  | UART ch0 受信                       |             |                 |

| 68         | INTUART0TX  | UART ch0 送信                       |             |                 |

| 69         | INTUART0ERR | UART ch0 エラー                      |             |                 |

| 70         | INTUART1RX  | UART ch1 受信                       |             |                 |

| 71         | INTUART1TX  | UART ch1 送信                       |             |                 |

| 72         | INTUART1ERR | UART ch1 エラー                      |             |                 |

| 73         | INTUART2RX  | UART ch2 受信                       |             |                 |

| 74         | INTUART2TX  | UART ch2 送信                       |             |                 |

| 75         | INTUART2ERR | UART ch2 エラー                      |             |                 |

| 76         | INTUART3RX  | UART ch3 受信                       |             |                 |

| 77         | INTUART3TX  | UART ch3 送信                       |             |                 |

| 78         | INTUART3ERR | UART ch3 エラー                      |             |                 |

| 79         | INTUART4RX  | UART ch4 受信                       |             |                 |

| 80         | INTUART4TX  | UART ch4 送信                       |             |                 |

| 81         | INTUART4ERR | UART ch4 エラー                      |             |                 |

| 82         | INTUART5RX  | UART ch5 受信                       |             |                 |

| 83         | INTUART5TX  | UART ch5 送信                       |             |                 |

| 84         | INTUART5ERR | UART ch5 エラー                      |             |                 |

# 表 4.7 割り込み要因一覧(割り込み制御レジスタB) (4/6)

| 割り込み<br>番号 | 割り込み要因         | 割り込み要求                              | 割り込み制御レジスタ | 割り込みモニタ レジスタ |

|------------|----------------|-------------------------------------|------------|--------------|

| 85         | INTT32A00A     | T32A ch0 タイマ A 一致、<br>オーバフロー、アンダフロー |            |              |

| 86         | INTT32A00ACAP0 | T32A ch0 タイマ A キャプチャ 0              |            |              |

| 87         | INTT32A00ACAP1 | T32A ch0 タイマ A キャプチャ 1              |            |              |

| 88         | INTT32A00B     | T32A ch0 タイマ B 一致、<br>オーバフロー、アンダフロー |            |              |

| 89         | INTT32A00BCAP0 | T32A ch0 タイマ B キャプチャ 0              |            |              |

| 90         | INTT32A00BCAP1 | T32A ch0 タイマ B キャプチャ 1              |            |              |

| 91         | INTT32A00C     | T32A ch0 タイマ C 一致、<br>オーバフロー、アンダフロー |            |              |

| 92         | INTT32A00CCAP0 | T32A ch0 タイマ C キャプチャ 0              |            |              |

| 93         | INTT32A00CCAP1 | T32A ch0 タイマ C キャプチャ 1              |            |              |

| 94         | INTT32A01A     | T32A ch1 タイマ A 一致、<br>オーバフロー、アンダフロー |            |              |

| 95         | INTT32A01ACAP0 | T32A ch1 タイマ A キャプチャ 0              |            |              |

| 96         | INTT32A01ACAP1 | T32A ch1 タイマ A キャプチャ 1              |            |              |

| 97         | INTT32A01B     | T32A ch1 タイマ B 一致、<br>オーバフロー、アンダフロー |            |              |

| 98         | INTT32A01BCAP0 | T32A ch1 タイマ B キャプチャ 0              |            |              |

| 99         | INTT32A01BCAP1 | T32A ch1 タイマ B キャプチャ 1              |            |              |

| 100        | INTT32A01C     | T32A ch1 タイマ C 一致、<br>オーバフロー、アンダフロー |            |              |

| 101        | INTT32A01CCAP0 | T32A ch1 タイマ C キャプチャ 0              |            |              |

| 102        | INTT32A01CCAP1 | T32A ch1 タイマ C キャプチャ 1              |            |              |

| 103        | INTT32A02A     | T32A ch2 タイマ A 一致、<br>オーバフロー、アンダフロー |            |              |

| 104        | INTT32A02ACAP0 | T32A ch2 タイマ A キャプチャ 0              |            |              |

| 105        | INTT32A02ACAP1 | T32A ch2 タイマ A キャプチャ 1              |            |              |

| 106        | INTT32A02B     | T32A ch2 タイマ B 一致、<br>オーバフロー、アンダフロー |            |              |

| 107        | INTT32A02BCAP0 | T32A ch2 タイマ B キャプチャ 0              |            |              |

| 108        | INTT32A02BCAP1 | T32A ch2 タイマ B キャプチャ 1              |            |              |

| 109        | INTT32A02C     | T32A ch2 タイマ C 一致、<br>オーバフロー、アンダフロー |            |              |

| 110        | INTT32A02CCAP0 | T32A ch2 タイマ C キャプチャ 0              |            |              |

| 111        | INTT32A02CCAP1 | T32A ch2 タイマ C キャプチャ 1              |            |              |

# 表 4.8 割り込み要因一覧(割り込み制御レジスタB) (5/6)

| 割り込み<br>番号 | 割り込み要因         | 割り込み要求                              | 割り込み制御 レジスタ | 割り込みモニタ<br>レジスタ |

|------------|----------------|-------------------------------------|-------------|-----------------|

| 112        | INTT32A03A     | T32A ch3 タイマ A 一致、<br>オーバフロー、アンダフロー |             |                 |

| 113        | INTT32A03ACAP0 | T32A ch3 タイマ A キャプチャ 0              |             |                 |

| 114        | INTT32A03ACAP1 | T32A ch3 タイマ A キャプチャ 1              |             |                 |

| 115        | INTT32A03B     | T32A ch3 タイマ B 一致、<br>オーバフロー、アンダフロー |             |                 |

| 116        | INTT32A03BCAP0 | T32A ch3 タイマ B キャプチャ 0              |             |                 |

| 117        | INTT32A03BCAP1 | T32A ch3 タイマ B キャプチャ 1              |             |                 |

| 118        | INTT32A03C     | T32A ch3 タイマ C 一致、<br>オーバフロー、アンダフロー |             |                 |

| 119        | INTT32A03CCAP0 | T32A ch3 タイマ C キャプチャ 0              |             |                 |

| 120        | INTT32A03CCAP1 | T32A ch3 タイマ C キャプチャ 1              |             |                 |

| 121        | INTT32A04A     | T32A ch4 タイマ A 一致、<br>オーバフロー、アンダフロー |             |                 |

| 122        | INTT32A04ACAP0 | T32A ch4 タイマ A キャプチャ 0              |             |                 |

| 123        | INTT32A04ACAP1 | T32A ch4 タイマ A キャプチャ 1              |             |                 |

| 124        | INTT32A04B     | T32A ch4 タイマ B 一致、<br>オーバフロー、アンダフロー |             |                 |

| 125        | INTT32A04BCAP0 | T32A ch4 タイマ B キャプチャ 0              |             |                 |

| 126        | INTT32A04BCAP1 | T32A ch4 タイマ B キャプチャ 1              |             |                 |

| 127        | INTT32A04C     | T32A ch4 タイマ C 一致、<br>オーバフロー、アンダフロー |             |                 |

| 128        | INTT32A04CCAP0 | T32A ch4 タイマ C キャプチャ 0              |             |                 |

| 129        | INTT32A04CCAP1 | T32A ch4 タイマ C キャプチャ 1              |             |                 |

| 130        | INTT32A05A     | T32A ch5 タイマ A 一致、<br>オーバフロー、アンダフロー |             |                 |

| 131        | INTT32A05ACAP0 | T32A ch5 タイマ A キャプチャ 0              |             |                 |

| 132        | INTT32A05ACAP1 | T32A ch5 タイマ A キャプチャ 1              |             |                 |

| 133        | INTT32A05B     | T32A ch5 タイマ B 一致、<br>オーバフロー、アンダフロー |             |                 |

| 134        | INTT32A05BCAP0 | T32A ch5 タイマ B キャプチャ 0              |             |                 |

| 135        | INTT32A05BCAP1 | T32A ch5 タイマ B キャプチャ 1              |             |                 |

| 136        | INTT32A05C     | T32A ch5 タイマ C 一致、<br>オーバフロー、アンダフロー |             |                 |

| 137        | INTT32A05CCAP0 | T32A ch5 タイマ C キャプチャ 0              |             |                 |

| 138        | INTT32A05CCAP1 | T32A ch5 タイマ C キャプチャ 1              |             |                 |

| 139        | INTT32A06A     | T32A ch6 タイマ A 一致、<br>オーバフロー、アンダフロー |             |                 |

| 140        | INTT32A06ACAP0 | T32A ch6 タイマ A キャプチャ 0              |             |                 |

| 141        | INTT32A06ACAP1 | T32A ch6 タイマ A キャプチャ 1              |             |                 |

# 表 4.9 割り込み要因一覧(割り込み制御レジスタB) (6/6)

| 割り込み<br>番号 | 割り込み要因         | 割り込み要求                              | 割り込み制御 レジスタ       | 割り込みモニタ<br>レジスタ                                     |

|------------|----------------|-------------------------------------|-------------------|-----------------------------------------------------|

| 142        | INTT32A06B     | T32A ch6 タイマ B 一致、<br>オーバフロー、アンダフロー |                   |                                                     |

| 143        | INTT32A06BCAP0 | T32A ch6 タイマ B キャプチャ 0              |                   |                                                     |

| 144        | INTT32A06BCAP1 | T32A ch6 タイマ B キャプチャ 1              |                   |                                                     |

| 145        | INTT32A06C     | T32A ch6 タイマ C 一致、<br>オーバフロー、アンダフロー |                   |                                                     |

| 146        | INTT32A06CCAP0 | T32A ch6 タイマ C キャプチャ 0              |                   |                                                     |

| 147        | INTT32A06CCAP1 | T32A ch6 タイマ C キャプチャ 1              |                   |                                                     |

| 148        | INTT32A07A     | T32A ch7 タイマ A 一致、<br>オーバフロー、アンダフロー |                   |                                                     |

| 149        | INTT32A07ACAP0 | T32A ch7 タイマ A キャプチャ 0              |                   |                                                     |

| 150        | INTT32A07ACAP1 | T32A ch7 タイマ A キャプチャ 1              |                   |                                                     |

| 151        | INTT32A07B     | T32A ch7 タイマ B 一致、<br>オーバフロー、アンダフロー |                   |                                                     |

| 152        | INTT32A07BCAP0 | T32A ch7 タイマ B キャプチャ 0              |                   |                                                     |

| 153        | INTT32A07BCAP1 | T32A ch7 タイマ B キャプチャ 1              |                   |                                                     |

| 154        | INTT32A07C     | T32A ch7 タイマ C 一致、<br>オーバフロー、アンダフロー |                   |                                                     |

| 155        | INTT32A07CCAP0 | T32A ch7 タイマ C キャプチャ 0              |                   |                                                     |

| 156        | INTT32A07CCAP1 | T32A ch7 タイマ C キャプチャ 1              |                   |                                                     |

| 157        | INTPARI        | RAM パリティ割り込み                        |                   |                                                     |

|            |                |                                     | [IBIMC000]<br>~   | [IMNFLG3]<br><int96flg></int96flg>                  |

| 158        | INTDMAATC      | DMAC Unit A 転送終了(ch0~31)            | [IBIMC031]<br>(注) | ~<br><int127flg><br/>(注)</int127flg>                |

| 159        | INTDMAAERR     | DMAC Unit A 転送エラー                   | [IBIMC032]        | [IMNFLG4]<br><int128flg></int128flg>                |

| 400        | INTERNACE      |                                     | [IBIMC033]<br>~   | [IMNFLG4]<br><int129flg><br/>~</int129flg>          |

| 160        | INTDMABTC      | DMAC Unit B 転送終了(ch0~31)            | [IBIMC064]<br>(注) | <i>[IMNFLG5]</i><br><int160flg><br/>(注)</int160flg> |

| 161        | INTDMABERR     | DMAC Unit B 転送エラー                   | [IBIMC065]        | [IMNFLG5]<br><int161flg></int161flg>                |

| 163        | INTRMC0        | リモコン割り込み                            | [IBIMC094]        | [IMNFLG5]<br><int190flg></int190flg>                |

| 164        | INTFLCRDY      | Code FLASH Ready 割り込み               |                   |                                                     |

| 165        | INTFLDRDY      | Data FLASH Ready 割り込み               |                   |                                                     |

注) 「4.4.1. 結合割り込みについて」を参照してください。

# 4.4.1. 結合割り込みについて

結合している割り込みの詳細は下記のとおりです。

表 4.10 結合割り込み一覧(1)

| 割り込み | 割り込み要因                      |                              | 割り込み制御                       | 割り込みモニタ                 |

|------|-----------------------------|------------------------------|------------------------------|-------------------------|

| 番号   | B172-75B                    |                              | レジスタ                         | レジスタ                    |

|      |                             | ᆔᅁᄜᆘᄀᇃᇷᄥᄀᇧ                   | [[D]MC0701                   | [IMNFLG5]               |

| 47   | INIT47 40                   | 外部割り込み端子 17                  | [IBIMC079]                   | <ĪNT175FLG>             |

| 17   | INT17_18                    | 티 현대비 [12] 가 보니 그 4.0        | !!D!!!!                      | [IMNFLG5]               |

|      |                             | 外部割り込み端子 18                  | [IBIMC080]                   | <int176flg></int176flg> |

|      |                             | ᆔᅘᄜᆘᄀᅺᆉ                      | [[D]]][[0.004]               | [IMNFLG5]               |

|      |                             | 外部割り込み端子 19                  | [IBIMC081]                   | <ĪNT177FLG>             |

|      |                             | 外部割り込み端子 20                  | [IDIMC0001                   | [IMNFLG5]               |

| 40   | INIT40 00                   | 外部割り込み端子 20<br>              | [IBIMC082]                   | <ĪNT178FLG>             |

| 18   | INT19_22                    | 外部割り込み端子 21                  | IIDIMC0021                   | [IMNFLG5]               |

|      |                             | 7ト印制の込み端子 21                 | [IBIMC083]                   | <int179flg></int179flg> |

|      |                             | 外部割り込み端子 22                  | IIDIMC0941                   | [IMNFLG5]               |

|      |                             | 外部割り込み端子 22 [IBIMC084]       | <int180flg></int180flg>      |                         |

|      |                             | 서 如劑시기 되받고 22                | 部割り込み端子 23 <b>[IBIMC085]</b> | [IMNFLG5]               |

|      |                             | 外間割り込み端子 23                  |                              | <int181flg></int181flg> |

|      |                             | 外部割り込み端子 24                  | [IBIMC086]                   | [IMNFLG5]               |

| 19   | INT23 26                    | 7下印刷り込みが刷 1 24               | [IBINIC000]                  | <int182flg></int182flg> |

| 13   | 114123_20                   | 外部割り込み端子 25                  | [IBIMC087]                   | [IMNFLG5]               |

|      |                             | 7下印刷 7 20 7 3                | [IBINICOOT]                  | <int183flg></int183flg> |

|      |                             | 外部割り込み端子 26                  | [IBIMC088]                   | [IMNFLG5]               |

|      |                             | 7下67日,7是67月前 1 20            | [IBINICO00]                  | <int184flg></int184flg> |

|      | 外部割り込み端子 27 <b>[IBIMC08</b> | [IBIMC089]                   | [IMNFLG5]                    |                         |

| 20   | INT27_28                    | 7下日7日197 <u>2</u> 2073川 1 27 | [IBINIO003]                  | <int185flg></int185flg> |

| 20   | 11127_20                    | トリストリント 外部割り込み端子 28          | [IBIMC090]                   | [IMNFLG5]               |

|      |                             | 71100172073111 20            | [1511110030]                 | <int186flg></int186flg> |

|      |                             | 外部割り込み端子 30                  | [IBIMC092]                   | [IMNFLG5]               |

| 22   | INT30 31                    | 71 474 7 20 7 34 1 3 00      | LIBINIOUSE                   | <int188flg></int188flg> |

|      | 114100_01                   | 外部割り込み端子 31                  | [IBIMC093]                   | [IMNFLG5]               |

|      |                             | 가 다리가 있으나 게이 기 이 기           | [151110030]                  | <int189flg></int189flg> |

表 4.11 結合割り込み一覧(2)

| 割り込み<br>番号 | 割り込み要因                           |      | 割り込み制御レジスタ | 割り込みモニタ<br>レジスタ                    |

|------------|----------------------------------|------|------------|------------------------------------|

|            |                                  | ch0  | [IBIMC000] | [IMNFLG3] <int96flg></int96flg>    |

|            |                                  | ch1  | [IBIMC001] | [IMNFLG3] <int97flg></int97flg>    |

|            |                                  | ch2  | [IBIMC002] | [IMNFLG3] <int98flg></int98flg>    |

|            |                                  | ch3  | [IBIMC003] | [IMNFLG3] <int99flg></int99flg>    |

|            |                                  | ch4  | [IBIMC004] | [IMNFLG3] <int100flg></int100flg>  |

|            |                                  | ch5  | [IBIMC005] | [IMNFLG3] <int101flg></int101flg>  |

|            |                                  | ch6  | [IBIMC006] | [IMNFLG3] <int102flg></int102flg>  |

|            |                                  | ch7  | [IBIMC007] | [IMNFLG3] <int103flg></int103flg>  |

|            |                                  | ch8  | [IBIMC008] | [IMNFLG3] <int104flg></int104flg>  |

|            |                                  | ch9  | [IBIMC009] | [IMNFLG3] <int105flg></int105flg>  |

|            |                                  | ch10 | [IBIMC010] | [IMNFLG3] <int106flg></int106flg>  |

|            |                                  | ch11 | [IBIMC011] | [IMNFLG3] <int107flg></int107flg>  |

|            | DMAC (Unit A)転送終了<br>(INTDMAATC) | ch12 | [IBIMC012] | [IMNFLG3]] <int108flg></int108flg> |

|            |                                  | ch13 | [IBIMC013] | [IMNFLG3] <int109flg></int109flg>  |

|            |                                  | ch14 | [IBIMC014] | [IMNFLG3] <int110flg></int110flg>  |

| 158        |                                  | ch15 | [IBIMC015] | [IMNFLG3] <int111flg></int111flg>  |

| 130        |                                  | ch16 | [IBIMC016] | [IMNFLG3] <int112flg></int112flg>  |

|            |                                  | ch17 | [IBIMC017] | [IMNFLG3] <int113flg></int113flg>  |

|            |                                  | ch18 | [IBIMC018] | [IMNFLG3] <int114flg></int114flg>  |

|            |                                  | ch19 | [IBIMC019] | [IMNFLG3] <int115flg></int115flg>  |

|            |                                  | ch20 | [IBIMC020] | [IMNFLG3] <int116flg></int116flg>  |

|            |                                  | ch21 | [IBIMC021] | [IMNFLG3] <int117flg></int117flg>  |

|            |                                  | ch22 | [IBIMC022] | [IMNFLG3] <int118flg></int118flg>  |

|            |                                  | ch23 | [IBIMC023] | [IMNFLG3] <int119flg></int119flg>  |

|            |                                  | ch24 | [IBIMC024] | [IMNFLG3] <int120flg></int120flg>  |

|            |                                  | ch25 | [IBIMC025] | [IMNFLG3] <int121flg></int121flg>  |

|            |                                  | ch26 | [IBIMC026] | [IMNFLG3] <int122flg></int122flg>  |

|            |                                  | ch27 | [IBIMC027] | [IMNFLG3] <int123flg></int123flg>  |

|            |                                  | ch28 | [IBIMC028] | [IMNFLG3] <int124flg></int124flg>  |

|            |                                  | ch29 | [IBIMC029] | [IMNFLG3] <int125flg></int125flg>  |

|            |                                  | ch30 | [IBIMC030] | [IMNFLG3] <int126flg></int126flg>  |

|            |                                  | ch31 | [IBIMC031] | [IMNFLG3] <int127flg></int127flg>  |

表 4.12 結合割り込み一覧(3)

| 割り込み<br>番号 | 割り込み要求                           |      | 割り込み制御 レジスタ | 割り込みモニタ<br>レジスタ                          |

|------------|----------------------------------|------|-------------|------------------------------------------|

|            |                                  | ch0  | [IBIMC033]  | [IMNFLG4] <int129flg></int129flg>        |

|            |                                  | ch1  | [IBIMC034]  | [IMNFLG4] <int130flg></int130flg>        |

|            |                                  | ch2  | [IBIMC035]  | [IMNFLG4] <int131flg></int131flg>        |

|            |                                  | ch3  | [IBIMC036]  | [IMNFLG4] <int132flg></int132flg>        |

|            |                                  | ch4  | [IBIMC037]  | [IMNFLG4] <int133flg></int133flg>        |

|            |                                  | ch5  | [IBIMC038]  | [IMNFLG4] <int134flg></int134flg>        |

|            |                                  | ch6  | [IBIMC039]  | [IMNFLG4] <int135flg></int135flg>        |

|            |                                  | ch7  | [IBIMC040]  | [IMNFLG4] <int136flg></int136flg>        |

|            |                                  | ch8  | [IBIMC041]  | [IMNFLG4] <int137flg></int137flg>        |

|            |                                  | ch9  | [IBIMC042]  | [IMNFLG4] <int138flg></int138flg>        |

|            |                                  | ch10 | [IBIMC043]  | [IMNFLG4] <int139flg></int139flg>        |

|            |                                  | ch11 | [IBIMC044]  | [IMNFLG4] <int140flg></int140flg>        |

|            | DMAC (Unit B)転送終了<br>(INTDMABTC) | ch12 | [IBIMC045]  | [IMNFLG4] <int141flg></int141flg>        |

|            |                                  | ch13 | [IBIMC046]  | [IMNFLG4] <int142flg></int142flg>        |

|            |                                  | ch14 | [IBIMC047]  | [IMNFLG4] <int143flg></int143flg>        |

| 160        |                                  | ch15 | [IBIMC048]  | <i>[IMNFLG4]</i> <int144flg></int144flg> |

| 100        |                                  | ch16 | [IBIMC049]  | [IMNFLG4] <int145flg></int145flg>        |

|            |                                  | ch17 | [IBIMC050]  | [IMNFLG4] <int146flg></int146flg>        |

|            |                                  | ch18 | [IBIMC051]  | [IMNFLG4] <int147flg></int147flg>        |

|            |                                  | ch19 | [IBIMC052]  | [IMNFLG4] <int148flg></int148flg>        |

|            |                                  | ch20 | [IBIMC053]  | [IMNFLG4] <int149flg></int149flg>        |

|            |                                  | ch21 | [IBIMC054]  | [IMNFLG4] <int150flg></int150flg>        |

|            |                                  | ch22 | [IBIMC055]  | [IMNFLG4] <int151flg></int151flg>        |

|            |                                  | ch23 | [IBIMC056]  | [IMNFLG4] <int152flg></int152flg>        |

|            |                                  | ch24 | [IBIMC057]  | [IMNFLG4] <int153flg></int153flg>        |

|            |                                  | ch25 | [IBIMC058]  | [IMNFLG4] <int154flg></int154flg>        |

|            |                                  | ch26 | [IBIMC059]  | [IMNFLG4] <int155flg></int155flg>        |

|            |                                  | ch27 | [IBIMC060]  | [IMNFLG4] <int156flg></int156flg>        |

|            |                                  | ch28 | [IBIMC061]  | [IMNFLG4] <int157flg></int157flg>        |

|            |                                  | ch29 | [IBIMC062]  | [IMNFLG4] <int158flg></int158flg>        |

|            |                                  | ch30 | [IBIMC063]  | [IMNFLG4] <int159flg></int159flg>        |

|            |                                  | ch31 | [IBIMC064]  | [IMNFLG5] <int160flg></int160flg>        |

# 4.5. 割り込み検知レベル

INTIF を経由して割り込みを使用するときは、割り込み制御レジスタ A または B で割り込み検知レベル("Low"レベル/"High"レベル/立ち上がりエッジ/立ち下がりエッジ)を選択できます。検出された割り込みは、"High"レベル信号で CPU に出力されます。

各種周辺機能から CPU へ直接割り込み信号が伝わるものは、割り込み要求として"High"パルスを CPU に出力します。

CPU は割り込み信号の"High"を割り込み要因とみなします。

## 4.5.1. 低消費電力モード解除時の注意

STOP1/2 モードからの解除設定には、下記 2つの設定が必要です。

- 割り込み制御レジスタ([IAIMCxx], [IBIMCxxx])の設定

- 割り込み検知レベル

- 割り込み検出許可/禁止

- NVIC割り込みイネーブルセットレジスタの設定

- 許可設定

STOP1 モードから NORMAL モードに復帰する動作は高速クロック発振後、割り込みにジャンプすることで停止している命令が再開されます。また、STOP2 モードから NORMAL モードへ復帰する動作は電源遮断ブロックに対して電源を投入し、リセットシーケンスから再開されます。

# 4.6. 処理手順

# 4.6.1. 処理の流れ

割り込みの処理の流れを以下に示します。 以下の説明で、ハードウエアによる処理とソフトウエアによる処理を示しています。

| 処理                      | 内容                                                                                                                                                  | 説明                                     |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 検出のための準備                | 割り込みを検出するための設定を、NVIC レジスタで行います<br>低消費電力モードの解除要因など割り込み検知レベルの設定が必要となる<br>割り込みは、INTIF の設定も必要です。<br>〇共通<br>NVIC レジスタの設定<br>〇低消費電力モードの解除の設定<br>INTIF の設定 | 4.0.0 % !!!                            |

| 要因発生のための準備              | 割り込みの要因発生のための設定を行います。割り込みの種類により設定内容が異なります。  ○外部割り込み ポートの設定  ○各周辺機能からの割り込み 各周辺機能の設定(使用する周辺機能のリファレンスマニュアルを参照してください。)                                  | 4.6.2 準備                               |

| 割り込み要因の発生               | 割り込みの要因が発生します                                                                                                                                       |                                        |

| INTIFを<br>経由しない<br>割り込み |                                                                                                                                                     |                                        |

| INTIF が割り込みを検出          | INTIF を経由して CPU に接続されています。                                                                                                                          | 4.6.3<br>検出(INTIF)                     |

|                         | CPU が割り込みを検出します                                                                                                                                     |                                        |

| CPU が割り込みを検出            | 複数の割り込み要因が発生する場合、優先順位に従って最も優先度の高い割り<br>込み要因を検出します。                                                                                                  | 4.6.4<br>検出(CPU)                       |

|                         |                                                                                                                                                     |                                        |

| CPU が割り込みを処理            | CPU が割り込み処理を行います                                                                                                                                    | 4.6.5                                  |

|                         | スタックにレジスタの内容を退避し、割り込み処理ルーチンへ分岐します                                                                                                                   | CPU の処理                                |

| 割り込みサービスルーチン実行          | 必要な処理をプログラミングしてください。<br>必要に応じて割り込み要因の取り下げを行ってください。                                                                                                  | 4.6.6<br>割り込み処理ル<br>ーチンでの処理<br>(要因の取り下 |

| 元のプログラムへ復帰              | 割り込み処理ルーチンから通常の処理プログラムに復帰します。                                                                                                                       | (ザ)                                    |

#### 4.6.2. 準備

割り込みの準備を行うときには、設定途中で不要な割り込みの発生を防ぐために設定の順番に注意が必要です。

割り込みの使用開始、または設定変更のときの基本的な順序は、まず、CPUで割り込みを禁止し、次に割り込み経路でCPUから遠いところから設定を行い、最後にCPUで割り込みを許可します。

INTIF の設定を行うときには、条件の設定を行った後、不要な割り込みが発生しないよう INTIF 内部の割り込み情報をクリアしてから割り込み許可の設定を行います。

以下に設定の手順と、手順ごとの具体的な設定方法を示します。

- 1. CPU 割り込み禁止

- 2. CPU 割り込み設定

- 3. 要因の準備(1)(外部割り込み端子)

- 4. 要因の準備(2)(周辺機能からの割り込み)

- 5. 要因の準備(3)(割り込み保留セットレジスタ)

- 6. INTIF の設定

- 7. CPU 割り込み許可

## (1) CPU 割り込み禁止

CPUを割り込み禁止状態にするには、[PRIMASK]レジスタに"1"をセットします。これにより、マスク不能割り込みとハードフォルト例外以外の全ての割り込みと例外がマスクされます。

このレジスタをセットするためには"MSR"命令を使用します。

| 割り込みマスクレジスタ |   |             |

|-------------|---|-------------|

| [PRIMASK]   | ← | "1"(割り込み禁止) |

注 1) [PRIMASK]レジスタは、ユーザ・アクセス・レベルではセットできません。

注 2) [PRIMASK] レジスタに"1" がセットされているとき、フォールトが発生するとハードフォールトとして扱われます。

## (2) CPU 割り込み設定

NVIC レジスタの割り込み優先度 レジスタで<PRI\_n>に優先度の設定を行います。

このレジスタは、8 ビットごとに各割り込み要因に割り当てられていますが、製品ごとに構成するビット数が異なります。8 ビットの構成の場合「0」から「255」までの優先度を設定することができます。最も高い優先度は「0」です。複数の要因を同じ優先度に設定した場合、番号の小さい割り込みの優先度が高くなります。

グループ優先度を設定する場合にはアプリケーション割り込みおよびリセット制御レジスタの <PRIGROUP>も設定します。

| NVIC レジスタ             |          |                           |  |

|-----------------------|----------|---------------------------|--|

| <pri_n></pri_n>       | ←        | 「優先度」                     |  |

| <prigroup></prigroup> | <b>←</b> | 「グループ優先度」(必要に応じて設定してください) |  |

## (3) 要因の準備(1) (外部割り込み端子)

外部割り込み端子を使用する場合、該当する端子のポートの設定を行います。機能端子として使用するため、該当するポートを入力として使用するために「PxIE」<PxmIE> を"1"に設定します。

| ポートレジスタ                |          |     |

|------------------------|----------|-----|

| [PxIE] <pxmie></pxmie> | <b>←</b> | "1" |

注) 「x」は該当ポート番号、「m」は該当ビットのファンクションレジスタ番号を示します。割り 込みの設定を行う際に、未使用の割り込みをイネーブルにしないようご注意ください。また、 「4.3.5 外部割り込み端子を使用する際の注意」の記載事項に注意してください。

#### (4) 要因の準備(2) (周辺機能からの割り込み)

周辺機能からの割り込みを使用する場合、設定方法は周辺機能によって異なります。各周辺機能のリファレンスマニュアルをご覧ください。

## (5) 要因の準備(3) (割り込み保留セットレジスタ)

割り込み保留セットレジスタで割り込みを発生する場合、該当するビットに"1"をセットします。

| NVIC レジスタ           |   |     |

|---------------------|---|-----|

| <setpend></setpend> | ← | "1" |

注) <SETPEND>は該当ビットを示します。

#### (6) INTIF の設定

INTIF を経由する割り込みは、割り込み制御レジスタで割り込み許可の設定を行います。

[IANIC00]/[IBNIC00]/[IAIMCxx]/[IBIMCxxx]レジスタは割り込み要求ごとの設定レジスタです。割り込み許可の前に、割り込み検出ロジックで不要な割り込み発生を防止するため割り込み要求のクリアを行います。

割り込み制御レジスタの詳細は以下を参照してください。

| 割り込み制御レジスタ                                                                                                                                                  |          |                                              |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------|--|--|

| [IAIMCxx] <intmode><br/>[IBIMCxxx]<intmode></intmode></intmode>                                                                                             | <b>←</b> | 使用する割り込み要求に対応する値<br>(割り込み検知レベルのある割り込み<br>のみ) |  |  |

| [IANIC00] <intnclr> [IBNIC00]<intpclr> [IAIMCxx]<intpclr><intnclr> [IBIMCxxx]<intpclr><intnclr></intnclr></intpclr></intnclr></intpclr></intpclr></intnclr> | <b>←</b> | 使用する割り込みの要求クリア                               |  |  |

| [IAIMCxx] <inten><br/>[IBIMCxxx]<inten></inten></inten>                                                                                                     | <b>←</b> | "1"(割り込み検出許可)                                |  |  |

注)「xx」、「xxx」は割り込み要求固有の番号を示します。

#### (7) CPU 割り込み許可

CPU の割り込み許可の設定をします。

割り込み保留クリアレジスタで保留状態の割り込みをクリアし、割り込みイネーブルセットレジスタで割り込みを許可します。これらのレジスタは1ビットずつ各割り込み要因に割り当てられています。

割り込み保留クリアレジスタの該当する割り込みのビットに"1"を書くことで保留されている要因をクリアすることができ、割り込みイネーブルセットレジスタの該当する割り込みのビットに"1"を書くことで割り込みを許可することができます。

ただし、割り込み保留セットレジスタの設定で割り込みを発生する場合、割り込み保留クリアを行う と割り込み要因そのものが失われるため、この操作は不要です。

最後に、[PRIMASK]レジスタを"0"にクリアします。

| NVIC レジスタ           |          |     |

|---------------------|----------|-----|

| <clrpend></clrpend> | ←        | "1" |

| <setena></setena>   | ←        | "1" |

| 割り込みマスクレジスタ         |          |     |

| [PRIMASK]           | <b>←</b> | "0" |

注1) <CLRPEND>、<SETENA>は該当ビットを示します。

注2) [PRIMASK]レジスタは、ユーザ・アクセス・レベルではセットできません。

## 4.6.3. 検出(INTIF)

INTIFで検出した割り込みは、INTIFから"High"レベルで CPU に伝えられます。

INTIFは割り込み検知レベル選択ロジック、割り込み検出ロジック、割り込み禁止/許可の機能があり、割り込み制御レジスタAまたはBで各機能の設定を行います。

INTIF は割り込みを検出すると割り込み制御レジスタで<検出フラグ>がクリアされるまで"High"レベルの割り込み信号をCPUに出力します。解除を行わずに復帰すると再度同じ割り込みが検出されますので、割り込み処理ルーチン内で必ず<検出フラグ>のクリアを行ってください。同時に対応する割り込みの割り込みモニタレジスタもクリアされます。

## 4.6.4. 検出(CPU)

CPU は優先順位に従って最も優先度の高い割り込み要因を検出します。

## 4.6.5. CPU の処理

割り込みが検出されると、CPUはスタックへxPSR、PC、LR、r12、r3~r0を退避し、検出した割り込みの割り込み処理ルーチンへ分岐します。

### 4.6.6. 割り込み処理ルーチンでの処理(要因の取り下げ)

割り込み処理ルーチンではアプリケーションにより必要な内容をプログラミングしますが、ここでは 推奨する処理と要因の取り下げについて説明します。

#### (1) 割り込み処理ルーチンでの処理

通常、割り込み処理ルーチンでは必要なレジスタの退避と割り込み処理を行います。

Cortex-M3 プロセッサは自動的に xPSR、PC、LR、r12、r3~r0 をスタックへ退避するため、これらのレジスタをユーザプログラムで退避する必要はありません。

その他のレジスタについては必要に応じて退避します。

割り込み処理ルーチン実行中でも、より高い優先度の割り込みや NMI などの例外は受け付けられます。そのため書き換わる可能性のある、汎用レジスタを退避することを推奨します。

#### (2) 割り込み要因の取り下げ

割り込みについては、割り込み制御レジスタで割り込み要求を解除する必要があるものがあります。 割り込み検知レベルがレベル検出の割り込みの場合、要因そのものを取り下げない限り割り込み要求 は存在し続けるため、まず要因を取り下げる必要があります。レベル検出の場合は、要因が取り下げら れると INTIF からの割り込み要求信号は自動的に取り下げられます。

エッジ検出の場合は INTIF の割り込み制御レジスタに該当する割り込みの値を設定することで要因は取り下げられ、再度有効なエッジが発生したときに改めて要因として認識されます。

注) 割り込みフラグをクリアした後はクリアしたフラグを必ずリードしてください。

# 5. 例外/割り込み関連レジスタ

## 5.1. レジスタ一覧

制御レジスタとアドレスは以下のとおりです。

#### 割り込み制御レジスタA

| E771= 1 1771 |    |           |            |

|--------------|----|-----------|------------|

| 周辺機能         |    | チャネル/ユニット | ベースアドレス    |

| 割り込み制御 A     | IA | -         | 0x4003E000 |

| レジスタ名                     |           | アドレス (+BASE) |

|---------------------------|-----------|--------------|

| マスク不能割り込み A コントロールレジスタ 00 | [IANIC00] | 0x0000       |

| 割り込み A モードコントロールレジスタ 00   | [IAIMC00] | 0x0020       |

| 割り込み A モードコントロールレジスタ 01   | [IAIMC01] | 0x0021       |

| 割り込み A モードコントロールレジスタ 02   | [IAIMC02] | 0x0022       |

| 割り込み A モードコントロールレジスタ 03   | [IAIMC03] | 0x0023       |

| 割り込み A モードコントロールレジスタ 16   | [IAIMC16] | 0x0030       |

| 割り込み A モードコントロールレジスタ 17   | [IAIMC17] | 0x0031       |

注)[IANIC00]、[IAIMCxx]レジスタアクセスは、バイト単位で行ってください。

### 割り込み制御レジスタB

| 周辺機能     |    | チャネル/ユニット | ベースアドレス    |

|----------|----|-----------|------------|

| 割り込み制御 B | IB | -         | 0x400F4E00 |

| レジスタ名                     |            | アドレス(+BASE) |

|---------------------------|------------|-------------|

| マスク不能割り込み B コントロールレジスタ 00 | [IBNIC00]  | 0x0010      |

| 割り込み B モードコントロールレジスタ 000  | [IBIMC000] | 0x0060      |

| 割り込み B モードコントロールレジスタ 001  | [IBIMC001] | 0x0061      |

| 割り込み B モードコントロールレジスタ 002  | [IBIMC002] | 0x0062      |

| 割り込み B モードコントロールレジスタ 003  | [IBIMC003] | 0x0063      |

| 割り込み B モードコントロールレジスタ 004  | [IBIMC004] | 0x0064      |

| 割り込み B モードコントロールレジスタ 005  | [IBIMC005] | 0x0065      |

| 割り込み B モードコントロールレジスタ 006  | [IBIMC006] | 0x0066      |

| 割り込み B モードコントロールレジスタ 007  | [IBIMC007] | 0x0067      |

| 割り込み B モードコントロールレジスタ 008  | [IBIMC008] | 0x0068      |

| 割り込み B モードコントロールレジスタ 009  | [IBIMC009] | 0x0069      |

| 割り込み B モードコントロールレジスタ 010  | [IBIMC010] | 0x006A      |

| 割り込み B モードコントロールレジスタ 011  | [IBIMC011] | 0x006B      |

| 割り込み B モードコントロールレジスタ 012  | [IBIMC012] | 0x006C      |

| 割り込み B モードコントロールレジスタ 013  | [IBIMC013] | 0x006D      |

| 割り込み B モードコントロールレジスタ 014  | [IBIMC014] | 0x006E      |

| 割り込み B モードコントロールレジスタ 015  | [IBIMC015] | 0x006F      |

| 割り込み B モードコントロールレジスタ 016  | [IBIMC016] | 0x0070      |

| 割り込み B モードコントロールレジスタ 017  | [IBIMC017] | 0x0071      |

| 割り込み B モードコントロールレジスタ 018  | [IBIMC018] | 0x0072      |

| 割り込み B モードコントロールレジスタ 019  | [IBIMC019] | 0x0073      |

| 割り込み B モードコントロールレジスタ 020  | [IBIMC020] | 0x0074      |

| 割り込み B モードコントロールレジスタ 021  | [IBIMC021] | 0x0075      |

| 割り込み B モードコントロールレジスタ 022  | [IBIMC022] | 0x0076      |

| 割り込み B モードコントロールレジスタ 023  | [IBIMC023] | 0x0077      |

| 割り込み B モードコントロールレジスタ 024  | [IBIMC024] | 0x0078      |

| 割り込み B モードコントロールレジスタ 025  | [IBIMC025] | 0x0079      |

| 割り込み B モードコントロールレジスタ 026  | [IBIMC026] | 0x007A      |

| 割り込み B モードコントロールレジスタ 027  | [IBIMC027] | 0x007B      |

| 割り込み B モードコントロールレジスタ 028  | [IBIMC028] | 0x007C      |

| 割り込み B モードコントロールレジスタ 029  | [IBIMC029] | 0x007D      |

| 割り込み B モードコントロールレジスタ 030  | [IBIMC030] | 0x007E      |

| 割り込み B モードコントロールレジスタ 031  | [IBIMC031] | 0x007F      |

| 割り込み B モードコントロールレジスタ 032  | [IBIMC032] | 0x0080      |

| 割り込み B モードコントロールレジスタ 033  | [IBIMC033] | 0x0081      |

| 割り込み B モードコントロールレジスタ 034  | [IBIMC034] | 0x0082      |

| レジスタ名                    |            | アドレス(+BASE) |

|--------------------------|------------|-------------|

| 割り込み B モードコントロールレジスタ 035 | [IBIMC035] | 0x0083      |

| 割り込み B モードコントロールレジスタ 036 | [IBIMC036] | 0x0084      |

| 割り込み B モードコントロールレジスタ 037 | [IBIMC037] | 0x0085      |

| 割り込み B モードコントロールレジスタ 038 | [IBIMC038] | 0x0086      |

| 割り込み B モードコントロールレジスタ 039 | [IBIMC039] | 0x0087      |

| 割り込み B モードコントロールレジスタ 040 | [IBIMC040] | 0x0088      |

| 割り込み B モードコントロールレジスタ 041 | [IBIMC041] | 0x0089      |

| 割り込み B モードコントロールレジスタ 042 | [IBIMC042] | 0x008A      |

| 割り込み B モードコントロールレジスタ 043 | [IBIMC043] | 0x008B      |

| 割り込み B モードコントロールレジスタ 044 | [IBIMC044] | 0x008C      |

| 割り込み B モードコントロールレジスタ 045 | [IBIMC045] | 0x008D      |

| 割り込み B モードコントロールレジスタ 046 | [IBIMC046] | 0x008E      |

| 割り込み B モードコントロールレジスタ 047 | [IBIMC047] | 0x008F      |

| 割り込み B モードコントロールレジスタ 048 | [IBIMC048] | 0x0090      |

| 割り込み B モードコントロールレジスタ 049 | [IBIMC049] | 0x0091      |

| 割り込み B モードコントロールレジスタ 050 | [IBIMC050] | 0x0092      |

| 割り込み B モードコントロールレジスタ 051 | [IBIMC051] | 0x0093      |

| 割り込み B モードコントロールレジスタ 052 | [IBIMC052] | 0x0094      |

| 割り込み B モードコントロールレジスタ 053 | [IBIMC053] | 0x0095      |

| 割り込み B モードコントロールレジスタ 054 | [IBIMC054] | 0x0096      |

| 割り込み B モードコントロールレジスタ 055 | [IBIMC055] | 0x0097      |

| 割り込み B モードコントロールレジスタ 056 | [IBIMC056] | 0x0098      |

| 割り込み B モードコントロールレジスタ 057 | [IBIMC057] | 0x0099      |

| 割り込み B モードコントロールレジスタ 058 | [IBIMC058] | 0x009A      |

| 割り込み B モードコントロールレジスタ 059 | [IBIMC059] | 0x009B      |

| 割り込み B モードコントロールレジスタ 060 | [IBIMC060] | 0x009C      |

| 割り込み B モードコントロールレジスタ 061 | [IBIMC061] | 0x009D      |

| 割り込み B モードコントロールレジスタ 062 | [IBIMC062] | 0x009E      |

| 割り込み B モードコントロールレジスタ 063 | [IBIMC063] | 0x009F      |

| 割り込み B モードコントロールレジスタ 064 | [IBIMC064] | 0x00A0      |

| 割り込み B モードコントロールレジスタ 065 | [IBIMC065] | 0x00A1      |

| 割り込み B モードコントロールレジスタ 066 | [IBIMC066] | 0x00A2      |

| 割り込み B モードコントロールレジスタ 067 | [IBIMC067] | 0x00A3      |

| 割り込み B モードコントロールレジスタ 068 | [IBIMC068] | 0x00A4      |

| 割り込み B モードコントロールレジスタ 069 | [IBIMC069] | 0x00A5      |

| 割り込み B モードコントロールレジスタ 070 | [IBIMC070] | 0x00A6      |

| 割り込み B モードコントロールレジスタ 071 | [IBIMC071] | 0x00A7      |

| 割り込み B モードコントロールレジスタ 072 | [IBIMC072] | 0x00A8      |

| レジスタ名                    |            | アドレス(+BASE) |

|--------------------------|------------|-------------|

| 割り込み B モードコントロールレジスタ 073 | [IBIMC073] | 0x00A9      |

| 割り込み B モードコントロールレジスタ 074 | [IBIMC074] | 0x00AA      |

| 割り込み B モードコントロールレジスタ 075 | [IBIMC075] | 0x00AB      |

| 割り込み B モードコントロールレジスタ 076 | [IBIMC076] | 0x00AC      |

| 割り込み B モードコントロールレジスタ 077 | [IBIMC077] | 0x00AD      |

| 割り込み B モードコントロールレジスタ 078 | [IBIMC078] | 0x00AE      |

| 割り込み B モードコントロールレジスタ 079 | [IBIMC079] | 0x00AF      |

| 割り込み B モードコントロールレジスタ 080 | [IBIMC080] | 0x00B0      |

| 割り込み B モードコントロールレジスタ 081 | [IBIMC081] | 0x00B1      |

| 割り込み B モードコントロールレジスタ 082 | [IBIMC082] | 0x00B2      |

| 割り込み B モードコントロールレジスタ 083 | [IBIMC083] | 0x00B3      |

| 割り込み B モードコントロールレジスタ 084 | [IBIMC084] | 0x00B4      |

| 割り込み B モードコントロールレジスタ 085 | [IBIMC085] | 0x00B5      |

| 割り込み B モードコントロールレジスタ 086 | [IBIMC086] | 0x00B6      |

| 割り込み B モードコントロールレジスタ 087 | [IBIMC087] | 0x00B7      |

| 割り込み B モードコントロールレジスタ 088 | [IBIMC088] | 0x00B8      |

| 割り込み B モードコントロールレジスタ 089 | [IBIMC089] | 0x00B9      |

| 割り込み B モードコントロールレジスタ 090 | [IBIMC090] | 0x00BA      |

| 割り込み B モードコントロールレジスタ 091 | [IBIMC091] | 0x00BB      |

| 割り込み B モードコントロールレジスタ 092 | [IBIMC092] | 0x00BC      |

| 割り込み B モードコントロールレジスタ 093 | [IBIMC093] | 0x00BD      |

| 割り込み B モードコントロールレジスタ 094 | [IBIMC094] | 0x00BE      |

### リセットフラグレジスタ

| 周辺機能           |     | チャネル/ユニット | ベースアドレス    |

|----------------|-----|-----------|------------|

| 低速発振/電源制御/リセット | RLM | -         | 0x4003E400 |

| レジスタ名         |              | アドレス(+BASE) |

|---------------|--------------|-------------|

| リセットフラグレジスタ 0 | [RLMRSTFLG0] | 0x0002      |

| リセットフラグレジスタ 1 | [RLMRSTFLG1] | 0x0003      |

注) リセットフラグレジスタのアクセスは、バイト単位で行ってください。

### 割り込みモニタレジスタ

| 周辺機能    |     | チャネル/ユニット | ベースアドレス    |

|---------|-----|-----------|------------|

| 割り込みモニタ | IMN | -         | 0x400F4F00 |

| レジスタ名               |             | アドレス(+BASE)) |

|---------------------|-------------|--------------|

| マスク不能割り込みモニタフラグレジスタ | [IMNFLGNMI] | 0x0000       |

| 割り込みモニタフラグレジスタ 1    | [IMNFLG1]   | 0x0004       |

| 割り込みモニタフラグレジスタ3     | [IMNFLG3]   | 0x000C       |

| 割り込みモニタフラグレジスタ 4    | [IMNFLG4]   | 0x0010       |

| 割り込みモニタフラグレジスタ 5    | [IMNFLG5]   | 0x0014       |

## NVIC レジスタ

| 周辺機能      | チャネル/ユニット | ベースアドレス    |

|-----------|-----------|------------|

| NVIC レジスタ | -         | 0xE000E000 |

| レジスタ名                     | アドレス(Base +)           |

|---------------------------|------------------------|

| SysTick 制御およびステータスレジスタ    | 0x0010                 |

| SysTick リロード値レジスタ         | 0x0014                 |

| SysTick 現在値レジスタ           | 0x0018                 |

| SysTick 較正値レジスタ           | 0x001C                 |

| 割り込みイネーブルセットレジスタ 0        | 0x0100                 |

| 割り込みイネーブルセットレジスタ 1        | 0x0104                 |

| 割り込みイネーブルセットレジスタ2         | 0x0108                 |

| 割り込みイネーブルセットレジスタ3         | 0x010C                 |

| 割り込みイネーブルセットレジスタ4         | 0x0110                 |

| 割り込みイネーブルセットレジスタ5         | 0x0114                 |

| 割り込みイネーブルクリアレジスタ 0        | 0x0180                 |

| 割り込みイネーブルクリアレジスタ 1        | 0x0184                 |

| 割り込みイネーブルクリアレジスタ 2        | 0x0188                 |

| 割り込みイネーブルクリアレジスタ3         | 0x018C                 |

| 割り込みイネーブルクリアレジスタ 4        | 0x0190                 |

| 割り込みイネーブルクリアレジスタ 5        | 0x0194                 |

| 割り込み保留セットレジスタ0            | 0x0200                 |

| 割り込み保留セットレジスタ1            | 0x0204                 |

| 割り込み保留セットレジスタ2            | 0x0208                 |

| 割り込み保留セットレジスタ3            | 0x020C                 |

| 割り込み保留セットレジスタ4            | 0x0210                 |

| 割り込み保留セットレジスタ5            | 0x0214                 |

| 割り込み保留クリアレジスタ0            | 0x0280                 |

| 割り込み保留クリアレジスタ1            | 0x0284                 |

| 割り込み保留クリアレジスタ2            | 0x0288                 |

| 割り込み保留クリアレジスタ3            | 0x028C                 |

| 割り込み保留クリアレジスタ4            | 0x0290                 |

| 割り込み保留クリアレジスタ5            | 0x0294                 |

| 割り込み優先度レジスタ               | 0x0400~0x04A5          |

| ベクタテーブルオフセットレジスタ          | 0x0D08                 |

| アプリケーション割り込みおよびリセット制御レジスタ | 0x0D0C                 |

| システムハンドラ優先度レジスタ           | 0x0D18, 0x0D1C, 0x0D20 |

| システムハンドラ制御および状態レジスタ       | 0x0D24                 |

# 5.2. 割り込み制御レジスタ A

## 5.2.1. [IANIC00] (マスク不能割り込み A コントロールレジスタ 00)

| Bit | Bit Symbol | リセット後 | Туре | 機能                                                 |

|-----|------------|-------|------|----------------------------------------------------|

| 7   | INTNCLR    | 0     | W    | 検出フラグクリア制御<br>0:-<br>1: クリア<br>リードすると"0" が読み出されます。 |

| 6   | -          | 0     | R    | リードすると"0"が読めます。                                    |

| 5   | INTNFLG    | 0     | R    | エッジ検出フラグ<br>0: 未検出<br>1: 検出                        |

| 4:0 | -          | 00101 | R    | リードすると"00101"が読めます。                                |

## 5.2.2. [IAIMC00~03,16,17] (割り込み A モードコントロールレジスタ nn)

### (1) [IAIMC00~03]レジスタ

| Bit | Bit Symbol   | リセット後 | Туре | 機能                                                                                                                     |

|-----|--------------|-------|------|------------------------------------------------------------------------------------------------------------------------|

| 7   | INTNCLR      | 0     | W    | 立ち下がりエッジ検出フラグクリア制御<br>0:-<br>1: クリア<br>リードすると"0" が読み出されます。                                                             |

| 6   | INTPCLR      | 0     | W    | 立ち上がりエッジ検出フラグクリア制御<br>0:-<br>1: クリア<br>リードすると"0" が読み出されます。                                                             |