# 32 ビット RISC マイクロコントローラー

# TMPM3H グループ(2)

リファレンスマニュアル 製品個別情報 (PINFO-M3H(2))

**Revision 3.3**

2021-01

東芝デバイス&ストレージ株式会社

# 目次

| 序章                                           | 9  |

|----------------------------------------------|----|

| 関連するドキュメント                                   | 9  |

| 表記規約                                         | 10 |

| 用語・略語                                        | 12 |

| 1. 概要                                        | 13 |

|                                              |    |

| 2.1. レジスターベースアドレス                            | 13 |

| 2.2. トリガーセレクター(TRGSEL)                       |    |

| 2.2.1. トリガーセレクターと製品対応                        |    |

| 2.2.2. 使用方法と設定                               |    |

| 2.2.3. レジスター一覧                               |    |

| 2.2.4. レジスター詳細                               |    |

| 2.2.4.1. <i>[TSEL0CR0]</i> (コントロールレジスター0)    | 25 |

| 2.2.4.2. <i>[TSEL0CR1]</i> (コントロールレジスター1)    |    |

| 2.2.4.3. <i>[TSEL0CR2]</i> (コントロールレジスター2)    | 29 |

| 2.2.4.4. [TSEL0CR3] (コントロールレジスター3)           | 31 |

| 2.2.4.5. <i>[TSEL0CR4]</i> (コントロールレジスター4)    | 33 |

| 2.2.4.6. <i>[TSEL0CR5]</i> (コントロールレジスター5)    | 35 |

| 2.2.4.7. [TSEL0CR6] (コントロールレジスター6)           | 37 |

| 2.2.4.8. <i>[TSEL0CR7]</i> (コントロールレジスター7)    | 39 |

| 2.2.4.9. <i>[TSEL0CR8]</i> (コントロールレジスター8)    | 41 |

| 2.2.4.10. <i>[TSEL0CR9]</i> (コントロールレジスター9)   | 43 |

| 2.2.4.11. <i>[TSEL0CR10]</i> (コントロールレジスター10) |    |

| 2.2.4.12. <i>[TSEL0CR11]</i> (コントロールレジスター11) |    |

| 2.2.4.13. <i>[TSEL0CR12]</i> (コントロールレジスター12) |    |

| 2.2.4.14. <i>[TSEL0CR13]</i> (コントロールレジスター13) |    |

| 2.2.4.15. <i>[TSEL0CR14]</i> (コントロールレジスター14) |    |

| 2.2.4.16. <i>[TSEL0CR15]</i> (コントロールレジスター15) |    |

| 2.2.4.17. [TSEL1CR0] (コントロールレジスター0)          |    |

| 2.2.4.18. [TSEL1CR1] (コントロールレジスター1)          |    |

| 2.2.4.19. [TSEL1CR2] (コントロールレジスター2)          |    |

| 2.3. クロック選択式ウオッチドッグタイマー(SIWDT)               |    |

| 2.3.1. 搭載チャネル                                |    |

| 2.3.2. カウントクロック                              |    |

| 2.3.3. 制御出力                                  |    |

| 2.4. 周波数検知回路(OFD)                            |    |

| 2.4.1. 搭載一覧                                  |    |

| 2.4.2. 基準クロック                                |    |

| 2.4.3. 検知対象クロック                              | 63 |

| 2.5. デバッグインターフェース                 | 64 |

|-----------------------------------|----|

| 2.5.1. 製品別デバッグインターフェース一覧          | 64 |

| 2.6. フラッシュメモリー                    | 65 |

| 2.6.1. 書き込み,消去操作用クロック             | 65 |

| 2.6.2. 製品別コードフラッシュブロック構成          | 65 |

| 2.6.3. 製品別データフラッシュブロック構成          | 66 |

| 2.6.4. シングルブート使用リソース              | 67 |

| 2.7. DMA コントローラー(DMAC)            | 68 |

| 2.7.1. 搭載ユニット                     | 68 |

| 2.7.2. DMA 要求一覧                   | 68 |

| 2.8. アドバンストプログラマブルモーター制御回路(A-PMD) | 76 |

| 2.8.1. 搭載チャネル                     | 76 |

| 2.8.2. 機能端子とポート                   | 76 |

| 2.8.3. DMA 要求                     | 76 |

| 2.8.4. その他接続                      | 77 |

| 2.8.5. PMD0DBG 使用時の追加設定           | 77 |

| 2.9. アドバンストエンコーダー入力回路(A-ENC)      | 78 |

| 2.9.1. 搭載チャネル                     | 78 |

| 2.9.2. 機能端子とポート                   | 78 |

| 2.9.3. 内部信号接続仕様                   | 78 |

| 2.9.3.1. T32A/A-PMD 接続            | 78 |

| 2.10. 12 ビットアナログデジタルコンバーター(ADC)   | 80 |

| 2.10.1. 搭載ユニット                    | 80 |

| 2.10.2. 機能端子とポート                  | 80 |

| 2.10.3. ADC 用変換クロック               | 81 |

| 2.10.4. モード設定レジスター2 の設定値          | 81 |

| 2.10.5. DMA 要求                    | 81 |

| 2.10.6. 内部信号接続仕様                  | 82 |

| 2.10.6.1. 起動トリガー接続仕様              |    |

| 2.10.6.2. T32A/A-PMD 接続           |    |

| 2.11. 8 ビットデジタルアナログコンバーター(DAC)    | 84 |

| 2.11.1. 搭載チャネル                    |    |

| 2.11.2. 機能端子とポート                  | 84 |

| 2.12. コンパレーター(COMP)               | 85 |

| 2.12.1. 搭載一覧                      | 85 |

| 2.13. 電圧検知回路(LVD)                 | 85 |

| 2.13.1. 搭載一覧                      | 85 |

| 2.13.2. 検知対象電源                    | 86 |

| 2.14. 32 ビットタイマーイベントカウンター(T32A)   | 86 |

| 2.14.1. 搭載チャネル                    | 86 |

| 2.14.2. 機能端子とポート                                  | 87  |

|---------------------------------------------------|-----|

| 2.14.3. プリスケーラー用クロック                              | 89  |

| 2.14.4. 内部信号接続仕様                                  | 89  |

| 2.14.4.1. キャプチャートリガー信号接続仕様                        | 90  |

| 2.14.4.2. 同期制御接続仕様                                | 94  |

| 2.14.5. 製品別パルスカウント対応一覧                            | 95  |

| 2.14.6. DMA 要求                                    | 96  |

| 2.14.7. 非対応割り込み                                   | 98  |

| 2.15. リアルタイムクロック(RTC)                             | 99  |

| 2.15.1. 搭載チャネル                                    | 99  |

| 2.15.2. 機能端子とポート                                  | 99  |

| 2.15.3. 時計カウントクロック                                | 99  |

| 2.16. 非同期シリアル通信回路(UART)                           | 100 |

| 2.16.1. 搭載チャネル                                    | 100 |

| 2.16.2. 機能端子とポート                                  | 100 |

| 2.16.3. 製品別ハーフクロックモード対応一覧                         | 102 |

| 2.16.4. プリスケーラー用クロック                              | 102 |

| 2.16.5. DMA 要求                                    | 102 |

| 2.16.6. 内部信号接続仕様                                  | 103 |

| 2.16.6.1. トリガー転送信号接続仕様                            | 103 |

| 2.16.6.2. T32A 接続                                 | 104 |

| 2.17. I <sup>2</sup> C インターフェース(I <sup>2</sup> C) | 105 |

| 2.17.1. 搭載チャネル                                    | 105 |

| 2.17.2. 機能端子とポート                                  | 105 |

| 2.17.3. プリスケーラー用クロック                              | 105 |

| 2.17.4. アドレス一致ウエイクアップ機能対応                         | 106 |

| 2.17.5. フィルター                                     | 106 |

| 2.17.6. DMA 要求                                    | 107 |

| 2.18. シリアルペリフェラルインターフェース(TSPI)                    | 108 |

| 2.18.1. 搭載チャネル                                    | 108 |

| 2.18.2. 機能端子とポート                                  | 109 |

| 2.18.3. 製品別転送モード対応一覧                              | 110 |

| 2.18.4. クロック                                      | 110 |

| 2.18.5. DMA 要求                                    | 111 |

| 2.18.6. 内部信号接続仕様                                  | 112 |

| 2.18.6.1. トリガー送信信号接続仕様                            | 112 |

| 2.18.6.2. T32A 接続                                 | 113 |

| 2.19. リモコン受信回路(RMC)                               | 114 |

| 2.19.1. 搭載チャネル                                    | 114 |

| 2.19.2. 機能端子とポート                                  | 114 |

| 2.19.3. サンプリングクロック                                | 114 |

|    | 2.20. デジタルノイズフィルター回路(DNF)  | 115   |

|----|----------------------------|-------|

|    | 2.20.1. 搭載ユニット             |       |

|    | 2.20.2. 製品別外部割り込みと DNF の対応 | 116   |

|    | 2.20.3. サンプリングソースクロック      | 117   |

| :  | 2.21. CRC 計算回路(CRC)        | 117   |

|    | 2.21.1. 搭載一覧               | 117   |

| :  | 2.22. RAM パリティー(RAMP)      | 117   |

|    | 2.22.1. 搭載一覧               | 117   |

|    | 2.22.2. エラー判定ブロックエリア       |       |

| :  | 2.23. トリミング回路(TRM)         |       |

|    | 2.23.1. 搭載一覧               | 118   |

|    | 2.23.2. 対象発振器              | 118   |

| 3. | 改訂履歴                       | . 119 |

| 刬  | 品取り扱い上のお願い                 | 122   |

# 図目次

| 図 2.1            | トリカーセレクター接続例                                       | 14        |

|------------------|----------------------------------------------------|-----------|

|                  |                                                    |           |

|                  |                                                    |           |

|                  |                                                    |           |

|                  | 表目次                                                |           |

| 表 2.1            | レジスターベースアドレスタイプ                                    |           |

|                  | 製品別トリガーセレクター対応一覧 (1/12)                            |           |

| 表 2.3            |                                                    |           |

| 表 2.4            |                                                    |           |

| 表 2.5            | 製品別トリガーセレクター対応一覧 (4/12)                            |           |

| 表 2.6<br>表 2.7   | 製品別トリガーセレクター対応一覧 (5/12)<br>製品別トリガーセレクター対応一覧 (6/12) |           |

| 表 2.7            | 製品別トリガーセレクター対応一覧 (7/12)                            |           |

| 表 2.0            | ,                                                  |           |

| 表 2.10           |                                                    |           |

| 表 2.11           | 製品別トリガーセレクター対応一覧 (10/12)                           |           |

| 表 2.12           |                                                    |           |

| 表 2.13           |                                                    |           |

| 表 2.14           | SIWDT 搭載チャネル                                       | 62        |

| 表 2.15           |                                                    |           |

| 表 2.16           |                                                    |           |

| 表 2.17           |                                                    |           |

| 表 2.18           |                                                    |           |

| 表 2.19           | - 10.000                                           |           |

| 表 2.20<br>表 2.21 | デバッグインターフェース搭載一覧<br>書き込み,消去操作用クロック                 |           |

| 表 2.21           |                                                    |           |

| 表 2.22           |                                                    |           |

| 表 2.24           |                                                    |           |

| 表 2.25           |                                                    |           |

| 表 2.26           |                                                    |           |

| 表 2.27           | DMA unitA 要求一覧(1/4)                                | 68        |

| 表 2.28           |                                                    | 69        |

| 表 2.29           |                                                    |           |

| 表 2.30           |                                                    |           |

| 表 2.31           |                                                    |           |

| 表 2.32           |                                                    |           |

| 表 2.33           |                                                    |           |

| 表 2.34           | /                                                  |           |

| 表 2.35           | ****                                               |           |

| 表 2.36<br>表 2.37 |                                                    |           |

| 表 2.37           |                                                    |           |

|                  | A-PMD 内部接続仕様:出力                                    |           |

| 表 2.40           |                                                    | , ,<br>77 |

| 表 2.41           |                                                    |           |

|                  | A-ENC 機能端子                                         |           |

|                  | A-ENC 内部信号接続仕様:入力                                  |           |

| 表 2.46 | ADC 機能端子とポート                                      | 90  |

|--------|---------------------------------------------------|-----|

| 表 2.40 | ADC 開変換クロック                                       |     |

| -      | ADC                                               |     |

| 表 2.48 |                                                   |     |

| 表 2.49 | ADC DMA 要求                                        |     |

| 表 2.50 | ADC 起動トリガー接続仕様                                    |     |

| 表 2.51 | ADC 内部接続仕様:出力                                     |     |

| 表 2.52 | DAC 搭載チャネル                                        |     |

| 表 2.53 | DAC 機能端子とポート                                      |     |

| 表 2.54 | コンパレーター 搭載チャネル                                    |     |

| 表 2.55 | コンパレーターの入力と出力                                     |     |

| 表 2.56 | LVD 搭載一覧                                          | 85  |

| 表 2.57 | LVD 検知対象電源                                        | 86  |

| 表 2.58 | T32A 搭載チャネル                                       | 86  |

| 表 2.59 | T32A 機能端子とポート(1/3)                                | 87  |

| 表 2.60 | T32A 機能信号とポート(2/3)                                | 88  |

| 表 2.61 | T32A 機能信号とポート(3/3)                                |     |

| 表 2.62 | T32A プリスケーラー用クロック                                 |     |

| 表 2.63 | T32A キャプチャートリガー信号接続仕様(1/4)                        |     |

| 表 2.64 | T32A キャプチャートリガー信号接続仕様(2/4)                        |     |

| 表 2.65 | T32A キャプチャートリガー信号接続仕様(3/4)                        |     |

| 表 2.66 | T32A キャプチャートリガー信号接続仕様(4/4)                        |     |

| 表 2.67 | T32A 同期制御接続仕様(1/2)                                |     |

| 表 2.68 | T32A 同期制御接続仕様(2/2)                                |     |

| 表 2.69 | T32A 同期前脚接続は様(2/2)                                |     |

|        |                                                   |     |

| 表 2.70 | T32A DMA 要求(1/3)                                  |     |

| 表 2.71 | T32A DMA 要求(2/3)                                  |     |

| 表 2.72 | T32A DMA 要求(3/3)                                  |     |

| 表 2.73 | RTC 搭載一覧                                          |     |

| 表 2.74 | RTC 機能端子とポート                                      |     |

| 表 2.75 | RTC 時計カウントクロック                                    |     |

| 表 2.76 | UART 搭載チャネル                                       |     |

| 表 2.77 | UART 端子信号とポート                                     | 101 |

| 表 2.78 | UART ハーフクロックモード対応一覧                               | 102 |

| 表 2.79 | UART プリスケーラー用クロック                                 | 102 |

| 表 2.80 | UART DMA 要求                                       |     |

| 表 2.81 | UART トリガー転送信号接続仕様                                 | 103 |

| 表 2.82 | UART 内部接続仕様:出力                                    |     |

| 表 2.83 | I <sup>2</sup> C インターフェース 搭載チャネル                  | 105 |

| 表 2.84 | I <sup>2</sup> C インターフェース 機能端子とポート                |     |

| 表 2.85 | I <sup>2</sup> C インターフェース プリスケーラー用クロック            | 105 |

| 表 2.86 | I <sup>2</sup> C インターフェース アドレス一致ウエイクアップ機能(I2CS)対応 | 106 |

| 表 2.87 | I <sup>2</sup> C インターフェース フィルター                   |     |

| 表 2.88 | I <sup>2</sup> C インターフェース DMA 要求                  |     |

| 表 2.89 | TSPI 搭載チャネル                                       |     |

| 表 2.90 | TSPI 機能端子とポート                                     |     |

| 表 2.91 | TSPI モード対応一覧                                      |     |

| 表 2.92 | TSPI 用クロック                                        |     |

| 表 2.93 | TSPI DMA 要求                                       |     |

| 表 2.93 | TSPI トリガー転送仕様                                     |     |

| 表 2.94 | TSPI トリカー転送仕様TSPI 内部接続仕様(出力)                      |     |

|        | TSPT 内部接続任様(四刀)<br>RMC 搭載チャネル                     |     |

| 表 2.96 |                                                   |     |

| 表 2.97 | RMC 機能端子とポート                                      | 114 |

#### TMPM3H グループ(2) 製品個別情報

| 表 2.98 RMC サンプリングクロック      | 114 |

|----------------------------|-----|

| 表 2.99 DNF 搭載ユニット          |     |

| 表 2.100 外部割り込みと DNF 対応     |     |

| 表 2.101 DNF サンプリングソースクロック  |     |

| 表 2.102 CRC 搭載チャネル         |     |

| 表 2.103 RAMP 搭載チャネル        | 117 |

| 表 2.104 RAMPの RAM エリアとアドレス | 118 |

| 表 2.105 TRM 搭載一覧           | 118 |

| 表 2.106 TRM トリミング対象発振器     | 118 |

| 表 3.1 改訂履歴                 | 119 |

# 序章

### 関連するドキュメント

| 文書名                           | IP 記号         |

|-------------------------------|---------------|

| 入出力ポート (TMPM3H グループ(2))       | PORT-MH3(2)   |

| クロック制御と動作モード (TMPM3H グループ(2)) | CG-M3H(2)-D   |

| 例外 (TMPM3H グループ(2))           | EXCEPT-M3H(2) |

| 電源とリセット動作 (TMPM3H グループ(2))    | RESET-M3H(2)  |

| DMA コントローラー                   | DMAC-B        |

| 32 ビットタイマーイベントカウンター           | T32A-B        |

| 非同期シリアル通信回路                   | UART-C        |

| シリアルペリフェラルインターフェース            | TSPI-B        |

| I <sup>2</sup> C インターフェース     | I2C-B         |

| 12 ビットアナログデジタルコンバーター          | ADC-A         |

| 8 ビットデジタルアナログコンバーター           | DAC-A         |

| アドバンストプログラマブルモーター制御回路         | A-PMD-B       |

| アドバンストエンコーダー入力回路              | A-ENC-A       |

| クロック選択式ウオッチドッグタイマー            | SIWDT-A       |

| リモコン受信回路                      | RMC-A         |

| リアルタイムクロック                    | RTC-A         |

| 周波数検知回路                       | OFD-A         |

| デバッグインターフェース                  | DEBUG-A       |

| デジタルノイズフィルター回路                | DNF-A         |

| トリミング回路                       | TRM-A         |

| 電圧検知回路                        | LVD-A         |

| フラッシュメモリー                     | FLASH512_32-A |

| CRC 計算回路                      | CRC-A         |

| RAM パリティー                     | RAMP-A        |

| コンパレーター                       | COMP-B        |

#### 表記規約

数値表記は以下の規則に従います。

16 進数表記: 0xABC

10 進数表記: 123 または 0d123 (10 進表記であることを示す必要のある場合だけ使用)

2 進数表記: 0b111 (ビット数が本文中に明記されている場合は「0b」を省略可)

● ローアクティブの信号は信号名の末尾に「 N」で表記します。

● 信号がアクティブレベルに移ることを「アサート (assert)」アクティブでないレベルに移ることを 「デアサート (deassert)」と呼びます。

複数の信号名は [m:n]とまとめて表記する場合があります。例: S[3:0] は S3,S2,S1,S0 の 4 つの信号名をまとめて表記しています。

• 本文中 // で囲まれたものはレジスターを定義しています。

例: [ABCD]

● 同種で複数のレジスター、フィールド、ビット名は「n」で一括表記する場合があります。

例: [XYZ1], [XYZ2], [XYZ3] → [XYZn]

「レジスター一覧」中のレジスター名でユニットまたはチャネルは「x」で一括表記しています。ユニットの場合、「x」は A,B,C...を表します。

例: [ADACR0], [ADBCR0], [ADCCR0]→[ADxCR0]

チャネルの場合、「x」は0,1,2,..を表します。

例: [T32A0RUNA], [T32A1RUNA], [T32A2RUNA]→[T32AxRUNA]

レジスターのビット範囲は [m:n] と表記します。例: [3:0] はビット3から0の範囲を表します。

レジスターの設定値は16進数または2進数のどちらかで表記されています。

例: [ABCD]<EFG> = 0x01 (16 進数)、 [XYZn]<VW> = 1 (2 進数)

ワード、バイトは以下のビット長を表します。

バイト: 8 ビット ハーフワード: 16 ビット ワード: 32 ビット

ダブルワード: 64 ビット

レジスター内の各ビットの属性は以下の表記を使用しています。

R: リードオンリー W: ライトオンリー R/W: リード / ライト

- 断りのない限り、レジスターアクセスはワードアクセスだけをサポートします。

- 本文中の予約領域「Reserved」として定義されたレジスターは書き換えを行わないでください。 また、読み出した値を使用しないでください。

- Default 値が「一」となっているビットから読み出した値は不定です。

- 書き込み可能なビットフィールドと、リードオンリー「R」のビットフィールドが共存するレジスターに書き込みを行う場合、リードオンリー「R」のビットフィールドには Default 値を書き込んでください。

Default 値が「一」となっている場合は、個々のレジスターの定義に従ってください。

- ライトオンリーのレジスターの Reserved ビットフィールドには Default 値を書き込んでください。 Default 値が「─」となっている場合は、個々のレジスターの定義に従ってください。

- 書き込みと読み出しで異なる定義のレジスターへのリードモディファイライト処理は行わないでく ださい。

Arm,Cortex および Thumb は Arm Limited(またはその子会社)の US またはその他の国における登録商標です。 All rights reserved.

FLASH メモリについては、米国 SST 社 (Silicon Storage Technology, Inc.) からライセンスを受けた Super Flash®技術を使用しています。Super Flash®は SST 社の登録商標です。

本資料に記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している 場合があります。

#### 用語・略語

この仕様書で使用されている用語・略語の一部を記載します。

ADC Analog to Digital Converter

A-ENC Advanced Encoder input Circuit

A-PMD Advanced Programmable Motor Control Circuit

COMP Comparator

CRC Cyclic Redundancy Check

DAC Digital to Analog Converter

DMAC Direct Memory Acess Controler

DNF Digital Noise Filter

EHOSC External High speed Oscillator

ELOSC External Low speed Oscillator

IHOSC Internal High speed Oscillator

INT Interrupt

I<sup>2</sup>C Inter-Integrated Circuit

I2CS I<sup>2</sup>C wake-up circuit from Stand-by mode

LVD Voltage Detection Circuit

OFD Oscillation Frequency Detector

RAMP RAM Parity

RMC Remote control signal preprocessor

RTC Real Time Clock

SIWDT Clock Selective Watchdog Timer

TRGSEL Trigger Selection circuit

TRM Trimming circuit

TSPI Serial Peripheral Interface

T32A 32-bit Timer Event Counter

UART Universal Asynchronous Receiver Transmitter

# 1. 概要

この章では、周辺機能に関し、チャネルまたはユニット数、端子情報、その他の製品固有機能の情報 について纏めています。各周辺機能のリファレンスマニュアルと合わせてご使用ください。

# 2. 各周辺機能の情報

### 2.1. レジスターベースアドレス

下記に各周辺機能で使用するレジスターのベースアドレスタイプを示します。

表 2.1 レジスターベースアドレスタイプ

| 製品             | レジスターベースアドレスタイプ |

|----------------|-----------------|

| TMPM3H グループ(2) | TYPE1           |

上記ベースアドレスタイプを参照して各周辺機能の開発を行ってください。

リファレンスマニュアルのレジスターベースアドレスに TYPE1/TYPE2/TYPE3 の記載がない場合は TYPE1 としてご使用ください。

### 2.2. トリガーセレクター(TRGSEL)

トリガーセレクターは、周辺機能、ポートなどから入力された複数のトリガーから、1つのトリガーを選択し周辺機能にトリガー信号を出力する回路です。

8本のトリガーから *[TSELxCRn]* < INSELm > で選択されたトリガーを、接続先の周辺機能に出力します。

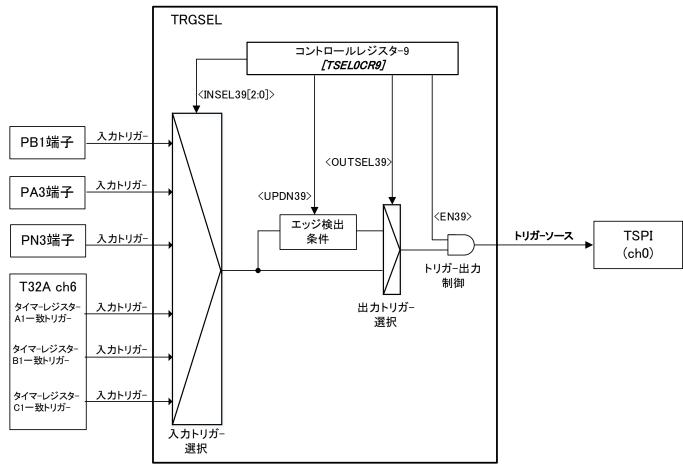

図 2.1 トリガーセレクター接続例は、ポート端子(PB1,PA3,PN3)及び 32 ビットタイマー/イベントカウンター(ch6)から出力されるタイマーレジスター一致トリガー(A1,B1,C1)が、トリガーセレクター経由で TSPI(ch0)に接続されている例です。*[TSEL0CR9]*<INSEL39[2:0]>で入力トリガー選択、エッジ検出の許可/禁止<UPDN39>とエッジ検出条件の設定<OUSEL39>およびトリガー出力制御<EN39>を行います。

図 2.1 トリガーセレクター接続例

# 2.2.1. トリガーセレクターと製品対応

TMPM3H グループ(2)のトリガーセレクターは、19本の制御レジスター(*[TSEL0CR0~15]*, *[TSEL1CR0~2]*)で構成されており 74本のトリガーを制御できます。

下記の表にコントロールレジスターと接続先および対応製品を示します。

表 2.2 製品別トリガーセレクター対応一覧 (1/12)

| レジスター      |             | トリガー           |                                                                                                                                                                                                                                                                                                                                       | 製品対応 (〇:対応、-:非対応) |      |      |      |      |  |

|------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|------|------|--|

|            | Bit Symbol  | ソース            | 入カトリガー信号                                                                                                                                                                                                                                                                                                                              | M3HQ              | МЗНР | МЗНИ | МЗНМ | M3HL |  |

| [TSEL0CR0] | INSEL0[2:0] | DMAC A<br>ch15 | ・T32A ch0 DMA 要求レジスターA1 一致 ・T32A ch0 DMA 要求レジスターC1 一致 ・T32A ch1 DMA 要求レジスターA1 一致 ・T32A ch1 DMA 要求レジスターC1 一致                                                                                                                                                                                                                           | 0                 | 0    | 0    | 0    | 0    |  |

|            | INSEL1[2:0] | DMAC A<br>ch16 | •T32A ch2 DMA 要求レジスターA1 一致 •T32A ch2 DMA 要求レジスターC1 一致 •T32A ch3 DMA 要求レジスターA1 一致 •T32A ch3 DMA 要求レジスターC1 一致                                                                                                                                                                                                                           | 0                 | 0    | 0    | 0    | 0    |  |

|            | INSEL2[2:0] | DMAC A<br>ch17 | ・T32A ch0 DMA 要求レジスターB1 一致<br>・T32A ch1 DMA 要求レジスターB1 一致                                                                                                                                                                                                                                                                              | 0                 | 0    | 0    | 0    | 0    |  |

|            | INSEL3[2:0] | DMAC A<br>ch18 | ・T32A ch2 DMA 要求レジスターB1 一致<br>・T32A ch3 DMA 要求レジスターB1 一致                                                                                                                                                                                                                                                                              | 0                 | 0    | 0    | 0    | 0    |  |

| [TSEL0CR1] | INSEL4[2:0] | DMAC A<br>ch19 | <ul> <li>・T32A DMA 要求 ch0 キャプチャーA0</li> <li>・T32A DMA 要求 ch0 キャプチャーA1</li> <li>・T32A DMA 要求 ch1 キャプチャーA0</li> <li>・T32A DMA 要求 ch1 キャプチャーA1</li> <li>・T32A DMA 要求 ch0 キャプチャーC0</li> <li>・T32A DMA 要求 ch0 キャプチャーC1</li> <li>・T32A DMA 要求 ch1 キャプチャーC0</li> <li>・T32A DMA 要求 ch1 キャプチャーC0</li> <li>・T32A DMA 要求 ch1 キャプチャーC1</li> </ul> | 0                 | 0    | 0    | 0    | 0    |  |

|            | INSEL5[2:0] | DMAC A<br>ch20 | ・T32A DMA 要求 ch2 キャプチャーA0<br>・T32A DMA 要求 ch2 キャプチャーA1<br>・T32A DMA 要求 ch3 キャプチャーA0<br>・T32A DMA 要求 ch3 キャプチャーA1<br>・T32A DMA 要求 ch2 キャプチャーC0<br>・T32A DMA 要求 ch2 キャプチャーC1<br>・T32A DMA 要求 ch3 キャプチャーC0<br>・T32A DMA 要求 ch3 キャプチャーC0                                                                                                  | 0                 | 0    | 0    | 0    | 0    |  |

|            | INSEL6[2:0] | DMAC A<br>ch21 | <ul> <li>・T32A DMA 要求 ch0 キャプチャーB0</li> <li>・T32A DMA 要求 ch0 キャプチャーB1</li> <li>・T32A DMA 要求 ch1 キャプチャーB0</li> <li>・T32A DMA 要求 ch1 キャプチャーB1</li> </ul>                                                                                                                                                                                | 0                 | 0    | 0    | 0    | 0    |  |

|            | INSEL7[2:0] | DMAC A<br>ch22 | ・T32A DMA 要求 ch2 キャプチャーB0<br>・T32A DMA 要求 ch2 キャプチャーB1<br>・T32A DMA 要求 ch3 キャプチャーB0<br>・T32A DMA 要求 ch3 キャプチャーB1                                                                                                                                                                                                                      | 0                 | 0    | 0    | 0    | 0    |  |

表 2.3 製品別トリガーセレクター対応一覧 (2/12)

|             |                          | トリガー                                                                                           |                                                                                                                      | 象    | ····································· | (〇:対応 | 、-:非対応 | <u>.</u> ) |

|-------------|--------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|---------------------------------------|-------|--------|------------|

| レジスター       | Bit Symbol               | ソース                                                                                            | 入カトリガー信号                                                                                                             | M3HQ | МЗНР                                  | мзни  | мзнм   | M3HL       |

| [TSEL0CR2]  | INSEL8[2:0]              | DMAC A<br>ch23                                                                                 | ・DMAC A ch0 転送終了割り込み<br>・DMAC A ch1 転送終了割り込み<br>・DMAC A ch6 転送終了割り込み<br>・DMAC A ch7 転送終了割り込み                         | 0    | 0                                     | 0     | 0      | 0          |

|             | INSEL9[2:0]              | DMAC A<br>ch24                                                                                 | ・DMAC A ch2 転送終了割り込み<br>・DMAC A ch3 転送終了割り込み<br>・DMAC A ch8 転送終了割り込み<br>・DMAC A ch9 転送終了割り込み                         | 0    | 0                                     | 0     | 0      | 0          |

|             | INSEL10[2:0] DMAC A ch25 | ・DMAC A ch4 転送終了割り込み<br>・DMAC A ch5 転送終了割り込み<br>・DMAC A ch10 転送終了割り込み<br>・DMAC A ch11 転送終了割り込み | 0                                                                                                                    | 0    | 0                                     | 0     | 0      |            |

|             | INSEL11[2:0]             | DMAC A<br>ch26                                                                                 | ・DMAC A ch12 転送終了割り込み ・DMAC A ch13 転送終了割り込み ・DMAC A ch14 転送終了割り込み                                                    | 0    | 0                                     | 0     | 0      | 0          |

|             | INSEL12[2:0]             | 2:0] DMAC A ch27                                                                               | ・DMAC A ch15 転送終了割り込み<br>・DMAC A ch19 転送終了割り込み                                                                       | 0    | 0                                     | 0     | 0      | 0          |

| ITSEL ACRAI | INSEL13[2:0]             | DMAC A<br>ch28                                                                                 | ・DMAC A ch16 転送終了割り込み・DMAC A ch20 転送終了割り込み                                                                           | 0    | 0                                     | 0     | 0      | 0          |

| [TSEL0CR3]  | INSEL14[2:0]             | DMAC A<br>ch29                                                                                 | ・DMAC A ch17 転送終了割り込み・DMAC A ch21 転送終了割り込み                                                                           | 0    | 0                                     | 0     | 0      | 0          |

|             | INSEL15[2:0]             | DMAC A<br>ch30                                                                                 | ・DMAC A ch18 転送終了割り込み<br>・DMAC A ch22 転送終了割り込み                                                                       | 0    | 0                                     | 0     | 0      | 0          |

|             | INSEL16[2:0]             | DMAC A<br>ch31                                                                                 | ·PB1 端子(TRGIN0)<br>·PA3 端子(TRGIN1)<br>·PN3 端子(TRGIN2)                                                                | 0    | 0                                     | 0     | 0      | 0          |

|             | INSEL17[2:0]             | DMAC B ch0                                                                                     | ・TSPI ch2 受信完了トリガー                                                                                                   | 0    | 0                                     | 0     | 0      | _          |

| (TOE) 00D41 |                          |                                                                                                | ・I <sup>2</sup> C ch3 受信完了トリガー                                                                                       | 0    | 0                                     | _     | _      | _          |

| [TSEL0CR4]  | INSEL18[2:0]             | ISEL18[2:0] DMAC B ch1                                                                         | ・TSPI ch2 送信完了トリガー                                                                                                   | 0    | 0                                     | 0     | 0      | _          |

|             |                          |                                                                                                | ・I <sup>2</sup> C ch3 送信完了トリガー                                                                                       | 0    | 0                                     | _     | _      | _          |

|             | INSEL19[2:0]             | DMAC B ch14                                                                                    | ・ADC ユニット A 汎用トリガーDMA 要求・ADC ユニット A 単独変換 DMA 要求・ADC ユニット A 連続変換 DMA 要求                                               | 0    | 0                                     | 0     | 0      | 0          |

| [TSEL0CR5]  | INSEL20[2:0]             | DMAC B<br>ch15                                                                                 | ・T32A ch4 DMA 要求レジスターA1 一致<br>・T32A ch4 DMA 要求レジスターC1 一致<br>・T32A ch5 DMA 要求レジスターA1 一致<br>・T32A ch5 DMA 要求レジスターC1 一致 | 0    | 0                                     | 0     | 0      | 0          |

|             | INSEL21[2:0]             | DMAC B<br>ch16                                                                                 | ・T32A ch6 DMA 要求レジスターA1 一致<br>・T32A ch6 DMA 要求レジスターC1 一致<br>・T32A ch7 DMA 要求レジスターA1 一致<br>・T32A ch7 DMA 要求レジスターC1 一致 | 0    | 0                                     | 0     | 0      | 0          |

|             | INSEL22[2:0]             | DMAC B ch17                                                                                    | ・T32A ch4 DMA 要求レジスターB1 一致<br>・T32A ch5 DMA 要求レジスターB1 一致                                                             | 0    | 0                                     | 0     | 0      | 0          |

|             | INSEL23[2:0]             | DMAC B<br>ch18                                                                                 | ・T32A ch6 DMA 要求レジスターB1 一致<br>・T32A ch7 DMA 要求レジスターB1 一致                                                             | 0    | 0                                     | 0     | 0      | 0          |

#### 表 2.4 製品別トリガーセレクター対応一覧 (3/12)

| レジスター       |              | トリガー           | 製品対応 (〇:対応、-:非対応)                                   |      |      |      |      |      |

|-------------|--------------|----------------|-----------------------------------------------------|------|------|------|------|------|

|             | Bit Symbol   | ソース            | 人力トリカー信号                                            | M3HQ | МЗНР | МЗНИ | МЗНМ | M3HL |

|             |              |                | ・T32A DMA 要求 ch4 キャプチャーA0 ・T32A DMA 要求 ch4 キャプチャーA1 |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch5 キャプチャーA0                           |      |      |      |      | í    |

|             |              | DMAC B         | ・T32A DMA 要求 ch5 キャプチャーA1                           | _    | _    | _    | _    | _    |

|             | INSEL24[2:0] | ch19           | ・T32A DMA 要求 ch4 キャプチャーC0                           | 0    | 0    | 0    | 0    | 0    |

|             |              |                | ・T32A DMA 要求 ch4 キャプチャーC1                           |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch5 キャプチャーC0                           |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch5 キャプチャーC1                           |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch6 キャプチャーA0                           |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch6 キャプチャーA1                           |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch7 キャプチャーA0                           |      |      |      |      |      |

| [TSEL0CR6]  | INSEL25[2:0] | DMAC B         | ・T32A DMA 要求 ch7 キャプチャーA1                           | 0    | 0    | 0    | 0    | 0    |

| [ISELUCKO]  | INSELZS[Z.U] | ch20           | ・T32A DMA 要求 ch6 キャプチャーC0                           | O    |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch6 キャプチャーC1                           |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch7 キャプチャーC0                           |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch7 キャプチャーC1                           |      |      |      |      |      |

|             | INSEL26[2:0] | DMAC B ch21    | ・T32A DMA 要求 ch4 キャプチャーB0                           | 0    | 0    | 0    | 0    | 0    |

|             |              |                | ・T32A DMA 要求 ch4 キャプチャーB1                           |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch5 キャプチャーB0                           |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch5 キャプチャーB1                           |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch6 キャプチャーB0                           | 0    | 0    | 0    | 0    | 0    |

|             | INSEL27[2:0] | DMAC B         | ・T32A DMA 要求 ch6 キャプチャーB1                           |      |      |      |      |      |

|             | INOLLET[2.0] | ch22           | •T32A DMA 要求 ch7 キャプチャーB0                           |      |      |      |      |      |

|             |              |                | ・T32A DMA 要求 ch7 キャプチャーB1                           |      |      |      |      |      |

|             |              |                | ・DMAC B ch0 転送終了割り込み                                | 0    | 0    | 0    | 0    | 0    |

|             | INSEL28[2:0] | DMAC B         | ・DMAC B ch1 転送終了割り込み                                |      |      |      |      |      |

|             |              | ch23           | ・DMAC B ch6 転送終了割り込み                                |      |      |      |      |      |

|             |              |                | ・DMAC B ch7 転送終了割り込み                                |      |      |      |      |      |

|             |              |                | ・DMAC B ch2 転送終了割り込み                                |      |      |      |      |      |

|             | INSEL29[2:0] | DMAC B         | - DMAC B ch3 転送終了割り込み                               | 0    | 0    | 0    | 0    | 0    |

| FT051 00571 |              | ch24           | - DMAC B ch8 転送終了割り込み                               |      |      |      |      |      |

| [TSEL0CR7]  |              |                | - DMAC B ch4 転送終了割り込み                               |      |      |      |      | 0    |

|             |              | DMAGG          | ・DMAC B ch4 転送終了割り込み<br>・DMAC B ch5 転送終了割り込み        |      |      |      |      |      |

|             | INSEL30[2:0] | DMAC B<br>ch25 | - DMAC B ch3 転送終了割り込み                               | 0    | 0    | 0    | 0    |      |

|             |              | GHZ5           | - DMAC B ch10 転送終了割り込み                              |      |      |      |      |      |

|             |              |                | ・DMAC B ch12 転送終了割り込み                               |      |      |      |      |      |

|             | INSEL31[2:0] | DMAC B         | - DMAC B ch12 転送終了割り込み                              | 0    | 0    | 0    | 0    | 0    |

|             |              | ch26           | - DMAC B ch14 転送終了割り込み                              |      |      |      |      |      |

|             |              |                |                                                     |      |      |      |      |      |

# 表 2.5 製品別トリガーセレクター対応一覧 (4/12)

| レジスター      | レジスター        |                               | 入力トリガー信号                                                                                                                                                                                                | 製品対応 (〇:対応、-:非対応) |      |      |      |      |

|------------|--------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|------|------|

|            | Bit Symbol   | ソース                           | 人 ハトリル 一 旧 方                                                                                                                                                                                            | M3HQ              | МЗНР | M3HN | МЗНМ | M3HL |

|            | INSEL32[2:0] | DMAC B<br>ch27                | ・DMAC B ch15 転送終了割り込み<br>・DMAC B ch19 転送終了割り込み                                                                                                                                                          | 0                 | 0    | 0    | 0    | 0    |

|            | INSEL33[2:0] | DMAC B<br>ch28                | ・DMAC B ch16 転送終了割り込み<br>・DMAC B ch20 転送終了割り込み                                                                                                                                                          | 0                 | 0    | 0    | 0    | 0    |

| [TSEL0CR8] | INSEL34[2:0] | DMAC B<br>ch29                | ・DMAC B ch17 転送終了割り込み<br>・DMAC B ch21 転送終了割り込み                                                                                                                                                          | 0                 | 0    | 0    | 0    | 0    |

|            | INSEL35[2:0] | DMAC B<br>ch30                | ・DMAC B ch18 転送終了割り込み<br>・DMAC B ch22 転送終了割り込み                                                                                                                                                          | 0                 | 0    | 0    | 0    | 0    |

|            | INSEL36[2:0] | ] DMAC B ch31                 | ・PB1 端子(TRGIN0)<br>・PA3 端子(TRGIN1)<br>・PN3 端子(TRGIN2)                                                                                                                                                   | 0                 | 0    | 0    | 0    | 0    |

|            | INSEL37[2:0] | ADC<br>(PMDTRG6)              | <ul> <li>・PB1 端子(TRGIN0)</li> <li>・PA3 端子(TRGIN1)</li> <li>・PN3 端子(TRGIN2)</li> <li>・T32A ch7 タイマーレジスターA1 一致トリガー</li> <li>・T32A ch7 タイマーレジスターB1 一致トリガー</li> <li>・T32A ch7 タイマーレジスターC1 一致トリガー</li> </ul> | 0                 | 0    | 0    | 0    | 0    |

| [TSEL0CR9] | INSEL38[2:0] | ADC<br>(ADATRGIN)<br>(汎用トリガー) | <ul> <li>・PB1 端子(TRGIN0)</li> <li>・PA3 端子(TRGIN1)</li> <li>・PN3 端子(TRGIN2)</li> <li>・T32A ch7 タイマーレジスターA1 一致トリガー</li> <li>・T32A ch7 タイマーレジスターB1 一致トリガー</li> <li>・T32A ch7 タイマーレジスターC1 一致トリガー</li> </ul> | 0                 | 0    | 0    | 0    | 0    |

|            | INSEL39[2:0] | TSPI ch0                      | <ul> <li>PB1 端子(TRGIN0)</li> <li>PA3 端子(TRGIN1)</li> <li>PN3 端子(TRGIN2)</li> <li>T32A ch6 タイマーレジスターA1 一致トリガー</li> <li>T32A ch6 タイマーレジスターB1 一致トリガー</li> <li>T32A ch6 タイマーレジスターC1 一致トリガー</li> </ul>       | 0                 | 0    | 0    | 0    | 0    |

#### 表 2.6 製品別トリガーセレクター対応一覧 (5/12)

| レジスター       |                                              | トリガー        | 製                                                                                                                                                                                                 | 品対応  | (〇:対応、-:非対応) |      |      |      |

|-------------|----------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|------|------|------|

|             | Bit Symbol                                   | ソース         | 人力トリカー信 <del>与</del>                                                                                                                                                                              | M3HQ | МЗНР         | МЗНИ | МЗНМ | M3HL |

|             | INSEL40[2:0]                                 | TSPI<br>ch1 | <ul> <li>PB1 端子(TRGIN0)</li> <li>PA3 端子(TRGIN1)</li> <li>PN3 端子(TRGIN2)</li> <li>T32A ch6 タイマーレジスターA1 一致トリガー</li> <li>T32A ch6 タイマーレジスターB1 一致トリガー</li> <li>T32A ch6 タイマーレジスターC1 一致トリガー</li> </ul> | 0    | 0            | 0    | 0    | 1    |

|             | INSEL41[2:0]                                 | TSPI<br>ch2 | <ul> <li>PB1 端子(TRGIN0)</li> <li>PA3 端子(TRGIN1)</li> <li>PN3 端子(TRGIN2)</li> <li>T32A ch6 タイマーレジスターA1 一致トリガー</li> <li>T32A ch6 タイマーレジスターB1 一致トリガー</li> <li>T32A ch6 タイマーレジスターC1 一致トリガー</li> </ul> | 0    | 0            | 0    | 0    | _    |

| [ISELUCKIO] | INSEL42[2:0] TSPI ch3  INSEL43[2:0] TSPI ch4 |             | <ul> <li>PB1 端子(TRGIN0)</li> <li>PA3 端子(TRGIN1)</li> <li>PN3 端子(TRGIN2)</li> <li>T32A ch6 タイマーレジスターA1 一致トリガー</li> <li>T32A ch6 タイマーレジスターB1 一致トリガー</li> <li>T32A ch6 タイマーレジスターC1 一致トリガー</li> </ul> | 0    | 0            | 0    | 0    | 1    |

|             |                                              |             | <ul> <li>PB1 端子(TRGIN0)</li> <li>PA3 端子(TRGIN1)</li> <li>PN3 端子(TRGIN2)</li> <li>T32A ch6 タイマーレジスターA1 一致トリガー</li> <li>T32A ch6 タイマーレジスターB1 一致トリガー</li> <li>T32A ch6 タイマーレジスターC1 一致トリガー</li> </ul> | 0    | 0            | 0    | 0    | _    |

# 表 2.7 製品別トリガーセレクター対応一覧 (6/12)

| レジスター                      |              | トリガー        | 3 本いは 60                                                                                                                                                                                                | 氢    | <b>以品対応</b> | (〇:対応 | 、-:非対応 | <u>\$</u> ) |

|----------------------------|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|-------|--------|-------------|

| <i>D D D D D D D D D D</i> | Bit Symbol   | ソース         | 入力トリガー信号                                                                                                                                                                                                | M3HQ | МЗНР        | МЗНИ  | МЗНМ   | M3HL        |

|                            | INSEL44[2:0] | UART<br>ch0 | <ul> <li>PB1 端子(TRGIN0)</li> <li>PA3 端子(TRGIN1)</li> <li>PN3 端子(TRGIN2)</li> <li>T32A ch6 タイマーレジスターA1 一致トリガー</li> <li>T32A ch6 タイマーレジスターB1 一致トリガー</li> <li>T32A ch6 タイマーレジスターC1 一致トリガー</li> </ul>       | 0    | 0           | 0     | 0      | 0           |

|                            | INSEL45[2:0] | UART<br>ch1 | <ul> <li>PB1 端子(TRGIN0)</li> <li>PA3 端子(TRGIN1)</li> <li>PN3 端子(TRGIN2)</li> <li>T32A ch6 タイマーレジスターA1 一致トリガー</li> <li>T32A ch6 タイマーレジスターB1 一致トリガー</li> <li>T32A ch6 タイマーレジスターC1 一致トリガー</li> </ul>       | 0    | 0           | 0     | 0      | 0           |

| [TSEL0CR11]                | INSEL46[2:0] | UART<br>ch2 | <ul> <li>・PB1 端子(TRGIN0)</li> <li>・PA3 端子(TRGIN1)</li> <li>・PN3 端子(TRGIN2)</li> <li>・T32A ch6 タイマーレジスターA1 一致トリガー</li> <li>・T32A ch6 タイマーレジスターB1 一致トリガー</li> <li>・T32A ch6 タイマーレジスターC1 一致トリガー</li> </ul> | 0    | 0           | 0     | 0      | 0           |

|                            | INSEL47[2:0] |             | <ul> <li>PB1 端子(TRGIN0)</li> <li>PA3 端子(TRGIN1)</li> <li>PN3 端子(TRGIN2)</li> <li>T32A ch6 タイマーレジスターA1 一致トリガー</li> <li>T32A ch6 タイマーレジスターB1 一致トリガー</li> <li>T32A ch6 タイマーレジスターC1 一致トリガー</li> </ul>       | 0    | 0           | 0     | 0      | 0           |

# 表 2.8 製品別トリガーセレクター対応一覧 (7/12)

| レジスター       |                 | トリガー                            | 入力トリガー信号                                                                                                                                                                                                | 製    | 品対応  | (〇:対応、-:非対応 |      | 応)   |

|-------------|-----------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------------|------|------|

|             | Bit Symbol      | ソース                             | 人力トリカー信号                                                                                                                                                                                                | M3HQ | МЗНР | M3HN        | МЗНМ | M3HL |

|             | INSEL48[2:0]    | UART<br>ch4                     | <ul> <li>・PB1 端子(TRGIN0)</li> <li>・PA3 端子(TRGIN1)</li> <li>・PN3 端子(TRGIN2)</li> <li>・T32A ch6 タイマーレジスターA1 一致トリガー</li> <li>・T32A ch6 タイマーレジスターB1 一致トリガー</li> <li>・T32A ch6 タイマーレジスターC1 一致トリガー</li> </ul> | 0    | 0    | 0           | 0    | 0    |

| [TSEL0CR12] | INSEL49[2:0]    | UART<br>ch5                     | <ul> <li>PB1 端子(TRGIN0)</li> <li>PA3 端子(TRGIN1)</li> <li>PN3 端子(TRGIN2)</li> <li>T32A ch6 タイマーレジスターA1 一致トリガー</li> <li>T32A ch6 タイマーレジスターB1 一致トリガー</li> <li>T32A ch6 タイマーレジスターC1 一致トリガー</li> </ul>       | 0    | 0    | 0           | 0    | 0    |

|             | INSEL50[2:0]    | T32A<br>SEL50[2:0] ch0<br>タイマーA | ・PB1 端子(TRGIN0) ・PA3 端子(TRGIN1) ・PN3 端子(TRGIN2) ・UART ch0 送信完了トリガー ・UART ch0 受信完了トリガー                                                                                                                   | 0    | 0    | 0           | 0    | 0    |

|             | INSEL51[2:0] ch | T32A<br>ch0<br>タイマーB            | ・T32A ch0 タイマーレジスターA0 一致トリガー<br>・T32A ch0 タイマーレジスターA1 一致トリガー<br>・T32A ch0 タイマーA オーバーフロートリガー<br>・T32A ch0 タイマーA アンダーフロートリガー                                                                              | 0    | 0    | 0           | 0    | 0    |

# 表 2.9 製品別トリガーセレクター対応一覧 (8/12)

| レジスター       |                  | トリガー                 | 入力トリガー信号                                                                                                                   | 製品   | 品対応  | (〇:対応 | 、-:非対 | 応)   |

|-------------|------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------|------|

|             | Bit Symbol       | ソース                  | 人のトッカー信号                                                                                                                   | M3HQ | МЗНР | МЗНМ  | МЗНМ  | M3HL |

|             | INSEL52[2:0]     | T32A<br>ch0<br>タイマーC | ・T32A ch7 タイマーレジスターC0 一致トリガー<br>・T32A ch7 タイマーレジスターC1 一致トリガー<br>・T32A ch7 タイマーC オーバーフロートリガー<br>・T32A ch7 タイマーC アンダーフロートリガー | 0    | 0    | 0     | 0     | 0    |

| [TSEL0CR13] | INSEL53[2:0]     | T32A<br>ch1<br>タイマーA | PB1 端子(TRGIN0) PA3 端子(TRGIN1) PN3 端子(TRGIN2) UART ch1 送信完了トリガー UART ch1 受信完了トリガー I <sup>2</sup> C ch0 送受信割り込み              | 0    | 0    | 0     | 0     | 0    |

|             | INSEL54[2:0]     | T32A<br>ch1<br>タイマーB | ・T32A ch1 タイマーレジスターA0 一致トリガー ・T32A ch1 タイマーレジスターA1 一致トリガー ・T32A ch1 タイマーA オーバーフロートリガー ・T32A ch1 タイマーA アンダーフロートリガー          | 0    | 0    | 0     | 0     | 0    |

|             | INSEL55[2:0] ch1 | T32A<br>ch1<br>タイマーC | ・T32A ch0 タイマーレジスターC0 一致トリガー<br>・T32A ch0 タイマーレジスターC1 一致トリガー<br>・T32A ch0 タイマーC オーバーフロートリガー<br>・T32A ch0 タイマーC アンダーフロートリガー | 0    | 0    | 0     | 0     | 0    |

### 表 2.10 製品別トリガーセレクター対応一覧 (9/12)

| レジスター      | レジスター         |                      | 入力トリガー信号                                                                                                                                                         | 製    | 品対応  | (〇:対応 | 、-:非対 | 応)   |

|------------|---------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------|------|

|            | Bit Symbol    | ソース                  | 人がトリルーはち                                                                                                                                                         | M3HQ | МЗНР | M3HN  | МЗНМ  | M3HL |

|            | INSEL56[2:0]  | T32A<br>ch2<br>タイマーA | ・PB1 端子(TRGIN0) ・PA3 端子(TRGIN1) ・PN3 端子(TRGIN2) ・UART ch2 送信完了トリガー ・UART ch2 受信完了トリガー ・TSPI ch0 送信完了信号 ・TSPI ch0 受信完了信号                                          | 0    | 0    | 0     | 0     | 0    |

|            |               |                      | ・I <sup>2</sup> C ch1 送受信割り込み                                                                                                                                    | 0    | 0    | 0     | 0     | _    |

| [TSEL0CR14 | INSEL57[2:0]  | T32A<br>ch2<br>タイマーB | <ul> <li>・T32A ch2 タイマーレジスターA0 一致トリガー</li> <li>・T32A ch2 タイマーレジスターA1 一致トリガー</li> <li>・T32A ch2 タイマーA オーバーフロートリガー</li> <li>・T32A ch2 タイマーA アンダーフロートリガー</li> </ul> | 0    | 0    | 0     | 0     | 0    |

| J          | INSEL58 [2:0] | T32A<br>ch2<br>タイマーC | ・T32A ch1 タイマーレジスターC0 一致トリガー<br>・T32A ch1 タイマーレジスターC1 一致トリガー<br>・T32A ch1 タイマーC オーバーフロートリガー<br>・T32A ch1 タイマーC アンダーフロートリガー                                       | 0    | 0    | 0     | 0     | 0    |

|            | INSEL59[2:0]  | T32A<br>ch3<br>タイマーA | ・PB1 端子(TRGIN0) ・PA3 端子(TRGIN1) ・PN3 端子(TRGIN2) ・UART ch3 送信完了トリガー ・UART ch3 受信完了トリガー ・I <sup>2</sup> C ch2 送受信割り込み                                              | 0    | 0    | 0     | 0     | 0    |

|            |               |                      | ・TSPI ch1 送信完了信号<br>・TSPI ch1 受信完了信号                                                                                                                             | 0    | 0    | 0     | 0     | _    |

# 表 2.11 製品別トリガーセレクター対応一覧 (10/12)

| レジスター       |                                   | トリガー                                                                                                              | 入力トリガー信号                                                                                                                   | 製    | 品対応  | (〇:対応 | 、-:非対 | 応)   |

|-------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------|------|

|             | Bit Symbol                        | ソース                                                                                                               | 人のドッカー信号                                                                                                                   | M3HQ | МЗНР | M3HN  | МЗНМ  | M3HL |

|             | INSEL60[2:0]                      | T32A<br>ch3<br>タイマーB                                                                                              | ・T32A ch3 タイマーレジスターA0 一致トリガー<br>・T32A ch3 タイマーレジスターA1 一致トリガー<br>・T32A ch3 タイマーA オーバーフロートリガー<br>・T32A ch3 タイマーA アンダーフロートリガー | 0    | 0    | 0     | 0     | 0    |

|             | INSEL61[2:0] ch3                  | T32A<br>ch3<br>タイマーC                                                                                              | ・T32A ch2 タイマーレジスターC0 一致トリガー<br>・T32A ch2 タイマーレジスターC1 一致トリガー<br>・T32A ch2 タイマーC オーバーフロートリガー<br>・T32A ch2 タイマーC アンダーフロートリガー | 0    | 0    | 0     | 0     | 0    |

| [TSEL0CR15] | INSEL62[2:0]                      | T32A                                                                                                              | ・PB1 端子(TRGIN0)<br>・PA3 端子(TRGIN1)<br>・PN3 端子(TRGIN2)<br>・UART ch4 送信完了トリガー<br>・UART ch4 受信完了トリガー                          | 0    | 0    | 0     | 0     | 0    |

|             |                                   |                                                                                                                   | ·TSPI ch2 送信完了信号<br>·TSPI ch2 受信完了信号                                                                                       | 0    | 0    | 0     | 0     | -    |

|             |                                   |                                                                                                                   | ・I <sup>2</sup> C ch3 送受信割り込み                                                                                              | 0    | 0    | _     | _     |      |

|             | T32A<br>INSEL63[2:0] ch4<br>タイマーB | ・T32A ch4 タイマーレジスターA0 一致トリガー ・T32A ch4 タイマーレジスターA1 一致トリガー ・T32A ch4 タイマーA オーバーフロートリガー ・T32A ch4 タイマーA アンダーフロートリガー | 0                                                                                                                          | 0    | 0    | 0     | 0     |      |

# 表 2.12 製品別トリガーセレクター対応一覧 (11/12)

| レジスター       |                      | トリガー                 | 入力トリガー信号                                                                                                                                                     | 製    | 品対応  | (〇:対応、-:非対応) |      |      |

|-------------|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------------|------|------|

|             | Bit Symbol           | ソース                  | 人が下りが一倍を                                                                                                                                                     | M3HQ | МЗНР | МЗНИ         | МЗНМ | M3HL |

|             | INSEL0[2:0]          | T32A<br>ch4<br>タイマーC | <ul> <li>T32A ch3 タイマーレジスターC0 一致トリガー</li> <li>T32A ch3 タイマーレジスターC1 一致トリガー</li> <li>T32A ch3 タイマーC オーバーフロートリガー</li> <li>T32A ch3 タイマーC アンダーフロートリガー</li> </ul> | 0    | 0    | 0            | 0    | 0    |

| [TSEL1CR0]  | INSEL1[2:0] ch5 タイマー | T32A<br>ch5<br>タイマーA | ・PB1 端子(TRGIN0) ・PA3 端子(TRGIN1) ・PN3 端子(TRGIN2) ・UART ch5 送信完了トリガー ・UART ch5 受信完了トリガー ・A-ENC ch0 分周パルス信号                                                     | 0    | 0    | 0            | 0    | 0    |

| [102210110] |                      |                      | ・TSPI ch3 送信完了信号<br> ・TSPI ch3 受信完了信号                                                                                                                        | 0    | 0    | 0            | 0    | -    |

|             | INSEL2[2:0]          | T32A<br>ch5<br>タイマーB | ・T32A ch5 タイマーレジスターA0 一致トリガー・T32A ch5 タイマーレジスターA1 一致トリガー・T32A ch5 タイマーA オーバーフロートリガー・T32A ch5 タイマーA アンダーフロートリガー                                               | 0    | 0    | 0            | 0    | 0    |

|             | INSEL3[2:0] ch5      | T32A<br>ch5<br>タイマーC | ・T32A ch4 タイマーレジスターC0 一致トリガー<br>・T32A ch4 タイマーレジスターC1 一致トリガー<br>・T32A ch4 タイマーC オーバーフロートリガー<br>・T32A ch4 タイマーC アンダーフロートリガー                                   | 0    | 0    | 0            | 0    | 0    |

#### 表 2.13 製品別トリガーセレクター対応一覧 (12/12)

| レジスター      |                                  | トリガー                 | 入力トリガー信号                                                                                                                                                                                                                                        | 製    | 品対応  | (〇:対応 | 、-:非対応 | <u>~</u> ) |

|------------|----------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------|------------|

|            | Bit Symbol                       | ソース                  | 人がパルーに方                                                                                                                                                                                                                                         | M3HQ | МЗНР | M3HN  | МЗНМ   | M3HL       |

|            | INSEL4[2:0]                      | T32A<br>ch6          | ·PB1 端子(TRGIN0)<br>·PA3 端子(TRGIN1)<br>·PN3 端子(TRGIN2)                                                                                                                                                                                           | 0    | 0    | 0     | 0      | 0          |

|            | INSEL4[2.0]                      | タイマーA                | ・TSPI ch4 送信完了信号<br>・TSPI ch4 受信完了信号                                                                                                                                                                                                            | 0    | 0    | -     | _      | _          |

|            |                                  |                      | ・ELOSC 低速クロック                                                                                                                                                                                                                                   | 0    | 0    | 0     | 0      | 0          |

|            | INSEL5[2:0]                      | T32A<br>ch6<br>タイマーB | ・T32A ch6 タイマーレジスターA0 一致トリガー<br>・T32A ch6 タイマーレジスターA1 一致トリガー<br>・T32A ch6 タイマーA オーバーフロートリガー<br>・T32A ch6 タイマーA アンダーフロートリガー                                                                                                                      | 0    | 0    | 0     | 0      | 0          |

| [TSEL1CR1] | INSEL6[2:0]                      | T32A ch6<br>タイマーC    |                                                                                                                                                                                                                                                 | 0    | 0    | 0     | 0      | 0          |

|            | T32A<br>INSEL7[2:0] ch7<br>タイマーA |                      | <ul> <li>・PB1 端子(TRGIN0)</li> <li>・PA3 端子(TRGIN1)</li> <li>・PN3 端子(TRGIN2)</li> <li>・ADC ユニット A 汎用トリガー割り込み</li> <li>・ADC ユニット A 単独変換割り込み</li> <li>・ADC ユニット A 連続変換割り込み</li> <li>・ADC ユニット A 監視 0 割り込み</li> <li>・ADC ユニット A 監視 1 割り込み</li> </ul> | 0    | 0    | 0     | 0      | 0          |

|            | INSEL8[2:0]                      | T32A<br>ch7<br>タイマーB | ・T32A ch7 タイマーレジスターA0 一致トリガー<br>・T32A ch7 タイマーレジスターA1 一致トリガー<br>・T32A ch7 タイマーA オーバーフロートリガー<br>・T32A ch7 タイマーA アンダーフロートリガー                                                                                                                      | 0    | 0    | 0     | 0      | 0          |

| [TSEL1CR2] | T32<br>INSEL9[2:0] ch            | T32A<br>ch7<br>タイマーC | ・T32A ch6 タイマーレジスターC0 一致トリガー<br>・T32A ch6 タイマーレジスターC1 一致トリガー<br>・T32A ch6 タイマーC オーバーフロートリガー<br>・T32A ch6 タイマーC アンダーフロートリガー                                                                                                                      | 0    | 0    | 0     | 0      | 0          |

#### 2.2.2. 使用方法と設定

TRGSEL を使用する場合は、CG(クロック制御と動作モード)の fsys 供給停止レジスターA または B ([CGFSYSENA], [CGFSYSENB])、fc 供給停止レジスター([CGFCEN])で該当するクロックイネーブルビットを"1"(クロック供給)に設定してください。詳細はリファレンスマニュアルの"クロック制御と動作モード"を参照してください。

トリガーセレクターの設定は以下の順序で行ってください。

(1) 入力トリガーの選択 (/TSELxCRn/<INSELm>)

トリガーセレクターの接続先に対し、入力トリガーの選択を行います。

入力トリガーの選択はコントロールレジスターの入力トリガー選択ビット (/TSELxCRn/<INSELm>)で設定してください。(n: レジスター番号、m: トリガー番号)

(2) エッジ検出条件の選択 (JTSELxCRnJ<UPDNm>)

選択された入力トリガー信号に対し、立ち上がりエッジまたは立ち下がりエッジの検出選択を 行います。

エッジ検出条件の選択はコントロールレジスターのエッジ検出条件ビット (/TSELxCRn/<UPDNm>)を設定してください。

エッジ検出が必要なトリガー信号は以下となります。

- ・外部トリガー入力(TRGIN0, TRGIN1, TRGIN2)

- ・ELOSC 低速クロック(fs)

- (3) 出力トリガーの選択 (*[TSELxCRn]*<OUTSELm>)

出力するトリガー信号に対し、エッジ検出なし出力またはエッジ検出あり出力の選択を行います。

トリガー出力の選択はコントロールレジスターのトリガー出力の選択ビット(/TSELxCRn/<OUTSELm>)で設定してください。

(4) トリガー出力制御の選択 (/TSELxCRn/<ENm>)

選択したトリガー信号の出力許可または禁止を選択します。

出力許可または禁止の選択はコントロールレジスターのトリガー出力制御ビット(*[TSELxCRn]* <ENm>)を設定してください。*[TSELxCRn]*<ENm>を"1"に設定するとトリガー出力が許可になります。

#### 2.2.3. レジスター一覧

制御レジスターとアドレスは以下のとおりです。

| 周辺機能            |        | チャネル/ユニット | ベースアドレス    |

|-----------------|--------|-----------|------------|

| トリガーセレクター       | TDCCEL | ch0       | 0x400BB800 |

| F-771-12-0-7-3- | TRGSEL | ch1       | 0x400BB900 |

| レジスター4        | 3           | アドレス(Base+) |

|---------------|-------------|-------------|

| コントロールレジスター0  | [TSELxCR0]  | 0x0000      |

| コントロールレジスター1  | [TSELxCR1]  | 0x0004      |

| コントロールレジスター2  | [TSELxCR2]  | 0x0008      |

| コントロールレジスター3  | [TSELxCR3]  | 0x000C      |

| コントロールレジスター4  | [TSELxCR4]  | 0x0010      |

| コントロールレジスター5  | [TSELxCR5]  | 0x0014      |

| コントロールレジスター6  | [TSELxCR6]  | 0x0018      |

| コントロールレジスター7  | [TSELxCR7]  | 0x001C      |

| コントロールレジスター8  | [TSELxCR8]  | 0x0020      |

| コントロールレジスター9  | [TSELxCR9]  | 0x0024      |

| コントロールレジスター10 | [TSELxCR10] | 0x0028      |

| コントロールレジスター11 | [TSELxCR11] | 0x002C      |

| コントロールレジスター12 | [TSELxCR12] | 0x0030      |

| コントロールレジスター13 | [TSELxCR13] | 0x0034      |

| コントロールレジスター14 | [TSELxCR14] | 0x0038      |

| コントロールレジスター15 | [TSELxCR15] | 0x003C      |

#### 2.2.4. レジスター詳細

以下の章でレジスターの詳細を示します。

各表の機能欄カッコ内の記号は各機能信号名を表しています。

# 2.2.4.1. [TSEL0CR0] (コントロールレジスター0)

| Bit   | Bit Symbol  | リセット後 | Туре | 機能                                                                                                                                                                                                               |

|-------|-------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                  |

| 30:28 | INSEL3[2:0] | 000   | R/W  | 入力トリガーの選択(DMAC A ch18) 000: T32A ch2 DMA 要求レジスターB1 一致 (T32A02DMAREQCMPB1) 001: T32A ch3 DMA 要求レジスターB1 一致 (T32A03DMAREQCMPB1) 010: reserved 011: reserved 100: reserved 101: reserved 110: reserved 111: reserved |

| 27    | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                  |

| 26    | UPDN3       | 0     | R/W  | エッジ検出条件<br>0: 立ち上がりエッジを検出<br>1: 立ち下がりエッジを検出                                                                                                                                                                      |

| 25    | OUTSEL3     | 0     | R/W  | 出力トリガーの選択<br>0: エッジ検出なし<br>1: エッジ検出あり                                                                                                                                                                            |

| 24    | EN3         | 0     | R/W  | トリガー出力制御<br>0: 禁止<br>1: 許可                                                                                                                                                                                       |

| 23    | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                  |

| 22:20 | INSEL2[2:0] | 000   | R/W  | 入力トリガーの選択(DMAC A ch17) 000: T32A ch0 DMA 要求レジスターB1 一致 (T32A00DMAREQCMPB1) 001: T32A ch1 DMA 要求レジスターB1 一致 (T32A01DMAREQCMPB1) 010: reserved 011: reserved 100: reserved 101: reserved 111: reserved               |

| 19    | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                  |

| 18    | UPDN2       | 0     | R/W  | エッジ検出条件<br>0: 立ち上がりエッジを検出<br>1: 立ち下がりエッジを検出                                                                                                                                                                      |

| 17    | OUTSEL2     | 0     | R/W  | 出力トリガーの選択<br>0: エッジ検出なし<br>1: エッジ検出あり                                                                                                                                                                            |

| 16    | EN2         | 0     | R/W  | トリガー出力制御<br>0: 禁止<br>1: 許可                                                                                                                                                                                       |

| 15    | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                  |

| Bit   | Bit Symbol  | リセット後 | Туре | 機能                                                                                                                                                                                                                                                                                         |

|-------|-------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14:12 | INSEL1[2:0] | 000   | R/W  | 入力トリガーの選択(DMAC A ch16) 000: T32A ch2 DMA 要求レジスターA1 一致 (T32A02DMAREQCMPA1) 001: T32A ch2 DMA 要求レジスターC1 一致 (T32A02DMAREQCMPC1) 010: T32A ch3 DMA 要求レジスターA1 一致 (T32A03DMAREQCMPA1) 011: T32A ch3 DMA 要求レジスターC1 一致 (T32A03DMAREQCMPC1) 100: reserved 101: reserved 110: reserved 111: reserved |

| 11    | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                                                                                            |

| 10    | UPDN1       | 0     | R/W  | エッジ検出条件<br>0: 立ち上がりエッジを検出<br>1: 立ち下がりエッジを検出                                                                                                                                                                                                                                                |

| 9     | OUTSEL1     | 0     | R/W  | 出力トリガーの選択<br>0: エッジ検出なし<br>1: エッジ検出あり                                                                                                                                                                                                                                                      |

| 8     | EN1         | 0     | R/W  | トリガー出力制御<br>0: 禁止<br>1: 許可                                                                                                                                                                                                                                                                 |

| 7     | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                                                                                            |

| 6:4   | INSEL0[2:0] | 000   | R/W  | 入力トリガーの選択(DMAC A ch15) 000: T32A ch0 DMA 要求レジスターA1 一致 (T32A00DMAREQCMPA1) 001: T32A ch0 DMA 要求レジスターC1 一致 (T32A00DMAREQCMPC1) 010: T32A ch1 DMA 要求レジスターA1 一致 (T32A01DMAREQCMPA1) 011: T32A ch1 DMA 要求レジスターC1 一致 (T32A01DMAREQCMPC1) 100: reserved 101: reserved 110: reserved 111: reserved |

| 3     | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                                                                                            |

| 2     | UPDN0       | 0     | R/W  | エッジ検出条件<br>0: 立ち上がりエッジを検出<br>1: 立ち下がりエッジを検出                                                                                                                                                                                                                                                |

| 1     | OUTSEL0     | 0     | R/W  | 出力トリガーの選択<br>0: エッジ検出なし<br>1: エッジ検出あり                                                                                                                                                                                                                                                      |

| 0     | EN0         | 0     | R/W  | トリガー出力制御<br>0: 禁止<br>1: 許可                                                                                                                                                                                                                                                                 |

# 2.2.4.2. *[TSEL0CR1]* (コントロールレジスター1)

| Bit   | Bit Symbol  | リセット後 | Туре | 機能                                                                                                                                                                                                                                                                                     |

|-------|-------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                                                                                        |

| 30:28 | INSEL7[2:0] | 000   | R/W  | 入力トリガーの選択(DMAC A ch22) 000: T32A DMA 要求 ch2 キャプチャーB0 (T32A02DMAREQCAPB0) 001: T32A DMA 要求 ch2 キャプチャーB1 (T32A02DMAREQCAPB1) 010: T32A DMA 要求 ch3 キャプチャーB0 (T32A03DMAREQCAPB0) 011: T32A DMA 要求 ch3 キャプチャーB1 (T32A03DMAREQCAPB1) 100: reserved 101: reserved 110: reserved 111: reserved |

| 27    | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                                                                                        |

| 26    | UPDN7       | 0     | R/W  | エッジ検出条件<br>0: 立ち上がりエッジを検出<br>1: 立ち下がりエッジを検出                                                                                                                                                                                                                                            |

| 25    | OUTSEL7     | 0     | R/W  | 出力トリガーの選択<br>0: エッジ検出なし<br>1: エッジ検出あり                                                                                                                                                                                                                                                  |

| 24    | EN7         | 0     | R/W  | トリガー出力制御<br>0: 禁止<br>1: 許可                                                                                                                                                                                                                                                             |

| 23    | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                                                                                        |

| 22:20 | INSEL6[2:0] | 000   | R/W  | 入力トリガーの選択(DMAC A ch21) 000: T32A DMA 要求 ch0 キャプチャーB0 (T32A00DMAREQCAPB0) 001: T32A DMA 要求 ch0 キャプチャーB1 (T32A00DMAREQCAPB1) 010: T32A DMA 要求 ch1 キャプチャーB0 (T32A01DMAREQCAPB0) 011: T32A DMA 要求 ch1 キャプチャーB1 (T32A01DMAREQCAPB1) 100: reserved 101: reserved 110: reserved 111: reserved |

| 19    | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                                                                                        |

| 18    | UPDN6       | 0     | R/W  | エッジ検出条件<br>0: 立ち上がりエッジを検出<br>1: 立ち下がりエッジを検出                                                                                                                                                                                                                                            |

| 17    | OUTSEL6     | 0     | R/W  | 出力トリガーの選択<br>0: エッジ検出なし<br>1: エッジ検出あり                                                                                                                                                                                                                                                  |

| 16    | EN6         | 0     | R/W  | トリガー出力制御<br>0: 禁止<br>1: 許可                                                                                                                                                                                                                                                             |

| 15    | -           | 0     | R    | リードすると"0"が読めます。                                                                                                                                                                                                                                                                        |

| Bit   | Bit Symbol  | リセット後 | Туре | 機能                                                                                                                                                                                                                                                                                                                                                                                                                                             |