# **TC32169FTG**

# **RF Transceiver for ETC**

Ver. 1

# **Table of contents**

| 1.  | Abs    | strac | zt                                                                     | 5  |

|-----|--------|-------|------------------------------------------------------------------------|----|

| 2.  | App    | olica | ition                                                                  | 5  |

| 3.  | Fea    | ature | es                                                                     | 5  |

| 4.  | Blo    | ck D  | Diagram                                                                | 6  |

| 5.  | Pin    | Ass   | signment                                                               | 7  |

| 3.  | Pin    | Des   | scription                                                              | 8  |

| 7.  | Fun    | nctio | nal Description                                                        | 9  |

| 7.  | 1      | Pov   | wer Supply                                                             | 9  |

| 7.: | 2      | RF    | Frequency                                                              | 9  |

| 7.  | 3      | Sys   | stem Clock generation                                                  | 9  |

| 7.  | 4      | Wa    | keup Operation                                                         | 10 |

| 7.  | 5      | RF    | Demodulation                                                           | 10 |

| 7.  | 6      | RF    | Modulation                                                             | 10 |

| 7.  | 7      | МО    | DEM                                                                    | 11 |

| 7.  | 8      | Sys   | stem Control and Data Communication                                    | 11 |

| 7.  | 9      | Sta   | te Transition Diagram                                                  | 12 |

| 7.  | 10     | Sta   | te Description                                                         | 12 |

|     | 7.10.  | 1     | Power Off and Power On States                                          | 12 |

|     | 7.10.2 | 2     | Power On State to Sleep State                                          | 13 |

|     | 7.10.3 | 3     | Sleep State                                                            | 13 |

|     | 7.10.4 | 4     | RX State                                                               | 13 |

|     | 7.10.  | 5     | TX State                                                               | 13 |

|     | 7.10.6 | 6     | Transition between RX State and TX State                               | 13 |

| 7.  | 11     | Sec   | quence Description                                                     | 14 |

|     | 7.11.1 | 1     | Chip Select and Reset                                                  | 14 |

|     | 7.11.2 | 2     | Operation after Power Supply                                           | 15 |

|     | 7.11.3 | 3     | Wakeup Function                                                        | 16 |

|     | 7.11.4 | 4     | Suspension                                                             | 18 |

|     | 7.11.5 | 5     | Use of Modem in TX/RX                                                  | 19 |

|     | 7.11.6 | 6     | Interrupt                                                              | 20 |

| 7.  | 12     | Flo   | wchart Examples                                                        | 21 |

|     | 7.12.  | 1     | Power On State to TX State (Direct Mode)                               | 21 |

|     | 7.12.2 | 2     | Power On State to RX State (Direct Mode)                               | 22 |

| ,   | 7.12.3 | 3     | Power On State to Sleep State to Prepare RX State (Normal/Auto Wakeup) | 23 |

|     | 7.12.4 | 4     | Suspension                                                             | 24 |

| ,   | 7.12.  | 5     | Sleep State to RX State (Normal Wakeup)                                | 25 |

| ,   | 7.12.6 | 6     | Sleep state to RX state (Auto Wakeup)                                  | 26 |

|     | 7.12.  | 7     | Sleep State to TX State                                                | 27 |

|     | 7.12.8 | 8     | RX State                                                               | 28 |

|     |        |       |                                                                        |    |

# **TOSHIBA**

| 7.12.9 |        | RX State at BST Reception                         | 29 |

|--------|--------|---------------------------------------------------|----|

| 7.1    | 2.10   | Reception Frequency Change                        | 30 |

| 7.1    | 2.11   | TX state                                          | 31 |

| 7.1    | 2.12   | Transmission Frequency Change                     | 32 |

| 7.1    | 2.13   | RX State to TX State                              | 33 |

| 7.1    | 2.14   | TX State to RX State                              | 34 |

| 7.13   | Se     | quential Reception of Downlink Frames             | 35 |

| 7.14   | Re     | ception of CRC Error Frame                        | 36 |

| 7.15   | CF     | RC Selection                                      | 36 |

| 7.16   | Re     | gister Access for System Control                  | 37 |

| 7.1    | 6.1    | SPI Control Data Format                           | 37 |

| 7.1    | 6.2    | SPI Signal Timing Specification                   | 39 |

| 8. R   | Regist | er Overview and Detail Description                | 40 |

| 8.1    | Re     | gister Overview                                   | 40 |

| 8.2    | 001    | h; Software Reset                                 | 42 |

| 8.3    | 011    | h; TX/RX State Selection                          | 43 |

| 8.4    | 021    | h; Selection of Function of INTRPT/DIO Pin        | 44 |

| 8.5    | 041    | h; Reception PLL Frequency Setting (LSB)          | 45 |

| 8.6    | 051    | h; Reception PLL Frequency Setting (MSB)          | 46 |

| 8.7    | 061    | h; Transmission PLL Frequency Setting (LSB)       | 47 |

| 8.8    | 071    | h; Transmission PLL Frequency Setting (MSB)       | 48 |

| 8.9    | 081    | h; Reset for PLL Block                            | 49 |

| 8.10   | 091    | h; Transmission Power Control                     | 50 |

| 8.11   | 0A     | h; Modulation and IF Filter Settings              | 51 |

| 8.12   | 0B     | h; Wakeup Sensitivity Setting                     | 52 |

| 8.13   | 101    | h; Read/Write Data of Transmission/Reception FIFO | 53 |

| 8.14   | 11h    | n; Interrupts                                     | 54 |

| 8.15   | 121    | h; Interrupt Mask Setting                         | 55 |

| 8.16   | 131    | h; Interrupt Clearing                             | 56 |

| 8.17   | 141    | h; Inversion of Interrupt Pin Output              | 57 |

| 8.18   | 151    | h; Transmission and Reception Bit Rate Settings   | 58 |

| 8.19   | 161    | h; Ramp Up and Down Coefficient Setting           | 59 |

| 8.20   | 171    | h; Maximum Reception Data Length Setting          | 61 |

| 8.21   | 181    | h; Setting of Cycle Number of Wakeup Detection    | 62 |

| 8.22   | 191    | h; Wakeup Operation Selection                     | 63 |

| 8.23   | 1A     | h; Calibration Start of Wakeup Detection Timer    | 64 |

| 8.24   | 1B     | h; Clearing of WAKE_UP Pin Output                 | 65 |

| 8.25   | 1C     | h; Data Write to Wakeup Register                  | 66 |

| 8.26   | 1D     | h; Byte Length Setting of Reception Data          | 67 |

| 8.27   | 2C     | h; CRC Setting                                    | 68 |

| 8.  | 28                                              | 28 36h; Reception Detection Timer Setting |    |  |  |  |

|-----|-------------------------------------------------|-------------------------------------------|----|--|--|--|

| 8.  | 29                                              | 3Ch; Tests Selection                      | 70 |  |  |  |

| 8.  | 8.30 3Dh; Frequency Setting of Wakeup Detection |                                           |    |  |  |  |

| 8.  | 31                                              | 3Eh; Wakeup Frequency Register Control    | 72 |  |  |  |

| 8.  | 32                                              | 43h; Reception FIFO Register Clearing     | 73 |  |  |  |

| 8.  | 33                                              | 56h; Crystal Oscillator Trimming          | 74 |  |  |  |

| 8.  | 34                                              | 5Ch; Reception CRC Selection              | 75 |  |  |  |

| 8.  | 35                                              | 5Dh; CRC Data Information                 | 76 |  |  |  |

| 9.  | Ab                                              | osolute Maximum Ratings                   | 77 |  |  |  |

| 10. | Op                                              | peration Range                            | 77 |  |  |  |

| 11. | Ele                                             | ectrical Characteristics                  | 78 |  |  |  |

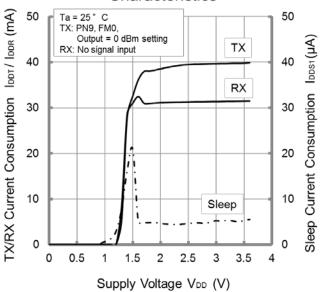

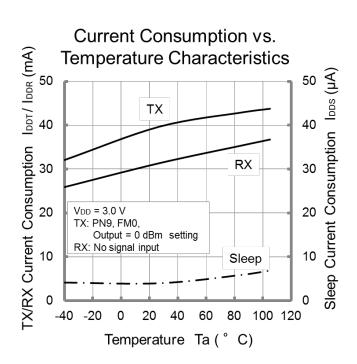

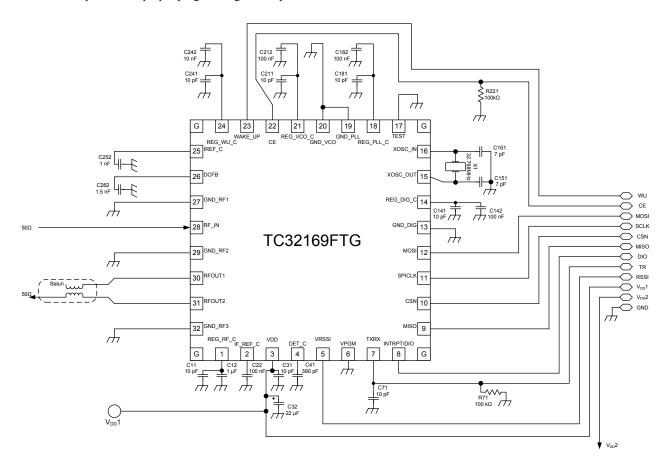

| 12. | Ту                                              | pical Measurement Circuit                 | 82 |  |  |  |

| 13. | Re                                              | eference Data                             | 84 |  |  |  |

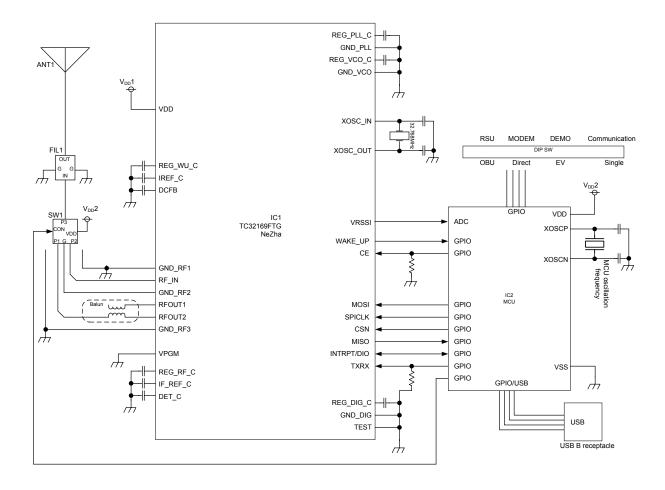

| 14. | Ex                                              | kample of Evaluation Circuit              | 87 |  |  |  |

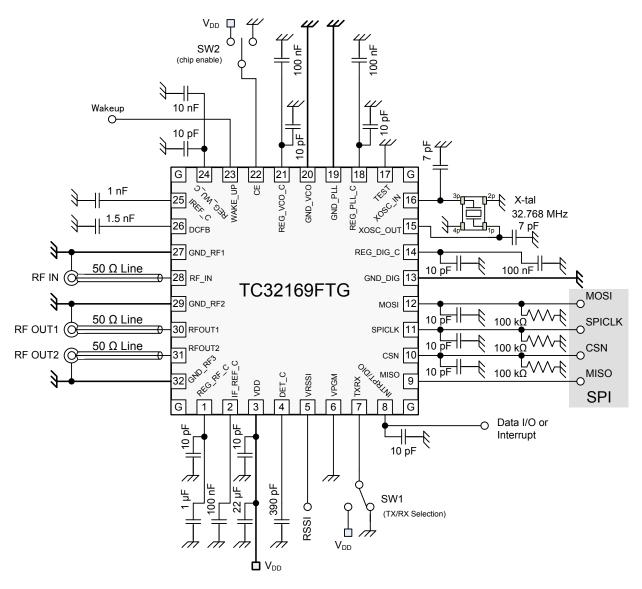

| 15. | Αp                                              | oplication Circuit (Reference)            | 88 |  |  |  |

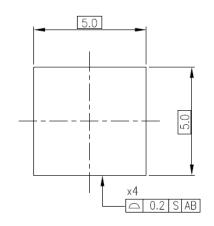

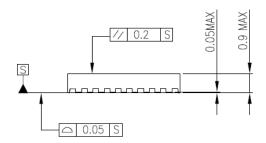

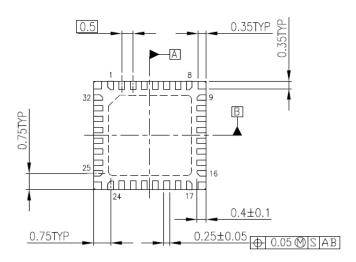

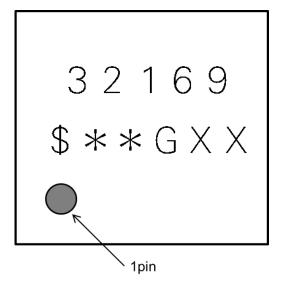

| 16. | Pa                                              | ackage Figure                             | 89 |  |  |  |

| 16  | 5.1                                             | Package Dimensions                        | 89 |  |  |  |

| 16  | 5.2                                             | Marking                                   | 90 |  |  |  |

| RE  | STRI                                            | ICTIONS ON PRODUCT USE                    | 91 |  |  |  |

**TOSHIBA CMOS Integrated Circuit Silicon Monolithic**

# **TC32169FTG**

## 5.8 GHz RF Transceiver for ETC including Modem/Wakeup

## 1. Abstract

TC32169FTG is a single-chip 5.8-GHz RF transceiver for ETC (<u>E</u>lectronic <u>T</u>oll <u>C</u>ollection) system. It is mainly used for OBU (<u>On Board Unit</u>) of automotive systems. Wakeup detector, Crystal oscillator, Mixer, IF amplifier, IF filter, RSSI (<u>R</u>eceived <u>S</u>ignal <u>S</u>trength <u>I</u>ndicator), ASK/OOK modulator/demodulator, Transmission band limiting filter, and PA are included in this IC.

Less than 5  $\mu$ A of the current consumption has been achieved in Sleep mode (only WAKEUP block is active). Also this IC supports a fast boot sequence for MLFF ( $\underline{M}$ ulti- $\underline{L}$ ane  $\underline{F}$ ree  $\underline{F}$ low) and a dual band reception waiting (a data reception at both 5830 MHz and 5840 MHz).

Weight: 0.08g (Typ.)

# 2. Application

This IC can be used for ETC systems whose bit rate is 256 kbps or 512 kbps.

## 3. Features

- Low current consumption

- Fast boot sequence (Refer to Electrical Characteristics for details.)

- Small package: P-VQFN32-0505-0.50-002, 5.0 mm × 5.0 mm square

- Including Wakeup function

- Including Modem functions (Addition of CRC, Postamble, or Preamble is available.)

- Modem mode: Data transmission through the internal modem

- Direct mode: Data transmission or reception through INTRPT/DIO pin is available.

- MLFF (Multi-Lane Free Flow) is supported.

- ➤ Boot control from MCU through CE pin

- Auto-wakeup function using an auto-boot sequence is selectable.

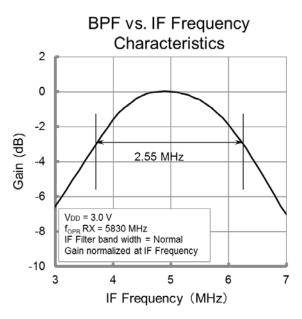

- Including IF filter

- ➤ High selection performance for a reception signal using the internal IF filter

- IC control from dedicated pins

- Fast boot sequence from Sleep mode using CE pin

- Fast switching between TX (Transmission) and RX (Reception) using TXRX pin

- Switching between TX and RX can be also done by using SPI (Serial Peripheral Interface) bus

- IC control from SPI bus

- Wakeup detection settings

- ♦ Setting of a cycle number of the output pulses

- ♦ Wakeup routine setting

- Internal frequency settings (PLL frequency synchronizer); PLL =  $\underline{P}$ hase  $\underline{L}$ ocked  $\underline{L}$ oop

- ♦ Transmission frequency setting

- ♦ Reception frequency setting

- Modem function setting

- Switching between Modem mode and Direct mode

# 4. Block Diagram

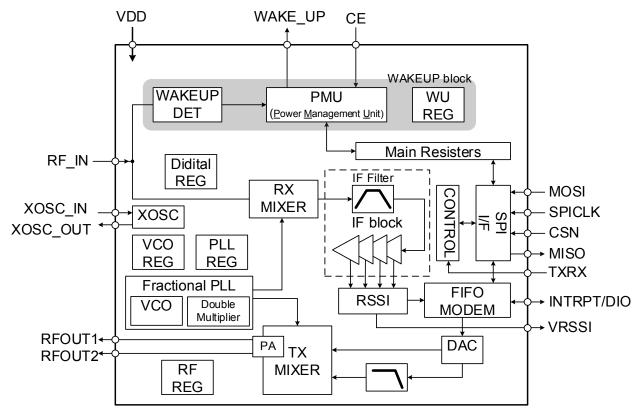

Figure 4-1 Block Diagram

Above figure is a schematic of this product. Some of the functional blocks and others in the block diagram may be omitted or simplified for explanatory purposes.

In this figure, only the circuits in the gray shaded block operate in Sleep mode.

# 5. Pin Assignment

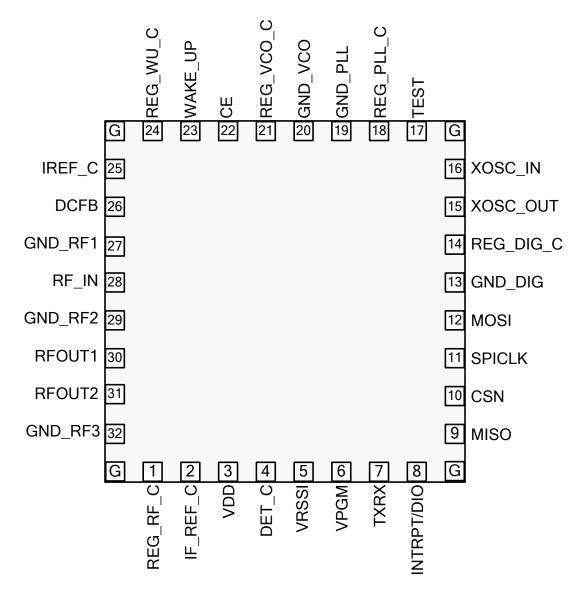

Figure 5-1 Pin Assignment (Top View)

Note: The G pins at the four corners of this IC package are internally connected to the substrate of this IC. It is recommended that those pins are connected to the ground on the printed-circuit board.

7

# 6. Pin Description

Table 6-1 Pin Description

| Pin No. | Name       | I/O          | Description                                                                                                                                                                                                                                   |

|---------|------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | REG_RF_C   | _            | Connect a bypass capacitor for internal regulator stabilization.                                                                                                                                                                              |

| 2       | IF_REF_C   | _            | Connect a capacitor for IF filter circuit stabilization.                                                                                                                                                                                      |

| 3       | VDD        | Power Supply | Supply voltage input pin. 3.0 V (Typ.). Connect a bypass capacitor.                                                                                                                                                                           |

| 4       | DET_C      | _            | Connect a capacitor for ASK/OOK detector.                                                                                                                                                                                                     |

| 5       | VRSSI      | 0            | RSSI output.                                                                                                                                                                                                                                  |

| 6       | VPGM       | _            | Connect to the ground directly (only for the test).                                                                                                                                                                                           |

| 7       | TXRX       | ı            | Select Transmission or Reception. "1": Transmission/"0": Reception                                                                                                                                                                            |

| 8       | INTRPT/DIO | I/O          | Select the pin function by SPI control.  Use for an interrupt: Set Modem mode by SPI.  Use for Data I/O: Set Direct mode by SPI.                                                                                                              |

| 9       | MISO       | 0            | Master input/Slave output of SPI (Master In Slave Out).                                                                                                                                                                                       |

| 10      | CSN        | I            | Enable of SPI communication. "0": Communication enable. "1": Communication stop.                                                                                                                                                              |

| 11      | SPICLK     | 1            | Clock of SPI. Input SPI clock for communication.                                                                                                                                                                                              |

| 12      | MOSI       | 1            | Master output/Slave input of SPI (Master Out Slave In).                                                                                                                                                                                       |

| 13      | GND_DIG    | _            | Ground for digital blocks. Connect to GND.                                                                                                                                                                                                    |

| 14      | REG_DIG_C  | ı            | Connect a bypass capacitor for internal regulator stabilization.                                                                                                                                                                              |

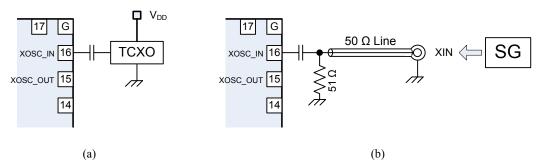

| 15      | XOSC_OUT   | 0            | Connect a crystal oscillator. (When TCXO is used, this pin should be open.)                                                                                                                                                                   |

| 16      | XOSC_IN    | I            | Connect a crystal oscillator. (When TCXO is used, connect it to this pin via a capacitor.)                                                                                                                                                    |

| 17      | TEST       | l            | Connect to the ground directly (only for the test).                                                                                                                                                                                           |

| 18      | REG_PLL_C  | _            | Connect a bypass capacitor for internal regulator stabilization.                                                                                                                                                                              |

| 19      | GND_PLL    | 1            | Ground for PLL. Connect to GND.                                                                                                                                                                                                               |

| 20      | GND_VCO    | _            | Ground for VCO. Connect to GND.                                                                                                                                                                                                               |

| 21      | REG_VCO_C  | _            | Connect a bypass capacitor for internal regulator stabilization.                                                                                                                                                                              |

| 22      | CE         | I            | "1" setting means Transmission/Reception is enabled. After the power is supplied, this pin should be set to "0". And then set to "1". (Refer to 7.11.2.)                                                                                      |

| 23      | WAKE_UP    | 0            | When 14-kHz Wakeup signal is detected, this pin outputs "1." Also when the Wakeup function is re-set up, this pin outputs "1."                                                                                                                |

| 24      | REG_WU_C   | _            | Connect a bypass capacitor for internal regulator stabilization.                                                                                                                                                                              |

| 25      | IREF_C     | _            | Connect an external capacitor for Wakeup detection.  Note; The characteristics of this pin is affected by the value of the connected capacitor. Use a ceramic capacitor, and pay attention to condensation or dust to avoid the leak current. |

| 26      | DCFB       | _            | Connect an external capacitor for Wakeup detection.  Note; The characteristics of this pin is affected by the value of the connected capacitor. Use a ceramic capacitor, and pay attention to condensation or dust to avoid the leak current. |

| 27      | GND_RF1    | _            | Ground for RF blocks. Connect to GND.                                                                                                                                                                                                         |

| 28      | RF_IN      | I            | RF signal input. The input impedance is 50-Ω (Typ.).                                                                                                                                                                                          |

| 29      | GND_RF2    |              | Ground for RF blocks. Connect to GND.                                                                                                                                                                                                         |

| 30      | RFOUT1     | 0            | RF signal output 1. Connect to a 50-Ω impedance signal line.                                                                                                                                                                                  |

| 31      | RFOUT2     | 0            | RF signal output 2. Connect to a 50-Ω impedance signal line.                                                                                                                                                                                  |

| 32      | GND_RF3    | _            | Ground for RF blocks. Connect to GND.                                                                                                                                                                                                         |

8

Note: In the table above, "1" means the supply voltage level and "0," the ground level.

2017-09-19

# 7. Functional Description

# 7.1 Power Supply

The power supply voltage of this product is in the range of 1.8 V to 3.6 V.

VDD pin should be connected to not only the power supply but also a bypass capacitor to reduce noises.

In this product, internal regulators deliver the voltage sources.

In Figure 4-1, "REG" boxes represent the regulators.

Circuits to control Wakeup operation (PMU, WAKEUP DET and WU REG in Figure 4-1) are always "ON" while the power is supplied.

The other circuits are controlled by the power supply voltage from the internal regulators.

## 7.2 RF Frequency

This product has a fractional PLL.

The internal oscillator consists of the fractional PLL, VCO, and the crystal oscillator circuit for PLL reference signal.

The oscillation frequency can be set to the value in the range of 5725 MHz to 5875 MHz via SPI bus.

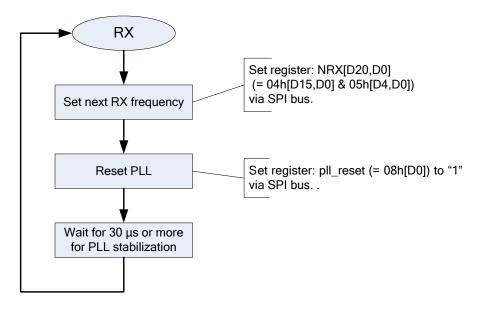

#### (1) Reception frequency setting

The difference between the reception frequency and the LOCAL frequency should be set to +/-5 MHz.

Either Upper LOCAL or Lower LOCAL can be selected according to the application system or the radio surroundings.

The frequency calculation is shown as follows:

```

\begin{aligned} f_{\text{OPR}}RX &= f_{\text{LO}} + /-5 \text{ (MHz)} \\ NRX[D20,D0] &= f_{\text{LO}} \text{ (MHz)} \times 125 \\ &= NRX[D20] \times 2^{20} + NRX[19] \times 2^{19} + \cdots + NRX[D2] \times 2^{2} + NRX[D1] \times 2^{1} + NRX[D0] \times 2^{0} \\ f_{\text{CPR}}RX &= f_{\text{CPR}} + f_{\text{CPR}}RX[D1] \times 2^{1} + NRX[D1] \times 2^{1} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX &= f_{\text{CPR}}RX[D1] \times 2^{1} + NRX[D1] \times 2^{1} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{1} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} \times 2^{0} + NRX[D1] \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} \times 2^{0} + NRX[D1] \times 2^{0} \times 2^{0} + NRX[D1] \times 2^{0} \times 2^{0} \\ &= f_{\text{CPR}}RX[D1] \times 2^{0} \times 2

```

$f_{OPR}RX$  is the reception frequency.  $f_{LO}$  is the LOCAL frequency which is set by the register NRX[D20,D0] (= 04h[D15,D0] and 05h[D4,D0]).

The sign "+/-" depends on the selection of the Upper LOCAL or Lower LOCAL frequency.

The initial value of the reception LOCAL frequency is 5835 MHz.

If the reception local frequency is not set to the register, the PLL is locked to 5835 MHz and this IC can receive both Ch1 (5830 MHz) and Ch2 (5840 MHz) after CE pin becomes "1".

The register setting is necessary to receive another frequency signal.

After a target frequency is set in NRX register, the register pll\_reset (= 08h[D0]) should be set to "1" (refer to 8.9). Then the PLL locks at the frequency.

After that, it is not necessary to write "0" to the register pll reset (= 08h[D0]).

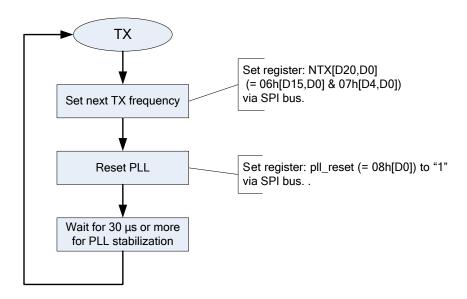

#### (2) Transmission frequency setting

For a transmission frequency, a target frequency should be directly set.

```

\begin{split} f_{OPR.}TX &= f_{LO} \text{ (MHz)} \\ NTX[D20,D0] &= f_{LO} \text{ (MHz)} \times 125 \\ &= NTX[D20] \times 2^{20} + NTX[D19] \times 2^{19} + \cdots + NTX[D2] \times 2^2 + NTX[D1] \times 2^1 + NTX[D0] \times 2^0 \\ f_{OPR.}TX \text{ is the transmission frequency. } f_{LO} \text{ is the internal frequency which is set by the register NTX[D20,D0] (= 06h[D15,D0] \text{ and } 07h[D4,D0]).} \end{split}

```

The initial value of the transmission frequency is 5790 MHz.

When the data reception changes to the data transmission, the PLL is locked to the transmission frequency.

In order to change the transmission frequency, the register pll\_reset should be set to "1", after a target frequency is set to the register NTX. After that, it is not necessary to write "0" to the register pll\_reset (= 08h[D0]).

# 7.3 System Clock generation

This product contains a crystal oscillator circuit. 32.768-MHz crystal oscillator should be used.

Heavy load capacity of the crystal oscillator may be the cause of slower oscillation starting. So, the crystal oscillator should be selected after enough evaluation on the system.

This datasheet shows the data values measured by using an evaluation board contained the crystal oscillator which is recommended.

## 7.4 Wakeup Operation

PMU and WAKEUP DET blocks are used for Wakeup operation.

PMU and WAKEUP DET are always "ON".

PMU controls the operation of this product.

WAKEUP DET can detect a 14-kHz waveform in the 5.8-GHz frequency band.

PMU and WAKEUP DET operate with the clock which is generated by an internal oscillator. So, no special oscillators for them are necessary.

### 7.5 RF Demodulation

A received signal is demodulated.

In Modem mode, the signal is decoded by the FIFO modem and stored in a register. The data can be output from SPI bus.

In Direct mode, the demodulated signal is output asynchronously from INTRPT/DIO pin.

For the details of these Modem modes, refer to 7.7.

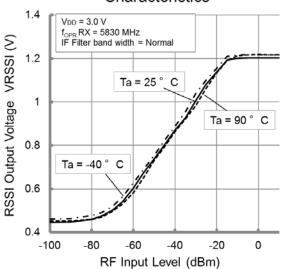

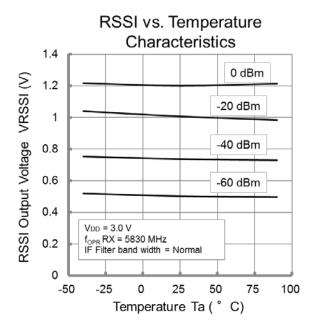

RSSI outputs a voltage level corresponding to the dB level of the input signal.

## 7.6 RF Modulation

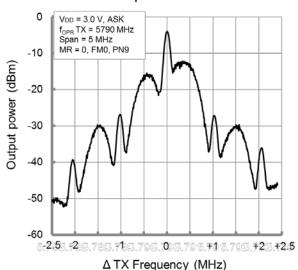

This product modulates the amplitude of the input signal and outputs the modulated signal from RFOUT 1 and RFOUT 2 pins as a high-frequency signal.

In Modem mode, when data is input from SPI bus, the data can be coded by the FIFO modem.

In Direct mode, when data is input from INTRPT/DIO pin, the data can be modulated.

The data coding cannot be done in Direct mode. A transmission data should be input as it is.

For details of these Modem modes, refer to 7.7.

The detail settings for the ASK modulation waveform in this IC is set to a register via SPI bus.

#### 7.7 MODEM

This product has two Modem modes as follows. The Modem modes can be selected by the registers dio\_sel and dio\_en (refer to 8.4). In Figure 4-1, the Modem is shown as FIFOMODEM.

#### (1) Modem Mode

In this mode an internal Modem of this IC is used. Full functions of this IC can be used and no external modem devices are necessary. In this mode, data input and output are done via SPI bus. INTRPT/DIO pin is used for an interrupt.

#### (2) Direct Mode

When the internal modem functions in this IC are not necessary, Direct mode should be set.

An external modem device should be prepared.

In this mode, INTRPT/DIO pin is used for data input and output.

The modem in this IC has following functions.

#### Reception:

- (1) Bit synchronization by a preamble

- (2) FM0 decoding

- (3) Frame detection by a frame start mark

- (4) Abort detection

- (5) ZERO detection

- (6) Generation of the frame length of the second layer in the information frame by a frame end mark

- (7) Error detection by CRC16

- (8) Clock recovery

- (9) Determination of a non-standard bit length of a reception signal

#### Transmission:

- (1) ZERO insertion

- (2) Addition of a frame start and a frame end marks

- (3) Addition of a preamble and a postamble

- (4) FM0 encoding

- (5) Frame check (CRC16)

# 7.8 System Control and Data Communication

The functions of this product are controlled by the combination of SPI bus and specified pin signals.

The function of the chip enable is controlled by CE pin.

If CE pin stays in "0," the control via SPI bus is disabled.

The settings via SPI bus should be done after the CE pin is set to "1."

The switching between the transmission and the reception is done by either the setting of TXRX pin or the register setting via SPI bus.

# 7.9 State Transition Diagram

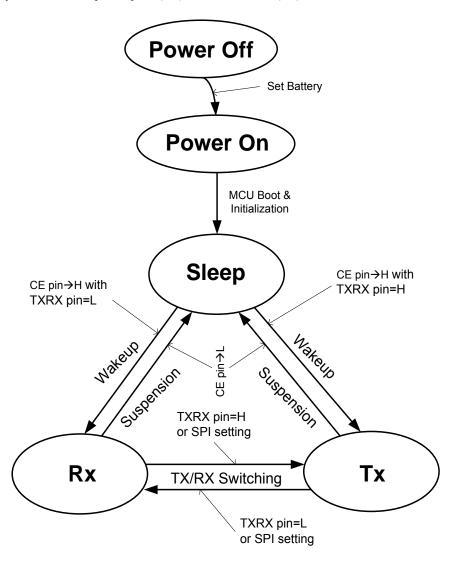

This product has mainly three states, Sleep, Reception (RX), and Transmission (TX).

Figure 7-1 State Transition Diagram of TC32169FTG

# 7.10 State Description

#### 7.10.1 Power Off and Power On States

In Power Off State, the power is not supplied to the OBU of ETC.

All functions stop because no power is supplied.

In Power On State, the power is supplied to the OBU of ETC.

The power is supplied to this IC and it is initialized.

## 7.10.2 Power On State to Sleep State

The MCU is waiting for the boot of itself.

The boot sequence for the MCU is supposed as follows: At first MCU is reset and initialized. Then MCU's pin assignment, I/O conditions and functions are set. Finally the MCU controls this IC.

After this product is reset and initialized by the MCU, this product enters one of the states, Sleep, RX or TX.

When this product is used on an OBU, Sleep state is recommended.

Note: CE pin should be kept "0" for 600 µs or more before it is set to "1" to initialize this IC surely. For details, refer to 7.11.2.

## 7.10.3 Sleep State

Only the Wakeup detection blocks of this product (PMU, WAKEUP DET and WU REG) are active.

The following instructions can execute:

Wakeup sensitivity setting, the number of cycles to start up the Wakeup signal, and the selection of Normal Wakeup or Auto Wakeup.

Other blocks of this IC are not supplied with power to reduce current consumption.

The external MCU is supposed to be in an idle state (a call sleep state, a low power state, and others) and is waiting for Wakeup interrupt from this IC.

The registers of PMU and WAKEUP DET keep their data during Sleep state.

#### 7.10.4 RX State

This product can receive ASK or OOK modulated RF signal.

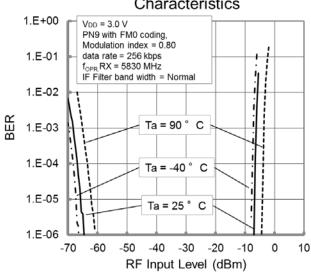

It can receive FM0 encoded 512 or 256-kbps ASK or OOK modulated RF signal at 5.8-GHz frequency band.

When TXRX pin is set to "0," this IC becomes RX State.

If using the register setting, the register  $TXRX_{en} (= 01h[D1])$  shound be set to "0" or the combination is done such as the register  $TXRX_{en}$  should be set to "1" and the register TXRX (= 01h[D0]), "0."

After that, this IC starts detecting the frame of the physical layer.

When the frame of the physical layer is detected, the information frame without FCS (<u>Frame Check Sequence</u>) is stored in the register TRXFIFO (= 10h[D2047,D0]). And rx ready interrupt is asserted to the external MCU.

Note: The stored reception data in the register TRXFIFO should be read out. After the register becomes full with the reception data, a new reception data is overwritten and the previous data disappears. To avoid this, the register dettimer\_dis (= 36h[D0]) is useful. It can control the flag error timer. The timer value is 2 ms. The stored data can be read during this 2 ms.

Note: If the FIFO data has been overwritten unintentionally, the register clr\_fifo (= 43h[D8]) should be set to "0" to clear the register TRXFIFO.

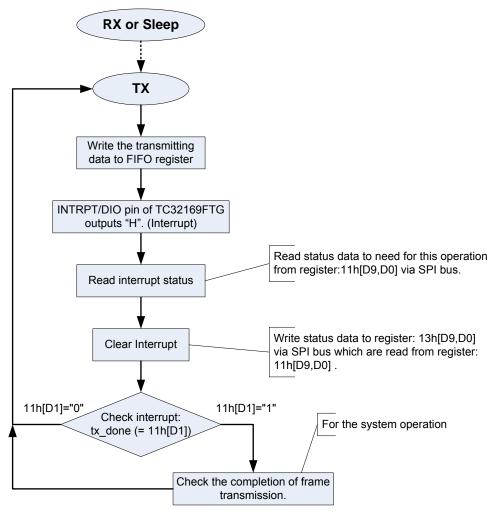

#### 7.10.5 TX State

This product can transmit ASK or OOK modulated signal.

It transmits FM0 encoded 512 or 256-kbps ASK or OOK modulated RF signal at 5.8-GHz frequency band.

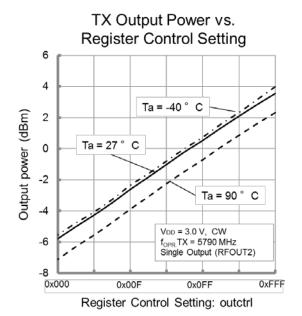

Maximum RF output level is +3 dBm (Typ.).

When TXRX pin is set to "1," this IC becomes TX State.

If using the register setting, the register  $TXRX_en (= 01h[D1])$  shound be set to "0" or the combination is done such as the register  $TXRX_en$  should be set to "1" and the register TXRX (= 01h[D0]), "1."

After a transmission data is stored in the register TRXFIFO, the data transmission can start.

After transmission completes, tx done interrupt is asserted to MCU.

#### 7.10.6 Transition between RX State and TX State

In order to transit between RX state and TX state, TXRX pin is used or the combination of the register TXRX and the register TXRX\_en is used. The selection is done by the register (0hXX).

When TXRX pin is used, the input data should be kept at least 1.3 µs to transit between TX state and RX state. Otherwise, the initialization of the PLL may not be done correctly and malfunction occurs.

It should be considered that PLL lock-up time which is approximately 30 µs is not included in the interval.

Appropriate frequencies should be set to the registers NRX and NTX just before the transition.

Whenever the transition between TX state and RX state occurs, the register TRXFIFO is cleared automatically.

Note: The signal durations described above depend on the frequency of the crystal oscillator.

# 7.11 Sequence Description

The abstract of the sequences for TC32169FTG is described here to implement suitable control. For details of the sequences, refer to 7.12 Flowchart Examples.

### 7.11.1 Chip Select and Reset

In the following cases, the chip enable and reset operations should be considered carefully.

- Periodic refreshing to recover from a register error caused by the cosmic ray, external noises, and others.

- Occurrence of unexpected operation in the system.

- Notice of an error from the interrupt register.

- No expected data can be acquired from the FIFO after receiving RF signal. Or reception failure occurs.

Some resets, such as PLL reset, will be used in the control routine of ETC.

It is also called the reset of Wakeup functon that the output setting of WAKE\_UP pin is reset and this product enters Sleep state.

The explanation of the chip enable and the reset of this IC is described in Table 7-1.

**Table 7-1 Chip Enable and Reset**

| Item              | Description                                                                                                                                          | Use Condition                                                                                                                                                                                                                            | Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wakeup<br>Reset   | Reset and initialization of Wakeup function. The initialization by this reset means to calibrate Wakeup detection timer to detect a 14-kHz waveform. | Wakeup function becomes available by this reset. That is, it is available in the following cases.  - before entering Sleep state to prepare the next transmission.  - after a fatal trouble occurs.  - after a reception failure occurs. | Mandatory.  Set the register wk_clr (=1Bh[D8]) to "1" to change WAKE_UP pin output from "1" to "0."  Recommended.  Set the register wk_reg_wen (= 1Ch[D8]) to "1". After the reset, the data of the register wk_reg_wen automatically returns to "0" (the initial value).  For initialization, set the register wkcal_en (= 1Ah[D8]) to "1" while Wakeup function's reset is asserted.  Set the registers w_s_set (=0Bh[D3,D0]), wk_num (=18h[D3,D0]), and autowk (=19h[D0]). Those register data are copied to registers in PMU and WAKEUP DET by setting the register wk_reg_wen to "1".  After copying the data, the register data in PMU and WAKEUP DET become valid. |

| Chip<br>Enable    | This IC enters Convergence state* after the power is suppled.  To escape from the state, the chip enable function should be                          | This chip enable shuold be asserted at the first connection of a battery (a voltage supply), after the ETC application system implementing this IC is manufactured.                                                                      | Keep CE pin to "0" for 600 μs or more after the power is supplied. Then, change CE pin from "0" to "1."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                   | controlled with CE pin input.                                                                                                                        | ETC system should be reset after a fatal trouble occurs.                                                                                                                                                                                 | Keep CE pin to "0" for 20 μs or more. Then, change CE pin from "0" to "1".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Software<br>Reset | All registers and modems are reset. The registers are initialized.                                                                                   | The software reset is asserted during transition from Power On state to Sleep/TX/RX state. It is also asserted at the following cases At the refreshing of registers When the MCU detects an error or an abnormal situation.             | Set the register RST (= 00h[D7]) to "1."  After the reset, the data of the register RST automatically returns to "0" (the initial value). The modem can also be reset by CE pin operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PLL<br>Reset      | PLL circuit starts up and the PLL locks on the expected frequency.                                                                                   | - At changing between RX state and TX state.  - At changing RF frequency.                                                                                                                                                                | Set the register PLL_RST (= 08h[D0]) to "1." PLL reset register is a trigger to initialize PLL circuit.  After that, it is not necessary to write "0."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Note: For details of Convergence state\*, refer to 7.11.2.

Note: The signal durations described in this table depend on the frequency of the crystal oscillator.

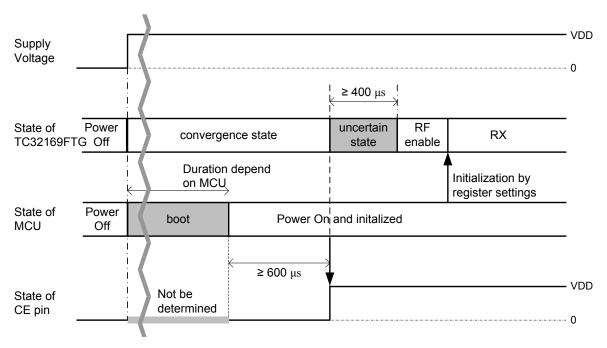

## 7.11.2 Operation after Power Supply

The ETC application system including TC32169FTG and MCU as a controller executes a system start routine after the power is supplied. "System" means here the unit which consists of this product and MCU as a controller.

At first, the reset should be asserted properly to both this IC and MCU to initialize them.

After the power is supplied, the states of this IC and MCU are indefinite. (The reset and initialization in the start routine of MCU is called "Boot.")

The MCU should reset and initialize (boot) itself after the supply voltage reaches the operation voltage of this product.

On the other hand, the state of PMU and WAKEUP DET in this IC is undefined (Sleep state, TX state, or RX state) after the power is supplied. MCU should set CE pin of this IC to "0" for 600 µs or more to determine the state of this IC. During the 600 µs duration this product is started up. Then this IC enters indefinite state temporarily.

The indefinite state means that the logical state of PMU and WAKEUP DET is indefinite, and it continues until the reset and the initialization by register setting are done.

Before the initialization is done by the register setting, MCU should wait 400 µs or more after the CE pin reset is deasserted. An example of the timing chart of the system start sequence is shown below.

Figure 7-2 Example of a timing chart about System starting

15

Note: Signal durations described in this figure depend on the frequency of the crystal oscillator.

Note: Operations of this IC cannot be guaranteed without keeping time relationships between the signals expressed in the figure.

## 7.11.3 Wakeup Function

This product has a Wakeup function to detect a 14-kHz waveform in 5.8-GHz frequency band.

When a 14-kHz Wakeup signal is detected, WAKE UP pin outputs "1" in Normal Wakeup mode.

After WAKE UP pin outputs "1," this IC status should be checked via SPI bus, and then, the target settings should be done.

This IC supports Auto Wakeup function for MLFF when this product is used for ETC.

When Auto Wakeup function is selected, this IC can automatically start data reception after receiving 14-kHz Wakeup signal. And this IC can receive 5830 and 5840-MHz signal simultaneously without any external control.

When the reception completes correctly, the data is stored in FIFO register and is kept there.

If CE pin turns to "1," the reception data is discarded.

The setting which Wakeup sequence is used should be done to a register via SPI bus while CE pin is "1" as follows.

To set Normal Wakeup, the register autowk (= 19h[D0]) should be set to "0" in the initialization of PMU and WAKEUP DET.

If the register has not been written, the initial value is "0" which selects Normal Wakeup.

To set Auto Wakeup, the register autowk (= 19h[D0]) should be set to "1" in the initialization of PMU and WAKEUP DET.

Before entering Sleep state, Wakeup setting data should be transmitted (write-back) to the register for PMU and WAKEUP DET. The selected Wakeup function becomes valid.

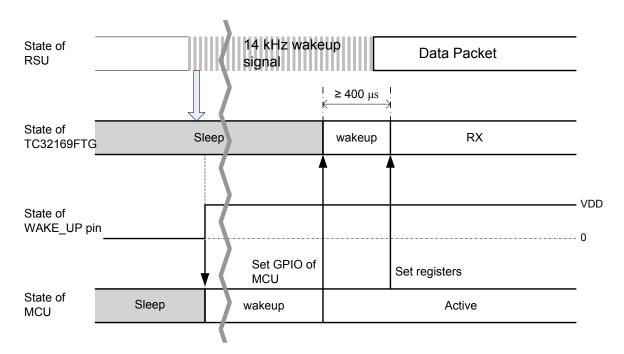

#### (1) Normal Wakeup

This function is available only while CE pin is "0."

When Normal Wakeup is set, WAKE\_UP pin outputs "1" when a 14-kHz Wakeup signal is detected.

The signal should be a trigger for this IC to be controlled by MCU. The system start-up time is the sum of the start-up times of this IC and MCU in Normal Wakeup operation.

Figure 7-3 Normal Wakeup

16

Note: Signal durations described in this figure depend on the frequency of the crystal oscillator.

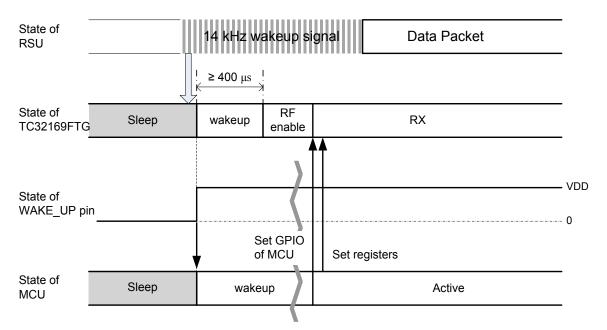

#### (2) Auto Wakeup

When Auto Wakeup is set, WAKE\_UP pin outputs "1" when a 14-kHz Wakeup signal is detected, regardless of CE pin value. This product becomes active and XOSC oscillation starts.

This IC will automatically return to Auto Wakeup if CE pin stays "0" for 20  $\mu$ s or more after WAKE\_UP pin becomes "1." This IC and MCU can start up in parallel in Auto Wakeup mode.

So the total time of the start-up can be shortened.

And the current consumption of the system can be reduced

Figure 7-4 Auto Wakeup

17

Note: Communication between MCU and TC32169FTG should start after finishing those Wakeup durations.

Note: Signal durations described in this figure depend on the frequency of the crystal oscillator.

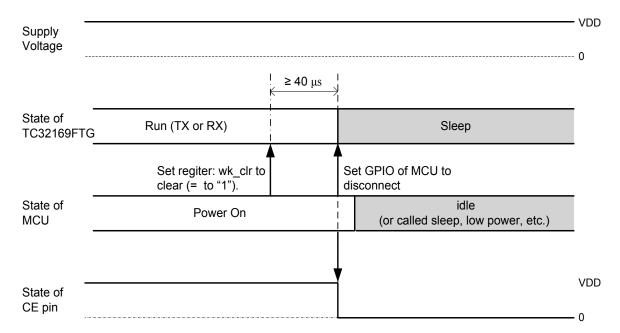

## 7.11.4 Suspension

When CE pin turns to "0," this IC enters Sleep state regardless of the register settings.

Before entering Sleep state or when staying in TX state or RX state, Wakeup function which is used in Sleep state should be set, then CE pin should be changed to "0."

This is called "write-back to Wakeup register." If this write-back is omitted, the Wakeup function may not operate correctly at the next Wakeup signal input.

The timing chart of Suspension is shown in Figure 7-5.

Before MCU enters Sleep state, it should set the register wk\_clr (= 1Bh[D8]) to "1."

Then, WAKE UP pin outputs "0" for 40 µs or more.

After that, CE pin should be set to "0."

Following reset and initialization of Wakeup function should be done during TX/RX state.

- Set the register wk reg wen (= 1Ch[D8]) to "1."

- Set the register wkcal en (= 1Ah[D8]) to "1."

- Set the register w s set (= 0Bh[D3,D0]) to the expected value for the application system.

- Set the register wk num (= 18h[D3,D0]) to the expected value for the application system.

- Set the register autowk (= 19h[D0]) to the expected value according to the type of Wakeup (Normal/Auto).

In addition, the reset and initialization of Wakeup function is useful at the occurrence of a reception failure. For the reset and initialization, also refer to Table 7-1.

Note: If CE pin is set to "0" before WAKE\_UP pin turns to "0", WAKE\_UP pin output keeps "1" during Sleep state. As a result, the operation of WAKE\_UP pin will fail when the next reception starts.

Note: In order not to fail the next reception, MCU should check the output of WAKE UP pin before entering Idle state.

Figure 7-5 Sleep timing diagram

Note: The reset and initialization of Wakeup function described in this section should also be executed, which is not shown in the figure. Note: Signal durations described in this figure depend on the frequency of the crystal oscillator.

18

#### 7.11.5 Use of Modem in TX/RX

This product has 4 combinations of Modem operations (Modem mode / Direct mode) and TX/RX states.

#### (1) Modem Mode and RX State

Modem mode is selected via SPI bus and RX state is also selected by TXRX pin or SPI setting. After completing to receive data, this IC stops data reception, INTRPT/DIO pin (used for an interrupt) becomes "1," and an interrupt is generated. The type of the interrupt can be checked via SPI bus. The reception data can also be read out via SPI bus. When the interrupt completes, this IC re-starts data reception.

If TXRX pin is "0" and the setting is the default one, RF frequency of 5830 MHz or 5840 MHz is automatically received. To receive another frequency signal, the setting of the reception internal frequency and PLL setting should be changed properly.

#### (2) Modem Mode and TX State

Modem mode is selected via SPI bus and TX state is also selected by TXRX pin or SPI setting. For starting transmission, the transmission frequency should be set via SPI bus and the transmission data should be written to the transmission data register. 5790-MHz RF signal is transmitted in the default setting in this IC.

After completing to transmit data, this IC stops data transmission, INTRPT/DIO pin (used for an interrupt) becomes "1," and an interrupt is generated. The type of the interrupt can be checked via SPI bus. It is recommended that the next transmission should be done after the generation of the interrupt is confirmed. After the next transmission data is written to the transmission data register, this IC can re-start transmitting.

#### (3) Direct Mode and RX State

Direct mode is selected via SPI bus and RX state is also selected by TXRX pin or SPI setting. This IC outputs a bit stream of the received ASK/OOK RF signal from INTRPT/DIO pin (used for DIO pin). A large amplitude of RF signal of ASK/OOK causes the output "1" from INTRPT/DIO pin, and a small amplitude of RF signal of ASK/OOK causes the output "0."

If TXRX pin is "0" and the setting is the default one, RF frequency of 5830 MHz or 5840 MHz is automatically received. To receive another frequency signal, the setting of the reception internal frequency and PLL setting should be changed properly.

The bit rate of transmission RF output is a fixed value (512/256 kHz) or a divided value (an integer) of 512 kHz.

#### (4) Direct Mode and TX State

Direct mode is selected via SPI bus and TX state is also selected by TXRX pin or SPI setting. This IC can output RF signal. "1" input to INTRPT/DIO pin generates a large amplitude output of ASK/OOK RF signal, and "0" generates a small amplitude output of ASK/OOK RF signal.

The bit error rate of the received RF signal can be measured in this mode.

#### 7.11.6 Interrupt

The signal of an interrupt is output from INTRPT/DIO pin. When an interrupt is asserted, the interrupt register should be read to identify the type of the interrupt.

The interrupt signal is a level sense one, not an edge sense one. So MCU should detect a level sense interrupt.

There are 10 interrupts asserted to MCU.

When rx ready, pre err, flag err, rxlen err, fm0 err, crc ng, rx abort, or post err interrupt is asserted, data reception re-starts with the preamble detection. When txlen\_err or tx\_done interrupt is asserted, MCU should clear these interrupts to transmit the next frame. The purpose of each interrupt is described as follows. For the register map, refer to 8.14.

Note: Interrupt Mask

Each interrupt is maskable separately. If an interrupt mask is set, the corresponding output of INTRPT/DIO pin is masked. An interrupt operation still executes even though the interrupt mask is set. For the register map, refer to 8.15.

Note: Clearing of Interrupt

Each interrupt can be cleared separately. The output of INTRPT/DIO pin becomes "0" after all asserted interrupts are cleared. The interrupt register should be checked to prepare the next interrupt. For the register map, refer to 8.16.

Note: Interrupt Polarity

The polarity of INTRPT/DIO output signal for the interrupts can be selected by the register int\_inv. In this document, the assertion of an interrupt is assumed to "1" output of INTRPT/DIO pin. For the control of the interrupt polarity, refer to 8.17.

Table 7-2 Interrupt types

Register

| Item      | Address | Description                                                                                                                                                                                         |  |

|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| rx_ready  | 11h[D0] | When the 2nd layer of the information frame is received correctly, rx_ready interrupt is asserted. MCU can read the 2nd layer of the information frame from TRXFIFO.                                |  |

| tx_done   | 11h[D1] | When the transmission of a frame completes, tx_done interrupt is asserted. tx_done interrupt should be cleared for MCU to transfer the next frame.                                                  |  |

| pre_err   | 11h[D2] | If no preambles are detected within 2 ms in RX state, pre_err interrupt is asserted.                                                                                                                |  |

| flag_err  | 11h[D3] | If no frame start marks are detected within 2 ms in RX state, flag_err interrupt is asserted.                                                                                                       |  |

| rxlen_err | 11h[D4] | When the reception frame length is larger than the value in the register (Address: 17h), rxlen_err interrupt is asserted.                                                                           |  |

| fm0_err   | 11h[D5] | If FM0 decoder error occurs during data reception, fm0_err interrupt is asserted.                                                                                                                   |  |

| crc_ng    | 11h[D6] | If the result of CRC check is incorrect, crc_ng interrupt is asserted.                                                                                                                              |  |

| rx_abort  | 11h[D7] | When an abort pattern is detected during frame reception, rx_abort interrupt is asserted.                                                                                                           |  |

| post_err  | 11h[D8] | When the postamble detection option is active, this interrupt can be asserted. If no postambles are detected, post_err interrupt is asserted. The postamble is not detected in the default setting. |  |

| txlen_err | 11h[D9] | If the transmission frame length is irregular, txlen_err interrupt is asserted. The irregular length means that the length is not the byte unit or the length is less than 2 bytes.                 |  |

# 7.12 Flowchart Examples

The flowcharts for MCU are described here.

As an example, the flowcharts for China's ETC system are described.

Those examples use the initial register settings as much as possible.

In the following flowcharts, only the registers necessary for explanation are described.

For a different system, necessary registers may be different. The registers should be set according to Section 8 "Register Overview and Detail Description."

Note: Signal durations described in the following flowcharts depend on the frequency of the crystal oscillator.

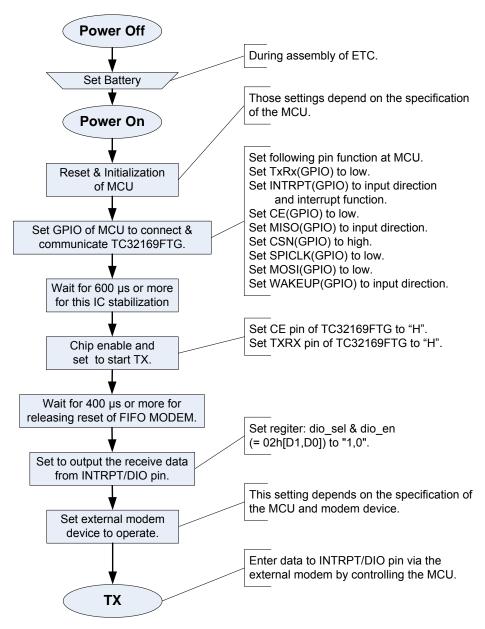

### 7.12.1 Power On State to TX State (Direct Mode)

Direct mode is selected via SPI bus and TX state is also selected by TXRX pin or SPI setting. A modulated signal should be input to INTRPT/DIO pin (used for DIO pin).

Figure 7-6 Flowchart of Power On state to TX state (Direct mode)

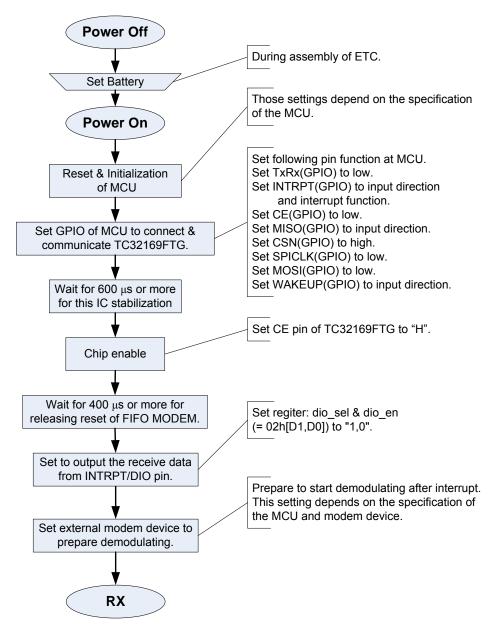

### 7.12.2 Power On State to RX State (Direct Mode)

Direct mode is selected via SPI bus and RX state is also selected by TXRX pin or SPI setting. This IC outputs a bit stream of the received ASK/OOK signal from INTRPT/DIO pin (used for DIO pin).

Figure 7-7 Flowchart of Power On state to RX state (Direct Mode)

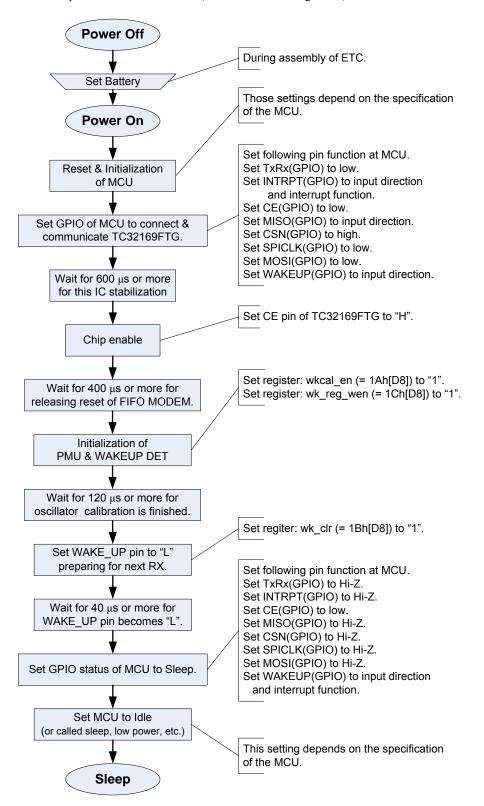

## 7.12.3 Power On State to Sleep State to Prepare RX State (Normal/Auto Wakeup)

A conventional sequence which sets up Sleep state to prepare RX state is described here. This IC has two ways to start receiving a signal, Normal Wakeup and Auto Wakeup. This flow contains both. (Refer to the following notes.)

Figure 7-8 Power On state to Sleep state to prepare RX state (Normal or Auto Wakeup)

Note: In order to start Auto Wakeup operation in RX state, it is necessary to set the register autowk (= 19h[D0]) to "1" at the initialization of PMU and WAKEUP DET.

Note: "Hi-Z" means high impedance. This setting reduces leakage current.

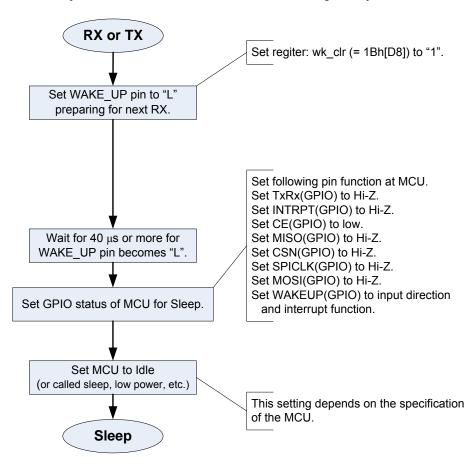

## 7.12.4 Suspension

When CE pin turns to "0," this IC enters Sleep state.

The register settings are ignored.

The preparation of the next reception or transmission should be done before executing the suspension.

Figure 7-9 TX/RX state to Sleep state

Note: When Wakeup operation is changed, the register autowk (= 19h[D0]) should be updated here.

Note: Before entering Sleep state, WAKEUP (GPIO) should be kept in an input to execute an interrupt surely.

Otherwise, MCU cannot be started up by WAKE\_UP pin output at the next reception.

Note: "Hi-Z" means high impedance. This setting reduces leakage current.

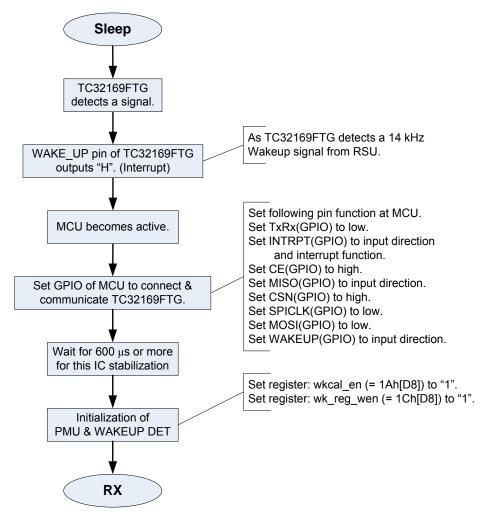

### 7.12.5 Sleep State to RX State (Normal Wakeup)

This product has a Wakeup function to detect a 14-kHz waveform in 5.8-GHz frequency band.

When a detected signal matches the expected signal, WAKE UP pin outputs "1."

There are two Wakeup operations, Normal Wakeup and Auto Wakeup.

In Normal Wakeup, MCU starts up this device when it sets CE pin to "1."

Figure 7-10 Transition from Sleep state to RX state by Normal Wakeup

25

Note: In the previous Suspension state, WAKEUP (GPIO) should be kept in an input to execute an interrupt surely. Otherwise, MCU cannot be started up by this Normal Wakeup sequence.

2017-09-19

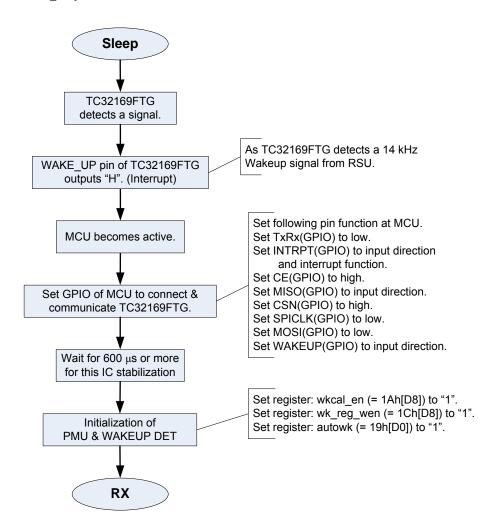

### 7.12.6 Sleep state to RX state (Auto Wakeup)

In Auto Wakeup sequence, this product becomes active automatically when a 14-kHz waveform in 5.8-GHz frequency band is detected and the detected signal matches the expected signal.

MCU starts up when WAKE UP pin becomes "1."

Figure 7-11 Transition from Sleep state to RX state by Auto Wakeup

Note: In the previous Suspension state, WAKEUP (GPIO) should be kept in an input to execute an interrupt surely. Otherwise, MCU cannot be started up by this Auto Wakeup sequence.

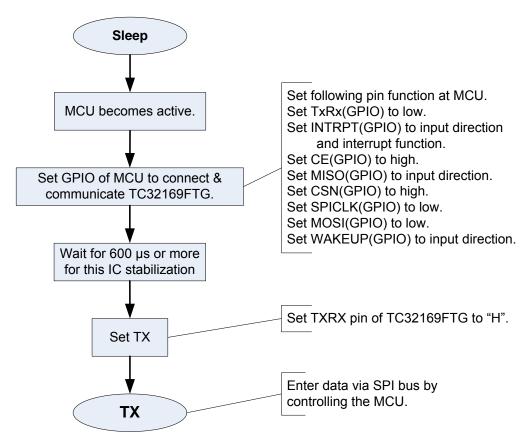

## 7.12.7 Sleep State to TX State

In the transition sequence from Sleep state to TX state, the MCU controls TC32169FTG and the application system.

Figure 7-12 Transition from Sleep state to TX state controlled by MCU

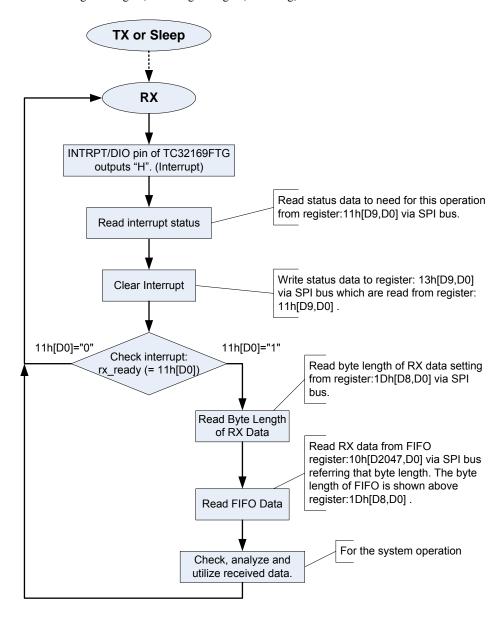

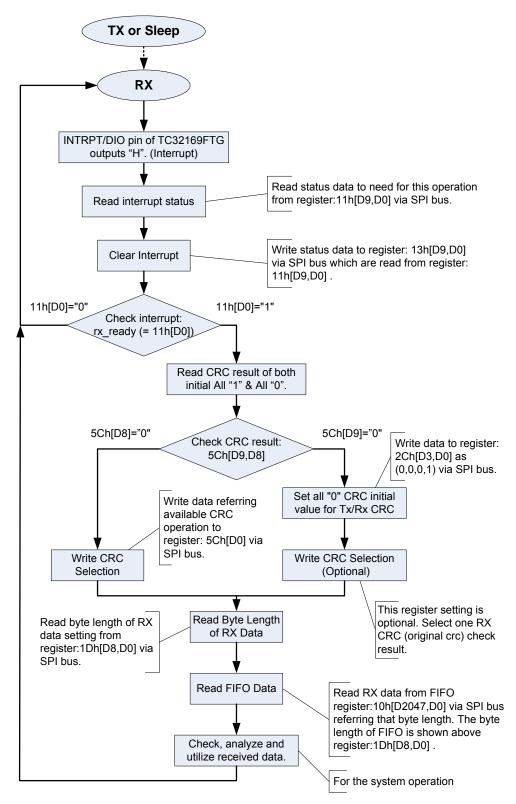

#### 7.12.8 RX State

The following flow shows waiting for a signal, receiving the signal, detecting, and data transmission to MCU.

Figure 7-13 Signal wait and reception

#### 7.12.9 RX State at BST Reception

As a special case, the following flow shows waiting for a signal, receiving the signal, detecting, and data transmission to MCU in Beijing's ETC system.

Figure 7-14 Signal wait and reception for BST reception (CRC rejection sequence in Beijing ETC System)

Note: rx\_ready interrupt can check that the register crc\_rslt\_b (= 5Ch[D9]) is "1" or the register crc\_rslt\_a (= 5Ch[D8]) is "1." Both cases are loop back paths. So, before CRC result is checked, it is necessary to set that neither cases should occur.

Note: For the detail of "Write of CRC Selection," refer to 7.15.

## 7.12.10 Reception Frequency Change

The following flow shows the sequence to change the reception frequency during RX state.

Figure 7-15 Reception frequency change during RX state

Note: The calculation of the reception frequency is shown in 7.2.

Note: When the initial reception frequency is not used, the PLL should be reset by setting the register NRX via SPI bus before starting data reception.

#### 7.12.11 TX state

The following flow shows the sequence of data transmission and MCU checking.

Figure 7-16 Sequence of data transmission and checking

## 7.12.12 Transmission Frequency Change

The following flow shows the sequence to change the transmission frequency during TX state.

Figure 7-17 Transmission frequency change during TX state

Note: The calculation of the transmission frequency is shown in 7.2.

Note: When the initial transmission frequency is not used, the PLL should be reset by setting the register NTX via SPI bus before starting data transmission.

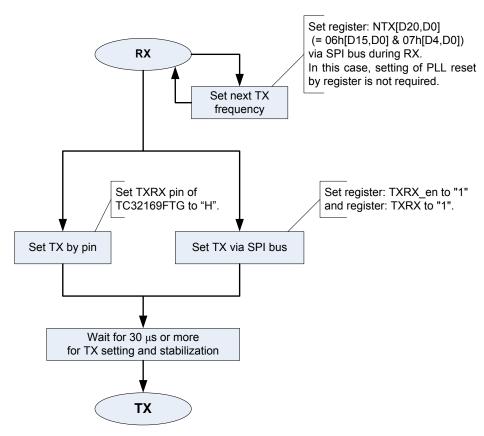

## 7.12.13 RX State to TX State

When the RF signal direction is changed, TXRX pin or SPI bus control is used.

Figure 7-18 RX state to TX state

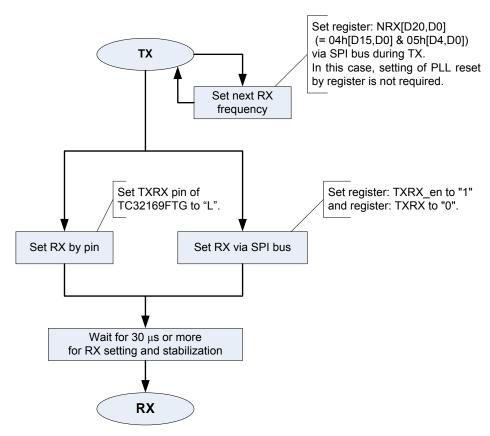

## 7.12.14 TX State to RX State

When the RF signal direction is changed, TXRX pin or SPI bus control is used.

Figure 7-19 TX state to RX state

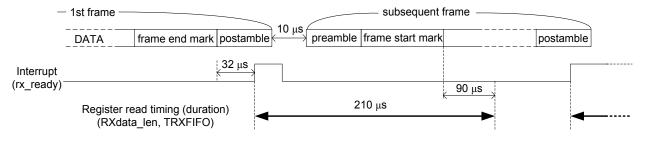

# 7.13 Sequential Reception of Downlink Frames

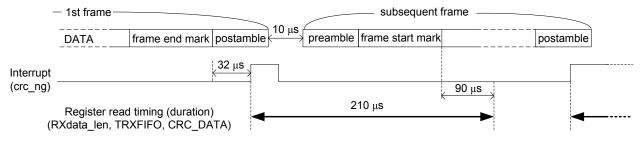

When two downlink frames are transmitted subsequently with the minimum interval ( $10 \mu s$ ), the read timing of the register for the reception data is shown as follows.

#### Case1:

Both the first frame and the subsequent frame are received.

Overwrite TRXFIFO by subsequent frame

Figure 7-20 TRXFIFO timing for two frame reception

The register RXdata\_len (= 1Dh[D8.D0]) and the register TRXFIFO (= 10h[D2047.D0]) have to be read in the interval between rx\_ready (= 11h[D0]) interrupt assertion and 90 µs after the head of the next transmission data (210 µs).

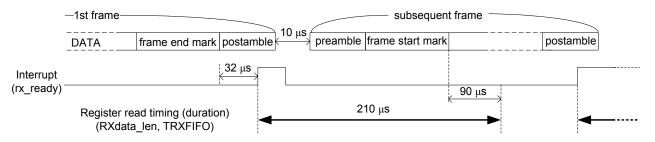

#### Case2:

Only the 1st frame is received. And TC32169FTG enters TX State.

Overwrite TRXFIFO by subsequent frame

Figure 7-21 TRXFIFO timing for one frame reception

The register RXdata\_len and the register TRXFIFO have to be read in the interval between rx\_ready interrupt assertion and 90  $\mu$ s after the head of the next transmitted data (210  $\mu$ s). When transiting to TX state, the register TRXFIFO is cleared.

## 7.14 Reception of CRC Error Frame

Even though CRC result is not correct, MCU can read the received frame and the CRC result if the frame end mark is correct. Reading method is the same as the case of the correct CRC result.

Overwrite TRXFIFO by subsequent frame

Figure 7-22 Reception of CRC error frame

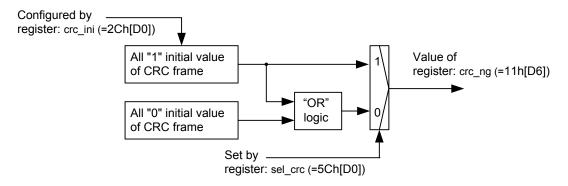

## 7.15 CRC Selection

When the register sel\_crc (= 5Ch[D0]) is set to "0" and the register crc\_inv/lsb\_msb/crc\_pol/crc\_ini (= 2Ch[D3,D0]) is set to (0,0,0,0), both CRC results whose initial values are all "1" and all "0" can be received. That means both CRC values are calculated simultaneously. "1" CRC check parameter can be set to the register crc\_ini (= 2Ch[D3,D0]). And the other CRC check parameters are determined according to the CRC result whose initial value is all "1."

The results of CRC calculation are stored to the registers crc\_rslt\_b and crc\_rslt\_a (= 5Ch[D9,D8]). Which CRC result should be used is decided after the registers crc\_rslt\_b and crc\_rslt\_a are read in rx\_ready interrupt sequence. When the register crc\_rslt\_b is "0," the CRC frame whose initial value is all "0" is received. When the register crc\_rslt\_a is "0," the CRC frame whose initial value is all "1" is received. According to the CRC results, the register crc\_ini (= 2Ch[D0]) should be set appropriately. When the register sel\_crc is set to "1," only "1" CRC check is effective, and the parameters for CRC with the initial value of all "0" become invalid. So the result of the CRC whose initial value is all "0" becomes incorrect. After the CRC selection, the register sel\_crc should be set to "1" to use only "1" CRC check. For the CRC selection, refer to Figure 7-23.

Figure 7-23 CRC selection

36

Note: The contents in 7.13, 7.14 and 7.15 are useful to construct a system for Beijing's ETC.

#### 7.16 Register Access for System Control

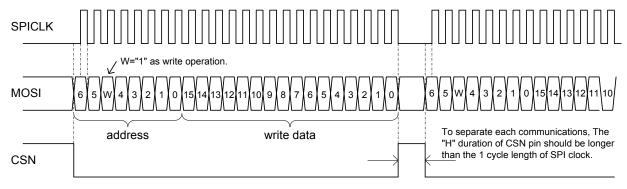

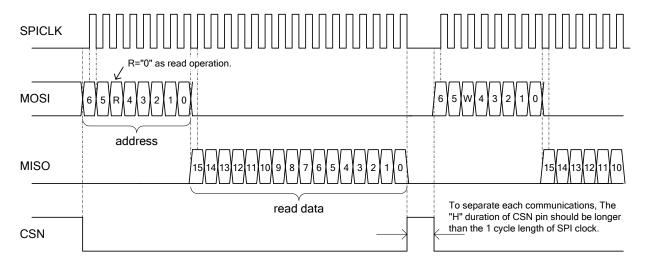

#### 7.16.1 SPI Control Data Format

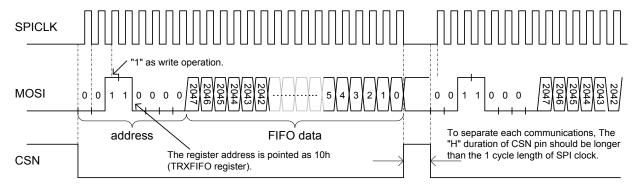

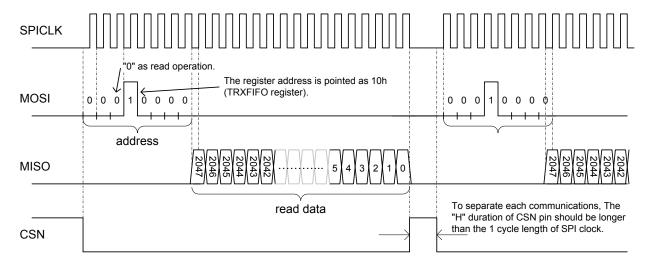

The conceptual diagrams of SPI control data format are shown as follows. The format consists of an address (8 bits) and a data (16 bits). The read or write is instructed in the value of the third bit. The bit "0" means data read and "1," data write. To separate each communication data, "1" duration which is 1-cycle or more length of SPI clock is inserted between the data.

#### (1) SPI Write Access Format

Figure 7-24 SPI write format

#### (2) SPI Read Access Format

Figure 7-25 SPI read format

The conceptual diagrams of SPI FIFO data format are shown as follows. The format consists of an address (8 bits) and a data (2048 bits). The length of FIFO data is an 8-byte unit. The data length is 128 bytes or less. The instruction of read or write and the separating each communication data are the same as those of SPI control data format. The address of the SPI FIFO data format is fixed to 10h (TRXFIFO register).

#### (3) SPI FIFO Data Write Access Format

Figure 7-26 SPI FIFO data write format

#### (4) SPI FIFO Data Read Access Format

Figure 7-27 SPI FIFO data read format

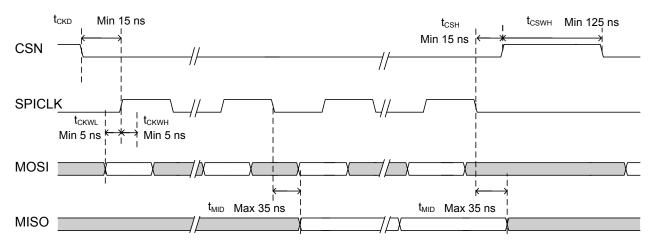

#### 7.16.2 SPI Signal Timing Specification

The conceptual diagrams of TC32169FTG's SPI signal timing specification is shown as follows. The figure shows the simplified operation for explanation.

The interrelationship among the signal timings should be compliant to specified values. The frequency of SPICLK should be 8 MHz or less not to fail the communication between this IC and MCU. The gray areas in the following figure show no influence on the communication.

Figure 7-28 SPI signal timing specification

| Item              | Symbol            | Min  | Тур. | Max   | Unit |

|-------------------|-------------------|------|------|-------|------|

| SPI CLK Frequency | f <sub>SPI</sub>  | 0.05 | 8.0  | 8.192 | MHz  |

| CLK "H" Time      | t <sub>CKWH</sub> | 5    | _    | _     | ns   |

| CLK "L" Time      | t <sub>CKWL</sub> | 5    | _    | 1     | ns   |

| CLK Delay Time    | t <sub>CKD</sub>  | 15   | _    | _     | ns   |

| CS "H" Time       | t <sub>CSWH</sub> | 125  | _    | _     | ns   |

| CS Hold Time      | t <sub>CSH</sub>  | 15   | _    |       | ns   |

| MISO Delay Time   | t <sub>MID</sub>  | _    | _    | 35    | ns   |

Table 7-3 SPI signal timing

Note: The values above should be used for the time values of SPI bus.

## 8. Register Overview and Detail Description

#### 8.1 Register Overview

The contents of Table 8-1 show the register overview in TC32169FTG for China's ETC application system. For the details, refer to the following sections.

**Table 8-1 Register Overview**

| Sec.        | Address | Function           | Name            | Used Bit   | R/W | Description                                            |  |  |

|-------------|---------|--------------------|-----------------|------------|-----|--------------------------------------------------------|--|--|

| <u>8.2</u>  | 00h     | SWRST              | RST             | D7         | W   | Software reset.                                        |  |  |

| <u>8.3</u>  | 01h     | TX RX Status       | TXRX_en         | D1         | W   | Select transmission or reception                       |  |  |

| 0.4         | 0.01-   | DIO ENADI E        | dio_sel         | D1         | R/W | Select the function of INTRPT/DIO pin.                 |  |  |

| <u>8.4</u>  | 02h     | DIO ENABLE         | dio_en          | D0         | R/W | Enable INTRPT/DIO pin.                                 |  |  |

| <u>8.5</u>  | 04h     | PLL_RX1            | NRX             | [D15,D0]   | R/W | Set the reception PLL frequency (LSB).                 |  |  |

| <u>8.6</u>  | 05h     | PLL_RX2            | NRX             | [D20,D16]  | R/W | Set the reception PLL frequency (MSB).                 |  |  |

| <u>8.7</u>  | 06h     | PLL_TX1            | NTX             | [D15,D0]   | R/W | Set the transmission PLL frequency (LSB).              |  |  |

| <u>8.8</u>  | 07h     | PLL_TX2            | NTX             | [D20,D16]  | R/W | Set the transmission PLL frequency (MSB).              |  |  |

| <u>8.9</u>  | 08h     | PLL_RST            | pll_reset       | D0         | W   | Reset of PLL block.                                    |  |  |

| <u>8.10</u> | 09h     | TX_Power_Control   | outctrl         | [D11,D0]   | R/W | Control of transmission power.                         |  |  |

|             |         |                    | bw              | D8         | W   | Select IF filter band width.                           |  |  |

| 0.44        | 0.45    | Analan Cattings    | ook             | D7         | W   | Select to use the anti-aliasing filter for modulation. |  |  |

| <u>8.11</u> | 0Ah     | Analog_Settings    | ph              | D6         | W   | Select RSSI peak hold operation.                       |  |  |

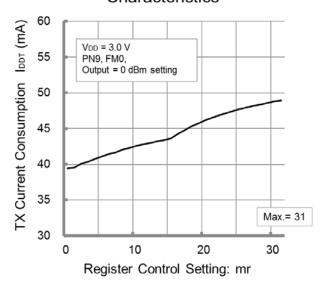

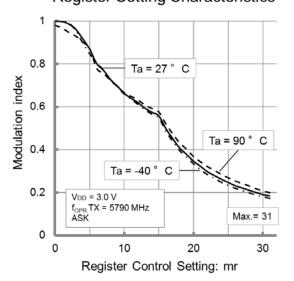

|             |         |                    | mr              | [D4,D0]    | W   | Set the modulation index.                              |  |  |

| <u>8.12</u> | 0Bh     | Analog_Settings_WU | w_s_set         | [D3,D0]    | R/W | Set Wakeup sensitivity.                                |  |  |

| <u>8.13</u> | 10h     | TRXFIFO            | txdata          | [D2047,D0] | R/W | Read/Write data of Transmission/Reception FIFO         |  |  |

|             |         |                    | txlen_err       | D9         | R   | Transmission frame length is invalid.                  |  |  |

|             |         |                    | post_err        | D8         | R   | No postambles are detected.                            |  |  |

|             |         |                    | rx_abort        | D7         | R   | Abort sequence is detected.                            |  |  |

|             |         |                    | crc_ng          | D6         | R   | CRC check result is not correct.                       |  |  |

| 0.14        | 11h     | INTO CT            | fm0dec_err      | D5         | R   | FM0 decode error occurs.                               |  |  |

| <u>8.14</u> | 1111    | INTR_ST            | rxlen_err       | D4         | R   | Reception frame length is invalid.                     |  |  |

|             |         |                    | flag_err        | D3         | R   | No frame start marks are detected.                     |  |  |

|             |         |                    | pre_err         | D2         | R   | No preambles are detected.                             |  |  |

|             |         |                    | tx_done         | D1         | R   | Complete transmission of a frame.                      |  |  |

|             |         |                    | rx_ready        | D0         | R   | Reception frame is received.                           |  |  |

|             |         |                    | txlen_err_mask  | D9         | R/W |                                                        |  |  |

|             |         |                    | post_err_mask   | D8         | R/W |                                                        |  |  |

|             |         |                    | rx_abort_mask   | D7         | R/W |                                                        |  |  |

|             |         |                    | crc_ng_mask     | D6         | R/W |                                                        |  |  |

| <u>8.15</u> | 10h     | INTO MIZ           | fm0dec_err_mask | D5         | R/W | Set an interrupt mask                                  |  |  |

| 0.15        | 12h     | INTR_MK            | rxlen_err_mask  | D4         | R/W | Set an interrupt mask.                                 |  |  |

|             |         |                    | flag_err_mask   | D3         | R/W |                                                        |  |  |

|             |         |                    | pre_err_mask    | D2         | R/W |                                                        |  |  |

|             |         |                    | tx_done_mask    | D1         | R/W |                                                        |  |  |

|             |         |                    | rx_ready_mask   | D0         | R/W |                                                        |  |  |

| Sec.        | Address | Function         | Name           | Used Bit    | R/W | Description                                             |  |

|-------------|---------|------------------|----------------|-------------|-----|---------------------------------------------------------|--|

|             |         |                  | txlen_err_clr  | D9          | W   |                                                         |  |

|             |         |                  | post_err_clr   | D8          | W   |                                                         |  |

|             |         |                  | rx_abort_clr   | D7          | W   |                                                         |  |

|             |         |                  | crc_ng_clr     | D6          | W   |                                                         |  |

|             | 4.01    |                  | fm0dec_err_clr | D5          | W   |                                                         |  |

| <u>8.16</u> | 13h     | INTR_CLR         | rxlen_err_clr  | D4          | W   | Clear an interrupt.                                     |  |

|             |         |                  | flag_err_clr   | D3          | W   |                                                         |  |

|             |         |                  | pre_err_clr    | D2          | W   |                                                         |  |

|             |         |                  | tx_done_clr    | D1          | W   |                                                         |  |

|             |         |                  | rx_ready_clr   | D0          | W   |                                                         |  |

| <u>8.17</u> | 14h     | INTR_INV         | int_inv        | D0          | R/W | Invert the output of the interrupt pin.                 |  |

| <u>8.18</u> | 15h     | BIT_RATE         | txrate         | [D9,D8]     | R/W | Set the transmission bit rate.                          |  |

| <u>8.18</u> | 15h     | BIT_RATE         | rxrate         | D0          | R/W | Set the reception bit rate.                             |  |

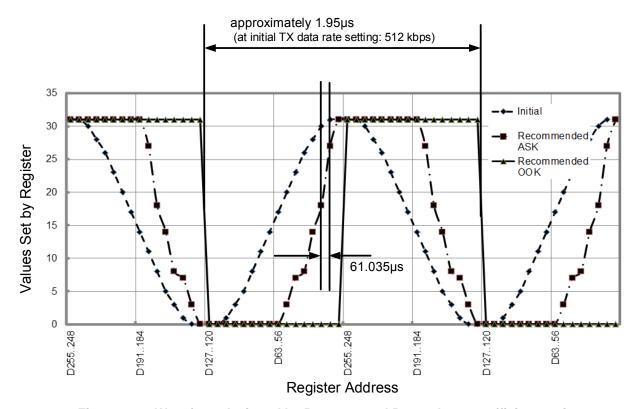

| <u>8.19</u> | 16h     | RAMP FIFO        | rmpup          | [D255,D128] | R/W | Set the ramp-up coefficient.                            |  |