# ディスクリート半導体 熱設計の勘どころ

# 概要

本資料はディスクリート半導体のチップ温度低減施策について述べたものです。

# 目次

| 概要                  | 1  |

|---------------------|----|

| 目次                  | 2  |

| 1. パッケージ単体での温度比較    | 3  |

| 2. 放熱器の効果           | 4  |

| 2.1. 放熱器の大きさ        | 4  |

| 2.2. 両面放熱パッケージ      | 5  |

| 3. 基板実装での改善効果       | 6  |

| 3.1. 基板の層数          | 6  |

| 3.2. サーマルビアの効果 1    | 7  |

| 3.3. サーマルビアの効果 2    | 8  |

| 4. 複数配置の影響(熱干渉)     | 9  |

| 5. パターン被覆率の影響       | 10 |

| 6. パッケージ温度とチップ温度の関係 | 11 |

| 7. モールド上面の温度測定方法    | 11 |

| 8. 簡易ツールによるシミュレーション | 12 |

| 制見取り扱い上のお願い         | 12 |

## 1. パッケージ単体での温度比較

現在、入手できる MOSFET には、数多くのパッケージ形状があります。それぞれのパッケージで熱経路が異なるために同じ電力損失でもチップの温度に差が見られます。弊社の主なパッケージ種類を表 1 に示します。

機器の小型化による自己放熱量の低減、基板内への高密度実装、使用環境温度の上昇、高速動作のための電力 損失の増加などにより、チップは高温になっていきます。そのため少しでも放熱効果が高い表面実装タイプのパッケージが主 流となりつつあると考えられます。

| ピン数 | 表面実装タイプ  |              |             | リード挿入タイプ  |            |           |

|-----|----------|--------------|-------------|-----------|------------|-----------|

|     | CST2B    | CST2C        | USC         | TO-220-2L | TO-220F-2L |           |

| 2   | US2H     | US-FLAT      | S-FLAT      |           |            |           |

|     | M-FLAT   |              |             |           |            |           |

|     | CST3     | UFM          | TSM         | IPAK      | TO-220     | TO-3P(N)  |

| 3   | SOT23    | SOT-23F      | S-Mini      | I2PAK     | TO-247     | TO-220SIS |

|     | PW-Mini  | DPAK+        | TO-220SM(W) | TO-3P(L)  |            |           |

| 4   |          | _            |             | TO-247-4L |            |           |

| 6   | ES6      | UF6          | UDFN6       |           |            |           |

|     | UDFN6B   | TSOP6F       | VS-6        |           | _          |           |

|     | VS-8     | TSON Advance | SOP-8       |           |            |           |

| 8   | PS-8     | DSOP Advance |             |           | _          |           |

|     | DFN8 x 8 | SOP Advance  |             |           |            |           |

表1. 東芝ディスクリート半導体の主なパッケージ

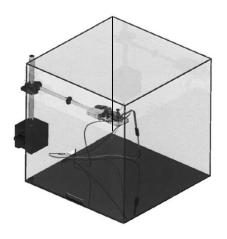

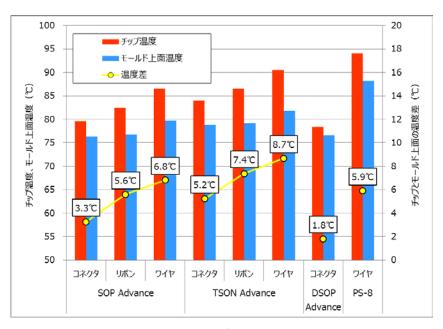

これらのディスクリート半導体パッケージ品のうち、図 1 に代表的な MOSFET デバイスのチップ温度を実測した値を示します。なお測定条件は、以下の条件で行いました。

電力損失 :1W

評価基板 : 弊社標準基板

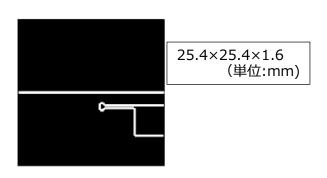

測定環境 : JEDEC 準拠自然流体用チャンバー

(規格 JESD51-2A)

その他: 基板固定部はオリジナル設定、放熱器なし

測定用チャンバー

**Application Note**

【グラフ下ラベルについて】 上段 : ソース接続方法 下段 : パッケージ名

図1. 代表的な弊社表面実装型 MOSFET のチップ温度実測値

パッケージ形状やデバイス内部構造によりチップの温度が変わることがわかります。またこれは一例であり使用するデバイスの消費電力、実装状態、周辺環境によりデバイスへの負荷が変わり、チップ温度はその都度、変わるため注意が必要になります。最大定格以内で使用することは勿論ですが、一般的に半導体は温度が高いほど寿命が短くなります。信頼性の面からもチップ温度を下げることが重要であり必要になります。

## 2. 放熱器の効果

#### 2.1. 放熱器の大きさ

チップ温度低減施策で、まず考えられるのは放熱器になります。放熱器は、熱源の熱量を熱伝導によって取り込みその表面から大気中に熱を放熱する機能をもち、その材質、形状、表面処理により冷却機能に差があります。

一般的に放熱器は、加工が容易で且つ比較的安価なアルミ材などで作られます。このアルミ放熱器は、表面にアルマイト加工(アルミニウム表面を電解処理により酸化被膜を生成する処理)などを行うことでアルミ表面の放射率をあげて、より放熱効果を上げることが可能です。また使用するアルミ材もその加工法により熱伝導率を変えることができます。また、放熱器の形状は羽根型(フィン)やピン型などがあり、表面積を増やす事で放熱効果が上がり、温度低減が見込めます。

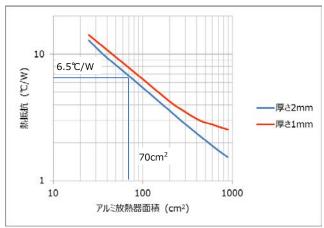

図 2 に厚みが 1 mm と 2 mm のアルミ板面積に対する放熱器熱抵抗の関係を示します。これにより熱抵抗の概算が可能になります。また放熱器のデータは、メーカの Web ページもしくは HP でも入手が可能です。

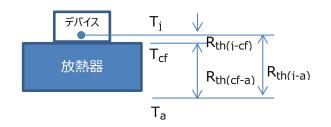

#### 【放熱器の選択方法】

電力損失: P チップ温度 (ジャンクション温度): T<sub>j</sub> デバイスと放熱器接触側面温度: T<sub>cf</sub> 使用雰囲気温度: T<sub>a</sub>

チップ-放熱器間の熱抵抗:Rth(j-cf)放熱器-雰囲気の熱抵抗:Rth(cf-a)

**Application Note**

図2. 放熱器面積と熱抵抗(例)

上図において熱抵抗、パワー、温度の関係は

$$(R_{th(i-cf)} + R_{th(cf-a)}) \times P = (T_i - T_a)$$

$$R_{th(cf-a)} = ((T_j - T_a)) / P) - R_{th(j-cf)}$$

となり

、 (デバイスと放熱器の接触熱抵抗を無視する)とした時には R<sub>th(cf-a)</sub>=6.5 ℃/W となります。

よって  $R_{th(cf-a)}$  < 6.5  $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$  の放熱器を使用すれば、条件を満たす放熱効果が見込めます。 ちなみに 2 mm 厚の アルミ板を使うと図 2 より面積は約 70 cm² になります。

#### 2.2. 両面放熱パッケージ

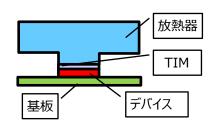

図3に当社の表面実装型パッケージシリーズのSOP Advance(以下SOP-Adv.と略)とDSOP Advance(以下DSOP-Adv.と略)、2つの代表的なパッケージを示します。両者の違いは、前者は通常の表面実装型パッケージでは一般的なパッケージ裏面からのみの放熱タイプであるのに対し、後者はパッケージ裏面と表面からの両面放熱が可能なタイプのパッケージであることです。

DSOP Advance 両面放熱効果 (シミュレーション)

DSOP Advance 両面放熱の概念

#### 図3. SOP Advance と DSOP Advance パッケージおよび両面放熱の説明

DSOP-Adv.では上面に放熱器を配置することで、放熱器のない場合と比較し約 32 %のチップ温度低下の模様がシミュレーションによってわかりました。また、基板側からの放熱が期待できない場合(サーマルビアや銅インレイ等の配置が困難)、上面に放熱器を配置できれば同様の放熱効果が得られると考えられます。

またはじめから両面放熱すればチップ温度の低減は明らかです(図3参照)。

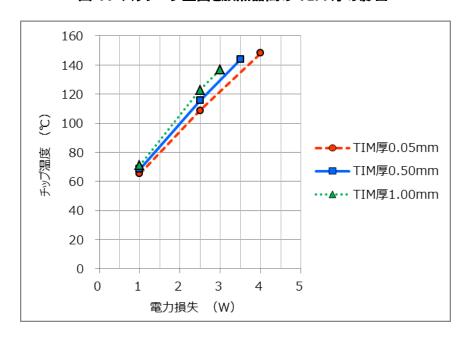

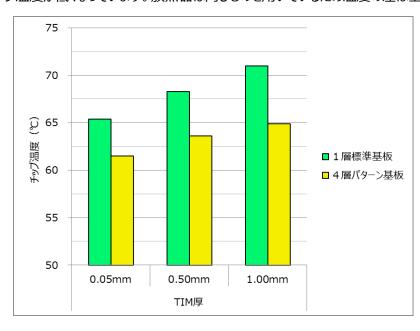

また、放熱器とデバイス上面の熱的接触には、サーマルグリース(TIM: Thermal Interface Material)を使用することがより効果的です。図4に放熱器とデバイス上面間に塗布した TIM 厚み別のチップ温度実測定値を示します。電力損失が大きいほどチップ温度が高くなります。2.5 W 損失でチップ温度を比較すると TIM 厚が最も薄い 0.05 mm の場合が最も低いチップ温度になっています。 TIM 自体の熱伝導率は高くないため、あまり厚めに塗ると逆効果になる可能性があります。 TIM は部品接触面の凹凸部を埋めることで空気層をなくし、熱伝導を良くするために使われます。 また TIM は接触面にムラなく均等に塗布することも重要になります。

図4. パッケージ上面と放熱器間の TIM 厚の影響

## 3. 基板実装での改善効果

### 3.1. 基板の層数

高密度実装に対応してデバイスの小型化が進み、その結果としてデバイス自身の表面積が小さくなり放熱量が減って、デバイス単独での温度低減が期待できなくなっています。

そのような場合、デバイスで発生した熱はドレインフレーム(E-pad)を経由して大部分は実装基板に流れていきます。基板に流れ込んだ熱の一部は空気との界面で熱伝達により放熱され、また一部は表面からの放射により放出されます。しかしながら熱の多くは熱伝導によって基板の表面や内部、裏面へ拡散していきます。

また基板の放熱量を上げるためには基板に直接、放熱器を取り付けることで温度低減を図ることができます。

通常、放熱器は基板裏面に配置されるため、デバイスが実装された表面から裏面の放熱器に熱を伝えるためには、熱伝 導率の高い基板を使用することが好ましいのですが、コスト面からも材質は限られてきます。

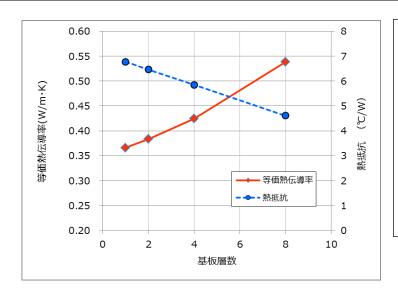

この様な場合、基板に銅などのパターンを挟み込んだ多層基板を用いる事で基板全体の等価熱伝導率を上げることができます。これを使うことで基板裏面の放熱器に流れ込む量が増えて全体の放熱効果を上げることが考えられます。図5に挟み込むパターンの層数に対して計算で求めた等価熱伝導率とそこから求まる熱抵抗を示します。層数の増加に従って等価熱伝導率は上がり、熱抵抗は下がることがわかります。

基板サイズ: 25.4×25.4 mm、厚み: 1.6 mm

パターン厚: 70 μm (2oz)

熱伝導率: パターン Cu:388(W/m·K)、

基板母材 FR4:0.35(W/m·K)

基板構造:パターンと基板母材が均等の厚みで設定。 その他:パターン形状は考慮しない。ベタパターンで計算。

熱抵抗の計算式

$$R_{th} = \frac{T}{\lambda \cdot S}$$

T:厚み (m)

λ: 熱伝導率(W/m·K) S:接触面積(m²)

図5. 等価熱伝導率と基板熱抵抗計算例

図 6 に層数の異なる基板でのチップ温度測定の結果を示します。この測定では両面放熱型の DSOP-Adv.を用いて上面放熱を行いながら TIM の厚みを変えています。すべての TIM 層において 4 層パターン基板の方が 1 層標準基板よりチップ温度が低くなっています。 放熱器は同じものを用いているため温度の差は基板による影響と考えられます。

デバイス: DSOP Advance 1 層基板: 弊社標準基板に準ずる 4 層基板: 第1層 Cu パターン面

第 2,3,4 層

Cu ベタパターン

パターン厚: Cu70µm (2oz)

基板材: FR4

放熱器:ともに有り(同一形状)

アルミブロックタイプ

図6. 多層基板のチップ温度への影響

#### 3.2. サーマルビアの効果1

基板の放熱を上げるために、基板の層数を増やす他にサーマルビアの導入があります。サーマルビアは、基板の表面から 裏面に貫通穴をあけ、その壁面に銅などの熱伝導率の高い金属素材をメッキにより形成します。基板の上下面を熱的につ なぐことで放熱面の増加が見込まれるほか、裏面に取付けられる放熱器への熱の伝導を容易に行うことができるようになりま す。限られた面積での基板ではサーマルビアによる熱の拡散は必要不可欠になります。サーマルビアの径の多くは、だいたいゆ 0.3 mm 程度になります。この径が小さすぎるとメッキ工程での層間パターンの接続不備が発生したりします。逆に大きすぎ るとデバイス実装時に半田の流れ込みが起こりデバイス側の半田濡れ率の低下やそれによる熱抵抗上昇などが懸念されま す。

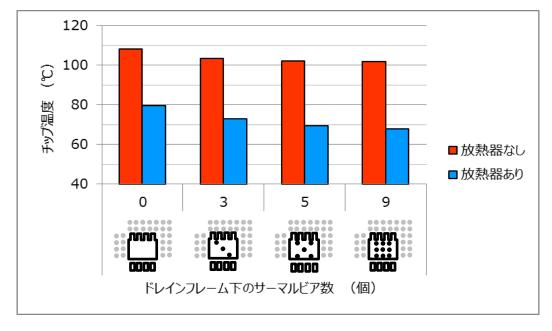

図 7 に SOP-Adv.のドレインパターン上のサーマルビアの個数を振った場合のチップ温度実測値を示します。サーマルビアの数が多い方が、チップ温度が低くなっていることが判ります。

図7. ドレインフレーム(E-pad)直下のサーマルビアの影響

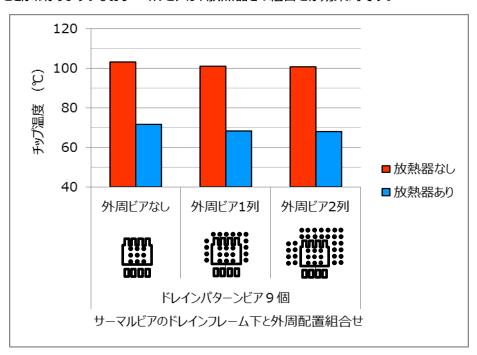

#### 3.3. サーマルビアの効果 2

デバイス周辺に配置するサーマルビアに関しても注意が必要になります。図 8 にサーマルビアをドレインパターン内部と周辺部に設けた場合の組合せによるチップ温度実測値を示します。外周ビアなしと外周ビア一列では、若干のチップ温度の低下が見られますが、外周ビアを二列に増やしてもチップ温度はほとんど変わっていません。外周ビアは前項の直下のビアに比べて効果が小さいことがわかります。なおサーマルビアは、放熱器との組合せが効果的です。

図8. サーマルビア配置とチップ温度

## 4. 複数配置の影響(熱干渉)

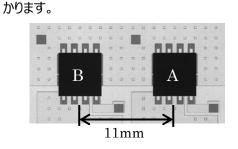

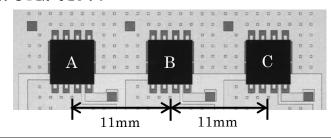

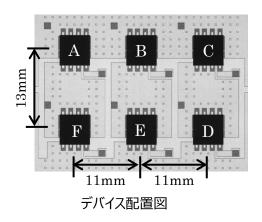

発熱源であるデバイスを同一基板上に複数個配置する場合、その距離などによって相互の熱干渉が発生します。とくに高温になるデバイスどうしの近接配置では相乗効果により単体での使用時より温度が高くなってしまいますので注意が必要になります。図 9 に近接(11 mm)したデバイスに単独通電した時と2素子同時通電した時の実測値から求めた熱抵抗(A デバイス)の比較を示します。2素子通電は熱の相互干渉により熱抵抗が上昇(温度が高い)していることがわ

1 素子通電: A デバイス

のみ通電

2素子通電:A、Bデバイス

ともに通電

図9. 熱の相互干渉の影響(熱抵抗の変化)

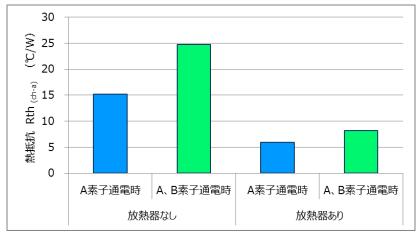

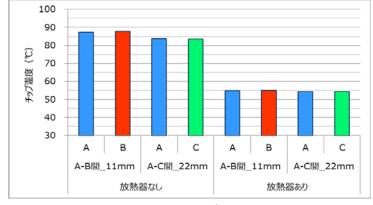

図 10 は、3 つのデバイスを並べてそれぞれの組合せで発熱させた場合の各デバイスの温度を示しています。

デバイスの間隔は、それぞれ 11 mm です。放熱器なしの時に A と B を同時に発熱させた場合のチップ温度は、85  $^{\circ}$  を超えています。一方、距離が離れた A と C を同時に発熱させた場合ではチップ温度は 85  $^{\circ}$  以下になっていることがわかります。

このようにデバイス間距離が近いとお互いの熱の影響により想定する以上の温度上昇が起こりデバイスにダメージを与える場合がありますので注意が必要です。これらを回避するためデバイスの間隔を考慮し、高発熱源どうしはなるべく距離をとるなどの工夫が必要になります。その他に放熱器等の使用も重要になります。放熱器を使うことでチップ温度は低減でき、且つお互いの熱の影響も低減することができます。

図10. 熱の相互干渉 デバイス間距離の影響

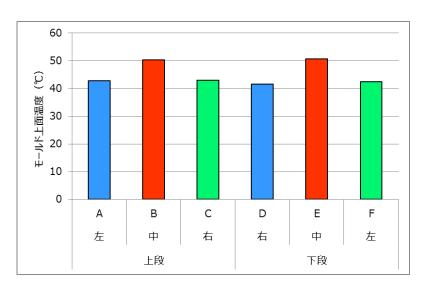

図 11 に 6 個のデバイス通電時のパッケージ上面温度を示します。この基板には裏面に放熱器が配置されています。基板のサーマルビアと放熱器の効果により各デバイスのチップ温度は下がっていますが、中央に配置された B、E デバイスが両側のチップ温度より高くなっているのがわかります。熱源に挟まれるデバイスは注意が必要になります。

- ・デバイス A、B、C のドレインリードは 共通パターンで接続。

- ・デバイス D、E、F のソースリードは 共通パターンで接続。

- ・6 デバイスを二直三並列で通電。

図11. 複数デバイス通電時のパッケージ上面温度

## 5. パターン被覆率の影響

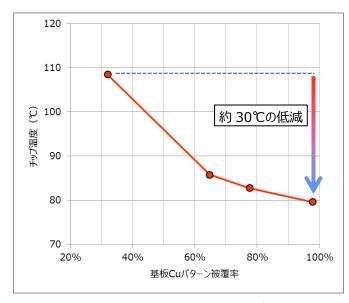

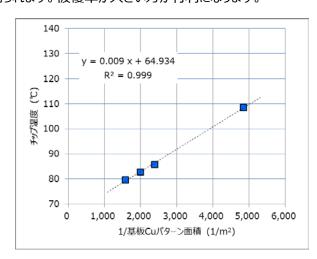

Cuパターンの被覆率を上げる事でも、チップ温度低減が図れます。図 12 に弊社標準基板(25.4 mm×25.4 mm、t=1.6 mm、Cuパターン厚 70 μm、片側 1 層パターン)において、第一層の Cu の被覆率を変えた場合のチップ温度を示します。この基板は、サーマルビア無しのベタ基板で Cu パターンから基板内に熱が拡がり裏面へと伝わるモデルです。被覆率 98 %と被覆率 33 %ではチップ温度にして約 30 ℃の差が見られます。被覆率が大きい方が有利になります。

図12. 基板被覆率とチップ温度

パターン面積の逆数とチップ温度の関係は、上図のように 直線で近似されます。よってパターン面積とチップ温度は 反比例していることが判ります

## 6. パッケージ温度とチップ温度の関係

デバイスを使用する上で注意すべきはチップ温度となります。しかしその温度の見積もりにはデバイスのテクニカルデータなどを参考にするしかありませんが、この熱抵抗値は雰囲気や基板等の影響により変わるため実用上はそのままの値を使用することはできません。このようなとき、デバイスのモールド上面温度を熱電対などで直接温度測定を行う方法が考えられます。図13 にチップ温度とそのモールド上面温度を示します。

モールド上面温度は、次項で示す方法で熱電対により測定しています。この図を見るとデバイス構造によりチップとモールド上面の温度差に違いが出ていることが判ります。 概ねコネクタ構造では 3~5 ℃の差であり、リボン構造で 5~7 ℃、ワイヤ構造では 7~9 ℃ほど差があります。 とくにワイヤ構造では温度差が大きく測定には注意が必要になります。

測定条件 測定基板:弊社標準測定基板 (ベタ基板) 基板サイズ:25.4×25.4mm、 基板厚み:1.6mm パターン:単層、厚み70µm(2oz) 環境:JEDEC 標準自然対流 条件準拠 (JEDEC チャンバー使用) 電力損失:1.0W

【グラフ下ラベルについて】 上段 : ソース接続方法 下段 : パッケージ名

図13. MOSFET 製品のチップ温度とそのモールド上面温度

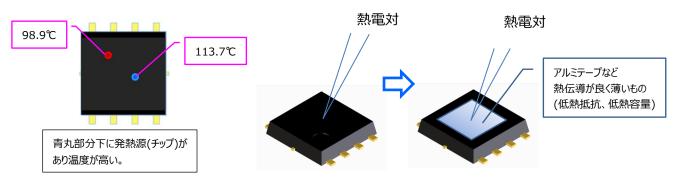

## 7. モールド上面の温度測定方法

前項でチップ温度とモールド上面温度の差が大きかったワイヤ構造ですが、この構造では熱の経路も他の構造に比べて 細くなり高温部分が局所的になります。その結果、チップの真上やワイヤ近傍に熱が集まりモールド上面には温度の分布が 発生してしまいます。図 14 に示すようにそのため熱の流出を防ぐために用いた細線熱電対では、その測定位置によって値に ばらつきが生じる結果となります。対策として図 15 に示すようにモールド上面に熱伝導率の高い金属テープ (例えばアルミテープなど) を貼り付けそのテープに熱電対を貼り付けることにより測定の位置による温度の差をある程度、抑えることができます。本来ならば最高温度ポイントでの測定が望ましいのですがそれが困難な場合、このようにすることで測定の誤差を緩和することができます。

図14. モールド表面温度 図15. モールド上面温度の測り方

## 8. 簡易ツールによるシミュレーション

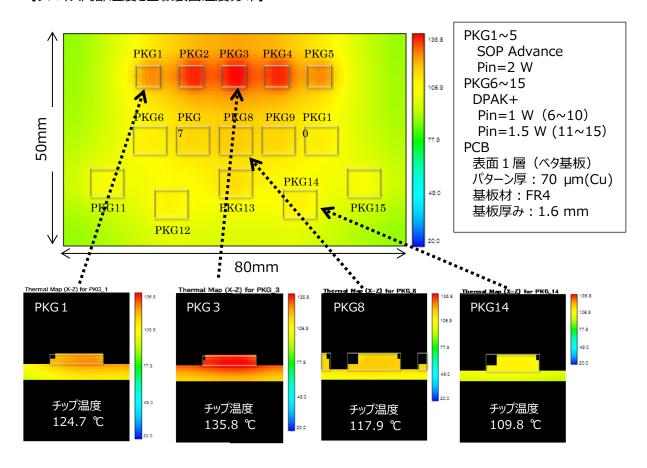

弊社では、簡易的に熱シミュレーションを行うことが可能です。図 16 に簡易シミュレーションによる熱解析事例を載せます。 シミュレーションを活用すれば素早くチップ温度を見積もることも可能になります。

#### 【デバイス内部温度と基板表面温度分布】

図16.デバイス内部温度と基板表面温度分布簡易シミュレーション事例

\*デバイスへの電力損失は任意の値でシミュレーション

この例の場合、PKG3のデバイスの温度が高いため何らかの対策が必要であることがわかります。

#### 製品取り扱い上のお願い

株式会社東芝およびその子会社ならびに関係会社を以下「当社」といいます。 本資料に掲載されているハードウエア、ソフトウエアおよびシステムを以下「本製品」といいます。

- 本製品に関する情報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を得て本資料を転載 複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

- 当社は品質、信頼性の向上に努めていますが、半導体・ストレージ製品は一般に誤作動または故障する場合があります。本製 品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、 お客様のハードウエア・ソフトウエア・システムに必要な安全設計を行うことをお願いします。なお、設計および使用に際しては、本 製品に関する最新の情報(本資料、仕様書、データシート、アプリケーションノート、半導体信頼性ハンドブックなど)および本製 品が使用される機器の取扱説明書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品デ ータ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品 単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

- 本製品は、特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な財産損 害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下"特定用途"という)に使用されることは意図さ れていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇宙機器、医療機器、車載・輸送機器、列 車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連機器、昇降機器、電力機器、金融関連機器などが含 まれますが、本資料に個別に記載する用途は除きます。特定用途に使用された場合には、当社は一切の責任を負いません。な お、詳細は当社営業窓口までお問い合わせください。

- ◆ 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

- 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用することはできません。

- ◆ 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及び第三者の 知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に関して、明示的に も黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の 権利の非侵害保証を含むがこれに限らない。) をしておりません。

- 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事 用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、「米国輸出管理規則」等、適用あ る輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- ◆ 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず当社営業窓口までお問い合わせください。本製品のご使用に 際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査の上、かかる法令に適合す るようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は一切の責任を負いかねます。