# 32 ビット RISC マイクロコントローラ TMPM4G グループ(1)

リファレンスマニュアル 製品個別情報 (PINFO-M4G(1))

**Revision 3.1**

2019-06

東芝デバイス&ストレージ株式会社

# 目次

| 序章                                        | 9  |

|-------------------------------------------|----|

| 関連するドキュメント                                | 9  |

| 表記規約                                      | 10 |

| 用語 • 略語                                   | 12 |

| 1. 概要                                     | 13 |

| 2. 各周辺機能の情報                               | 13 |

| 2.1. レジスタ ベースアドレス                         |    |

| 2.2. トリガセレクタ(TRGSEL)                      |    |

| 2.2.1. トリガセレクタと製品対応                       |    |

| 2.2.2. 使用方法と設定                            |    |

| 2.2.3. レジスター覧                             |    |

| 2.2.4. レジスタ詳細                             |    |

| 2.2.4.1. <i>[TSELOCRO]</i> (コントロールレジスタ 0) |    |

| 2.2.4.2. [TSELOCR1] (コントロールレジスタ 1)        |    |

| 2.2.4.3. [TSEL0CR2] (コントロールレジスタ 2)        |    |

| 2.2.4.4. [TSEL0CR3] (コントロールレジスタ 3)        |    |

| 2.2.4.5. <i>[TSEL0CR4]</i> (コントロールレジスタ 4) |    |

| 2.2.4.6. [TSEL0CR5] (コントロールレジスタ 5)        | 35 |

| 2.2.4.7. [TSEL0CR6] (コントロールレジスタ 6)        | 37 |

| 2.2.4.8. [TSEL0CR7] (コントロールレジスタ 7)        | 39 |

| 2.2.4.9. [TSEL0CR8] (コントロールレジスタ 8)        | 41 |

| 2.2.4.10. [TSEL0CR9] (コントロールレジスタ 9)       | 43 |

| 2.2.4.11. [TSEL0CR10] (コントロールレジスタ 10)     | 45 |

| 2.2.4.12. [TSEL0CR11] (コントロールレジスタ 11)     | 47 |

| 2.2.4.13. [TSEL0CR12] (コントロールレジスタ 12)     |    |

| 2.2.4.14. [TSEL0CR13] (コントロールレジスタ 13)     |    |

| 2.3. クロック選択式ウォッチドッグタイマ(SIWDT)             |    |

| 2.3.1. 搭載チャネル                             |    |

| 2.3.2. カウントクロック                           |    |

| 2.3.3. プロテクト機能                            |    |

| 2.3.4. 発振クロックプロテクト機能                      | 53 |

| 2.4. 周波数検知回路(OFD)                         | 54 |

| 2.4.1. 搭載一覧                               |    |

| 2.4.2. 基準クロック                             | 54 |

| 2.4.3. 検知対象クロック                           |    |

| 2.5. デバッグインタフェース                          |    |

| 2.5.1. 製品別デバッグインタフェース一覧                   |    |

| 2.6. ノンブレークデバッグ インタフェース(NBDIF)            |    |

| 2.6.1. 機能対応                               | 56 |

| 2.6.2. 製品別 NBDIF 一覧               | 56 |

|-----------------------------------|----|

| 2.7. フラッシュメモリ                     | 57 |

| 2.7.1. 書き込み,消去操作用クロック             | 57 |

| 2.7.2. 製品別コードフラッシュブロック構成          | 57 |

| 2.7.3. 製品別データフラッシュブロック構成          | 59 |

| 2.7.4. シングルブート使用リソース              | 60 |

| 2.8. 高速 DMA コントローラ(HDMAC)         | 61 |

| 2.8.1. 搭載ユニット                     | 61 |

| 2.8.2. DMA 転送要求一覧                 | 61 |

| 2.9. 多機能 DMA コントローラ(MDMAC)        | 63 |

| 2.9.1. 搭載ユニット                     | 63 |

| 2.9.2. DMA 転送要求一覧                 | 63 |

| 2.10. アドバンストプログラマブルモータ制御回路(A-PMD) | 67 |

| 2.10.1. 搭載チャネル                    | 67 |

| 2.10.2. 機能端子とポート                  | 67 |

| 2.10.3. DMA 要求                    | 68 |

| 2.10.4. 内部信号接続仕様                  | 69 |

| 2.10.4.1. ADC 接続                  | 69 |

| 2.11. 12 ビットアナログデジタルコンバータ(ADC)    | 70 |

| 2.11.1. 搭載ユニット                    | 70 |

| 2.11.2. 機能端子とポート                  | 70 |

| 2.11.3. アナログ基準端子                  | 71 |

| 2.11.4. ADC 用変換クロック               | 71 |

| 2.11.5. モード設定レジスタ 2 の設定値          | 71 |

| 2.11.6. DMA 要求                    | 71 |

| 2.11.7. 監視機能                      | 72 |

| 2.11.8. 内部信号接続仕様                  |    |

| 2.11.8.1. 起動トリガ接続仕様               |    |

| 2.12. 8 ビットデジタルアナログコンバータ(DAC)     |    |

| 2.12.1. 搭載チャネル                    |    |

| 2.12.2. 機能端子とポート                  |    |

| 2.13. 電圧検知回路(LVD)                 | 75 |

| 2.13.1. 搭載一覧                      |    |

| 2.13.2. 検知対象電源                    | 75 |

| 2.14. 32 ビットタイマイベントカウンタ(T32A)     | 76 |

| 2.14.1. 搭載チャネル                    |    |

| 2.14.2. 機能端子とポート                  |    |

| 2.14.3. プリスケーラ用クロック               | 79 |

| 2.14.4. 内部信号接続仕様                  |    |

| 2.14.4.1. キャプチャ/カウンタチャネル間接続仕様     | 80 |

| 2.14.4.2. 同期制御接続仕様                               | 82  |

|--------------------------------------------------|-----|

| 2.14.4.3. T32A タイマチャネル間リロードトリガ接続仕様               | 85  |

| 2.14.4.4. TSPI/UART-T32A 間接続仕様                   | 86  |

| 2.14.4.5. T32A - ISD 間接続仕様                       | 86  |

| 2.14.4.6. ELOSC 低速クロック-T32A 間接続仕様                | 87  |

| 2.14.5. 製品別パルスカウント対応一覧                           | 87  |

| 2.14.6. DMA 要求                                   | 88  |

| 2.15. リアルタイムクロック(RTC)                            | 91  |

| 2.15.1. 搭載一覧                                     | 91  |

| 2.15.2. 機能端子とポート                                 | 91  |

| 2.15.3. 時計カウントクロック                               | 91  |

| 2.16. ロングタームタイマ(LTTMR)                           | 92  |

| 2.16.1. 搭載チャネル                                   | 92  |

| 2.16.2. カウントクロック                                 | 92  |

| 2.16.3. 内部信号接続仕様                                 | 92  |

| 2.16.3.1. CEC/RMC 接続                             | 92  |

| 2.17. 非同期シリアル通信回路(UART)                          | 93  |

| 2.17.1. 搭載チャネル                                   | 93  |

| 2.17.2. 機能端子とポート                                 | 93  |

| 2.17.3. 製品別ハーフクロックモード対応一覧                        | 94  |

| 2.17.4. プリスケーラ用クロック                              | 94  |

| 2.17.5. DMA 要求                                   | 95  |

| 2.17.6. 内部信号接続仕様                                 | 96  |

| 2.17.6.1. トリガ転送信号接続仕様                            | 96  |

| 2.18. 高精度非同期シリアル通信回路(FUART)                      | 97  |

| 2.18.1. 搭載チャネル                                   | 97  |

| 2.18.2. 機能端子とポート                                 |     |

| 2.18.3. プリスケーラ用クロック                              | 98  |

| 2.18.4. DMA 要求                                   | 98  |

| 2.19. I <sup>2</sup> C インタフェース(I <sup>2</sup> C) | 99  |

| 2.19.1. 搭載チャネル                                   | 99  |

| 2.19.2. 機能端子とポート                                 | 99  |

| 2.19.3. プリスケーラ用クロック                              | 99  |

| 2.19.4. 通信スピード                                   | 100 |

| 2.19.5. ウエイクアップ機能対応                              | 100 |

| 2.19.6. ノイズフィルタ選択                                | 100 |

| 2.19.7. DMA 要求                                   | 101 |

| 2.20. シリアルペリフェラルインタフェース(TSPI)                    | 102 |

| 2.20.1. 搭載チャネル                                   | 102 |

| 2.20.2. 機能端子とポート                                 | 103 |

| 2.20.3. 製品別転送モード対応一覧                             | 105 |

| 2.20.4. <i>[TSPIxCR2]</i> <rxdly>の設定値</rxdly> | 105 |

|-----------------------------------------------|-----|

| 2.20.5. プリスケーラ用クロック                           | 105 |

| 2.20.6. DMA 要求                                | 106 |

| 2.20.7. 内部信号接続仕様                              | 107 |

| 2.20.7.1. トリガ送信信号接続仕様                         | 107 |

| 2.21. シリアルメモリインタフェース(SMIF)                    | 108 |

| 2.21.1. 搭載チャネル                                | 108 |

| 2.21.2. 機能端子とポート                              | 108 |

| 2.22. CEC 制御回路 (CEC)                          | 109 |

| 2.22.1. 搭載チャネル                                | 109 |

| 2.22.2. 機能端子とポート                              | 109 |

| 2.22.3. サンプリングクロック                            | 109 |

| 2.23. リモコン受信回路(RMC)                           | 110 |

| 2.23.1. 搭載チャネル                                | 110 |

| 2.23.2. 機能端子とポート                              | 110 |

| 2.23.3. サンプリングクロック                            | 110 |

| 2.23.4. 内部信号接続仕様                              | 111 |

| 2.23.4.1. T32A 接続                             | 111 |

| 2.24. デジタルノイズフィルタ回路(DNF)                      | 112 |

| 2.24.1. 搭載ユニット                                | 112 |

| 2.24.2. 製品別外部割り込みと DNF の対応                    | 112 |

| 2.24.3. サンプリングソースクロック                         | 113 |

| 2.25. インタバルセンサ検知回路(ISD)                       | 114 |

| 2.25.1. 搭載ユニット                                | 114 |

| 2.25.2. 機能端子とポート                              | 114 |

| 2.25.3. 基準クロック                                | 115 |

| 2.25.4. 内部信号接続仕様                              | 115 |

| 2.26. バウンダリスキャン(BSC)                          | 116 |

| 2.26.1. 機能対応                                  | 116 |

| 2.26.2. 製品別 JTAG インタフェース一覧                    | 116 |

| 2.26.3. バウンダリスキャン順序                           | 117 |

| 2.27. トリミング回路(TRM)                            | 121 |

| 2.27.1. 搭載一覧                                  | 121 |

| 2.27.2. 対象発振器                                 | 121 |

| 2.28. 外部バスインタフェース(EBIF)                       | 122 |

| 2.28.1. 機能端子とポート                              | 122 |

| 3. 改訂履歴                                       | 123 |

| 製品取り扱い上のお願い                                   | 125 |

# 図目次

|   |                                     | トリガセレクタ接続例                            |    |

|---|-------------------------------------|---------------------------------------|----|

| 义 | 2.2                                 | ADC 起動トリガ接続仕様概略図                      | 73 |

|   |                                     |                                       |    |

|   |                                     |                                       |    |

|   |                                     |                                       |    |

|   |                                     |                                       |    |

|   |                                     | ± □ \ <del>\</del>                    |    |

|   |                                     | 表目次                                   |    |

| 表 | 2.1                                 | レジスタベースアドレスタイプ (1/3)                  | 13 |

| 表 | 2.2                                 | レジスタベースアドレスタイプ (2/3)                  | 14 |

| 表 | 2.3                                 | レジスタベースアドレスタイプ (3/3)                  | 15 |

|   |                                     | 製品別トリガセレクタ対応一覧 (1/6)                  |    |

| 表 | 2.5                                 | 製品別トリガセレクタ対応一覧 (2/6)                  |    |

| 表 | 2.6                                 | 製品別トリガセレクタ対応一覧 (3/6)                  |    |

|   | 2.7                                 | 製品別トリガセレクタ対応一覧 (4/6)                  |    |

|   | 2.8                                 | 製品別トリガセレクタ対応一覧 (5/6)                  |    |

|   | 2.9                                 | 製品別トリガセレクタ対応一覧 (6/6)                  |    |

|   |                                     | SIWDT 搭載チャネル                          |    |

|   | 2.10                                |                                       |    |

|   | 2.12                                |                                       |    |

|   | 2.12                                |                                       |    |

|   | 2.13                                | — · · · · ·                           |    |

|   | 2.14                                |                                       |    |

|   | 2.15                                | , ハウライファフェース指載一員<br>NBDIF 機能対応        |    |

|   |                                     |                                       |    |

|   | 2.17                                |                                       |    |

|   | <ul><li>2.18</li><li>2.19</li></ul> |                                       |    |

|   |                                     |                                       |    |

|   | 2.20                                | 製品別データフラッシュ                           |    |

|   | 2.21                                |                                       |    |

|   | 2.22                                |                                       |    |

|   | 2.23                                |                                       |    |

|   | 2.24                                | - 1 <del>-11-21   2</del> 2   - 1     |    |

|   | 2.25                                |                                       |    |

|   |                                     | MDMAC 搭載ユニット                          |    |

|   |                                     | MDMAC DMA 転送要求一覧 : ユニット A (1/4)       |    |

|   | 2.28                                | · · · · · · · · · · · · · · · · · · · |    |

|   |                                     | MDMAC DMA 転送要求一覧 : ユニット A (3/4)       |    |

|   | 2.30                                | ,                                     |    |

|   | 2.31                                |                                       |    |

| 表 | 2.32                                | A-PMD 機能端子                            | 67 |

| 表 | 2.33                                | A-PMD DMA 要求                          | 68 |

| 表 | 2.34                                | A-PMD 内部信号接続仕様:出力                     | 69 |

| 表 | 2.35                                | ADC 搭載ユニット                            | 70 |

| 表 | 2.36                                | ADC 機能端子とポート                          | 70 |

| 表 | 2.37                                | ADC 用変換クロック                           | 71 |

|   | 2.38                                |                                       | 71 |

| 表 | 2.39                                |                                       |    |

|   | 2.40                                |                                       |    |

|   | 2.41                                |                                       |    |

|   | 2.42                                |                                       |    |

|   | 2.43                                | · · · · · · · · · · · · · · · · · · · |    |

|   |                                     | DAC 機能端子とポート                          |    |

|   |                                     | page m 4 = 1 - 1                      |    |

# **TOSHIBA**

| 表 2.45                                                                                           | LVD 搭載一覧                                                                                                                                                                                                                                                                                                                                             | 75                                                         |

|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 表 2.46                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

| 表 2.47                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

| 表 2.48                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

| 表 2.49                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

|                                                                                                  | ` ,                                                                                                                                                                                                                                                                                                                                                  |                                                            |

| 表 2.50                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

| 表 2.51                                                                                           | T32A 機能信号とポート(4/4)                                                                                                                                                                                                                                                                                                                                   |                                                            |

| 表 2.52                                                                                           | T32A プリスケーラ用クロック                                                                                                                                                                                                                                                                                                                                     |                                                            |

| 表 2.53                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

| 表 2.54                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

| 表 2.55                                                                                           | T32A 同期制御接続仕様(1/3)                                                                                                                                                                                                                                                                                                                                   |                                                            |

| 表 2.56                                                                                           | ,                                                                                                                                                                                                                                                                                                                                                    |                                                            |

| 表 2.57                                                                                           | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                              |                                                            |

| 表 2.58                                                                                           | T32A リロードトリガ接続                                                                                                                                                                                                                                                                                                                                       |                                                            |

| 表 2.59                                                                                           | T32A TSPI/UART-T32A 間接続仕様                                                                                                                                                                                                                                                                                                                            | 86                                                         |

| 表 2.60                                                                                           | T32A - ISD 間接続仕様                                                                                                                                                                                                                                                                                                                                     | 86                                                         |

| 表 2.61                                                                                           | T32A ELOSC 低速クロック-T32A 間接続仕様                                                                                                                                                                                                                                                                                                                         | 87                                                         |

| 表 2.62                                                                                           | T32A 製品別パルスカウント対応一覧                                                                                                                                                                                                                                                                                                                                  | 87                                                         |

| 表 2.63                                                                                           | T32A DMA 要求(1/3)                                                                                                                                                                                                                                                                                                                                     |                                                            |

| 表 2.64                                                                                           | ,                                                                                                                                                                                                                                                                                                                                                    |                                                            |

| 表 2.65                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

| 表 2.66                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

| 表 2.67                                                                                           | RTC 機能端子とポート                                                                                                                                                                                                                                                                                                                                         |                                                            |

| 表 2.68                                                                                           | RTC 時計カウントクロック                                                                                                                                                                                                                                                                                                                                       |                                                            |

| 表 2.69                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

| 表 2.70                                                                                           | LTTMR カウントクロック                                                                                                                                                                                                                                                                                                                                       |                                                            |

| 表 2.70                                                                                           | LTTMR CEC/RMC 信号接続仕様                                                                                                                                                                                                                                                                                                                                 |                                                            |

| 表 2.71                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

|                                                                                                  |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

| 表 2.73                                                                                           |                                                                                                                                                                                                                                                                                                                                                      |                                                            |

| 表 2.74                                                                                           | UART ハーフクロックモード(1 端子モード)対応一覧                                                                                                                                                                                                                                                                                                                         |                                                            |

| ± 0.75                                                                                           |                                                                                                                                                                                                                                                                                                                                                      | 0.4                                                        |

| 表 2.75                                                                                           | UART プリスケーラ用クロック                                                                                                                                                                                                                                                                                                                                     |                                                            |

| 表 2.76                                                                                           | UART DMA 要求                                                                                                                                                                                                                                                                                                                                          | 95                                                         |

| 表 2.76<br>表 2.77                                                                                 | UART DMA 要求<br>UART トリガ転送信号接続仕様                                                                                                                                                                                                                                                                                                                      | 95<br>96                                                   |

| 表 2.76<br>表 2.77<br>表 2.78                                                                       | UART DMA 要求<br>UART トリガ転送信号接続仕様<br>FUART 搭載チャネル                                                                                                                                                                                                                                                                                                      | 95<br>96<br>97                                             |

| 表 2.76<br>表 2.77<br>表 2.78<br>表 2.79                                                             | UART DMA 要求<br>UART トリガ転送信号接続仕様<br>FUART 搭載チャネル<br>FUART 端子信号とポート                                                                                                                                                                                                                                                                                    |                                                            |

| 表 2.76<br>表 2.77<br>表 2.78<br>表 2.79<br>表 2.80                                                   | UART DMA 要求<br>UART トリガ転送信号接続仕様<br>FUART 搭載チャネル<br>FUART 端子信号とポート<br>FUART プリスケーラ用クロック                                                                                                                                                                                                                                                               |                                                            |

| 表 2.76<br>表 2.77<br>表 2.78<br>表 2.79<br>表 2.80<br>表 2.81                                         | UART DMA 要求<br>UART トリガ転送信号接続仕様<br>FUART 搭載チャネル<br>FUART 端子信号とポート<br>FUART プリスケーラ用クロック<br>FUART DMA 要求                                                                                                                                                                                                                                               |                                                            |

| 表 2.76<br>表 2.77<br>表 2.78<br>表 2.79<br>表 2.80                                                   | UART DMA 要求                                                                                                                                                                                                                                                                                                                                          | 95<br>96<br>97<br>97<br>98<br>98                           |

| 表 2.76<br>表 2.77<br>表 2.78<br>表 2.79<br>表 2.80<br>表 2.81                                         | UART DMA 要求                                                                                                                                                                                                                                                                                                                                          | 95<br>96<br>97<br>97<br>98<br>98<br>99                     |

| 表 2.76<br>表 2.77<br>表 2.78<br>表 2.79<br>表 2.80<br>表 2.81<br>表 2.82                               | UART DMA 要求                                                                                                                                                                                                                                                                                                                                          | 95<br>96<br>97<br>97<br>98<br>98<br>99                     |

| 表 2.76<br>表 2.77<br>表 2.78<br>表 2.79<br>表 2.80<br>表 2.81<br>表 2.82<br>表 2.83                     | UART DMA 要求         UART トリガ転送信号接続仕様         FUART 搭載チャネル         FUART 端子信号とポート         FUART プリスケーラ用クロック         FUART DMA 要求         I²C インタフェース 搭載チャネル         I²C インタフェース 機能端子とポート         I²C インタフェース プリスケーラ用クロック                                                                                                                              | 95<br>96<br>97<br>97<br>98<br>98<br>99                     |

| 表 2.76<br>表 2.77<br>表 2.78<br>表 2.79<br>表 2.80<br>表 2.81<br>表 2.82<br>表 2.83<br>表 2.84           | UART DMA 要求 UART トリガ転送信号接続仕様 FUART 搭載チャネル FUART 端子信号とポート FUART プリスケーラ用クロック FUART DMA 要求 I <sup>2</sup> C インタフェース 搭載チャネル I <sup>2</sup> C インタフェース 機能端子とポート I <sup>2</sup> C インタフェース プリスケーラ用クロック I <sup>2</sup> C インタフェース プリスケーラ用クロック I <sup>2</sup> C 通信スピード対応                                                                                        | 95<br>96<br>97<br>97<br>98<br>98<br>99<br>99               |

| 表 2.76<br>表 2.77<br>表 2.78<br>表 2.79<br>表 2.80<br>表 2.81<br>表 2.82<br>表 2.83<br>表 2.85<br>表 2.85 | UART DMA 要求 UART トリガ転送信号接続仕様 FUART 搭載チャネル FUART 端子信号とポート FUART プリスケーラ用クロック FUART DMA 要求 I <sup>2</sup> C インタフェース 搭載チャネル I <sup>2</sup> C インタフェース 機能端子とポート I <sup>2</sup> C インタフェース プリスケーラ用クロック I <sup>2</sup> C インタフェース プリスケーラ用クロック I <sup>2</sup> C 通信スピード対応                                                                                        | 95<br>96<br>97<br>97<br>98<br>98<br>99<br>99               |

| 表 2.76<br>表 2.77<br>表 2.78<br>表 2.79<br>表 2.80<br>表 2.81<br>表 2.82<br>表 2.83<br>表 2.85<br>表 2.85 | UART DMA 要求                                                                                                                                                                                                                                                                                                                                          | 95<br>96<br>97<br>97<br>98<br>98<br>99<br>99<br>100<br>100 |

| 表 2.76 表 2.77 表 2.78 表 2.79 表 2.80 表 2.81 表 2.82 表 2.84 表 表 表 表 表 表 表 表 表 表 表 表 表 表 表 表 表 表 表    | UART DMA 要求 UART トリガ転送信号接続仕様 FUART 搭載チャネル FUART 端子信号とポート FUART DMA 要求 I²C インタフェース 搭載チャネル I²C インタフェース 機能端子とポート I²C インタフェース フィルク運択 I²C インタフェース フィルク選択 I²C インタフェース DMA 要求 TSPI 搭載チャネル                                                 | 95<br>96<br>97<br>97<br>98<br>98<br>99<br>99<br>100<br>100 |

| 表 2.76 表 2.77 表 2.78 表 2.79 表 2.80 表 2.81 表 2.82 表 表 表 表 表 表 表 表 表 表 表 表 表 表 表 表 表 表 表           | UART DMA 要求                                                                                                                                                                                                                                                                                                                                          | 95 96 97 97 98 98 99 99 100 100 101                        |

| 表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表                                                           | UART DMA 要求 UART トリガ転送信号接続仕様  FUART 搭載チャネル  FUART 端子信号とポート  FUART プリスケーラ用クロック  FUART DMA 要求  I²C インタフェース 搭載チャネル  I²C インタフェース 機能端子とポート  I²C インタフェース プリスケーラ用クロック  I²C 通信スピード対応  I²C インタフェース フィルタ選択  I²C インタフェース DMA 要求  TSPI 搭載チャネル  TSPI 機能端子とポート(1/2)  TSPI 機能端子とポート(2/2)                                                                            | 95 96 97 97 98 98 98 99 99 100 100 101 102                 |

| 表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表                                                           | UART DMA 要求                                                                                                                                                                                                                                                                                                                                          | 95 96 97 97 98 98 98 99 99 100 100 101 103                 |

| 表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表                                                           | UART DMA 要求 UART トリガ転送信号接続仕様 FUART 搭載チャネル FUART 端子信号とポート FUART プリスケーラ用クロック FUART DMA 要求 I²C インタフェース 搭載チャネル I²C インタフェース 機能端子とポート I²C インタフェース プリスケーラ用クロック I²C 通信スピード対応 I²C インタフェース フィルタ選択 I²C インタフェース DMA 要求 TSPI 搭載チャネル TSPI 機能端子とポート(1/2) TSPI 機能端子とポート(2/2) TSPI モード対応一覧 TSPI 制御レジスタ 2 <rxdly>の設定値</rxdly>                                          | 95 96 97 97 98 98 99 99 100 100 101 102 103 104 105        |

| 表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表                                                           | UART DMA 要求 UART トリガ転送信号接続仕様 FUART 搭載チャネル FUART 端子信号とポート FUART プリスケーラ用クロック FUART DMA 要求 I²C インタフェース 搭載チャネル I²C インタフェース 機能端子とポート I²C インタフェース プリスケーラ用クロック I²C 通信スピード対応 I²C インタフェース フィルタ選択 I²C インタフェース DMA 要求 TSPI 搭載チャネル TSPI 機能端子とポート(1/2) TSPI 機能端子とポート(2/2) TSPI 機能端子とポート(2/2) TSPI 制御レジスタ 2 <rxdly>の設定値 TSPI プリスケーラ用クロック</rxdly>                   | 95 96 97 97 98 98 98 99 99 100 100 101 102 103 104 105     |

| 表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表                                                            | UART DMA 要求 UART トリガ転送信号接続仕様 FUART 搭載チャネル FUART 端子信号とポート FUART DMA 要求 I²C インタフェース 搭載チャネル I²C インタフェース 機能端子とポート I²C インタフェース プリスケーラ用クロック I²C インタフェース フリスケーラ用クロック I²C インタフェース フリスケーラ用クロック I²C インタフェース DMA 要求 TSPI 搭載チャネル TSPI 機能端子とポート(1/2) TSPI 機能端子とポート(2/2) TSPI 機能端子とポート(2/2) TSPI 制御レジスタ 2 <rxdly>の設定値 TSPI プリスケーラ用クロック TSPI DMA 要求</rxdly>         | 95 96 97 97 98 98 98 99 99 100 100 101 103 104 105         |

| 表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表                                                            | UART DMA 要求 UART トリガ転送信号接続仕様 FUART 搭載チャネル FUART 端子信号とポート FUART プリスケーラ用クロック FUART DMA 要求 I²C インタフェース 搭載チャネル I²C インタフェース 機能端子とポート I²C インタフェース プリスケーラ用クロック I²C 通信スピード対応 I²C インタフェース フィルタ選択 I²C インタフェース DMA 要求 TSPI 搭載チャネル TSPI 機能端子とポート(1/2) TSPI 機能端子とポート(2/2) TSPI モード対応一覧 TSPI 別印レジスタ 2 <rxdly>の設定値 TSPI プリスケーラ用クロック TSPI DMA 要求 TSPI DMA 要求</rxdly> | 95 96 97 97 98 98 98 99 99 100 100 101 102 103 105 105     |

| 表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表表                                                            | UART DMA 要求 UART トリガ転送信号接続仕様 FUART 搭載チャネル FUART 端子信号とポート FUART プリスケーラ用クロック FUART DMA 要求 I²C インタフェース 搭載チャネル I²C インタフェース 機能端子とポート I²C インタフェース プリスケーラ用クロック I²C 通信スピード対応 I²C インタフェース フィルタ選択 I²C インタフェース DMA 要求 TSPI 搭載チャネル TSPI 機能端子とポート(1/2) TSPI 機能端子とポート(2/2) TSPI モード対応一覧 TSPI 別印レジスタ 2 <rxdly>の設定値 TSPI プリスケーラ用クロック TSPI DMA 要求 TSPI DMA 要求</rxdly> | 95 96 97 97 98 98 98 99 99 100 100 101 102 103 104 105 105 |

# **TOSHIBA**

| 表 | 2.98  | CEC 搭載チャネル             | . 109 |

|---|-------|------------------------|-------|

| 表 | 2.99  | CEC 機能端子とポート           | .109  |

| 表 | 2.100 | CEC サンプリングクロック         | .109  |

| 表 | 2.101 | RMC 搭載チャネル             | .110  |

| 表 | 2.102 | RMC 機能端子とポート           | .110  |

| 表 | 2.103 | RMC サンプリングクロック         | .110  |

| 表 | 2.104 | RMC T32A 接続仕様          | .111  |

| 表 | 2.105 | DNF 搭載ユニット             |       |

| 表 | 2.106 | 外部割り込みと DNF 対応(ユニット A) | . 112 |

| 表 | 2.107 | 外部割り込みと DNF 対応(ユニット B) |       |

| 表 | 2.108 | DNF サンプリングソースクロック      |       |

| 表 | 2.109 | ISD 搭載ユニット             |       |

| 表 | 2.110 | ISD 機能端子とポート           |       |

|   | 2.111 | ISD 基準クロック             |       |

|   | 2.112 | ISD 制御接続仕様             |       |

| 表 | 2.113 | バウンダリスキャン 機能対応         |       |

|   | 2.114 | JTAG インタフェース搭載一覧       |       |

|   | 2.115 | バウンダリスキャン順序(1/4)       |       |

|   | 2.116 | バウンダリスキャン順序(2/4)       |       |

|   | 2.117 | バウンダリスキャン順序(3/4)       |       |

|   | 2.118 | バウンダリスキャン順序(4/4)       |       |

|   | 2.119 | TRM 搭載一覧               |       |

|   | 2.120 | TRM トリミング対象発振器         |       |

| 表 | 2.121 | EBIF 機能端子とポート          | . 122 |

| 耒 | 31 7  | 收計履歴                   | 123   |

# 序章

#### 関連するドキュメント

| 文書名                           | IP 記号          |  |  |

|-------------------------------|----------------|--|--|

| 入出力ポート (TMPM4G グループ(1))       | PORT-M4G(1)    |  |  |

| メモリマップ (TMPM4G グループ(1))       | MMAP-M4G(1)    |  |  |

| 例外 (TMPM4G グループ(1))           | EXCEPT-M4G(1)  |  |  |

| クロック制御と動作モード (TMPM4G グループ(1)) | CG-M4G(1)-C    |  |  |

| 電源とリセット動作 (TMPM4G グループ(1))    | RESET-M4G(1)   |  |  |

| フラッシュメモリ                      | FLASH15MHD32-A |  |  |

| トリミング回路                       | TRM-A          |  |  |

| 周波数検知回路                       | OFD-A          |  |  |

| 電圧検知回路                        | LVD-C          |  |  |

| デジタルノイズフィルタ回路                 | DNF-A          |  |  |

| デバッグインタフェース                   | DEBUG-A        |  |  |

| ノンブレークデバッグインタフェース             | NBDIF-A        |  |  |

| インタバルセンサ検知回路                  | ISD-A          |  |  |

| 多機能 DMA コントローラ                | MDMAC-A        |  |  |

| 高速 DMA コントローラ                 | HDMAC-A        |  |  |

| 外部バスインタフェース                   | EBIF-A         |  |  |

| シリアルメモリインタフェース                | SMIF-A         |  |  |

| 非同期シリアル通信回路                   | UART-C         |  |  |

| 高精度非同期シリアル通信回路                | FUART-B        |  |  |

| シリアルペリフェラルインタフェース             | TSPI-C         |  |  |

| I2C インタフェース                   | I2C-B          |  |  |

| CEC 制御回路                      | CEC-A          |  |  |

| 12 ビットアナログデジタルコンバータ           | ADC-C          |  |  |

| 8 ビットデジタルアナログコンバータ            | DAC-A          |  |  |

| アドバンストプログラマブルモータ制御回路          | A-PMD-C        |  |  |

| 32 ビットタイマイベントカウンタ             | T32A-B         |  |  |

| ロングタームタイマ                     | LTTMR-A        |  |  |

| リアルタイムクロック                    | RTC-A          |  |  |

| クロック選択式ウォッチドックタイマ             | SIWDT-A        |  |  |

| リモコン受信回路                      | RMC-B          |  |  |

| バウンダリスキャン                     | BSC-A          |  |  |

#### 表記規約

数値表記は以下の規則に従います。

16 進数表記: 0xABC

10 進数表記: 123 または 0d123 (10 進表記であることを示す必要のある場合だけ使用)

2進数表記: 0b111 (ビット数が本文中に明記されている場合は「0b」を省略可)

● ローアクティブの信号は信号名の末尾に「\_N」で表記します。

● 信号がアクティブレベルに移ることを「アサート (assert)」アクティブでないレベルに移ることを「デアサート (deassert)」と呼びます。

複数の信号名は [m:n]とまとめて表記する場合があります。例: S[3:0] は S3.S2.S1.S0 の 4 つの信号名をまとめて表記しています。

本文中 /1 で囲まれたものはレジスタを定義しています。

例: [ABCD]

● 同種で複数のレジスタ、フィールド、ビット名は「n」で一括表記する場合があります。

例: [XYZ1], [XYZ2], [XYZ3] → [XYZn]

● 「レジスター覧」中のレジスタ名でユニットまたはチャネルは「x」で一括表記しています。 ユニットの場合、「x」は A,B,C...を表します。

例: [ADACRO], [ADBCRO], [ADCCRO]→[ADxCRO]

チャネルの場合、「x」は0.1.2...を表します。

例: [T32A0RUNA], [T32A1RUNA], [T32A2RUNA]→[T32AxRUNA]

レジスタのビット範囲は [m:n] と表記します。例: [3:0] はビット3から0の範囲を表します。

● レジスタの設定値は16進数または2進数のどちらかで表記されています。

例: **[ABCD]**<EFG> = 0x01 (16 進数)、 **[XYZn]**<VW> = 1 (2 進数)

ワード、バイトは以下のビット長を表します。

バイト: 8 ビット ハーフワード: 16 ビット ワード: 32 ビット

ダブルワード: 64 ビット

レジスタ内の各ビットの属性は以下の表記を使用しています。

R: リードオンリー W: ライトオンリー R/W: リード / ライト

- 断りのない限り、レジスタアクセスはワードアクセスだけをサポートします。

- 本文中の予約領域「Reserved」として定義されたレジスタは書き換えを行わないでください。 また、読み出した値を使用しないでください。

- Default 値が「一」となっているビットから読み出した値は不定です。

- 書き込み可能なビットフィールドと、リードオンリー「R」のビットフィールドが共存するレジス タに書き込みを行う場合、リードオンリー「R」のビットフィールドには Default 値を書き込んでく ださい。

Default 値が「一」となっている場合は、個々のレジスタの定義に従ってください。

- ライトオンリーのレジスタのReserved ビットフィールドにはDefault 値を書き込んでください。Default 値が「一」となっている場合は、個々のレジスタの定義に従ってください。

- 書き込みと読み出しで異なる定義のレジスタへのリードモディファイライト処理は行わないでくだ さい。

2019-06-17 10 / 125 Rev. 3.1

Arm,Cortex および Thumb は Arm Limited(またはその子会社)の US またはその他の国における 登録商標です。 All rights reserved.

FLASH メモリについては、米国 SST 社 (Silicon Storage Technology, Inc.) からライセンスを受けた Super Flash®技術を使用しています。Super Flash®は SST 社の登録商標です。

本資料に記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している 場合があります。

#### 用語・略語

この仕様書で使用されている用語・略語の一部を記載します。

Analog to Digital Converter **ADC**

Advanced Programmable Motor Control Circuit A-PMD

Consumer Electronics Control CEC CG Clock control and Generations DAC Digital to Analog Converter Direct Memory Access **DMA**

Direct Memory Access Controller **DMAC**

Digital Noise Filter **DNF** External Bus Interface **EBIF**

**EHOSC** External High Speed Oscillator External Low Speed Oscillator **ELOSC** frequency of SYSTEM Clock fsvs

Full Universal Asynchronous Receiver Transmitter **FUART**

**HDMAC** High speed DMAC

Internal High Speed Oscillator **IHOSC**

Inter-Integrated Circuit  $I^2C$

INT Interrupt

**Interval Sensor Detection** ISD

Long Term Timer LTTMR

LVD Voltage Detection Circuit Multi-Function DMA controller **MDMAC** Non Break Debug Interface **NBDIF** NMI Non-Maskable Interrupt Oscillation Frequency Detector **OFD** Power On Reset Circuit

**POR**

Reset LOSC<Low Power> Manager **RLM RMC** Remote Control Signal Preprocessor

Real Time Clock **RTC**

Clock Selective Watchdog Timer **SIWDT**

**SMIF** Serial memory interface 32-bit Timer Event Counter T32A TRGSEL Trigger Selection circuit Serial Peripheral Interface **TSPI**

**UART** Universal Asynchronous Receiver Transmitter

# 1. 概要

この章では、周辺機能に関し、チャネルまたはユニット数、端子情報、その他の製品固有機能の情報 について纏めています。各周辺機能のリファレンスマニュアルと合わせてご使用ください。

# 2. 各周辺機能の情報

# 2.1. レジスタ ベースアドレス

TMPM4G グループ(1)のレジスタベースアドレスタイプを下記に示します。

表 2.1 レジスタベースアドレスタイプ (1/3)

| 周辺機能                    |                  | スアドレス: | Base Address |       |     |            |            |

|-------------------------|------------------|--------|--------------|-------|-----|------------|------------|

|                         |                  | TYPE1  | TYPE2        | TYPE3 |     |            |            |

| 高速 DMA コントローラ           | HDMAC            | ユニット A | 0            | _     | _   | 0x40000000 |            |

| 同述 DIVIA コンドローフ         | (ユニット A~B)       | ユニット B |              |       |     | 0x40001000 |            |

| シリアルメモリインタフェース          | SMIF             | ch 0   | 0            | _     | _   | 0x4000C000 |            |

| 電圧検出回路                  | LVD              | -      | 0            | _     | _   | 0x4003EC00 |            |

| ロングタームタイマ               | LTTMR            | ch 0   | 0            | _     | -   | 0x4003FF00 |            |

|                         |                  | ch 0   |              |       |     | 0x4006A000 |            |

|                         |                  | ch 1   |              | -     |     | 0x4006A400 |            |

| シリアルペリフェラルインタフェース       | TSPI<br>(ch 0~5) | ch 2   |              |       | 0   | 0x4006A800 |            |

| ラリアルベリフェブルインダフェース       |                  | ch 3   | _            |       |     | 0x4006AC00 |            |

|                         |                  | ch 4   |              |       |     | 0x4006B000 |            |

|                         |                  | ch 5   |              |       |     | 0x4006B400 |            |

| 外部バスインタフェース             | EBIF             | -      | -            | _     | 0   | 0x40076000 |            |

| デジタルノイズフィルタ回路           | DNF              | ユニット A |              | _     | - 0 |            | 0x400A0200 |

| ナンダルノイスフィルダ回路           | (ユニット A~B)       | ユニット B | _            | O     | _   | 0x400A0300 |            |

| トリガセレクタ                 | TRGSEL           | ch 0   | _            | 0     | _   | 0x400A0400 |            |

| クロック選択式ウォッチドックタイマ       | SIWDT            | ch 0   | -            | 0     | -   | 0x400A0600 |            |

| ノンブレークデバッグインタフェース       | NBD              | -      | _            | 0     | -   | 0x400A2000 |            |

| 多機能 DMA コントローラ          | MDMAC            | ユニット A | -            | 0     | -   | 0x400A4000 |            |

| 高精度非同期シリアル通信回路          | FUART            | ch 0   | _            | 0     |     | 0x400A8000 |            |

| 同相反非问州ンリアル週間凹路          | (ch 0~1)         | ch 1   |              |       | _   | 0x400A9000 |            |

| 12 ビットアナログデジタルコンバータ     | ADC              | ユニット A | -            | 0     | -   | 0x400BA000 |            |

| 8 ビットデジタルアナログコンバータ      | DAC              | ch 0   | _            |       |     | 0x400BC800 |            |

| 0 ビッド / ンダル / / ロクコンハーダ | (ch 0~1)         | ch 1   | ] -          | 0     | _   | 0x400BC900 |            |

#### 表 2.2 レジスタベースアドレスタイプ (2/3)

| 周辺機能                        |                           |       | ベースアドレスタイプ<br>(O:該当、-:非該当) |       |   | Base Address |  |

|-----------------------------|---------------------------|-------|----------------------------|-------|---|--------------|--|

|                             |                           | TYPE1 | TYPE2                      | TYPE3 |   |              |  |

|                             |                           | ch 0  |                            |       |   | 0x400C1000   |  |

|                             |                           | ch 1  |                            |       |   | 0x400C1400   |  |

|                             |                           | ch 2  |                            |       |   | 0x400C1800   |  |

|                             |                           | ch 3  |                            |       |   | 0x400C1C00   |  |

|                             |                           | ch 4  |                            |       |   | 0x400C2000   |  |

|                             |                           | ch 5  |                            |       |   | 0x400C2400   |  |

| 32 ビットタイマイベントカウンタ           | T32A                      | ch 6  | _                          | 0     | _ | 0x400C2800   |  |

| 32 = 71-3-1 (41-(21-31-72-3 | (ch 0~13)                 | ch 7  |                            | O     |   | 0x400C2C00   |  |

|                             |                           | ch 8  |                            |       |   | 0x400C3000   |  |

|                             |                           | ch 9  |                            |       |   | 0x400C3400   |  |

|                             |                           | ch 10 |                            |       |   | 0x400C3800   |  |

|                             |                           | ch 11 |                            |       |   | 0x400C3C00   |  |

|                             |                           | ch 12 |                            |       |   | 0x400C4000   |  |

|                             |                           | ch 13 |                            |       |   | 0x400C4400   |  |

|                             | TODI                      | ch 6  |                            | 0     | - | 0x400CB800   |  |

| シリアルペリフェラルインタフェース           | TSPI<br>(ch 6~8)          | ch 7  | -                          |       |   | 0x400CBC00   |  |

|                             |                           | ch 8  |                            |       |   | 0x400CC000   |  |

|                             |                           | ch 0  |                            |       |   | 0x400CE000   |  |

|                             |                           | ch 1  |                            |       |   | 0x400CE400   |  |

| ┃<br>┃ 非同期シリアル通信回路          | UART                      | ch 2  | _                          | 0     | _ | 0x400CE800   |  |

| 非问期ンリアル通信凹陷<br>             | (ch 0~5)                  | ch 3  | _                          | O     | _ | 0x400CEC00   |  |

|                             |                           | ch 4  |                            |       |   | 0x400CF000   |  |

|                             |                           | ch 5  |                            |       |   | 0x400CF400   |  |

|                             |                           | ch 0  |                            |       |   | 0x400D1000   |  |

|                             | 120                       | ch 1  |                            |       |   | 0x400D2000   |  |

| I <sup>2</sup> C インタフェース    | I <sup>2</sup> C (ch 0~4) | ch 2  | -                          | 0     | - | 0x400D3000   |  |

|                             | (611 04)                  | ch 3  |                            |       |   | 0x400D4000   |  |

|                             |                           | ch 4  |                            |       |   | 0x400D5000   |  |

#### 表 2.3 レジスタベースアドレスタイプ (3/3)

| 周辺機能                 |                   | スアドレス:<br>亥当、-:非 | Base Address |       |       |            |

|----------------------|-------------------|------------------|--------------|-------|-------|------------|

|                      |                   |                  | TYPE1        | TYPE2 | TYPE3 |            |

| トリミング回路              | TRM               | -                | -            | 0     | -     | 0x400E3100 |

| 周波数検知回路              | OFD               | -                | -            | 0     | -     | 0x400E4000 |

| リアルタイムクロック           | RTC               | -                | -            | 0     | -     | 0x400E4800 |

| CEC 制御回路             | CEC               | ch 0             | -            | 0     | -     | 0x400E8000 |

| リモコン受信回路             | RMC<br>(ch 0~1)   | ch 0             |              | 0     |       | 0x400E8100 |

| りてコン支信回路             |                   | ch 1             | -            |       | -     | 0x400E8200 |

| アドバンストプログラマブルモータ制御回路 | A-PMD             | ch 0             | -            | 0     | -     | 0x400E9000 |

|                      | ISD<br>(ユニット A~C) | ユニット A           |              |       |       | 0x400F0000 |

| インタバルセンサ検知回路         |                   | ユニット B           | -            | 0     | -     | 0x400F0100 |

|                      | (==>1 / ( 0)      | ユニット C           |              |       |       | 0x400F0200 |

| フラッシュメモリ             | FLASH             | -                | 0            | -     | -     | 0x5DFF0000 |

上記のベースアドレスタイプを参照し、各周辺機能の開発を行ってください。

### 2.2. トリガセレクタ(TRGSEL)

トリガセレクタは、周辺機能、ポートなどから入力された複数のトリガから、1つのトリガを選択し 周辺機能にトリガ信号を出力する回路です。

8本のトリガから[TSELOCRn]<INSELm>で選択されたトリガを、接続先の周辺機能に出力します。

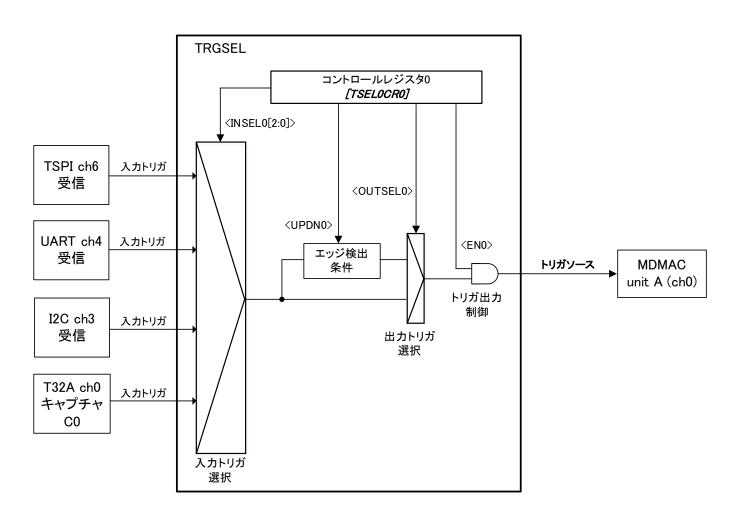

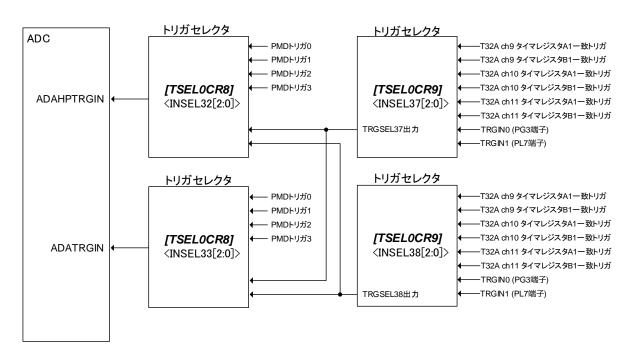

図 2.1 トリガセレクタ接続例は、TSPI, UART, I2C, T32A からのトリガ信号が、トリガセレクタ経由で DMA コントローラに接続されている例です。[TSELOCRO] <INSELO>で入力トリガ選択、エッジ検出の許可/禁止とエッジ検出条件の設定および出力トリガの許可/禁止制御を行います。

図 2.1 トリガセレクタ接続例

#### 2.2.1. トリガセレクタと製品対応

TMPM4G グループ(1)のトリガセレクタは、14 本の制御レジスタ(*[TSEL0CR0~13]*)で構成されており 56 本のトリガを制御できます。

下記の表にコントロールレジスタと接続先および対応製品を示します。

表 2.4 製品別トリガセレクタ対応一覧 (1/6)

| 1.25=6      |               | 111477 -                         | 7 41114                         | 製品対応 (〇:あり、×:なし) |      |      |      |  |  |

|-------------|---------------|----------------------------------|---------------------------------|------------------|------|------|------|--|--|

| レジスタ        | Bit Symbol    | トリガソース                           | 入力トリガ                           | M4G9             | M4G8 | M4G7 | M4G6 |  |  |

|             |               |                                  | ·TSPI ch6 受信 DMA 要求             | 0                | 0    | ×    | ×    |  |  |

|             | INCEL 0[0.0]  | MDMAC                            | ・UART ch4 受信 DMA 要求             | 0                | 0    | ×    | ×    |  |  |

|             | INSEL0[2:0]   | A<br>ch0                         | ·I <sup>2</sup> C ch3 受信 DMA 要求 | 0                | 0    | ×    | ×    |  |  |

|             |               |                                  | ・T32A ch0 DMA 要求 キャプチャ A0       | 0                | 0    | 0    | 0    |  |  |

|             |               |                                  | ·TSPI ch6 送信 DMA 要求             | 0                | 0    | ×    | ×    |  |  |

|             | INSEL1[2:0]   | MDMAC                            | ·UART ch4 送信 DMA 要求             | 0                | 0    | ×    | ×    |  |  |

| (TCEL OCDO) | INSELI[2.0]   | A<br>ch1                         | ·I <sup>2</sup> C ch3 送信 DMA 要求 | 0                | 0    | ×    | ×    |  |  |

| [TSEL0CR0]  |               |                                  | ・T32A ch0 DMA 要求 キャプチャ C0       | 0                | 0    | 0    | 0    |  |  |

|             |               | MDMAC                            | ·TSPI ch7 受信 DMA 要求             | 0                | 0    | ×    | ×    |  |  |

|             | INSEL2[2:0]   | A<br>ch2                         | ·FUART ch1 受信 DMA 要求            | 0                | 0    | ×    | ×    |  |  |

|             |               |                                  | ·I <sup>2</sup> C ch4 受信 DMA 要求 | 0                | 0    | ×    | ×    |  |  |

|             | INSEL3[2:0]   | MDMAC<br>A<br>ch3                | •TSPI ch7 送信 DMA 要求             | 0                | 0    | ×    | ×    |  |  |

|             |               |                                  | •FUART ch1 送信 DMA 要求            | 0                | 0    | ×    | ×    |  |  |

|             |               |                                  | ·I <sup>2</sup> C ch4 送信 DMA 要求 | 0                | 0    | ×    | ×    |  |  |

|             | INSEL4[2:0]   | MDMAC<br>A<br>ch4                | ·TSPI ch8 受信 DMA 要求             | 0                | ×    | ×    | ×    |  |  |

|             |               |                                  | ・T32A ch0 DMA 要求 レジスタ A1 一致     | 0                | 0    | 0    | 0    |  |  |

|             |               |                                  | ・T32A ch0 DMA 要求 レジスタ C1 一致     | 0                | 0    | 0    | 0    |  |  |

|             |               | MDMAC                            | ·TSPI ch8 送信 DMA 要求             | 0                | ×    | ×    | ×    |  |  |

|             | INSEL5[2:0] A |                                  | ・T32A ch0 DMA 要求 レジスタB1 一致      | 0                | 0    | 0    | 0    |  |  |

|             |               | ch5<br>・T32A ch0 DMA 要求 キャプチャ B0 |                                 | 0                | 0    | 0    | 0    |  |  |

| [TSEL0CR1]  |               |                                  | ・T32A ch1 DMA 要求 レジスタ A1 一致     | 0                | 0    | 0    | 0    |  |  |

| [TSELUCKI]  |               | MDMAC                            | ・T32A ch1 DMA 要求 レジスタ C1 一致     | 0                | 0    | 0    | 0    |  |  |

|             | INSEL6[2:0]   | A<br>ch6                         | ・T32A ch1 DMA 要求 キャプチャ A0       | 0                | 0    | 0    | 0    |  |  |

|             |               |                                  | ・T32A ch1 DMA 要求 キャプチャ C0       | 0                | 0    | 0    | 0    |  |  |

|             |               |                                  | ・T32A ch1 DMA 要求 レジスタB1 一致      | 0                | 0    | 0    | 0    |  |  |

|             | INSEL7[2:0]   | MDMAC                            | ・T32A ch1 DMA 要求 キャプチャ B0       | 0                | 0    | 0    | 0    |  |  |

|             | INOLLI[Z.U]   | A<br>ch7                         | ·UART ch0 受信 DMA 要求             | 0                | 0    | 0    | 0    |  |  |

|             |               |                                  | ·I <sup>2</sup> C ch0 受信 DMA 要求 | 0                | 0    | 0    | 0    |  |  |

表 2.5 製品別トリガセレクタ対応一覧 (2/6)

| 1.35= A    |                |                       | トリガソース 入力トリガ                    |      | 対応 (〇 | :あり、× : | :なし) |  |    |                                 |   |   |   |   |

|------------|----------------|-----------------------|---------------------------------|------|-------|---------|------|--|----|---------------------------------|---|---|---|---|

| レジスタ       | Bit Symbol     | トリガソース 入力トリガ          |                                 | M4G9 | M4G8  | M4G7    | M4G6 |  |    |                                 |   |   |   |   |

|            |                |                       | ・T32A ch2 DMA 要求 レジスタ A1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INCEL 0[0.0]   | MDMAC                 | ・T32A ch2 DMA 要求 レジスタ C1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INSEL8[2:0]    | A<br>ch8              | ・T32A ch2 DMA 要求 キャプチャ A0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                | 01.0                  | ・T32A ch2 DMA 要求 キャプチャ C0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                |                       | ・T32A ch2 DMA 要求 レジスタ B1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INCEL 0[0:0]   | MDMAC                 | ・T32A ch2 DMA 要求 キャプチャ B0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INSEL9[2:0]    | A<br>ch9              | ·UART ch0 送信 DMA 要求             | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

| [TSEL0CR2] |                | 0.10                  | ·I <sup>2</sup> C ch0 送信 DMA 要求 | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

| [TOLLOOKE] |                |                       | ・T32A ch3 DMA 要求 レジスタ A1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INCEL 40(2:01  | MDMAC                 | ・T32A ch3 DMA 要求 レジスタ C1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INSEL10[2:0]   | A<br>ch10             | ・T32A ch3 DMA 要求 キャプチャ A0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                | CITTO                 | ・T32A ch3 DMA 要求 キャプチャ C0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                |                       | ・T32A ch3 DMA 要求 レジスタ B1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INSEL11[2:0]   | MDMAC<br>A<br>ch11    | ・T32A ch3 DMA 要求 キャプチャ B0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                |                       | ・UART ch1 受信 DMA 要求             | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                |                       | •I <sup>2</sup> C ch1 受信 DMA 要求 | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                | MDMAC<br>SEL12[2:0] A | ・T32A ch4 DMA 要求 レジスタ A1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INICEL 12[2:0] |                       | ・T32A ch4 DMA 要求 レジスタ C1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INSEL12[2:0]   | ch12                  | ・T32A ch4 DMA 要求 キャプチャ A0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                | OIIIZ                 | ・T32A ch4 DMA 要求 キャプチャ C0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                |                       | ・T32A ch4 DMA 要求 レジスタ B1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INSEL13[2:0]   | MDMAC                 | ・T32A ch4 DMA 要求 キャプチャ B0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INSEL IS[2.0]  | A<br>ch13             | ・UART ch1 送信 DMA 要求             | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

| [TSEL0CR3] |                | 55                    | ·I <sup>2</sup> C ch1 送信 DMA 要求 | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

| [ISELUCKS] |                |                       | ・T32A ch5 DMA 要求 レジスタ A1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INSEL14[2:0]   | MDMAC                 | ・T32A ch5 DMA 要求 レジスタ C1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | 11NSEL 14[2.0] | A<br>ch14             | ・T32A ch5 DMA 要求 キャプチャ A0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                | 5                     | ・T32A ch5 DMA 要求 キャプチャ C0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                |                       | ・T32A ch5 DMA 要求 レジスタ B1 一致     | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | INSEL15[2:0]   | MDMAC                 | ・T32A ch5 DMA 要求 キャプチャ B0       | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            | NSEL   5 2:0]  | A<br>ch15             | ·FUART ch0 送信 DMA 要求            | 0    | 0     | 0       | 0    |  |    |                                 |   |   |   |   |

|            |                |                       |                                 |      |       |         |      |  | 55 | ・I <sup>2</sup> C ch2 送信 DMA 要求 | 0 | 0 | 0 | 0 |

表 2.6 製品別トリガセレクタ対応一覧 (3/6)

| レジスタ        |                | 11145.             | トリガソース 入力トリガ                    |      | 対応 (O | :あり、× : | :なし) |

|-------------|----------------|--------------------|---------------------------------|------|-------|---------|------|

| レンスタ        | Bit Symbol     | トリカソース             | スカトリカ                           | M4G9 | M4G8  | M4G7    | M4G6 |

|             |                |                    | ・T32A ch6 DMA 要求 レジスタ A1 一致     | 0    | 0     | 0       | 0    |

|             | INIOEL 4010-01 | MDMAC              | ・T32A ch6 DMA 要求 レジスタ C1 一致     | 0    | 0     | 0       | 0    |

|             | INSEL16[2:0]   | A<br>ch16          | ・T32A ch6 DMA 要求 キャプチャ A0       | 0    | 0     | 0       | 0    |

|             |                | 01110              | ・T32A ch6 DMA 要求 キャプチャ C0       | 0    | 0     | 0       | 0    |

|             |                |                    | ・T32A ch6 DMA 要求 レジスタ B1 一致     | 0    | 0     | 0       | 0    |

|             | INICEL 47[0:0] | MDMAC              | ・T32A ch6 DMA 要求 キャプチャ B0       | 0    | 0     | 0       | 0    |

|             | INSEL17[2:0]   | A<br>ch17          | ·FUART ch0 受信 DMA 要求            | 0    | 0     | 0       | 0    |

| ITCEL ACDAI |                | 01117              | ·I <sup>2</sup> C ch2 受信 DMA 要求 | 0    | 0     | 0       | 0    |

| [TSEL0CR4]  |                |                    | ・T32A ch7 DMA 要求 レジスタ A1 一致     | 0    | 0     | 0       | 0    |

|             | INIOEL 4010-01 | MDMAC              | ・T32A ch7 DMA 要求 レジスタ C1 一致     | 0    | 0     | 0       | 0    |

|             | INSEL18[2:0]   | A<br>ch18          | ・T32A ch7 DMA 要求 キャプチャ A0       | 0    | 0     | 0       | 0    |

|             |                | 01110              | ・T32A ch7 DMA 要求 キャプチャ C0       | 0    | 0     | 0       | 0    |

|             |                |                    | ・T32A ch7 DMA 要求 レジスタ B1 一致     | 0    | 0     | 0       | 0    |

|             | INIOEL 4010-01 | MDMAC              | ・T32A ch7 DMA 要求 キャプチャ B0       | 0    | 0     | 0       | 0    |

|             | INSEL19[2:0]   | A<br>ch19          | ·UART ch2 受信 DMA 要求             | 0    | 0     | 0       | 0    |

|             |                |                    | ・ADC ユニット A 汎用トリガ DMA 要求        | 0    | 0     | 0       | 0    |

|             |                |                    | ・T32A ch8 DMA 要求 レジスタ A1 一致     | 0    | 0     | 0       | 0    |

|             | INICEL 2012-01 | MDMAC<br>A<br>ch20 | ・T32A ch8 DMA 要求 レジスタ C1 一致     | 0    | 0     | 0       | 0    |

|             | INSEL20[2:0]   |                    | ・T32A ch8 DMA 要求 キャプチャ A0       | 0    | 0     | 0       | 0    |

|             |                | 01.20              | ・T32A ch8 DMA 要求 キャプチャ C0       | 0    | 0     | 0       | 0    |

|             |                |                    | ・T32A ch8 DMA 要求 レジスタ B1 一致     | 0    | 0     | 0       | 0    |

|             | INICEL 24[2:0] | MDMAC              | ・T32A ch8 DMA 要求 キャプチャ B0       | 0    | 0     | 0       | 0    |

|             | INSEL21[2:0]   | A<br>ch21          | ・UART ch2 送信 DMA 要求             | 0    | 0     | 0       | 0    |

| ITCEL ACDEL |                | 01.21              | ・ADC ユニット A 最優先 DMA 要求          | 0    | 0     | 0       | 0    |

| [TSEL0CR5]  |                |                    | ・T32A ch9 DMA 要求 レジスタ A1 一致     | 0    | 0     | 0       | 0    |

|             | INICEL 22[2:0] | MDMAC              | ・T32A ch9 DMA 要求 レジスタ C1 一致     | 0    | 0     | 0       | 0    |

|             | INSEL22[2:0]   | A<br>ch22          | ・T32A ch9 DMA 要求 キャプチャ A0       | 0    | 0     | 0       | 0    |

|             |                | V                  | ・T32A ch9 DMA 要求 キャプチャ C0       | 0    | 0     | 0       | 0    |

|             |                |                    | ・T32A ch9 DMA 要求 レジスタ B1 一致     | 0    | 0     | 0       | 0    |

|             | INSEL23[2:0]   | MDMAC              | ・T32A ch9 DMA 要求 キャプチャ B0       | 0    | 0     | 0       | 0    |

|             | NOEL23[2.0]    | A<br>ch23          | ・T32A ch9 DMA 要求 キャプチャ A1       | 0    | 0     | 0       | 0    |

|             |                |                    | ・T32A ch9 DMA 要求 キャプチャ B1       | 0    | 0     | 0       | 0    |

#### 表 2.7 製品別トリガセレクタ対応一覧 (4/6)

| 1.22-6      |                | トリガソース             | 3 41 1142                    | 製品   | 対応 (〇 | :あり、× : | :なし) |

|-------------|----------------|--------------------|------------------------------|------|-------|---------|------|

| レジスタ        | Bit Symbol     | トリルソース             | 入力トリガ                        | M4G9 | M4G8  | M4G7    | M4G6 |

|             |                |                    | ・T32A ch10 DMA 要求 レジスタ A1 一致 | 0    | 0     | 0       | 0    |

|             | INICEL 0410-01 | MDMAC              | ・T32A ch10 DMA 要求 レジスタ C1 一致 | 0    | 0     | 0       | 0    |

|             | INSEL24[2:0]   | A<br>ch24          | ・T32A ch10 DMA 要求 キャプチャ A0   | 0    | 0     | 0       | 0    |

|             |                | 01121              | ・T32A ch10 DMA 要求 キャプチャ C0   | 0    | 0     | 0       | 0    |

|             |                |                    | ・T32A ch10 DMA 要求 レジスタ B1 一致 | 0    | 0     | 0       | 0    |

|             | INICEL OFFO    | MDMAC              | ・T32A ch10 DMA 要求 キャプチャ B0   | 0    | 0     | 0       | 0    |

|             | INSEL25[2:0]   | A<br>ch25          | ・T32A ch10 DMA 要求 キャプチャ A1   | 0    | 0     | 0       | 0    |

| ITSEL OCDEL |                | 01120              | ・T32A ch10 DMA 要求 キャプチャ B1   | 0    | 0     | 0       | 0    |

| [TSEL0CR6]  |                |                    | ・T32A ch11 DMA 要求 レジスタ A1 一致 | 0    | 0     | 0       | 0    |

|             | INCEL OCIO-O   | MDMAC              | ・T32A ch11 DMA 要求 レジスタ C1 一致 | 0    | 0     | 0       | 0    |

|             | INSEL26[2:0]   | A<br>ch26          | ・T32A ch11 DMA 要求 キャプチャ A0   | 0    | 0     | 0       | 0    |

|             |                | 01120              | ・T32A ch11 DMA 要求 キャプチャ C0   | 0    | 0     | 0       | 0    |

|             | INSEL27[2:0]   |                    | ・T32A ch11 DMA 要求 レジスタ B1 一致 | 0    | 0     | 0       | 0    |

|             |                | MDMAC<br>A<br>ch27 | ・T32A ch11 DMA 要求 キャプチャ B0   | 0    | 0     | 0       | 0    |

|             |                |                    | ・T32A ch11 DMA 要求 キャプチャ A1   | 0    | 0     | 0       | 0    |

|             |                |                    | ・T32A ch11 DMA 要求 キャプチャ B1   | 0    | 0     | 0       | 0    |

|             | INSEL28[2:0]   | MDMAC              | ・T32A ch12 DMA 要求 レジスタ A1 一致 | 0    | 0     | 0       | 0    |

|             |                | Α                  | ・T32A ch12 DMA 要求 レジスタ C1 一致 | 0    | 0     | 0       | 0    |

|             |                | ch28               | ・UART ch3 受信 DMA 要求          | 0    | 0     | 0       | ×    |

|             |                | MDMAC              | ・T32A ch12 DMA 要求 レジスタ B1 一致 | 0    | 0     | 0       | 0    |

|             | INSEL29[2:0]   | Α                  | ・UART ch3 送信 DMA 要求          | 0    | 0     | 0       | ×    |

| ITSEL OCDZI |                | ch29               | ・A-PMD ch0 PWM 割り込み          | 0    | 0     | 0       | 0    |

| [TSEL0CR7]  |                | MDMAC              | ・T32A ch13 DMA 要求 レジスタ A1 一致 | 0    | 0     | 0       | 0    |

|             | INSEL30[2:0]   | Α                  | ・T32A ch13 DMA 要求 レジスタ C1 一致 | 0    | 0     | 0       | 0    |

|             |                | ch30               | ・UART ch5 受信 DMA 要求          | 0    | ×     | ×       | ×    |

|             |                | MDMAC              | ・T32A ch13 DMA 要求 レジスタ B1 一致 | 0    | 0     | 0       | 0    |

|             | INSEL31[2:0]   | Α                  | ・UART ch5 送信 DMA 要求          | 0    | ×     | ×       | ×    |

|             |                | ch31               | ·TRGIN2 (PT3 端子)             | 0    | 0     | 0       | 0    |

#### 表 2.8 製品別トリガセレクタ対応一覧 (5/6)

| 1.257 h    |                | トリガソース             | 3 41 1122                   | 製品                          | 製品対応 (〇:あり、×:なし) |      |      |   |  |