# Bipolar Transistors Thermal stability and thermal design

## **Description**

This document describes the thermal stability and thermal design of bipolar transistors.

### **Table of Contents**

| Description                                                     | 1  |

|-----------------------------------------------------------------|----|

| Table of Contents                                               | 2  |

| 1. Thermal stability and thermal design for transistor circuits | 4  |

| 1.1. Temperature characteristics of transistors                 | 4  |

| 1.2. Thermal design                                             | 8  |

| 1.3. Thermal resistance                                         | 13 |

| 1.4. Example of thermal design calculation                      | 15 |

| 1.5. Thermal design taking reliability into consideration       | 18 |

| RESTRICTIONS ON PRODUCT USE                                     | 20 |

# **List of Figures**

| Figure 1.1 Stability factors for bias circuits                                      | 7    |

|-------------------------------------------------------------------------------------|------|

| Figure 1.2 Equivalent thermal circuit                                               | 8    |

| Figure 1.3 Circuit of transient thermal impedance                                   | 9    |

| Figure 1.4 Temperature change when pulse loss is applied                            | . 10 |

| Figure 1.5 Example of transient thermal impedance                                   | . 12 |

| Figure 1.6 The approximation to a square waveform of the loss waveform              | . 12 |

| Figure 1.7 The method to approximate a sine wave and a triangular wave loss wavefor | orm  |

| to a square waveform                                                                | . 12 |

| Figure 1.8 Heat sink surface area vs. thermal resistance                            | . 14 |

#### 1. Thermal stability and thermal design for transistor circuits

As described in Chapter 1, one of the characteristics of transistors and other semiconductor devices is that the electrical characteristics are very sensitive to temperature. Therefore, when creating a circuit design, it is necessary to consider changes in the operating point due to changes in temperature.

#### 1.1. Temperature characteristics of transistors

#### (1) Thermal stability

The performance stability factor S is defined by:

$$S = \frac{\partial I_C}{\partial I_{CBO}} \qquad (1-1)$$

This equation represents a change in the collector current  $I_C$  in response to a change in the collector cut-off current due to a change in temperature. The transistor parameters with the greatest temperature dependence are the cut-off current  $I_{CBO}$  ( $I_{CEO}$ ) and the base-emitter voltage  $V_{BF}$ . These parameters are expressed as a function of temperature:

$$I_{CBO(T_X)} = I_{CBO(T_O)} e^{K(T_X-T_O)}$$

..... (1-2)

$$I_{\text{F}} = I_{\text{CBO}} e^{\frac{q V_{\text{BE}}}{k T}} \qquad (1-3)$$

T<sub>O</sub>: Reference temperature (K)

$T_X$ : Temperature to be found (K)

K : Temperature coefficient, which is generally 0.07/ °C to 0.08/ °C for silicon transistors

q : Elementary charge  $(1.602 \times 10^{-19})$  C)

k : Boltzmann constant (1.38×10<sup>-23</sup> J/ K)

T: Absolute temperature (K)

Let the power dissipation applied to a junction be  $P_C$ . Then, a change in  $P_C$ ,  $\Delta P_{C(1)}$ , due to some reason causes a junction temperature change of  $\Delta P_{C(1)}R_{th(j-a)}$ . This causes changes in  $I_{CBO}$  and  $V_{BE}$  ( $\Delta I_{CBO}$  and  $\Delta V_{BE}$ ), which in turn cause changes of S  $I_{CBO}$  and  $g_m$   $\Delta V_{BE}$  in the collector current respectively. (The transconductance  $g_m$  of the transistor is defined as  $g_m = \partial I_C / \partial V_{BE}$ .)

If the variation in the power dissipation caused by these changes,  $P_{C(2)}$ , is greater than  $\Delta P_{C(1)}$ , the junction temperature continues to increase. It is therefore necessary to keep

the power dissipation due to  $\Delta I_{CBO}$  and  $\Delta V_{BE}$ ,  $P_{C(2)}$ , below  $P_{C(1)}$ .

Hence, it is considered that a transistor is stable when the following condition is met:

$$\Delta P_{C(1)} \ge V_C \left( S \Delta I_{CBO} + g_m \Delta V_{BE} \right) \quad \cdots \qquad (1-4)$$

where, V<sub>C</sub> is collector voltage.

Equation 1-4 can be restated as:

$$V_C S \frac{\Delta I_{CBO}}{\Delta P_C} + V_C gm \frac{\Delta V_{BE}}{\Delta P_C} \le 1$$

(1-5)

As  $\Delta T$  is considered to be equal to  $\Delta P_C R_{th(j-a)}$ , differentiating Equation 1-2 with respect to  $P_C$  gives:

$$\frac{\Delta I_{CBO}}{\Delta P_{C}} = \frac{\Delta I_{CBO}}{\Delta T} \frac{\Delta T}{\Delta P_{C}} = K R_{th (j-a)} I_{CBO(T_{0})} e^{K(T_{X} - T_{0} + P_{C} R_{th (j-a)})} \cdots (1-6)$$

From Equation 1-3, the temperature characteristics of  $V_{BE}$  that provide a constant  $I_{E}$  can be calculated as follows:

$$\frac{\Delta V_{BE}}{\Delta T} \approx \frac{k K T}{q} \approx -2.0 \times 10^{-3} \text{ V/°C} \qquad (1-7)$$

\*  $\Delta V_{BE}/\Delta T$  is normally calculated to be -1.8 to -2.2 mV/ °C depending on the bias condition of the transistor. In general, -2 mV/ °C is used as a typical temperature coefficient. The temperature coefficient of a Darlington transistor is twice as great as this value (-4.0 to -4.5 mV/ °C).

Hence:

$$\frac{\Delta V_{BE}}{\Delta P_{C}} = \frac{\Delta V_{BE}}{\Delta T} \frac{\Delta T}{\Delta P_{C}} \approx -2.0 \times 10^{-3} \times R_{th (j-a)}$$

(1-8)

Substituting Equations 1-6 and 1-8 into Equation 1-5 gives:

$$V_{C} S K R_{th (j-a)} I_{CBO(T_{O})} e^{K(T_{X}-T_{O}+P_{C}R_{th (j-a)})} - 2.0 \times 10^{-3} R_{th (j-a)} V_{C} gm \le 1$$

$$\cdots \cdots (1-9)$$

$$T_{X} - T_{O} + P_{C} R_{th (j-a)} \ge T_{jmax} - T_{O}$$

A transistor circuit is considered stable if Equation 1-9 is satisfied. However, this equation is too complicated to be of practical use. When changes in  $I_C$  in the definition of S in response to changes in  $V_{BE}$  are taken into consideration, the second term of Equation 1-9 can be ignored in practice. Therefore, Equation 1-9 can be simplified to:

$$V_{C} \; S \; K \; R_{th \; (\; j \; - \; a \;)} \; I_{CBO \; (\; To \;)} \; e^{\; K \; (\; Tx \; - \; To \; + \; P_{C} \; R_{th} \; (\; j \; - \; a \;))} \leq 1 \qquad \cdots \qquad (1-10)$$

$$Tx - To + P_C R_{th(j-a)} \ge T_{jmax} - To$$

The critical voltage V<sub>crit</sub> is defined as:

$$V_{crit} = \frac{1}{S K R_{th (j-a)} I_{CBO (To)}}$$

(1-11)

Substituting Equation 1-11 into Equation 1-10 gives:

$$\frac{V_{C}}{V_{crit}} e^{K \left( Tx - To + P_{C} R_{th \, (j-a)} \right)} \leq 1 \qquad (1-12)$$

Let K be 0.08 and the reference temperature  $T_0$  (ambient temperature) be 25 °C. Then, Equation 1-12 can be restated as:

$$P_{C} R_{th(j-a)} + T - 25 \le 29 ln \frac{V_{C}}{V_{crit}}$$

(1-13)

Therefore, Equation 1-11 and Equation 1-13 represent the conditions that a transistor circuit must satisfy to maintain stability.

#### (2) Stability factors for bias circuits

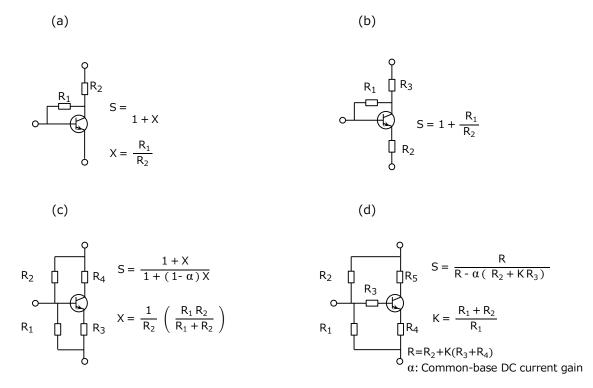

Figure 1.1 shows the stability factors for several bias circuits. (a), (b), and (c) are typical bias circuits whereas (d) is a bias circuit in which the DC resistance of the input transformer cannot be ignored.

Figure 1.1 Stability factors for bias circuits

Generally, it is preferable for a stability factor to be small. However, a reduction in the stability factor increases DC dissipation, causing efficiency to deteriorate. Since reducing the stability factor causes an increase in DC dissipation, a temperature-compensating device is generally used to improve the thermal stability of the output-stage bias circuit.

The use of a temperature-compensating device makes it possible to freely select a thermal stability level. Thermistors and varistors are commonly used as temperature-compensating devices. For how to use these devices, refer to the respective technical documents.

#### 1.2. Thermal design

(1) Maximum allowable collector power dissipation and equivalent thermal circuit When the bias circuit is sufficiently thermally stable, the maximum collector power dissipation ( $P_{Cmax}$ ) of a transistor can be expressed as follows in terms of the ambient temperature  $T_a$ , the transistor's maximum junction temperature  $T_{jmax}$ , and the total thermal resistance from the junction to the ambient  $R_{th(j-a)}$ :

$$P_{C \max(T_{a})} = \frac{T_{j \max} - T_{a}}{R_{th(j-a)}}, \quad P_{C \max(T_{c})} = \frac{T_{j \max} - T_{c}}{R_{th(j-c)}} \quad \dots \quad (1-14)$$

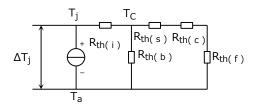

A heat flow can be modeled by analogy to an electrical circuit. Using this model, the heat flow from the junction of a transistor to the ambient air is expressed using thermal resistances and thermal capacitances. Figure 1.2 shows an equivalent thermal circuit in a thermally steady state.

$R_{th(i)}$ : Junction-to-case thermal resistance

$R_{th(b)}$ : Case-to-ambient thermal resistance

$R_{th(s)}\;$  : Thermal resistance of an insulation plate

$R_{\text{th(c)}}\,\,$  : Contact thermal resistance between case

and heat sink

Figure 1.2 Equivalent thermal circuit

$R_{th(f)}$ : Thermal resistance of a heat sink

From the equivalent circuit of Figure 1.2, the junction-to-ambient thermal resistance  $R_{\text{th(j-a)}}$  can be calculated as follows:

$$R_{th(j-a)} = R_{th(i)} + \frac{R_{th(b)}(R_{th(s)} + R_{th(s)} + R_{th(f)})}{R_{th(b)} + R_{th(s)} + R_{th(f)} + R_{th(f)}}$$

(1-15)

Since no heat sink is generally used for transistors with medium or lower output,  $R_{th(j-a)}$  can be calculated as:

$$R_{th(j-a)} = R_{th(i)} + R_{th(b)}$$

..... (1-16)

The datasheets for low- or medium-output transistors show their maximum allowable collector power dissipation at an ambient temperature ( $T_a$ ) of 25 °C. This is calculated as follows from  $R_{th(j-a)}$  given by Equation 1-16 and  $T_{jmax}$ .

$$P_{\text{Cmax}(Ta = 25 °C)} = \frac{T_{j \text{ max}} - 25}{R_{\text{th}(j-a)}}$$

(1-17)

The case-to-ambient thermal resistance  $R_{th(b)}$  varies with the material and shape of the case. Generally,  $R_{th(b)}$  is significantly larger than  $R_{th(i)}$ ,  $R_{th(c)}$ ,  $R_{th(s)}$ , and  $R_{th(f)}$ . Therefore, Equation 1-15 can be simplified to:

$$R_{th(j-a)} = R_{th(i)} + R_{th(c)} + R_{th(s)} + R_{th(f)} + R_{th(f)}$$

.....(1-18)

Equation 1-18 can be used to create a thermal design that satisfies the maximum rating requirement for DC dissipation. When transistors are used in a switching circuit, great care is required to ensure that the peak  $T_j$  value does not exceed  $T_{jmax}$ .

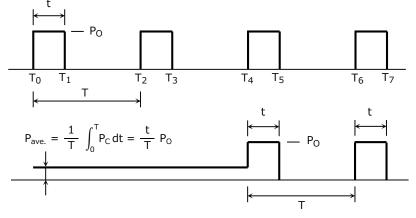

#### (2) Pulse response of junction temperature

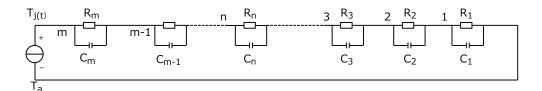

Generally, the thermal impedance of a transistor is modeled as a distributed constant circuit as shown in Figure 1.3.

Figure 1.3 Circuit of transient thermal impedance

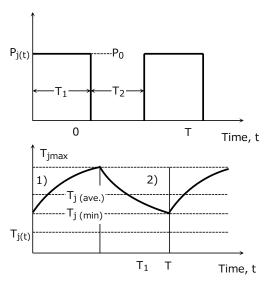

Figure 1.4 Temperature change when pulse loss is applied

When the pulse dissipation  $P_{j(t)}$  shown in Figure 1.4 is applied to the circuit of Figure 1.3, a change in junction temperature  $T_{j(t)}$  that appears at the mth parallel RC circuit under stable thermal conditions can be calculated as follows:

1) In the region where  $P_{i(t)} = P_0$ :

$$\begin{split} &T_{j(t)} = \sum_{n=1}^{m} \{ (\ P_0 \, R_n \ ) \ -T_{n \, (min \, )} \} \bigg\{ \, 1 - e^{\, \left( \, \frac{-t}{C_n \, R_n} \, \right)} \, \, \bigg\} \, \, + \\ &T_{n \, (min \, )} \end{split}$$

2) In the region where  $P_{j(t)} = 0$ :

$$T_{j(t)} = \sum_{n=1}^{m} \left\{ T_{n(min)} e^{\left(\frac{-t}{C_n R_n}\right)} \right\}$$

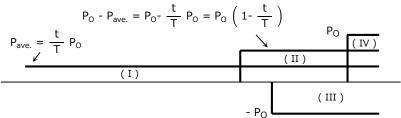

For typical transistors, the actual  $P_{j(t)}$  value can be approximated by substituting 4 for n. However, if the C and R values are indefinite, it is difficult to calculate  $T_j$ . Therefore,  $T_{jmax}$  is generally calculated using transient thermal impedance as follows:

Figure 1.5 shows an example of typical transient thermal impedance characteristics.

Suppose that a single rectangular pulse (with a pulse width of t and a peak value of  $P_0$ ) is applied. From the Figure, we read the transient thermal impedance at a pulse width of t, and then use Equation 1-21 to calculate  $T_{jmax}$ .

$$T_{j \text{ (max)}} = r_{th \text{ (t)}} P_0 + T_a$$

..... (1-21)

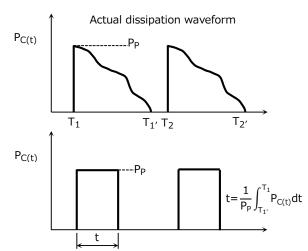

When a repetitive pulse train with a cyclic period of T is applied as shown in Figure 1.4,  $T_{ipeak}$  is given by Equation 1-22 using the principle of superposition.

(a) Repetitive application of dissipation

(b) Approximated dissipation

(c) Using the principle of superposition

$$\Delta T_{j(I)} = P_0 \frac{t}{T} R_{th(j-a)}$$

$$\Delta T_{j(II)} = P_{O} \left( 1 - \frac{t}{T} \right) r_{th(T+t)}$$

$$\Delta T_{j (III)} = - P_{O} r_{th(T)}$$

$$\Delta T_{j(IV)} = P_0 r_{th(t)}$$

$$T_{j \text{ (max )}} = P_{O} \left[ \frac{t}{T} R_{th (j-a)} + \left( 1 + \frac{t}{T} \right) r_{th (T+t)} - r_{th (T)} + r_{th (t)} \right] + T_{a}$$

..... (1-22)

Equation 1-22 is applicable only to the thermally limited region of the SOA where no current concentration occurs due to secondary breakdown.

Great care should be exercised in the thermal design for a pulsed power application to ensure that  $T_{jmax}$  given by Equation 1-22 does not exceed the maximum rated junction temperature of the transistor.

Figure 1.5 Example of transient thermal impedance

Figure 1.6 The approximation to a square waveform of the loss waveform

The above description assumes that a rectangular waveform is applied to a transistor. However, for actual transistor applications, a rectangular  $P_{j(t)}$  waveform is seldom used.

Therefore, in order to estimate  $T_{jpeak}$  using Equation 1-22, a power dissipation waveform should be approximated to a rectangular wave as shown in Figure 1.6.

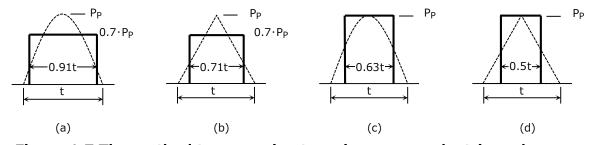

Sine and triangular waves can be approximated to rectangular waves as shown in Figure 1.7.

$T_{o}$  obtain a rectangle with an area equal to a half-sine or triangle area, multiply the peak value of  $P_{P}$  by 0.7 in the case of (a) and (b), and multiply the pulse width by 0.91 for (a) and by 0.71 for (b).

In the case of (c) and (d), use the same peak value of  $P_P$ , and multiply the pulse width by 0.63 for (c) and by 0.5 for (d).

Figure 1.7 The method to approximate a sine wave and a triangular wave loss waveform to a square waveform

#### 1.3. Thermal resistance

The thermal resistance values shown in the equivalent thermal circuit of Figure 1.2 can be explained as follows:

(1) Junction-to-case thermal resistance (internal thermal resistance):  $R_{th(i)}$  The internal thermal resistance  $R_{th(i)}$  from the junction of a transistor to the case depends on the structure and material of the transistor and differs from transistor to transistor.

To measure internal thermal resistance, the case of the transistor must be cooled to maintain a constant temperature. When the case temperature  $T_c$  is held at 25 °C, the maximum allowable power dissipation,  $P_{Cmax}$ , of a transistor can be calculated using Equation (1-23):

$$P_{C \max} = \frac{T_{j \max} - T_{C}}{R_{th(i)}} = \frac{T_{j \max} - 25}{R_{th(i)}} \quad (W) \quad \dots (1-23)$$

In the datasheets for high-power transistors, the maximum allowable collector power dissipation  $P_{Cmax}$  is specified either at  $T_{C} = 25$  °C or assuming the use of an infinite heat sink.  $P_{Cmax}$  is determined by the internal thermal resistance of the transistor as indicated by Equation 1-23.

#### (2) Contact thermal resistance: R<sub>th(c)</sub>

Contact thermal resistance  $R_{th(c)}$  varies according to the condition of the contact surface between the case of a transistor and a heat sink. This condition is greatly affected by factors such as the evenness, coarseness, and area of contact, as well as the tightening of the transistor onto the heat sink. The influence of the coarseness and unevenness of the contact surface can be reduced by applying silicone grease or attaching silicone rubber.

#### (3) Insulation plate's thermal resistance: R<sub>th(s)</sub>

If it is necessary to provide electrical insulation between a transistor and a heat sink, an insulation plate must be inserted between them. The thermal resistance of this insulation plate  $R_{th(s)}$  varies with the materials, thickness, and area of the plate and is not negligible.

For packages insulated by mold resin, the thermal resistance specified for a transistor includes the insulator's thermal resistance  $R_{th(s)}$ .

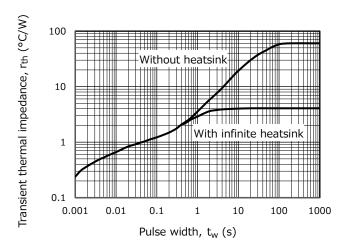

#### (4) Heat sink's thermal resistance: R<sub>th(f)</sub>

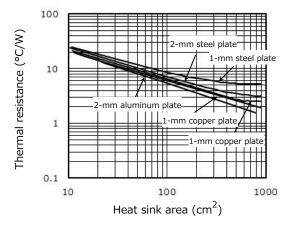

The thermal resistance of a heat sink can be considered as the distributed thermal resistance of a heat path from the surface of a heat sink to the ambient air. The thermal resistance of a heat sink depends on the condition of the ambient, a difference in temperature between the heat sink and the ambient air, and the effective area of the heat sink. It is difficult to mathematically express  $R_{th(f)}$ . At present,  $R_{th(f)}$  is obtained by measurement. Figure 1.8 shows an example of thermal resistance data measured for a transistor standing vertically at the center of a heat sink.

Various heat sinks are available from many vendors. Optimal heat sinks should be selected, referring to their technical datasheets.

Figure 1.8 Heat sink surface area vs. thermal resistance

#### 1.4. Example of thermal design calculation

This section provides examples of calculation for thermal design. The given constants or the constants that need to be found are as follows:

- (a)  $R_{th(i)}$  and  $T_{imax}$  of the transistor

- (b) Collector power dissipation of the transistor: PC

- (c) Ambient temperature: Ta

- (d) Thermal resistance of a heat sink: R<sub>th(f)</sub>

Example 1: Let's calculate the thermal resistance required for a heat sink when the  $R_{th(i)}$ ,  $T_{jmax}$ , and  $P_C$  of a transistor and the ambient temperature are predefined.

Suppose that the transistor is used at a collector power dissipation ( $P_C$ ) of 15 W and an ambient temperature ( $T_a$ ) of 60 °C.

The conditions given are  $P_{Cmax} = 80$  W (at  $T_C = 25$  °C) ,  $T_{jmax} = 150$  °C,  $P_C = 15$  W, and  $T_a = 60$  °C. Suppose that the sum of the thermal resistance of an insulating plate and silicone grease is  $R_{th(c)} + R_{th(s)} = 0.8$  °C/ W.

From Equation 1-17 and Equation 1-23,

$$R_{th (i)} = \frac{T_{j \text{ max}} - T_{C}}{P_{C \text{ max}}} = \frac{150 - 25}{80} \approx 1.6 \text{ °C / W}$$

$$R_{th(j-a)} = \frac{T_{j max} - T_a}{P_C} = \frac{150 - 60}{15} = 6 °C / W$$

From Equation (1-18),

$$R_{th\,(\,f\,)} = R_{th\,(\,j\,-\,a\,\,)} \,\, - \, \left(\,\,R_{th(\,i\,\,)} \,+\, R_{th(\,C\,\,)} \,+\, R_{th(\,s\,\,)}\,\,\right) \approx \, 6 \,\, - \, (\,\,1.6 \,+\, 0.8\,\,) \,=\, 3.6 \,\, ^{\circ}\text{C} \,\, / \,\, \text{W}$$

Therefore, a heat sink with a thermal resistance less than 3.6 °C/ W is required. Figure 1.8 shows that when we use a heat sink made of a 2-mm aluminum plate, a heat sink with an area of 200 cm $^2$  is required. Therefore, an aluminum heat sink measuring 140 × 140 × 2 mm is suitable.

Example 2: Let's calculate the maximum allowable collector power dissipation of a transistor when the  $R_{th\ (i)}$  and  $T_{jmax}$  of the transistor, the ambient temperature, and the thermal resistance of a heat sink are predefined.

Suppose that a transistor is attached to an aluminum heat sink with the size of  $100 \times 100 \times 2$  mm using an insulating plate and silicone grease and that the transistor is used at an ambient temperature ( $T_a$ ) of 60 °C. The conditions given are  $P_C = 20$  W (at  $T_C = 25$  °C),  $T_{jmax} = 150$  °C, and  $T_a = 60$  °C. From Figure 1.8,  $R_{th~(f)} = 5.4$  °C/ W. Suppose that  $R_{th(c)} + R_{th(s)} = 0.6$  °C/ W.

From Equation (1-23),

$$R_{th (i)} = \frac{T_{j \text{ max}} - 25}{P_{C \text{ max}}} = \frac{150 - 25}{20} = 6.25 \text{ °C/W}$$

From Equation (1-18),

$$R_{th(i-a)} = R_{th(i)} + R_{th(C)} + R_{th(s)} + R_{th(f)} = 6.25 + 0.6 + 5.4 = 12.25$$

°C/W

From Equation (1-14),

$$P_C = \frac{T_{j \text{ max}} - T_a}{R_{th (j-a)}} = \frac{150 - 60}{12.25} \approx 7.3 \text{ W}$$

Example 3: Let's calculate the maximum operating ambient temperature when the  $R_{th\ (i)}$ ,  $T_{jmax}$ , and  $P_C$  of a transistor and the thermal resistance of a heat sink are predefined.

Suppose that a transistor is attached to an aluminum heat sink with the size of  $100 \times 100 \times 2$  mm using an insulating plate and silicone grease. Also suppose that a transistor operates at a collector power dissipation of 15 W. The conditions given are  $P_{Cmax} = 150$  W (at  $T_C = 25$  °C) and  $T_{jmax} = 150$  °C. From Figure 1.8,  $R_{th}$  (f) = 5.4 °C/ W; hence,  $P_C = 15$  W.  $R_{th}$  (c) +  $R_{th}$  (s) = 0.7 °C/ W.

From Equation (1-23),

$$R_{\text{th (i)}} = \frac{T_{\text{j max}} - T_{\text{C}}}{P_{\text{C max}}} = \frac{150 - 25}{150} \approx 0.83 \text{ °C / W}$$

From Equation (1-18),

$$R_{th(i-a)} = R_{th(i)} + R_{th(c)} + R_{th(s)} + R_{th(f)} = 0.83 + 0.7 + 5.4 \approx 6.9 \, ^{\circ}\text{C} / W$$

From Equation (1-14),

$$T_a = T_{j \text{ max}}$$

-  $R_{th \, (\, j \, \text{-} \, a \, )}$   $P_C = 150 \, \text{-} \, 6.9 \, \times \, 15 \approx 46.5 \, ^{\circ}\text{C}$

Therefore, the maximum operating ambient temperature is 46.5 °C.

#### 1.5. Thermal design taking reliability into consideration

In addition to thermal stability and the thermal design considerations described above, reliability should be taken into account.

For industrial and other applications requiring many transistors, their maximum ratings should be derated, considering reliability.

Since the useful life of a transistor decreases exponentially with its junction temperature, reliability can be increased by derating the maximum ratings with respect to junction temperature (although the benefit of derating depends on the type of transistor). It is therefore necessary to minimize the junction temperature (i.e., the sum of the ambient temperature and a temperature rise caused by the power applied), particularly for applications requiring high reliability.

In addition, if transistors are exposed to sudden changes in junction temperature when a system is turned on and off, their internal lead bonds could suffer thermal fatigue damage owing to repeated on-off cycles. To prevent this problem, their junction temperature as well as changes in junction temperature should be considered when derating transistors.

The following is an example of thermal design calculation, considering reliability.

Example 4: Let's calculate the size of a heat sink required when the collector power dissipation and ambient temperature are predefined.

Suppose that the transistor operates at a collector power dissipation of 3 W and an ambient temperature of up to 55 °C. The conditions given are  $P_{Cmax} = 25$  W (at  $T_{C} = 25$  °C) and  $T_{jmax} = 150$  °C.

From Equation (1-23),

$$R_{th (i)} = \frac{T_{j max} - T_{C}}{P_{C max}} = \frac{150 - 25}{25} = 5 \text{ °C/W}$$

To achieve high reliability, let's derate the maximum operating junction temperature by 50 °C:

$$T_{i \text{ (opr) max}} = 150 - 50 = 100 \text{ °C}$$

From Equation (1-14),

$$R_{th \, (j-a)} = \frac{T_{j \, (opr) \, max} - T_{a \, (max)}}{P_C} = \frac{100 - 55}{3} = 15 \, {^{\circ}C} \, / \, W$$

Suppose that  $R_{th(c)} + R_{th(s)} = 0.6$  °C/ W. Then, from Equation 1-18:

$$R_{th\,(\,f\,)} = R_{th\,(\,j\,-\,a\,)} \,\, \cdot \, \left( \,\, R_{th\,(\,i\,)} \,+\, R_{th\,(\,c\,)} \,+\, R_{th\,(\,s\,)} \,\, \right) = 15 \,\, \cdot \, (\,5\,+\,0.6\,) = 9.4\,\,^{\circ}\text{C}\,/\,\,\text{W}$$

Therefore, a heat sink with a thermal resistance of less than 9.4 °C/ W is required. From Figure 1.8, an aluminum heat sink with the size of  $65 \times 65 \times 2$  mm is suitable.

#### RESTRICTIONS ON PRODUCT USE

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- · TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE

EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF

WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC

IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes,

without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life supporting

medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment,

equipment used to control combustions or explosions, safety devices, elevators and escalators, and devices related to power plant.

IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please

contact your TOSHIBA sales representative or contact us via our website.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE

FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY

WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES

OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION

AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS

RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF

MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of

Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled

substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR

LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

#### TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION

https://toshiba.semicon-storage.com/